74VHC139MTC中文资料

74系列芯片数据手册大全

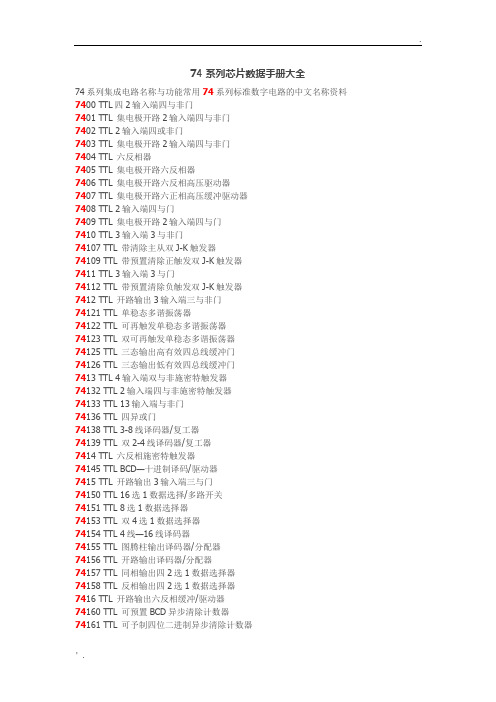

74系列芯片数据手册大全【强烈推荐】74系列集成电路名称与功能常用74系列标准数字电路的中文名称资料7400 TTL四2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压缓冲驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相高压缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D 触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器7425 双4输入端或非门(有选通端74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门缓冲器74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D触发器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D 锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器7443 4线-10线译码器(余3码输入)7444 4线-10线译码器(余3葛莱码输入) 74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动7449 4线-7段译码器74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门7452 4路2-3-2-2输入与或门7453 4路2-2-2-2输入与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器7460 双4输入与扩展器7461 三3输入与扩展器7462 4路2-3-3-2输入与或扩展器7464 4路4-2-3-2输入与或非门74645 TTL 三态输出八同相总线传送接收器7465 4路4-2-3-2输入与或非门(OC)74670 TTL 三态输出4×4寄存器堆7470 与门输入J-K触发器√7471 与或门输入J-K触发器√7472 与门输入J-K触发器7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双上升沿D触发器7476 TTL 带预置清除双J-K 触发器7478 双D型触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7487 4位二进制原码/反码7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\输出移位寄存器7497 TTL 6位同步二进制乘法器74101 与或门输入J-K触发器74102 与门输入J-K触发器74107 双主-从J-K触发器74108 双主-从J-K触发器74109 双主-从J-K触发器74110 与门输入J-K触发器74111 双主-从J-K触发器74112 双下降沿J-K触发器113 双下降沿J-K触发器114 双下降沿J-K触发器116 双4位锁存器120 双脉冲同步驱动器121 单稳态触发器122 可重触发单稳态触发器123 可重触发双稳态触发器125 四总线缓冲器126 四总线缓冲器128 四2输入端或非线驱动器132 四2输入端与非门。

74VHC14MTCX,74VHC14MX,74VHC14MTC,74VHC14M,规格书,Datasheet 资料

74VHC14Hex Schmitt InverterGeneral DescriptionThe VHC14 is an advanced high speed CMOS Hex Schmitt Inverter fabricated with silicon gate CMOS technol-ogy. It achieves the high speed operation similar to equiva-lent Bipolar Schottky TTL while maintaining the CMOS low power dissipation. Pin configuration and function are the same as the VHC04 but the inputs have hysteresis between the positive-going and negative-going input thresholds, which are capable of transforming slowly changing input signals into sharply defined, jitter-free out-put signals, thus providing greater noise margin than con-ventional inverters.An input protection circuit ensures that 0V to 7V can be applied to the input pins without regard to the supply volt-age. This device can be used to interface 5V to 3V systems and two supply systems such as battery back up. This cir-cuit prevents device destruction due to mismatched supply and input voltages.Features■High Speed: t PD= 5.5 ns (typ) at V CC= 5V■Low power dissipation: I CC= 2 μA (Max) at T A= 25°C ■High noise immunity: V NIH= V NIL= 28% V CC (Min)■Power down protection is provided on all inputs■Low noise: V OLP= 0.8V (Max)■Pin and function compatible with 74HC14Ordering Code:Order Number PackageNumberPackage Description74VHC14M(Note 1)M14A14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow74VHC14MX_NL (Note 2)M14A Pb-Free 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150"Narrow74VHC14SJ(Note 1)M14D Pb-Free 14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide74VHC14MTC(Note 1)MTC1414-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide74VHC14MTC_NL (Note 3)MTC14Pb-Free 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153,4.4mm Wide74VHC14MTCX_NL (Note 2)MTC14Pb-Free 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153,4.4mm Wide74VHC14N(Obsolete)N14A14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" WidePb-Free package per JEDEC J-STD-020B.Note 1: Surface mount packages are also available on Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.Note 2: “_NL” indicates Pb-Free product (per JEDEC J-STD-020B). Device is available in Tape and Reel only.Note 3: “_NL” indicates Pb-Free product (per JEDEC J-STD-020B).© 2010 Fairchild Semiconductor Corporation Logic Symbol/sIEEE/IECPin DescriptionsPin Names DescriptionA n InputsO n OutputsConnection Diagram/sTruth Table/sA OL HH L2Absolute Maximum Ratings(Note 4)Supply Voltage (V CC)−0.5V to +7.0V DC Input Voltage (V IN)−0.5V to +7.0V DC Output Voltage (V OUT)−0.5V to V CC+ 0.5V Input Diode Current (I IK)−20 mA Output Diode Current (I OK)±20 mA DC Output Current (I OUT)±25 mA DC V CC/GND Current (I CC)±50 mA Storage Temperature (T STG)−65°C to +150°C Lead Temperature (T L)Soldering (10 seconds)260°C Recommended Operating Conditions (Note 5)Supply Voltage (V CC)+2.0V to +5.5V Input Voltage (V IN)0V to +5.5V Output Voltage (V OUT)0V to V CC Operating Temperature (T OPR)−40°C to +85°C Note 4: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. The data book specifica-tions should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading vari-ables. Fairchild does not recommend operation outside databook specifica-tions.Note 5: Unused inputs must be held HIGH or LOW. They may not float.DC Electrical CharacteristicsSymbol Parameter V CCT A= 25°C T A=−40°C to +85°CUnits Conditions Min Typ Max Min MaxV P Positive Threshold Voltage 3.0 2.20 2.204.5 3.15 3.15V5.5 3.85 3.85V N Negative Threshold Voltage 3.00.900.904.5 1.35 1.35V5.5 1.65 1.65V H Hysteresis Voltage 3.00.30 1.200.30 1.204.50.40 1.400.40 1.40V5.50.50 1.600.50 1.60V OH HIGH Level Output Voltage 2.0 1.9 2.0 1.9V IN=V IL3.0 2.9 3.0 2.9V I OH=−50 μA4.5 4.4 4.5 4.43.0 2.58 2.48V I OH=−4 mA4.5 3.94 3.80I OH=−8 mA V OL LOW Level Output Voltage 2.00.00.10.1V IN= V IH3.00.00.10.1V I OL= 50 μA4.50.00.10.13.00.360.44V I OL= 4 mA4.50.360.44I OL= 8 mAI IN Input Leakage Current0–5.5±0.1±1.0μA V IN= 5.5V or GNDI CC Quiescent Supply Current 5.5 2.020.0μA V IN= V CC or GND Noise CharacteristicsSymbol Parameter V CCT A= 25°CUnits Conditions Typ LimitsV OLP (Note 6)Quiet Output Maximum Dynamic V OL5.00.40.8VC L= 50 pFV OLV (Note 6)Quiet Output Minimum Dynamic V OL5.0−0.4−0.8VC L= 50 pFV IHD (Note 6)Minimum HIGH Level Dynamic Input Voltage5.0 3.5VC L= 50 pFV ILD (Note 6)Maximum LOW Level Dynamic Input Voltage5.0 1.5VC L= 50 pFNote 6: Parameter guaranteed by design.AC Electrical CharacteristicsSymbol Parameter V CCT A= 25°C T A=−40°C to +85°CUnits Conditions Min Typ Max Min Maxt PLH Propagation Delay 3.3 ± 0.38.312.8 1.015.0ns C L= 15 pFt PHL Time10.816.3 1.018.5C L= 50 pF5.0 ± 0.5 5.58.6 1.010.0ns C L= 15 pF7.010.6 1.012.0C L= 50 pFC IN Input Capacitance41010pF V CC= OpenC PD Power Dissipation Capacitance21pF(Note 7)Note 7: C PD is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load. Average operating current can be obtained by the equation: I CC (Opr) = C PD * V CC * f IN+ I CC/6 (per Gate)468。

74VHC139MTR;74VHC139TTR;中文规格书,Datasheet资料

1/1November 2004s HIGH SPEED: t PD = 5.0 ns (TYP.) at V CC = 5V sLOW POWER DISSIPATION:I CC = 4 µA (MAX.) at T A =25°C sHIGH NOISE IMMUNITY:V NIH = V NIL = 28% V CC (MIN.)s POWER DOWN PROTECTION ON INPUTS sSYMMETRICAL OUTPUT IMPEDANCE:|I OH | = I OL = 8 mA (MIN)sBALANCED PROPAGATION DELAYS:t PLH ≅ t PHLsOPERATING VOLTAGE RANGE:V CC (OPR) = 2V to 5.5VsPIN AND FUNCTION COMPATIBLE WITH 74 SERIES 139sIMPROVED LATCH-UP IMMUNITYDESCRIPTIONThe 74VHC139 is an advanced high-speed CMOS DUAL 2 TO 4 LINE DECODER/DEMULTIPLEXER fabricated with sub-micron silicon gate and double-layer metal wiring C 2MOS technology.The active low enable input can be used for gating or as a data input for demultiplexing applications.While the enable input is held high, all four outputs are high independently of the other inputs.Power down protection is provided on all input and 0 to 7V can be accepted on inputs with n regard to the supply voltage. This device can b used to interface 5V to 3V.All inputs and outputs are equipped wit protection circuits against static discharge, givin them 2KV ESD immunity and transient exces voltage.74VHC139DUAL 2 TO 4 DECODER/DEMULTIPLEXERFigure 1: Pin Connection And IEC Logic SymbolsTable 1: Order CodesPACKAGE T & RSOP 74VHC139MTR TSSOP74VHC139TTRd u c t (s ) - O b s o le t e P r o d u c t (s ) l e t e P r o d u c t (s ) - O b s o l e t e P r o dl e t e P r o d u c t (s ) 2/12Figure 2: Input Equivalent Circuit Table 2: Pin DescriptionTable 3: Truth TableX : Don’t careFigure 3: Logic DiagramPIN N°SYMBOL NAME AND FUNCTION 1, 15 1G, 2G Enable Inputs 2, 31A, 1B Address Inputs 4, 5, 6, 71Y0 to 1Y3Outputs 12, 11, 10, 9 2Y0 to 2Y3Outputs14, 132A, 2B Address Inputs 8GND Ground (0V)16V CCPositive Supply VoltageINPUTSOUTPUTSENABLESELECTG BAY0Y1Y2Y3HX X H H H H L L L L H H H L L H H L H H L H L H H L H LHHHHHL- O b s o l e t e P r o d u c t (Ob s o l e t e P r o d uc t (s ) - O b s o l e t e P r od u c t (s ) 3/1Table 4: Absolute Maximum RatingsAbsolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions not impliedTable 5: Recommended Operating Conditions1) V IN from 30% to 70% of V CCSymbol ParameterValue Unit V CC Supply Voltage -0.5 to +7.0V V I DC Input Voltage -0.5 to +7.0V V O DC Output Voltage -0.5 to V CC + 0.5V I IK DC Input Diode Current - 20mA I OK DC Output Diode Current ± 20mA I ODC Output Current± 25mA I CC or I GND DC V CC or Ground Current± 75mA T stgStorage Temperature -65 to +150°C T LLead Temperature (10 sec)300°CSymbol ParameterValueUnit V CC Supply Voltage 2 to 5.5V V I Input Voltage 0 to 5.5VV OOutput Voltage0 to V CC VT opOperating Temperature-55 to 125°Cdt/dvInput Rise and Fall Time (note 1) (V CC = 3.3 ± 0.3V) (V CC = 5.0 ± 0.5V)0 to 1000 to 20ns/VO b s o l e t e P r o d u c t (s ) - O b s o l e t e P r o d u c t (Ob s ol e t e P r o d u c t (s ) - O b s o l e t e P r o d u c t (s ) 4/12Table 6: DC SpecificationsTable 7: AC Electrical Characteristics (Input t r = t f = 3ns)(*) Voltage range is 3.3V ± 0.3V (**) Voltage range is 5.0V ± 0.5VSymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.V IHHigh Level Input Voltage2.0 1.5 1.5 1.5V3.0 to 5.50.7V CC0.7V CC0.7V CCV ILLow Level Input Voltage2.00.50.50.5V3.0 to 5.50.3V CC0.3V CC0.3V CCV OHHigh Level Output Voltage2.0I O =-50 µA1.92.0 1.9 1.9V3.0I O =-50 µA 2.9 3.0 2.9 2.94.5I O =-50 µA 4.44.54.44.43.0I O =-4 mA 2.582.48 2.44.5I O =-8 mA 3.943.83.7V OLLow Level OutputVoltage2.0I O =50 µA 0.00.10.10.1V3.0I O =50 µA 0.00.10.10.14.5I O =50 µA 0.00.10.10.13.0I O =4 mA 0.360.440.554.5I O =8 mA0.360.440.55I I Input Leakage Current0 to 5.5V I = 5.5V or GND ± 0.1± 1± 1µA I CCQuiescent Supply Current5.5V I = V CC or GND44040µASymbol ParameterTest Condition ValueUnitV CC (V)C L (pF)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.t PLH t PHLPropagation Delay TimeA, B to Y3.3(*)157.211.0 1.013.0 1.013.0ns3.3(*)509.714.5 1.016.5 1.016.55.0(**)15 5.07.2 1.08.51.08.55.0(**)50 6.59.2 1.010.5 1.010.5t PLH t PHLPropagation Delay Time G to Y3.3(*)15 6.49.2 1.011.0 1.011.0ns3.3(*)508.912.7 1.014.5 1.014.55.0(**)15 4.4 6.3 1.07.5 1.07.55.0(**)505.98.31.09.51.09.5O b s o l e t e P r o d u c t (s ) - O b s o l e t e P r o d u c t ((s 5/1Table 8: Capacitive Characteristics1) C PD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption withou load. (Refer to Test Circuit). Average operating current can be obtained by the following equation. I CC(opr) = C PD x V CC x f IN + I CC /2 (per Decoder)Figure 4: Test CircuitC L =15/50pF or equivalent (includes jig and probe capacitance)R T = Z OUT of pulse generator (typically 50Ω)Figure 5: Waveform - Propagation Delays For Inverting Outputs (f=1MHz; 50% duty cycle)SymbolParameterTest ConditionValue UnitT A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.C IN Input Capacitance 4101010pF C PDPower Dissipation Capacitance (note 1)26pFPOb s ol e t e P r o d u c t (s ) - O b s o l e t e P r o d u 6/12Figure 6: Waveform - Propagation Delays For Non-inverting Outputs (f=1MHz; 50% duty cycle)O b s o l e t e P r o d u c t (s ) - O b s o l e tO b s ol e te Pr o du ct(s)-O bs ol e te Pr o du ct(s)7/1 DIM.mm.inchMIN.TYP MAX.MIN.TYP.MAX.A 1.750.068a10.10.250.0040.010 a2 1.640.063 b0.350.460.0130.018 b10.190.250.0070.010 C0.50.019c145° (typ.)D9.8100.3850.393E 5.8 6.20.2280.244e 1.270.050e38.890.350F 3.8 4.00.1490.157G 4.6 5.30.1810.208L0.5 1.270.0190.050 M0.620.024 S8° (max.)SO-16 MECHANICAL DATA0016020D O bs ol e te Pr o du ct(s)-O bs ol e te Pr o du ct(Ob s ol e t e P r o d u c t (s ) - O b s o l e t e P r o d u c t (s ) 8/12DIM.mm.inchMIN.TYPMAX.MIN.TYP.MAX.A 1.20.047A10.050.150.0020.0040.006A20.81 1.050.0310.0390.041b 0.190.300.0070.012c0.090.200.0040.0079D 4.955.10.1930.1970.201E6.26.4 6.60.2440.2520.260E1 4.34.44.480.1690.1730.176e0.65 BSC0.0256 BSCK 0˚8˚0˚8˚L0.450.600.750.0180.0240.030TSSOP16 MECHANICAL DATAc Eb A2A E1D1PIN 1 IDENTIFICATIONA1LKe0080338DO b s o l e t e P r o d u c t (s ) - O b s o l e t e P r o d u c t (O b s ol e te Pr o du ct(s)-O bs ol e te Pr o du ct(s)9/1 DIM.mm.inchMIN.TYP MAX.MIN.TYP.MAX.A33012.992 C12.813.20.5040.519 D20.20.795N60 2.362T22.40.882 Ao 6.45 6.650.2540.262 Bo10.310.50.4060.414 Ko 2.1 2.30.0820.090 Po 3.9 4.10.1530.161 P7.98.10.3110.319Tape & Reel SO-16 MECHANICAL DATAO bs ol e te Pr o du ct(s)-O bs ol e te Pr o du ct(O b s ol e te Pr o du ct(s)-O bs ol e te Pr o du ct(s)10/12DIM.mm.inchMIN.TYP MAX.MIN.TYP.MAX. A33012.992 C12.813.20.5040.519 D20.20.795N60 2.362T22.40.882 Ao 6.7 6.90.2640.272 Bo 5.3 5.50.2090.217 Ko 1.6 1.80.0630.071 Po 3.9 4.10.1530.161 P7.98.10.3110.319 Tape & Reel TSSOP16 MECHANICAL DATAO b s ol e te Pr o du ct(s)-O bs ol e te Pr o du ct(分销商库存信息:STM74VHC139MTR74VHC139TTR。

74系列各个芯片详细介绍

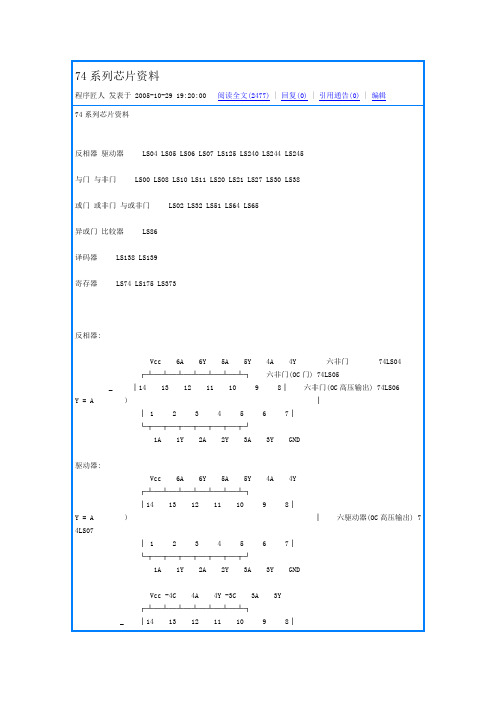

74系列芯片资料程序匠人发表于 2005-10-29 19:20:00 阅读全文(2477) | 回复(0) | 引用通告(0) | 编辑74系列芯片资料反相器驱动器 LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245与门与非门 LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38或门或非门与或非门 LS02 LS32 LS51 LS64 LS65异或门比较器 LS86译码器 LS138 LS139寄存器 LS74 LS175 LS373反相器:Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04┌┴─┴─┴─┴─┴─┴─┴┐六非门(OC门) 74LS05_ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06Y = A )││ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GND驱动器:Vcc 6A 6Y 5A 5Y 4A 4Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│Y = A )│六驱动器(OC高压输出) 74LS07│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GNDVcc -4C 4A 4Y -3C 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐_ │14 13 12 11 10 9 8│Y =A+C )│四总线三态门 74LS125│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘-1C 1A 1Y -2C 2A 2Y GNDVcc -G B1 B2 B3 B4 B8 B6 B7 B8┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8位总线驱动器 74LS245 │20 19 18 17 16 15 14 13 12 11│)│ DIR=1 A=>B│ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘DIR A1 A2 A3 A4 A5 A6 A7 A8 GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑与门,与非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│Y = AB )│ 2输入四正与门 74LS08 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐__ │14 13 12 11 10 9 8│Y = AB )│ 2输入四正与非门 74LS00 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 1C 1Y 3C 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐___ │14 13 12 11 10 9 8│Y = ABC )│ 3输入三正与非门 74LS10 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 2A 2B 2C 2Y GNDVcc H G Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│)│ 8输入与非门 74LS30│ 1 2 3 4 5 6 7│ ________└┬─┬─┬─┬─┬─┬─┬┘ Y = ABCDEFGHA B C D E F GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑或门,或非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐ 2输入四或门 74LS32│14 13 12 11 10 9 8│)│ Y = A+B│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4Y 4B 4A 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐ 2输入四或非门 74LS02│14 13 12 11 10 9 8│ ___)│ Y = A+B│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Y 1A 1B 2Y 2A 2B GNDVcc 2Y 2B 2A 2D 2E 1F┌┴─┴─┴─┴─┴─┴─┴┐双与或非门 74S51│14 13 12 11 10 9 8│ _____)│ 2Y = AB+DE│ 1 2 3 4 5 6 7│ _______└┬─┬─┬─┬─┬─┬─┬┘ 1Y = ABC+DEF1Y 1A 1B 1C 1D 1E GNDVcc D C B K J Y┌┴─┴─┴─┴─┴─┴─┴┐ 4-2-3-2与或非门 74S64 74S65(OC门) │14 13 12 11 10 9 8│ ______________)│ Y = ABCD+EF+GHI+JK│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘A E F G H I GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器2输入四异或门 74LS86Vcc 4B 4A 4Y 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│)│ _ _│ 1 2 3 4 5 6 7│ Y=AB+AB└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2Y 2A 2B GND8*2输入比较器 74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8*2输入比较器 74LS688│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器3-8译码器 74LS138Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6 __ _ _ _ __ _ _ __ _ _ __ _ ┌┴─┴─┴─┴─┴─┴─┴─┴┐ Y0=A B C Y1=A B B Y2=A B C Y3=A B C │16 15 14 13 12 11 10 9 │)│ __ _ _ __ _ __ _ __│ 1 2 3 4 5 6 7 8│ Y4=A B C Y5=A B C Y6=A B C Y7=A B C └┬─┬─┬─┬─┬─┬─┬─┬┘A B C -CS0 -CS1 CS2 -Y7 GND双2-4译码器 74LS139Vcc -2G 2A 2B -Y0 -Y1 -Y2 -Y3 __ __ __ __ __ __ __ __┌┴─┴─┴─┴─┴─┴─┴─┴┐ Y0=2A 2B Y1=2A 2B Y2=2A 2B Y3=2A 2B │16 15 14 13 12 11 10 9 │)│ __ __ __ __ __ __ __ __│ 1 2 3 4 5 6 7 8│ Y0=1A 1B Y1=1A 1B Y2=1A 1B Y3=1A 1B └┬─┬─┬─┬─┬─┬─┬─┬┘-1G 1A 1B -Y0 -Y1 -Y2 -Y3 GND8*2输入比较器 74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8*2输入比较器 74LS688│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8寄存器:Vcc 2CR 2D 2Ck 2St 2Q -2Q┌┴─┴─┴─┴─┴─┴─┴┐双D触发器 74LS74│14 13 12 11 10 9 8 │)││ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Cr 1D 1Ck 1St 1Q -1Q GNDVcc 8Q 8D 7D 7Q 6Q 6D 5D 5Q ALE┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8位锁存器 74LS373│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘-OE 1Q 1D 2D 2Q 3Q 3D 4D 4Q GND型号器件名称厂牌[数据表]SN7400四2输入端与非门 TI[DATA]SN7401四2输入端与非门(OC) SN7402四2输入端或非门 TI[DATA]SN7403四2输入端与非门(OC)TI[DATA]SN7404六反相器 TI[DATA]SN7405六反相器(OC)TI[DATA]SN7406六高压输出反相器 (OC,30V)TI[DATA]SN7407六高压输出缓冲,驱动器(OC,30V)TI[DATA]SN7408四2输入端与门 TI[DATA]SN7409四2输入端与门(OC)TI[DATA]SN7410三3输入端与非门 TI[DATA]SN7412三3输入端与非门(OC)TI[DATA]SN7413双4输入端与非门 TI[DATA]SN7414六反相器TI[DATA]SN7416六高压输出反相缓冲/驱动器 I[DATA]SN7417六高压输出缓冲/驱动器(OC,15V)TI[DATA]SN7420双4输入端与非门 TI[DATA]SN7422双4输入端与非门(OC)TI[DATA]SN7423可扩展双4输入端或非门 TI[DATA]SN7425双4输入端或非门TI[DATA]SN7426四2输入端高压输出与非缓冲器 [DATA]SN7427三3输入端或非门TI[DATA]SN7428四2输入端或非缓冲器 I[DATA]SN74308输入端与非门TI[DATA]SN7432四2输入端或门。

74系列功能大全(中文)

74系列功能大全(中文)74、74HC、74LS系列芯片资料,从网上下的,集合了一下系列电平典型传输延迟ns 最大驱动电流(-Ioh/Lol)mAAHC CMOS 8.5 -8/8AHCT COMS/TTL 8.5 -8/8HC COMS 25 -8/8HCT COMS/TTL 25 -8/8ACT COMS/TTL 10 -24/24F TTL 6.5 -15/64ALS TTL 10 -15/64LS TTL 18 -15/24注:同型号的74系列、74HC系列、74LS系列芯片,逻辑功能上是一样的。

74LSxx的使用说明如果找不到的话,可参阅74xx或74HCxx的使用说明。

有些资料里包含了几种芯片,如74HC161资料里包含了74HC160、74HC161、74HC162、74HC163四种芯片的资料。

找不到某种芯片的资料时,可试着查看一下临近型号的芯片资料。

7400 QUAD 2-INPUT NAND GATES 与非门7401 QUAD 2-INPUT NAND GATES OC 与非门7402 QUAD 2-INPUT NOR GATES 或非门7403 QUAD 2-INPUT NAND GATES 与非门7404 HEX INVERTING GATES 反向器7406 HEX INVERTING GATES HV 高输出反向器7408 QUAD 2-INPUT AND GATE 与门7409 QUAD 2-INPUT AND GATES OC 与门7410 TRIPLE 3-INPUT NAND GATES 与非门7411 TRIPLE 3-INPUT AND GATES 与门74121 ONE-SHOT WITH CLEAR 单稳态74132 SCHMITT TRIGGER NAND GATES 触发器与非门7414 SCHMITT TRIGGER INVERTERS 触发器反向器74153 4-LINE TO 1 LINE SELECTOR 四选一74155 2-LINE TO 4-LINE DECODER 译码器74180 PARITY GENERATOR/CHECKER 奇偶发生检验74191 4-BIT BINARY COUNTER UP/DOWN 计数器7420 DUAL 4-INPUT NAND GATES 双四输入与非门7426 QUAD 2-INPUT NAND GATES 与非门7427 TRIPLE 3-INPUT NOR GATES 三输入或非门7430 8-INPUT NAND GATES 八输入端与非门7432 QUAD 2-INPUT OR GATES 二输入或门7438 2-INPUT NAND GATE BUFFER 与非门缓冲器7445 BCD-DECIMAL DECODER/DRIVER BCD译码驱动器7474 D-TYPE FLIP-FLOP D型触发器7475 QUAD LATCHES 双锁存器7476 J-K FLIP-FLOP J-K触发器7485 4-BIT MAGNITUDE COMPARATOR 四位比较器7486 2-INPUT EXCLUSIVE OR GATES 双端异或门74HC00 QUAD 2-INPUT NAND GATES 双输入与非门74HC02 QUAD 2-INPUT NOR GATES 双输入或非门74HC03 2-INPUT OPEN-DRAIN NAND GATES 与非门74HC04 HEX INVERTERS 六路反向器74HC05 HEX INVERTERS OPEN DRAIN 六路反向器74HC08 2-INPUT AND GATES 双输入与门74HC107 J-K FLIP-FLOP WITH CLEAR J-K触发器74HC109A J-K FLIP-FLOP W/PRESET J-K触发器74HC11 TRIPLE 3-INPUT AND GATES 三输入与门74HC112 DUAL J-K FLIP-FLOP 双J-K触发器74HC113 DUAL J-K FLIP-FLOP PRESET 双JK触发器74HC123A RETRIGGERABLE MONOSTAB 可重触发单稳74HC125 TRI-STATE QUAD BUFFERS 四个三态门74HC126 TRI-STATE QUAD BUFFERS 六三态门74HC132 2-INPUT TRIGGER NAND 施密特触发与非门74HC133 13-INPUT NAND GATES 十三输入与非门74HC137 3-TO-8 DECODERS W/LATCHES 3-8线译码器74HC138 3-8 LINE DECODER 3线至8线译码器74HC139 2-4 LINE DECODER 2线至4线译码器74HC14 TRIGGERED HEX INVERTER 六触发反向器74HC147 10-4 LINE PRIORITY ENCODER 10-4编码器74HC148 8-3 LINE PRIORITY ENCODER 8-3编码器74HC149 8-8 LINE PRIORITY ENCODER 8-8编码器74HC151 8-CHANNEL DIGITAL MUX 8通道多路器74HC153 DUAL 4-INPUT MUX 双四输入多路器74HC154 4-16 LINE DECODER 4线至16线译码器74HC155 2-4 LINE DECODER 2线至4线译码器74HC157 QUAD 2-INPUT MUX 四个双端多路器74HC161 BINARY COUNTER 二进制计数器74HC163 DECADE COUNTERS 十进制计数器74HC164 SERIAL-PARALLEL SHIFT REG 串入并出74HC165 PARALLEL-SERIAL SHIFT REG 并入串出74HC166 SERIAL-PARALLEL SHIFT REG 串入并出74HC173 TRI-STATE D FLIP-FLOP 三态D触发器74HC174 HEX D FLIP-FLOP W/CLEAR 六D触发器74HC175 HEX D FLIP-FLOP W/CLEAR 六D触发器74HC181 ARITHMETIC LOGIC UNIT 算术逻辑单元74HC182 LOOK AHEAD CARRYGENERATR 进位发生器74HC190 BINARY UP/DN COUNTER 二进制加减计数器74HC191 DECADE UP/DN COUNTER 十进制加减计数器74HC192 DECADE UP/DN COUNTER 十进制加减计数器74HC193 BINARY UP/DN COUNTER 二进制加减计数器74HC194 4BIT BI-DIR SHIFT 4位双向移位寄存器74HC195 4BIT PARALLEL SHIFT 4位并行移位寄存器74HC20 QUAD 4-INPUT NAND GATE 四个四入与非门74HC221A NON-RETRIG MONOSTAB 不可重触发单稳74HC237 3-8 LINE DECODER 地址锁3线至8线译码器74HC242/243 TRI-STAT TRANSCEIVER 三态收发器74HC244 OCTAL 3-STATE BUFFER 八个三态缓冲门74HC245 OCTAL 3-STATE TRANSCEIVER 三态收发器74HC251 8-CH 3-STATE MUX 8路3态多路器74HC253 DUAL 4-CH 3-STATE MUX 4路3态多路器74HC257 QUAD 2-CH 3-STATE MUX 4路3态多路器74HC258 2-CH 3-STATE MUX 2路3态多路器74HC259 3-8 LINE DECODER 8位地址锁存译码器74HC266A 2-INPUT EXCLUSIVE NOR GATE 异或非74HC27 TRIPLE 3-INPUT NOR GATE三个3输入或非门74HC273 OCTAL D FLIP-FLOP CLEAR 8路D触发器74HC280 9BIT ODD/EVEN GENERATOR 奇偶发生器74HC283 4BIT BINARY ADDER CARRY 四位加法器74HC299 3-STATE UNIVERSAL SHIFT 三态移位寄存74HC30 8-INPUT NAND GATE 8输入端与非门74HC32 QUAD 2-INPUT OR GATE 四个双端或门74HC34 NON-INVERTER 非反向器74HC354 8-CH 3-STATE MUX 8路3态多路器74HC356 8-CH 3-STATE MUX 8路3态多路器74HC365 HEX 3-STATE BUFFER 六个三态缓冲门74HC366 3-STATE BUFFER INVERTER 缓冲反向器74HC367 3-STATE BUFFER INVERTER 缓冲反向器74HC368 3-STATE BUFFER INVERTER 缓冲反向器74HC373 3-STATE OCTAL D LATCHES 三态D型锁存器74HC374 3-STATE OCTAL D FLIPFLOP 三态D触发器74HC393 4-BIT BINARY COUNTER 4位二进制计数器74HC4016 QUAD ANALOG SWITCH 四路模拟量开关74HC4020 14-Stage Binary Counter 14输出计数器74HC4017 Decade Counter/Divider with 10 Decoded Outputs 十进制计数器带10个译码输出端74HC4040 12 Stage Binary Counter 12出计数器74HC4046 PHASE LOCK LOOP 相位监测输出器74HC4049 LEVEL DOWN CONVERTER 电平变低器74HC4050 LEVEL DOWN CONVERTER 电平变低器74HC4051 8-CH ANALOG MUX 8通道多路器74HC4052 4-CH ANALOG MUX 4通道多路器74HC4053 2-CH ANALOG MUX 2通道多路器74HC4060 14-STAGE BINARY COUNTER 14阶BIN计数74HC4066 QUAD ANALOG MUX 四通道多路器74HC4075 TRIPLE 3-INPUT OR GATE 3输入或门74HC42 BCD TO DECIMAL BCD转十进制译码器74HC423A RETRIGGERABLE MONOSTAB 可重触发单稳74HC4511 BCD-7 SEG DRIVER/DECODER 7段译码器74HC4514 4-16 LINE DECODER 4至16线译码器74HC4538A RETRIGGERAB MONOSTAB 可重触发单稳74HC4543 LCD BCD-7 SEG LCD用的BCD-7段译码驱动74HC51 AND OR GATE INVERTER 与或非门74HC521 8BIT MAGNITUDE COMPARATOR 判决定路74HC533 3-STATE D LATCH 三态D锁存器74HC534 3-STATE D FLIP-FLOP 三态D型触发器74HC540 3-STATE BUFFER 三态缓冲器74HC541 3-STATE BUFFER INVERTER三态缓冲反向器74HC58 DUAL AND OR GATE 与或门74HC589 3STATE 8BIT SHIFT 8位移位寄存三态输出74HC594 8BIT SHIFT REG 8位移位寄存器74HC595 8BIT SHIFT REG 8位移位寄存器出锁存74HC597 8BIT SHIFT REG 8位移位寄存器入锁存74HC620 3-STATE TRANSCEIVER 反向3态收发器74HC623 3-STATE TRANSCEIVER 八路三态收发器74HC640 3-STATE TRANSCEIVER 反向3态收发器74HC643 3-STATE TRANSCEIVER 八路三态收发器74HC646 NON-INVERT BUS TRANSCEIVER 总线收发器74HC648 INVERT BUS TRANCIVER 反向总线收发器74HC688 8BIT MAGNITUDE COMPARATOR 8位判决电路74HC7266 2-INPUT EXCLUSIVE NOR GATE 异或非门74HC73 DUAL J-K FLIP-FLOP W/CLEAR 双JK触发器74HC74A PRESET/CLEAR D FLIP-FLOP 双D触发器74HC75 4BIT BISTABLE LATCH 4位双稳锁存器74HC76 PRESET/CLEAR JK FLIP-FLOP 双JK触发器74HC85 4BIT MAGNITUDE COMPARATOR 4位判决电路74HC86 2INPUT EXCLUSIVE OR GATE 2输入异或门74HC942 BAUD MODEM 300BPS低速调制解调器74HC943 300 BAUD MODEM 300BPS低速调制解调器74LS00 QUAD 2-INPUT NAND GATES 与非门74LS02 QUAD 2-INPUT NOR GATES 或非门74LS03 QUAD 2-INPUT NAND GATES 与非门74LS04 HEX INVERTING GATES 反向器74LS05 HEX INVERTERS OPEN DRAIN 六路反向器74LS08 QUAD 2-INPUT AND GATE 与门74LS09 QUAD 2-INPUT AND GATES OC 与门74LS10 TRIPLE 3-INPUT NAND GATES 与非门74LS109 QUAD 2-INPUT AND GATES OC 与门74LS11 TRIPLE 3-INPUT AND GATES 与门74LS112 DUAL J-K FLIP-FLOP 双J-K触发器74LS113 DUAL J-K FLIP-FLOP PRESET 双JK触发器74LS114 NEGATIVE J-K FLIP-FLOP 负沿J-K触发器74LS122 Retriggerable Monostab 可重触发单稳74LS123 Retriggerable Monostable 可重触发单稳74LS125 TRI-STATE QUAD BUFFERS 四个三态门74LS13 QUAL 4-in NAND TRIGGER 4输入与非触发器74LS160 BCD DECADE 4BIT BIN COUNTERS 计数器74LS136 QUADRUPLE 2-INPUT XOR GATE 异或门74LS138 3-8 LINE DECODER 3线至8线译码器74LS139 2-4 LINE DECODER 2线至4线译码器74LS14 TRIGGERED HEX INVERTER 六触发反向器74HC147 10-4 LINE PRIORITY ENCODER 10-4编码器74HC148 8-3 LINE PRIORITY ENCODER 8-3编码器74HC149 8-8 LINE PRIORITY ENCODER 8-8编码器74LS151 8-CHANNEL DIGITAL MUX 8通道多路器74LS153 DUAL 4-INPUT MUX 双四输入多路器74LS155 2-4 LINE DECODER 2线至4线译码器74LS156 2-4 LINE DECODER/DEMUX 2-4译码器74LS157 QUAD 2-INPUT MUX 四个双端多路器74LS158 2-1 LINE MUX 2-1线多路器74LS160A BINARY COUNTER 二进制计数器74LS161A BINARY COUNTER 二进制计数器74LS162A BINARY COUNTER 二进制计数器74LS163A DECADE COUNTERS 十进制计数器74LS164 SERIAL-PARALLEL SHIFT REG 串入并出74LS168 BI-DIRECT BCD TO DECADE 双向计数器74LS169 4BIT UP/DN BIN COUNTER 四位加减计数器74LS173 TRI-STATE D FLIP-FLOP 三态D触发器74LS174 HEX D FLIP-FLOP W/CLEAR 六D触发器74LS175 HEX D FLIP-FLOP W/CLEAR 六D触发器74LS190 BINARY UP/DN COUNTER 二进制加减计数器74LS191 DECADE UP/DN COUNTER 十进制加减计数器74LS192 DECADE UP/DN COUNTER 十进制加减计数器74LS193 BINARY UP/DN COUNTER 二进制加减计数器74LS194A 4BIT BI-DIR SHIFT 4位双向移位寄存器74LS195A 4BIT PARALLEL SHIFT4位并行移位寄存器74LS20 QUAD 4-INPUT NAND GATE 四个四入与非门74LS21 4-INPUT AND GATE 四输入端与门74LS240 OCTAL 3-STATE BUFFER 八个三态缓冲门74LS244 OCTAL 3-STATE BUFFER 八个三态缓冲门74LS245 OCTAL 3-STATE TRANSCEIVER 三态收发器74LS253 DUAL 4-CH 3-STATE MUX 4路3态多路器74LS256 4BIT ADDRESS LATCH 四位可锁存锁存器74LS257 QUAD 2-CH 3-STATE MUX 4路3态多路器74LS258 2-CH 3-STATE MUX 2路3态多路器74LS27 TRIPLE 3-INPUT NOR GATES 三输入或非门74LS279 QUAD R-S LATCHES 四个RS非锁存器74LS28 QUAD 2-INPUT NOR BUFFER 四双端或非缓冲74LS283 4BIT BINARY ADDER CARRY 四位加法器74LS30 8-INPUT NAND GATES 八输入端与非门74LS32 QUAD 2-INPUT OR GATES 二输入或门74LS352 4-1 LINE SELECTOR/MUX 4-1线选择多路器74LS365 HEX 3-STATE BUFFER 六个三态缓冲门74LS367 3-STATE BUFFER INVERTER 缓冲反向器74LS368A 3-STATE BUFFER INVERTER 缓冲反向器74LS373 OCT LATCH W/3-STATE OUT三态输出锁存器74LS76 Dual JK Flip-Flop w/set 2个JK触发器74LS379 QUAD PARALLEL REG 四个并行寄存器74LS38 2-INPUT NAND GATE BUFFER 与非门缓冲器74LS390 DUAL DECADE COUNTER 2个10进制计数器74LS393 DUAL BINARY COUNTER 2个2进制计数器74LS42 BCD TO DECIMAL BCD转十进制译码器74LS48 BCD-7 SEG BCD-7段译码器74LS49 BCD-7 SEG BCD-7段译码器74LS51 AND OR GATE INVERTER 与或非门74LS540 OCT Buffer/Line Driver 8路缓冲驱动器74LS541 OCT Buffer/LineDriver 8路缓冲驱动器74LS74 D-TYPE FLIP-FLOP D型触发器74LS682 8BIT MAGNITUDE COMPARATOR 8路比较器74LS684 8BIT MAGNITUDE COMPARATOR 8路比较器74LS75 QUAD LATCHES 双锁存器74LS83A 4BIT BINARY ADDER CARRY 四位加法器74LS85 4BIT MAGNITUDE COMPARAT 4位判决电路74LS86 2INPUT EXCLUSIVE OR GATE 2输入异或门74LS90 DECADE/BINARY COUNTER 十/二进制计数器74LS95B 4BIT RIGHT/LEFT SHIFT 4位左右移位寄存74LS688 8BIT MAGNITUDE COMPARAT 8位判决电路74LS136 2-INPUT XOR GATE 2输入异或门74LS651 BUS TRANSCEIVERS 总线收发器74LS653 BUS TRANSCEIVERS 总线收发器74LS670 3-STATE 4-BY-4 REG 3态4-4寄存器74LS73A DUAL J-K FLIP-FLOP W/CLEAR 双JK触发器。

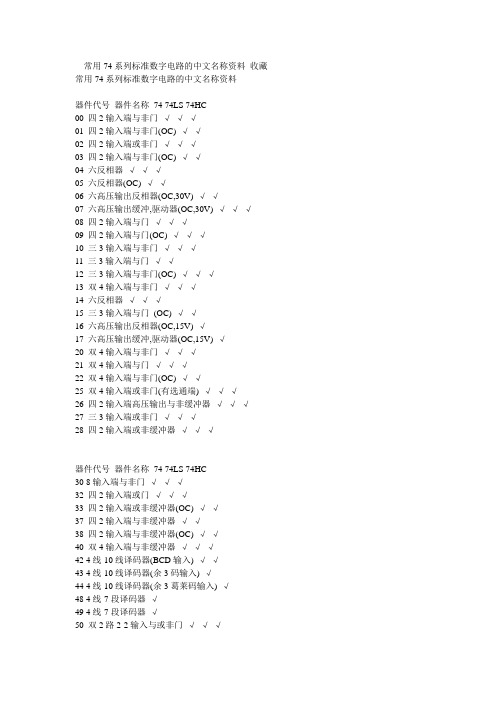

常用74系列标准数字电路的中文名称资料

常用74系列标准数字电路的中文名称资料收藏常用74系列标准数字电路的中文名称资料器件代号器件名称74 74LS 74HC00 四2输入端与非门√√√01 四2输入端与非门(OC) √√02 四2输入端或非门√√√03 四2输入端与非门(OC) √√04 六反相器√√√05 六反相器(OC) √√06 六高压输出反相器(OC,30V) √√07 六高压输出缓冲,驱动器(OC,30V) √√√08 四2输入端与门√√√09 四2输入端与门(OC) √√√10 三3输入端与非门√√√11 三3输入端与门√√12 三3输入端与非门(OC) √√√13 双4输入端与非门√√√14 六反相器√√√15 三3输入端与门(OC) √√16 六高压输出反相器(OC,15V) √17 六高压输出缓冲,驱动器(OC,15V) √20 双4输入端与非门√√√21 双4输入端与门√√√22 双4输入端与非门(OC) √√25 双4输入端或非门(有选通端) √√√26 四2输入端高压输出与非缓冲器√√√27 三3输入端或非门√√√28 四2输入端或非缓冲器√√√器件代号器件名称74 74LS 74HC30 8输入端与非门√√√32 四2输入端或门√√√33 四2输入端或非缓冲器(OC) √√37 四2输入端与非缓冲器√√38 四2输入端与非缓冲器(OC) √√40 双4输入端与非缓冲器√√√42 4线-10线译码器(BCD输入) √√43 4线-10线译码器(余3码输入) √44 4线-10线译码器(余3葛莱码输入) √48 4线-7段译码器√49 4线-7段译码器√50 双2路2-2输入与或非门√√√51 2路3-3输入,2路2-2输入与或非门√√√52 4路2-3-2-2输入与或门√53 4路2-2-2-2输入与或非门√54 4路2-3-3-2输入与或非门√√55 2路4-4输入与或非门√60 双4输入与扩展器√√61 三3输入与扩展器√62 4路2-3-3-2输入与或扩展器√64 4路4-2-3-2输入与或非门√65 4路4-2-3-2输入与或非门(OC) √70 与门输入J-K触发器√71 与或门输入J-K触发器√72 与门输入J-K触发器√器件代号器件名称74 74LS 74HC74 双上升沿D型触发器√√78 双D型触发器√√85 四位数值比较器√86 四2输入端异或门√√√87 4位二进制原码/反码√95 4位移位寄存器√101 与或门输入J-K触发器√102 与门输入J-K触发器√107 双主-从J-K触发器√108 双主-从J-K触发器√74F74是高速的TTL芯片和74HC一样就是速度高109 双主-从J-K触发器√110 与门输入J-K触发器√111 双主-从J-K触发器√√112 双下降沿J-K触发器√113 双下降沿J-K触发器√114 双下降沿J-K触发器√116 双4位锁存器√120 双脉冲同步驱动器√121 单稳态触发器√√√122 可重触发单稳态触发器√√√123 可重触发双稳态触发器√√√125 四总线缓冲器√√√126 四总线缓冲器√√√128 四2输入端或非线驱动器√√√132 四2输入端与非门√√√d触发器芯片有:74HC74 74LS90 双D触发器74LS7474LS364八D触发器(三态)7474、74 H74、74F74、74ALS74、74L74、74LS74A、74S74、74HC73、74C74双D型正沿触发器(带预置和清除端)74174、74LS174、74F174、74ALS174、74S174、74HC174、74C174六D型触发器(带清除端)74175、74LS175、74F175、74ALS175、74S175、74HC175、74C175 四D型触发器(带清除端)74273、74LS273、74S273、74F273、74ALS273、74HC273 八D型触发器(带清除端)74LS364八D触发器(三态)74LS377、74F377、74S3777八D 触发器74LS378、74F378、74S378、74HC378六D 触发器74LS379、74F379、74S379、74HC379八D 触发器。

74hc系列芯片的功能介绍

74hc系列芯片的功能介绍74HC01 2输入四与非门 (oc)74HC02 2输入四或非门74HC03 2输入四与非门 (oc)74HC04 六倒相器74HC05 六倒相器(oc)74HC06 六高压输出反相缓冲器/驱动器(oc,30v) 74HC07 六高压输出缓冲器/驱动器(oc,30v)74HC08 2输入四与门74HC09 2输入四与门(oc)74HC10 3输入三与非门74HC11 3输入三与门74HC12 3输入三与非门 (oc)74HC13 4输入双与非门 (斯密特触发)74HC14 六倒相器(斯密特触发)74HC15 3输入三与门 (oc)74HC16 六高压输出反相缓冲器/驱动器(oc,15v) 74HC17 六高压输出缓冲器/驱动器(oc,15v)74HC18 4输入双与非门 (斯密特触发)74HC19 六倒相器(斯密特触发)74HC20 4输入双与非门74HC21 4输入双与门74HC22 4输入双与非门(oc)74HC23 双可扩展的输入或非门74HC24 2输入四与非门(斯密特触发)74HC25 4输入双或非门(有选通)74HC26 2输入四高电平接口与非缓冲器(oc,15v) 74HC27 3输入三或非门74HC28 2输入四或非缓冲器74HC30 8输入与非门74HC31 延迟电路74HC32 2输入四或门74HC33 2输入四或非缓冲器(集电极开路输出) 74HC34 六缓冲器74HC35 六缓冲器(oc)74HC36 2输入四或非门(有选通)74HC37 2输入四与非缓冲器74HC38 2输入四或非缓冲器(集电极开路输出) 74HC39 2输入四或非缓冲器(集电极开路输出) 74HC40 4输入双与非缓冲器74HC41 bcd-十进制计数器74HC42 4线-10线译码器(bcd输入)74HC43 4线-10线译码器(余3码输入)74HC44 4线-10线译码器(余3葛莱码输入) 74HC45 bcd-十进制译码器/驱动器74HC46 bcd-七段译码器/驱动器74HC47 bcd-七段译码器/驱动器74HC48 bcd-七段译码器/驱动器74HC49 bcd-七段译码器/驱动器(oc)74HC50 双二路2-2输入与或非门(一门可扩展) 74HC51 双二路2-2输入与或非门74HC51 二路3-3输入,二路2-2输入与或非门74HC52 四路2-3-2-2输入与或门(可扩展)74HC53 四路2-2-2-2输入与或非门(可扩展) 74HC53 四路2-2-3-2输入与或非门(可扩展) 74HC54 四路2-2-2-2输入与或非门74HC54 四路2-3-3-2输入与或非门74HC54 四路2-2-3-2输入与或非门74HC55 二路4-4输入与或非门(可扩展)74HC60 双四输入与扩展74HC61 三3输入与扩展74HC62 四路2-3-3-2输入与或扩展器74HC63 六电流读出接口门74HC64 四路4-2-3-2输入与或非门74HC65 四路4-2-3-2输入与或非门(oc)74HC70 与门输入上升沿jk触发器74HC71 与输入r-s主从触发器74HC72 与门输入主从jk触发器74HC73 双j-k触发器(带清除端)74HC74 正沿触发双d型触发器(带预置端和清除端)74HC75 4位双稳锁存器74HC76 双j-k触发器(带预置端和清除端)74HC77 4位双稳态锁存器74HC78 双j-k触发器(带预置端,公共清除端和公共时钟端) 74HC80 门控全加器74HC81 16位随机存取存储器74HC82 2位二进制全加器(快速进位)74HC83 4位二进制全加器(快速进位)74HC84 16位随机存取存储器74HC85 4位数字比较器74HC86 2输入四异或门74HC87 四位二进制原码/反码/oi单元74HC89 64位读/写存储器74HC90 十进制计数器74HC91 八位移位寄存器74HC92 12分频计数器(2分频和6分频)74HC93 4位二进制计数器74HC94 4位移位寄存器(异步)74HC95 4位移位寄存器(并行io)74HC96 5位移位寄存器74HC97 六位同步二进制比率乘法器74HC100 八位双稳锁存器74HC103 负沿触发双j-k主从触发器(带清除端)74HC106 负沿触发双j-k主从触发器(带预置,清除,时钟) 74HC107 双j-k主从触发器(带清除端)74HC108 双j-k主从触发器(带预置,清除,时钟)74HC109 双j-k触发器(带置位,清除,正触发)74HC110 与门输入j-k主从触发器(带锁定)74HC111 双j-k主从触发器(带数据锁定)74HC112 负沿触发双j-k触发器(带预置端和清除端) 74HC113 负沿触发双j-k触发器(带预置端)74HC114 双j-k触发器(带预置端,共清除端和时钟端) 74HC116 双四位锁存器74HC120 双脉冲同步器/驱动器74HC121 单稳态触发器(施密特触发)74HC122 可再触发单稳态多谐振荡器(带清除端)74HC123 可再触发双单稳多谐振荡器74HC125 四总线缓冲门(三态输出)74HC126 四总线缓冲门(三态输出)74HC128 2输入四或非线驱动器74HC131 3-8译码器74HC132 2输入四与非门(斯密特触发)74HC133 13输入端与非门74HC134 12输入端与门(三态输出)74HC135 四异或/异或非门74HC136 2输入四异或门(oc)74HC137 八选1锁存译码器/多路转换器74HC138 3-8线译码器/多路转换器74HC139 双2-4线译码器/多路转换器74HC140 双4输入与非线驱动器74HC141 bcd-十进制译码器/驱动器74HC142 计数器/锁存器/译码器/驱动器74HC145 4-10译码器/驱动器74HC147 10线-4线优先编码器74HC148 8线-3线八进制优先编码器74HC150 16选1数据选择器(反补输出)74HC151 8选1数据选择器(互补输出)74HC152 8选1数据选择器多路开关74HC153 双4选1数据选择器/多路选择器74HC154 4线-16线译码器74HC155 双2-4译码器/分配器(图腾柱输出)74HC156 双2-4译码器/分配器(集电极开路输出) 74HC157 四2选1数据选择器/多路选择器74HC158 四2选1数据选择器(反相输出)74HC160 可预置bcd计数器(异步清除)74HC161 可预置四位二进制计数器(并清除异步) 74HC162 可预置bcd计数器(异步清除)74HC163 可预置四位二进制计数器(并清除异步) 74HC164 8位并行输出串行移位寄存器74HC165 并行输入8位移位寄存器(补码输出) 74HC166 8位移位寄存器74HC167 同步十进制比率乘法器74HC168 4位加/减同步计数器(十进制)74HC169 同步二进制可逆计数器74HC170 4*4寄存器堆74HC171 四d触发器(带清除端)74HC172 16位寄存器堆74HC173 4位d型寄存器(带清除端)74HC174 六d触发器74HC175 四d触发器74HC176 十进制可预置计数器74HC177 2-8-16进制可预置计数器74HC178 四位通用移位寄存器74HC179 四位通用移位寄存器74HC180 九位奇偶产生/校验器74HC181 算术逻辑单元/功能发生器74HC182 先行进位发生器74HC183 双保留进位全加器74HC184 bcd-二进制转换器74HC185 二进制-bcd转换器74HC190 同步可逆计数器(bcd,二进制)74HC191 同步可逆计数器(bcd,二进制)74HC192 同步可逆计数器(bcd,二进制)74HC193 同步可逆计数器(bcd,二进制)74HC199 八位移位寄存器74HC210 2-5-10进制计数器74HC213 2-n-10可变进制计数器74HC221 双单稳触发器74HC230 八3态总线驱动器74HC231 八3态总线反向驱动器74HC240 八缓冲器/线驱动器/线接收器(反码三态输出) 74HC241 八缓冲器/线驱动器/线接收器(原码三态输出) 74HC242 八缓冲器/线驱动器/线接收器74HC243 4同相三态总线收发器74HC244 八缓冲器/线驱动器/线接收器74HC245 八双向总线收发器74HC246 4线-七段译码/驱动器(30v)74HC247 4线-七段译码/驱动器(15v)74HC248 4线-七段译码/驱动器74HC249 4线-七段译码/驱动器74HC251 8选1数据选择器(三态输出)74HC253 双四选1数据选择器(三态输出)74HC256 双四位可寻址锁存器74HC257 四2选1数据选择器(三态输出)74HC258 四2选1数据选择器(反码三态输出) 74HC259 8为可寻址锁存器74HC260 双5输入或非门74HC261 4*2并行二进制乘法器74HC265 四互补输出元件74HC266 2输入四异或非门(oc)74HC270 2048位rom (512位四字节,oc) 74HC271 2048位rom (256位八字节,oc) 74HC273 八d触发器74HC274 4*4并行二进制乘法器74HC275 七位片式华莱士树乘法器74HC276 四jk触发器74HC278 四位可级联优先寄存器74HC279 四s-r锁存器74HC280 9位奇数/偶数奇偶发生器/较验器74HC28174HC283 4位二进制全加器74HC290 十进制计数器74HC291 32位可编程模74HC293 4位二进制计数器74HC294 16位可编程模74HC295 四位双向通用移位寄存器74HC298 四-2输入多路转换器(带选通)74HC299 八位通用移位寄存器(三态输出)74HC348 8-3线优先编码器(三态输出)74HC352 双四选1数据选择器/多路转换器74HC353 双4-1线数据选择器(三态输出)74HC354 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC355 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC356 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC357 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC365 6总线驱动器74HC366 六反向三态缓冲器/线驱动器74HC367 六同向三态缓冲器/线驱动器74HC368 六反向三态缓冲器/线驱动器74HC373 八d锁存器74HC374 八d触发器(三态同相)74HC375 4位双稳态锁存器74HC377 带使能的八d触发器74HC378 六d触发器74HC379 四d触发器74HC381 算术逻辑单元/函数发生器74HC382 算术逻辑单元/函数发生器74HC384 8位*1位补码乘法器74HC385 四串行加法器/乘法器74HC386 2输入四异或门74HC390 双十进制计数器74HC391 双四位二进制计数器74HC395 4位通用移位寄存器74HC396 八位存储寄存器74HC398 四2输入端多路开关(双路输出)74HC399 四-2输入多路转换器(带选通)74HC422 单稳态触发器74HC423 双单稳态触发器74HC440 四3方向总线收发器,集电极开路74HC441 四3方向总线收发器,集电极开路74HC442 四3方向总线收发器,三态输出74HC443 四3方向总线收发器,三态输出74HC444 四3方向总线收发器,三态输出74HC445 bcd-十进制译码器/驱动器,三态输出74HC446 有方向控制的双总线收发器74HC448 四3方向总线收发器,三态输出74HC449 有方向控制的双总线收发器74HC465 八三态线缓冲器74HC466 八三态线反向缓冲器74HC467 八三态线缓冲器74HC468 八三态线反向缓冲器74HC490 双十进制计数器74HC540 八位三态总线缓冲器(反向)74HC541 八位三态总线缓冲器74HC589 有输入锁存的并入串出移位寄存器74HC590 带输出寄存器的8位二进制计数器74HC591 带输出寄存器的8位二进制计数器74HC592 带输出寄存器的8位二进制计数器74HC593 带输出寄存器的8位二进制计数器74HC594 带输出锁存的8位串入并出移位寄存器74HC595 8位输出锁存移位寄存器74HC596 带输出锁存的8位串入并出移位寄存器74HC597 8位输出锁存移位寄存器74HC598 带输入锁存的并入串出移位寄存器74HC599 带输出锁存的8位串入并出移位寄存器74HC604 双8位锁存器74HC605 双8位锁存器74HC606 双8位锁存器74HC607 双8位锁存器74HC620 8位三态总线发送接收器(反相)74HC621 8位总线收发器74HC622 8位总线收发器74HC623 8位总线收发器74HC640 反相总线收发器(三态输出)74HC641 同相8总线收发器,集电极开路74HC642 同相8总线收发器,集电极开路74HC643 8位三态总线发送接收器74HC644 真值反相8总线收发器,集电极开路74HC645 三态同相8总线收发器74HC646 八位总线收发器,寄存器74HC647 八位总线收发器,寄存器74HC648 八位总线收发器,寄存器74HC649 八位总线收发器,寄存器74HC651 三态反相8总线收发器74HC652 三态反相8总线收发器74HC653 反相8总线收发器,集电极开路74HC654 同相8总线收发器,集电极开路74HC668 4位同步加/减十进制计数器74HC669 带先行进位的4位同步二进制可逆计数器74HC670 4*4寄存器堆(三态)74HC671 带输出寄存的四位并入并出移位寄存器74HC672 带输出寄存的四位并入并出移位寄存器74HC673 16位并行输出存储器,16位串入串出移位寄存器74HC674 16位并行输入串行输出移位寄存器74HC681 4位并行二进制累加器74HC682 8位数值比较器(图腾柱输出)74HC683 8位数值比较器(集电极开路)74HC684 8位数值比较器(图腾柱输出)74HC685 8位数值比较器(集电极开路)74HC686 8位数值比较器(图腾柱输出)74HC687 8位数值比较器(集电极开路)74HC688 8位数字比较器(oc输出)74HC689 8位数字比较器74HC690 同步十进制计数器/寄存器(带数选,三态输出,直接清除) 74HC691 计数器/寄存器(带多转换,三态输出)74HC692 同步十进制计数器(带预置输入,同步清除)74HC693 计数器/寄存器(带多转换,三态输出)74HC696 同步加/减十进制计数器/寄存器(带数选,三态输出,直接清除)74HC697 计数器/寄存器(带多转换,三态输出)74HC698 计数器/寄存器(带多转换,三态输出)74HC699 计数器/寄存器(带多转换,三态输出)74HC716 可编程模n十进制计数器74HC718 可编程模n十进制计数器。

74LV139中文资料

元器件交易网DIP16:plastic dual in-line package; 16 leads (300 mil)SOT38-4SO16:plastic small outline package; 16 leads; body width 3.9 mm SOT109-1SSOP16:plastic shrink small outline package; 16 leads; body width 5.3 mm SOT338-1TSSOP16:plastic thin shrink small outline package; 16 leads; body width 4.4 mm SOT403-1NOTESPhilips Semiconductors and Philips Electronics North America Corporation reserve the right to make changes, without notice, in the products,including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright,or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.LIFE SUPPORT APPLICATIONS Philips Semiconductors and Philips Electronics North America Corporation Products are not designed for use in life support appliances, devices,or systems where malfunction of a Philips Semiconductors and Philips Electronics North America Corporation Product can reasonably be expected to result in a personal injury. Philips Semiconductors and Philips Electronics North America Corporation customers using or selling Philips Semiconductors and Philips Electronics North America Corporation Products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors and Philips Electronics North America Corporation for any damages resulting from such improper use or sale.This data sheet contains preliminary data, and supplementary data will be published at a later date. PhilipsSemiconductors reserves the right to make changes at any time without notice in order to improve designand supply the best possible product.Philips Semiconductors811 East Arques AvenueP .O. Box 3409Sunnyvale, California 94088–3409Telephone 800-234-7381DEFINITIONSData Sheet IdentificationProduct Status Definition Objective Specification Preliminary Specification Product Specification Formative or in Design Preproduction Product Full ProductionThis data sheet contains the design target or goal specifications for product development. Specificationsmay change in any manner without notice.This data sheet contains Final Specifications. Philips Semiconductors reserves the right to make changesat any time without notice, in order to improve design and supply the best possible product.© Copyright Philips Electronics North America Corporation 1998All rights reserved. Printed in U.S.A.print codeDate of release: 05-96。

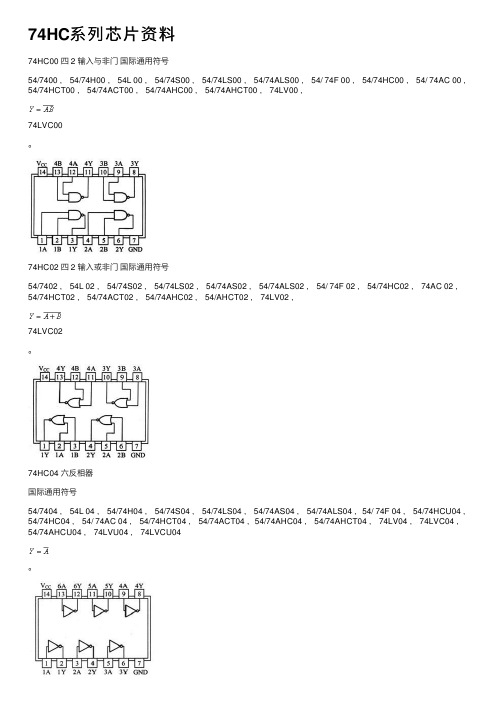

74HC系列芯片资料

74HC系列芯⽚资料74HC00 四 2 输⼊与⾮门国际通⽤符号54/7400 , 54/74H00 , 54L 00 , 54/74S00 , 54/74LS00 , 54/74ALS00 , 54/ 74F 00 , 54/74HC00 , 54/ 74AC 00 ,54/74HCT00 , 54/74ACT00 , 54/74AHC00 , 54/74AHCT00 , 74LV00 ,74LVC00。

74HC02 四 2 输⼊或⾮门国际通⽤符号54/7402 , 54L 02 , 54/74S02 , 54/74LS02 , 54/74AS02 , 54/74ALS02 , 54/ 74F 02 , 54/74HC02 , 74AC 02 ,54/74HCT02 , 54/74ACT02 , 54/74AHC02 , 54/AHCT02 , 74LV02 ,74LVC02。

74HC04 六反相器国际通⽤符号54/7404 , 54L 04 , 54/74H04 , 54/74S04 , 54/74LS04 , 54/74AS04 , 54/74ALS04 ,54/ 74F 04 , 54/74HCU04 ,54/74HC04 , 54/ 74AC 04 , 54/74HCT04 , 54/74ACT04 ,54/74AHC04 , 54/74AHCT04 , 74LV04 , 74LVC04 ,54/74AHCU04 , 74LVU04 , 74LVCU04。

74HC08 四 2 输⼊与门国际通⽤符号54/7408 , 54/74S08 , 54/74LS08 , 54/74AS08 , 54/74ALS08 , 54/ 74F 08 , 54/74HC08 ,54/74HCT08 , 54/ 74AC 08 , 54/74ACT08 , 54/74AHC08 , 54/74AHCT08 , 74LV08 , 74LVC08。

74ACT139MTC中文资料

IEEE/IEC

FIGURE 1. Gate Functions (Each Half)

Truth Table

Inputs E H L L L L A0 X L H L H A1 X L L H H O0 H L H H H Outputs O1 H H L H H O2 H H H L H O3 H H H H L

2.0V to 6.0V 4.5V to 5.5V 0V to VCC 0V to VCC −40°C to +85°C

125 mV/ns

DC Electrical Characteristics for AC

Symbol VIH Parameter Minimum HIGH Level Input Voltage VIL Maximum LOW Level Input Voltage VOH Minimum HIGH Level Output Voltage VCC (V) 3.0 4.5 5.5 3.0 4.5 5.5 3.0 4.5 5.5 3.0 4.5 5.5 VOL Maximum LOW Level Output Voltage 3.0 4.5 5.5 3.0 4.5 5.5 IIN (Note 4) IOLD IOHD ICC (Note 4) Maximum Input Leakage Current Minimum Dynamic Output Current (Note 3) Maximum Quiescent Supply Current 5.5 5.5 5.5 5.5 4.0 0.002 0.001 0.001 TA = +25°C Typ 1.5 2.25 2.75 1.5 2.25 2.75 2.99 4.49 5.49 2.1 3.15 3.85 0.9 1.35 1.65 2.9 4.4 5.4 2.56 3.86 4.86 0.1 0.1 0.1 0.36 0.36 0.36 ± 0.1 TA = −40°C to +85°C Guaranteed Limits 2.1 3.15 3.85 0.9 1.35 1.65 2.9 4.4 5.4 VIN = VIL or VIH 2.46 3.76 4.76 0.1 0.1 0.1 VIN = VIL or VIH 0.44 0.44 0.44 ± 1.0 75 −75 40.0 µA mA mA µA V IOL = 12 mA IOL = 24 mA IOL = 24 mA (Note 2) VI = VCC, GND VOLD = 1.65V Max VOHD = 3.85V Min VIN = VCC or GND V IOUT = 50 µA V IOH = −12 mA IOH = −24 mA IOH = −24 mA (Note 2) V IOUT = −50 µA V VOUT = 0.1V or VCC − 0.1V V Units Conditions VOUT = 0.1V or VCC − 0.1V

74系列各个芯片详细介绍

74系列芯片资料程序匠人发表于 2005-10-29 19:20:00 阅读全文(2477) | 回复(0) | 引用通告(0) | 编辑74系列芯片资料反相器驱动器 LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245与门与非门 LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38或门或非门与或非门 LS02 LS32 LS51 LS64 LS65异或门比较器 LS86译码器 LS138 LS139寄存器 LS74 LS175 LS373反相器:Vcc 6A 6Y 5A 5Y 4A 4Y 六非门74LS04 ┌┴─┴─┴─┴─┴─┴─┴┐六非门(OC门) 74LS05_ │1413 12 11 10 9 8│六非门(OC高压输出) 74LS06Y = A )││ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GND驱动器:Vcc 6A 6Y 5A 5Y 4A 4Y┌┴─┴─┴─┴─┴─┴─┴┐│1413 12 11 10 9 8│Y = A )│六驱动器(OC高压输出) 7 4LS07│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GNDVcc -4C 4A 4Y -3C 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐_ │1413 12 11 10 9 8│Y =A+C )│四总线三态门 74LS125 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘-1C 1A 1Y -2C 2A 2Y GNDVcc -G B1 B2 B3 B4 B8 B6 B7 B8┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐8位总线驱动器 74LS245│2019 18 17 16 15 14 13 12 11│)│DIR =1 A=>B│ 1 2 3 4 5 6 7 8 9 10│DIR=0 B=>A└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘DIR A1 A2 A3 A4 A5 A6 A7 A8 GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑与门,与非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐│1413 12 11 10 9 8│Y = AB )│2输入四正与门 74LS08 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐__ │1413 12 11 10 9 8│Y = AB )│2输入四正与非门 74LS 00│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 1C 1Y 3C 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐___ │1413 12 11 10 9 8│Y = ABC )│3输入三正与非门 74LS 10│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 2A 2B 2C 2Y GNDVcc H G Y┌┴─┴─┴─┴─┴─┴─┴┐│1413 12 11 10 9 8│)│8输入与非门 74LS30│ 1 2 3 4 5 6 7│________└┬─┬─┬─┬─┬─┬─┬┘Y = ABCDEFGHA B C D E F GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑或门,或非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐2输入四或门 74LS32│1413 12 11 10 9 8│)│Y = A+B│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4Y 4B 4A 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐2输入四或非门 74LS02│1413 12 11 10 9 8│ ___)│ Y = A+B│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Y 1A 1B 2Y 2A 2B GNDVcc 2Y 2B 2A 2D 2E 1F┌┴─┴─┴─┴─┴─┴─┴┐双与或非门 74S51│1413 12 11 10 9 8│ _____)│2Y = AB+DE│ 1 2 3 4 5 6 7│ _______└┬─┬─┬─┬─┬─┬─┬┘1Y = ABC+DEF1Y 1A 1B 1C 1D 1E GNDVcc D C B K J Y┌┴─┴─┴─┴─┴─┴─┴┐4-2-3-2与或非门 74S64 74S65(OC门)│1413 12 11 10 9 8│______________)│Y = ABCD+EF+GHI+JK│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘A E F G H I GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器2输入四异或门 74LS86Vcc 4B 4A 4Y 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐│1413 12 11 10 9 8│)│_ _│ 1 2 3 4 5 6 7│Y=AB+AB└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2Y 2A 2B GND8*2输入比较器 74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐8*2输入比较器 74LS688│2019 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器3-8译码器 74LS138Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6 __ _ _ _ __ _ _ __ _ _ __ _ ┌┴─┴─┴─┴─┴─┴─┴─┴┐Y0=A B C Y1=A B B Y2=A B C Y3=A B C│1615 14 13 12 11 10 9 │)│__ _ _ ___ __ _ __│ 1 2 3 4 5 6 7 8│Y4=A B C Y5=A B C Y6=A B C Y 7=A B C└┬─┬─┬─┬─┬─┬─┬─┬┘A B C -CS0 -CS1 CS2 -Y7 GND双2-4译码器 74LS139Vcc -2G 2A 2B -Y0 -Y1 -Y2 -Y3 __ __ __ __ __ __ __ __┌┴─┴─┴─┴─┴─┴─┴─┴┐Y0=2A 2B Y1=2A 2B Y2=2A 2B Y3=2A 2B│1615 14 13 12 11 10 9 │)│__ __ __ __ __ __ __ __│ 1 2 3 4 5 6 7 8│Y0=1A 1B Y1=1A 1B Y2=1A 1B Y 3=1A 1B└┬─┬─┬─┬─┬─┬─┬─┬┘-1G 1A 1B -Y0 -Y1 -Y2 -Y3 GND8*2输入比较器 74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐8*2输入比较器 74LS688│2019 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8寄存器:Vcc 2CR 2D 2Ck 2St 2Q -2Q┌┴─┴─┴─┴─┴─┴─┴┐双D触发器 74LS74│1413 12 11 10 9 8 │)││ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Cr 1D 1Ck 1St 1Q -1Q GNDVcc 8Q 8D 7D 7Q 6Q 6D 5D 5Q ALE┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐8位锁存器 74LS373│2019 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘-OE 1Q 1D 2D 2Q 3Q 3D 4D 4Q GND型号器件名称厂牌[数据表]SN7400四2输入端与非门 TI[DATA]SN7401四2输入端与非门(OC) SN7402四2输入端或非门 TI[DATA]SN7403四2输入端与非门(OC)TI[DATA]SN7404六反相器 TI[DATA]SN7405六反相器(O C)TI[DATA]SN7406六高压输出反相器(OC,30V)TI[DATA]SN7407六高压输出缓冲,驱动器(OC,30V)TI[DATA]SN7408四2输入端与门TI[DATA]SN7409四2输入端与门(OC)TI[DATA]SN7410三3输入端与非门 TI[DATA]SN7412三3输入端与非门(OC)TI[DATA]SN7413双4输入端与非门TI[DATA]SN7414六反相器TI[DATA]SN7416六高压输出反相缓冲/驱动器 I[DATA]SN7417六高压输出缓冲/驱动器(OC,15V)TI[DATA]SN7420双4输入端与非门 TI[DATA]SN7422双4输入端与非门(OC)TI[DATA]SN7423可扩展双4输入端或非门 TI[DATA]SN7425双4输入端或非门TI[DATA]SN7426四2输入端高压输出与非缓冲器 [DATA]SN7427三3输入端或非门TI[DATA]SN7428四2输入端或非缓冲器 I[DATA]SN74308输入端与非门TI[DATA]SN7432四2输入端或门。

74hc139中文资料参数

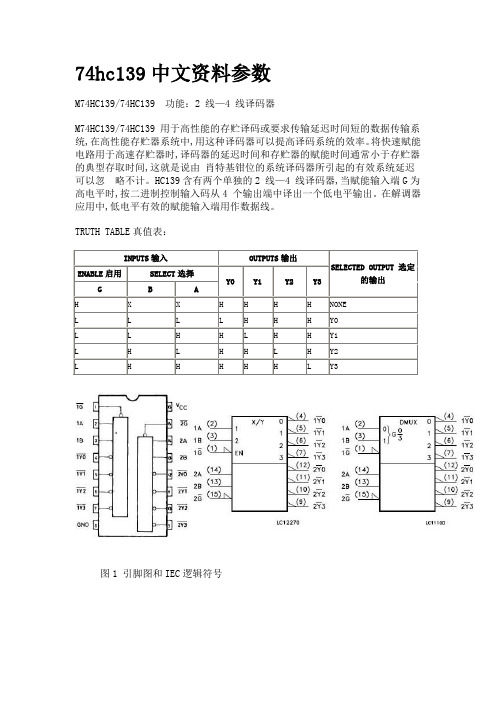

74hc139中文资料参数M74HC139/74HC139 功能:2 线—4 线译码器M74HC139/74HC139 用于高性能的存贮译码或要求传输延迟时间短的数据传输系统,在高性能存贮器系统中,用这种译码器可以提高译码系统的效率。

将快速赋能电路用于高速存贮器时,译码器的延迟时间和存贮器的赋能时间通常小于存贮器的典型存取时间,这就是说由 肖特基钳位的系统译码器所引起的有效系统延迟可以忽 略不计。

HC139含有两个单独的2 线—4 线译码器,当赋能输入端G 为高电平时,按二进制控制输入码从4 个输出端中译出一个低电平输出。

在解调器应用中,低电平有效的赋能输入端用作数据线。

TRUTH TABLE 真值表:INPUTS 输入OUTPUTS 输出SELECTED OUTPUT 选定的输出ENABLE 启用SELECT 选择 Y0 Y1Y2Y3 G BAH X X H H H H NONE L L L L H H H Y0 L L H H L H H Y1 L H L H H L H Y2 LHHHHH LY3图1 引脚图和IEC 逻辑符号图2 输入输出等效电路图3 逻辑图引脚功能表:引脚位SYMBOL 符号NAME AND FUNCTION名称及功能1,151G,2G Enable Inputs使能输入2,31A,1B Address Inputs地址输入4,5,6,71Y0 to 1Y3Outputs输出12,11,10,92Y0 to 2Y3Outputs输出14,132A,2B Address Inputs地址输入8GND Ground接地(0V)16VCC Positive Supply Voltage正电源电压ABSOLUTE MAXIMUM RATINGS绝对最大额定值:SYMBOL 符号Parameter 参数Value 数值Unit 单位VCC Supply Voltage电源电压-0.5 to +7VDC SPECIFICATIONS直流电气规格:AC ELECTRICAL CHARACTERISTICS交流电气特性:应用电路:图4图5 晶体管H桥电机驱动电路。

74系列芯片数据手册大全

74系列芯片数据手册大全74系列集成电路名称与功能常用74系列标准数字电路的中文名称资料7400 TTL四2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压缓冲驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相高压缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器7425 双4输入端或非门(有选通端74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门缓冲器74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D触发器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器7443 4线-10线译码器(余3码输入)7444 4线-10线译码器(余3葛莱码输入) 74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动7449 4线-7段译码器74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门7452 4路2-3-2-2输入与或门7453 4路2-2-2-2输入与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器7460 双4输入与扩展器7461 三3输入与扩展器7462 4路2-3-3-2输入与或扩展器7464 4路4-2-3-2输入与或非门74645 TTL 三态输出八同相总线传送接收器7465 4路4-2-3-2输入与或非门(OC)74670 TTL 三态输出4×4寄存器堆7470 与门输入J-K触发器√7471 与或门输入J-K触发器√7472 与门输入J-K触发器7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双上升沿D触发器7476 TTL 带预置清除双J-K触发器7478 双D型触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7487 4位二进制原码/反码7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\输出移位寄存器7497 TTL 6位同步二进制乘法器74101 与或门输入J-K触发器74102 与门输入J-K触发器74107 双主-从J-K触发器74108 双主-从J-K触发器74109 双主-从J-K触发器74110 与门输入J-K触发器74111 双主-从J-K触发器74112 双下降沿J-K触发器74113 双下降沿J-K触发器74114 双下降沿J-K触发器74116 双4位锁存器74120 双脉冲同步驱动器74121 单稳态触发器74122 可重触发单稳态触发器74123 可重触发双稳态触发器74125 四总线缓冲器74126 四总线缓冲器74128 四2输入端或非线驱动器74132 四2输入端与非门。

74VHC123AMTCX中文资料

74VHC123A Dual Retriggerable Monostable Multivibrator元器件交易网74VHC123A Dual Retriggerable Monostable MultivibratorConnection Diagram Pin DescriptionLogic SymbolIEEE/IECTruth TableH = HIGH Voltage Level L = LOW Voltage Level = HIGH-to-LOW Transition = LOW-to-HIGH Transition X = Don't CarePin NamesDescriptionA Trigger Inputs (Negative Edge)B Trigger Inputs (Positive Edge)CLR Reset InputsC x External Capacitor R x External Resistor Q, QOutputsInputs OutputsFunctionABCLRQ QH H Output Enable X L H L H Inhibit H XH LHInhibit L HOutput Enable L H Output Enable XXLLHReset元器件交易网74VHC123A Dual Retriggerable Monostable MultivibratorBlock DiagramsNote A: C x , R x , D x are external Capacitor, Resistor, and Diode, respectively. Note B: External clamping diode, D x ;External capacitor is charged to V CC level in the wait state, i.e. when no trigger is applied.If the supply voltage is turned off, C x discharges mainly through the internal (parasitic) diode. If C x is sufficiently large and V CC drops rapidly, there will be some possibility of damaging the IC through in rush current or latch-up. If the capacitance of the supply voltage filter is large enough and V CC drops slowly, the in rush current is automatically limited and damage to the IC is avoided.The maximum value of forward current through the parasitic diode is ±20mA. In the case of a large Cx, the limit of fall time of the supply voltage is determined as follows:t f ≥ (V CC –0.7) C x / 20mA(t f is the time between the supply voltage turn off and the supply voltage reaching 0.4 V CC )In the event a system does not satisfy the above condition, an external clamping diode (D x) is needed to protect the ICfrom rush current.元器件交易网74VHC123A Dual Retriggerable Monostable MultivibratorSystem DiagramTiming Chart元器件交易网Functional Description1.Stand-by StateThe external capacitor (C x) is fully charged to V CC in the Stand-by State. That means, before triggering, the Q P and Q N transistors which are connected to the R x/C x node are in the off state. Two comparators that relate to the timing of the output pulse, and two refer-ence voltage supplies turn off. The total supply cur-rent is only leakage current.2.T rigger OperationTrigger operation is effective in any of the following three cases. First, the condition where the A input is LOW, and B input has a rising signal; second, where the B input is HIGH, and the A input has a falling sig-nal; and third, where the A input is LOW and the B input is HIGH, and the CLR input has a rising signal.After a trigger becomes effective, comparators C1 and C2start operating, and Q N is turned on. The external capacitor discharges through Q N. The volt-age level at the R x/C x node drops. If the R x/C x volt-age level falls to the internal reference voltage V ref L, the output of C1 becomes LOW. The flip-flop is then reset and Q N turns off. At that moment C1 stops but C2 continues operating.After Q N turns off, the voltage at the R x/C x node starts rising at a rate determined by the time constant of external capacitor C x and resistor R x.Upon triggering, output Q becomes HIGH, following some delay time of the internal F/F and gates. It stays HIGH even if the voltage of R x/C x changes from fall-ing to rising. When R x/C x reaches the internal refer-ence voltage V ref H, the output of C2 becomes LOW,the output Q goes LOW and C2 stops its operation.That means, after triggering, when the voltage level of the R x/C x node reaches V ref H, the IC returns to its MONOSTABLE state.With large values of C x and R x, and ignoring the dis-charge time of the capacitor and internal delays of the IC, the width of the output pulse, t W (OUT), is as follows:t W (OUT) = 1.0 C x R x3.Retrigger operation (74VHC123A)When a new trigger is applied to either input A or B while in the MONOSTABLE state, it is effective only if the IC is charging C x. The voltage level of the R x/C x node then falls to V ref L level again. Therefore the Q output stays HIGH if the next trigger comes in before the time period set by C x and R x.If the new trigger is very close to a previous trigger, such as an occurrence during the discharge cycle, it will have no effect.The minimum time for a trigger to be effective 2nd trigger, t RR (Min), depends on V CC and C x.4.Reset OperationIn normal operation, the CLR input is held HIGH. If CLR is LOW, a trigger has no affect because the Q output is held LOW and the trigger control F/F is reset. Also, Q p turns on and C x is charged rapidly to V CC.This means if CLR is set LOW, the IC goes into a wait state.元器件交易网74VHC123A Dual Retriggerable Monostable Multivibrator74VHC123A Dual Retriggerable Monostable MultivibratorAbsolute Maximum RatingsStresses exceeding the absolute maximum ratings may damage the device. The device may not function or beoperable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.Recommended Operating Conditions (1)The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.Notes:1.Unused inputs must be held HIGH or LOW. They may not float.2.The maximum allowable values of C x and R x are a function of the leakage of capacitor C x , the leakage of the device, and leakage due to board layout and surface resistance. Susceptibility to externally induced noise signals may occur for R x > 1M Ω.Symbol ParameterRatingV CC Supply Voltage –0.5V to +7.0V V IN DC Input Voltage –0.5V to +7.0V V OUT DC Output Voltage –0.5V to V CC + 0.5VI IK Input Diode Current –20mA I OK Output Diode Current ±20mA I OUT DC Output Current ±25mA I CC DC V CC /GND Current ±50mAT STG Storage Temperature–65°C to +150°CT LLead Temperature (Soldering, 10 seconds)260°CSymbol ParameterRatingV CC Supply Voltage 2.0V to +5.5V V IN Input Voltage 0V to +5.5V V OUT Output Voltage 0V to V CCT OPR Operating Temperature–40°C to +85°C t r , t fInput Rise and Fall Time (CLR only) V CC = 3.3V ± 0.3V V CC = 5.0V ± 0.5V 0ns/V ∼ 100ns/V 0ns/V ∼ 20ns/V External Capacitor, C x No Limitation (2) F External Resistor, R x>5k Ω(2) (V CC = 2.0V)>1k Ω(2) (V CC > 3.0V)元器件交易网Note:3.Per circuit.Current I CCActive—State (3)Supply Current3.0V IN = V CC or GND, R x /C x = 0.5 V CC160250280µA4.53805006505.5560750975Notes:4.Refer to Timing Chart.5.C PD is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load. Average operating current can be obtained by the equation:I CC (opr.) = C PD • V CC • f IN+ I CC 1 • Duty / 100 + I CC / 2 (per Circuit)I CC 1: Active Supply Current Duty: %R x = 1k Ω5.0 ± 0.50.91.0 1.10.91.1∆t WOUTOutput Pulse Width Error Between Circuits (In same Package)±1%C IN Input Capacitance V CC = Open41010pF C PDPower Dissipation Capacitance(5)73pF74VHC123A Dual Retriggerable Monostable MultivibratorAC Operating Requirement (6)Note:6.Refer to Timing Chart.SymbolParameterV CC (V)Conditions T A = 25°CT A = –40°C to +85°C UnitsMin.Typ.Max.Min.Max.t W (L), t W (H)Minimum Trigger Pulse Width 3.3 5.0 5.0ns5.0 5.0 5.0t W (L)Minimum Clear Pulse Width 3.3 5.0 5.0ns 5.0 5.05.0t RRMinimum Retrigger Time3.3 ± 0.3R x = 1k Ω, C X = 100pF 60ns 5.0 ± 0.5393.3R x = 1k Ω, C X = 0.01µF1.5µs5.01.2Device Characteristicst wout*C x Characteristics (Typ.)Output Pulse Width Constant K-Supply Voltage(Typ.)t RR*V CC Characteristics (Typ.)Input Equivalent Circuit74VHC123A Dual Retriggerable Monostable Multivibrator74VHC123A Dual Retriggerable Monostable Multivibrator The™。

CD74HCT139资料

Ordering Information

PART NUMBER TEMP. RANGE (oC) PACKAGE

PKG. NO.

CD74HC139E

-55 to 125

16 Ld PDIP E16.3

CD74HCT139E

-55 to 125

16 Ld PDIP E16.3

CD74HC139M

-55 to 125

115

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . 150oC

Maximum Storage Temperature Range . . . . . . . . . .-65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . 300oC

(SOIC - Lead Tips Only)

Operating Conditions

Temperature Range (TA) . . . . . . . . . . . . . . . . . . . . . -55oC to 125oC Supply Voltage Range, VCC

74HC139-(芯片资料)

TL F 5311MM54HC139 MM74HC139 Dual 2-To-4 Line DecoderJanuary1988 MM54HC139 MM74HC139Dual2-To-4Line DecoderGeneral DescriptionThis decoder utilizes advanced silicon-gate CMOS technol-ogy and is well suited to memory address decoding or datarouting applications It possesses the high noise immunityand low power consumption usually associated with CMOScircuitry yet has speeds comparable to low power SchottkyTTL logicThe MM54HC139 MM74HC139contain two independentone-of-four decoders each with a single active low enableinput(G1 or G2) Data on the select inputs(A1 and B1orA2 and B2)cause one of the four normally high outputs togo lowThe decoder’s outputs can drive10low power Schottky TTLequivalent loads and are functionally as well as pin equiva-lent to the54LS139 74LS139 All inputs are protected fromdamage due to static discharge by diodes to V CC andgroundFeaturesY Typical propagation delaysSelect to outputs(4delays) 18nsSelect to output(5delays) 28nsEnable to output 20nsY Low power 40m W quiescent supply powerY Fanout of10LS-TTL devicesY Input current maximum1m A typical10pA Connection DiagramDual-In-Line PackageTL F 5311–1Order Number MM54HC139or MM74HC139Truth Table’HC139InputsOutputsEnable SelectG B A Y0Y1Y2Y3H X X H H H HL L L L H H HL L H H L H HL H L H H L HL H H H H H LH e high level L e low level X e don’t careLogic DiagramMM54HC139 MM74HC139TL F 5311–2(1of2)C1995National Semiconductor Corporation RRD-B30M105 Printed in U S AAbsolute Maximum Ratings(Notes1 2) If Military Aerospace specified devices are required please contact the National Semiconductor Sales Office Distributors for availability and specifications Supply Voltage(V CC)b0 5to a7 0V DC Input Voltage(V IN)b1 5to V CC a1 5V DC Output Voltage(V OUT)b0 5to V CC a0 5V Clamp Diode Current(I IK I OK)g20mA DC Output Current per pin(I OUT)g25mA DC V CC or GND Current per pin(I CC)g50mA Storage Temperature Range(T STG)b65 C to a150 C Power Dissipation(P D)(Note3)600mW S O Package only500mW Lead Temp (T L)(Soldering10seconds)260 C Operating ConditionsMin Max Units Supply Voltage(V CC)26V DC Input or Output Voltage0V CC V (V IN V OUT)Operating Temp Range(T A)MM74HC b40a85 C MM54HC b55a125 C Input Rise or Fall TimesV CC e2 0V(t r t f)1000ns V CC e4 5V500nsV CC e6 0V400nsDC Electrical Characteristics(Note4)T A e25 C 74HC54HCSymbol Parameter Conditions V CC T A eb40to85 C T A eb55to125 C UnitsTyp Guaranteed LimitsV IH Minimum High Level2 0V1 51 51 5V Input Voltage4 5V3 153 153 15V6 0V4 24 24 2VV IL Maximum Low Level2 0V0 50 50 5V Input Voltage 4 5V1 351 351 35V6 0V1 81 81 8VV OH Minimum High Level V IN e V IH or V ILOutput Voltage l I OUT l s20m A2 0V2 01 91 91 9V4 5V4 54 44 44 4V6 0V6 05 95 95 9VV IN e V IH or V ILl I OUT l s4 0mA4 5V4 23 983 843 7Vl I OUT l s5 2mA6 0V5 75 485 345 2V V OL Maximum Low Level V IN e V IH or V ILOutput Voltage l I OUT l s20m A2 0V00 10 10 1V4 5V00 10 10 1V6 0V00 10 10 1VV IN e V IH or V ILl I OUT l s4 0mA4 5V0 20 260 330 4Vl I OUT l s5 2mA6 0V0 20 260 330 4V I IN Maximum Input V IN e V CC or GND6 0V g0 1g1 0g1 0m ACurrentI CC Maximum Quiescent V IN e V CC or GND6 0V8 080160m ASupply Current I OUT e0m ANote1 Absolute Maximum Ratings are those values beyond which damage to the device may occurNote2 Unless otherwise specified all voltages are referenced to groundNote3 Power Dissipation temperature derating plastic‘‘N’’package b12mW C from65 C to85 C ceramic‘‘J’’package b12mW C from100 C to125 C Note4 For a power supply of5V g10%the worst case output voltages(V OH and V OL)occur for HC at4 5V Thus the4 5V values should be used when designing with this supply Worst case V IH and V IL occur at V CC e5 5V and4 5V respectively (The V IH value at5 5V is3 85V )The worst case leakage current(I IN I CC and I OZ)occur for CMOS at the higher voltage and so the6 0V values should be usedV IL limits are currently tested at20%of V CC The above V IL specification(30%of V CC)will be implemented no later than Q1 CY’892AC Electrical Characteristics V CC e5V T A e25 C C L e15pF t r e t f e6nsSymbol Parameter Conditions Typ GuaranteedUnits Limitt PHL t PLH Maximum Propagation1830ns Delay Binary Select to any Output4levels of delayt PHL t PLH Maximum Propagation2838ns Delay Binary Select to any Output5levels of delayt PHL t PLH Maximum Propagation1930ns Delay Enable to any OutputAC Electrical Characteristics C L e50pF t r e t f e6ns(unless otherwise specified)T A e25 C 74HC54HCSymbol Parameter Conditions V CC T A eb40to85 C T A eb55to125 C UnitsTyp Guaranteed Limitst PHL t PLH Maximum Propagation(Note6)2 0V110175219254ns Delay Binary Select to4 5V22354451nsany Output4levels of delay6 0V18303844nst PHL t PLH Maximum Propagation(Note7)2 0V165220275320ns Delay Binary Select to any4 5V33445564nsOutput5levels of delay6 0V28384754nst PHL t PLH Maximum Propagation2 0V115175219254ns Delay Enable to any4 5V23354451nsOutput6 0V19303844nst TLH t TLH Maximum Output Rise2 0V307595110ns and Fall Time4 5V8151922ns6 0V7131619nsC IN Maximum Input3101010pFCapacitanceC PD Power Dissipation(Note5)75pFCapacitance(Note5)Note5 C PD determines the no load dynamic power consumption P D e C PD V CC2f a I CC V CC and the no load dynamic current consumption I S e C PD V CC f a I CC Note6 4levels of delay are A to Y1 Y3and B to Y2 Y3Note7 5levels of delay are A to Y0 Y2and B to Y0 Y13M M 54H C 139 M M 74H C 139D u a l 2-T o -4L i n e D e c o d e rPhysical Dimensions inches (millimeters)Order Number MM54HC139J or MM74HC139JNS Package J16AOrder Number MM74HC139NNS Package N16ELIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION As used herein 1 Life support devices or systems are devices or 2 A critical component is any component of a life systems which (a)are intended for surgical implant support device or system whose failure to perform can into the body or (b)support or sustain life and whose be reasonably expected to cause the failure of the life failure to perform when properly used in accordance support device or system or to affect its safety or with instructions for use provided in the labeling can effectivenessbe reasonably expected to result in a significant injury to the userNational Semiconductor National Semiconductor National Semiconductor National Semiconductor CorporationEuropeHong Kong LtdJapan Ltd1111West Bardin RoadFax (a 49)0-180-530858613th Floor Straight Block Tel 81-043-299-2309。

含两个2-4译码器地74HC139芯片版图

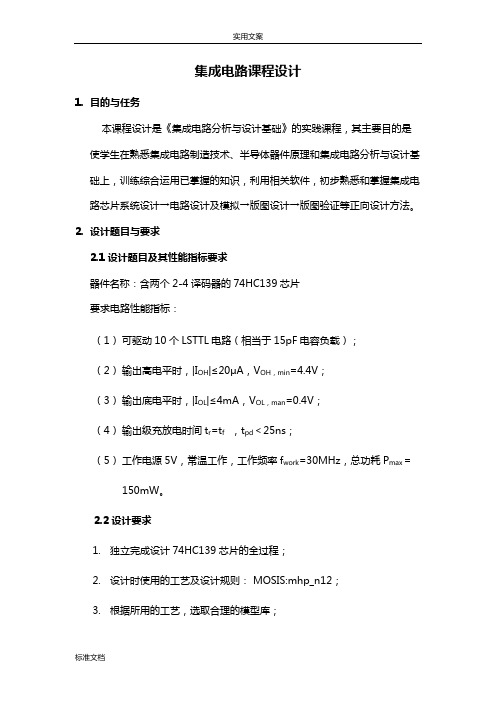

集成电路课程设计1.目的与任务本课程设计是《集成电路分析与设计基础》的实践课程,其主要目的是使学生在熟悉集成电路制造技术、半导体器件原理和集成电路分析与设计基础上,训练综合运用已掌握的知识,利用相关软件,初步熟悉和掌握集成电路芯片系统设计→电路设计及模拟→版图设计→版图验证等正向设计方法。

2.设计题目与要求2.1设计题目及其性能指标要求器件名称:含两个2-4译码器的74HC139芯片要求电路性能指标:(1)可驱动10个LSTTL电路(相当于15pF电容负载);(2)输出高电平时,|I OH|≤20μA,V OH,min=4.4V;(3)输出底电平时,|I OL|≤4mA,V OL,man=0.4V;(4)输出级充放电时间t r=t f ,t pd<25ns;(5)工作电源5V,常温工作,工作频率f work=30MHz,总功耗P max=150mW。

2.2设计要求1.独立完成设计74HC139芯片的全过程;2.设计时使用的工艺及设计规则: MOSIS:mhp_n12;3.根据所用的工艺,选取合理的模型库;4.选用以lambda(λ)为单位的设计规则;5.全手工、层次化设计版图;6.达到指导书提出的设计指标要求。

3.设计方法与计算3.174HC139芯片简介74HC139是包含两个2线-4线译码器的高速CMOS数字电路集成芯片,能与TTL集成电路芯片兼容,它的管脚图如图1所示,其逻辑真值表如表1所示:图1 74HC139芯片管脚图表1 74HC139真值表片选输入数据输出C s A1 A0 Y0 Y1Y2Y30 0 0 0 1 1 10 0 1 1 0 10 1 0 1 1 0 1设计时只需分析其中一个2—4译码器即可,从真值表我们可以得出Cs 为片选端,当其为0时,芯片正常工作,当其为1时,芯片封锁。

A1、A0为输入端,Y0-Y3为输出端,而且是低电平有效。

2—4译码器的逻辑表达式,如下所示:01010A A C A A C Y s s ⋅⋅=++= 01011A A C A A C Y s s ⋅⋅=++= 01012A A C A A C Y s s ⋅⋅=++= 01013A A C A A C Y s s ⋅⋅=++=74HC139的逻辑图如图2所示:图2 74HC139逻辑图3.2电路设计本次设计采用的是m12_20的模型库参数进行各级电路的尺寸计算,其参数如下:NMOS:εox=3.9×8.85×10﹣12F/m μn=605.312×10﹣4㎡/Vst ox=395×10﹣10m V tn=0.81056VPMOS: εox=3.9×8.85×10﹣12F/m μp=219×10﹣4㎡/Vst ox=395×10﹣10m V tp=﹣0.971428V3.2.1 输出级电路设计根据要求输出级电路等效电路图如图3所示,输入Vi为前一级的输出,可认为是理想的输出,即V IL=Vss, V IH=V DD。

HD74LVC139FP中文资料

HD74LVC139Dual 2-to-4-line Decoders / DemultiplexersADE-205-069B(Z)Rev.2September 1995 DescriptionThe HD74LVC139 has two independent two-to-four-line decoders each with a single active low enable input in a 16 pin package. Data on the select inputs cause one of the four normally high outputs to go low. Low voltage and high speed operation is suitable at the battery drive product (note type personal computer) and low power consumption extends the life of a battery for long time operation.Features•V CC = 2.0 V to 5.5 V•All inputs V IH (Max.) = 5.5 V (@V CC = 0 V to 5.5 V)•Typical V OL ground bounce < 0.8 V (@V CC = 3.3 V, Ta = 25°C)•Typical V OH undershoot > 2.0 V (@V CC = 3.3 V, Ta = 25°C)•High output current ±24 mA (@V CC = 3.0 V to 5.5 V)Function TableInputEnable Select OutputsG B A Y0Y1Y2Y3H X X H H H H L L L L H H H L L H H L H H L H L H H L H L H H H H H L H :High levelL :Low levelX :ImmaterialHD74LVC139Rev.2, Sep. 1995, page 2 of 7Pin ArrangementAbsolute Maximum RatingsItemSymbol Ratings Unit ConditionsSupply voltage V CC –0.5 to 6.0V Input diode current I IK –50mA V I = –0.5 V Input voltage V I –0.5 to 6.0V Output diode current I OK –50mA V O = –0.5 V 50mA V O = V CC +0.5 V Output voltage V O –0.5 to V CC +0.5V Output current I O±50mA V CC , GND current / pin I CC or I GND 100mA Storage temperatureTstg–65 to 150°CNote:The absolute maximum ratings are values which must not individually be exceeded, and furthermore,no two of which may be realized at the same time.HD74LVC139Rev.2, Sep. 1995, page 3 of 7Recommended Operating ConditionsItemSymbol Ratings Unit Conditions Supply voltage V CC 1.5 to 5.5V Data retention 2.0 to 5.5V At operation Input / output voltage V I 0 to 5.5V G, A, B V O 0 to V CC V Y 0 to Y 3Operating temperature Ta –40 to 85°C Output currentI OH –12mA V CC = 2.7 V –24 *2mA V CC = 3.0 V to 5.5 V I OL12mA V CC = 2.7 V 24 *2mA V CC = 3.0 V to 5.5 V Input rise / fall time *1t r , t f10ns/VNotes: 1.This item guarantees maximum limit when one input switches.Waveform : Refer to test circuit of switching characteristics.2.duty cycle ≤ 50%Electrical CharacteristicsTa = –40 to 85°CItem Symbol V CC (V)Min Max Unit Test Conditions Input voltageV IH 2.7 to 3.6 2.0—V 4.5 to 5.5V CC ×0.7—V V IL2.7 to3.6—0.8V 4.5 to 5.5—V CC ×0.3V Output voltageV OH2.7 to 5.5V CC –0.2—V I OH = –100 µA 2.7 2.2—V I OH = –12 mA3.0 2.4—V 3.0 2.0—V I OH = –24 mA4.53.8—V V OL2.7 to 5.5—0.2V I OL = 100 µA 2.7—0.4V I OL = 12 mA3.0—0.55V I OL = 24 mA4.5—0.55V Input currentI IN 0 to 5.5—±5.0µA V IN = 5.5 V or GND Quiescent supply current I CC5.5—20µA V IN = V CC or GND∆I CC3.0 to 3.6—500µAV IN = one input at (V CC –0.6)V,other inputs at V CC or GNDHD74LVC139Rev.2, Sep. 1995, page 4 of 7Switching CharacteristicsTa = –40 to 85°CItemSymbol V CC (V)Min Typ Max Unit From (Input)To (Output)Propagation delay timet PLH 2.7—7.010.0ns G, A, BY 0 to Y 3t PHL3.3±0.3 1.5 5.09.0ns 5.0±0.5— 3.57.5ns Input capacitance C IN 2.7— 3.0—pF Output capacitanceC O2.7—15.0—pFTest CircuitHD74LVC139 WaveformsRev.2, Sep. 1995, page 5 of 7HD74LVC139 Package DimensionsRev.2, Sep. 1995, page 6 of 7HD74LVC139Rev.2, Sep. 1995, page 7 of 7Disclaimer1.Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s patent,copyright, trademark, or other intellectual property rights for information contained in this document.Hitachi bears no responsibility for problems that may arise with third party’s rights, including intellectual property rights, in connection with use of the information contained in this document.2.Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.3.Hitachi makes every attempt to ensure that its products are of high quality and reliability. However,contact Hitachi’s sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation,traffic, safety equipment or medical equipment for life support.4.Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installationconditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.5.This product is not designed to be radiation resistant.6.No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.7.Contact Hitachi’s sales office for any questions regarding this document or Hitachi semiconductor products.Sales OfficesHitachi, Ltd.Semiconductor & Integrated Circuits.Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109Copyright Hitachi, Ltd., 2000. All rights reserved. Printed in Japan.Hitachi Asia Ltd. Hitachi Tower16 Collyer Quay #20-00, Singapore 049318Tel : <65>-538-6533/538-8577 Fax : <65>-538-6933/538-3877URL : .sg URLNorthAmerica : /Europe : /hel/ecg Asia : Japan : http://www.hitachi.co.jp/Sicd/indx.htmHitachi Asia Ltd.(Taipei Branch Office)4/F, No. 167, Tun Hwa North Road, Hung-Kuo Building, Taipei (105), Taiwan Tel : <886>-(2)-2718-3666 Fax : <886>-(2)-2718-8180 Telex : 23222 HAS-TPURL : Hitachi Asia (Hong Kong) Ltd.Group III (Electronic Components) 7/F., North Tower, World Finance Centre,Harbour City, Canton Road Tsim Sha Tsui, Kowloon, Hong KongTel : <852>-(2)-735-9218 Fax : <852>-(2)-730-0281URL : Hitachi Europe Ltd.Electronic Components Group.Whitebrook ParkLower Cookham Road MaidenheadBerkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000Fax: <44> (1628) 585160Hitachi Europe GmbHElectronic Components Group Dornacher Straße 3D-85622 Feldkirchen, Munich GermanyTel: <49> (89) 9 9180-0Fax: <49> (89) 9 29 30 00Hitachi Semiconductor (America) Inc.179 East Tasman Drive,San Jose,CA 95134 Tel: <1> (408) 433-1990Fax: <1>(408) 433-0223For further information write to:Colophon 2.0。

74LVC139数据手册

SO16:plastic small outline package; 16 leads; body width 3.9 mm SOT109-1SSOP16:plastic shrink small outline package; 16 leads; body width 5.3 mm SOT338-1TSSOP16:plastic thin shrink small outline package; 16 leads; body width 4.4 mm SOT403-1Philips Semiconductors and Philips Electronics North America Corporation reserve the right to make changes, without notice, in the products,including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright,or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.LIFE SUPPORT APPLICATIONS Philips Semiconductors and Philips Electronics North America Corporation Products are not designed for use in life support appliances, devices,or systems where malfunction of a Philips Semiconductors and Philips Electronics North America Corporation Product can reasonably be expected to result in a personal injury. Philips Semiconductors and Philips Electronics North America Corporation customers using or selling Philips Semiconductors and Philips Electronics North America Corporation Products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors and Philips Electronics North America Corporation for any damages resulting from such improper use or sale.This data sheet contains preliminary data, and supplementary data will be published at a later date. PhilipsSemiconductors reserves the right to make changes at any time without notice in order to improve designand supply the best possible product.Philips Semiconductors811 East Arques AvenueP .O. Box 3409Sunnyvale, California 94088–3409Telephone 800-234-7381DEFINITIONSData Sheet IdentificationProduct Status Definition Objective Specification Preliminary Specification Product Specification Formative or in Design Preproduction Product Full ProductionThis data sheet contains the design target or goal specifications for product development. Specificationsmay change in any manner without notice.This data sheet contains Final Specifications. Philips Semiconductors reserves the right to make changesat any time without notice, in order to improve design and supply the best possible product.© Copyright Philips Electronics North America Corporation 1998All rights reserved. Printed in U.S.A.print codeDate of release: 05-96。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。