S-AV38中文资料

AVXX08中文资料

A PLUS MAKE YOUR PRODUCTION A-PLUSAVxx08 SeriesDATA SHEETA PLUS INTEGRATED CIRCUITS INC.Address:3 F-10, No. 32, Sec. 1, Chenggung Rd., Taipei, Taiwan 115, R.O.C.(115)台北市南港區成功路㆒段32號3樓之10. TEL: 886-2-2782-9266FAX: 886-2-2782-9255WEBSITE : http: // Sales E-mail:sales@Technology E-mail: service@1. GENERAL DESCRIPTION:The AVH308 , AV0708 , AV1408 and AV2108 are single-chip voice synthesizing CMOS IC.They are low cost with proper functions and can synthesize voice up to 3.5, 7, 14 and 21 seconds, usingA plus 4-bit LOGPCM algorithm. Customer speech data can be programmed into ROM by changing one maskduring the device fabrication. Besides, not only a very flexible functions I/O pin is available for the user to apply in various applications, but also an interactive development tool “EzSpeech” is ready for user-friendly programming.2. FEATURES:(1). Single power supply can operate from 2.4V to 6.4V (in this range, user can set Rosc as a fixed value).(2). The total voice duration is about 3.5, 7, 14 or 21 seconds those can be partitioned up to 8 voice_sections.Each voice_section length is flexible.(3). Voice length can be individually up to 3.5, 7, 14 or 21 seconds at 6kHz S.R. for each voice_section.Voice+mute length can be individually up to 11, 21, 21 or 21 seconds at 6kHz sample rate for eachvoice_section.(4). Total 16 voice_steps are available for 2 sub_tables. Each sub_table can only use maximum 8voice_steps. For each voice_step, it can specify one voice_section and IO1 output enable options if IO1 is set as an output.(5). Build in oscillator, 15 kinds of playback speed option for internal resistor used : ( 4.0k ~ 18.1kHz)A B C D E F G H18.1kHz 14.4kHz 12.0kHz 10.3kHz 9.0kHz 8.0kHz 7.2kHz 6.6kHzI J K L M N O -6.0kHz 5.6kHz 5.2kHz 4.8kHz 4.5kHz 4.3kHz 4.0kHz -<Internal oscillator: OSC pad must be bonded to GND>(6). IO1 can be either input or output pin (Mask option).(7). Optional “Two Triggers Input” (TG and IO1), or “One Trigger Input” (TG pin only).(A). Each input pin has mask options for Edge/Level, Hold/Unhold and Retrigger/Irritrigger trigger modes.(B). TG input can choose CDS+1M、CDS、1M pull-low、10M pull low or floating input type.(C). IO1 input can choose CDS+1M、CDS、1M pull-low or floating input type.(D). Debounce time: Long debounce for push buttons. Short debounce for switches. (※In Two TriggersInput Mode, only one kind of debounce time is available.)(E). Priority:TG > IO1.(8). IO1 has the following output option A~F :(A). Stop_High pulse : high active stop pulse output whenever device stop playing.(B). Busy_High active : high active signal output during playing.(C). Busy_Low active : low active signal output during playing.(D). LED 3Hz flash : 3Hz sink signal output for driving LED during playing at 6kHz sample rate.(E). LED 6Hz flash : 6Hz sink signal output for driving LED during playing at 6kHz sample rate.(F). LED dynamic 2/4 : dynamic sink signal output for driving LED during playing.※Where (D) and (E) is the LED flash rate at 6kHz sample rate. For different sample rate, the LED flash rate is different from original 3Hz or 6Hz.(9). PWM1 and PWM2 can directly drive buzzer or 8, 16, 32 or 64 ohms speaker.(10). The voice_section length of “voice length + mute length” must be the multiple of 80Hex (AVH308 ) or100Hex (AV0708 , AV1408 , AV2108).(11). In voice_section sequence arrangement (00~07), If there are some voice_sections with only mute andwithout voice, they should be put next to the last voice_section with voice. Besides, that is not allowed to put a pure mute voice_section between 2 voice_sections with voice, or put the pure mute voice_section on first place (00).(12). Oscillator selection:(A). External oscillator: Connect OSC pin to Vdd with a resistor, Rosc.(B). Internal oscillator: Connect OSC pin to GND. (Not suggested because of frequency shift and systemstability)※Input Type Description:Option DescriptionCDS + 1M Normal selection for button trigger.Only 1M pull-low resistance when key-pressed, and 1M+300K(parallel) pull-low resistance when key-released.CDS Internal 300K ohms pull-low resistance, usually for photo-resistor trigger.1M pull-low Internal 1M ohms pull-low resistance, reserve for some special applications. 10M pull-low Internal 10M ohms weak pull-low, usually for touching trigger.Floating No internal resistor connection, usually connected to other output pin or connected to GND by an external resistor.* 10M pull-low option is not available for IO1 input.18.1kHz 14.4kHz 12.0kHz 10.3kHz 9.0kHz 8.0kHz 7.2kHz 6.6kHzI J K L M N O - 6.0kHz 5.6kHz 5.2kHz 4.8kHz 4.5kHz 4.3kHz 4.0kHz - <如果選擇內建的頻率振盪器,請將 OSC 腳接㆞。

S-AV33A中文资料

TOSHIBA RF POWER AMPLIFIER MODULES-AV33AFM RF POWER AMPLIFIER MODULE FOR 32W COMMERCIAL VHF RADIO APPLICATIONS・Power Gain: 28 dB (Min.)・Total Efficiency: 45% (Min.)ABSOLUTE MAXIMUM RATINGS (Tc = 25°C, I T < 10 A, Z G = Z L = 50Ω)CHARACTERISTICS SYMBOL TESTCONDITION RATING UNIT Maximum Current I T10 A Power Supply Voltage V DD V GG = 0 V (GND), RF: none 16.5 VControl Voltage V GG 10.5≤ V DD≤ 16.5 V, Pi = 50 mW 5.5 V Instantaneous Output Power PomaxV GG≤ 5.5 V, Pi = 50 mW, 10.5 ≤V DD ≤16.5V, within 2 seconds40 WInput Power P i 10.5≤ V DD≤ 16.5 V, V GG≤ 5.5 V 100 mW Operating Case Temperature T c (opr)10.5 ≤V DD ≤16.5 V, V GG≤ 5.5 V, Pi = 50mW (Note 2)-30 to 100 °C Storage Temperature T stg-40 to 110 °CNote 1: The maximum ratings are the limits that must not be exceeded even for an instant, under worst possible conditions. Exceeding the ratings may cause device damage, ignition, or deterioration. Therefore, whendesigning the circuitry, derating factors should be applied so that the absolute maximum ratings are notexceeded.Note 2: The output power rating satisfies the range shown in Figures 1 and 2 according to the operating case temperature. Ensure that the device should be operated within the specified operating range. The figures belowindicate the output power obtained 2 seconds after Po is generated.Note 3: The case temperature is monitored using the screw terminal blocks on the input side that are used for the module implementation.Note 4: To protect a device from being permanently damaged, the power-on sequence must be as follows (, while the reversed order should be applied when turning off): 1. VDD, 2. Pi, 3. VGG*When the device is used at Tc =100°C, the output power rating is 31 W as shown in Figure 1. When the power dissipation at Tc = 100°C exceeds the rating shown in Figure 2, the output derating is required to limit the dissipation within the specified range.Figure 1 Pomax-Tc Figure 2 PDmax-TcPACKAGE OUTLINEELECTRICAL CHARACTERISTICS (Tc = 25°C, Z G = 50Ω)CHARACTERISTICS SYMBOL TEST CONDITIONMIN TYP. MAXUNITFrequency Range f range — 134 — 174MHzOutput Power P o 32 — — WPower Gain G p 28 — — dB Total Efficiency ηT 45 — — %Input VSWR VSWRin — — 3.0 — Second Harmonic 2nd HRM V DD = 12.5 VV GG = 5 VPi = 50 mW Z L = 50 Ω — — -30 dB Third Harmonic3rd HRM——-30dBRuggedness — 10.5 V ≤ V DD ≤ 16.5 V, 0 V ≤ V GG ≤ V GGajs(V GG = V GGajs @ Po = 32 W)Pi = 50 mWP o = 32 W (Adjusted via V GG @ Z L = 50Ω)VSWR LOAD 20: 1 ALL PHASE (@ 2 s) No Damage —Stability — 10.5 V ≤ V DD ≤ 16.5 V, 0 V ≤ V GG ≤ V GGajs(V GG = V GGajs @ Po = 32 W)Pi = 50 mWP o ≤ 32 W (Adjusted via V GG @ Z L = 50Ω)VSWR LOAD 3: 1 ALL PHASENo spurious output of -60 dB or greater—Note 5:The output power is intended to follow the rating provided in Figure 1 in Note 2. Note 6: StabilityMeasurements are performed under the conditions where VSWR is at 3:1 through all phases over the whole frequency range, and they are guaranteed only under those conditions. Even though it is guaranteed to be stable where VSWR is at 3:1, the VSWR load over the operating frequency should be designed to be 50 Ω .At the same time, ensure that the VSWR load does not deviate much from 50Ω even for a moment, nor deviate even a little from 50Ω continually. The S-AU82AL is not intended for such operations, and proper operation under such conditions is not guaranteed due to the possibilities of heat generation in the module and its applications.HANDLING PRECAUTIONS・Since this product has a protective cap, care should be taken to avoid applying an excessive impact and allowing foreign objects to get inside when handling this product. Also, please do not remove a cap. If the cap is removed, the foreign object inside the module or the applied impact may lead IC failure, causing smoke or ignition.・Since this product is structurally susceptible to static electricity, protections against the static electricity should be applied to objects that may come in direct contact with devices, such as worktables, equipment, operators and solder irons.・This product is not designed nor intended to perform a continuous transmission for applications like a base station.Please do not use this product for such applications, for the reliability cannot be guaranteed.・This product is intended to be used for a single operation (single-device operation). A proper operation is not guaranteed for a parallel operation. A parallel operation should be performed in accordance with your own good judgment.・Mounting method・The flatness of a heat sink must not exceed 50 μm. If the flatness exceeds 50 μm, the device may experience an unexpected stress that may lead to module breakdown due to damage or ignition in the substrate inside a module and other module parts.・Please apply thermal compound between a module and a heat sink to improve the adhesive property.・Use a 4-mm diameter screw with the clamping screw torque of 1.2 to 1.5 Nm.・Please solder the module leads after the screw is clamped.EQUIVALENT CIRCUITTEST FIXTURE① PiZ G = 50 ΩGG ③ V DDPo = 50 Ω ⑤GROUND (Flange )V GGV DDμFMARKINGProduct Number (without A)characters: Date of manufactureExplanation of Lot No.RESTRICTIONS ON PRODUCT USE20070701-EN •The information contained herein is subject to change without notice.•TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the “Handling Guide for Semiconductor Devices,” or “TOSHIBA Semiconductor Reliability Handbook” etc.• The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.).These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury (“Unintended Usage”). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in his document shall be made at the customer’s own risk.•The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations.• The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third parties.• Please contact your sales representative for product-by-product details in this document regarding RoHS compatibility. Please use these products in this document in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances. Toshiba assumes no liability for damage or losses occurring as a result of noncompliance with applicable laws and regulations.。

FR38中文资料

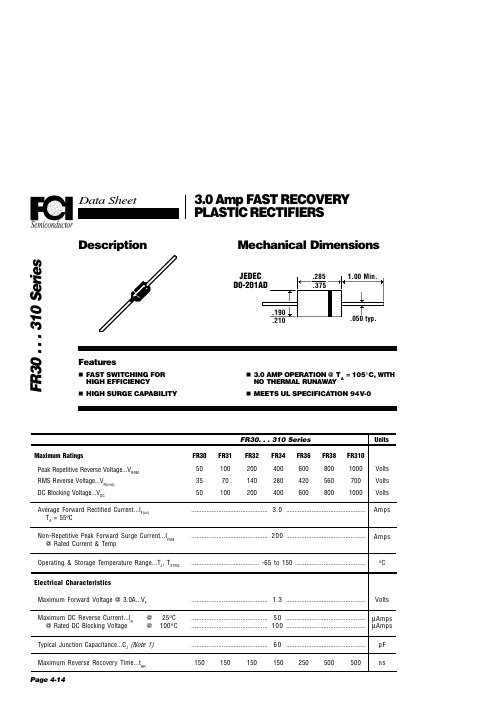

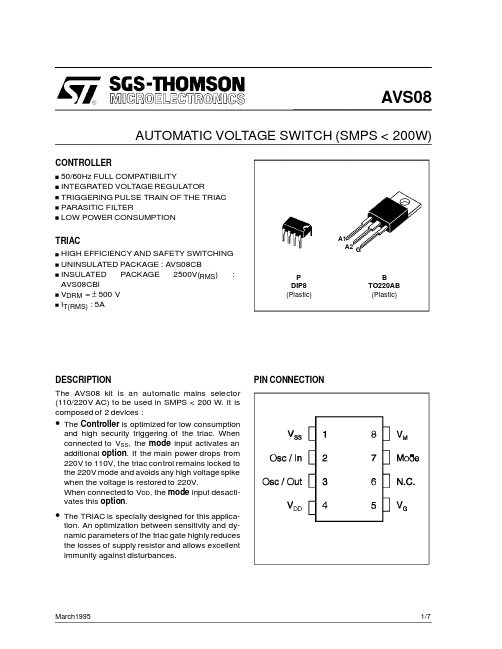

Data Sheet

3.0 Amp FAST RECOVERY PLASTIC RECTIFIERS

Mechanical Dimensions

JEDEC D0-201AD

.190 .210 .285 .375 1.00 Min.

Description

FR30 . . . 310 Series

NOTES: 1. Measured @ 1 MHz and applied reverse voltage of 4.0V. 2. Thermal Resistance Junction to Case, Jedec Method.

Page 4-15

FR30 . . . 310 Series

Oscilliscope Note 1

(+)

0A -.25A

Notes: 1 . Rise Time = 7 ns Max. Impedance = 1 megohm, 22 pF 2 . Rise Time = 10 ns Max. Source Impedance = 50 Ohms

-1.0A

1 cm Time Base Set @ 50/100ns/cm

FR30. . . 310 Series Maximum Ratings Peak Repetitive Reverse Voltage...VRRM RMS Reverse Voltage...VR(rms) DC Blocking Voltage...VDC Average Forward Rectified Current...IF(av) TA = 55°C Non-Repetitive Peak Forward Surge Current...IFSM @ Rated Current & Temp Operating & Storage Temperature Range...TJ, TSTRG Electrical Characteristics Maximum Forward Voltage @ 3.0A...VF Maximum DC Reverse Current...IR @ Rated DC Blocking Voltage @ @ 25°C 100°C ............................................. 1.3 ............................................... FR30 50 35 50 FR31 100 70 100 FR32 200 140 200 FR34 400 280 400 FR36 600 420 600 FR38 800 560 800 FR310 1000 700 1000

SM8JZ47中文资料

Gate Non−Trigger Voltage

Holding Current

Thermal Resistance

Critical Rate of Rise of Off−State Voltage

SM8GZ47 SM8JZ47

SM8GZ47A SM8JZ47A

Critical Rate of Rise of Off−State Voltage at Commutation

SM8GZ47,SM8JZ47,SM8GZ47A,SM8JZ47A

TOSHIBA BI−DIRECTIONAL TRIODE THYRISTOR SILICON PLANAR TYPE

SM8GZ47,SM8JZ47,SM8GZ47A,SM8JZ47A

AC POWER CONTROL APPLICATIONS

SYMBOL

TOSHIBA PRODUCT MARK

SM8GZ47, SM8GZ47A

TYPE

SM8JZ47, SM8JZ47A

SM8GZ47A, SM8JZ47A

*4

MARK

M8GZ47 M8JZ47

A

Example 8A : January 1998 8B : Febrary 1998 8L : December 1998

· The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

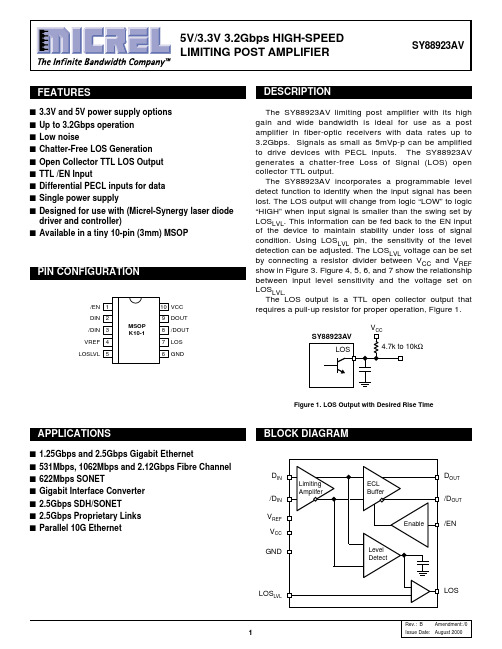

SY88923AV资料

s 3.3V and 5V power supply options s Up to 3.2Gbps operation s Low noises Chatter-Free LOS Generation s Open Collector TTL LOS Output s TTL /EN Inputs Differential PECL inputs for data s Single power supplysDesigned for use with (Micrel-Synergy laser diode driver and controller)s Available in a tiny 10-pin (3mm) MSOPThe SY88923AV limiting post amplifier with its high gain and wide bandwidth is ideal for use as a post amplifier in fiber-optic receivers with data rates up to 3.2Gbps. Signals as small as 5mVp-p can be amplified to drive devices with PECL inputs. The SY88923AV generates a chatter-free Loss of Signal (LOS) open collector TTL output.The SY88923AV incorporates a programmable level detect function to identify when the input signal has been lost. The LOS output will change from logic “LOW” to logic “HIGH” when input signal is smaller than the swing set by LOS LVL . This information can be fed back to the EN input of the device to maintain stability under loss of signal condition. Using LOS LVL pin, the sensitivity of the level detection can be adjusted. The LOS LVL voltage can be set by connecting a resistor divider between V CC and V REF show in Figure 3. Figure 4, 5, 6, and 7 show the relationship between input level sensitivity and the voltage set on LOS LVL.The LOS output is a TTL open collector output that requires a pull-up resistor for proper operation, Figure 1.s 1.25Gbps and 2.5Gbps Gigabit Ethernets 531Mbps, 1062Mbps and 2.12Gbps Fibre Channel s 622Mbps SONETs Gigabit Interface Converter s 2.5Gbps SDH/SONETs 2.5Gbps Proprietary Links sParallel 10G EthernetFigure 1. LOS Output with Desired Rise TimeΩV /EN DIN /DIN VREF LOSLVL VCC DOUT /DOUT LOS GNDGND/ENLOSD IN /D IN V REF V CC LOS LVLD OUT /D OUTMICREL-SYNERGY3250 SCOTT BOULEVARD SANTA CLARA CA 95054USA TEL + 1 (408) 980-9191 FAX + 1 (408) 914-7878 WEB This information is believed to be accurate and reliable, however no responsibility is assumed by Micrel for its use nor for any infringement of patents or other rights of third parties resulting from its use. No license is granted by implication or otherwise under any patent or patent right of Micrel Inc.© 2000 Micrel Incorporated。

彩电总线调整中英文对照表

1 3.58或3 表示3.58MHz N TSC制2 4.43或4 表示4.43MHz副载波或PAL3 50Hz或5 加在调整项目中,特指此调整项目针对50Hz场扫描4 60Hz或6 加在调整项目中,特指此调整项目针对60Hz场扫描5 50Hz C POS 50Hz行中心校正6 H - SIZE 行幅7 V - AMP: 场幅8 V - HEIGHT9 V - LINERITY场线性10 V - PHASE 场相位(场中心)11 V - S - CORRECT 垂直S校正12 ABL ABL(自动亮度限制);ABL开关13 ABL CON T ABL(自动亮度限制)控制值14 ABL GAIN 自动亮度控制增益15 ABL POIN T 自动亮度控制点16 ABL STAR ABL(自动亮度限制)起始值17 ADDRESS 地址18 ADJUSTMEN T 调整19 AF 自动频率控制状态20 AFC AFC;A FC环路增益;AFC开关;AFC模式21 AFC MODE EX T 自动频率控制外接模式22 AFC MODE TV自动频率控制电视模式23 AFF AFC关断24 AFT 自动频率微调 F V CO(图像中频压控振荡器)调整;中频VCO25 AFT/SKIP 自动微调/跳跃26 AFTO AFT输出27 AGC 自动增益控制;AGC自动/恒定;AGC起控点28 AGC - TAKE AGC起控点29 AIP 调整中频锁相环30 AKB 显像管暗平衡自动调整;AKB关断蓝截止31 AL 自动音量调整32 ALIGN; 调整33 ALIGNMENTS34 ALS 音频电平设置35 AMPLI50Hz 50Hz场幅调整36 AS 自动扫描37 AUDIO 伴音;音频38 AUTO FLESH 自动肤色校正39 AUTO SRCH自动搜索40 A V 音频/视频;视频设定;A V输入端子数41 A V MODE A V模式42 A V SHARPNESS A V锐度43 A V TINT A V色调44 A VI ONLY Y/YN 可选择一路A V或两路A V输入45 A V-MODE A V模式46 AX AGC删除47 B;B-显像管亮平衡蓝色调整48 B BIAS;B_;B CU T OFF 蓝偏置;显像管阿暗平衡蓝色调整49 B DRIVE(GAIN) 蓝色激励(增益);显像管亮平衡蓝色激励调整50 BLUE 蓝色51 BALANCE 平衡52 BAND MODE 波段控制模式53 BAND OUT 波段输出54 BASIC 基本(型)55 BASS 低音;副低音56 BB;BC;BCF;B - CO; 蓝枪截止点;显像管暗平衡蓝枪调整57 BCT;BCU T;BCUT OFF;B-58 CU TOFF59 BCW 亮度控制范围60 BD;BDR;B-DRIVE;BDRV; 蓝激励;显像管亮平衡蓝激励调整61 BDRY62 BEL;BELL;BELLFO;BELL FILTER SECA M钟型滤波器63 BG B.G伴音制式设置64 BG;B - GAIN 蓝激励;显像管亮平衡蓝激励调整65 BH童锁66 BK时钟67 BKP 消隐图像;消隐关断图像;消隐关断时的图像数据68 BL 平衡69 BALCK STR;BLACKSTRECH黑电平扩展70 BLACK STRETCH POINT 黑电平扩展点71 BLK SW 消隐开关72 BLOCK组件73 BLU;BLUE 蓝;蓝背景;蓝背景ON/OFF74 BLUE BACK MODE 蓝背景模式75 BLUE GAIN 蓝激励;显像管亮平衡蓝激励调整76 BOW 弓形77 BR 亮度;副亮度78 BR ABL TH亮度ABL阀值;ABL起控点调整79 BRAND 商标;厂标显示80 BRC 蓝枪截止点;显像管暗平衡蓝枪调整81 BRI亮度;副亮度82 BRI ABL TH亮度ABL阀值;ABL起控点调整83 BRI CE 亮度中心调值84 BRI MA;BRI MI亮度最大(最小)值85 BRIGHT; BRIGHT-NESS 亮度;副亮度86 BR T 亮度;框亮度数据(索尼)87 BR T ABL 亮度ABL(控制量)88 BR TC 副亮度中间值;亮度调整中心数据89 BR TN 最小亮度;副亮度最小值90 BR TS 亮度调整中心数据校正;副亮度校正91 BR TX 副亮度最大值92 BT 亮度93 BTSC BTSC制立体声94 BUS 总线95 BUS CONT OK总线控制正常96 BUS LINE OK 总线正常97 BUS OFF 总线关断98 B-Y BLACK OFFSET B-Y信号黑偏移量99 C.BLK 色度信号消隐100 CANCEL 清除101 C-B 显像管暗平衡蓝色调整102 CFO色度陷波器f o调整103 C-G 显像管暗平衡绿色调整104 CHINESE OSD中文屏显105 CHINESE TUNER 中国制式高频头106 SUB R-CU TOFF 在彩色降噪接通时的红枪截止点校正107 SUB SHARP;SUB-SHARTNESS 副锐度108 SUB TINT 副色调109 SUB-VOLUME 副音量110 SU PER WIDE GEOMETRY超宽屏幕几何失真111 SURROUND 环绕声112 SV4 4.43A V(视频)副清晰度(中心值)113 SX4 4.43副清晰度最大值114 SY;SYS;SYSTEM 制式;多制式系统115 SYN;SYNC 同步;合成器116 TC 梯形失真117 TCC 色调控制中心118 T-COLOR BA R 彩条信号119 TCW 色调控制范围120 TEB 文本显示亮度121 TEC 文本显示对比度122 TELETEX T 图文电视123 TEST PA TTERN 测试图124 TEST SIGNAL 测试信号125 TEXT CON TRAST 文本对比度126 TEXT.H;TEX T.V屏显水平(垂直)位置127 TEXT/MIX文本/混合128 TINT 色调129 TINTC 色调中心值130 TLT 倾斜失真(梯形失真)131 TMN;TMX色调控制最小(最大)值132 TN 高频头133 TNTC 副色调中间值134 TNTN;TN TX 副色调最小(最大)值135 TONE 音调136 TRAP 陷波137 TPC;TR;TRAP;TRP 梯形失真138 TRAPEZIUM;TRAPEZOID 梯形失真139 TRE;TREBLE 高音140 TSC 图文对比度141 TUNER 调谐器;高频头142 TV SY STEMS 电视制式143 TXCN;TXCX屏显对比度最小(最大)值144 TXH 屏显水平位置145 TXP;TXPIC 图文图像(对比度)146 TXT 文本;图文;屏显147 TYPE 类型148 UCBOW 上部偏中弓形失真149 UCC 对比度控制中心150 UCP 上角枕形失真151 UCW 单色控制范围152 UHF ONLY Y/N可选择一路UHF接收获全接收153 ULN 上部场线性154 UNKNOWN 不能确定155 UP 上156 UTIL T;UTL 上部倾斜失真(梯形失真)157 UV UHF/VHF158 UVG 用户可变y校正159 UYB;UYBOW 垂直上角弓形失真160 V AMPLITUDE 场幅161 V CEN TERING 场中心162 V COMP 场补偿163 V FREQUENCY 场频164 V LIN;V LNEARITY场线性165 V OU T PHASE50 50Hz场中心(场输出相位) 166 V POSI 场中心167 V SC;V S-CORRECTION场S校正168 V SHIFT 场中心169 V SIZE 场幅170 V25;V 50 音量调整20%(50%)位置音量数据值171 V60 60Hz场中心调节;60Hz场幅(飞利浦)172 V A;V-A场幅度;垂直孔阑补偿173 V AD 视频输出幅度174 V AG 对角失真(平行四边形失真)175 value 数值176 V AM;V-AMPL;V-AMPLITUDE 场幅177 V-ANG 场对角形失真178 V AP 场幅179 V A W 垂直孔阑白色180 V-BIAS 场偏置181 VBW 场消隐宽度控制182 VCD MD EX T 视频时的VCD(视频/色度/扫描)模式183 VCD MD TEX T 图文时的VCD(视频/色度/扫描)模式184 VCD MD TV TV时的VCD(视频/色度/扫描)模式185 V-CENTER 场中心186 VCO压控振荡器;38MHz中频振荡187 VCOMP 亮度变化引起的场幅失真校正188 V-COMPENSA TION 场补偿189 V-CORRECT 垂直校正;场线性校正190 VCP 垂直补偿;光栅亮度变化时,场幅校正设置191 VCX压控晶体振荡器自由振荡频率192 VENH 梳状滤波器垂直加强(轮廓校正)193 VER;VERSION 版本;类型194 VERT LINEARITY场线性调整195 VFQ;VFR 场频196 VH 场幅197 VID 视频;图像检波;视频识别模式198 V-ID SW 视频识别开关199 VIDEO 视频;视频输入设定(设定为3个)200 VIDEO H.CEN 行相位;行中心201 VIDEO LEVEL 视频电平202 VIF SY S中频设定203 VL;V-L 伴音限制;场线性204 VLB 场线性校正205 VLIN;V-LIN;V-LINEAR;VLN 场线性206 CHROMA GAIN 色度增益207 CHROMA TRA P FO 色度信号陷波频率208 CHROMA TRA P Q色度信号陷波Q值209 CLC 彩色控制中心;色度控制中心210 CLOCK时钟211 CMN;CMX 色度控制最小(最大)值212 CNP;CNR 光栅角部校正失真213 CNR GAIN 彩色降噪增益214 CN T 对比度215 CN T CE 对比度中心值216 CN T MA;CNT MI对比度最大(最小)值217 CNTC 对比度调整中间值;副对比度中间值218 CNTN;CNTX (副)对比度最小(最大)值219 CO443 PA L彩色(色度)中心220 COINCIDENTDET LEVEL 符合检测电平221 COL MA彩色(色度)最大值222 COLC N制副色度中间值;色度调整中间值223 COLN 副色度最小值224 COLOR 彩色;色度225 COLOR LIMIT LEVEL 色度限制电平226 COLOR LIMIT SW 色度限制切换227 COLOUR 彩色228 COLP PAL制色度中间值AL副色度中心值229 COLS SECAM色度中间值;SECA M副色度中间值230 COLX 副色度最大值231 COMB 梳状滤波器232 COMMUNICA TION 通讯233 CONNECTION 连接234 CON;CONT;CON TRAST 对比度;副对比度235 COOL 冷;白平衡冷色调236 COR;CO RINC 核化(降噪);核化降噪峰值237 CORPN;CP;C-P;CR 四角枕形失真238 C-R 显像管暗平衡红色调整239 CRH;CRL 设定字符高(低)240 CROSS HA TCH格子信号241 CSD字符的显示位置242 CSW 彩色开关243 S-SYSTEM 彩色制式244 CT 对比度;色度陷波(索尼)245 CUT-OFF 截止;显像管截止点调整(暗平衡调整)246 CV屏显垂直位置;CV/YC(复合视频信号/Y C信号)选择247 DA TA 数据248 DA TE 日期249 D-B 显像管亮平衡蓝色调整250 DC GREEN PAL 绿枪截止(显像管暗平衡)调整251 DC RED PAL 红枪截止(显像管暗平衡)调整252 DC TRAIN RA TE 直流补偿程度253 DEFECT MODULE 产生故障的电路组件254 DEGAU 消磁;消磁功能接通/断开255 DELTA COOL 偏冷色(白平衡)256 DELTA COOL BLUE(GREEN RED) 冷色调白平衡蓝(绿\红)数据257 DELTA WARM 偏暖色白平衡258 DELTA WARM BLUE(GREEN RED) 暖色调白平衡蓝(绿\红)数据259 DEMP FO去加重频率260 DIAGNOSE 故障自检(代码)261 DID 消磁关闭262 DIGI OSD;DIGITAL OSD 数字OSD(屏显)设定263 DIGITAL SCAN数字扫描264 DISPLA Y显示;屏显语言选择265 DK D/K伴音制式设置266 DL;DLT;DLY 延迟控制;延时267 DPC 枕形失真校正(东芝);动态图像ON/OFF(索尼)268 DPCS 50Hz/60Hz校正269 DPI;D-PIC 动态图像270 D-R 显像管亮平衡红色调整271 DRG SW 以红枪或绿枪为准(DRGSW用于转换显像管红绿枪,按遥控器电平增/减键在R、G(红、枪)之间转变)272 DRV CN T 激励控制273 DSHFT 直流电平移(水平静会聚微调)274 DT 延时275 DT BW 黑白延时276 DVM VM(速度调制)静噪失效277 EAST/WEST CO RNER 光栅四角调整278 EAST/WEST PARABOLA光栅左右枕形失真279 EAST/WEST TO P COMPENSA TION 光栅顶部补偿280 EAST/WEST TRAPEZIUM 光栅梯形失真281 EEPROM 电可檫可编程存储器282 EFFECT 效果283 EHH;EHV 高压对光栅行幅(场幅)的影响284 ENGLISH ONLY 仅有英文285 EQ+DOLBY 均衡器+杜比286 EQUALIZER 均衡器287 ER;ERR;ERRORS 故障;错误;故障自检代码288 ERC 误差计数;故障计数289 EURO A V 欧洲标准A V输入290 EVG 场保护启动291 EVOL 外接信号预置音量292 EW 光栅左右枕形失真293 EW-CORNER 光栅左右角部失真294 EW-PARABO;EW-PARABOLA光栅左右枕形失真295 F TRAP 陷波微调296 FAC 工厂297 FBP BL SW 行逆程脉冲消隐开关298 F-BW 强制黑白切换299 FEA TURE-BOX 特色电路组件300 FG P FM伴音(BG、I、DK制)预置音量301 FILT;FIL TER;FL T 滤波器302 FM 调频模拟伴音303 FM GAIN 调频伴音增益304 FM LEVEL 调频伴音电平305 FMA调频伴音衰减电平306 FORCED COLOUR 强制彩色307 FRAME 桢;框308 FRU、FRV、FRY U(V、Y)信号桢309 FSW 强制开关310 FU福字设定(康佳)311 FUNCTIONAL TEST 功能测试312 FVOL FM伴音音量预刻度313 G 绿;显像管亮平衡绿色调整314 G BIAS;G CUT OFF;G_ 显像管暗平衡绿色调整315 G DRIVE;G DRIVE GAIN 绿色激励(显像管亮平衡绿色调整)316 GAM;GAMMA Y校正317 GA TE PULSE 选通脉冲318 GB;GC;GCF;GCO;GCT;GCU T;GCU T OFF绿色截止点;显像管暗平衡绿色调整319 GD;GDR;GDRV 绿激励;显像管亮平衡绿色调整320 GENERAL 一般性的(调整)321 GEOMETRIC;GEOMETRY光栅几何失真322 GG;G-GAIN 绿增益;显像管亮平衡绿色调整323 GLOBAL 全球;全球立体声324 GRC 绿色截止点;显像管暗平衡绿色调整325 GREEN 绿326 GREEN GAIN 绿增益;显像管亮平衡绿色调整327 H AFC 行A FC(增益)328 H AMPLITUDE 行幅329 H BLANK L;H BLK L 行左消隐;左黑边调整330 H BLANK R;H BLK R 行右消隐;右黑边调整331 H BLK PHASE50 50Hz行消隐相位332 H CEN TER 50 50Hz行中心333 H FREQ 行频334 H PHASE;H PHASE SHIFT 航向位;行中心335 H POSI TION 行中心;(字符)水平位置336 H SHIFT 行中心337 H AMP H.AMP(行幅)338 HAFC 行A FC;AFC中心数据339 HALF TONE SW 半色调增益选择340 HBL;HBR 水平消隐左(右)宽度341 HBS 行消隐宽度ON/OFF342 HC 四角失真(飞利浦)343 HC;H-C;H-CENTER 行中心344 HCO 高压跟踪模式345 H-COMPENSA TION行补偿346 H-CORNER 行边角失真;角部枕形失真347 H-CORRECT 水平校正348 HCP 水平补偿;光栅屏幕亮度变化时,行幅校正设置349 HD 行中心(飞利浦)350 H-FRE 行频351 HI BLUE 显像管亮平衡蓝色调整352 HI GAIN高增益;增强接受设定(康佳)353 HI GREEN 显像管亮平衡绿色调整354 HIT高度;场幅355 HITS 60Hz场扫描场幅校正数据;50/60Hz场幅差异356 HOLD 保持357 HOR 水平;行;画中画左右对称(海信)358 HORIZONTAL POS50 50Hz场频行中心359 HOTEL 旅馆模式360 HOTEL CHANNEL 旅馆频道361 HOUT CLOCK SW 行输出时钟切换362 HP;H-PARAB 水平枕形失真;左右枕形失真363 H-PHA;H-PHASE 行相位;水平中心364 HPOS;H-POS;HPS 水平位置;行中心365 HR 屏显水平位置366 HS 旅馆模式(飞利浦)367 H-S;HSF;HSH;H-SHIFT 水平位置;行中心368 HSIZE;HSZ 行幅369 HT;H TILT;H TLHTR;H-TRA P;HTRP 几何失真;水平倾斜失真(梯形失真) 370 HTR;H-TRAP;H TRP 几何失真;水平倾斜失真(梯形失真)371 HVH;HVV 高压变动引起的行幅(场幅)变化补偿372 HW;H-W;H-WIDTH行幅373 I I伴音制式设置374 IF-FRE 中频频率375 IR-PLL 中频锁相环376 IGR IGR立体声;西德制式立体声377 INDEX 索引378 INTC 色调调整中心数据379 ITL 隔行扫描380 JSW 跳跃ON/OFF开关381 KARAOKE 卡拉OK382 KEY 梯形失真校正383 KEYS 60Hz梯形失真校正384 LA音频电平调整385 LAN;LANG 语言;屏显语言设定386 LANG/LOGO 语言/标志387 LANGUAGE 语言;菜单文字设定388 LBK 左消隐宽度389 LCB;LCBOW 下部偏中弓形失真390 LCP 下角枕形失真391 LEFT 左;画中画靠左边位置(海信)392 LEV 电平393 LIM 限幅;RGB限幅ON/OFF(索尼)394 LIN 线性;场线性395 LINE WIDTH行宽396 LLN 下部场线性397 LO BLUE;LO GREEN 暗平衡蓝色(绿色)调整398 LT1 亮度信号瞬态改善(L TI)方式1399 LTIL T;LTL 下部倾斜失真(梯形失真)400 LUM LINEAR 亮度信号线性401 LYB;LYBOW 垂直下角弓形失真402 M M伴音制式设置403 M00 模式数据(M表示模式数据,数字表示第几个模式数据)404 MAIN MENU 主菜单405 M-DSP 主屏幕显示位置水平方向406 VLIS 60Hz场线性407 VM 速度调制;VM(速度调制)电平;VM(速度调制)ON/OFF;伴音静音408 VM0 视频模式0;VCD(视频/色度/扫描)模式0409 VMC 距屏幕顶1/4~3/4区域进行线性调整;垂直S校正;垂直积分补偿410 VMH VM(速度调整)限幅器(高)411 VML VM(速度调整)限幅器(低)412 VOCAL CU T 消声413 VOF 场关断414 VOL 音量415 VOL32 音量32值设定416 VOLS SCAR T接口音量417 VOLUME-CON 音量控制418 VOM 音量输出增益419 VP;VPO S;VPOSI TION;VPS 场中心420 VS 场S校正(飞利浦)421 VS;V-S 场中心422 V-S.CORR;VSC;VSCO;VSCOR 场S校正423 VSC;V-SCROLL 垂直卷动(索尼\三星)424 VS-CORRECTION场S校正425 VSD场扫描关闭,进入水平一条亮线状态426 VSF;VSH;VSHFT;VSHIFT 场中心427 VSL;V-SLOPE 场线性;场线性对称点428 VSM50 场同步范围开关(场频50Hz时)429 VSW 视频静噪开关430 VSZ 场幅431 VX 场放大432 VZW 垂直变焦433 WARM (白平衡)暖色调434 WD窗口选择435 WDS 窗口选择436 W-H 加权437 WHI TE DRIVE 显像管亮平衡调整;白平衡激励调整438 WHI TE PEAK LIMI T 峰白限制439 WHI TE TONE 白色调;白平衡色温440 WID;WIDE 宽度;行幅441 WIDE PICTURE-MU TE 图像消隐开关442 WIDE P-MU TE STAR T 图像静噪开始443 WIDE P-MU TE STOP 图像静噪停止444 WIDE V-BLK STAR T 场消隐开始445 WIDE V-BLK STOP 场消隐停止446 WIDE V-BLK SW 场消隐宽度开关447 WIDS 60Hz行幅度448 WI P 划变449 WOOFER 低音扬声器450 WRP 写入位置451 WSP 划变速度452 XBS BASS 重低音453 XTL 晶振454 XVOL 外接预置音量455 Y亮度信号456 Y SUB 副对比度457 Y SUB CONTRAST 亮度信号副对比度458 Y BLK 亮度信号消隐459 Y-BOW 场弓形失真460 YC-AJ Y C调整461 Y-CI DELA Y Y-CI(亮度/色度改善)延时462 Y-DELA Y;YDL 亮度信号延迟463 Y-DL SW PAL NTSC PAL/NTSC亮度延迟464 YFI亮度信号滤波器调整465 YNR 亮度信号降噪466 ZOOM 变焦467 ZSW 变焦开关。

CY7C026AV-20AC资料

3.3V 4K/8K/16K x 16/18 Dual-Port Static RAMCY7C024AV/025AV/026AV CY7C0241AV/0251AV/036AVFeatures•True dual-ported memory cells which allowsimultaneous access of the same memory location •4/8/16K × 16 organization (CY7C024AV/025AV/026AV)•4/8K × 18 organization (CY7C0241AV/0251AV)•16K × 18 organization (CY7C036AV)•0.35-micron CMOS for optimum speed/power •High-speed access: 20 and 25 ns •Low operating power—Active: I CC = 115 mA (typical)—Standby: I SB3 = 10 µA (typical)•Fully asynchronous operation •Automatic power-down•Expandable data bus to 32/36 bits or more using Master/Slave chip select when using more than one device•On-chip arbitration logic•Semaphores included to permit software handshaking between ports•INT flag for port-to-port communication •Separate upper-byte and lower-byte control •Pin select for Master or Slave•Commercial and industrial temperature ranges •Available in 100-pin TQFPNotes:1.I/O 8–I/O 15 for x16 devices; I/O 9–I/O 17 for x18 devices.2.I/O 0–I/O 7 for x16 devices; I/O 0–I/O 8 for x18 devices.3.A 0–A 11 for 4K devices; A 0–A 12 for 8K devices; A 0–A 13 for 16K devices.4.BUSY is an output in master mode and an input in slave mode.R/W L OE LI/O 8/9L –I/O 15/17LI/O Control Address DecodeA 0L –A 11/12/13L CE L OE L R/W LBUSY L I/O ControlCE L Interrupt Semaphore ArbitrationSEM L INT L M/SUB LLB L I/O 0L –I/O 7/8LR/W R OE RI/O 8/9L –I/O 15/17RCE R UB RLB R I/O 0L –I/O 7/8RUB L LB LLogic Block DiagramA 0L –A 11/1213LTrue Dual-Ported RAM Array A 0R –A 11/12/13RCE R OE R R/W R BUSY R SEM RINT R UB R LB RAddress DecodeA 0R –A 11/12/13R[1][1][2][2][4][4]12/13/148/98/912/13/148/98/912/13/1412/13/14[3][3][3][3]Pin ConfigurationsNotes:5.A12L on the CY7C025AV.6.A12R on the CY7C025AV.Top View100-Pin TQFP100 9997989623142415960611213151416454039959417269108761127283029313235343637383367666465636268697075737472718988868785939284NCNCNCNCA5LA4LINT LA2LA0LLGNDINT RA0RA1L NCNCNCNCI/O10LI/O11LI/O15LV CCGNDI/O1RI/O2RV CC9091A3LM/SR I/O14LGNDI/O12LI/O13LA1RA2RA3RA4RNCNCNCNCI/O3RI/O4RI/O5RI/O6RNCNCNCNC18192021222324258382818079787776585756555453525143444546 47484950I/O9LI/O8LI/O7LI/O6LI/O5LI/O4LI/O3LI/O2LGNDI/O1LI/OLOELSEM LVCCCELUBLLBLNCA11LA1LA9LA8LA7LA6LI/O0RI/O7RI/O8RI/O9RI/O1RI/O11RI/O12RI/O13RI/O14RGNDI/O15RŒRRWRGNDSEMRCERUBRLBRNCA11RA1RA9RA8RA7RA6RA5RCY7C024AV (4K × 16)R/W L[5][6CY7C025AV (8K × 16)Notes:7.A 12L on the CY7C0251AV.8.A 12R on the CY7C0251AVC.Pin Configurations (continued)Top View100-Pin TQFP100 9997989623142415960611213151416454039959417269108761127283029313235343637383367666465636268697075737472718988868785939284NC NC NC NC A 5L A 4L INT L A 2L A 0L BUSY L GND INT R A 0R A 1L NC NC I/O 11L I/O 12L I/O 16L V CC GND I/O 1R I/O 2R V CC 9091A 3L M/S BUSY R I/O 15L GND I/O 13L I/O 14L A 1R A 2R A 3R A 4R NC NC NC NCI/O 3R I/O 4R I/O 5R I/O 6R NC NC18192021222324258382818079787776585756555453525143444546 47484950I /O 9LI /O 7LI /O 6LI /O 5LI /O 4LI /O 3LI /O 2LI /O 10LG N DI /O 1LI /O 0LO E LS E M LV C CC E LU B LL B LN C A 11LA 10LA 9LA 8LA 7LA 6LI/O 0R I /O 7RI /O 16RI /O 9RI /O 10RI /O 11RI /O 12RI /O 13RI /O 14RG N D I /O 15RO E RR W R G N D S E M R C E R U B R L B R N C A 11R A 10R A 9R A 8RA 7R A 6RA 5RCY7C0241AV (4K × 18)I/O 8L I/O 17L I/O 8R I/O 17RR /W L[8][7]1329291908485878688898382817678777980939495969798991005960616766646563626869707573747271NC NC NC A6L A5L A4L INTL A2L A0L GND M/S A0R A1R A1L A3L BUSYR INTR A2R A3R A4R A5R NC NC NCBUSYL 5857565554535251CY7C026AV (16K × 16)NC NC NC NC I/O10L I/O11L I/O15L I/O13L I/O14L GND I/O0R VCC I/O3R GND I/O12L I/O1R I/O2R I/O4R I/O5R I/O6R NC NC NC NCVCC 17161591012111314876451819202122232425I /O 9L I /O 8L I /O 7L I /O 6L I /O 5L I /O 4L I /O 0L I /O 2L I /O 1L V C C R W L U B L L B L G N D I /O 3L S E M L C E L A 113L A 12L A 11L A 10L A 9L A 8L A 7LO E L 3435364241394038374344455048494746A 6R A 7R A 8R A 9R A 10R A 11R C E R A 13R U B R G N D R W R G N D I /O 14R L B R A 12R O E R I /O 15R I /O 13R I /O 12R I /O 11R I /O 10R I /O 9R I /O 8R I /O 7R S E M R 3332313029282726CY7C0251AV (8K × 18)Pin Configurations (continued)Top View100-Pin TQFP 100 9997989623142415960611213151416454039959417269108761127283029313235343637383367666465636268697075737472718988868785939284NC NC NC A 5L A 4L INT L A 2L A 0L BUSY L GND INT R A 0R A 1L NC NC I/O 11L I/O 12L I/O 16L V CC GND I/O 1R I/O 2R V CC 9091A 3L R I/O 15L GND I/O 13L I/O 14L A 1R A 2R A 3R A 4R NC NC NCI/O 3R I/O 4R I/O 5R I/O 6R NC NC18192021222324258382818079787776585756555453525143444546 47484950I /O 9LI /O 7LI /O 6LI /O 5LI /O 4LI /O 3LI /O 2LI /O 10LG N DI /O 1LI /O 0LO E LS E M LV C CC E LU B LL B L A 11LA 10LA 9LA 8LA 7L A 6LI/O 0R I /O 7RI /O 16RI /O 9RI /O 10RI /O 11RI /O 12RI /O 13RI /O 14RG N D I /O 15RO E R R W R G N D S E M RC E RU B RL B RA 11RA 10RA 9R A 8RA 7RA 6RA 5RI/O 8L I/O 17L I/O 8R I/O 17RR /W LCY7C036AV (16K × 18)A 13L A 13R A 12LA 12RSelection GuideCY7C024AV/025AV/026AV CY7C0241AV/0251AV/036AV-20CY7C024AV/025AV/026AV CY7C0241AV/0251AV/036AV-25Unit Maximum Access Time 2025ns Typical Operating Current 120115mA Typical Standby Current for I SB1(Both ports TTL Level)3530mA Typical Standby Current for I SB3(Both ports CMOS Level)1010µAArchitectureThe CY7C024AV/025AV/026AV and CY7C0241AV/0251AV/ 036AV consist of an array of 4K, 8K, and 16K words of 16 and 18 bits each of dual-port RAM cells, I/O and address lines, and control signals (CE, OE, R/W). These control pins permit independent access for reads or writes to any location in memory. To handle simultaneous writes/reads to the same location, a BUSY pin is provided on each port. Two Interrupt (INT) pins can be utilized for port-to-port communication. Two Semaphore (SEM) control pins are used for allocating shared resources. With the M/S pin, the devices can function as a master (BUSY pins are outputs) or as a slave (BUSY pins are inputs). The devices also have an automatic power-down feature controlled by CE. Each port is provided with its own output enable control (OE), which allows data to be read from the device.Functional DescriptionThe CY7C024AV/025AV/026AV and CY7C0241AV/0251AV /036AV are low-power CMOS 4K, 8K, and 16K ×16/18 dual-port static RAMs. Various arbitration schemes are included on the devices to handle situations when multiple processors access the same piece of data. Two ports are provided, permitting independent, asynchronous access for reads and writes to any location in memory. The devices can be utilized as standalone 16/18-bit dual-port static RAMs or multiple devices can be combined in order to function as a 32/36-bit or wider master/slave dual-port static RAM. An M/S pin is provided for implementing 32/36-bit or wider memory applications without the need for separate master and slave devices or additional discrete logic. Application areas include interprocessor/multiprocessor designs, communications status buffering, and dual-port video/graphics memory. Each port has independent control pins: Chip Enable (CE), Read or Write Enable (R/W), and Output Enable (OE). Two flags are provided on each port (BUSY and INT). BUSY signals that the port is trying to access the same location currently being accessed by the other port. The Interrupt flag (INT) permits communication between ports or systems by means of a mail box. The semaphores are used to pass a flag, or token, from one port to the other to indicate that a shared resource is in use. The semaphore logic is comprised of eight shared latches. Only one side can control the latch (semaphore) at any time. Control of a semaphore indicates that a shared resource is in use. An automatic power-down feature is controlled independently on each port by a Chip Select (CE) pin.The CY7C024AV/025AV/026AV and CY7C0241AV/0251AV/ 036AV are available in 100-pin Thin Quad Plastic Flatpacks (TQFP).Write OperationData must be set up for a duration of t SD before the rising edge of R/W in order to guarantee a valid write. A write operation is controlled by either the R/W pin (see Write Cycle No. 1 waveform) or the CE pin (see Write Cycle No. 2 waveform). Required inputs for non-contention operations are summarized in Table1.If a location is being written to by one port and the opposite port attempts to read that location, a port-to-port flowthrough delay must occur before the data is read on the output; otherwise the data read is not deterministic. Data will be valid on the port t DDD after the data is presented on the other port. Read OperationWhen reading the device, the user must assert both the OE and CE pins. Data will be available t ACE after CE or t DOE after OE is asserted. If the user wishes to access a semaphore flag, then the SEM pin must be asserted instead of the CE pin, and OE must also be asserted.Pin DefinitionsLeft Port Right Port DescriptionCE L CE R Chip Enable.R/W L R/W R Read/Write Enable.OE L OE R Output Enable.A0L–A13L A0R–A13R Address (A0–A11 for 4K devices; A0–A12 for 8K devices; A0–A13 for16K).I/O0L–I/O17L I/O0R–I/O17R Data Bus Input/Output.SEM L SEM R Semaphore Enable.UB L UB R Upper Byte Select (I/O8–I/O15 for x16 devices; I/O9–I/O17 for x18devices).LB L LB R Lower Byte Select (I/O0–I/O7 for x16 devices; I/O0–I/O8 for x18devices).INT L INT R Interrupt Flag.BUSY L BUSY R Busy Flag.M/S Master or Slave Select.V CC Power.GND Ground.NC No Connect.InterruptsThe upper two memory locations may be used for message passing. The highest memory location (FFF for the CY7C024AV/41AV, 1FFF for the CY7C025AV/51AV, 3FFF for the CY7C026AV/36AV) is the mailbox for the right port and the second-highest memory location (FFE for the CY7C024AV/ 41AV, 1FFE for the CY7C025AV/51AV, 3FFE for the CY7C026AV/36AV) is the mailbox for the left port. When one port writes to the other port’s mailbox, an interrupt is generated to the owner. The interrupt is reset when the owner reads the contents of the mailbox. The message is user defined.Each port can read the other port’s mailbox without resetting the interrupt. The active state of the busy signal (to a port) prevents the port from setting the interrupt to the winning port. Also, an active busy to a port prevents that port from reading its own mailbox and, thus, resetting the interrupt to it.If an application does not require message passing, do not connect the interrupt pin to the processor’s interrupt request input pin.The operation of the interrupts and their interaction with Busy are summarized in Table2.BusyThe CY7C024AV/025AV/026AV and CY7C0241AV/0251AV/ 036AV provide on-chip arbitration to resolve simultaneous memory location access (contention). If both ports’ CEs are asserted and an address match occurs within t PS of each other, the busy logic will determine which port has access. If t PS is violated, one port will definitely gain permission to the location, but it is not predictable which port will get that permission. BUSY will be asserted t BLA after an address match or t BLC after CE is taken LOW.Master/SlaveA M/S pin is provided in order to expand the word width by configuring the device as either a master or a slave. The BUSY output of the master is connected to the BUSY input of the slave. This will allow the device to interface to a master device with no external components. Writing to slave devices must be delayed until after the BUSY input has settled (t BLC or t BLA), otherwise, the slave chip may begin a write cycle during a contention situation. When tied HIGH, the M/S pin allows the device to be used as a master and, therefore, the BUSY line is an output. BUSY can then be used to send the arbitration outcome to a slave.Semaphore OperationThe CY7C024AV/025AV/026AV and CY7C0241AV/0251AV/ 036AV provide eight semaphore latches, which are separate from the dual-port memory locations. Semaphores are used to reserve resources that are shared between the two ports. The state of the semaphore indicates that a resource is in use. For example, if the left port wants to request a given resource, it sets a latch by writing a zero to a semaphore location. The left port then verifies its success in setting the latch by reading it. After writing to the semaphore, SEM or OE must be deasserted for t SOP before attempting to read the semaphore. The semaphore value will be available t SWRD + t DOE after the rising edge of the semaphore write. If the left port was successful (reads a zero), it assumes control of the shared resource, otherwise (reads a one) it assumes the right port has control and continues to poll the semaphore. When the right side has relinquished control of the semaphore (by writing a one), the left side will succeed in gaining control of the semaphore. If the left side no longer requires the semaphore, a one is written to cancel its request.Semaphores are accessed by asserting SEM LOW. The SEM pin functions as a chip select for the semaphore latches (CE must remain HIGH during SEM LOW). A0–2 represents the semaphore address. OE and R/W are used in the same manner as a normal memory access. When writing or reading a semaphore, the other address pins have no effect.When writing to the semaphore, only I/O0 is used. If a zero is written to the left port of an available semaphore, a one will appear at the same semaphore address on the right port. That semaphore can now only be modified by the side showing zero (the left port in this case). If the left port now relinquishes control by writing a one to the semaphore, the semaphore will be set to one for both sides. However, if the right port had requested the semaphore (written a zero) while the left port had control, the right port would immediately own the semaphore as soon as the left port released it. Table 3 shows sample semaphore operations.When reading a semaphore, all sixteen/eighteen data lines output the semaphore value. The read value is latched in an output register to prevent the semaphore from changing state during a write from the other port. If both ports attempt to access the semaphore within t SPS of each other, the semaphore will definitely be obtained by one side or the other, but there is no guarantee which side will control the semaphore.Table 1.Non-Contending Read/WriteInputs OutputsCE R/W OE UB LB SEM I/O9–I/O17I/O0–I/O8OperationH X X X X H High Z High Z Deselected: Power-DownX X X H H H High Z High Z Deselected: Power-Down L L X L H H Data In High Z Write to Upper Byte Only L L X H L H High Z Data In Write to Lower Byte Only L L X L L H Data In Data In Write to Both BytesL H L L H H Data Out High Z Read Upper Byte OnlyL H L H L H High Z Data Out Read Lower Byte OnlyL H L L L H Data Out Data Out Read Both BytesX X H X X X High Z High Z Outputs DisabledH H L X X L Data Out Data Out Read Data in Semaphore FlagX H L H H L Data Out Data Out Read Data in Semaphore FlagH X X X L Data In Data In Write D IN0 into Semaphore FlagX X H H L Data In Data In Write D IN0 into Semaphore Flag L X X L X L Not AllowedL X X X L L Not AllowedTable 2.Interrupt Operation Example (assumes BUSY L = BUSY R = HIGH)[9]Left Port Right Port Function R/W L CE L OE L A0L–13L INT L R/W R CE R OE R A0R–13R INT R Set Right INT R Flag L L X FFF[12]X X X X X L[11] Reset Right INT R Flag X X X X X X L L FFF (or 1/3FFF)H[10] Set Left INT L Flag X X X X L[10]L L X1FFE (or 1/3FFE)X Reset Left INT L Flag X L L1FFE[12]H[11]X X X X X Table 3.Semaphore Operation ExampleFunction I/O0–I/O17 Left I/O0–I/O17 Right StatusNo action11Semaphore-freeLeft port writes 0 to semaphore01Left Port has semaphore tokenRight port writes 0 to semaphore01No change. Right side has no write access to semaphore Left port writes 1 to semaphore10Right port obtains semaphore tokenLeft port writes 0 to semaphore10No change. Left port has no write access to semaphore Right port writes 1 to semaphore01Left port obtains semaphore tokenLeft port writes 1 to semaphore11Semaphore-freeRight port writes 0 to semaphore10Right port has semaphore tokenRight port writes 1 to semaphore11Semaphore freeLeft port writes 0 to semaphore01Left port has semaphore tokenLeft port writes 1 to semaphore11Semaphore-freeNotes:9.See Functional Description for specific highest memory locations by device.10.If BUSY R=L, then no change.11.If BUSY L=L, then no change.12.See Functional Description for specific addresses by device.Maximum Ratings [13](Above which the useful life may be impaired. For user guide-lines, not tested.)Storage Temperature .................................–65°C to +150°C Ambient Temperature withPower Applied.............................................–55°C to +125°C Supply Voltage to Ground Potential...............–0.5V to +4.6V DC Voltage Applied toOutputs in High-Z State..........................–0.5V to V CC + 0.5V DC Input Voltage[14]...............................–0.5V to V CC + 0.5V Output Current into Outputs (LOW).............................20 mA Static Discharge Voltage.......................................... > 2001V Latch-up Current.................................................... > 200 mA Operating RangeRange Ambient Temperature V CC Commercial0°C to +70°C 3.3V ± 300 mV Industrial[15]–40°C to +85°C 3.3V ± 300 mVElectrical Characteristics Over the Operating RangeParameter DescriptionCY7C024AV/025AV/026AVCY7C0241AV/0251AV/036AVUnit -20-25Min.Typ.Max.Min.Typ.Max.V OH Output HIGH Voltage (V CC=3.3V) 2.4 2.4V V OL Output LOW Voltage0.40.4V V IH Input HIGH Voltage 2.0 2.0V V IL Input LOW Voltage0.80.8V I OZ Output Leakage Current–1010–1010µA I IX Input Leakage Current–1010–1010µAI CC Operating Current (V CC = Max., I OUT=0mA) Outputs Disabled Com’l.120175115165mA Ind.[15]135185mAI SB1Standby Current (Both Ports TTL Level)CE L & CE R≥ V IH, f = f MAX Com’l.35453040mA Ind.[15]4050mAI SB2Standby Current (One Port TTL Level) CE L| CE R≥ V IH, f = f MAX Com’l.751106595mA Ind.[15]75105mAI SB3Standby Current (Both Ports CMOS Level)CE L & CE R≥ V CC−0.2V, f = 0Com’l.1050010500µA Ind.[15]10500µAI SB4Standby Current (One Port CMOS Level)CE L | CE R≥ V IH, f = f MAX[16]Com’l.70956080mA Ind.[15]7090mACapacitance[17]Parameter Description Test Conditions Max.UnitC IN Input Capacitance T A = 25°C, f = 1 MHz,V CC = 3.3V 10pFC OUT Output Capacitance10pF Notes:13.The Voltage on any input or I/O pin can not exceed the power pin during power-up.14.Pulse width < 20 ns.15.Industrial parts are available in CY7C026AV and CY7C036AV only.16.f MAX = 1/t RC = All inputs cycling at f = 1/t RC (except output enable). f = 0 means no address or control lines change. This applies only to inputs at CMOS level standby I SB3.17.Tested initially and after any design or process changes that may affect these parameters.AC Test Loads and Waveforms3.0V GND90%90%10%3ns3ns10%ALL INPUT PULSES(a)Normal Load (Load 1)R1=590Ω3.3VOUTPUT R2=435ΩC =30pFV TH =1.4VOUTPUTC =30pF(b)Thévenin Equivalent (Load 1)(c)Three-State Delay (Load 2)R1=590ΩR2=435Ω3.3VOUTPUTC =5pFR TH =250Ω≤≤including scope and jig)(Used for t LZ , t HZ , t HZWE , and t LZWE Switching Characteristics Over the Operating Range [18]Parameter DescriptionCY7C024AV/025AV/026AV CY7C0241AV/0251AV/036AV Unit-20-25Min.Max.Min.Max.Read Cycle t RC Read Cycle Time 2025ns t AA Address to Data Valid2025ns t OHA Output Hold From Address Change 33ns t ACE [19]CE LOW to Data Valid 2025ns t DOEOE LOW to Data Valid 1213ns t LZOE [20, 21, 22]OE Low to Low Z 33ns t HZOE [20, 21, 22]OE HIGH to High Z 1215ns t LZCE [20, 21, 22]CE LOW to Low Z 33ns t HZCE [20, 21, 22]CE HIGH to High Z 1215ns t PU [22]CE LOW to Power-Up 0ns t PD [22]CE HIGH to Power-Down 2025ns t ABE [19]Byte Enable Access Time2025nsWrite Cycle t WC Write Cycle Time 2025ns t SCE [19]CE LOW to Write End 1520ns t AW Address Valid to Write End 1520ns t HA Address Hold From Write End 00ns t SA [19]Address Set-up to Write Start 00ns t PWE Write Pulse Width 1520ns t SDData Set-up to Write End1515nsNotes:18.Test conditions assume signal transition time of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specifiedI OI /I OH and 30-pF load capacitance.19.SCE time.20.At any given temperature and voltage condition for any given device, t HZCE is less than t LZCE and t HZOE is less than t LZOE .21.Test conditions used are Load 3.22.This parameter is guaranteed but not tested. For information on port-to-port delay through RAM cells from writing port to reading port, refer to Read Timingwith Busy waveform.Data Retention ModeThe CY7C024AV/025AV/ 026AV and CY7C0241AV/ 0251AV/036AV are designed with battery backup in mind. Data retention voltage and supply current are guaranteed over temperature. The following rules ensure data retention:1.Chip Enable (CE) must be held HIGH during data retention, within V CC to V CC – 0.2V.2.CE must be kept between V CC – 0.2V and 70% of V CC during the power-up and power-down transitions.3.The RAM can begin operation >t RC after V CC reaches the minimum operating voltage (3.0V).Notes:23.For information on port-to-port delay through RAM cells from writing port to reading port, refer to Read Timing with Busy waveform.24.Test conditions used are Load 2.25.t BDD is a calculated parameter and is the greater of t WDD –t PWE (actual) or t DDD –t SD (actual).26.CE = V CC , V in = GND to V CC , T A = 25°C. This parameter is guaranteed but not tested.t HDData Hold From Write Endns t HZWE [21, 22]R/W LOW to High Z 1215ns t LZWE [21, 22]R/W HIGH to Low Z3ns t WDD [23]Write Pulse to Data Delay4550ns t DDD [23]Write Data Valid to Read Data Valid 3035ns Busy Timing [24]t BLA BUSY LOW from Address Match 2020ns t BHA BUSY HIGH from Address Mismatch 2020ns t BLC BUSY LOW from CE LOW 2020ns t BHC BUSY HIGH from CE HIGH 1717ns t PS Port Set-up for Priority 55ns t WB R/W HIGH after BUSY (Slave)00ns t WH R/W HIGH after BUSY HIGH (Slave)1517ns t BDD [25]BUSY HIGH to Data Valid 2025ns Interrupt Timing [24]t INS INT Set Time 2020ns t INR INT Reset Time2020ns Semaphore Timingt SOP SEM Flag Update Pulse (OE or SEM)1012ns t SWRD SEM Flag Write to Read Time 55ns t SPS SEM Flag Contention Window 55ns t SAASEM Address Access Time2025nsSwitching Characteristics Over the Operating Range (continued)[18]Parameter DescriptionCY7C024AV/025AV/026AV CY7C0241AV/0251AV/036AV Unit -20-25Min.Max.Min.Max.TimingParameter Test Conditions [26]Max.Unit ICC DR1@ VCC DR = 2V50µAData Retention Mode3.0V3.0VV CC > 2.0VV CC to V CC –0.2VV CCCEt RCV IHSwitching WaveformsNotes:27.R/W is HIGH for read cycles.28.Device is continuously selected CE = V IL and UB or LB = V IL . This waveform cannot be used for semaphore reads.29.OE = V IL .30.Address valid prior to or coincident with CE transition LOW.31.To access RAM, CE = V IL , UB or LB = V IL , SEM = V IH . T o access semaphore, CE = V IH , SEM = V IL .t RCt AAt OHADATA VALIDPREVIOUS DATA VALIDDATA OUTADDRESSt OHARead Cycle No.1 (Either Port Address Access)[27, 28, 29]t ACEt LZOEt DOEt HZOEt HZCEDATA VALIDt LZCEt PUt PDI SBI CCDATA OUTOECE and LB or UBCURRENTRead Cycle No.2 (Either Port CE/OE Access)[27, 30, 31]UB or LBDATA OUTt RCADDRESSt AAt OHACEt LZCEt ABEt HZCEt HZCEt ACE t LZCERead Cycle No. 3 (Either Port)[27, 29, 30, 31]Notes:32.R/W must be HIGH during all address transitions.33. A write occurs during the overlap (t SCE or t PWE ) of a LOW CE or SEM and a LOW UB or LB.34.t HA is measured from the earlier of CE or R/W or (SEM or R/W) going HIGH at the end of write cycle.35.If OE is LOW during a R/W controlled write cycle, the write pulse width must be the larger of t PWE or (t HZWE + t SD ) to allow the I/O drivers to turn off and data to be placed onthe bus for the required t SD . If OE is HIGH during an R/W controlled write cycle, this requirement does not apply and the write pulse can be as short as the specified t PWE .36.To access RAM, CE = V IL , SEM = V IH .37.To access upper byte, CE = V IL , UB = V IL , SEM = V IH .T o access lower byte, CE = V IL , LB = V IL , SEM = V IH .38.Transition is measured ±500 mV from steady state with a 5-pF load (including scope and jig). This parameter is sampled and not 100% tested.39.During this period, the I/O pins are in the output state, and input signals must not be applied.40.If the CE or SEM LOW transition occurs simultaneously with or after the R/W LOW transition, the outputs remain in the high-impedance state.Switching Waveforms (continued)t AWt WCt PWE t HDt SDt HACER/WOEDATAOUTDATA INADDRESSt HZOE t SAt HZWE t LZWEWrite Cycle No.1: R/W Controlled Timing [32, 33, 34, 35][38][38][35][36, 37]NOTE 39NOTE 39t AWt WCt SCE t HDt SDt HACER/WDATA INADDRESSt SAWrite Cycle No. 2: CE Controlled Timing [32, 33, 34, 40][36, 37]Notes:41.CE = HIGH for the duration of the above timing (both write and read cycle).42.I/O 0R = I/O 0L = LOW (request semaphore); CE R = CE L = HIGH.43.Semaphores are reset (available to both ports) at cycle start.44.If t SPS is violated, the semaphore will definitely be obtained by one side or the other, but which side will get the semaphore is unpredictable.Switching Waveforms (continued)t SOPt SAAVALID ADRESS VALID ADRESSt HD DATA IN VALID DATA OUT VALIDt OHAt AWt HAt ACEt SOPt SCEt SDt SAt PWEt SWRDt DOEWRITE CYCLEREAD CYCLEOER/WI/O 0SEMA 0–A 2Semaphore Read After Write Timing, Either Side [41]MATCHt SPSA 0L –A 2LMATCHR/W L SEM LA 0R –A 2RR/W R SEM RTiming Diagram of Semaphore Contention [42, 43, 44]。

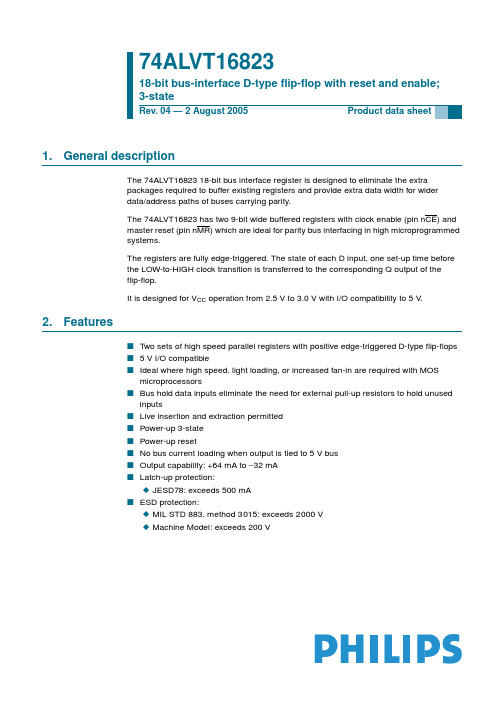

AV16823DL资料

74ALVT1682318-bit bus-interface D-type flip-flop with reset and enable;3-stateRev. 04 — 2 August 2005Product data sheet1.General descriptionThe 74ALVT16823 18-bit bus interface register is designed to eliminate the extrapackages required to buffer existing registers and provide extra data width for widerdata/address paths of buses carrying parity.The 74ALVT16823 has two 9-bit wide buffered registers with clock enable (pin nCE) andmaster reset(pin nMR)which are ideal for parity bus interfacing in high microprogrammedsystems.The registers are fully edge-triggered. The state of each D input, one set-up time beforethe LOW-to-HIGH clock transition is transferred to the corresponding Q output of theflip-flop.It is designed for V CC operation from 2.5 V to 3.0 V with I/O compatibility to 5 V.2.Featuress Two sets of high speed parallel registers with positive edge-triggered D-type flip-flopss 5 V I/O compatibles Ideal where high speed, light loading, or increased fan-in are required with MOSmicroprocessorss Bus hold data inputs eliminate the need for external pull-up resistors to hold unusedinputss Live insertion and extraction permitteds Power-up 3-states Power-up resets No bus current loading when output is tied to 5 V buss Output capability: +64 mA to−32 mAs Latch-up protection:x JESD78: exceeds 500 mAs ESD protection:x MIL STD 883, method 3015: exceeds 2000 Vx Machine Model: exceeds 200 V3.Quick reference data4.Ordering informationTable 1:Quick reference data T amb = 25°C.Symbol Parameter ConditionsMin Typ Max Unit t PLH propagation delay nCP to nQx C L = 50 pF; V CC =2.5V 1.5 2.9 4.5ns C L = 50 pF; V CC =3.3V 1.0 2.3 3.1ns t PHL propagation delay nCP to nQx C L = 50 pF; V CC =2.5V 1.4 2.7 4.2ns C L = 50 pF; V CC =3.3V 1.0 2.1 2.9ns C i input capacitance V I = 0 V or V CC -3-pF C o output capacitance V I/O = 0 V or V CC -9-pF I CCquiescent supply currentoutputs disabled;V CC =2.5V -40-µA outputs disabled;V CC =3.3V-70-µATable 2:Ordering informationType numberPackagetemperature range NameDescriptionVersion 74ALVT16823DL −40°C to +85°C SSOP56plastic shrink small outline package; 56leads;body width 7.5mmSOT371-174ALVT16823DGG−40°C to +85°CTSSOP56plastic thin shrink small outline package;56leads;body width 6.1mmSOT364-15.Functional diagramFig 1.IEC logic symbolFig 2.Bushold circuit (one data input)4D1,2543525516498489471045128D5,644134314421541164017381937203621342333243126001aad24255G328R65627EN530G72EN1R23C41291D01D11D21D31D41D51D61D71D82D02D12D22D32D42D52D62D72D81Q01Q11Q21Q31Q41Q51Q61Q71Q82Q02Q12Q22Q32Q42Q52Q62Q72Q81CE 2MR 1CP 2OE 2CE 1OE 1MR 2CP 7C8001aad245data input to internal circuitV CCxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxx x x x xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xx xx xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxx x xxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxx xxx74ALVT16823_4© Koninklijke Philips Electronics N.V . 2005. All rights reserved.Product data sheet Rev. 04 — 2 August 20054 of 20Philips Semiconductors74ALVT1682318-bit bus-interface D-type flip-flop with reset and enable; 3-stateFig 3.Logic diagram001aad243nQ8nD8nQ3nD3nQ2nD2nQ1nD1nQ0nD0nD QnCPRnD QRnD QRnD QRnD QRnOEnMR CP CP CP CP CP nCEnQ4nD4nD QRCP nQ5nD5nD QRCP nQ6nD6nD QRCP nQ7nD7nD QRCP6.Pinning information6.1Pinning6.2Pin descriptionFig 4.Pin configuration74ALVT168231MR 1CP 1OE 1CE 1Q01D0GND GND 1Q11D11Q21D2V CC V CC 1Q31D31Q41D41Q51D5GND GND 1Q61D61Q71D71Q81D82Q02D02Q12D12Q22D2GND GND 2Q32D32Q42D42Q52D5V CC V CC 2Q62D62Q72D7GND GND 2Q82D82OE 2CE 2MR 2CP001aad4031234567891011121314151617181920212223242526272856555453525150494847464544434241403938373635343332313029Table 3:Pin descriptionSymbol Pin Description1MR 1 1 master reset input (active-LOW)1OE 2 1 output enable input (active-LOW)1Q03 1 data output 0GND 4ground (0 V)1Q15 1 data output 11Q26 1 data output 2V CC 7supply voltage 1Q381 data output 3Table 3:Pin description …continuedSymbol Pin Description1Q49 1 data output 41Q510 1 data output 5GND11ground (0 V)1Q612 1 data output 61Q713 1 data output 71Q814 1 data output 82Q015 2 data output 02Q116 2 data output 12Q217 2 data output 2GND18ground (0 V)2Q319 2 data output 32Q420 2 data output 42Q521 2 data output 5V CC22supply voltage2Q623 2 data output 62Q724 2 data output 7GND25ground (0 V)2Q826 2 data output 82OE27 2 output enable input (active-LOW)2MR28 2 master reset input (active-LOW)2CP29 2 clock pulse input (active rising edge) 2CE30 2 clock enable input (active-LOW)2D831 2 data input 8GND32ground (0 V)2D733 2 data input 72D634 2 data input 6V CC35supply voltage2D536 2 data input 52D437 2 data input 42D338 2 data input 3GND39ground (0 V)2D240 2 data input 22D141 2 data input 12D042 2 data input 01D843 1 data input 81D744 1 data input 71D645 1 data input 6GND46ground (0 V)1D547 1 data input 51D448 1 data input 41D349 1 data input 37.Functional description7.1Function table[1]H = HIGH voltage level;h = HIGH voltage level one set-up time prior to the LOW-to-HIGH clock transition;L = LOW voltage level;l = LOW voltage level one set-up time prior to the LOW-to-HIGH clock transition;NC = no change;X = don’t care;Z = high-impedance OFF-state;↑ = LOW-to-HIGH clock transition;↑ = not a LOW-to-HIGH clock transition.8.Limiting valuesV CC 50supply voltage 1D251 1 data input 21D152 1 data input 1GND 53ground (0 V)1D054 1 data input 01CE 55 1 clock enable input (active-LOW)1CP561 clock pulse input (active rising edge)Table 3:Pin description …continuedSymbol Pin Description Table 4:Function tableOperating mode Input OutputnOEnMR nCE nCP nDx nQx clearL L X X X L load and read data L H L ↑h H l L holdL H H ↑X NC high-impedanceHXXXXZTable 5:Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134).Symbol Parameter Conditions Min Max Unit V CC supply voltage −0.5+4.6V V I input voltage [1]−0.5+7.0V V O output voltage output in OFF-state or HIGH-state [1]−0.5+7.0V I IK input diode current V I < 0 V −50-mA I OKoutput diode currentV O < 0 V−50-mA[1]The input and output negative voltage ratings may be exceeded if the input and output clamp current ratings are observed.[2]The performance capability of a high-performance integrated circuit in conjunction with its thermal environment can create junction temperatures which are detrimental to reliability.9.Recommended operating conditionsI O output current output in LOW-state -128mA output in HIGH-state−64-mA T stg storage temperature −65+150°C T jjunction temperature[2]-150°CTable 5:Limiting values …continuedIn accordance with the Absolute Maximum Rating System (IEC 60134).Symbol Parameter Conditions Min Max Unit Table 6:Recommended operating conditionsSymbol Parameter ConditionsMin Typ Max Unit V CC =2.5 V V CC supply voltage 2.3- 2.7V V I input voltage0- 5.5V V IH HIGH-level input voltage 1.7--V V IL LOW-level input voltage --0.7V I OH HIGH-level output current --−8mA I OLLOW-level output currentnone--8mA current duty cycle ≤50%;f ≥ 1 kHz--24mA ∆t/∆v input transition rise or fall rateoutputs enabled --10ns/V T amb ambient temperature in free air−40-+85°C V CC =3.3 VV CC supply voltage 3.0- 3.6V V I input voltage0- 5.5V V IH HIGH-level input voltage 2.0--V V IL LOW-level input voltage --0.8V I OH HIGH-level output current --−32mA I OLLOW-level output currentnone--32mA current duty cycle ≤50%;f ≥ 1 kHz--64mA ∆t/∆v input transition rise or fall rateoutputs enabled --10ns/V T ambambient temperaturein free air −40-+85°C10.Static characteristicsTable 7:Static characteristicsAt recommended operating conditions; voltages are referenced to GND (ground=0V); T amb =−40°C to +85°C. Symbol Parameter Conditions Min Typ Max Unit V CC = 2.5 V± 0.2 V[1]V IK input clamping voltage V CC = 2.3V; I IK=−18mA-−0.85−1.2VV OH HIGH-level output voltage V CC = 2.3 V to 2.7 V; I OH=−100µA V CC− 0.2V CC-VV CC = 2.3 V; I OH=−8mA 1.8 2.5-VV OL LOW-level output voltage V CC = 2.3V; I OL=100µA-0.070.2VV CC = 2.3V; I OL=24 mA-0.30.5VV CC = 2.3V; I OL=8 mA--0.4VV OL(pu)power-up LOW-level outputvoltage V CC = 2.7 V; I O = 1 mA;V I=V CC or GND[2]--0.55VI LI input leakage currentcontrol pins V CC=2.7V; V I = V CC or GND-0.1±1µAV CC = 0 V to 2.7 V; V I=5.5V-0.110µA I/O data pins V CC =2.7V; V I= V CC[3]-0.11µAV CC =2.7V; V I= 0V[3]-+0.1−5µA I OFF off current V CC = 0V; V I or V O=0V to 4.5V-+0.1±100µA I HOLD bus hold current data inputs V CC = 2.3V; V I = 0.7V[4]-100-µAV CC = 2.3V; V I = 1.7V[4]-−70-µA I EX external current into output output HIGH-state when V O>V CC;V O=5.5V; V CC=2.3 V-10125µAI PU power-up 3-state outputcurrent V CC≤ 1.2V; V O=0.5V to V CC;V I=GND or V CC[5]-1±100µAI PD power-down 3-state outputcurrent V CC≤ 1.2V; V O=0.5V to V CC;V I=GND or V CC[5]-1±100µAI OZ3-state output current V CC = 2.7 V; V I = V IL or V IHoutput HIGH state; V O = 2.3 V-0.55µAoutput LOW-state; V O = 0.5 V-+0.5−5µA I CC quiescent supply current V CC = 2.7 V; V I = GND or V CC; I O = 0Aoutputs HIGH-state-0.040.1mAoutputs LOW-state- 2.7 4.5mAoutputs disabled[6]-0.040.1mA∆I CC additional quiescent supplycurrent per input pin V CC = 2.3 V to 2.7 V; one input atV CC−0.6V, other inputs at V CC or GND[7]-0.040.4mAC I input capacitance V I = 0 V or V CC-3-pF C O output capacitance V I/O = 0 V or 3.0V-9-pF V CC = 3.3 V± 0.3 V[8]V IK input clamping voltage V CC = 3.0V; I IK=−18mA-−0.85−1.2V V OH HIGH-level output voltage V CC = 3.0 V to 3.6 V; I OH=−100µA V CC− 0.2V CC-VV CC = 3.0 V; I OH=−32mA 2.0 2.3-V[1]All typical values are at V CC = 2.5V and T amb = 25°C.[2]For valid test results, data must not be loaded into the flip-flops (or latches) after applying power.[3]Unused pins at V CC or GND.[4]Not guaranteed.[5]This parameter is valid for any V CC between 0V and 1.2V with a transition time of up to 10ms.From V CC =1.2V to V CC =2.5V ±0.2V a transition time of 100µs is permitted. This parameter is valid for T amb =25°C only.[6]I CC is measured with outputs pulled up to V CC or pulled down to ground.[7]This is the increase in supply current for each input at the specified voltage level other than V CC or GND.[8]All typical values are at V CC = 3.3V and T amb = 25°C.[9]This is the bus hold overdrive current required to force the input to the opposite logic state.V OLLOW-level output voltageV CC = 3.0V; I OL =100µA -0.070.2V V CC = 3.0V; I OL =16 mA -0.250.4V V CC = 3.0V; I OL =32 mA -0.30.5V V CC = 3.0V; I OL =64 mA-0.40.55V V OL(pu)power-up LOW-level output voltageV CC = 3.6 V; I O = 1 mA;V I =V CC or GND[2]--0.55VI LIinput leakage current control pins V CC =3.6V; V I = V CC or GND -0.1±1µA V CC = 0 V or 3.6 V; V I =5.5V -0.110µA I/O data pinsV CC = 3.6 V; V I =V CC [3]-0.51µA V CC =3.6V; V I = 0 V[3]-+0.1−5µA I OFF off currentV CC = 0V; V I or V O =0V to 4.5V -0.1±100µA I HOLDbus hold current data inputsV CC = 3V; V I = 0.8V 75130-µA V CC = 3V; V I = 2.0V −75−140-µA V CC = 3.6 V; V I = 0V to 3.6 V[9]±500--µA I EX external current into output output HIGH-state when V O >V CC ;V O =5.5V; V CC =3.0 V -10125µA I PU power-up 3-state output currentV CC ≤ 1.2V; V O =0.5V to V CC ;V I =GND or V CC[10]-1±100µA I PD power-down 3-state output currentV CC ≤ 1.2V; V O =0.5V to V CC ;V I =GND or V CC[10]-1±100µAI OZ3-state output currentV CC = 3.6 V; V I = V IL or V IH output HIGH state; V O = 3.0 V -0.55µA output LOW-state; V O = 0.5 V-+0.5−5µA I CCquiescent supply currentV CC = 3.6 V; V I = GND or V CC ; I O = 0A outputs HIGH-state -0.060.1mA outputs LOW-state - 3.9 5.5mA outputs disabled[6]-0.060.1mA ∆I CC additional quiescent supply current per input pin V CC = 3 V to 3.6 V; one input atV CC −0.6V , other inputs at V CC or GND [7]-0.040.4mA C I input capacitance V I = 0 V or V CC -3-pF C Ooutput capacitanceV I/O = 0 V or 3.0V-9-pFTable 7:Static characteristics …continuedAt recommended operating conditions; voltages are referenced to GND (ground =0V); T amb =−40°C to +85°C.Symbol Parameter ConditionsMin Typ Max Unit[10]This parameter is valid for any V CC between0V and1.2V with a transition time of up to10ms.From V CC=1.2V to V CC=3.3V±0.3Va transition time of 100µs is permitted. This parameter is valid for T amb=25°C only.11.Dynamic characteristicsTable 8:Dynamic characteristicsVoltages are referenced to GND (ground=0V); for test circuit see Figure10;T amb=−40°C to+85°C.Symbol Parameter Conditions Min Typ Max UnitV CC = 2.5 V± 0.2 V[1]f max maximum clock frequency see Figure5150--MHzt PLH propagation delay nCP to nQx see Figure5 1.5 2.9 4.5nst PHL HIGH-to-LOW propagation delaynCP to nQx see Figure5 1.4 2.7 4.2nsnMR to nQx see Figure7 1.5 2.7 4.2ns t PZH output enable time to HIGH-level see Figure8 2.1 3.4 5.0nst PZL output enable time to LOW-level see Figure9 1.8 3.0 4.7nst PHZ output disable time from HIGH-level see Figure8 1.7 3.0 4.3nst PLZ output disable time from LOW-level see Figure9 1.4 2.3 3.3nst su(H)set-up time HIGHnDx to nCP see Figure6 1.00.5-nsnCE to nCP see Figure6 1.00.2-ns t su(L)set-up time LOWnDx to nCP see Figure6 1.8 1.3-nsnCE to nCP see Figure6+0.5−0.1-ns t h(H)hold time HIGHnDx to nCP see Figure6+0.1−1.4-nsnCE to nCP see Figure6 1.00.2-ns t h(L)hold time LOWnDx to nCP see Figure6+0.1−0.5-nsnCE to nCP see Figure6+1.0−0.1-ns t WH pulse width HIGH nCP see Figure5 2.00.8-nst WL pulse width LOWnCP see Figure5 3.0 2.1-nsnMR see Figure7 2.00.8-ns t rec recovery time nMR to nCP see Figure7 2.0 1.3-nsV CC = 3.3 V± 0.3 V[2]f max maximum clock frequency see Figure5250--MHzt PLH propagation delay nCP to nQx see Figure5 1.0 2.3 3.1nst PHL HIGH-to-LOW propagation delaynCP to nQx see Figure5 1.0 2.1 2.9nsnMR to nQx see Figure7 1.0 2.3 2.9ns t PZH output enable time to HIGH-level see Figure8 1.7 2.7 4.0nst PZL output enable time to LOW-level see Figure9 1.4 2.3 3.5ns[1]All typical values are measured at V CC = 2.5V and T amb = 25°C.[2]All typical values are measured at V CC = 3.3V and T amb = 25°C.12.Waveformst PHZ output disable time from HIGH-level see Figure 8 2.2 3.1 4.0ns t PLZ output disable time from LOW-level see Figure 9 1.8 2.6 3.5ns t su(H)set-up time HIGH nDx to nCP see Figure 6 1.00.5-ns nCE to nCPsee Figure 6 1.00.1-ns t su(L)set-up time LOW nDx to nCP see Figure 6 1.6 1.1-ns nCE to nCPsee Figure 6+0.5−0.5-ns t h(H)hold time HIGH nDx to nCP see Figure 6+0.1−0.7-ns nCE to nCPsee Figure 6 1.00.5-ns t h(L)hold time LOW nDx to nCP see Figure 6+0.1−0.5-ns nCE to nCPsee Figure 6+1.0−0.1-ns t WH pulse width HIGH nCP see Figure 5 1.50.7-ns t WLpulse width LOW nCP see Figure 5 2.5 1.4-ns nMRsee Figure 7 2.0 1.5-ns t recrecovery time nMR to nCPsee Figure 72.01.1-nsTable 8:Dynamic characteristics …continuedVoltages are referenced to GND (ground =0V); for test circuit see Figure 10;T amb =−40°C to +85°C.Symbol Parameter ConditionsMin Typ Max Unit Measurement points are given in Table 9.V OH is a typical voltage output drop that occur with the output load.Fig 5.Propagation delay, clock input to output, clock pulse width and maximum clockfrequencyV M V MV Mt PLHt PHLt WH t WL1/f maxV Minput nCPoutput nQx0 VV I0 VV OH001aad399Measurement points are given in Table 9.The shaded areas indicate when the input is permitted to change for predictable output performance.Fig 6.Data set-up and hold timesMeasurement points are given in Table 9.V OH is a typical voltage output drop that occur with the output load.Fig 7.Master reset pulse width, master reset to output delay and master reset to clockrecovery timeMeasurement points are given in Table 9.V OH is a typical voltage output drop that occur with the output load.Fig 8.3-state output enable time to HIGH-level and output disable time from HIGH-level001aad401V M input nDx,nCEinput nCPV M V M V MV MV M t su(H)t h(H)t su(L)t h(L)0 V0 VV IV Iinput nMRinput nCPoutput nQxt PHLt WLt RECV M0 VV OH0 V0 VV M V MV M001aad400V IV I001aad402V M V YV Mt PHZt PZHV MV OH0 V0 Vinput nOEoutput nQxV IMeasurement points are given in Table 9.V OL is a typical voltage output drop that occur with the output load.Fig 9.3-state output enable time to LOW-level and output disable time from LOW-level Table 9:Measurement pointsSupply voltageInput Output V MV M V XV Y≥3 V 1.5 V 1.5 V V OL + 0.3V V OH − 0.3 V ≤2.7 V0.5× V CC0.5×V CCV OL + 0.3VV OH − 0.3 V001aad404input nOEV M V MV Xt PLZt PZLoutput nQxV M0 VV OLV IV IMeasurement points are given in Table9.a.Input pulse definitionTest data is given in T able10.Definitions test circuit:R L = Load resistor.C L = Load capacitance including jig and probe capacitance.R T = Termination resistance should be equal to output impedance Z o of the pulse generator.V EXT = Test voltage for switching times.b.T est circuitFig 10.Load circuitry for switching timesTable 10:Test dataInput Load V EXTV I f i t W t r, t f C L R L t PLZ, t PZL t PLH, t PHL t PHZ,t PZH3.0 V or V CC whichever is less ≤ 10 MHz500 ns≤ 2.5 ns50 pF500Ω 6 V or2× V CCopen GND001aac221V M V Mt Wt W10 %90 %90 %0 VV IV Inegativepulsepositivepulse0 VV M V M90 %10 %10 %t THL(t f)t TLH(t r)t TLH(t r)t THL(t f)V EXTV CCV I V Omna616DUTC LR TR LR LPULSEGENERATOR13.Package outlineFig 11.Package outline SOT371-1 (SSOP56)UNIT A 1A 2A 3b p c D (1)E (1)e H E L L p Q Z y w v θ REFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IECJEDEC JEITAmm0.40.22.352.200.250.30.20.220.1318.5518.307.67.40.63510.410.11.00.61.21.00.850.4080oo 0.180.251.40.1DIMENSIONS (mm are the original dimensions)Note1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.SOT371-199-12-2703-02-18(1)w Mb pD H EE Z ecv M AXAy5629MO-118281θAA 1A 2L pQdetail XL(A )3pin 1 index0510 mmscaleSSOP56: plastic shrink small outline package; 56 leads; body width 7.5 mmSOT371-1Amax.2.8Fig 12.Package outline SOT364-1 (TSSOP56)UNIT A 1A 2A 3b p c D (1)E (2)e H E L L p Q Z y w v θ REFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IECJEDEC JEITAmm0.150.0580oo 0.1DIMENSIONS (mm are the original dimensions).Notes1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.SOT364-199-12-2703-02-19w MθAA 1A 2D L p Qdetail XE ZecLX(A )30.251285629ypin 1 indexb H 1.050.850.280.170.20.114.113.96.26.00.518.37.90.500.350.50.10.080.250.80.4pEv M AATSSOP56: plastic thin shrink small outline package; 56 leads; body width 6.1 mm SOT364-1Amax.1.20 2.5 5 mmscaleMO-15314.Revision historyTable 11:Revision historyDocument ID Release date Data sheet status Change notice Doc. number Supersedes74ALVT16823_420050802Product data sheet--74ALVT16823_3 Modifications:•The format of this data sheet has been redesigned to comply with the new presentation andinformation standard of Philips Semiconductors.•Section2: modified ‘Jedec Std 17’ into ‘JESD78’•Table8: changed propagation delays.74ALVT16823_319980612Product specification-9397 750 0401674ALVT16823_2 74ALVT16823_219980612Product specification-9397 750 0401674ALVT16823 74ALVT1682319980303----15.Data sheet status[1]Please consult the most recently issued data sheet before initiating or completing a design.[2]The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL .[3]For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.16.DefinitionsShort-form specification —The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device.These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.17.DisclaimersLife support —These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductorscustomers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.Right to make changes —Philips Semiconductors reserves the right to make changes in the products - including circuits, standard cells, and/or software - described or contained herein in order to improve design and/or performance. When the product is in full production (status ‘Production’),relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes noresponsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to theseproducts,and makes no representations or warranties that these products are free from patent,copyright,or mask work right infringement,unless otherwise specified.18.TrademarksNotice —All referenced brands, product names, service names and trademarks are the property of their respective owners.19.Contact informationFor additional information, please visit: For sales office addresses, send an email to: sales.addresses@Level Data sheet status [1]Product status [2][3]DefinitionI Objective data Development This data sheet contains data from the objective specification for product development. Philips Semiconductors reserves the right to change the specification in any manner without notice.IIPreliminary dataQualificationThis data sheet contains data from the preliminary specification.Supplementary data will be published at a later date.Philips Semiconductors reserves the right to change the specification without notice,in order to improve the design and supply the best possible product.III Product data ProductionThis data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design,manufacturing and supply.Relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN).20.Contents1General description. . . . . . . . . . . . . . . . . . . . . . 12Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13Quick reference data. . . . . . . . . . . . . . . . . . . . . 24Ordering information. . . . . . . . . . . . . . . . . . . . . 25Functional diagram . . . . . . . . . . . . . . . . . . . . . . 36Pinning information. . . . . . . . . . . . . . . . . . . . . . 56.1Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56.2Pin description . . . . . . . . . . . . . . . . . . . . . . . . . 57Functional description . . . . . . . . . . . . . . . . . . . 77.1Function table. . . . . . . . . . . . . . . . . . . . . . . . . . 78Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 79Recommended operating conditions. . . . . . . . 810Static characteristics. . . . . . . . . . . . . . . . . . . . . 911Dynamic characteristics . . . . . . . . . . . . . . . . . 1112Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1213Package outline . . . . . . . . . . . . . . . . . . . . . . . . 1614Revision history. . . . . . . . . . . . . . . . . . . . . . . . 1815Data sheet status. . . . . . . . . . . . . . . . . . . . . . . 1916Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1917Disclaimers. . . . . . . . . . . . . . . . . . . . . . . . . . . . 1918Trademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . . 1919Contact information . . . . . . . . . . . . . . . . . . . . 19© Koninklijke Philips Electronics N.V.2005All rights are reserved.Reproduction in whole or in part is prohibited without the priorwritten consent of the copyright owner.The information presented in this document doesnot form part of any quotation or contract,is believed to be accurate and reliable and maybe changed without notice.No liability will be accepted by the publisher for anyconsequence of its use.Publication thereof does not convey nor imply any license underpatent- or other industrial or intellectual property rights.Date of release: 2 August 2005Document number: 74ALVT16823_4。

AV38 数字型通用控制器 说明书

上海谷雨环保科技有限公司上海谷雨环保科技有限公司 谷雨销售部:021-51078654021-27087986F:021-********E-Mail:***************AV38数字型通用控制器数字型通用控制器AV38是DataStick TM 数字化传感器系统通用的操作平台,可自动识别传感器,并提供校准、配置、诊断的功能。

特点特点::·可同时连接多达247只Datastick 传感器(任意组合) ·增加Datastick 传感器时无需增加输入模块 ·支持多种通讯协议·连接Datastick 传感器,可“即插即用”,无需初始化系统 ·盘装或壁挂式安装此外还有以下此外还有以下特点特点特点::·高对比度背光灯的LCD 显示 ·安装尺寸:1/4-DIN 或1/2-DIN ·防护等级:NEMA 4X ·电源:24VDC 或 100-240VAC·最多2路电流输出 ,最多2路继电器输出·可选多种数字通讯:Modbus;DeviceNet;EtherNet;RS-232/ RS-485;DF1;Profibus DP 等。

AquaClear 低量程浊度仪低量程浊度仪((数字化数字化))该浊度仪符合或超过USEPA180.1标准,其独特的流通池能有效的去除水样中的气泡,消除低量程测量中最主要的干扰,且系统容易校准、清洁和维修。

特点特点::.符合USEPA180.1规范 .稳定高效的气泡去除系统 .结构紧凑,占用空间小 .光源质保2年.流通池135mL—时滞小,灵敏度高 .温度测量.即插即用的通讯适配器技术参数技术参数:: ..清洗维护简单量程量程 0~200 NTU 分辨率分辨率0.001 NTU精度精度 读数的2%(小于40NTU);读数的5%(大于40NTU)响应时间响应时间 90秒达到90% 测量系统测量系统测量单位测量单位 浊度:NTU 温度:℃水体温度水体温度 -5℃~50℃ 流速范围流速范围250mL/min~750mL/min空气温度空气温度 -20℃~60℃进出口尺寸进出口尺寸 3/8”ID 的软管 或 1/4”NPT 的硬管运行环境运行环境安装尺寸安装尺寸300×300 mm 光源光源//光室光室 钨灯,阳极氧化铝 结构结构传感器材质传感器材质石英,阳极氧化铝。

电磁换向阀SV38-38中文.pdf

⩡ⷭ䬬䔜䟄箫洀┷ 痒 抩 ♛⚠硰㷱 稛☚绬先㙡遙梏 䞷ℝ尐㻑苀秼䆞䤓微戌≬虚ㄣ䞷҈ ⤲蛦䟄㢅 SV38-38 硰㷱㽈稛⅝ 税⚠ 㒥⅝ 税⚠ 抩䟄㢅 硰㷱㽈稛⅝ 税⚠ 㒥⅝ 税⚠➥◥欬着䟄箫兎皽釭⚗扭兼ぴ⇫梏矒兞䫻德⮓䚕 功䞷₣苀秼䆞 ♾折兎皽䟄☚✛兗簖 舊磧䄎㆞嫣材兢㨓 㙡ↅ䟄☚♾疸㗱♾折 ,3 . 腋㻃 ( ⨚兎皽 㠃⇢㲰枇⨚兎皽幍帰ぴ₩抩䞷梏ⷣ➥҈ 喝 EDU SVL ≭䛻喝莋屐㊶賍⦍䘔⇰喝⦷ EDU SVL 㢅 秧◖ ⒕朮 穚 ⒕朮 ⍕ 㠯 喝 綍 㪖瘮ₐ受蟇厅蓒⺐㏫ ䷉ 䉋䒩喝♾⦷ 綍 䤓欬着䟄☚喒⦃茫扭兼ぴ⇫20č ⮰㏫ ⩡≭喝㪖瘮兎皽 9'& 㢅 眸 9$& ⏷㽱㠃税 㢅 眸 ( ⨚兎皽 9'& 㢅 眸 9'& 㢅 眸 ⩡ 喝 EDU SVL 㢅欬着⋋䤓 䓳␐喝莋屐Ϸ䉔喝伧矑⅚ℝ F6W VVX 䤓䪎䓸㽈㒥牑㦘䀵袛⇫䞷䤓⚗㒟㽈 㷱喝蠼㦘腏Ⓟ 莋屐 䬬 喝9& 莋屐䬬 喝&7 ;; 莋屐 ㏰Т 喝6. ; 00 莋屐㏫ 㳦喝肺ↅ莓 ⺈ℝ 㦗 㡴ⓜ䞮ℶ䤓 ( ⨚兎皽 庆莋屐簛 欄䤓兎皽绬租痥㋾げUSASI/ISO:㘩 ⅔㖖㙡ↅ1.390.111.0/1608.3/1205.5/802.8/403.8113.8/2007.6211.4340°C 时 32 cSt/150 ssu 的油液流量 (lpm/gpm)压降 (b a r /p s i )207/3000138/200069/10003.81流量 (lpm/gpm)压力 (b a r /p s i )7.6211.43性能范围阴影:① 为进油口,② 为负载油口,③ 为油箱油口阴影:选择阀进油口阴影线:③ 为进油口,② 为负载油口,1.390.2䃎䉙Т喝摜摞 ◒⏚ 箬朱Ⓟ ぴ⇫槱兞䫻德⮓䚕 盶缂槱柏枛 ₐ受蟇厅 2 ⨚皽✛貆㺷鉽㖰皽 㪖瘮⨚ 䬬 喝摜摞 ◒⏚箬 棂㨐㺶荩舊薦矑杬⚗摠 珩莓 7 欬着☚┪才 EDU SVL 莋屐 㙟∪䚒犐枇材✛朱Ⓟ梏⧦ ⻉⺇♾賍㦘硵ₜ⚛ 庆莧幱ぴ☑㏫ 喝摜摞 ◒⏚箬 兮䍼⫠⺐遙 + 儶功舊䂸䆕癕兎 莋屐E ㏫ 喝摜摞 ◒⏚箬 ⧩⦉摠⻭盶⮂⏷⺐遙 䶵⚗ ,3 . 腋㔳㪖瘮 揜㦘鍻㒟扭碟犀 ∔喝 E ㏫ ⮰ ⩔喏䄣 㻭 3.400.1SV38-38__ - __ __ __ - __ - __ __ __ __ __ₐ受㳰厅 㪖⨚ N 㺮㳰厅 V䬬 ⇥ ♹帱徼㙡遙ↅ 0 6$( 6T 喀⺇ %63 2B%63 梏⧦⅔棟喀⦌Ⓟ抯䔵Т㡯䴉䤌1.8446.7英寸毫米最大安装线圈时,字母必须朝上㏫ ㏴〛 (VDC) DS ♛㓐ㇱ㘴⯃ DG ',1 DL ⺋兎D L/W ⺋兎 サ :HDWKHUSDN ®扭㘴⣷DR 'HXWVFK '7 3 ㏫ ㏴〛 (VAC) AG ',1 AP 喀⺇⺋兎丰 E ㏫ ㏴〛 (VDC) ER 'HXWVFK '7 3 䶵⚗ ,3 . 㪖EY 0HWUL 3DFN ®䶵⚗ ,3 . 㪖㙟∪サ␔函ℛ㨐丰䤓兎⦗ 庆✷幱ぴ☑㪖兎⦗䟄☚ 0 㡯兎⦗10 9'&†12 9'& 24 9'& 36 9'& 48 9'& 24 9$& 115 9$&230 9$&▔㕻㪖兎⦗婉㹜†⅔棟 '6 ': 㒥 '/ 兗䵾E ㏫10 9'& 12 9'& 20 9'& 24 9'&。

AVS08中文资料