IC datasheet pdf-UA9637A,pdf(Dual Differential Line Receiver)

IC datasheet pdf-ADS7846,pdf(Touch-Screen Controller)

"

"

"

"

"

"

NOTE: (1) For the most current package and ordering information, see the Package Option Addendum located at the end of this data sheet, or see the TI web site at .

US Patent No. 6246394 QSPI and SPI are registered trademarks of Motorola.

+VCC

X+ X–

Temperature Sensor

SAR

Y+ Y–

ADS7846

DOUT BUSY

Comparator 6-Channel MUX CDAC Serial Data Out CS

ADS7846

ADS 7846

AD S784 6

®

AD

S784

6

SBAS125H – SEPTEMBER 1999 – REVISED JANUARY 2005

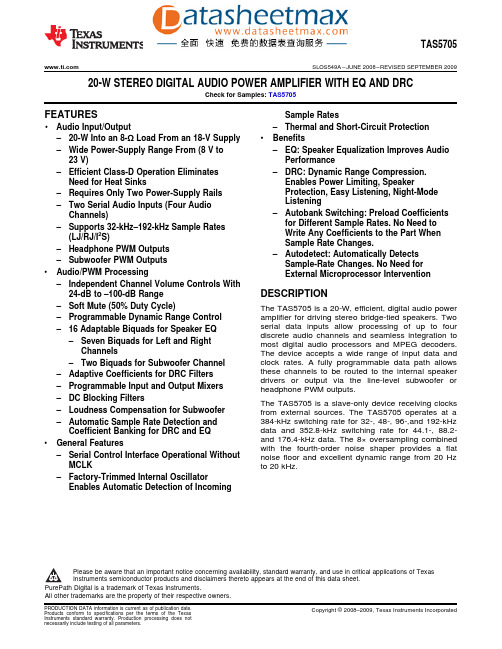

TOUCH SCREEN CONTROLLER

FEATURES

q SAME PATION q INTERNAL 2.5V REFERENCE q q q q DIRECT BATTERY MEASUREMENT (0V to 6V) ON-CHIP TEMPERATURE MEASUREMENT TOUCH-PRESSURE MEASUREMENT QSPITM/SPITM 3-WIRE INTERFACE

PENIRQ

A3150光耦DataSheet

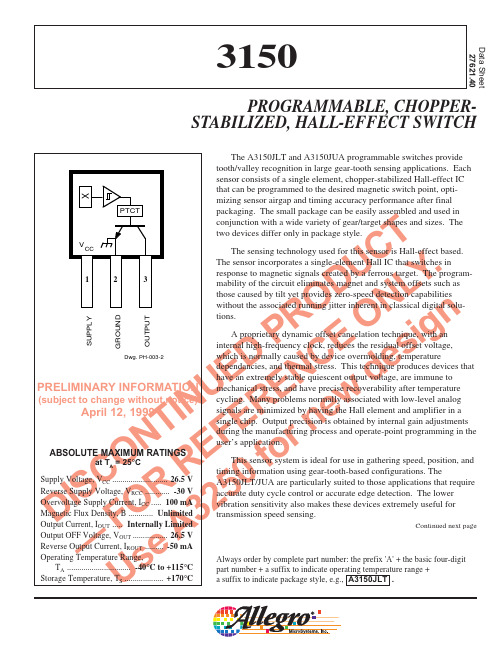

U E D P R O D U C T E F E R E N C E O N L Y .U250 f o r n e w d e s i g n Data Sheet 27621.40The A3150JLT and A3150JUA programmable switches provide tooth/valley recognition in large gear-tooth sensing applications. Each sensor consists of a single element, chopper-stabilized Hall-effect IC that can be programmed to the desired magnetic switch point, opti-mizing sensor airgap and timing accuracy performance after final packaging. The small package can be easily assembled and used in conjunction with a wide variety of gear/target shapes and sizes. The two devices differ only in package style.The sensing technology used for this sensor is Hall-effect based.The sensor incorporates a single-element Hall IC that switches inresponse to magnetic signals created by a ferrous target. The program-mability of the circuit eliminates magnet and system offsets such as those caused by tilt yet provides zero-speed detection capabilities without the associated running jitter inherent in classical digital solu-tions.A proprietary dynamic offset cancelation technique, with an internal high-frequency clock, reduces the residual offset voltage,which is normally caused by device overmolding, temperaturedependancies, and thermal stress. This technique produces devices that have an extremely stable quiescent output voltage, are immune to mechanical stress, and have precise recoverability after temperature cycling. Many problems normally associated with low-level analog signals are minimized by having the Hall element and amplifier in a single chip. Output precision is obtained by internal gain adjustments during the manufacturing process and operate-point programming in the user’s application.This sensor system is ideal for use in gathering speed, position, and timing information using gear-tooth-based configurations. TheA3150JLT/JUA are particularly suited to those applications that require accurate duty cycle control or accurate edge detection. The lower vibration sensitivity also makes these devices extremely useful for transmission speed sensing.3150Always order by complete part number: the prefix 'A' + the basic four-digit part number + a suffix to indicate operating temperature range +a suffix to indicate package style, e.g., A3150JLT .PROGRAMMABLE, CHOPPER-STABILIZED, HALL-EFFECT SWITCHContinued next page115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-********PROGRAMMABLE, CHOPPER-STABILIZED, PRECISION,HALL-EFFECT SWITCHCopyright © 2000, Allegro MicroSystems, Inc.Two package styles provide a magnetically opti-mized package for most applications. Suffix ‘–LT’ is a miniature SOT-89/TO-243AA transistor package for surface-mount applications; while suffix ‘–UA’ is a three-lead ultra-mini-SIP for through-hole mounting.FEATURES AND BENEFITSs Chopper Stabilized forExtremely Low Switch-Point Drift and Immunity to Mechanical Stresss Externally Programmed Switch Point s On-Chip Supply-Transient Protection s Output Short-Circuit Protections Single-Chip Sensing IC for High Reliability s Small Mechanical Size s <50µs Power-On Times Wide Operating Voltage Range s Defined Power-On State3150PROGRAMMABLE, CHOPPER-STABILIZED, PRECISION,HALL-EFFECT SWITCHLimitsCharacteristic Symbol Test ConditionsMin.Typ.Max.Units Operate PointB OPProgrammable offset range 500670850G Initial (before programming)02040G Resolution8.01114G ∆B OPV CC = 14 V, after programming, B OP ≈ 500 G-358.0+35G HysteresisB hys5.02035GNOTE: Typical data is at V CC = 5 V and T A = +25°C and is for design information only.ELECTRICAL CHARACTERISTICS over operating voltage and temperature range (unless otherwise noted).LimitsCharacteristic Symbol Test Conditions Min.Typ.Max.Units Supply Voltage V CC Operating, T J < 165°C4.25–26V Power-On State POS After programming, V CC = 0 ¡ 5 V HIGH HIGH HIGH –Low Output Voltage V OUT(SAT)I OUT = 20 mA –175400mV Output Current Limit I OUTM V OUT = 12 V 658095mA Output Leakage Current I OFF V OUT = 24 V–0.210µA Supply CurrentI CCBefore programming, output OFF – 4.07.0mA Before programming, output ON– 5.08.0mA Reverse Supply Current I RCC V RCC = -30 V ––-5.0mA Power-On Delay t on V CC > 5 V–2050µs Output Rise Time t r R L = 820 Ω, C L = 20 pF –200–ns Output Fall Time t f R L = 820 Ω, C L = 20 pF–100–ns Clock Frequency f C –340–kHz Zener Voltage V Z I ZT = 100 µA, T A = 25°C 2732–V Zener Impedancez zI ZT = 10 mA, T A = 25°C –50100ΩNOTE: Typical data is at V CC = 5 V and T A = +25°C and is for design information only.MAGNETIC CHARACTERISTICS over operating supply voltage and temperature ranges.115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-50003150PROGRAMMABLE, CHOPPER-STABILIZED, PRECISION,HALL-EFFECT SWITCHTYPICAL ELECTRICAL CHARACTERISTICS255075100AMBIENT TEMPERATURE IN °C-50Dwg. GH-053-2125-25S U P P L Y C U R R E N T I N m A5.04.03.02.01.015010152025SUPPLY VOLTAGE IN VOLTSDwg. GH-041-25S U P P L Y C U R R E N T I N m A10300AMBIENT TEMPERATURE IN °C200Dwg. GH-040-4S A T U R A T I O N V O L T A G E I N m V3150PROGRAMMABLE, CHOPPER-STABILIZED, PRECISION,HALL-EFFECT SWITCHFUNCTIONAL DESCRIPTIONChopper-Stabilized Technique. These devices use a proprietary dynamic offset cancellation technique, with an internal high-frequency clock to reduce the residual offset voltage of the Hall element that is normally caused by device overmolding, temperature dependencies, and thermal stress.This technique produces devices that have an extremely stable quiescent Hall output voltage, are immune to thermal stress, and have precise recoverability after temperature cycling. Thistechnique will also slightly degrade the device output repeatabil-ity.The Hall element can be considered as a resistor arraysimilar to a Wheatstone bridge. A large portion of the offset is a result of the mismatching of these resistors. The chopper-stabilizing technique cancels the mismatching of the resistors by changing the direction of the current flowing through the Hall plate and Hall voltage measurement taps, while maintaining the Hall-voltage signal that is induced by the external magnetic flux.The signal is, then, captured by a sample-and-hold circuit.Operation. The output of these devices switches low (turns ON) when a magnetic field (south pole) perpendicular to the Hall sensor exceeds the operate point threshold (B OP ). After turn-ON, the output is capable of sinking 25 mA and the output voltage is V OUT(SAT). When the magnetic field is reduced below the release point (B RP ), the device output goes high (turns OFF).The difference in the magnetic operate and release points is the hysteresis (B hys ) of the device. This built-in hysteresis allows clean switching of the output even in the presence of external mechanical vibration and electrical noise.Applications. It is strongly recommended that an external bypass capacitor be connected (in close proximity to the Hall sensor) between the supply and ground of the device to reduce both external noise and noise generated by the chopper-stabiliza-tion technique.The simplest form of magnet that will operate these devices is a bar magnet with the south-seeking pole towards the branded surface of the device. Many other methods of operation are possible. Extensive applications information on magnets and Hall-effect sensors is also available in the Allegro Electronic Data Book AMS-702 or Application Note 27701, orO U T P U T V O L T A G EFLUX DENSITYDwg. GH-007-2115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-50003150PROGRAMMABLE, CHOPPER-STABILIZED, PRECISION,HALL-EFFECT SWITCHPROGRAMMING PROTOCOLThe A3150JLT and A3150JUA operate points are pro-grammed by serially addressing the device through the supply terminal (pin1). After the correct operate point is determined, the device programming bits are selected and then a “lock” set to prevent any further (accidental)programming.Program Enable. To program the device, a sequence of pulses is used to activate/enable the addressing mode as shown in figure 1. This sequence of a V PP pulse, at least seven V PH pulses, and a V PP pulse with no supply interrup-tions, is designed to prevent the device from being pro-grammed accidentally (for example, as a result of noise on the supply line).VV V Dwg. WH-013Figure 1 — Program enablePROGRAMMING PROTOCOL over operating temperature range.LimitsCharacteristic Symbol DescriptionMin.Typ.Max.Units Programming VoltageV PL Minimum voltage during programming4.55.0 5.5V V PH 9.01011V V PP202325V Programming Current I PP Max. supply current during programming –250–mA Pulse Widtht d(0)OFF time between bits20––µs t d(1)Enable, address, program, or lock bit ON time 20––µs t dPProgram pulse ON time 100300–µs Pulse Rise Time t r V PL to V PH or V PP 11––µs Pulse Fall Timet fV PH or V PP to V PL 5.0––µsNOTE: Typical data is at T A = +25°C and is for design information only.3150PROGRAMMABLE, CHOPPER-STABILIZED, PRECISION,HALL-EFFECT SWITCH* In application, the terms “gear” and “target” are often interchanged. However, “gear” is preferred when motion is transferred.Address Determination. The operate point is adjust-able in 64 increments. With the appropriate target or gear*in position, the 64 switch points are sequentially selected (figure 2) until the required operate point is reached. Note that the difference between the operate point and the release point (hysteresis) is a constant for all addresses.Set-Point Programming. After the desired set-point address is determined (0 through 63), each bit of theequivalent binary address is programmed individually. For example, as illustrated in figure 3, to program address code 5 (binary 000101), bits 1 and 3 need to be programmed.Each bit is programmed during the wide V PP pulse and is not reversible.Lock Programming. After the desired set point is programmed, the program lock is then activated (figure 4)to prevent further programming of the device.V PV 0Dwg. WH-014A D D R E S S 0A D D R E S S 1A D D R E S S 2A D D R E S S N (UP T O 63)A D D R E S S N -1A D D R E S S N -2Figure 2 — Address determinationFigure 4 — Lock programmingV V VDwg. WH-016Figure 3 — Set-point programmingV V V Dwg. WH-015A115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-50003150PROGRAMMABLE, CHOPPER-STABILIZED, PRECISION,HALL-EFFECT SWITCHAll Allegro sensors are subjected to stringent qualification requirements prior to being released to production.To become qualified, except for the destructive ESD tests, no failures are permitted.CRITERIA FOR DEVICE QUALIFICATIONQualification Test Test Method and Test Conditions Test Length SamplesComments Biased Humidity (HAST)T A = 130°C, RH = 85%50 hrs 77V CC = V OUT = 5 V High-Temperature JESD22-A108,408 hrs77V CC = 24 V,Operating Life (HTOL)T A = 150°C, T J = 165°C V OUT = 20 V Accelerated HTOLJESD22-A108,504 hrs 77V CC = 24 V,T A = 175°C, T J = 190°C V OUT = 20 VAutoclave, Unbiased JESD22-A102, Condition C,96 hrs 77T A = 121°C, 15 psig High-Temperature MIL-STD-883, Method 1008,1000 hrs 77(Bake) Storage Life T A = 170°CTemperature CycleMIL-STD-883, Method 1010,500 cycles 77-65°C to +150°C Latch-Up—Pre/Post 6Reading Electro-Thermally—Pre/Post 6Induced Gate Leakage Reading ESD,CDF-AEC-Q100-002Pre/Post x per Test to failure,Human Body Model Reading test All leads > TBDElectrical DistributionsPer Specification—303150PROGRAMMABLE, CHOPPER-STABILIZED, PRECISION,HALL-EFFECT SWITCHSENSOR LOCATIONS(±0.005” [0.13 mm] die placement)Package Designators “UA” and "UA-TL"Although sensor location is accurate to three sigma for a particular design, product improvements may result in small changes to sensor location.Dwg. MH-008-80.030"0.76 mm NOMDwg. MH-011-9APackage Designator “LT”115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-50003150PROGRAMMABLE, CHOPPER-STABILIZED, PRECISION,HALL-EFFECT SWITCH0.440.35PACKAGE DESIGNATOR 'LT'(SOT-89/TO-243AA)Dimensions in Inches (for reference only)Dimensions in Millimeters (controlling dimensions)Dwg. MA-012-3 mmPads 1, 2, 3, and B — Low-Stress VersionPads 1, 2, and 3 only — Lowest Stress, But Not Self AligningNOTE: Exact body and lead configuration at vendor’s option within limits shown.Dwg. MA-012-3 inads 1, 2, 3, and B — Low-Stress Versionads 1, 2, and 3 only — Lowest Stress, But Not Self Aligning3150 PROGRAMMABLE, CHOPPER-STABILIZED, PRECISION,HALL-EFFECT SWITCH Surface-Mount Lead Form (Suffix '-TL')Dimensions in Inches (controlling dimensions)Dimensions in Millimeters (for reference only)PACKAGE DESIGNATOR 'UA'Dwg. MH-014E mm1.27BSC°Dwg. MH-014E inBSC°NOTES: 1.Tolerances on package height and width represent allowable mold offsets. Dimensions given are measured at the widest point (parting line).2.Exact body and lead configuration at vendor’s option within limits shown.3.Height does not include mold gate flash.4.Recommended minimum PWB hole diameter to clear transition area is 0.035” (0.89 mm).5.Where no tolerance is specified, dimension is nominal.115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-50003150PROGRAMMABLE, CHOPPER-STABILIZED, PRECISION,HALL-EFFECT SWITCHThe products described herein are manufactured under one or more of the following U.S. patents: 5,045,920; 5,264,783; 5,442,283;5,389,889; 5,581,179; 5,517,112; 5,619,137; 5,621,319; 5,650,719;5,686,894; 5,694,038; 5,729,130; 5,917,320; and other patents pending.Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, ormanufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.Allegro products are not authorized for use as critical components in life-support appliances, devices, or systems without express written approval.The information included herein is believed to be accurate andreliable. However, Allegro MicroSystems, Inc. assumes no responsibil-ity for its use; nor for any infringements of patents or other rights of third parties that may result from its use.。

AAT 器件选型指南.pdf说明书

Part No.

Amplifiers Include

Vcc (V)

Icc

Ptot

(mA) (mW)

Toper Vio Iio (℃) (mV) (nA)

PKG

Replace Brand

LM358 LM393 LM324 LM339

2

16~32 50

500

0~70

2

2

SOP-8/DIP-8

2

2~36 0.4

128*8 256*8 512*8 1028*8 2056*8 5012*8 10024*8

Frequency Icc

Isb

(KHz)

(mA) (µA)

PKG

Replace Brand

Application

400

0.4~3 0.6~18 SOP-8/DIP-8 ATMEL/ISSI/ST/ROHM

400

400

0.4~3 0.6~18 SOP-8/DIP-8 ATMEL/ISSI/ST/ROHM

400

0.4~3 0.6~18 SOP-8/DIP-8 ATMEL/ISSI/ST/ROHM

400

0.4~3 0.6~18 SOP-8/DIP-8 ATMEL/ISSI/ST/ROHM

■ AAT General Line-up

I2-PAK

TO-220AB

TO-220IS

AAT PRODUCTS FOR CUSTOMERS

General Freque

Vcc

Device

ncy

Name

(KHz)

(V)

Vout (V)

Io (A)

7805

---

5~18

IC datasheet pdf-MAXQ1010,pdf (Security Token Microcontroller)

_______________________________________________________________ Maxim Integrated Products 1For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim’s website at .MAXQ1010Security Token Microcontroller with RTC and USBNote: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, go to: /errata .19-5259; Rev 0; 4/10Ordering Information continued on last page.+Denotes a lead(Pb)-free/RoHS-compliant package.*Contact factory for availability.**EP = Exposed pad.Selector Guide appears at end of data sheet.General Description The MAXQ1010 is a small, low-cost, low-power securemicrocontroller designed for security token applicationsand battery-powered applications where power andsecurity are both critically important.The microcontroller family contains a 32KB, 64KB, or128KB programmable flash memory that can be usedfor both application code and data storage. Each 512Bflash memory page supports 20,000 erase cycles and is programmable 16 bits at a time. This allows for uniqueschemes to extend the lifetime of the flash. For instance, dedicating four flash pages to store 32B of data that changes very often, the effective number of write cycles can approach 1.2 million (4 x 512 x 20,000/32). The device also contains 1KB or 2KB SRAM. An additional 128B secure key storage SRAM is instantly erased when a self-destruct input is triggered.The microcontroller also contains a hardware DES engi-ne and an AES accelerator, allowing applications to quickly respond to challenges and authenticate other devices using standards-based cryptography. A true-hardware random-number generator (RNG) is available for general application use, such as key generation, challenge generation, and random padding. Firmware and reference designs are available from Maxim for authentication applications.Multiple communication interfaces are implemented; an integrated USB transceiver and serial interface engine make USB applications extremely low cost. Other com-munication options include ISO 7816 UART, SPI K , I 2C, and a standard USART (universal synchronous/asynchro-nous receiver-transmitter). A real-time clock (RTC) is also included for security applications requiring a time base.For the ultimate in low-power battery-operated perfor-mance, an ultra-low-power stop mode (400nA typ) is included. In this mode, the minimum amount of circuitry is powered. Wake-up sources include external interrupts, the power-fail interrupt, a wake-up timer interrupt, and an RTC interrupt.Applications One-Time Password Generator USB Card Readers Features S High-Performance, Low-Power, 16-Bit RISC Core S DC to 12MHz Operation Across Entire Operating Range S 6MHz Internal Oscillator S 12MHz External Crystal (Required for USB Operation)S 1.7V to 3.6V Operating Voltage Range S 33 Total Instructions for Simplified Programming S Three Independent Data Pointers Accelerate Data Movement with Automatic Increment/Decrement S Dedicated Pointer for Direct Read from Code Space S 16-Bit Instruction Word, 16-Bit Data BusS 16 x 16-Bit General-Purpose Working Registers S 1-Wire ® Interface for Debugger and Flash Programming S Security FeaturesDES and AES Hardware AcceleratorsHardware True RNGSelf-Destruct Input Pin128B, Fast Wipe, Secure Secret Key SRAM RTC with Integrated OscillatorS Memory32/64/128KB Flash512-Byte Memory Page Sectors20,000 Erase/Write Cycles per SectorUp to 2KB Data SRAM6KB Utility ROM with User-Callable Routines S I/O and PeripheralsUSB 2.0 SIE and TransceiverSPI and USART I 2C Communication Ports ISO 7816 UART31 General-Purpose I/O PinsUp to 15 External Interrupts AvailableS Low Power ConsumptionSingle 1.7V to 3.6V Supply< 1µA Current in Lowest Power Stop ModeDivided System Clock Modes AvailableS Additional PeripheralsPower-Fail WarningPower-On Reset (POR)Programmable Watchdog TimerOrdering Information MAXQ and 1-Wire are registered trademarks of Maxim Integrated Products, Inc.SPI is a trademark of Motorola, Inc.PART TEMP RANGE PIN-PACKAGEMAXQ1010-A01+-40°C to +85°C 48 TQFN-EP**MAXQ1010X-0000+*-40°C to +85°C Bare dieMAXQ1010Security Token Microcontrollerwith RTC and USB 15 Block Diagram Note to readers: This document is an abridged version of the full data sheet. To request the full data sheet, go to /MAXQ1010 and click on Request Full Data Sheet .。

IC datasheet pdf-LT1013AM,pdf(DUAL PRECISION OPERATIONAL AMPLIFIERS)

LT1013, DUAL PRECISION OPERATIONALLT1013, LT1013A, LT1013D DUAL PRECISION OPERATIONAL AMPLIFIERSLT1013, LT1013A, LT1013D DUAL PRECISION OPERATIONAL AMPLIFIERSLT1013, LT1013A, LT1013D DUAL PRECISION OPERATIONAL AMPLIFIERSLT1013, LT1013A, LT1013D DUAL PRECISION OPERATIONAL AMPLIFIERSLT1013, DUAL PRECISION OPERATIONALLT1013, DUAL PRECISION OPERATIONALPACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)5962-88760012A ACTIVE LCCC FK201TBD POST-PLATE N/A for Pkg Type 5962-8876001PA ACTIVE CDIP JG81TBD A42N/A for Pkg Type 5962-88760022A ACTIVE LCCC FK201TBD POST-PLATE N/A for Pkg Type 5962-8876002PA ACTIVE CDIP JG81TBD A42N/A for Pkg Type LT1013AMFKB ACTIVE LCCC FK201TBD POST-PLATE N/A for Pkg Type LT1013AMJG ACTIVE CDIP JG81TBD A42N/A for Pkg Type LT1013AMJGB ACTIVE CDIP JG81TBD A42N/A for Pkg Type LT1013AMP OBSOLETE PDIP P8TBD Call TI Call TILT1013CD ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLT1013CDE4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLT1013CDG4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLT1013CDR ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLT1013CDRE4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLT1013CDRG4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLT1013CP ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeLT1013CPE4ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeLT1013DD ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLT1013DDE4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLT1013DDG4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLT1013DDR ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLT1013DDRE4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLT1013DDRG4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLT1013DID ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLT1013DIDE4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLT1013DIDG4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLT1013DIDR ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLT1013DIDRE4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLT1013DIDRG4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)LT1013DIP ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeLT1013DIPE4ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg Type LT1013DMD ACTIVE SOIC D875TBD CU NIPDAU Level-1-220C-UNLIM LT1013DMDG4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMLT1013DP ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeLT1013DPE4ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg Type LT1013IP OBSOLETE PDIP P8TBD Call TI Call TILT1013MFKB ACTIVE LCCC FK201TBD POST-PLATE N/A for Pkg Type LT1013MJG ACTIVE CDIP JG81TBD A42N/A for Pkg Type LT1013MJGB ACTIVE CDIP JG81TBD A42N/A for Pkg TypeLT1013MP OBSOLETE PDIP P8TBD Call TI Call TILT1013Y OBSOLETE DIESALE Y0TBD Call TI Call TI(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS),Pb-Free(RoHS Exempt),or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free(RoHS Exempt):This component has a RoHS exemption for either1)lead-based flip-chip solder bumps used between the die and package,or2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free(RoHS compatible)as defined above.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.TAPE AND REEL INFORMATION*All dimensions are nominal Device Package Type Package DrawingPinsSPQ Reel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant LT1013CDR SOICD 82500330.012.4 6.4 5.2 2.18.012.0Q1LT1013DDR SOICD 82500330.012.4 6.4 5.2 2.18.012.0Q1LT1013DIDR SOIC D 82500330.012.4 6.4 5.2 2.18.012.0Q1*All dimensions are nominalDevice Package Type Package Drawing Pins SPQ Length(mm)Width(mm)Height(mm) LT1013CDR SOIC D8*******.5338.120.6 LT1013DDR SOIC D8*******.5338.120.6 LT1013DIDR SOIC D8*******.5338.120.6IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDLP®Products Communications and /communicationsTelecomDSP Computers and /computersPeripheralsClocks and Timers /clocks Consumer Electronics /consumer-appsInterface Energy /energyLogic Industrial /industrialPower Mgmt Medical /medicalMicrocontrollers Security /securityRFID Space,Avionics&/space-avionics-defenseDefenseRF/IF and ZigBee®Solutions /lprf Video and Imaging /videoWireless /wireless-appsMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2010,Texas Instruments Incorporated。

UA9637

PACKAGING INFORMATION Orderable DeviceStatus (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball Finish MSL Peak Temp (3)UA9637ACDACTIVE SOIC D 875Pb-Free (RoHS)CU NIPDAU Level-2-250C-1YEAR UA9637ACDRACTIVE SOIC D 82500Pb-Free (RoHS)CU NIPDAU Level-2-250C-1YEAR UA9637ACJGOBSOLETE CDIP JG 8None Call TI Call TI UA9637ACPACTIVE PDIP P 850Pb-Free (RoHS)CU NIPDAU Level-NC-NC-NC UA9637ACPSRACTIVE SO PS 82000Pb-Free (RoHS)CU NIPDAU Level-2-260C-1YEAR/Level-1-235C-UNLIM (1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -May not be currently available -please check /productcontent for the latest availability information and additional product content details.None:Not yet available Lead (Pb-Free).Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green (RoHS &no Sb/Br):TI defines "Green"to mean "Pb-Free"and in addition,uses package materials that do not contain halogens,including bromine (Br)or antimony (Sb)above 0.1%of total product weight.(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDECindustry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of thedate that it is provided.TI bases its knowledge and belief oninformation provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.PACKAGE OPTION ADDENDUM 18-Feb-2005Addendum-Page 1IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

AD9637BCPZ-40;AD9637BCPZ-80;AD9637BCPZRL7-40;AD9637BCPZRL7-80;AD9637-80EBZ;中文规格书,Datasheet资料

Octal, 12-Bit, 40/80 MSPS, Serial LVDS,1.8 V Analog-to-Digital Converter Data Sheet AD9637Rev. 0Information furnished by Analog Devices is believed to be accurate and reliable. However, noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, M A 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.FEATURESLow power: 60 mW per channel at 80 MSPS with scalable power optionsSNR = 71.5 dBFS (to Nyquist)SFDR = 92 dBc (to Nyquist)DNL = ±0.4 LSB (typical), INL = ±0.5 LSB (typical)Serial LVDS (ANSI-644, default)Low power, reduced signal option (similar to IEEE 1596.3) Data and frame clock outputs650 MHz full power analog bandwidth2 V p-p differential input voltage range1.8 V supply operationSerial port controlFull chip and individual channel power-down modes Flexible bit orientationBuilt-in and custom digital test pattern generation Programmable clock and data alignment Programmable output resolutionStandby modeAPPLICATIONSMedical imaging and nondestructive ultrasoundPortable ultrasound and digital beam-forming systems Quadrature radio receiversDiversity radio receiversOptical networkingTest equipmentGENERAL DESCRIPTIONThe AD9637 is an octal, 12-bit, 40/80 MSPS analog-to-digital converter (ADC) with an on-chip sample-and-hold circuit designed for low cost, low power, small size, and ease of use. The product operates at a conversion rate of up to 80 MSPS and is optimized for outstanding dynamic performance and low power in applications where a small package size is critical. The ADC requires a single 1.8 V power supply and LVPECL-/ CMOS-/LVDS-compatible sample rate clock for full performance operation. No external reference or driver components are required for many applications.The ADC automatically multiplies the sample rate clock for the appropriate LVDS serial data rate. A data clock output (DCO) for capturing data on the output and a frame clock output (FCO) for signaling a new output byte are provided. Individual channel power-down is supported and typically consumes less than 2 mW when all channels are disabled.The ADC contains several features designed to maximize flexibility and minimize system cost, such as programmableFUNCTIONAL BLOCK DIAGRAMDFS DTP10215-1Figure 1.clock and data alignment and programmable digital test pattern generation. The available digital test patterns include built-in deterministic and pseudorandom patterns, along with custom user-defined test patterns entered via the serial port interface (SPI). The AD9637 is available in a RoHS-compliant, 64-lead LFCSP. It is specified over the industrial temperature range of −40°C to +85°C. This product is protected by a U.S. patent.PRODUCT HIGHLIGHTS1.Small Footprint. Eight ADCs are contained in a small,space-saving package.2.Low Power of 60 mW/Channel at 80 MSPS with ScalablePower Options.3.Ease of Use. A data clock output (DCO) is provided thatoperates at frequencies of up to 480 MHz and supportsdouble data rate (DDR) operation.er Flexibility. The SPI control offers a wide range offlexible features to meet specific system requirements.5.Pin Compatible with the AD9257 (14-Bit Octal ADC).AD9637Data SheetRev. 0 | Page 2 of 40TABLE OF CONTENTSFeatures..............................................................................................1 Applications.......................................................................................1 General Description.........................................................................1 Functional Block Diagram..............................................................1 Product Highlights...........................................................................1 Table of Contents..............................................................................2 Revision History...............................................................................2 Specifications.....................................................................................3 DC Specifications.........................................................................3 AC Specifications..........................................................................4 Digital Specifications...................................................................5 Switching Specifications..............................................................6 Timing Specifications..................................................................6 Absolute Maximum Ratings............................................................8 Thermal Characteristics..............................................................8 ESD Caution..................................................................................8 Pin Configuration and Function Descriptions.............................9 Typical Performance Characteristics...........................................11 AD9637-80..................................................................................11 AD9637-40..................................................................................14 Equivalent Circuits.........................................................................17 Theory of Operation......................................................................18 Analog Input Considerations....................................................18 Voltage Reference.......................................................................19 Clock Input Considerations......................................................20 Power Dissipation and Power-Down Mode...........................22 Digital Outputs and Timing.....................................................23 Built-In Output Test Modes..........................................................27 Output Test Modes.....................................................................27 Serial Port Interface (SPI)..............................................................28 Configuration Using the SPI.....................................................28 Hardware Interface.....................................................................29 Configuration Without the SPI................................................29 SPI Accessible Features..............................................................29 Memory Map..................................................................................30 Reading the Memory Map Register Table...............................30 Memory Map Register Table.....................................................31 Memory Map Register Descriptions........................................34 Applications Information..............................................................36 Design Guidelines......................................................................36 Power and Ground Recommendations...................................36 Exposed Pad Thermal Heat Slug Recommendations............36 VCM.............................................................................................36 Reference Decoupling................................................................36 SPI Port........................................................................................36 Outline Dimensions.......................................................................37 Ordering Guide.. (37)REVISION HISTORY10/11—Revision 0: Initial VersionData SheetAD9637Rev. 0 | Page 3 of 40SPECIFICATIONSDC SPECIFICATIONSAVDD = 1.8 V , DRVDD = 1.8 V , 2 V p-p differential input, 1.0 V internal reference, AIN = −1.0 dBFS, unless otherwise noted. Table 1.AD9637-40 AD9637-80Parameter 1Temp M in Typ M ax M in Typ M ax Unit RESOLUTION 14 14 Bits ACCURACY No Missing Codes Full Guaranteed Guaranteed Offset Error Full −0.6 −0.3 +0.1 −0.7 −0.3 +0.1 % FSR Offset Matching Full 0.0 0.2 0.6 0.0 0.2 0.6 % FSR Gain Error Full −8.0 −2.1 +2.0 −7.0 −3.2 +1.0 % FSR Gain Matching Full −1.0 +1.7 +5.0 −1.0 +2.3 +6.0 % FSR Differential Nonlinearity (DNL) Full −0.8 ±0.3 +0.8 −0.8 ±0.4 +0.8 LSB Integral Nonlinearity (INL) Full −1.0 ±0.4 +1.0 −1.2 ±0.5 +1.2 LSB TEMPERATURE DRIFT Offset Error Full ±2 ±2 ppm/°C INTERNAL VOLTAGE REFERENCE Output Voltage (1 V Mode) Full 0.98 0.99 1.01 0.98 0.99 1.01 V Load Regulation at 1.0 mA (V REF = 1 V) Full 2 2 mV Input Resistance Full 7.5 7.5 kΩ INPUT REFERRED NOISE V REF = 1.0 V 25°C 0.36 0.49 LSB rms ANALOG INPUTS Differential Input Voltage (V REF = 1 V) Full 2 2 V p-p Common-Mode Voltage Full 0.9 0.9 V Differential Input Resistance 5.2 5.2 kΩ Differential Input Capacitance Full 3.5 3.5 pF POWER SUPPLYAVDD Full 1.7 1.8 1.9 1.7 1.8 1.9 V DRVDD Full 1.7 1.8 1.9 1.7 1.8 1.9 V I AVDD (Eight Channels) Full 142 151 221 234 mA I DRVDD (Eight Channels, ANSI-644 Mode) Full 51 79 58 85 mA I DRVDD (Eight Channels, Reduced Range Mode) 25°C 36 43 mA TOTAL POWER CONSUMPTION Total Power Dissipation (Eight Channels, ANSI-644 Mode) Full 347 414 502 574 mW Total Power Dissipation (Eight Channels, Reduced Range Mode) 25°C 320 475 mW Power-Down Dissipation 25°C 1 1 mW Standby Dissipation 2 25°C 72 98 mW1 See the AN-835 Application Note , Understanding High Speed ADC Testing and Evaluation , for definitions and for details on how these tests were completed. 2Can be controlled via the SPI.AD9637Data SheetRev. 0 | Page 4 of 40AC SPECIFICATIONSAVDD = 1.8 V , DRVDD = 1.8 V , 2 V p-p differential input, 1.0 V internal reference, AIN = −1.0 dBFS, unless otherwise noted. Table 2.AD9637-40 AD9637-80Parameter 1Temp M in Typ M ax M in Typ M ax Unit SIGNAL-TO-NOISE RATIO (SNR) f IN = 9.7 MHz 25°C 72.0 71.5 dBFS f IN = 19.7 MHz Full 70.0 72.0 71.0 71.5 dBFS f IN = 30.5 MHz 25°C 72.0 71.5 dBFS f IN = 63.5 MHz 25°C 71.5 dBFS f IN = 69.5 MHz 25°C 71.5 dBFS f IN = 123.5 MHz 25°C 70.5 dBFS SIGNAL-TO-NOISE AND DISTORTION RATIO (SINAD) f IN = 9.7 MHz 25°C 71.0 70.5 dBFS f IN = 19.7 MHz Full 69.0 71.0 70.0 70.5 dBFS f IN = 30.5 MHz 25°C 71.0 70.5 dBFS f IN = 63.5 MHz 25°C 70.5 dBFS f IN = 69.5 MHz 25°C 70.5 dBFS f IN = 123.5 MHz 25°C 69.5 dBFS EFFECTIVE NUMBER OF BITS (ENOB) f IN = 9.7 MHz 25°C 11.5 11.4 Bits f IN = 19.7 MHz Full 11.2 11.5 11.3 11.4 Bits f IN = 30.5 MHz 25°C 11.5 11.4 Bits f IN = 63.5 MHz 25°C 11.4 Bits f IN = 69.5 MHz 25°C 11.4 Bits f IN = 123.5 MHz 25°C 11.3 Bits SPURIOUS-FREE DYNAMIC RANGE (SFDR) f IN = 9.7 MHz 25°C 96 93 dBc f IN = 19.7 MHz Full 78 95 78 92 dBc f IN = 30.5 MHz 25°C 96 92 dBc f IN = 63.5 MHz 25°C 93 dBc f IN = 69.5 MHz 25°C 89 dBc f IN = 123.5 MHz 25°C 88 dBc WORST HARMONIC (SECOND OR THIRD) f IN = 9.7 MHz 25°C −99 −96 dBc f IN = 19.7 MHz Full −96 −78 −92 −78 dBc f IN = 30.5 MHz 25°C −98 −92 dBc f IN = 63.5 MHz 25°C −95 dBc f IN = 69.5 MHz 25°C −89 dBc f IN = 123.5 MHz 25°C −89 dBc WORST OTHER (EXCLUDING SECOND OR THIRD) f IN = 9.7 MHz 25°C −98 −97 dBFS f IN = 19.7 MHz Full −98 −86 −97 −86 dBFS f IN = 30.5 MHz 25°C −98 −97 dBFS f IN = 63.5 MHz 25°C −97 dBFS f IN = 69.5 MHz 25°C −97 dBFS f IN = 123.5 MHz 25°C −92 dBFSTWO-TONE INTERMODULATION DISTORTION (IMD)—AIN1 AND AIN2 = −7.0 dBFS f IN1 = 8 MHz, f IN2 = 10 MHz 25°C 93 dBc f IN1 = 30 MHz, f IN2 = 32 MHz 25°C 85 dBcData Sheet AD9637Rev. 0 | Page 5 of 40 AD9637-40 AD9637-80CROSSTALK 25°C−98−96dBCrosstalk (Overrange Condition)225°C−89−89dBANALOG INPUT BANDWIDTH, FULL POWER 25°C 650 650 MHz1 See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for definitions and for details on how these tests were completed.2 Overrange condition is specified with3 dB of the full-scale input range.DIGITAL SPECIFICATIONSAVDD = 1.8 V, DRVDD = 1.8 V, 2 V p-p differential input, 1.0 V internal reference, AIN = −1.0 dBFS, unless otherwise noted.Table 3.Parameter1 TempM inTypM axUnit CLOCK INPUTS (CLK+, CLK−)Logic Compliance CMOS/LVDS/LVPECLDifferential Input Voltage2 Full0.2 3.6Vp-pInput Voltage Range Full AGND − 0.2 AVDD + 0.2 VInput Common-Mode Voltage Full 0.9 VInput Resistance (Differential) 25°C 15 kΩInput Capacitance 25°C 4 pFLOGIC INPUTS (PDWN, SYNC, SCLK)Logic 1 Voltage Full 1.2 AVDD + 0.2 VLogic 0 Voltage Full 0 0.8 VInput Resistance 25°C 30 kΩInput Capacitance 25°C 2 pFLOGIC INPUT (CSB)Logic 1 Voltage Full 1.2 AVDD + 0.2 VLogic 0 Voltage Full 0 0.8 VInput Resistance 25°C 26 kΩInput Capacitance 25°C 2 pFLOGIC INPUT (SDIO)Logic 1 Voltage Full 1.2 AVDD + 0.2 VLogic 0 Voltage Full 0 0.8 VInput Resistance 25°C 26 kΩInput Capacitance 25°C 5 pFLOGIC OUTPUT (SDIO)3Logic 1 Voltage (I OH = 800 μA) Full 1.79 VLogic 0 Voltage (I OL = 50 μA) Full 0.05 VDIGITAL OUTPUTS (D± x), ANSI-644Logic Compliance LVDSDifferential Output Voltage (V OD) Full247350454mVOutput Offset Voltage (V OS) Full1.131.211.38VOutput Coding (Default) Twos complementDIGITAL OUTPUTS (D± x), LOW POWER,REDUCED SIGNAL OPTIONLogic Compliance LVDSDifferential Output Voltage (V OD) Full150200250mVOutput Offset Voltage (V OS) Full1.131.211.38VOutput Coding (Default) Twos complement1 See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for definitions and for details on how these tests were completed.2 This is specified for LVDS and LVPECL only.3 This is specified for 13 SDIO/DFS pins sharing the same connection.AD9637Data SheetRev. 0 | Page 6 of 40SWITCHING SPECIFICATIONSAVDD = 1.8 V , DRVDD = 1.8 V , 2 V p-p differential input, 1.0 V internal reference, AIN = −1.0 dBFS, unless otherwise noted. Table 4.Parameter 1, 2 Temp M in Typ M ax Unit CLOCK 3 Input Clock Rate Full 10 640 MHz Conversion Rate Full 10 40/80 MSPS Clock Pulse Width High (t EH ) Full 12.5/6.25 ns Clock Pulse Width Low (t EL ) Full 12.5/6.25 ns OUTPUT PARAMETERS 3 Propagation Delay (t PD ) Full 2.3 ns Rise Time (t R ) (20% to 80%) Full 300 ps Fall Time (t F ) (20% to 80%) Full 300 ps FCO Propagation Delay (t FCO ) Full 1.5 2.3 3.1 ns DCO Propagation Delay (t CPD )4 Full t FCO + (t SAMPLE /24) nsDCO to Data Delay (t DATA )4Full (t SAMPLE /24) − 300 (t SAMPLE /24) (t SAMPLE /24) + 300 ps DCO to FCO Delay (t FRAME )4 Full (t SAMPLE /24) − 300 (t SAMPLE /24) (t SAMPLE /24) + 300 psData to Data Skew(t DATA-MAX − t DATA-MIN ) Full ±50 ±200 ps Wake-Up Time (Standby) 25°C 35 μsWake-Up Time (Power-Down)525°C 375 μs Pipeline Latency Full 16 ClockcyclesAPERTURE Aperture Delay (t A ) 25°C 1 ns Aperture Uncertainty (Jitter) 25°C 0.1 ps rms Out-of-Range Recovery Time 25°C 1 Clockcycles1 See the AN-835 Application Note , Understanding High Speed ADC Testing and Evaluation , for definitions and for details on how these tests were completed. 2Measured on standard FR-4 material. 3Can be adjusted via the SPI. 4t SAMPLE /24 is based on the number of bits divided by 2 because the delays are based on half duty cycles. t SAMPLE = 1/f S . 5Wake-up time is defined as the time required to return to normal operation from power-down mode.TIMING SPECIFICATIONSTable 5.ParameterDescription Limit Unit SYNC TIMING REQUIREMENTSt SSYNC SYNC to rising edge of CLK+ setup time 0.24 ns typ t HSYNCSYNC to rising edge of CLK+ hold time 0.40 ns typ SPI TIMING REQUIREMENTS See Figure 61t DS Setup time between the data and the rising edge of SCLK 2 ns min t DH Hold time between the data and the rising edge of SCLK 2 ns min t CLK Period of the SCLK40 ns min t S Setup time between CSB and SCLK 2 ns min t H Hold time between CSB and SCLK 2 ns min t HIGH SCLK pulse width high 10 ns min t LOW SCLK pulse width low10 ns min t EN_SDIO Time required for the SDIO pin to switch from an input to an output relative to the SCLK falling edge (not shown in Figure 61)10 ns min t DIS_SDIOTime required for the SDIO pin to switch from an output to an input relative to the SCLK rising edge (not shown in Figure 61)10ns minData SheetAD9637Rev. 0 | Page 7 of 40DCO–DCO+D– xD+ xCLK–CLK+05967-002Figure 2. Word-Wise DDR, 1× Frame, 12-Bit Output Mode (Default)10215-003CLK+D– xD+ xFigure 3. Word-Wise DDR, 1× Frame, 10-Bit Output Mode10215-004Figure 4. SYNC Input Timing RequirementsAD9637Data SheetRev. 0 | Page 8 of 40ABSOLUTE MAXIMUM RATINGSTable 6.Parameter RatingElectricalAVDD to AGND −0.3 V to +2.0 VDRVDD to AGND −0.3 V to +2.0 VDigital Outputs(D± x, DCO+, DCO−, FCO+, FCO−) to AGND −0.3 V to +2.0 V CLK+, CLK− to AGND −0.3 V to +2.0 VVIN+ x, VIN− x to AGND −0.3 V to +2.0 VSCLK/DTP , SDIO/DFS, CSB to AGND −0.3 V to +2.0 VSYNC, PDWN to AGND −0.3 V to +2.0 V RBIAS to AGND −0.3 V to +2.0 V VREF, SENSE to AGND −0.3 V to +2.0 V Environmental Operating Temperature Range (Ambient) −40°C to +85°C Maximum Junction Temperature 150°C Lead Temperature (Soldering, 10 sec) 300°C Storage Temperature Range (Ambient) −65°C to +150°C Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operationalsection of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. THERMAL CHARACTERISTICSThe exposed paddle must be soldered to the ground plane for the LFCSP package. Soldering the exposed paddle to the printedcircuit board (PCB) increases the reliability of the solder jointsand maximizes the thermal capability of the package.Table 7. Thermal Resistance Package Type Airflow Velocity(m/sec) θJA 1, 2 θJC 1, 3 θJB 1, 4 JT 1, 2 Unit 64-Lead LFCSP 9 mm × 9 mm(CP-64-4) 0 22.3 1.4 N/A 0.1 °C/W 1.0 19.5 N/A 11.8 0.2 °C/W 2.5 17.5 N/A N/A0.2 °C/W 1Per JEDEC 51-7, plus JEDEC 25-5 2S2P test board. 2 Per JEDEC JESD51-2 (still air) or JEDEC JESD51-6 (moving air). 3Per MIL-Std 883, Method 1012.1. 4Per JEDEC JESD51-8 (still air).Typical θJA is specified for a 4-layer PCB with a solid ground plane. As shown Table 7, airflow improves heat dissipation, which reduces θJA . In addition, metal in direct contact with the package leads from metal traces, through holes, ground, and power planes reduces θJA .ESD CAUTIONData SheetAD9637Rev. 0 | Page 9 of 40PIN CONFIGURATION AND FUNCTION DESCRIPTIONS17181920212223242526272829303132D – G D + G D – F D + F D –E D + E D C O –D C O +F C O –F C O +D – D D + D D – C D + C D – B D + B 64636261605958575655545352515049V I N + F V I N – F A V D D V I N – E V I N + E A V D D S Y N C V C M V R E F S E N S E R B I A S V I N + D V I N – D A V D D V I N – C V I N + CAVDD VIN+ B VIN– B AVDD VIN– A VIN+ A AVDD PDWN CSBSDIO/DFS SCLK/DTP AVDD DNC DRVDD D+ A D– A48474645444342414039383736353433NOTES1. DNC = DO NOT CONNECT. DO NOT CONNECT TO THIS PIN.2. THE EXPOSED PAD MUST BE CONNECTED TO ANALOG GROUND.10215-005Figure 5. Pin Configuration, Top ViewTable 8. Pin Function DescriptionsPin No. Mnemonic Description0, EPAGND,Exposed Pad Analog Ground, Exposed Pad. The exposed thermal pad on the bottom of the package provides the analog ground for the part. This exposed pad must be connected to analog ground for proper operation. 1, 4, 7, 8, 11, 12, 37, 42, 45, 48, 51, 59, 62 AVDD1.8 V Analog Supply.13, 36 DNC Do Not Connect. Do not connect to this pin. 14, 35 DRVDD 1.8 V Digital Output Driver Supply. 2, 3 VIN+ G, VIN− G ADC G Analog Input True, ADC G Analog Input Complement. 5, 6 VIN− H, VIN+ H ADC H Analog Input Complement, ADC H Analog Input True. 9, 10 CLK−, CLK+ Input Clock Complement, Input Clock True. 15, 16 D− H, D+ H ADC H Digital Output Complement, ADC H Digital Output True. 17, 18 D− G, D+ G ADC G Digital Output Complement, ADC G Digital Output True. 19, 20 D− F, D+ F ADC F Digital Output Complement, ADC F Digital Output True. 21, 22 D− E, D+ E ADC E Digital Output Complement, ADC E Digital Output True. 23, 24 DCO−, DCO+ Data Clock Digital Output Complement, Data Clock Digital Output True. 25, 26 FCO−, FCO+ Frame Clock Digital Output Complement, Frame Clock Digital Output True. 27, 28 D− D, D+ D ADC D Digital Output Complement, ADC D Digital Output True. 29, 30 D− C, D+ C ADC C Digital Output Complement, ADC C Digital Output True. 31, 32 D− B, D+ B ADC B Digital Output Complement, ADC B Digital Output True. 33, 34 D− A, D+ A ADC A Digital Output Complement, ADC A Digital Output True. 38 SCLK/DTP Serial Clock (SCLK)/Digital Test Pattern (DTP). 39 SDIO/DFS Serial Data Input/Output (SDIO)/Data Format Select (DFS). 40 CSB Chip Select Bar. 41 PDWN Power-Down. 43, 44 VIN+ A, VIN− A ADC A Analog Input True, ADC A Analog Input Complement. 46, 47 VIN− B, VIN+ B ADC B Analog Input Complement, ADC B Analog Input True. 49, 50 VIN+ C, VIN− C ADC C Analog Input True, ADC C Analog Input Complement.AD9637 Data SheetPin No. Mnemonic Description52, 53 VIN− D, VIN+ D ADC D Analog Input Complement, ADC D Analog Input True.54 RBIAS Sets analog current bias. Connect to 10 kΩ (1% tolerance) resistor to ground.55 SENSE Reference Mode Selection.56 VREF Voltage Reference Input/Output.57 VCM Analog Output Voltage at Midsupply. Sets common mode of the analog inputs.58 SYNC Digital Input. SYNC input to clock divider. 30 kΩ internal pull-down.60, 61 VIN+ E, VIN− E ADC E Analog Input True, ADC E Analog Input Complement.63, 64 VIN− F, VIN+ F ADC F Analog Input Complement, ADC F Analog Input True.Rev. 0 | Page 10 of 40分销商库存信息:ANALOG-DEVICESAD9637BCPZ-40AD9637BCPZ-80AD9637BCPZRL7-40 AD9637BCPZRL7-80AD9637-80EBZ。

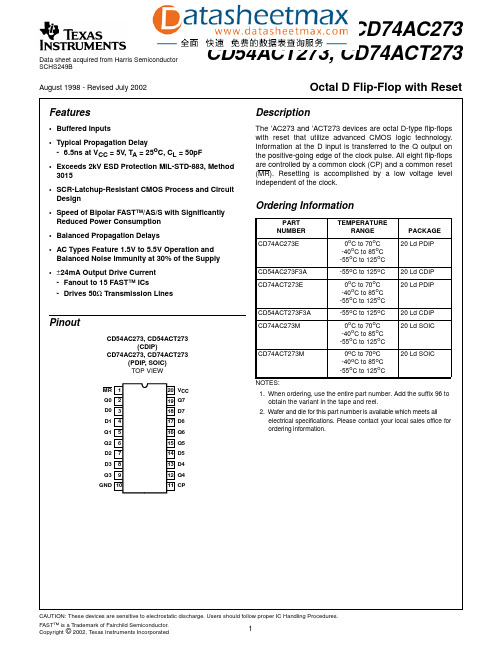

IC datasheet pdf-CD54AC273, CD74AC273,CD54ACT273, CD74ACT273,pdf(Octal D Flip-Flop)

Data sheet acquired from Harris SemiconductorSCHS249BFeatures•Buffered Inputs•Typical Propagation Delay- 6.5ns at V CC = 5V , T A = 25o C, C L = 50pF•Exceeds 2kV ESD Protection MIL-STD-883, Method 3015•SCR-Latchup-Resistant CMOS Process and Circuit Design •Speed of Bipolar FAST™/AS/S with Significantly Reduced Power Consumption •Balanced Propagation Delays•AC Types Feature 1.5V to 5.5V Operation and Balanced Noise Immunity at 30% of the Supply •±24mA Output Drive Current -Fanout to 15 FAST™ ICs-Drives 50Ω Transmission LinesPinoutCD54AC273, CD54ACT273(CDIP)CD74AC273, CD74ACT273(PDIP , SOIC)TOP VIEWDescriptionThe ’AC273and ’ACT273devices are octal D-type flip-flops with reset that utilize advanced CMOS logic rmation at the D input is transferred to the Q output on the positive-going edge of the clock pulse.All eight flip-flops are controlled by a common clock (CP)and a common reset (MR).Resetting is accomplished by a low voltage level independent of the clock.1112131415161718201910987654321MR Q0D0D1Q1Q2D3D2Q3GND V CC D7D6Q6Q7Q5D5D4Q4CPOrdering InformationPART NUMBER TEMPERATURERANGE PACKAGE CD74AC273E0o C to 70o C -40o C to 85o C -55o C to 125o C 20 Ld PDIPCD54AC273F3A -55o C to 125o C 20 Ld CDIP CD74ACT273E0o C to 70o C -40o C to 85o C -55o C to 125o C 20 Ld PDIPCD54ACT273F3A -55o C to 125o C 20 Ld CDIP CD74AC273M0o C to 70o C -40o C to 85o C -55o C to 125o C 20 Ld SOICCD74ACT273M 0o C to 70o C -40o C to 85o C -55o C to 125o C20 Ld SOICNOTES:1.When ordering,use the entire part number.Add the suffix 96to obtain the variant in the tape and reel.2.Wafer and die for this part number is available which meets allelectrical specifications.Please contact your local sales office for ordering information.August 1998 - Revised July 2002CD54AC273, CD74AC273CD54ACT273, CD74ACT273Octal D Flip-Flop with ResetFunctional DiagramTRUTH TABLE INPUTSOUTPUTSRESET (MR)CLOCK CP DATA Dn Qn L X X L H ↑H H H ↑L L HLXQ0H =High level (steady state),L =Low level (steady state),X =Irrel-evant,↑=Transition from Low to High level,Q0=The level of Q before the indicated steady-state input conditions were estab-lished.Q0Q1Q2Q3Q4Q5Q6Q7RESET MRD0D1D2D3D4D5D6D7CLOCKCPDATA INPUTSDATAOUTPUTSAbsolute Maximum Ratings Thermal InformationDC Supply Voltage, V CC. . . . . . . . . . . . . . . . . . . . . . . .-0.5V to 6V DC Input Diode Current, I IKFor V I < -0.5V or V I > V CC + 0.5V. . . . . . . . . . . . . . . . . . . . . .±20mA DC Output Diode Current, I OKFor V O < -0.5V or V O > V CC + 0.5V . . . . . . . . . . . . . . . . . . . .±50mA DC Output Source or Sink Current per Output Pin, I OFor V O > -0.5V or V O < V CC + 0.5V . . . . . . . . . . . . . . . . . . . .±50mA DC V CC or Ground Current, I CC or I GND (Note 3) . . . . . . . . .±100mA Operating ConditionsTemperature Range, T A . . . . . . . . . . . . . . . . . . . . . .-55o C to 125o C Supply Voltage Range, V CC (Note 4)AC T ypes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1.5V to 5.5V ACT T ypes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4.5V to 5.5V DC Input or Output Voltage, V I, V O . . . . . . . . . . . . . . . . .0V to V CC Input Rise and Fall Slew Rate, dt/dvAC T ypes, 1.5V to 3V . . . . . . . . . . . . . . . . . . . . . . . . .50ns (Max) AC T ypes, 3.6V to 5.5V. . . . . . . . . . . . . . . . . . . . . . . .20ns (Max) ACT T ypes, 4.5V to 5.5V. . . . . . . . . . . . . . . . . . . . . . .10ns (Max)Thermal Resistance,θJA(Typical, Note 5)E Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69o C/W M Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58o C/W Maximum Junction T emperature (Plastic Package) . . . . . . . . . .150o C Maximum Storage Temperature Range . . . . . . . . . .-65o C to 150o C Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . . .300o CCAUTION:Stresses above those listed in“Absolute Maximum Ratings”may cause permanent damage to the device.This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.NOTES:3.For up to 4 outputs per device, add±25mA for each additional output.4.Unless otherwise specified, all voltages are referenced to ground.5.The package thermal impedance is calculated in accordance with JESD 51.DC Electrical SpecificationsPARAMETER SYMBOLTESTCONDITIONS VCC(V)25o C-40o C TO85o C-55o C TO125o CUNITS V I(V)I O(mA)MIN MAX MIN MAX MIN MAXAC TYPESHigh Level Input Voltage V IH-- 1.5 1.2- 1.2- 1.2-V3 2.1- 2.1- 2.1-V5.5 3.85- 3.85- 3.85-V Low Level Input Voltage V IL-- 1.5-0.3-0.3-0.3V3-0.9-0.9-0.9V5.5- 1.65- 1.65- 1.65V High Level Output Voltage V OH V IH or V IL-0.05 1.5 1.4- 1.4- 1.4-V-0.053 2.9- 2.9- 2.9-V-0.05 4.5 4.4- 4.4- 4.4-V-43 2.58- 2.48- 2.4-V-24 4.5 3.94- 3.8- 3.7-V-75(Note 6, 7)5.5-- 3.85---V-50(Note 6, 7)5.5---- 3.85-VLow Level Output VoltageV OLV IH or V IL0.05 1.5-0.1-0.1-0.1V 0.053-0.1-0.1-0.1V 0.05 4.5-0.1-0.1-0.1V 123-0.36-0.44-0.5V 24 4.5-0.36-0.44-0.5V 75(Note 6, 7) 5.5--- 1.65--V 50(Note 6, 7)5.5----- 1.65V Input Leakage Current I I V CC or GND - 5.5-±0.1-±1-±1µA Quiescent Supply Current MSI I CCV CC or GND5.5-8-80-160µAACT TYPESHigh Level Input Voltage V IH -- 4.5 to 5.52-2-2-V Low Level Input Voltage V IL -- 4.5 to 5.5-0.8-0.8-0.8V High Level Output VoltageV OHV IH or V IL-0.05 4.5 4.4- 4.4- 4.4-V -24 4.5 3.94- 3.8- 3.7-V -75(Note 6, 7) 5.5-- 3.85---V -50(Note 6, 7)5.5---- 3.85-V Low Level Output VoltageV OLV IH or V IL0.05 4.5-0.1-0.1-0.1V 24 4.5-0.36-0.44-0.5V 75(Note 6, 7) 5.5--- 1.65--V 50(Note 6, 7)5.5----- 1.65V Input Leakage Current I I V CC or GND - 5.5-±0.1-±1-±1µA Quiescent Supply Current MSII CC V CC or GND 0 5.5-8-80-160µA Additional Supply Current per Input Pin TTL Inputs High 1 Unit Load ∆I CCV CC -2.1- 4.5 to 5.5- 2.4- 2.8-3mANOTES:6.Test one output at a time for a 1-second maximum duration.Measurement is made by forcing current and measuring voltage to minimize power dissipation.7.Test verifies a minimum 50Ω transmission-line-drive capability at 85o C, 75Ω at 125o C.ACT Input Load TableINPUT UNIT LOADDn 0.5MR 0.57CP1NOTE:Unit load is ∆I CC limit specified in DC Electrical Specifications T able, e.g., 2.4mA max at 25o C.DC Electrical Specifications(Continued)PARAMETERSYMBOL TEST CONDITIONSV CC (V)25o C -40o C TO 85o C -55o C TO 125o C UNITS V I (V)I O (mA)MIN MAX MIN MAX MIN MAXPrerequisite For Switching FunctionPARAMETER SYMBOL V CC (V)-40o C TO 85o C-55o C TO 125o CUNITS MIN MAX MIN MAXAC TYPESData to CP Set-Up Time t SU 1.52-2-ns3.3(Note 9)2-2-ns5(Note 10)2-2-ns Hold Time t H 1.52-2-ns3.32-2-ns52-2-ns Removal Time,MR to CP t REM 1.52-2-ns3.32-2-ns52-2-ns MR Pulse Width t W 1.555-63-ns3.3 6.1-7-ns5 4.4-5-ns CP Pulse Width t W 1.555-63-ns3.3 6.1-7-ns5 4.4-5-ns CP Frequency f MAX 1.59-8-MHz3.381-71-MHz5114-100-MHz ACT TYPESData to CP Set-Up Time t SU5(Note 10)2-2-ns Hold Time t H52-2-ns Removal Time MR to CP t REM52-2-ns MR Pulse Width t W5 4.4-5-ns CP Pulse Width t W5 5.3-6-ns CP Frequency f MAX597-85-MHz Switching Specifications Input t r, t f = 3ns, C L= 50pF (Worst Case)PARAMETER SYMBOL V CC (V)-40o C TO 85o C-55o C TO 125o CUNITS MIN TYP MAX MIN TYP MAXAC TYPESPropagation Delay, CP to Qn t PLH, t PHL 1.5--154--169ns3.3(Note 9)4.9-17.2 4.7-18.9ns5(Note 10)3.5-12.3 3.4-13.5nsPropagation Delay,MR to Qnt PLH , t PHL1.5--154--169ns 3.3 4.9-17.2 4.7-18.9ns 53.5-12.3 3.4-13.5ns Input CapacitanceC I ---10--10pF Power Dissipation Capacitance C PD (Note 11)--45--45-pFACT TYPES Propagation Delay,CP to Qnt PLH , t PHL 5(Note 10)3.5-12.3 3.4-13.5ns Propagation Delay,MR to Qn t PLH , t PHL5 3.5-12.3 3.4-13.5ns Input CapacitanceC I ---10--10pF Power Dissipation Capacitance C PD (Note 11)--45--45-pFNOTES:8.Limits tested 100%.9.3.3V Min is at 3.6V, Max is at 3V.10.5V Min is at 5.5V, Max is at 4.5V.11.C PD is used to determine the dynamic power consumption per flip-flop.AC: P D = C PD V CC 2 f i =∑ (C L V CC 2 f o )ACT:P D =C PD V CC 2f i +∑(C L V CC 2f o )+V CC ∆I CC where f i =input frequency,f o =output frequency,C L =output load capacitance,V CC = supply voltage.FIGURE 1.PROPAGATION DELAY TIMES AND CLOCKPULSE WIDTH FIGURE 2.PREREQUISITE AND PROPAGATION DELAYTIMES FOR MASTER RESETSwitching Specifications Input t r , t f = 3ns, C L = 50pF (Worst Case)(Continued)PARAMETERSYMBOL V CC (V)-40o C TO 85o C-55o C TO 125o CUNITS MIN TYP MAX MIN TYP MAX 90%t f t r V SV S V SV SV St PLHt PHLt W 10%10%CP INPUT LEVEL QMR CPINPUT LEVELV SQV St REMV SV St PLHt WGNDINPUT(Q)FIGURE 3.PREREQUISITE FOR CLOCKDV S V S V SV S V S V St H (H)t SU (L)t H (L)t SU (H)CPOUTPUT LEVELDUT OUTPUTR L (NOTE)OUTPUT LOAD500ΩC L 50pFNOTE:For AC Series Only: When V CC = 1.5V , R L = 1k Ω.FIGURE 4.PROPAGATION DELAY TIMESACACT Input LevelV CC 3V Input Switching Voltage, V S 0.5 V CC 1.5V Output Switching Voltage, V S0.5 V CC0.5 V CCPACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)CD54AC273F3A ACTIVE CDIP J201TBD A42N/A for Pkg Type CD54ACT273F3A ACTIVE CDIP J201TBD A42N/A for Pkg Type CD74AC273E ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeCD74AC273EE4ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeCD74AC273M ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74AC273M96ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74AC273M96E4ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74AC273M96G4ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74AC273ME4ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74AC273MG4ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273E ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeCD74ACT273EE4ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeCD74ACT273M ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273M96ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273M96E4ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273M96G4ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273ME4ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273MG4ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273PW ACTIVE TSSOP PW2070Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273PWE4ACTIVE TSSOP PW2070Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273PWG4ACTIVE TSSOP PW2070Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273PWR ACTIVE TSSOP PW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273PWRE4ACTIVE TSSOP PW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273PWRG4ACTIVE TSSOP PW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273SM96ACTIVE SSOP DB202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273SM96E4ACTIVE SSOP DB202000Green(RoHS&CU NIPDAU Level-1-260C-UNLIMOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)no Sb/Br)CD74ACT273SM96G4ACTIVE SSOP DB202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS),Pb-Free(RoHS Exempt),or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free(RoHS Exempt):This component has a RoHS exemption for either1)lead-based flip-chip solder bumps used between the die and package,or2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free(RoHS compatible)as defined above.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.TAPE AND REELINFORMATION*All dimensionsare nominalDevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant CD74AC273M96SOIC DW 202000330.024.410.813.0 2.712.024.0Q1CD74ACT273M96SOIC DW 202000330.024.410.813.0 2.712.024.0Q1CD74ACT273PWR TSSOP PW 202000330.016.4 6.957.1 1.68.016.0Q1CD74ACT273SM96SSOPDB202000330.016.48.27.52.512.016.0Q1PACKAGE MATERIALS INFORMATION11-Mar-2008*Alldimensions are nominal DevicePackage Type Package Drawing Pins SPQ Length (mm)Width (mm)Height (mm)CD74AC273M96SOIC DW 202000346.0346.041.0CD74ACT273M96SOIC DW 202000346.0346.041.0CD74ACT273PWRTSSOP PW 202000346.0346.033.0CD74ACT273SM96SSOP DB 202000346.0346.033.0PACKAGE MATERIALS INFORMATION 11-Mar-2008Pack Materials-Page 2IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers AudioData Converters AutomotiveDLP®Products BroadbandDSP Digital ControlClocks and Timers MedicalInterface MilitaryLogic Optical NetworkingPower Mgmt SecurityMicrocontrollers TelephonyRFID Video&ImagingRF/IF and ZigBee®Solutions WirelessMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2009,Texas Instruments Incorporated。

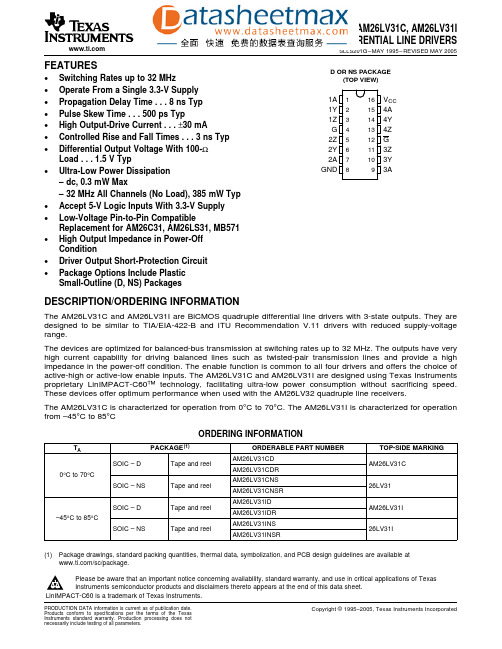

IC datasheet pdf-AM26LV31C,AM26LV31I,pdf(LOW-VOLTAGE HIGH-SPEED QUADRUPLE DIFFERENTIAL LINE DRIVERS)