AD8146中文资料

AD9516_3中文版资料

AD9516_3----集成的2.0 GHz VCO的14路输出时钟发生器一、特征:①低相位噪声,锁相环(PLL)②片上VCO从1.75 GHz到2.25 GHz调谐③外部可选的VCO / VCXO 高达2.4 GHz④1个差分或2个单端参考输入⑤接受LVPECL ,LVDS或CMOS 250 MHz的输出频率⑥6双1.6 GHz的LVPECL输出,每对输出共享1到32位分频器与粗相位延迟⑦4对为800 MHz LVDS时钟输出,每对输出共用两个级联的粗相位延迟1到32的分频器⑧上电时所有输出自动同步可用手动输出同步64引脚LFCSP二、介绍:AD9516 -31集成了片上PLL和VCO,提供了多输出时钟分配功能,具有亚皮秒级的抖动性能。

片上VCO从1.75 GHz到2.25 GHz调谐,芯片外部可以使用高达2.4 GHz的VCO / VCXO 。

AD9516- 3侧重于低抖动和相位噪声数据转换器的性能最大化问题,可以应用于对抖动和相位噪声要求很高的问题上。

三、应用①低抖动,低相位噪声时钟分配②10/40/100 Gb /秒的网络线卡,包括SONET③同步以太网,OTU2/3/4④前向纠错(G.710 )⑤高速时钟的ADCs, DACs, DDSs, DDCs, DUCs, MxFEs⑥高性能无线收发器⑦自动测试设备(ATE)和高性能仪器仪表四、芯片的规格(1)供应的电源:Vs=Vs_LVPECL=3.3 V ± 5%;Vs≤ Vcp≤ 5.25 V; Ta= 25°C; RSET = 4.12 kΩ; CPRSET = 5.1 kΩ四、原理框图AD9516-3具有6个LVPECL输出(三对),4个LVDS输出(两对)。

每个LVDS输出可配置为两个CMOS输出,LVPECL输出工作频率为1.6 GHz ,LVDS输出工作频率为800 MHz,CMOS输出工作频率为250 MHz。

AD9116中文资料

元器件交易网

AD9114/AD9115/AD9116/AD9117

TABLE OF CONTENTS

Features .............................................................................................. 1 Applications....................................................................................... 1 General Description ......................................................................... 1 Product Highlights ........................................................................... 1 Revision History ............................................................................... 2 Functional Block Diagram .............................................................. 3 Specifications..................................................................................... 4

2. CMOS Clock Input. High speed, single-ended CMOS clock input supports 125 MSPS conversion rate.

AD8556中文资料

5 678

+VS REF1 REF2

–VS

05947-001

Figure 1. 4mm × 4 mm LFCSP

Table 1. In Amps and Differential Amplifier by Category

High

Low

Performance Cost

High Mil Voltage Grade

The AD8222 is the first dual-instrumentation amplifier in the small 4 mm × 4mm LFCSP. It requires the same board area as a typical single instrumentation amplifier. The smaller package allows a 2× increase in channel density and a lower cost per channel, all with no compromise in performance.

Thermal Resistance ...................................................................... 6 ESD Caution.................................................................................. 6 Pin Configuration and Function Descriptions............................. 7 Typical Performance Characteristics ............................................. 8 Theory of Operation ...................................................................... 15 Amplifier Architecture .............................................................. 15 Gain Selection ............................................................................. 15 Reference Terminal .................................................................... 16

AD8148中文资料

Triple Differential Driver for Wideband Video

AD8146/AD8147/AD8148

FUNCTIONAL BLOCK DIAGRAMS

VS+ –IN B +IN B VS– VOCMA VOCMB

OPD 1 VS– 2 –IN A 3 +IN A 4 VS– 5 –OUT A 6

Output balance error −50 dB @ 50 MHz On-chip, sync-on common-mode encoding (AD8147/AD8148) Output pull-down feature for line isolation Low power: 57 mA @ 5 V for 3 drivers (AD8146) Wide supply voltage range: +5 V to ±5 V Available in a small 4 mm × 4 mm LFCSP

Thermal Resistance ...................................................................... 7 ESD Caution.................................................................................. 7 Pin Configuration and Function Descriptions............................. 8 Typical Performance Characteristics ........................................... 10 Theory of Operation ...................................................................... 14 Definition of Terms.................................................................... 14 Analyzing an Application Circuit............................................. 14 Closed-Loop Gain ...................................................................... 14 Calculating the Input Impedance............................................. 15

ADG1406中文资料

Table 1. Related Devices

Part No.

Description

ADG1206/ADG1207 Low capacitance, low charge injection, and low leakage 8-/16-channel ±15 V multiplexers

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

APPLICATIONS

PC814A中文资料

NOTICEG The circuit application examples in this publication are provided to explain representative applications of SHARP devices and are not intended to guarantee any circuit design or license any intellectual property rights. SHARP takes no responsibility for any problems related to any intellectual property right of a third party resulting from the use of SHARP's devices.G Contact SHARP in order to obtain the latest device specification sheets before using any SHARP device. SHARP reserves the right to make changes in the specifications, characteristics, data, materials, structure, and other contents described herein at any time without notice in order to improve design or reliability. Manufacturing locations are also subject to change without notice.G Observe the following points when using any devices in this publication. SHARP takes no responsibility for damage caused by improper use of the devices which does not meet the conditions and absolute maximum ratings to be used specified in the relevant specification sheet nor meet the following conditions:(i)The devices in this publication are designed for use in general electronic equipment designs such as:--- Personal computers--- Office automation equipment--- Telecommunication equipment [terminal]--- Test and measurement equipment--- Industrial control--- Audio visual equipment--- Consumer electronics(ii)Measures such as fail-safe function and redundant design should be taken to ensure reliability and safety when SHARP devices are used for or in connection with equipment that requires higher reliability such as:--- Transportation control and safety equipment (i.e., aircraft, trains, automobiles, etc.)--- Traffic signals--- Gas leakage sensor breakers--- Alarm equipment--- Various safety devices, etc.(iii)SHARP devices shall not be used for or in connection with equipment that requires an extremely high level of reliability and safety such as:--- Space applications--- Telecommunication equipment [trunk lines]--- Nuclear power control equipment--- Medical and other life support equipment (e.g., scuba).G If the SHARP devices listed in this publication fall within the scope of strategic products described in the Foreign Exchange and Foreign Trade Law of Japan, it is necessary to obtain approval to export such SHARP devices.G This publication is the proprietary product of SHARP and is copyrighted, with all rights reserved. Under the copyright laws, no part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, for any purpose, in whole or in part, without the express written permission of SHARP. Express written permission is also required before any use of this publication may be made by a third party.G Contact and consult with a SHARP representative if there are any questions about the contents of this publication.。

LTC1163CS8#PBF;LTC1165CN8;LTC1165CN8#PBF;LTC1165CS8;LTC1165CS8#PBF;中文规格书,Datasheet资料

MOSFET DriversSFEATUREs Operates from 1.8V to 6Vs0.01µA Standby Currents95µA Operating Current per Channel at 3.3Vs Fully Enhances N-Channel Switchess No External Charge Pump Componentss Built-In Gate Voltage Clampss Easily Protected Against Supply Transientss Controlled Switching ON and OFF Timess Compatible with 5V, 3V and Sub-3V Logic Families s Available in 8-Pin SOIC D UESCRIPTIOThe LTC1163/LTC1165 triple low voltage MOSFET drivers make it possible to switch supply or ground referenced loads through inexpensive, low R DS(ON) N-channel switches from as little as a 1.8V supply. The LTC1165 has inverting inputs and makes it possible to directly replace P-channel MOSFET switches while maintaining system drive polar-ity. The LTC1163 has noninverting inputs. Micropower operation, with 0.01µA standby current and 95µA operating current, coupled with a power supply range of 1.8V to 6V, make the LTC1163/LTC1165 ideally suited for 2- to 4-cell battery-powered applications. The LTC1163/LTC1165 are also well suited for sub-3V, 3.3V and 5V nominal supply applications.The LTC1163/LTC1165 internal charge pumps boost the gate voltage 8V above a 3.3V rail, fully enhancing inexpen-sive N-channels for high- or low-side switch applications. The LTC1163/LTC1165 are available in both an 8-pin DIP and an 8-pin SOIC.SUPPLY VOLTAGE (V)GATEOUTPUTVOLTAGE(V)26810418LTC1163/65 • TA02426121416315MOSFET Switch Gate Voltage 2-Cell Triple High-Side SwitchU SA OPPLICATIs PCMCIA Card 3.3V/5V Switchs2-Cell High-Side Load Switchings Boost Regulator Shutdown to Zero Standby Currents Replacing P-Channel Switchess Notebook Computer Power Managements Palmtop Computer Power Managements Portable Medical Equipments Mixed 3.3V and 5V Supply SwitchingUA OPPLICATITYPICAL12LTC1163/LTC1165SYMBOL PARAMETER CONDITIONSMIN TYP MAXUNITS I QQuiescent Current OFFV S = 1.8V, V IN1 = V IN2 = V IN3 = V OFF (Note 1,2)0.011µA V S = 3.3V, V IN1 = V IN2 = V IN3 = V OFF (Note 1,2)0.011µA V S = 5V, V IN1 = V IN2 = V IN3 = V OFF (Note 1,2)0.011µA Quiescent Current ONV S = 1.8V, V IN = V ON (Note 2,3)60120µA V S = 3.3V, V IN = V ON (Note 2,3)95200µA V S = 5V, V IN = V ON (Note 2,3)180400µA V INH Input High Voltage 1.8V < V S < 2.7V q 80% × V S V 2.7V < V S < 6V q 70% × V SVV INL Input Low Voltage 1.8V < V S < 6V q 15% × V SV I IN Input Current 0V ≤ V IN ≤ V Sq±1µA C IN Input Capacitance 5pF V GATE – V SGate Voltage Above SupplyV S = 1.8V, V IN = V ON (Note 2)q 3.5 4.1 6.0V V S = 2V, V IN = V ON (Note 2)q 4.0 4.6 7.0V V S = 2.2V, V IN = V ON (Note 2)q 4.5 5.2 8.0V V S = 3.3V, V IN = V ON (Note 2)q 6.08.0 9.5V V S = 5V, V IN = V ON (Note 2)q5.09.013.0V t ONTurn-ON TimeV S = 3.3V, C GATE = 1000pF Time for V GATE > V S + 1V 40120400µs Time for V GATE > V S + 2V 60180600µs V S = 5V, C GATE = 1000pF Time for V GATE > V S + 1V 3095300µs Time for V GATE > V S + 2V40130400µsA UG WA WUW A R BSOLUTEXI TI SOperating Temperature RangeLTC1163C/LTC1165C........................... 0°C to 70°C Storage Temperature Range................ –65°C to 150°C Lead Temperature (Soldering, 10 sec)................. 300°CSupply Voltage ......................................................... 7V Any Input Voltage.......................... 7V to (GND – 0.3V)Any Output Voltage....................... 20V to (GND – 0.3V)Current (Any Pin)................................................. 50mAWUUPACKAGE/ORDER I FOR ATIOV S = 1.8V to 6V, T A = 25°C, unless otherwise noted.ELECTRICAL C C HARA TERISTICSLTC1163C/LTC1165C /3LTC1163/LTC1165ELECTRICAL C C HARA TERISTICSV S = 1.8V to 6V, T A = 25°C, unless otherwise noted.SYMBOL PARAMETER CONDITIONSMIN TYP MAX UNITSt OFFTurn-OFF TimeV S = 3.3V, C GATE = 1000pFTime for V GATE < 0.5V 2065200µs V S = 5V, C GATE = 1000pF Time for V GATE < 0.5V1545150µsLTC1163C/LTC1165C The q denotes specifications which apply over the full operating temperature range.Note 1: Quiescent current OFF is for all channels in OFF condition.Note 2: LTC1163: V OFF = 0V, V ON = V S . LTC1165: V OFF = V S , V ON = 0V Note 3: Quiescent current ON is per driver and is measured independently.Gate Voltage Above SupplySupply Current per Driver ONStandby Supply CurrentC C HARA TERISTICSU WA TYPICAL PERFOR CE SUPPLY VOLTAGE (V)0SU P P L Y C U R R E N T (µA )5 4 3 2 1 0 –11234LTC1163/65 • TPC0156SUPPLY VOLTAGE (V)V G A T E – V S (V )1210 8 6 4 2 01234LTC1163/65 • TPC0356SUPPLY VOLTAGE (V)0S U PP L Y C U R R E N T (µA )600 500 400 300 200 100 01234LTC1163/65 • TPC0256Input Threshold VoltageTurn-ON TimeTurn-OFF TimeSUPPLY VOLTAGE (V)0I N P U T T H R E S H O L DV O L T A G E (V )65 4 3 2 1 01234LTC1163/65 • T PC0456SUPPLY VOLTAGE (V)T U R N -O N T IM E (µs )600500 400 300 200 100 01234LTC1163/65 • TPC0556SUPPLY VOLTAGE (V)0T U R N -OF F T I M E (µs )300250 200 150 100 50 01234LTC1163/65 • TA06564LTC1163/LTC1165C C HARA TERISTICSU WA TYPICAL PERFOR CE PI FU CTIO SU U U Input PinsThe LTC1163 is noninverting; i.e., the MOSFET gate is driven above the supply when the input pin is held high.The LTC1165 is inverting and drives the MOSFET gate high when the input pin is held low. The inverting inputs of the LTC1165 allow P-channel switches to be replaced by lower resistance/cost N-channel switches while maintain-ing system drive polarity.The LTC1163/LTC1165 logic inputs are high impedance CMOS gates with ESD protection diodes to ground and therefore should not be forced below ground. The inputs can however, be driven above the power supply rail as there are no clamping diodes connected between the input pins and supply pin. This facilitates operation in mixed 5V/3V systems.Output PinsThe output pin is either driven to ground when the switch is turned OFF or driven above the supply rail when the switch is turned ON. The output is clamped to about 14V above ground by a built-in Zener clamp. This pin has a relatively high impedance when driven above the rail (the equivalent of a few hundred k Ω). Care should be taken to minimize any loading of this pin by parasitic resistance to ground or supply.Supply PinA 150Ω resistor should be inserted in series with the ground pin or supply pin if negative supply voltage tran-sients are anticipated. This will limit the current flowing from the power source into the LTC1163/LTC1165 to tens of milliamps during reverse battery conditions.OPERATIOUThe LTC1163/LTC1165 are triple micropower MOSFET drivers designed for operation over the 1.8V to 6V supply range and include the following functional blocks:3V Logic Compatible InputsThe LTC1163/LTC1165 inputs have been designed to accommodate a wide range of 3V and 5V logic families.The input threshold voltage is set at roughly 50% of the supply voltage and approximately 200mV of input hyster-esis is provided to ensure clean switching.The input enables all of the following circuit blocks: the bias generator, the high frequency oscillator and gate charge pump. Therefore, when the input is turned off, the entire circuit powers down and the supply current drops below 1µA.Standby Supply CurrentTEMPERATURE (°C)0S U P P L Y C U R R E N T (µA )5 4 3 2 1 0 –110203040LTC1163/65 • TPC07506070MOSFET Gate Drive CurrentGATE VOLTAGE ABOVE SUPPLY (V)1G A T E D R I V E C U R R E N T (µA )1010010004680.1210LTC1163/65 • TPC09Supply Current per Driver ONTEMPERATURE (°C)0S U P P L Y C U R R E N T (µA )300 250200150 100 50 010203040LTC1163/65 • TPC08506070/5LTC1163/LTC1165OPERATIOUGate Charge PumpGate drive for the power MOSFET is produced by an internal charge pump circuit which generates a gate volt-age substantially higher than the power supply voltage.The charge pump capacitors are included on chip and therefore no external components are required to generate gate drive.Controlled Gate Rise and Fall TimesWhen the input is switched ON and OFF, the gate is charged by the internal charge pump and discharged in a controlled manner. The charge and discharge rates have been set to minimize RFI and EMI emissions.BLOCK DIAGRA W(One Channel)APPLICATIO S I FOR ATIOW UU U Logic-Level MOSFET SwitchesThe LTC1163/LTC1165 are designed to operate with logic-level N-channel MOSFET switches. Although there is some variation among manufacturers, logic-level MOSFET switches are typically rated with V GS = 4V with a maximum continuous V GS rating of ±10V. R DS(ON) and maximum V DS ratings are similar to standard MOSFETs and there is generally little price differential. Logic-level MOSFETs are frequently designated by an “L” and are usually available in surface mount packaging. Some logic-level MOSFETs are rated with V GS up to ±15V and can be used in applications which require operation over the entire 1.8V to 6V range.Powering Large Capacitive LoadsElectrical subsystems in portable battery-powered equip-ment are typically bypassed with large filter capacitors to reduce supply transients and supply induced glitching. If not properly powered however, these capacitors may themselves become the source of supply glitching.For example, if a 100µF capacitor is powered through a switch with a slew rate of 0.1V/µs, the current during start-up is:I START = C(∆V/∆t)= (100 × 10–6)(1 × 105)= 10AObviously, this is too much current for the regulator (or output capacitor) to supply and the output will glitch by as much as a few volts.The startup current can be substantially reduced by limit-ing the slew rate at the gate of an N-channel as shown in Figure 1. The gate drive output of the LTC1163/LTC1165is passed through a simple RC network, R1 and C1, which substantially slows the slew rate of the MOSFET gate to approximately 1.5 × 10–4V/µs. Since the MOSFET is operating as a source follower, the slew rate at the source is essentially the same as that at the gate, reducing the startup current to approximately 15mA which is easilyGATEINPUT6LTC1163/LTC1165APPLICATIO S I FOR ATIOW UU U Figure 1. Powering a Large Capacitive Loadon a 3.3V supply which is compatible with 5V TTL and CMOS logic. (The LTC1163/LTC1165 cannot however, be driven by 3V logic when powered from a 5V supply because the threshold is approximately 2.5V.)TYPICAL APPLICATIO SUPCMCIA Card 3.3V/5V V CC SwitchNOTE: USE LTC1163 WITH NONINVERTING PCMCIA CONTROLLERSmanaged by the system regulator. R2 is required to eliminate the possibility of parasitic MOSFET oscillations during switch transitions. It is a good practice to isolate the gates of paralleled MOSFETs with 1k resistors to decrease the possibility of interaction between switches.Mixed 5V/3V SystemsBecause the input ESD protection diodes are referenced to ground instead of the supply pin, it is possible to drive the LTC1163/LTC1165 inputs from 5V CMOS or TTL logic even though the LTC1163/LTC1165 are powered from a 3.3V supply as shown in Figure 2. The input threshold voltage is approximately 50% of the supply voltage or 1.6VReverse Battery ProtectionThe LTC1163/LTC1165 can be protected against reverse battery conditions by connecting a 150Ω resistor in series with the ground pin or supply pin. The resistor limits the supply current to less than 24mA with –3.6V applied.Because the LTC1163/LTC1165 draw very little currentwhile in normal operation, the drop across the resistor is minimal. The 3.3V µP (or control logic) can be protected by adding 10k resistors in series with the input pins.Figure 2. Direct Interface to 5V LogicV IN/7LTC1163/LTC1165Information furnished by Linear Technology Corporation is believed to be accurate and reliable.However, no responsibility is assumed for its use. Linear Technology Corporation makes no represen-tation that the interconnection of its circuits as described herein will not infringe on existing patent rights.TYPICAL APPLICATIO SU2-Cell to 3.3V, 5V and 12V High-Side Switch/Converterwith 0.01µA Standby Current3.3VµF3.3VUltra-Low Drop Triple 3.3V High-Side SwitchPCMCIA Card Socket V PP Switch/ReglatorV CC MMDF3N02HDPP = 0V, 3.3V,EN0 0 1 0 1EN1 0 0 1 1OUTPUT 0V 12V V CC HI-Z8LTC1163/LTC1165Linear Technology Corporation1630 McCarthy Blvd., Milpitas, CA 95035-7487(408) 432-1900 qFAX : (408) 434-0507 qTELEX : 499-3977© U SA OPPLICATITYPICAL S8 Package 8-Lead Plastic SOICPACKAGE DESCRIPTIO U3-Cell to 3.3V Ultra-Low Drop Regulator with 2 Ramped SwitchesµFMixed Voltage High- and Low-Side SwitchesN8 Package 8-Lead Plastic DIPDimensions in inches (millimeters) unless otherwise noted.–0.3818.2550.053 – 0.069 BSC/分销商库存信息:LINEAR-TECHNOLOGYLTC1163CS8#PBF LTC1165CN8LTC1165CN8#PBF LTC1165CS8LTC1165CS8#PBF LTC1163CS8LTC1165CS8#TR LTC1165CS8#TRPBF LTC1163CS8#TR LTC1163CS8#TRPBF LTC1163CN8LTC1163CN8#PBF。

差分信号

1 简介简介简介简介无屏蔽双绞线(UTP),比如超五类线(Cat-5e),最初主要设计用于局域网(LAN)传输,因为其具有良好的性能和较低的成本,现已成为其他许多信号传输应用的经济型解决方案。

标准的Cat-5e 线缆中有4 对双绞线,在宽带视频信号的传输系统中,可以采用 4 对双绞线中的3对来传输RGB(红、绿、蓝)的电脑视频信号或YPbPr(亮度和两个色差)的高清分量视频信号。

所需的水平和垂直同步脉冲可以在视频信号消隐间隔中嵌入,也可以在3对双绞线中作为差分信号的共模来传输。

目前,模拟宽频带视频信号主要有RGB信号和高清分量视频信号(YPbPr)量大类。

这些信号在使用标准的四对差分对的UTP 传输线来进行长距离传输时会产生信号质量下降的问题。

一方面是由于传输的“表皮效应”而产生的非线性的带宽限制,从而导致信号弥散和信号的高频成分丢失。

这会使图像的锐度降低,并产生拖尾现象。

另外,由于电缆阻抗损耗引起的低频信号衰减会降低图像的对比度。

还有,由于双绞线扭曲率的不一致会导致三路差分对的传输线长度的不同,从而使三路接收信号的延时不一致,造成图像出现颜色误差。

为了解决以上几个问题,ADI 公司提出了基于UTP 视频传输的自动补偿系统的参考设计,可以针对这些问题来自动进行EQ 补偿和Skew补偿。

22 硬件设计硬件设计硬件设计硬件设计本参考设计整体系统分为两个部分:发送端(Driver Board)和接收端(Receiver Board)。

视频信号通过VGA 接口进入发送端,将单端的RGB 信号调理为差分信号,并将行/场同步信号调制为信号的共模,然后通过UTP(Unshielded Twisted Pair)线来进行长距离传输(通常使用非交叉式网线Cat-5e 即可)。

接收端需要将差分信号转化为单端信号,同时提取行/ 场同步信号。

由于长距离的传输会产生信号衰减和RGB信号不同步的问题,所以在接收端还需要进行EQ补偿和Skew补偿。

控制和配电箱 8146 5 系列使用说明书

控制和配电箱8146/5 系列使用说明书其他语种 ENFRITESRUNLDKSEFIPTGRPLCZSKHUSLROBGLVLTEECHKRCN –保存以备将来使用!–内容目录2控制和配电箱8146/5 系列内容目录1总体信息...............................................................................................................31.1制造商..................................................................................................................31.2关于本使用说明书................................................................................................31.3其他文档...............................................................................................................31.4标准和规定的符合性.............................................................................................32符号说明...............................................................................................................42.1本使用说明书中的符号.........................................................................................42.2设备上的符号.......................................................................................................43安全......................................................................................................................53.1设计用途...............................................................................................................53.2人员资格...............................................................................................................53.3残余风险...............................................................................................................64运输和仓储...........................................................................................................85产品选择、项目设计和修改..................................................................................95.1增加钻孔.............................................................................................................105.2外部的加装组件 (电缆接头、堵头、呼吸阀)..................................................116安装和装配.........................................................................................................126.1安装/拆卸..........................................................................................................126.2装配....................................................................................................................137调试....................................................................................................................178维护、保养、修理..............................................................................................188.1维护....................................................................................................................188.2保养....................................................................................................................188.3修理....................................................................................................................189退回....................................................................................................................1810清洁....................................................................................................................1911废弃物处置.........................................................................................................1912附件和备件.........................................................................................................1913附录A................................................................................................................2013.1技术数据.............................................................................................................2014附录B................................................................................................................2114.1尺寸信息/固定尺寸 (21)279557 / 81466953002023-03-23·BA00·III·zh·10总体信息3控制和配电箱8146/5 系列1总体信息1.1制造商1.2关于本使用说明书▶在使用前必须认真阅读本使用说明书,尤其是安全提示。

AD7896AR_12位AD转换中文资料-力通

AD7896AR:12位A/D转换器。

中文资料2010年5月译者:海克医疗QQ:21404945 性能介绍:内置:采样、保持电路,逐次比较转换片内时钟;最大转换频率:100 KHz;连续转换时间:8μS;8引脚;双列直插式封装DIP和贴片SOIC封装;高速,操作简单、串口输出;12位串口输出;单电源供电: +2.7 V 至 +5.5 V模拟电压输入范围:0 V 至 VDD高输入阻抗:约500KΩ;低的能耗:典型值:9 mW ;最大输出功率:450 mW说明:VDD也作为模拟量输入的基准电压;精度:当电压VDD = 5 V ± 10%,输出精度:±4 LSB max非线性:±1LSB max输入电流:±10 μA max(相当输入电阻:500KΩ);输入电容:10 pF max;串口通信时:高电位:2.4 V min,低电位:0.4 V max通信驱动电流:ISOURCE = 2 mA;ISINK = 2 mA转换时间:模态 1 操作8或8.5 μs max;模态 2操作14或14.5 μs max转换率 : 模态 1 操作120或117KHz max;模态 2操作71KHz maxSCLK 最大值频率是 10MHz。

AD7896引脚功能:1 模拟电压输入端,输入范围是: 0 V至VDD。

2 VDD正电源输入端, 输入范围是:+2.7 V至5.5 V 的。

(最大极限输入范围:-0.3至+7V)3 AGND 模拟地。

4 SCLK 时钟输入。

一个外部的时钟脉冲是应用对转换后的数字读入时。

下边缘时钟时读出数据。

其中高电平最少保持10ns。

(注:A/D7896内部的寄存器是在下降沿时输出。

对于上位单片机而言,应在上升沿时“读入数据:)5 SDATA 转换后数据输出。

16位数据被读出,其中12位有效数字,最前面的4位无效数字被补0,当16位数字全被读出后。

SDADT进入三态状态。

ADS7846中文规格书-new

电压

内部基准 -

温漂

静态电流 -

外部基准输入

输入电压 -

范围

输入阻抗 内部基准电路停止

内部基准电路启用

电池电压监测

电压输入 -

范围

输入阻抗 采样电池电压

关闭电池电压监测

准确率

外部基准 2.5V

内部基准

温度检测

温度测量 -

范围

分辨率

差动模式(3)

准确率

TEMP0(4) 差动模式(3)

TEMP0(4)

数字输入/输出

电源电压在 2.7V 时功耗的典型值为 0.75mW (关闭内部基准), 转换速率为 125kHz,ADS7846芯片是电 池供电系统的理想选择,譬如 PDAs 与属于触摸屏、传呼器、手机和其它便携式的设备。ADS7846 有 TSSOP16、QFN16 和 VFBGA48 等封装形式,可在–40℃+85℃温度范围内工作。

-40

85

℃

注释:(1)LSB 是最低有效位,当 VREF=+2.5V 时 1LSB=610μV;(2)超过 50mA 的源电流将导致

器件性能降低;(3)差动模式下,测量 TEMP0 和 TEMP1 间的电压差;(4)TEMP0 模式下温漂为-2.1mV/℃;

(5)ADS7846 在 2.2V 的电源电压下,数字部分将停止工作。

F81216AD中文资料

F81216AD

F81216AD

LPC to 4 UART + 9-bit Protocol

Release Date: July, 2008 Version: V0.20P

F81216AD.

July, 2008 V0.20P

元器件交易网

F81216AD.

July, 2008 பைடு நூலகம்0.20P

元器件交易网

F81216AD

Table of Content

1. General Description.................................................................................................................................1 2. Feature List..............................................................................................................................................1 3. Pin Configuration ....................................................................................................................................2 4. Pin Description........................................................................................................................................3 4.1 ISA/LPC Interface ................................................................................................................................. 3 4.2 UART Interface...................................................................................................................................... 4 4.3 Power ..................................................................................................................................................... 7 5. Functional Description ............................................................................................................................8 5.1 LPC Interface ...................................................................................................................................... 8 5.2 UART.................................................................................................................................................. 8 5.3 IR Function ....................................................................................................................................... 13 5.4 Watch Dog Timer Function............................................................................................................... 13 5.5 Serial IRQ ......................................................................................................................................... 14 6. Register Description......................................................................................................................17 6.1. Global Control Registers............................................................................................................... 19 6.2. UART1 Registers (CR00) ............................................................................................................. 21 6.3. UART2 Registers (CR01) ............................................................................................................. 25 6.4. UART3 Registers (CR02) ............................................................................................................. 28 6.5. UART4 Registers (CR03) ............................................................................................................. 31 6.6. Watchdog Timer Registers (CR08) ............................................................................................... 34 7. Electron Characteristic .......................................................................................................................36 7.1 Absolute Maximum Ratings ............................................................................................................. 36 7.2 DC Characteristics ............................................................................................................................... 36 8. Ordering Information .........................................................................................................................37 9. Package Dimensions ..........................................................................................................................38 10. Application Circuit ...........................................................................................................................39

AD8386资料

10-Bit, 12-Channel OutputDecimating LCD DriverAD8386 Rev. 0Information furnished by Analog Devices is believed to be accurate and reliable. However, noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, N orwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113 © 2005 Analog Devices, Inc. All rights reserved.FEATURESHigh voltage driveTo within 1.3 V of supply railsOutput short-circuit protectionHigh update ratesFast, 100 Ms/s 10-bit input data update rateStatic power dissipation: 1.4 WVoltage-controlled video reference (brightness), offset,and full-scale (contrast) output levelsINV bit reverses polarity of video signal3.3 V logic, 9 V to 18 V analog suppliesHigh accuracy voltage outputsLaser trimming eliminates the need for adjustments orcalibrationFlexible logicXFR allows parallel AD8386 operationFast settling into capacitive loads35 ns settling time to 0.25% into 150 pF loadSlew rate 400 V/μsAvailable in 64-lead 9 mm × 9 mm LFCSP_VQGENERAL DESCRIPTIONThe AD8386 provides a fast, 10-bit, latched, decimating digital input that drives 12 high voltage outputs. Input words with10 bits are loaded sequentially into 12 separate high speed, bipolar DACs. Flexible digital input format allows severalAD8386s to be used in parallel in high resolution displays. The output signal can be adjusted for dc reference, signal inversion, and contrast for maximum flexibility.The AD8386 is fabricated on ADI’s fast bipolar, 26 V XFHV process, which provides fast input logic, bipolar DACs with trimmed accuracy and fast settling, high voltage, precision drive amplifiers on the same chip.The AD8386 dissipates 1.4 W nominal static power.The AD8386 is offered in a 64-lead 9 mm × 9 mm LFCSP_VQ package and operates over the commercial temperature range of 0°C to 85°C. FUNCTIONAL BLOCK DIAGRAMVID0VID1VID2VID3VID4VID5VID6VID7VID8VID9VID10VID11VAO5687-1Figure 1.AD8386Rev. 0 | Page 2 of 20TABLE OF CONTENTSFeatures..............................................................................................1 General Description.........................................................................1 Functional Block Diagram..............................................................1 Revision History...............................................................................2 Specifications.....................................................................................3 DecDriver® Section.......................................................................3 Serial Interface Section................................................................5 Absolute Maximum Ratings............................................................6 Maximum Power Dissipation.....................................................6 Overload Protection.....................................................................6 Exposed Paddle.............................................................................6 ESD Caution..................................................................................6 Operating Temperature Range...................................................7 Pin Configuration and Function Descriptions.............................8 DecDriver Block Diagram and Timing........................................10 Serial Interface Block Diagram and Timing...............................12 Functional Description..................................................................13 Reference and Control Input Descriptions.............................13 Transfer Function and Analog Output Voltage......................13 Accuracy......................................................................................14 3-Wire Serial Interface...............................................................14 Output Operating Modes..........................................................14 Overload Protection...................................................................14 Applications.....................................................................................15 Optimized Reliability with the Thermal Protection Circuit 15 Operation in High Ambient Temperature..............................15 Power Supply Sequencing.........................................................15 Grounded Output Mode During Power-Off..........................15 Typical Application Circuits.....................................................16 PCB Design for Optimized Thermal Performance...............17 AD8386 PCB Design Recommendations...............................17 Outline Dimensions.......................................................................19 Ordering Guide.. (19)REVISION HISTORY8/05—Revision 0: Initial VersionAD8386Rev. 0 | Page 3 of 20SPECIFICATIONSDECDRIVER® SECTIONAt 25°C, AVCC = 15.5 V , DVCC = 3.3 V , T A MIN = 0°C, T A MAX = 85°C, VRH = 9.5 V , VRL = 7 V , unless otherwise noted. Table 1.Parameter Conditions Min Typ Max Unit VIDEO DC PERFORMANCE 1T A MIN to T A MAX VDE DAC Code 450 to 800 −7.5 +7.5 mV VCME DAC Code 450 to 800 −3.5 +3.5 mV VIDEO OUTPUT DYNAMIC PERFORMANCE T A MIN to T A MAX , C L = 150 pF Data Switching Slew Rate 20% to 80%, V O = 5 V step 400 V/μs Invert Switching Slew Rate 20% to 80%, V O = 10 V step 560 V/μs Data Switching Settling Time to 1% 24 35 ns Data Switching Settling Time to 0.25% 35 50 ns Invert Switching Settling Time to 1% 80 130 ns Invert Switching Settling Time to 0.25% 250 500 ns Invert Switching Overshoot 10 V Step 100 200 mVCLK and Data Feedthrough 215 mV p-p All-Hostile Crosstalk 3 Amplitude 50 mV p-p Glitch Duration 30 ns DAC Transition Glitch Energy DAC code 511 to 512 0.6 nV-s VIDEO OUTPUT CHARACTERISTICS Output Voltage Swing AVCC − VOH, VOL − AGND 1.1 1.3 V Output Voltage—Grounded Mode 200 mVData Switching Delay: t 945 V step 12 14 16 ns INV Switching Delay: t 10510 V step 15 17 19 ns Output Current 100 mA Output Resistance 29 Ω REFERENCE INPUTS VRL Range VRH ≥ VRL 5.25 AVCC − 4 V VRH Range VRH ≥ VRL VRL AVCC V VRH – VRL Range VFS = 2 × (VRH − VRL) 0 2.75 V VRH Input Resistance To VRL 20 kΩ VRL Input Current −45 μA VRH Input Current 125 μA RESOLUT ON Coding Binary 10 Bits DIGITAL INPUT CHARACTERISTICS C IN 3 pF I IH 0.05 μA I IL −2 μA V IH 2 V V IL 0.8 V V TH 1.65 V I IH TSW 330 μA I IL TSW −2 μA TSW R PULLDOWN 10 kΩAD8386Rev. 0 | Page 4 of 20Parameter Conditions Min Typ Max Unit DIGITAL TIMING CHARACTERISTICS T A MIN to T A MAX Maximum Input Data Update Rate 100 Ms/s Data Setup Time: t 1 1 ns XFR Setup Time: t 3 0 ns INV Setup Time: t 11 0 ns Data Hold Time: t 2 3.5 ns XFR Hold Time: t 4 4.5 ns INV Hold Time: t 12 4 ns CLK High Time: t 7 6 ns CLK Low Time: t 8 4 ns1 VDE = differential error voltage. VCME = common-mode error voltage. Full-scale output voltage = VFS =2 × (VRH − VRL). See the Accuracy section. 2Measured on two outputs differentially as CLK and DB (0:9) are driven and XFR is held low. 3Measured on two outputs differentially as the others are transitioning by 5 V. Measured for both states of INV. 4Measured from 50% of rising CLK edge to 50% of output change. Measurement is made for both states of INV. 5Measured from 50% of rising CLK edge, which follows a valid XFR, to 50% of output change. See Figure 6 for the definition.AD8386Rev. 0 | Page 5 of 20SERIAL INTERFACE SECTIONAt 25°C, AVCC = 15.5 V , DVCC = 3.3 V , T A MIN = 0°C, T A MAX = 85°C, VRH = 9.5 V , VRL = 7 V , unless otherwise noted. Table 2.Parameter Conditions Min Typ Max Unit SERIAL DAC DC PERFORMANCE DNL SVFS = 5 V −1 +1 LSB INL SVFS = 5 V −1.5 +1.5 LSB Output Offset Error −2.0 +2.0 LSB Scale Factor Error −3.0 +3.0 LSB SERIAL DAC OUTPUT DYNAMIC PERFORMANCE To 0.5% VAO Settling Time, t 26 C L = 100 pF 1 2 μs VAO Settling Time, t 26 C L = 33 μF 15 ms SERIAL DAC OUTPUT CHARACTERISTICS VAO Maximum SVRH − 1 LSB V VAO Minimum SVRL V VAO − Grounded Mode 150 mV VAO Output Resistance All supplies OFF 75 kΩ I OUT ±30 mAC LOAD Low Range 10.002 μFC LOAD High Range 10.047 μF REFERENCE INPUTS SVRH Range SVRL < SVRH SVRL + 1 AVCC − 3.5 V SVRL Range SVRL < SVRH AGND + 1.5 SVRH − 1 V SVFS Range 1 8 V SVRH Input Current SVRS = 5 V 0.1 μA SVRL Input Current SVRS = 5 V −1.6 −1.3 mA DIGITAL INPUT CHARACTERISTICS C IN 3 pF I IH 0.05 μA I IL −1 μA V IH 2.0 DVCC V V IL DGND 0.8 V V TH 1.65 V DIGITAL TIMING CHARACTERISTICS T A MIN to T A MAX SEN to SCL Setup Time, t 20 10 ns SCL, High Level Pulse Width, t 21 10 ns SCL, Low Level Pulse Width, t 22 10 ns SCL to SEN Hold Time, t 23 10 ns SDI Setup Time, t 24 10 ns SDI Hold Time, t 25 10 ns POWER SUPPLIES DVCC, Operating Range 3 3.3 3.6 V DVCC, Quiescent Current 54 75 mA AVCC Operating Range 9 18 V Total AVCC Quiescent Current 80 100 mA OPERATING TEMPERATURESAmbient Temperature Range, T A 2Still air, TSW = HIGH 0 70 °CAmbient Temperature Range, T A 2Still air, TSW = LOW 0 85 °C1Output VAO is designed to drive capacitive loads less than 0.002 μF or more than 0.047 μF. Load capacitances in the range 0.002 μF − 0.047 μF cause the outputovershoot to exceed 100 mV. 2Operation at high ambient temperature requires a thermally optimized PCB layout (see the Applications section). In systems with limited or no airflow, the maximum ambient operating temperature is limited to 70°C with the thermal protection enabled, VFS = 4 V, data update rate = 85 Ms/s. Operation at 85°C ambient temperature requires the thermal protection circuit turned disabled (TSW = LOW).AD8386Rev. 0 | Page 6 of 20ABSOLUTE MAXIMUM RATINGSTable 3.Parameter RatingSupply VoltageAVCCx − AGNDx 18 VDVCC − DGND 4.5 VInput VoltageMaximum Digital Input Voltage DVCC + 0.5 VMinimum Digital Input Voltage DGND − 0.5 VMaximum Analog Input Voltage AVCC + 0.5 VMinimum Analog Input Voltage AGND − 0.5 V Internal Power Dissipation 1 LFCSP @ T A = 25°C 3.7 WOperating Temperature Range 0°C to 85°CStorage Temperature Range –65°C to +125°CLead Temperature Range (Soldering 10 sec) 300°C Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.164-lead VQ_LFCSP:θJA = 27°C/W in still air (JEDEC STD, 4-layer PCB with 16 vias on Epad)θJA = 25°C/W @ 200 lfm airflow (JEDEC STD, 4-layer PCB with 16 vias on Epad) θJA = 24°C/W @ 400 lfm airflow (JEDEC STD, 4-layer PCB with 16 vias on Epad) ΨJT = 0.2°C/W in still air (JEDEC STD, 4-layer PCB with 16 vias on Epad) ΨJB = 13.8°C/W in still air (JEDEC STD, 4-layer PCB with 16 vias on Epad)MAXIMUM POWER DISSIPATIONThe maximum power that can be safely dissipated by theAD8386 is limited by its junction temperature. The maximumsafe junction temperature for plastic encapsulated devices, asdetermined by the glass transition temperature of the plastic, isapproximately 150°C. Exceeding this limit temporarily maycause a shift in the parametric performance due to a change inthe stresses exerted on the die by the package. Exceeding ajunction temperature of 175°C for an extended period canresult in device failure.OVERLOAD PROTECTION The AD8386 overload protection circuit consists of an outputcurrent limiter and a thermal protection circuit.When TSW is LOW , the thermal protection circuit is disabled,and the output current limiter is turned on. The maximumcurrent at any one output of the AD8386 is internally limited to 100 mA average. In the event of a momentary short circuit between a video output and a power supply rail (AVCC or AGND), the output current limit is sufficiently low to provide temporary protection.When TSW is HIGH, the output current limiter, as well as the thermal protection circuit, is turned on. The thermal protection circuit debiases the output amplifier when the junctiontemperature reaches the internally set trip point. In the event of an extended short circuit between a video output and a power supply rail, the output amplifier current continues to switch between 0 mA and 100 mA typical with a period determined by the thermal time constant and the hysteresis of the thermal trip point. The thermal protection circuit limits the average junction temperature to a safe level, which provides long-term protection.EXPOSED PADDLETo ensure optimal thermal performance, the exposed paddle must be electrically connected to an external plane, such as AVCC or GND, as described in the Applications section.ESD CAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performancedegradation or loss of functionality.AD8386Rev. 0 | Page 7 of 20OPERATING TEMPERATURE RANGEThe maximum operating junction temperature is 150°C. The junction temperature trip point of the thermal protection circuit is 165°C. Production tests guarantee a minimum junction temperature trip point of 125°C.Consequently, the maximum guaranteed operating junction temperature is 125°C when the thermal protection circuit is enabled and 150°C when the thermal protection circuit is disabled.To ensure operation within the specified operating temperature range, it is necessary to limit the maximum power dissipation as()()59.009.0lfm in Airflow T T P Air Still JA A JMAX DMAX ×−θ−≈M A X I M U M P O W E R D I S S I P A T I O N (W )AMBIENT TEMPERATURE (°C)OVERLOADFigure 2. Maximum Power Dissipation vs. TemperatureThe AD8386 is on a 4-layer JEDEC PCB with a thermally optimized landing pattern with 16 vias.The quiescent power dissipation of the AD8386 is 1.4 W . When driving a 12-channel 720p HDTV panel with an input capacitance of 150 pF, the AD8386 dissipates 1.66 W whendisplaying 1 pixel wide alternating white and black vertical lines generated by a standard 720p HDTV input video. Conditions include the following: • AVCC = 15.5 V • DVCC = 3.3 V • VFS = 5 V • C L = 150 pF• f PIXEL = 74.25 MHz• Black-to-white transition = 4 V • Active video time = 75%Figure 2 shows these power dissipations.AD8386Rev. 0 | Page 8 of 20PIN CONFIGURATION AND FUNCTION DESCRIPTIONS17181920212223242526272829303132G S W T S W D V C C D G N D A G N D S S V R L S V R L S V R H V A O A V C C S B Y P A G N D 11V I D 11A V C C 10, 11V I D 10A G N D 9, 1064636261605958575655545352515049D V C C D G N D C L K X F R I N V R /L T S T A A G N D D A V C C D V R H V R H V R L A G N D 0V I D 0A V C C 0, 1V I D 112345678910111213141516NC NC DB0DB1DB2DB3DB4DB5DB6DB7DB8DB9SDI SEN SCL GCTL AGND1, 2VID2AVCC2, 3VID3AGND3, 4VID4AVCC4, 5VID5AGND5, 6VID6AVCC6, 7VID7AGND7, 8VID8AVCC8, 9VID94847464544434241403938373635343305687-003Figure 3. 64-Lead LFCSP_VQ Pin ConfigurationAD8386Rev. 0 | Page 9 of 20Table 4. 64-Lead LFCSP_VQ Pin Function DescriptionsPin No. Mnemonic FunctionDescription1, 2 NCNo Connect No Internal Connection.3 to 12 DB0 to DB9 Data Input10-Bit Data Input. MSB = DB(9).13SDISerial Data InputWhile the SEN input is LOW, one 12-bit serial word is loaded into the serial DAC on the rising edges of the SCL.14 SEN Serial DAC Enable A falling edge of this input initiates a loading cycle. While this input is heldLOW, the serial DAC is enabled and data is loaded on every rising edge of SCL. The output is updated on the rising edge of a valid SEN. A valid SEN must remain LOW for at least three SCL cycles. While this input is held HIGH, the control DAC is disabled.15 SCL Serial Data Clock Serial Data Clock. 16 GCTL Output Mode Control When this input is HIGH, the output mode is determined by the functionprogrammed into the serial interface. When LOW, the output mode is controlled by the GSW input.17 GSW Output Mode Switch When GCTL is LOW and this input is HIGH, the video outputs and VAOoperate normally. When GCTL and this input are both LOW, the video outputs and VAO are asynchronously forced to AGND, regardless ofthe function programmed into the serial interface. This function operates when AVCC power is OFF but requires DVCC power supply to be ON.18 TSW Thermal Switch When this input is LOW, the thermal protection circuit is disabled. WhenHIGH, the thermal protection circuit is enabled. This pin has a 10 kΩ internal pull-down resistor.19, 64 DVCC Digital Power Supply Digital Power Supply. 20, 63 DGND Digital Ground Digital Supply Return. 21 AGNDS Analog Ground Analog Supply Return. 22, 23, 24 SVRL, SVRH Serial DAC Reference Voltage The voltage applied between these pins sets the serial DAC full-scale voltage. 25 VAO Serial DAC Output This output voltage is updated in the rising edge of the SEN input. 26 AVCCS Analog Power Supply Analog Power Supply. 27 BYP Bypass A 0.1 μF capacitor connected between this pin and AGND ensuresoptimum settling time. 28, 32, 36, 40, 44, 48, 52 AGND11 to AGND0Analog GroundAnalog Supply Returns. 29, 31, 33, 35, 37, 39, 41, 43, 45, 47, 49, 51VID11 toVID0 Analog Output These pins are directly connected to the analog inputs of the LCD panel. 30, 34, 38, 42, 46, 50 AVCC10, 11 to AVCC0, 1 Analog Power SupplyAnalog Power Supplies. 53 VRL Video Center Reference The voltage applied to this pin sets the video center voltage. The videooutputs are above this reference while the INV = HIGH and below this reference while INV = LOW.54, 55 VRH Full-Scale Reference The full-scale video output voltage is VFS = 2 × (VRH − VRL). 56 AVCCD Analog Power Supply Analog Power Supply. 57 AGNDD Analog Ground Analog Supply Return. 58 TSTA Test Pin Connect this pin to AGND. 59 R/L Right/Left Select A new data loading sequence begins on the left with Channel 0 whenthis input is LOW, and on the right with Channel 11 when this input is HIGH.60 I NV Invert When this input is HIGH, the VIDx output voltages are above VRL. WhenLOW, the VIDx outputs voltages are below VRL. The state of INV is latched on the first rising CLK edge after XFR is detected. The VIDx outputs change on the rising CLK edge after the next XFR is detected.61 XFR Transfer/Start Sequence The state of XFR is detected on the rising edge of CLK. Data is transferred tothe outputs and a new loading sequence begins on the next rising edge of CLK after XFR is detected HIGH.62 CLK Clock Video Data Clock.AD8386Rev. 0 | Page 10 of 20DECDRIVER BLOCK DIAGRAM AND TIMINGVID1VID3VID5VID7VID9VID11VID0VID2VID4VID6VID8VID10XFR CLK R/LBYPDB(0:9)VRH VRL05687-004Figure 4. AD8386 DecDriver Section05687-005Figure 5. Input Timing–VFSCLK DB(0:9)XFR INVVID(0:11)05687-006Figure 6. Output Timing (R/L LOW)Table 5.Parameter Conditions Min Typ Max Unit Data Setup Time, t 1 Input t r , t f = 2 ns 1 ns Data Hold Time, t 2 3.5 ns XFR Setup Time, t 3 0 ns XFR Hold Time, t 4 4.5 ns CLK High Time, t 7 6 ns CLK Low Time, t 8 4 ns Data Switching Delay, t 9 12 14 16 ns Invert Switching Delay, t 10 15 17 19 ns Invert Setup Time, t 11 0 ns Invert Hold Time, t 12 4 nsSERIAL INTERFACE BLOCK DIAGRAM AND TIMINGSVRH SVRL SDI SCL SENTSWGSWGCTLVAOVID(0:11)05687-007Figure 7. Serial Interface Block DiagramSCLSENSDI D11D10D9D8D7D6D5D4D3D2D1D0VAO05687-008Figure 8. Serial Interface Timing DiagramSENSCLSDIVAO05687-009Figure 9. Serial Interface Timing DiagramTable 6.Parameter Conditions Min Typ Max Unit SEN to SCL Setup Time, t 20 10 ns SCL, High Level Pulse Width, t 21 10 ns SCL, Low Level Pulse Width, t 22 10 ns SCL to SEN Hold Time, t 23 10 ns SDI Setup Time, t 24 10 ns SDI Hold Time, t 25 10 ns VAO Settling Time, t 26 SVFS = 5 V, to 0.5 %, C L = 100 pF 1 2 μs VAO Settling Time, t 26 SVFS = 5 V, to 0.5 %, C L = 33 μF 15 msFUNCTIONAL DESCRIPTIONThe AD8386 is a system building block designed todirectly drive the columns of LCD microdisplays of the type popularized for use in projection systems. It has 12 channels of precision, 10-bit digital-to-analog converters (DACs) loaded from a single high speed serial input. Precision current feedback amplifiers, which provide well-damped pulse response and fast voltage settling into large capacitive loads, buffer the 12 outputs. Laser trimming at the wafer level ensures low absolute output errors and tight channel-to-channel matching. Tight part-to-part matching in high resolution systems is guaranteed by the use of external voltage references.REFERENCE AND CONTROL INPUT DESCRIPTIONS Data transfer/start sequence control—input data loading, data transfer.A valid XFR control input initiates a new six-clock loading cycle, during which data is transferred to the outputs, and 12 input data-words are loaded sequentially into the 12 internal channels. Data is loaded on both the rising and falling edges of CLK. Data loaded from the previous cycle is transferred to the outputs on the rising CLK edge when the XFR is held HIGH at the preceding rising CLK edge only. A new loading sequence begins on the current rising CLK edge when XFR is held HIGH at the preceding rising CLK edge only.Right/left control—input data loading.To facilitate image mirroring, the direction of the loading sequence is set by the R/L control.A new loading sequence begins at Channel 0 and proceeds to Channel 11 when the R/L control is held LOW. It begins at Channel 11 and proceeds to Channel 0 when the R/L control is held HIGH.VRH, VRL inputs—full-scale video reference inputs.The full-scale output voltage is VFS = 2 × (VRH − VRL).INV control—analog output inversion.The analog voltage equivalent of the input code is subtracted from (VRL + VFS) while INV is held HIGH, and added to (VRL − VFS) while INV is held LOW.The state of the INV input is latched on the first rising edge of CLK, immediately following a valid XFR. The VIDx outputs invert on the first rising CLK edge, immediately following the next valid XFR.TSW control—thermal switch control.When this input is HIGH, the thermal protection circuit is enabled. When LOW or left unconnected, the thermal protection circuit is disabled. An internal 10 kΩ pull-down resistor disables the thermal switch when this pin is left unconnected.GCTL, GSW controls—output mode control.Table 7. GTCL, GSW Truth TableGTCL GSW Action0 0 All video outputs and VAO are forced nearAGND. While the outputs are disabled, AVCC canbe removed.0 1 All video outputs and VAO operate normally.1 X Output operating mode is controlled by theserial interface.TRANSFER FUNCTION AND ANALOG OUTPUT VOLTAGEThe DecDriver has two regions of operation where the video output voltages are either above or below the reference voltage VRL. The transfer function defines the video output voltage as the function of the digital input code asVIDx(n) = VRL + VFS × (1 − n/1023), for INV = HIGHVIDx(n) = VRL − VFS × (1 − n/1023), for INV = LOW where:n = input codeVFS = 2 × (VRH − VRL)A number of internal limits define the usable range of the video output voltages, VIDx, shown in Figure 10.VIDx– VOLTS(VRLVIDx vs. INPUT CODE≤ AVCC18VINTERNAL LIMITS ANDUSABLE VOLTAGE RANGES05687-10 Figure 10. Transfer Function and Usable Voltage RangesACCURACYTo best correlate transfer function errors to image artifacts, the overall accuracy of the DecDriver is defined by two parameters, VDE and VCME.VDE, the differential error voltage, measures the difference between the rms value of the output and the rms value of the ideal. The defining expression is()()()[]VFS n n VOUTP n VOUTN n VDE ×⎟⎠⎞⎜⎝⎛−−−=102312VCME, the common-mode error voltage, measures ½ the dc offset of the output. The defining expression is()()()⎥⎦⎤⎢⎣⎡−+=VRL n VOUTP n VOUTN n VCME 13-WIRE SERIAL INTERFACEThe serial interface controls the 8-bit serial DAC and the videooutput operating mode via a 12-bit serial word. The two most significant bits (MSB) select the function and the eight least significant bits (LSB) are the data for the serial DAC. Table 8. Bit DefinitionsBit Name Bit Functionality SD (0:7) 8-Bit SDAC Data. MSB = SD7. SD8 Not Used. SD9 Not Used. SD10 VAO Load Selection. SD11Output Mode Selection When GCTL = 1.Table 9. Truth Table @ GCTL = HIGHSEN SD Action 11 10 9 80 0 X X Normal Output Mode. No change to VAO.0 1 X X Normal Output Mode. Load VAO.1 0 X X Grounded Output Mode. No change to VAO.1 1 X X Grounded Output Mode. Load VAO.X X X X Start a Serial Interface Loading Cycle. No change to VAO.Table 10. Truth Table @ GCTL = LOWSE N SD Action 111098X 0 X X No Change to VAO.X 1 X X Load VAO.X X X X Start a Serial Interface Loading Cycle. Nochange to VAO.Serial DACThe serial DAC is loaded via the serial interface. The output voltage is determined byVAO = SVRL + (SVRH − SVRL ) × n /256 where n is the SD (0:7) serial input code.Output V AO is designed to drive capacitive loads less than 0.002 μF or more than 0.047 μF. Load capacitances in the0.002 μF − 0.047 μF range cause the output overshoot to exceed 100 mV .OUTPUT OPERATING MODESIn normal operating mode, the voltage of the video outputs isdetermined by the inputs.In grounded output mode, the video outputs are forced to (AGND + 0.2 V) typ.OVERLOAD PROTECTIONThe overload protection employs current limiters and a thermal protection circuit to protect the video output pins against accidental shorts between any video output pin and AVCC or AGND. The junction temperature trip point of the thermal protectioncircuit is 165°C. Production tests guarantee a minimum junction temperature trip point of 125°C. Consequently, the operating junction temperature should not rise above 125°C when the thermal protection circuit is enabled.For systems that operate at high internal ambient temperatures and require large capacitive loads to be driven by the AD8386 at high frequencies, junction temperatures above 125°C may be required. In such systems, the thermal protection circuit should either be disabled or a minimum airflow of 200 lfm must be maintained.APPLICATIONSOPTIMIZED RELIABILITY WITH THE THERMAL PROTECTION CIRCUITThe AD8386 is designed for enhanced reliability through features that provide protection against accidental shorts that may occur during PCB assembly repair, such as solder bridging, or during system assembly, such as a misaligned flat panel cable in the connector.While internal current limiters provide short-term protection against temporary shorts at the outputs, the thermal shutdown provides protection against persistent shorts lasting for several seconds. To optimize reliability, the following sequence of operations is recommended.Initial Power-Up after PCB Assembly or RepairDisable grounded output mode and enable thermal protection. Ensure that the GCTL and GSW pins are LOW and the TSW pin is HIGH upon initial power-up and remains unchanged throughout this procedure.•Execute the initial power-up.•Identify any shorts at the outputs.•Power-down, repair shorts, and repeat the initial power-up sequence until proper system functionality is verified. Power-Up during Normal OperationDisable grounded output mode and disable the thermal protection circuit using either of the following two methods: •GCTL = HIGH, TSW = HIGH and serial code0XXXXXXXXXXX sent immediately following a power-up, places all outputs into normal operating mode and disables the thermal protection circuit.•TSW = LOW disables the thermal protection circuit. GCTL = LOW and GSW = HIGH puts all outputs into normal operating mode.OPERATION IN HIGH AMBIENT TEMPERATURETo extend the maximum operating junction temperature of the AD8386 to 150°C, keep the thermal protection circuit disabled (TSW = LOW) during normal operation. POWER SUPPLY SEQUENCINGAs indicated in the Absolute Maximum Ratings section, the voltage at any input pin cannot exceed its supply voltage by more than 0.5 V. Power-on and power-off sequencing may be required to comply with the Absolute Maximum Ratings.Failure to comply with the Absolute Maximum Ratings may result in functional failure or damage to the internal ESD diodes. Damaged ESD diodes may cause temporary parametric failures, which may result in image artifacts. Damaged ESD diodes cannot provide full ESD protection, reducing reliability.The following power supply sequencing ensures that the Absolute Maximum Ratings are not violated.Power-on sequence is:•Turn ON AVCC and analog reference voltages.•Turn ON DVCC and digital signals.Power-off sequence is:•Turn OFF AVCC and analog reference voltages.•Turn OFF DVCC and digital signals.GROUNDED OUTPUT MODE DURING POWER-OFF Certain applications require that the video outputs be held near AGND during power-down. The following power-off sequence ensures that the outputs are near ground during power-off and the Absolute Maximum Ratings are not violated.•Enable grounded output mode in one of two ways:GTCL = LOW and GSW = LOW, or GCTL = HIGHand code 1XXXXXXXXXXX sent via the serial interface.•Turn OFF AVCC and analog reference voltages.•Turn OFF DVCC and digital signals.。

双通道、14位、80 msps 125 msps串行lvds 1.8 v模数转换器 - 应用说明书

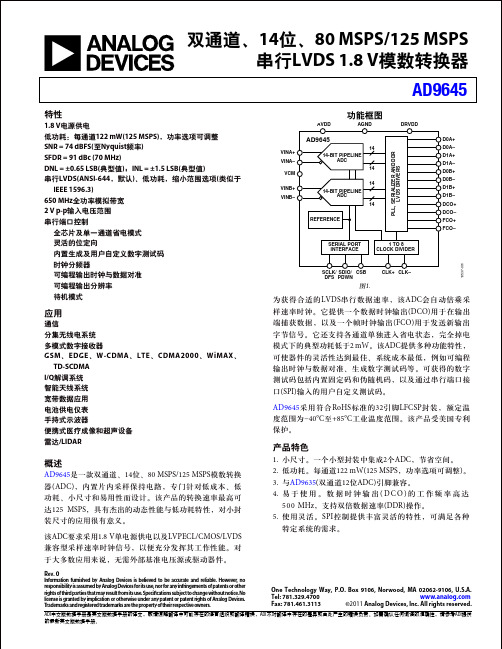

功能框图10537-001REFERENCEAD964514VINA+AVDDDRVDD1414VINB+VINB–D0A+14D0B+VINA–VCM D1A+D1B+AGNDD0A–D1A–D0B–D1B–DCO+DCO–FCO+FCO–14-BIT PIPELINEADC14-BIT PIPELINEADCP L L , S E R I A L I Z E R A N D D D R L V D S D R I V E R SSERIAL PORT INTERFACE 1 TO 8CLOCK DIVIDERSCLK/DFS SDIO/PDWNCSB CLK+CLK–图1.双通道、14位、80 MSPS/125 MSPS串行LVDS 1.8 V 模数转换器AD9645特性1.8 V 电源供电低功耗:每通道122 mW(125 MSPS),功率选项可调整 SNR = 74 dBFS(至Nyquist 频率) SFDR = 91 dBc (70 MHz)DNL = ±0.65 LSB(典型值);INL = ±1.5 LSB(典型值)串行LVDS(ANSI-644,默认)、低功耗,缩小范围选项(类似于 IEEE 1596.3)650 MHz 全功率模拟带宽 2 V p-p 输入电压范围 串行端口控制全芯片及单一通道省电模式 灵活的位定向内置生成及用户自定义数字测试码 时钟分频器可编程输出时钟与数据对准 可编程输出分辨率 待机模式应用通信分集无线电系统 多模式数字接收器GSM 、EDGE 、W-CDMA 、LTE 、CDMA2000、WiMAX 、 TD-SCDMA I/Q 解调系统 智能天线系统 宽带数据应用 电池供电仪表 手持式示波器便携式医疗成像和超声设备 雷达/LIDAR概述AD9645是一款双通道、14位、80 MSPS/125 MSPS 模数转换器(ADC),内置片内采样保持电路,专门针对低成本、低功耗、小尺寸和易用性而设计。

(2021年整理)adc0808中文资料

adc0808中文资料编辑整理:尊敬的读者朋友们:这里是精品文档编辑中心,本文档内容是由我和我的同事精心编辑整理后发布的,发布之前我们对文中内容进行仔细校对,但是难免会有疏漏的地方,但是任然希望(adc0808中文资料)的内容能够给您的工作和学习带来便利。

同时也真诚的希望收到您的建议和反馈,这将是我们进步的源泉,前进的动力。

本文可编辑可修改,如果觉得对您有帮助请收藏以便随时查阅,最后祝您生活愉快业绩进步,以下为adc0808中文资料的全部内容。

11.2。

4 典型的集成ADC芯片为了满足多种需要,目前国内外各半导体器件生产厂家设计并生产出了多种多样的ADC芯片。

仅美国AD公司的ADC产品就有几十个系列、近百种型号之多.从性能上讲,它们有的精度高、速度快,有的则价格低廉.从功能上讲,有的不仅具有A/D转换的基本功能,还包括内部放大器和三态输出锁存器;有的甚至还包括多路开关、采样保持器等,已发展为一个单片的小型数据采集系统。

尽管ADC芯片的品种、型号很多,其内部功能强弱、转换速度快慢、转换精度高低有很大差别,但从用户最关心的外特性看,无论哪种芯片,都必不可少地要包括以下四种基本信号引脚端:模拟信号输入端(单极性或双极性);数字量输出端(并行或串行);转换启动信号输入端;转换结束信号输出端。

除此之外,各种不同型号的芯片可能还会有一些其他各不相同的控制信号端.选用ADC芯片时,除了必须考虑各种技术要求外,通常还需了解芯片以下两方面的特性.(1)数字输出的方式是否有可控三态输出。

有可控三态输出的ADC 芯片允许输出线与微机系统的数据总线直接相连,并在转换结束后利用读数信号RD选通三态门,将转换结果送上总线。

没有可控三态输出(包括内部根本没有输出三态门和虽有三态门、但外部不可控两种情况)的ADC芯片则不允许数据输出线与系统的数据总线直接相连,而必须通过I/O接口与MPU交换信息。

(2)启动转换的控制方式是脉冲控制式还是电平控制式.对脉冲启动转换的ADC芯片,只要在其启动转换引脚上施加一个宽度符合芯片要求的脉冲信号,就能启动转换并自动完成。

检测复习题 - 修改综述

第一预备专题(28)1.51和52原型单片机的三条主要区别是什么?51单片机有T0和T1有两个定时器52单片机有T0,T1,T2三个定时器51单片机 128 RAM 52单片机 256 RAM51单片机 4K ROM 52单片机 8K ROM2.51兼容单片机机器周期时钟较少的有哪些型号?STC12C54XX 一个TI的MSC1210 四个Winbond的W77E58 四个3.STC12C系列单片机速度快到什么程度?35MHz4.STC12C系列单片机有PWM吗?有5.STC12C系列单片机能在系统编程吗?能6.STC12C系列单片机用什么方法在系统编程?有串行接口7.STC12C系列单片机自带复位吗?带8.什么51系列单片机有双串口?Winbond的W77E58,STC12C5A60S29.I2C总线有哪些线?时钟线,数据线10.SPI总线有哪些线?输入数据线,输出数据线,时钟线,片选控制线11.I2C和SPI总线哪个快?SPI快12.51原型单片机的管脚驱动能力各个口有什么差别,是多少?P0口低电平3.2 mA,高电平80uA,P1~P3口低电平1.6 mA,高电平80uA13.如果单片机的PWM只有8位,要扩展为11位,如果PWM分为0,1,2,3,4,5,6和7个时间段依次反复循环,PWM的DA变换值为961,各个时间段的PWM值应为多少?961/8=120 (1)14.AduC812/814/816的AD变换器有什么区别?ADuC812 8通道 12位AD 采样率200ks/s,快ADuC814 6通道 12位AD 采样率247ks/s,快ADuC816 两个16位AD 采样速度慢15.MSC1210的PWM有多少位?16位16.MSC1210的PWM有几个通道?1个17.如果你使用MSC1210,那么理由是什么?AD精度高,带16位PWM,精密18.在有AD变换器的51系列单片机中那种位数最多,精度最高,那种通道最多?MCS121019.相对于51系列单片机,Microchip的PIC单片机和Ti的MSP单片机有什么长处?功耗低20.在什么情况下你必须选择具有在系统下载程序功能的单片机?使用贴片封装的单片机21.哪些51系列单片机没有双列直插和PLCC封装?MCS1210,ADuC812/814/81622.为什么建议51系列的晶振频率取1.8432MHz的整倍数?有哪两条理由?获得标准的波特率,获得标准的秒分频23.通常可获得的1.8432MHz整倍数的晶振有哪4种?3.6864 MHz; 11.0592MHz;18.432 MHz;22.1184MHz24.为什么建议不要用阻容复位电路,而要用复位芯片,他们的功能上有什么差别?阻容复位电路只能上电复位,不能掉电复位,掉电时数据可能被破坏25.为什么在设计含有单片机的仪器时要尽量采用串行器件?系统单片化,不扩地址线、数据线。

AD168矩阵说明书(编程手册)

系统操作员任务 .................................................................................................................................1-3

谁使用本手册 .........................................................................................................................................vii

如何使用本手册 .....................................................................................................................................vii

触摸追踪器,American Dynamics 是由Sensormatic电子公司注册的商标.这里讲述的产 品可以是其他公司的

目录

关于本手册 ................................................................................................................VII

ADS7846

VBAT AUX

Battery Monitor

DCLK DIN

VREF

Internal 2.5V Reference

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2

ADS7846

SBAS125H

ELECTRICAL CHARACTERISTICS

At TA = –40°C to +85°C, +VCC = +2.7V, VREF = 2.5V internal voltage, fSAMPLE = 125kHz, fCLK = 16 • fSAMPLE = 2MHz, 12-bit mode, and digital inputs = GND or +VCC, unless otherwise noted. ADS7846E PARAMETER ANALOG INPUT Full-Scale Input Span Absolute Input Range Capacitance Leakage Current SYSTEM PERFORMANCE Resolution No Missing Codes Integral Linearity Error Offset Error Gain Error Noise Power-Supply Rejection SAMPLING DYNAMICS Conversion Time Acquisition Time Throughput Rate Multiplexer Settling Time Aperture Delay Aperture Jitter Channel-to-Channel Isolation SWITCH DRIVERS On-Resistance Y+, X+ Y–, X– Drive Current(2) REFERENCE OUTPUT Internal Reference Voltage Internal Reference Drift Quiescent Current REFERENCE INPUT Range Input Impedance CONDITIONS Positive Input-Negative Input Positive Input Negative Input MIN 0 –0.2 –0.2 25 0.1 12 11 ±2 ±6 ±4 70 70 12 3 125 500 30 100 100 TYP MAX VREF +VCC + 0.2 +0.2 UNITS V V V pF µA Bits Bits LSB(1) LSB LSB µVrms dB CLK Cycles CLK Cycles kHz ns ns ps dB

AD7846JP-REEL资料

Resistance from VREF+ to VREF – Typically 30 kΩ

To 0 V To 0 V To 0 V or Any Power Supply

DIGITAL INPUTS

VIH (Input High Voltage)

2.4

2.4

V min

VIL (Input Low Voltage)

Relative Accuracy @ +25°C

±6

TMIN to TMAX

±8

Differential Nonlinearity Error

±1

Gain Error @ +25°C

±6

TMIN to TMAX

± 16

Offset Error @ +25°C

±6

TMIN to TMAX

± 16

Bipolar Zero Error @ +25°C

2. Readback The ability to read back the DAC register contents minimizes software routines when the AD7846 is used in ATE systems.

3. Power Dissipation Power dissipation of 100 mW makes the AD7846 the lowest power, high accuracy DAC on the market.

In addition to the excellent accuracy specifications, the AD7846 also offers a comprehensive microprocessor interface. There are 16 data I/O pins, plus control lines (CS, R/W, LDAC and CLR). R/W and CS allow writing to and reading from the I/O latch. This is the readback function which is useful in ATE applications. LDAC allows simultaneous updating of DACs in a multiDAC system and the CLR line will reset the contents of the DAC latch to 00 . . . 000 or 10 . . . 000 depending on the state of R/W. This means that the DAC output can be reset to 0 V in both the unipolar and bipolar configurations.

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。