ZL30100中文资料

Z0130中文资料

SILICON ZENER DIODES

DO - 41

0.107 (2.7) 0.080 (2.0)

1.00 (25.4) MIN.

MECHANICAL DATA

* Case : DO-41 Molded plastic * Epoxy : UL94V-O rate flame retardant * Lead : Axial lead solderable per MIL-STD-202, method 208 guaranteed * Polarity : Color band denotes cathode end * Mounting position : Any * Weight : 0.339 gram

L = 3/8" (9.5mm)

Page 1 of 2

Rev易网

ELECTRICAL CHARACTERISTICS

Rating at = 25 °C ambient temperature unless otherwise specified

0.205 (5.2) 0.166 (4.2)

0.034 (0.86) 0.028 (0.71)

1.00 (25.4) MIN.

Dimensions in inches and ( millimeters )

Rating at 25 °C ambient temperature unless otherwise specified

Nominal Zener Type No. Voltage

VZ @ IZT (V)

Test Current

IZT (mA)

Maximum Zener Impedance ZZT @ IZT ZZK @ IZK

30B

3

卸载高度(45°卸载角)(mm)

2800

卸载距离(最大卸载高度时)(mm)

950

最高行驶速度(km/h)

30

最小转弯半径(mm)

4837

工作装置动作时间(s)

10.2

斗容(m3)

1.5-2.5

掘起力(kN)

90

总长度×总宽度×总高度(mm)

6550×2510×3100

工作质量(t)

10

轴距(mm)

2500

ZL30B高效节能/30典范

●稳居国内30市场优势地位,二十余载辉煌不负众望。

●高品质、低油耗、适应广,堪称成工30系列装载机里程碑。

●机身轻巧,动力强劲,为您创造高效作业佳绩。

●独具特色的成工双变总成和成工30加强桥,结合全液压转向系统,动力传递高效可靠。

ZL30B

发动机型号

锡柴6110/125G-18

工程机械装载机的发展史

由于卸料和铲装不需转向,所以能在较狭窄的场地上作业,但它的侧

向稳定性不好,限制了相同功率的主机斗容量的增大。 4.1.5.2 侧卸式装载机是为满足市场需求而开发的机种。其除具备标准装 载机的性能外,用户可自行根据装卸场地的特定要求设置料斗往左或 右倾卸的方式进行作业。

30

侧卸式

31

杂物叉

32

4.1.6 装载机按发动机功率可分为小型、中型、大型和特大型四种。发动 机功率小于74千瓦的为小型装载机,发动机功率在74至147千瓦的为中 型装载机,发动机功率在147至515千瓦的为大型装载机,发动机功率 大于515千瓦的为特大型装载机。

1963年日本在华展出了一台轮式装载机125A,展出结束后,当时的机械工业主管 部门将该展出样机送给了天津工程机械研究所进行研究、测绘,仿制并将图样 交由柳工,并在1966年由柳工制造出我国第一台l轮式装载机-Z435 功率:100;斗容量1.7M3

14

2.2 第二代装载机

采用双涡轮液力变矩器 双行星排动力换档变速箱 带有轮边行星减速的驱动轿 钳盘式制动器 Z型连杆机构 铰接车架转向

6

1.2 四十年代发展专用底盘期

1947年,克拉克公司生产,用液压—连杆机构,取代了门架式结构,专用底盘,具备了现代 装载机的外形,提高了提升速度、卸载高度和掘起力,因而可用于铲装松散的土方和石 方,这是装载机发展过程中第一次重大突破。

7

W5型轮式装载机

1957年第一台320型两头忙挖掘装载机

1.3 五十年代——结构性能完善期 1951年美国开始采用液力机械传动,同时车架结构采用三点支承,提高 了车辆的越野性和牵引性,这时期开始形成了系列化专业化生产。 50年代中传动系统的发展是关键性的10年,形成了柴油机——液力变矩 器——动力换档变速箱——双桥驱动,这是第二次重大突破。

各种绝缘子型号

悬式绝缘子X-3,X-3C,X-4.5,XP-4.5C,XP-70,XP-70C,XP-100,XP-120,XP-160,XW P-70,XWP-100,XWP-120,XWP-160,XMP-70,XMP-100,XMP-120,X MP-160,XHP-70,XHP-100,XHP-120,XHP-160。

柱式绝缘子PS-15,PS-20,PS-35。

瓷横担绝缘子S-10/2.5,S-35/5.0,S-185,S-210,S-280,S-380,S-450。

针式绝缘子P-6,P-10,P-15,P-20,P-35。

复合悬式绝缘子FXBW4-10/70,FXBW4-35/70,FXBW4-66/70,FXBW4-110/70,FXBW4 -220/100,FXBW4-220/160,FXBW4-330/160,FXBW4-500/180。

针式复合绝缘子FPQ-10/4T20,FPQ-35/6T20。

瓷拉棒SL-10/30,SL-10/40,SL-15/30,SL-15/40。

拉紧绝缘子J-4.5,J-5,J-7,J-9。

低压蝶式绝缘子ED-1,ED-2,ED-3。

电车、机车绝缘子WX-01,WX-02,WH-01,WH-02,CD-1,CD-01。

针式瓷瓶PD-1,PD-2,PD-3。

户内外支柱绝缘子ZA-6Y,ZA-6T,ZB-6Y,ZB-6T,ZA-10Y,ZA-10T,ZB-10Y,ZB-10T,ZC-10 F,ZD-10F,ZD-20F,ZA-35Y,ZA-35T,ZB-35F,ZL-10/4,ZL-10/8,ZL-10/1 6,ZL-20/16,ZL-20/30,ZL-35/4,ZL-35/4Y,ZL-35/8,ZLA-35T,户内内胶装支柱绝缘子ZLA-10MM,ZLB-10MM,ZNA-6MM,ZNB-10MM,ZNB-10SS。

户外针式支柱绝缘子ZLA-6,ZPB-10,ZPD-10。

(改)威步产品目录2011.03(1) ZLMICRO半导体品牌

Low ESR Caps Compatible High Speed LDO Voltage Regulators with ON/OFF Switch High Current, High Speed LDO Regulators 3A 150KHZ PWM Buck DC/DC Converter 2A 150KHZ PWM Buck DC/DC Converter Low-Power DC/DC Boost Converter In SOT-23 And Son Packages Multiple Voltage Regulator

EEPROM

K24C01 K24C02 K24C04 K24C08 K24C16 K24C32 K24C64

RDS解码

AT6588 AT6579 BU1924

锁相环

AT9256 AT9257 LC72131

LCD驱动

HL1621 ZL LP6578 ZL75823A ZL75823B ZL75823C ZL75824 Temp Sensor DS3501 新增产品 MP2259 MP2359DJ AD9943 TW2868 TW2867 ZLIA171 K24C256

step-up DC/DC converter is optimized for driving OLEDs or white LEDs inductor-based DC/DC boost converter designed to drive LED Arrays 1.3A Fixed Frequency White LED Driver 1.3A Fixed Frequency white LED Driver 3A, 28V, 385KHz Step-Down Converter 250mW Dual Channel Audio Power Amplifier With Shutdown 1 Watt Audio Power Amplifier Dual 2.2w Audio Amplifier Plus Stereo Headphone Function 1.1W Audio Power Amplifier With Shutdown Mode 5X5W Amplifier With DC Volume Control 2x6W Stereo Power Amplifier 4X35W Quad Bridge Car Radio Amplifier 4X45W Quad Bridge Car Radio Amplifier 4X41W Quad Bridge Car Radio Amplifier 4-Channel Audio Processor IC 4 channels sound effect processor 4 channels sound effect processor Car radio multimedia signal processor (CMSP) 3 Band Car Audio Processor 3 Band Car Audio Processor Car Audio Processor Sound Processor for car audio SigmaDSP® 28/56-Bit Audio Processor with 2ADC/4DAC SigmaDSP® 28/56-Bit Audio Processor with 2ADC/4DAC 3-Input Video Switch 3-Input Video Switch With 75Ω Driver 8-Input,6-Output Video Switch Matrix With Output Drivers,Input clamp,and Bias Circuitry 12-Input,9-Output Video Switch Matrix With Input clamp,Input Bias Circuitry,and Output Drivers 10-Bit, 4× Oversampling SDTV Video Decoder

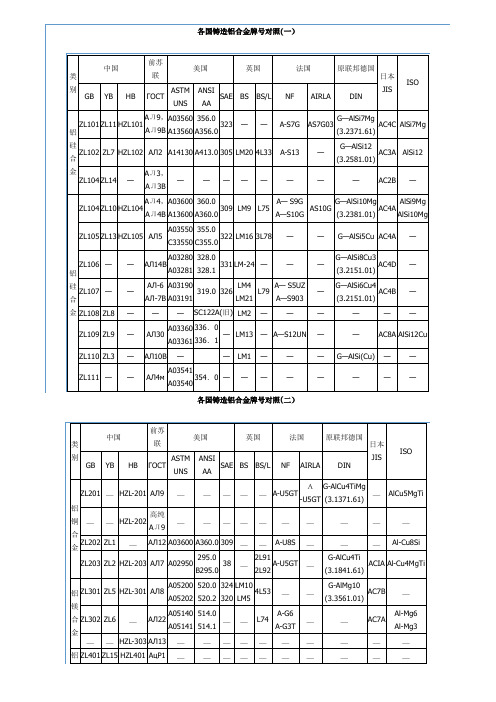

世界各国金属牌号对照

_ _ _

AC7A _ _

锌 合 金

ZL402 _ _

_

AЛ24

A07120 A07122 _

7122.2 _ _ _

_ _

_ _

A-Z5G _

_ _

_ _

_ _

Al-Zn5Mg _

_ HZL-505 AЛ11

注:YB-冶标,HB-航空、航天标准。

各国硬质合金牌号近似对照

制造厂家和商标

ISO 国际标准代号 P10 YT15 P20 YT14 P30 YT5 M10 YW1 M20 YW2 K10 YG6A YG6X YM051 YD15 YD10.1 YD10.2 YW3 YW4 YW3 YM20 CA15* CN16* YB03* YDS15 SD15 CA15* CN16* YB03* YB435* YD20 CA25* CN26* YB03* YB435* YB3015* YL10.1 YL10. YC25 YL10.2 YS2 (YG10HT) K15 YG6 K20 YG6 YG8N K30 YG8 YG8N

YG813 YG532 ZC01* ZC02* ZC03* ZC04* ZC06* ZC08* YG640 YG546 ZC08* ZK30

YN510N* ZC08* ZP01+ YN520N+ 中国北方工具厂 中国天津硬质合金工具厂 (引进维迪亚) 美国亚当斯碳化物公司 (Adamas) 美国通用电器公司卡波洛依系统部 (Carboloy) 美国肯纳金属 (Kennametal) YD10 YD15 TTM TTR 434 YTT YTN AT15 AT15

GC315* GC435* H13A

GC015* GC1025* GC1025*

ZL30零件图册.doc

NutM12

2

14

GB93-87

垫圈12

Washer12

10

15

GB5782-86

螺栓M12×

BoltM12×

10

16

螺栓

Bolt

8

17

GB93-87

垫圈20

Washer20

8

18

508100B

盘式制动器总成

Disc brake assembly

2

ZL30主减速器总成零件目录ZL30Parts listforfinal drive assembly

2

31

O型密封圈

O-ring

2

32

制动盘

Braking disc

2

33

GB93-87

垫圈16

Washer16

24

34

GB5782-86

螺栓M16×45

BoltM16×45

24

35

油封FB120×150×14

Oil sealFB120×150×14

4

制动器总成零件目录Parts list and exploded view for brake assembly

GB297-94

轴承31311

Bearing31311

1

14

调整垫片

Adjustshim

set

15

隔套

Spacer

1

16

轴承座

Bearingseat

1

17

GB297-94

轴承31311

Bearing31311

1

18

调整垫片

Adjust shim

LW100中文使用说明书

爱安达LW 100系列使用手册LW 100 BLW 100 ELW 100 E1总论本手册包含安全使用LW充气机所必需的操作及保养程序。

所以请事先认真阅读并严格执行,任何违反说明所造成的后果不在本公司的保修范围内。

注意以下几点:●试用期内只充气瓶●请勿超过容器允许压力等级●对过滤系统做好保养●避免污染空气进入进气口●不得超出最高工作温度安全手则●仔细阅读操作手册●只允许专业人员操作本充气机●操作时,不得放置任何物体于机上●运转时,确保无任何人或物体触及运作的部件●确保进气清洁,无有毒气体●必须在拔掉充气机电线插头及泄压后,才可进行维护工作●定期检查是否漏气或漏油●不得焊接损坏的高压气管●充气管必须处于良好的工作状态,必须特别注意接口处●任何维护工作之前,必须拔掉电线插头●维护时,不得触及高温部件,待冷却后进行工作呼吸空气压缩机(LW100B;LW100E;LW100E1)应用便携式高压呼吸空气压缩机适用于移动或其他轻量充气应用.发动机LW100B:强力万达牌V4冲程发动机(4.5千瓦),集成式燃料箱,手拉式启动;低油水平时停机.LW100E:2.2千瓦电动马达/400伏3相电压 /50赫兹开关按钮,可连接电缆和16安CEE插口LW100E12.2千瓦 E 发动机/230伏电压/50赫兹或者60赫兹开关按钮,可连接电缆和CE插口配置∙不锈钢提携结构∙3级压缩机机头∙全部活塞带金属活塞环∙水/油分离器∙每级压缩有安全阀∙压力维持止回阀∙带不锈钢头的充气软管∙带压力表充气阀∙充气连接(DIN200巴带YOKE接口或DIN3OO巴)∙便携手柄∙呼吸空气净化纯度符合 EN12021/DIN 3188/ISP2533规程∙过滤器容量:在20摄氏度时大约为108立方米选项∙要加带充气阀和气瓶连接的进气软管∙替换的一套压力开关,以及限压300巴的安全阀,选择阀和第二只充气管/阀/连接装置∙终压时自动停机装置∙特选电压/频率充气首次充气前,请检查在额定工作压力条件下的最终安全阀和其他进气连接装置,以确保工作压力及(在充气时)能让压缩机自动停机(如果可能的话)的正确操作:这是通过关闭充气阀和压缩机来完成的,让压缩机形成压力,压力表将在压力维持表打开(大约启动后1分钟左右),才显示压力的增加.压力将增加到安全阀泄放或者自动切断压缩机.如果压缩机超过额定工作压力,而安全阀门不能自动泄放,请立即手动关闭压缩机并询问技术工程师。

ZL30小型装载机

ZL30小型装载机装载机是一种广泛用于公路、铁路、建筑、水电、港口、矿山等建设工程的土石方施工机械,它主要用于铲装土壤、砂石、石灰、煤炭等散状物料,也可对矿石、硬土等作轻度铲挖作业。

换装不同的辅助工作装置还可进行推土、起重和其他物料如木材的装卸作业。

在道路、特别是在高等级公路施工中,装载机用于路基工程的填挖、沥青混合料和水泥混凝土料场的集料与装料等作业。

此外还可进行推运土壤、刮平地面和牵引其他机械等作业。

由于装载机具有作业速度快、效率高、机动性好、操作轻便等优点,因此它成为工程建设中土石方施工的主要机种之一。

Zy04 ZL30小型装载机概述:ZL30小型装载机是一种广泛用于公路、铁路、建筑、水电、港口、矿山等建设工程的土石方施工机械,它主要用于铲装土壤、砂石、石灰、煤炭等散状物料,也可对矿石、硬土等作轻度铲挖作业。

换装不同的辅助工作装置还可进行推土、起重和其他物料如木材的装卸作业。

在道路、特别是在高等级公路施工中,装载机用于路基工程的填挖、沥青混合料和水泥混凝土料场的集料与装料等作业。

此外还可进行推运土壤、刮平地面和牵引其他机械等作业。

由于装载机具有作业速度快、效率高、机动性好、操作轻便等优点,因此它成为工程建设中土石方施工的主要机种之一。

ZL30小型装载机用途:ZL30小型装载机主要用来铲、装、卸、运土和石料一类散状物料,也可以对岩石、硬土进行轻度铲掘作业。

如果换不同的工作装置,还可以完成推土、起重、装卸其他物料的工作。

在公路施工中主要用于路基工程的填挖,沥青和水泥混凝土料场的集料、装料等作业。

由于它具有作业速度快,机动性好,操作轻便等优点,因而发展很快,成为土石方施工中的主要机械。

ZL30小型装载机参数:型号:ZL30额定载重:3t装载机械类型:小型装载机动臂提升时间:6(s)铲臂提升时间:6(s)最大牵引力:58(kN)额定斗容量:1.5(m3)发动机功率:56(kw)整机重量:6(t)装卸方式:前卸式行走方式:轮胎式颜色:工程黄或红白驱动:四驱额定装载质量(kg):3000 制动形式:气顶油四轮盘制动整机质量(kg):6000驱动方式:轮边四轮液力驱动额定斗容量(m3):1动臂提升时间(s):4.8发动机型号:4108卸料时间(s):1.1额定功率(kw):56动臂下降时间(s):3.3卸载高度(mm):3600爬坡能力(max):60卸载距离(mm):900轮胎型号:16/70-24外形尺寸:6200*1920*2860 行驶速度(max):26。

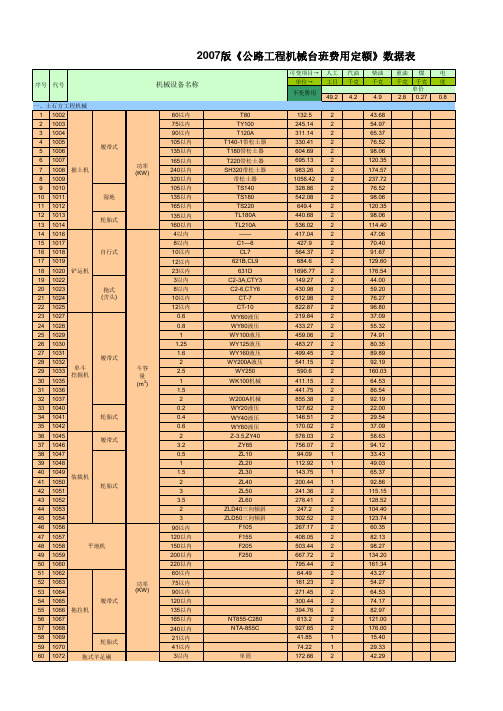

2008版公路工程机械台班费用定额数据表(含柴油发电机油料消耗)

17.34

9.39 29.57 41.91 32.80 44.00 46.80 50.40

32.8

12.45 421.91 649.09

85.01 104.85 178.53 64.75 86.33 114.08

21.14 55.32 74.17 84.86 103.72 147.72

拖式振动碾(含头) 蛙式夯土机 内燃夯土机

78 1097

79 1098

强夯机械

80 1099

81 1101

82 1102 83 1103 凿岩机

风动式

84 1104

85 1105

86 1108 凿岩 87 1109 台车

二臂 三臂

88 1112 潜孔 89 1113 钻机

液压

90 1114 潜孔 91 1115 钻车

156 1213

生产 能力 (t/h)

30以内 60以内 80以内 120以内

LB-30 LB800 LB1000 LB1500

149 1205

160以内

LB2000

150 1206

240以内

LB3000

151 1207

320以内

H40000

152 1209

153 1210

154

1211

沥青 混合料

155 1212 摊铺机

导轨式

电动

内燃式

轮胎式MINB027PRL

轮胎式H178

38~76

38~115

孔径 (mm)

100以内 150以内 38~105

38~170

38~200

机动

0.2以内

人民币四、五版补号大全

人民币四、五版补号大全四、五版补号大全(转)所谓“补票”即是指印钞厂用设定的某冠号,预先印好的后,作备用替补在印制各正常号过程中的不合格产品,这就形成了“补票”,后文简称补票。

四版币80年壹角:JA\5、JB\15、JC\4、JG\2500、JH\25、JI\215、JJ\8、JN\10、JO\5、JT\450、JU\1180、JW\20、JX\10、JZ\5、NJ\30、NY\75、NZ\4、ZH\8、ZI\6、ZJ\10、ZM\35、ZN\8、ZO\8、ZW\10、ZX\50、ZY\8、ZZ\4、ZT\50、ZU\7080年贰角:JX\160、JZ\8、ZI\8、ZJ\22、ZN\15、ZO\1580年伍角:JH\30、JI\135、JJ\30、JU\35、JW\13、JX\2880、JZ\1280、ZI\10、ZJ\10、ZN\23、ZO\260、ZW\10、ZY\10、ZX\8080年壹元:JU\22、JW\12、JX\13、JZ\20、ZF\60、ZG\12、ZH\8、ZI\22、ZJ\1290年壹元:JK\10、JL\50、JM\40、JO\8、ZB\100、ZC\20、ZD\15、ZE\30、ZL\20、ZM\120、ZN\100、ZO\12、96年壹元:JO\300、JR\160、JT\95、JU\20、JW\25、JX\15、JY\18、JZ\15、JN\?、NX\20000,NY\160、NZ\550、ZM\?、ZN\50、ZO\60、ZE\800、ZF\10、ZG\15、ZH\700、ZJ\300、80年贰元:JZ\1890年贰元:JU\260、JW\25、JX\15、ZI\25、ZJ\10、ZH\2580年伍元:JW(U)\15、JX\18、JZ\70、JN\25、JO\25、ZI\22、ZJ\18、ZM\35、ZN\15、ZO\18 80年拾元:JJ\15、JN\25、JO\3500、JU\奇缺、JX\?、JZ\280、NI\18、NJ\100、NY\20、NZ\50、ZG\25、ZH\25、ZI\40、ZJ\100、ZK\40、ZL\25、ZM\奇缺、ZN\奇缺、ZO\150 80年伍拾元:JZ\160090年伍拾元:JU\65、JX\55、ZH\90、ZI\55、ZJ\5580年壹佰圆:JZ\40090年壹佰圆:JS\120、JY\120、JU\260、JX\190、ZG\300、ZH\110、ZI\120、ZJ\115、ZM\400、ZN\110、ZO\110五版币99年壹元:AD\830、AE\95、AH\20、AG\40、AJ\20、AI\580、HS\40、HT\?、HU\25、HW\40、HX\45、HY\5、HZ\60、MS\40、MY\?、MZ\20、UA\150、UB\55、UC\50、UD\20、UE\奇缺、UF\85、XS\90、XT\80、XU\95、XW\5、XX\120、XY\奇缺、XZ\5、YK\?、YL\10、YN\奇缺、YM\15、YO\10、WX\10、99年伍圆:AG\?、AH\100、AJ\15、AI\20、UH\?、(UI\?)、UJ\15099年拾圆:AH\120、AJ\?、AI\?、UH\2000、UI\30、UJ\60、HU\1600 FF\120、99年贰拾圆:AH\100、AJ\80、AI\30、UJ\42099年伍拾圆:AH\80、AJ\1600、AI\6599年壹佰圆:AH\?、AJ\?、AI\?、UH\?、UG\?、UI\?、UJ\?、HU\?、HW\?、HX\奇缺、HY\?、HZ\?、YN\?、YO\180、XW\?、XU\奇缺、XX\?、XY\120、XZ\150 05年伍圆:AJ\12、AI\20、AE\12、AD\?UG\18、UH\?、UI\?、UJ\?05年拾圆:AE\?、AJ\?、AD\40、HW\40、UG\?、UH\20、UI\20、UJ\?、ZL\8005年贰拾圆:AJ\2305年伍拾元:AE\5505年壹佰圆:AD\130、AI\?、AE\?、AC\?、(AJ\?)、AH\?、HU\?HT\?、HW\130、HY\105、HX\?、HZ\?、UE\?、UF\?、UG\?、UI\?、UJ\?、UH\130、XU\?、XW\?、XX\130、XY\?80年1元一共发行159个冠号,90年1元148个,96年1元302个;80年2元54个,90年2元133个;5元264个;10元401个;80年50元24个,90年50元169个;80年100元16个,80100共16种冠号(不含连体)CP,CQ,CR,CS,CT,CU,CW,CX,CY,CZ,EP,EQ,ER,ES,ET补号:JZ,90年100元204个。

柳工ZL30E装载机

柳工ZL30E装载机专业工程机械技术服务与营销班级姓名2012年03月07日目录绪论 (3)第1章柳工ZL30E装载机概述 (5)1.1、柳工ZL30E轮式装载机简介 (5)1.1.1、装载机的分类及相关参数 (5)1.1.2、柳工ZL30E简介 (6)1.2、柳工ZL30E总体结构 (7)1.3、柳工ZL30E传动系统 (9)1.4、转向系统 (12)1.5、制动系统 (14)1.6、工作装置 (16)1.7、工作液压系统 (18)1.8、散热系统 (22)第2章柳工ZL30E型轮式装载机的常见故障分析及解决措施 (23)2.1、柳工ZL30E型轮式装载机的整机常见故障分类 (23)2.1.1、作业无力问题 (23)2.1.2、功率下降 (23)2.1.3、后桥异响 (24)2.2.柳工ZL30E型轮式装载机的液压系统常见故障分类 (25)2.2.1、动臂举升缓慢,无力或无动作,而转斗翻转正常 (25)2.2.2、动臂工作正常;转斗翻转缓慢、无力或无动作 (27)2.2.3、液压油过热 (28)第3章柳工ZL30E型轮式装载机的主要性能表 (29)第4章装载机国内外主要制造厂商简介 (35)第5章技术发展动态与趋势 (36)结束语 (37)参考文献 (38)致谢 (39)绪论现代轮式装载机起始于20世纪60年代中期的Z435型。

该机为整体机架、后桥转向。

经过几年的努力,在吸收当时世界最先进的轮式装载机技术的基础上,开发成功了功率为162KW的铲接式轮式装载机,定型为Z450(即后来的ZL50),并于1971年12月18日正式通过专家鉴定。

就这样诞生了我国第一台铰接式轮式装载机,从而开创了我国装载机行业形成与发展的历史。

Z450型装载机具有液力机械传动、动力换挡、双桥驱动、液压操纵、铰接式动力转向、气推油加力制动等现代轮式装载机的基本结构,为当时世界先进水平。

也基本上代表了我国第一代轮式装载的基本结构。

ZL30

环磨损量为 50~ . m 动环磨损量为 30~ . 。改进后 6 0 m, . 4 0r m 的密封性能 良好 , 磨损 量 减少 , 用 寿命增 长 , 使 能满 足运 行要 求 。为 了使磨损量更 小更理 想 , 目前 , 我们 叉在静环 材料上 进 行 了进一步改进 , 采用耐磨橡胶加膨胀石 墨, 一来 形成 自润滑 , 再则更加增大补偿能 力 , 可见 能进 一步 延长密 封 的运行 寿命。 与此 同时 , 了保持 补偿弹 簧不 因锈蚀 而失去 弹性补偿 , 为 将原 测试说明, 当封水 比压 力 由4 . P 降至 1 a 漏水 00ka 60k 时 P 量增大到 22—2 4倍 , . 当封水 比压力 由 4 P 00ka增大 至 8 ' 30

因而温度较 高。

维普资讯

Z 3 7型 轴 流 采轴 承 密封 装 置 的 改 进 L0—

同思年

黄 爱忠 阚水 庚 等

4 l

2 密封装置的改进方案 比较

根据 上分析 , 造厂 主张对静环 结构进 行第 一次改 进。 制 在静环 摩擦 面上开设 8m m宽 的环形 水槽 , 设想 在槽 中注入 压

本文介绍该密封装置改造 的过程 和运行状 况 , 供有关 泵 可 站及 制造 厂家进一步研究轴承密封的改进 提供 参考 :

1 改进 以来 轴承的运行 状况

江都 四站从 17 年 元月正式投运 , 97 运行 短时间后 , 漏水 量 减少, 但至同年 7月漏 水量 剐增 , 使油轴 承浸水 。经 检查 发 致

裹 1 轴承密封装置运行时间厦磨损情况

该泵的轴承采用筒式 自循环稀油润滑结 构 , 承的密 封装 轴 置采用平板密封结构 ( 便于拆检 , 具有 一定 的补偿能力 ) 。此密 封装置在长期运行过 程 中, 经制造 厂 和我 单位 多次 改进 , 目前 运行 基本稳定 , 运行寿命达 2 0 左 右。 000h

zl30409_dde中文资料_数据手册_IC数据表

Data Sheet

April 2006

Ordering Information

ZL30409/DDE 48 Pin SSOP ZL30409/DDF 48 Pin SSOP ZL30409DDE1 48 Pin SSOP* ZL30409DDF1 48 Pin SSOP*

Changes from September 2005 Issue to March 2006 Issue. Page, section, figure and table numbers refer to this current issue.

Page Item 1

Change Updated Ordering Information

Primary Reference (Input). See SEC pin description. This pin is internally pulled up to VDD.

Positive Supply Voltage. +3.3VDC nominal.

OSCo OSCi F16o F0o RSP TSP F8o C1.5o

TIE Circuit Reset (Input). A logic low at this input resets the Time Interval Error (TIE) correction circuit resulting in a realignment of input phase with output phase as shown in Figure 13. The TCLR pin should be held low for a minimum of 300 ns. This pin is internally pulled down to GND.

机械设备租赁价格表

8000 12000 15000 5000 5000 5000

16000 18000 24000 35000 45000

JC350 JZ500 HZS25 HZS30 HZS50 HZS60 HZS100

JC6 JC8 HBT60电力 HBT60内燃 砼汽车泵车 砼汽车泵车 砼汽车泵车

搅拌运输车 搅拌运输车 输送泵60 输送泵60 32米,65m3 36米,90m3 37米,120m3

单位

T T T T 片 片 片 个 个 个 片 片 片 个 个 个 套 套 T 根

50 130

砼机械

发电机组

周转材料

日租单价 材料名称规格

6

8

8 6 2.8 1 0.5 0.1 0.1 0.15 1 0.7 0.6 6.2 15 6 500 400 4.5 0.3

胶轮压路机

胶轮压路机

英格索兰 英格索兰 戴纳派克 戴纳派克

宝马

挖掘机

200

压路机

平地机

30000 32000 38000 48000 53000

22000

18000

15000 12000

23000 20000 58000 53000 60000 55000 40000

24000 22000 21000

钢模板 搭架钢管(碗

扣) 管扣 可调上托 可调下托 连接销 大门架1914 小门架 门架斜拉杆

15000 18000 30000 33000 60000

20000 30000 23000 26000 70000 75000 100000

7000 9000 12000 15000

单位

m2

T

个 个 个 个 个 个 个

Daikin 100 拓展版 商品说明书

World-class products designedfor AfricaStabilizer Free100TABLE OF CONTENTSAbout DaikinDaikin Makesthe DifferenceInverterTechnologyR32 - GreenRefrigerantBespokeFeaturesProductLine-upUnit OptionsFeatures ListDaikin is a leadinginnovator and provider of advanced, high-quality air-conditioning solutions for residential, commercial and industrial applications.As World’s LeadingAir-conditioning Company, Daikin is committed to delivering air-conditioning solutions that enhance the quality of life all around the world.A diverse multinational company, Daikin Industries Ltd., active in air-conditioning, chemicals and oil hydraulics, was establishedin 1924. With headquarters at Osaka, Japan, the Daikin family has more than 84,000 members, working across 100 production base units and 315 consolidated subsidiaries worldwide. As the world’s sole manufacturer that develops a long line of products,DAIKINfrom refrigerants to air-conditioners,Daikin advocates comfortableliving on the strength of advancedtechnologies.Daikin is present in USA andCanada, Europe and Russia, MiddleEast, Africa, Central Asia, SoutheastAsia, Oceania and Latin America.We aim to serve our customers ineach of these markets by providingoptimal air-conditioning products.12Daikin calls an inverter model that is equipped with a DC motor as DC inverter. A DC motor offers higher efficiency than an AC motor. A DC motor uses the power of magnets to attract and repel to generate rotation. A DC motor that is equipped with power neodymium magnets, which enable even greater efficiency, is called a reluctance DC motor.Recipient of Electric Science Promotion Award (Reluctance DC motor for compressor)DAIKIN MAKES THE DIFFERENCE20010080604020Approx. 40% increase 0E ffi c i e n c y (%)DC motorE ffi c i e n c y o f D C m o t o r f o r f a n *(c o m p a r i s o n w i t h a c o n v e n t i o n a l A C m o t o r )3Neodymium magnets are used in the pink-coloured area.The swing compressor can reduce operational vibration and Swing bush Refrigerant gasIntegral piston of blade and rollerFerrite magnetNeodymium magnetWhat is Inverter Technology and how is it different from Non-Inverter Technology?An inverter is a device for convertingfrequency. The technology is used in many home appliances and controls electric voltage, current and frequency. Inverter air-conditioners vary their cooling/heating capacity by adjusting the power supply frequency of their compressors.AHEAD WITH INVERTER TECHNOLOGYAn inverter type air-conditioner adjusts the speed of the compressor to control the refrigerant (gas) flow rate,thereby consuming less current and power. An inverter has precise temperature control and as the set temperature is attained, the unit adjusts its capacity to eliminate any temperature fluctuations.In contrast, non-inverter air-conditioners have a fixed cooling/heating capacity and can only control the indoor temperature by starting or stopping their compressors.Non-inverter air-conditioners stops and starts repeatedly. The power consumption and current goes down when the operation stops, but it goes up sharply at the time of restart and thus it has high average power consumption and temperature variations. As a result, inverter air-conditioners are more energy-saving and comfortable than non-inverter air-conditioners.Inverter air-conditioners are able to vary their operating capacity. Non-inverter air-conditioners can only operate at a fixed capacity.Variable capacity operationNon-inverter type air-conditionerPowerInverter power controlCompressorRaise frequencyLower frequencyHigh-speedHigh capacityLow capacityLow-speedPowerCompressorConstant Speed rotationFixed CapacityLet’s take anexample of 1.5 Ton AC. Inverter AC can work from 0.3 to 1.7 ton based on cooling requirement. Non-inverter AC can work at 1.5 ton only (fixed capacity)*.424°Temperature remains constant24°24°24°Inverter air-conditionerScenario: Indoor Temperature: 24°, Set Temperature: 24°25°Compressor stopsTemperature rises and compressorstarts again23°23°25°vvvNon-inverter air-conditionerInverter air-conditioners are more comfortable than non-inverter models.Diagrams are used for illustrative purpose only; actual conditions and scenario may vary from the one shown.Compressor stopsTemperature fluctuatesvWhat are the benefits of Inverter Air-Conditioners?ComfortableInverter air-conditioners finely adjust capacity according to changes in the air-conditioning load and the difference between the indoor temperature and set temperature is small. This gives higher comfort level than the non-inverter air-conditioners.Energy savingAfter the indoor temperature approaches the set temperature, inverter control adjusts to low capacity operation to maintain this temperature. This makes inverter models more energy saving than non-inverter models, which must repeatedly start or stop their compressors to maintain theroom temperature.PowerfulInverter air-conditioners operate at maximum capacity as soon as they start up. As a result, the set temperature can be reached more quickly.5Air is something that surrounds us 24 hours a day. In fact, our existence, as well as earth’s depends on it. At Daikin, the future of the world’s air is our greatest concern. We, the manufacturer of world’s best air-conditioners, are always paving the path to save our environment for next generation.• R-32 – ENERGY EFFICIENTREFRIGERANT – SAVES POWER & MONEYWe phased out all R-22 model and shifted to the green refrigerant R-32. Now, whole world is coming together to find and work on way to address global warming issue. We are also offering worldwide free access to patents for equipment using next generation refrigerant, R-32. Refrigerant choice is a key in saving the ozone layer and reducing global warming.R-32 –BEFRIENDING THE ENVIRONMENT6• DAIKIN IS BRINGING GLOBAL TREND OF ECO-FRIENDLYREFRIGERANT BASED PRODUCTS TO AFRICAR-32 has zero Ozone Depletion Potential (ODP) and Modified Global Warming Potential (GWP) of 472, compared to R-410A’s Modified GWP of 2,027. Also R-32 is a single component refrigerant, which makes it easy to recycle. It is because of these reasons that R-32 offers the lowest total emissions and best overall life cycle climate performance.Most balanced refrigerant=x GWP5001,0001,5002,0002,500675HCFC 22HFC 410A HFC 322,0901,810Charging ratio (%)02040806010012070HCFC 22HFC 410A HFC 3297100Theoretical Modified GWP5001,0001,5002,0002,500472HCFC 22HFC 410A HFC 322,0271,810R-32 is Environment-FriendlyR-32 offers superior performanceBetter life cycle climate performanceZero Ozone Depletion Potential1/3rd Global Warming Potential75% less carbon dioxide emissionsBetter performance at higher temperature as compared to R-22 (low derating)15.3% more cooling as compared to R-410A~30% less refrigerant charging volume as compared to R-410A &R-22~5% more power savings compared toR-410A12345Ozo neEconomySafetyEnergyLCCPHFC410A 12345Ozo neEconomySafetyEnergyLCCPHFO1234YFEconomy12345Ozo neSafetyEnergyLCCPPropane (HFC290)12345Ozo neEconomySafetyEnergy LCCPHFC327LEADING WITH INNOVATIONPatented Streamer Discharge TechnologyRoleFunctionality8Streamer discharge reduces unpleasant smell and virus inside the room cleaning the indoor air.A type of plasma discharge comprising high speed electrons with high oxidation capacity is released within the unit, decomposing odours and harmful gases. High speed electrons are generated and then absorbed within the unit to ensure safety.ECONO OperationPower Consumption Maximum during normaloperationNormal operationMaximum during ECONOoperationECONO operation9LEADING WITH INNOVATIONIndoor Unit Quiet OperationRoleFunctionality10This feature ensures low noise level resulting in sound sleep. It optimises the speed of the airflow according to low noise level to give you uninterrupted comfort.The airflow rate is balanced with sound level to produce minimal noise while under this operation. When the airflow is set to the quiet operation starts and noise from the indoor unit will reduce.Coanda Airflow OperationRoleFunctionalityNote: When POWER CHILL operation is started during COANDA operation, the flap turns downward, allowing the air to blow directly onto people. The combination of COANDA and POWER CHILL operations provides sufficient cooling performance to quickly cool down the room. After POWER CHILL operation is finished, the system automatically returns to COANDA operation.11Coanda airflow operation gives you the bestair-conditioning experience. The powerful air draft does not fall on your head directly, but it is steered upward letting air circulate into the corners of the room creating a comfortable ambience.The horizontal flap is controlled not to blow air directly at people in the room. The airflow rate can be set to any level. However, a low airflow rate may cause cold air to go down and blow on people. If SWING button is pressed during COANDA operation, Coanda operation will be cancelled.When COANDA operation is started during POWER CHILL operation, the system prevents the air from blowing directly onto people.Power Chill OperationLEADING WITH INNOVATIONOperation mode Fan speed Target Temperature COOL H tap + A rpm180CDRY Dry rotating speed + A rpmLowered by 2.50C FAN H tap + A rpm—12Self Diagnosis13The machine auto detects the error and shows the related code on the remote screen. Now you can easily self diagnose the error and report it to your Daikin authorised service centre for a quick resolution.RoleFunctionalityWhen the fault is recognised by the indoor unit it sends the corresponding error code to the remote control, which is displayed on the remote control.1. P ress and hold CANCEL button on the remote for 5 seconds, “00” blinks in the temperature display section. 2. P ress CANCEL button repeatedly until a long beep is produced. The code indication changes as shown below, and notifies with a long beep.Self Diagnosis codesCode DiagnosisA1Indoor unit PCB malfunction E1Outdoor unit PCB malfunction U0Low Refrigerant detection E6Compressor lockL3Electrical box temperature rise E8Input overcurrent detectionU2Low-voltage/over-voltage detection# For More details please refer User Manual /Service ManualFunctionalityOptimizes energy consumption—AC Operation Guarantee (160V~264V)—and protect the electrical components of the AC during power fluctuations.RoleStabilizer inside operationLEADING WITH INNOVATIONThis feature helps stabilize operations by stepping up and stepping down the power voltage during voltage fluctuations.14Stabilizer free operation1515Start living in a cleanenvironment with Daikin filters that absorb harmful germs andgases to provide health-giving air for your family.Titanium apatitephotocatalytic air-purifying filter Absorbs bacteria and viruses while eliminating odour.Silver particle anti-bacterial filterFilter is embedded with silver particles that kills bacteria.PM2.5 & 0.1 filterTraps fine air particles – 0.1 to 2.5 microns in width.Anti-microbial filterIts unique micro-structure andelectrostatic charge provide effective particle capture, and prohibiting growth of mold and mildew on filter media.& 0.1PURE AIR FOR A HEALTHY LIVING16OTHER KEY FEATURESAvailable inIntelligent eyeSpecificationsModel name Indoor unit GTKJ35TV16UZ GTKJ50TV16UZ GTKJ60TV16UZOutdoor unit RKJG35TV16UZ RKJG50TV16UZ RKJG60TV16UZ Power supply1 50Hz 230V1 50Hz 230V1 50Hz 230V(220-240V)(220-240V)(220-240V)Measurement conditions:1. Cooling capacity is based on: indoor temp. 27° CDB, 19° CWB; outdoor temp. 35° CDB, piping length 5 m.2. Sound levels are based on temperature conditions 1. above with 5m piping length. These are anechoic conversion values. These values are normally somewhat higher during actual operation as a result of ambient conditions.18Specifications19Coanda airflowMeasurement conditions:1. Cooling capacity is based on: indoor temp. 27° CDB, 19° CWB; outdoor temp. 35° CDB, piping length 5 m.2. S ound levels are based on temperature conditions 1. above with 5m piping length. These are anechoic conversion values. These values are normally somewhat higher during actual operation as a result of ambient conditions.Specifications 20Coanda airflowModel name Indoor unit GTHT35TV16XZ GTHT50TV16UZ GTHT60TV16UZ Outdoor unit RHTG35TV16XZ RHTG50TV16UZ RHTG60TV16UZ Power supply1 50Hz 230V1 50Hz 230V1 50Hz 230V(220-240V)(220-240V)(220-240V)Outdoor unit Outdoor unit Outdoor unit1. Cooling capacity is based on: indoor temp. 27° CDB, 19° CWB; outdoor temp. 35° CDB, piping length 5 m.2. Sound levels are based on temperature conditions 1. above with 5m piping length. These are anechoic conversion values. These values are normally somewhat higher during actual operation as a result of ambient conditions. Cooling and heating capacities above areCoandaairflowSpecifications*T1 Outdoor: 35°CDB T1 Indoor: 27°CDB / 19°CWB21UNIT OPTIONS5 rooms centralised controller NAWiring adopter for time clock / remote control KRP413AB1S + New Optional power adaptor Air purifying filter (PM 0.1)KAF010A503Air purifying filter (PM 2.5)KAF250A502Titanium apatite deodorising air purifying filter KAF970A45Ag-ion filter KAF057A41Anti-microbial filter KAF500A504Air purifying filter (PM 0.1) for streamer Included with the unit in accessories bag Air purifying filter (PM 2.5) for streamer KAF250A505Remote Holder Included with the unit in accessories bagOptional Parts GTHT35/50/60GTKL35/50/60 RHT35/50/60RKLG35/50/605 rooms centralised controller NA NAWiring adopter for time clock / remote control KRP413AB1S + New Optional power adaptor (5.0 &6.0kW only)KRP413AB1S + New Optional power adaptor(5.0 & 6.0kW only)Air purifying filter (PM 0.1)KAF010A503KAF010A503Air purifying filter (PM 2.5)Included with the unit in accessories bag KAF250A502Titanium apatite deodorising air purifying filter KAF970A45KAF970A45Ag-ion filter KAF057A41KAF057A41Anti-microbial filter KAF500A504Included with the unit in accessories bag Air purifying filter (PM 0.1) for streamer NA NAAir purifying filter (PM 2.5) for streamer NA NARemote Holder NA NAOptional Parts GTL28GTQ35/60GTE50 Titanium apatite deodorising air purifying filter KAF970A45KAF970A45KAF970A45 (Optional)Air purifying filter (PM 2.5)KAF250A502KAF250A502Included with the unit in accessoriesbagAir purifying filter (PM 0.1) KAF010A503KAF010A503KAF010A503 (Optional) Ag-ion filter KAF057A41KAF057A41KAF057A41 (Optional) Anti-microbial filter Included with the unit in accessoriesbagKAF500A5KAF500A504 (Optional)2223FEATURES LISTFunctionGTKJ35/50/ 60TV16UZ GTHT35/50/ 60TV16UZ GTKL35/50/ 60TV16XZ GTL28 TV16X2Z GTQ35/60 TV16X2Z GTE50 RKJG35/50/ 60TV16UZRHTG35/50/ 60TV16UZRKLG35/50/ 60TV16XZRLG28 TV16X2Z RQG35/60 TV16X2ZRQG50T e c h n o l o g ySwing compressor ———Rotary comp.———Reluctance DC motor ——— PAM control———C o m f o r t a b l e A i r fl o w New comfort airflow mode (COANDA)Power-airflow dual flaps Wide-angle louversVertical auto-swing (up and down)Horizontal auto-swing (left and right)—— — — —3-D airflow—— — — —C o m f o r t C o n t r o lIndoor unit quiet operation ———Outdoor unit quiet operation —— ———Intelligent eye—— ———Automatic operation (Heating and Cooling)—————Auto fan speed L i f e s t y l eECONO modeInverter powerful operation — — ———New dry mode function POWER CHILL operation—Indoor unit ON/OFF switch Fan onlyC l e a n l i n e s s Patented Streamer Discharge Air Purifier —————Mold proof operation — ————Smell proof operation— Titanium apatite deodorising air purifying filter Option Option Option Option Option Option Ag ion filterOption Option Option Option Option Option Air purifying filter (PM2.5)Option —Option Option Option Option Air purifying filter (PM0.1)—OptionOption Option Option Anti-microbial filterOption—Option Option Option Wipe-clean flat panel (washable)C o n t r o l sPower Display at Indoor unit—————Set Temperature Display at Indoor Unit —————Room Temperature Display at Indoor Unit —————R/C with back light— Luminescent R/C button Indoor temp. display on R/C —— — — —R/C LCD back light OFF — ———Child lock— — — —T i m e r s24-Hr ON/OFF timer————Count up-down ON/OFF timer — —Good Sleep Off Timer——New Good Sleep Off Timer—— — —W o r r y F r e eAuto-restart (after power failure)Stabilizer Inside ———Stabilizer free ———New stabilizer modefor 5.0 & 6.0kWModel—————Self -diagnosis (RC,LED) displayPE Anti-corrosion treatment of outdoor heat exchangerThe present publication is drawn up by way of information only and does not constitute an offer binding upon Daikin MEA. Daikin MEA has compiled the content of thispublication to the best of its knowledge. No express or implied warranty is given for the completeness, accuracy, reliability or fitness for particular purpose of its content and the products and services presented therein. Specifications are subject to change without prior notice. Daikin MEA explicitly rejects any liability for any direct or indirect damage, inthe broadest sense, arising from or related to the use and/or interpretation of this publication. All content is copyrighted by Daikin MEA.www.daik DMEA21-214Office 332, Regus Mulliner Tower, Ikoyi, Lagos | Contact Number: +234 8065421038E-mail: ********************* Web:Distributed by。

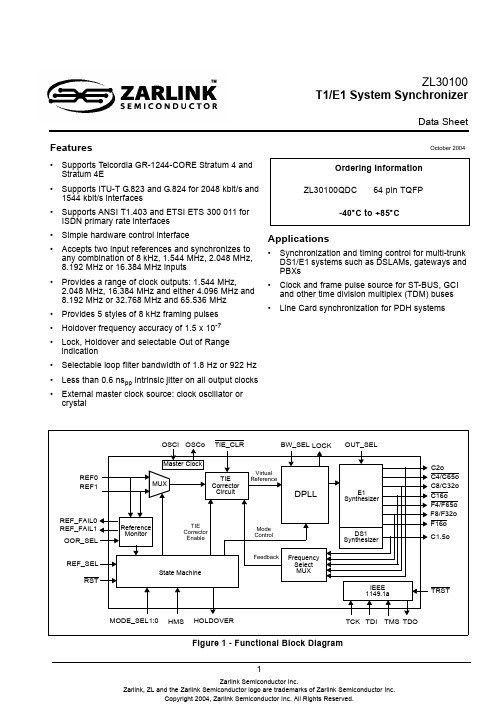

zl30100中文资料_数据手册_IC数据表

1Features•Supports Telcordia GR-1244-CORE Stratum 4 and Stratum 4E•Supports ITU-T G.823 and G.824 for 2048kbit/s and 1544kbit/s interfaces•Supports ANSI T1.403 and ETSI ETS 300 011 for ISDN primary rate interfaces •Simple hardware control interface•Accepts two input references and synchronizes to any combination of 8kHz, 1.544MHz, 2.048MHz, 8.192MHz or 16.384MHz inputs•Provides a range of clock outputs: 1.544MHz,2.048MHz, 16.384MHz and either 4.096MHz and 8.192MHz or 32.768MHz and 65.536MHz •Provides 5 styles of 8kHz framing pulses •Holdover frequency accuracy of 1.5 x 10-7•Lock, Holdover and selectable Out of Range indication•Selectable loop filter bandwidth of 1.8Hz or 922Hz •Less than 0.6 ns pp intrinsic jitter on all output clocks •External master clock source: clock oscillator or crystalApplications•Synchronization and timing control for multi-trunk DS1/E1 systems such as DSLAMs, gateways and PBXs•Clock and frame pulse source for ST-BUS, GCI and other time division multiplex (TDM) buses •Line Card synchronization for PDH systemsOctober 2004ZL30100T1/E1 System SynchronizerData SheetFigure 1 - Functional Block DiagramReference MonitorMode ControlVirtual ReferenceIEEE 1149.1aFeedbackTIE Corrector EnableState MachineFrequency Select MUXTIE Corrector CircuitMODE_SEL1:0TCK REF1RSTREF_SELTIE_CLRC1.5oC4/C65o C8/C32o C16o F4/F65o F8/F32o F16oOSCo OSCi Master ClockTDOREF0TDI TMS TRSTHOLDOVER BW_SEL HMS LOCK REF_FAIL0REF_FAIL1DPLLOUT_SELC2oE1SynthesizerDS1SynthesizerMUXOOR_SEL Ordering InformationZL30100QDC64 pin TQFP-40°C to +85°CZL30100Data Sheet DescriptionThe ZL30100 T1/E1 System Synchronizer contains a digital phase-locked loop (DPLL), which provides timing and synchronization for multi-trunk T1 and E1 transmission equipment.The ZL30100 generates ST-BUS and other TDM clock and framing signals that are phase locked to one of two input references. It helps ensure system reliability by monitoring its references for accuracy and stability and by maintaining stable output clocks during reference switching operations and during short periods when a reference is unavailable.The ZL30100 is intended to be the central timing and synchronization resource for network equipment that complies with Telcordia, ETSI, ITU-T and ANSI network specifications.ZL30100Data SheetTable of Contents1.0 Change Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52.0 Physical Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62.1 Pin Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62.2 Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103.1 Reference Select Multiplexer (MUX). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103.2 Reference Monitor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103.3 Time Interval Error (TIE) Corrector Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123.4 Digital Phase Lock Loop (DPLL). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.5 Frequency Synthesizers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.6 State Machine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.7 Master Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .164.0 Control and Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .164.1 Out of Range Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .164.2 Loop Filter Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .174.3 Output Clock and Frame Pulse Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .174.4 Modes of Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .174.4.1 Freerun Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .174.4.2 Holdover Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184.4.3 Normal Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184.5 Reference Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .195.0 Measures of Performance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .205.1 Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .205.2 Jitter Generation (Intrinsic Jitter). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .205.3 Jitter Tolerance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .205.4 Jitter Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .205.5 Frequency Accuracy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215.6 Holdover Accuracy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215.7 Pull-in Range. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215.8 Lock Range. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215.9 Phase Slope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215.10 Time Interval Error (TIE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215.11 Maximum Time Interval Error (MTIE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215.12 Phase Continuity. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215.13 Lock Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .216.0 Applications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .226.1 Power Supply Decoupling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .226.2 Master Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .236.2.1 Clock Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .236.2.2 Crystal Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .236.3 Power Up Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .246.4 Reset Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .257.0 Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .267.1 AC and DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .267.2 Performance Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31ZL30100Data SheetList of FiguresFigure 1 - Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - Pin Connections (64 pin TQFP, please see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Figure 3 - Reference Monitor Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 4 - Behaviour of the Dis/Requalify Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 5 - DS1 Mode Out-of-Range Limits (OOR_SEL=0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 6 - E1 Mode Out-of-Range Limits (OOR_SEL=1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 7 - Timing Diagram of Hitless Reference Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 8 - Timing Diagram of Hitless Mode Switching. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 9 - DPLL Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 10 - Mode Switching in Normal Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Figure 11 - Reference Switching in Normal Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Figure 12 - Recommended Power Supply Decoupling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Figure 13 - Clock Oscillator Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 Figure 14 - Crystal Oscillator Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 Figure 15 - Power-Up Reset Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Figure 16 - Timing Parameter Measurement Voltage Levels. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Figure 17 - Input to Output Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 Figure 18 - Output Timing Referenced to F8/F32o . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30ZL30100Data Sheet 1.0 Changes SummaryChanges from June 2004 Issue to September 2004 Issue. Page, section, figure and table numbers refer to this issue.Page Item Change1Text Jitter changed to 0.6 ns from 0.5 ns6Figure 2Added note specifying not e-Pad7Table “Pin Description“Added information about Schmitt trigger feedback paths toC1.5o, C2o, C16o, and F8/F32o10Section 3.2Added text about input pulse width restriction15Section 3.4Added details to "Lock Indicator" on LOCK pin behaviour19Section 4.5Added text and Figure 11 explaining LOCK pin behaviour20Section 5.0Added Jitter definition26Table “Absolute Maximum Ratings*“Corrected package power rating27Table “DC Electrical Characteristics*“Corrected current consumptionCorrected input voltage characteristics to reflect Schmitt triggerCorrected input leakage current to reflect internal pull-upsCorrected output voltage note to reflect two pad strengths28Table “AC Electrical Characteristics* -Added explanatory noteInput timing for REF0 and REF1references (see Figure 17)“Changed jitter numbers32Table “Performance Characteristics*:Output Jitter Generation - ANSIT1.403 Conformance“Changed jitter number32Table “Performance Characteristics*:Output Jitter Generation - ITU-TG.812 Conformance“Changed jitter numbers, removed UI column32Table “Performance Characteristics* -Unfiltered Intrinsic Jitter“ZL30100Data Sheet2.0 Physical Description2.1 Pin ConnectionsFigure 2 - Pin Connections (64 pin TQFP, please see Note 1)Note 1: The ZL30100 uses the TQFP shown in the package outline designated with the suffix QD, the ZL30100does not use the e-Pad TQFP .ZL3010034363840424446486462605856525054161412108642OSCo NC GND OUT_SEL C1.5o MODE_SEL1V DD AV DD IC NC RSTNC AGNDF4/F65o V DD REF1NC ICC 8/C 32o N C C 2o A G N DA V D DN C F 8/F 32o C 4/C 65o REF_SEL1820222426303228C 16o F16o TIE_CLR OOR_SELICOSCi A V D DA V D DA V D DA V C O R EA G N D A G N D A G N D NC NC IC ICMODE_SEL0NC BW_SELREF0V C O R EL O C K H M ST R S T G N DT D O T M S H O L D O V E R I C T C K T D I V C O R EA V C O R EG N D R E F _F A I L 0R E F _F A I L 1ZL30100Data Sheet2.2 Pin DescriptionPin DescriptionPin # Name Description1GND Ground. 0 V.2V CORE Positive Supply Voltage. +1.8 V DC nominal.3LOCK Lock Indicator (Output). This output goes to a logic high when the PLL is frequencylocked to the selected input reference.4HOLDOVER Holdover (Output). This output goes to a logic high whenever the PLL goes intoholdover mode.5REF_FAIL0Reference 0 Failure Indicator (Output). A logic high at this pin indicates that the REF0 reference frequency has exceeded the out-of-range limit set by the OOR_SEL pin or thatit is exhibiting abrupt phase or frequency changes.6IC Internal bonding Connection. Leave unconnected.7REF_FAIL1Reference 1 Failure Indicator (Output). A logic high at this pin indicates that the REF1 reference frequency has exceeded the out-of-range limit set by the OOR_SEL pin or thatit is exhibiting abrupt phase or frequency changes.8TDO Test Serial Data Out (Output). JTAG serial data is output on this pin on the falling edge of TCK. This pin is held in high impedance state when JTAG scan is not enabled.9TMS Test Mode Select (Input). JTAG signal that controls the state transitions of the TAPcontroller. This pin is internally pulled up to V DD. If this pin is not used then it should beleft unconnected.10TRST Test Reset (Input). Asynchronously initializes the JTAG TAP controller by putting it in the Test-Logic-Reset state. This pin should be pulsed low on power-up to ensure thatthe device is in the normal functional state. This pin is internally pulled up to V DD. Ifthis pin is not used then it should be connected to GND.11TCK Test Clock (Input): Provides the clock to the JTAG test logic. If this pin is not used then it should be pulled down to GND.12V CORE Positive Supply Voltage. +1.8 V DC nominal.13GND Ground. 0 V.14AV CORE Positive Analog Supply Voltage. +1.8 V DC nominal.15TDI Test Serial Data In (Input). JTAG serial test instructions and data are shifted in on this pin. This pin is internally pulled up to V DD. If this pin is not used then it should be leftunconnected.16HMS Hitless Mode Switching (Input). The HMS circuit controls phase accumulation during the transition from Holdover or Freerun mode to Normal mode on the same reference. Alogic low at this pin will cause the ZL30100 to maintain the delay stored in the TIEcorrector circuit when it transitions from Holdover or Freerun mode to Normal mode. Alogic high on this pin will cause the ZL30100 to measure a new delay for its TIE correctorcircuit thereby minimizing the output phase movement when it transitions from Holdoveror Freerun mode to Normal mode.17MODE_SEL0Mode Select 0 (Input). This input combined with MODE_SEL1 determines the mode(Normal, Holdover or Freerun) of operation, see Table4 on page17.18MODE_SEL1Mode Select 1 (Input). See MODE_SEL0 pin description.ZL30100Data Sheet Pin Description (continued)Pin # Name Description19RST Reset (Input). A logic low at this input resets the device. On power up, the RST pin must be held low for a minimum of 300ns after the power supply pins have reachedthe minimum supply voltage. When the RST pin goes high, the device will transitioninto a Reset state for 3ms. In the Reset state all outputs will be forced into highimpedance.20OSCo Oscillator Master Clock (Output). For crystal operation, a 20MHz crystal is connected from this pin to OSCi. This output is not suitable for driving other devices. For clockoscillator operation, this pin must be left unconnected.21OSCi Oscillator Master Clock (Input). For crystal operation, a 20MHz crystal is connected from this pin to OSCo. For clock oscillator operation, this pin must be connected to aclock source.22IC Internal Connection. Leave unconnected.23GND Ground. 0V.24NC No internal bonding Connection. Leave unconnected.25V DD Positive Supply Voltage. +3.3 V DC nominal.26OUT_SEL Output Selection (Input).This input selects the signals on the combined output clockand frame pulse pins, see Table3 on page17.27IC Internal Connection. Connect this pin to ground.28IC Internal Connection. Connect this pin to ground.29AV DD Positive Analog Supply Voltage. +3.3 V DC nominal.30NC No internal bonding Connection. Leave unconnected.31NC No internal bonding Connection. Leave unconnected.32C1.5o Clock 1.544MHz (Output). This output is used in DS1 applications.This clock output pad includes a Schmitt input which serves as a PLL feedback path;proper transmission-line termination should be applied to maintain reflections belowSchmitt trigger levels.33AGND Analog Ground. 0 V34AGND Analog Ground. 0 V35AV CORE Positive Analog Supply Voltage. +1.8 V DC nominal.36AV DD Positive Analog Supply Voltage. +3.3 V DC nominal.37AV DD Positive Analog Supply Voltage. +3.3 V DC nominal.38NC No internal bonding Connection. Leave unconnected.39NC No internal bonding Connection. Leave unconnected.40AGND Analog Ground.0V41AGND Analog Ground.0V42C4/C65o Clock 4.096MHz or 65.536MHz (Output). This output is used for ST-BUS operation at2.048Mbps, 4.096Mbps or 65.536MHz (ST-BUS 65.536Mbps). The output frequency isselected via the OUT_SEL pin.ZL30100Data Sheet Pin Description (continued)Pin # Name Description43C8/C32o Clock 8.192MHz or 32.768MHz (Output). This output is used for ST-BUS and GCIoperation at 8.192Mbps or for operation with a 32.768MHz clock. The output frequencyis selected via the OUT_SEL pin.44AV DD Positive Analog Supply Voltage. +3.3 V DC nominal.45AV DD Positive Analog Supply Voltage. +3.3 V DC nominal.46C2o Clock 2.048MHz (Output). This output is used for standard E1 interface timing and for ST-BUS operation at 2.048Mbps.This clock output pad includes a Schmitt input which serves as a PLL feedback path;proper transmission-line termination should be applied to maintain reflections belowSchmitt trigger levels.47C16o Clock 16.384MHz (Output). This output is used for ST-BUS operation with a16.384MHz clock.This clock output pad includes a Schmitt input which serves as a PLL feedback path;proper transmission-line termination should be applied to maintain reflections belowSchmitt trigger levels.48F8/F32o Frame Pulse (Output). This is an 8kHz 122ns active high framing pulse (OUT_SEL=0) or it is an 8kHz 31ns active high framing pulse (OUT_SEL=1), which marks thebeginning of a frame.This clock output pad includes a Schmitt input which serves as a PLL feedback path;proper transmission-line termination should be applied to maintain reflections belowSchmitt trigger levels.49F4/F65o Frame Pulse ST-BUS 2.048Mbps or ST-BUS at 65.536MHz clock (Output). Thisoutput is an 8kHz 244ns active low framing pulse (OUT_SEL=0), which marks thebeginning of an ST-BUS frame. This is typically used for ST-BUS operation at2.048Mbps and 4.096Mbps. Or this output is an 8kHz 15ns active low framing pulse(OUT_SEL=1), typically used for ST-BUS operation with a clock rate of 65.536MHz.50F16o Frame Pulse ST-BUS 8.192Mbps (Output). This is an 8kHz 61ns active low framing pulse, which marks the beginning of an ST-BUS frame. This is typically used for ST-BUSoperation at 8.192Mbps.51AGND Analog Ground.0V52IC Internal Connection. Connect this pin to ground.53REF_SEL Reference Select (Input). This input selects the input reference that is used forsynchronization, see Table5 on page19. This pin is internally pulled down to GND.54NC No internal bonding Connection. Leave unconnected.55REF0Reference (Input). This is one of two (REF0, REF1) input reference sources used for synchronization. One of five possible frequencies may be used: 8kHz, 1.544MHz,2.048MHz, 8.192MHz or 16.384MHz. This pin is internally pulled down to GND.56NC No internal bonding Connection. Leave unconnected.57REF1Reference (Input). See REF0 pin description.58NC No internal bonding Connection. Leave unconnected.ZL30100Data Sheet Pin Description (continued)Pin # Name Description59IC Internal Connection. Connect this pin to ground.60OOR_SEL Out Of Range Selection (Input). This pin selects the out of range reference rejection limits, see Table1 on page16.61V DD Positive Supply Voltage. +3.3 V DC nominal.62NC No internal bonding Connection. Leave unconnected.63TIE_CLR TIE Corrector Circuit Reset (Input). A logic low at this input resets the Time IntervalError (TIE) correction circuit resulting in a realignment of the input phase with the outputphase.64BW_SEL Filter Bandwidth Selection (Input). This pin selects the bandwidth of the DPLL loopfilter, see Table2 on page17. Set continuously high to track jitter on the input referenceclosely or set temporarily high to allow the ZL30100 to quickly lock to the input reference.3.0 Functional DescriptionThe ZL30100 is a DS1/E1 System Synchronizer providing timing (clock) and synchronization (frame) signals to interface circuits for DS1 and E1 Primary Rate Digital Transmission links, see Table 1. Figure 1 is a functional block diagram which is described in the following sections.3.1 Reference Select Multiplexer (MUX)The ZL30100 accepts two simultaneous reference input signals and operates on their rising edges. One of them, the primary reference (REF0) or the secondary reference (REF1) signal can be selected as input to the TIE corrector circuit based on the reference selection (REF_SEL) input.3.2 Reference MonitorThe input references are monitored by two independent reference monitor blocks, one for each reference. The block diagram of a single reference monitor is shown in Figure 3. For each reference clock, the frequency is detected and the clock is continuously monitored for three independent criteria that indicate abnormal behavior of the reference signal, for example; long term drift from its nominal frequency or excessive jitter. To ensure proper operation of the reference monitor circuit, the minimum input pulse width restriction of 15nsec must be observed.•Reference Frequency Detector: This detector determines whether the frequency of the reference clock is 8kHz, 1.544MHz, 2.048MHz, 8.192MHz or 16.384MHz and provides this information to the various monitor circuits and the phase detector circuit of the DPLL.•Precise Frequency Monitor: This circuit determines whether the frequency of the reference clock is within the applicable out-of-range limits selected by the OOR_SEL pin, see Figure 5, Figure 6 and Table 1. It will take the precise frequency monitor up to 10 s to qualify or disqualify the input reference.•Coarse Frequency Monitor (CFM): This circuit monitors the reference frequency over intervals of approximately 30 µs to quickly detect large frequency changes.•Single Cycle Monitor (SCM): This detector checks the period of a single clock cycle to detect large phase hits or the complete loss of the clock.ZL30100Data SheetFigure 3 - Reference Monitor CircuitExceeding the thresholds of any of the monitors forces the corresponding REF_FAIL pin to go high. The single cycle and coarse frequency failure flags force the DPLL into Holdover mode and feed a timer that disqualifies the reference input signal when the failures are present for more than 2.5s. The single cycle and coarse frequency failures must be absent for 10s to let the timer requalify the input reference signal as valid. Multiple failures of less than 2.5s each have an accumulative effect and will disqualify the reference eventually. This is illustrated in Figure 4.Figure 4 - Behaviour of the Dis/Requalify TimerWhen the incoming signal returns to normal (REF_FAIL=0), the DPLL returns to Normal mode with the output signal locked to the input signal. Each of the monitors has a build-in hysteresis to prevent flickering of the REF_FAIL status pin at the threshold boundaries. The precise frequency monitor and the timer do not affect the mode (Holdover/Normal) of the DPLL. Reference Frequency Detector Single Cycle Monitor Precise Frequency MonitorCoarse Frequency Monitor dis/requalify timerREF0 / REF1OR OR REF_DIS= reference disrupted.This is an internal signal.Mode select state machine HOLDOVERREF_DIS REF_FAIL0 / REF_FAIL12.5 s10 scurrent REFtimerREF_FAILSCM or CFM failureHOLDOVERZL30100Data SheetFigure 5 - DS1 Mode Out-of-Range Limits (OOR_SEL=0)Figure 6 - E1 Mode Out-of-Range Limits (OOR_SEL=1)3.3 Time Interval Error (TIE) Corrector CircuitThe TIE corrector circuit eliminates phase transients on the output clock that may occur during reference switching or the recovery from Holdover mode to Normal mode.On the recovery from Holdover mode (dependent on the HMS pin) or when switching to another reference input, the TIE corrector circuit measures the phase delay between the current phase (feedback signal) and the phase of the selected reference signal. This delay value is stored in the TIE corrector circuit. This circuit creates a new virtual reference signal that is at the same phase position as the feedback signal. By using the virtual reference, the PLL minimizes the phase transient it experiences when it switches to another reference input or recovers from Holdover mode.。

ZL主要特点及用途解析

ZL主要特点及⽤途解析ZL各种牌号铝合⾦的主要特点及⽤途ZL101的特点是成分简单,容易熔炼和铸造,铸造性能好,⽓密性好、焊接和切削加⼯性能也⽐较好,但⼒学性能不⾼。

适合铸造薄壁、⼤⾯积和形状复杂的、强度要求不⾼的各种零件,如泵的壳体、齿轮箱、仪表壳(框架)及家电产品上的零件等。

主要采⽤砂型铸造和⾦属型铸造。

Zl101A由于是在ZL101的基础上加了微量Ti,细化了晶粒,强化了合⾦的组织,其综合性能⾼于Zl101、ZL102,并有较好的抗蚀性能,可⽤作⼀般载荷的⼯程结构件和摩托车、汽车及家电、仪表产品上的各种结构件的优质铸件。

其使⽤量⽬前仅次于ZL102。

多采⽤砂型和⾦属型铸造。

Zl102这种合⾦的最⼤特点是流动性好,其它性能与ZL101差不多,但⽓密性⽐ZL101要好,可⽤来铸造各种形状复杂、薄壁的压铸件和强度要求不⾼的薄壁、⼤⾯积、形状复杂的⾦属或砂型铸件。

不论是压铸件还是⾦属型、砂型铸件,都是民⽤产品上⽤得最多的⼀个铸造铝合⾦品种。

Zl104因其⼯晶体量多,⼜加⼊了Mn,抵消了材料中混⼊的Fe有害作⽤,有较好的铸造性能和优良的⽓密性、耐蚀性,焊接和切削加⼯性能也⽐较好,但耐热性能较差,适合制作形状复杂、尺⼨较⼤的有较⼤负荷的动⼒结构件,如增压器壳体、⽓缸盖,⽓缸套等零件,主要⽤压铸,也多采⽤砂型和⾦属型铸造。

Zl105、ZL105A由于加⼊了Cu,降低了Si的含量,其铸造性能和焊接性能都⽐ZL104差,但室温和⾼温强度、切削加⼯性能都⽐ZL104要好,塑性稍低,抗蚀性能较差。

适合⽤作形状复杂、尺⼨较⼤、有重⼤负荷的动⼒结构件。

如增压器壳体、⽓缸盖、⽓缸套等零件。

Zl105A是降低了ZL105的杂质元素Fe的含量,提⾼了合⾦的强度,具有⽐ZL105更好的⼒学性能,多采⽤铸造优质铸件。

ZL106由于提⾼了Si的含量,⼜加⼊了微量的Ti、Mn,使合⾦的铸造性能和⾼温性能优于ZL105⽓密性、耐蚀性也较好,可⽤作⼀般负荷的结构件及要求⽓密性较好和在较⾼温度下⼯作的零件,主要采⽤砂型和⾦属型铸造。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。