R1973BBLKGILGR1;中文规格书,Datasheet资料

LM73CIMK-1中文资料

LM732.7V,SOT-23,11-to-14Bit Digital Temperature Sensor with 2-Wire InterfaceGeneral DescriptionThe LM73is an integrated,digital-output temperature sensor featuring an incremental Delta-Sigma ADC with a two-wire interface that is compatible with the SMBus and I 2C ®inter-faces.The host can query the LM73at any time to read temperature.Available in a 6-pin SOT-23package,the LM73occupies very little board area while operating over a wide temperature range (-40˚C to 150˚C)and providing ±1.0˚C accuracy from -10˚C to 80˚C.The user can optimize be-tween the conversion time and the sensitivity of the LM73by programming it to report temperature in any of four different resolutions.Defaulting to 11-bit mode (0.25˚C/LSB),the LM73measures temperature in a maximum time of 14ms,making it ideal for applications that require temperature data very soon after power-up.In its maximum resolution,14-bit mode (0.03125˚C/LSB),the LM73is optimized to sense very small changes in temperature.A single multi-level address line selects one of three unique device addresses.An open-drain ALERT output goes active when the temperature exceeds a programmable limit.Both the data and clock lines are filtered for excellent noise toler-ance and reliable communication.Additionally,a time-out feature on the clock and data lines causes the LM73to automatically reset these lines if either is held low for an extended time,thus exiting any bus lock-up condition without processor intervention.Applicationsn Portable Electronics n Notebook Computers n Automotiven System Thermal Management nOffice ElectronicsKey Specificationsj Supply Voltage 2.7V to 5.5Vj Supply Currentoperating 320µA (typ)495µA (max)shutdown8µA (max)1.9µA (typ)j Temperature −10˚C to 80˚C ±1.0˚C (max)Accuracy−25˚C to 115˚C ±1.5˚C (max)−40˚C to 150˚C±2.0˚C (max)j Resolution 0.25˚C to 0.03125˚Cj Conversion Time11-bit (0.25˚C)14ms (max)14-bit (0.03125˚C)112ms (max)Featuresn Single address pin offers choice of three selectable addresses per version for a total of six possible addresses.n SMBus and I 2C-compatible two-wire interface n Supports 400kHz operationn Shutdown mode with one-shot feature available for very low average power consumptionn Programmable digital temperature resolution from 11bits to 14bits.n Fast conversion rate ideal for quick power up and measuring rapidly changing temperaturen Open-drain ALERT output pin goes active whentemperature is above a programmed temperature limit n Very stable,low-noise digital ouput.n UL Recognized ComponentTypical Application20147803I 2C is a registered trademark of Philips Electronics N.V.CorporationJuly 2006LM732.7V,SOT-23,11-to-14Bit Digital Temperature Sensor with 2-Wire Interface©2006National Semiconductor Corporation Simplified Block Diagram20147801Connection DiagramSOT23-620147802TOP VIEWL M 73 2Ordering InformationPart Number PackageMarkingNS PackageNumberTransportMediaSMBus Device AddressAddress Pin Device AddressLM73CIMK-0T730MK06A(Thin SOT23-6)1000Units onTape and ReelFloatGroundV DD100100010010011001010LM73CIMKX-0T730MK06A(Thin SOT23-6)3000Units onTape and ReelFloatGroundV DD100100010010011001010LM73CIMK-1T731MK06A(Thin SOT23-6)1000Units onTape and ReelFloatGroundV DD100110010011011001110LM73CIMKX-1T731MK06A(Thin SOT23-6)3000Units onTape and ReelFloatGroundV DD100110010011011001110Note1:Available in RoHS-compliant packages.More details at .Pin DescriptionsLabel Pin#Type Equivalent Circuit FunctionADDR1Logic Input,threelevels Address Select Input:One of three device addresses is selected by connecting to ground,left floating,or connecting to V DD.GND2Ground GroundV DD3Power Supply VoltageSMBCLK4CMOS LogicInput Serial Clock:SMBus clock signal. Operates up to400kHz.Low-pass filtered.ALERT5Open-DrainOutput Digital output which goes active whenever the measured temperature exceeds a programmable temperature limit.SMBDAT6Open-DrainInput/OutputSerial Data:SMBus bi-directionaldata signal used to transfer serialdata synchronous to the SMBCLK.Low-pass filtered.LM733Absolute Maximum Ratings (Note 2)Supply Voltage −0.3V to 6.0VVoltage at Any Pin −0.3V to (V DD +0.5V)Input Current at Any Pin (Note 3)±5mAStorage Temperature −65˚C to +150˚CESD Susceptibility (Note 5)Human Body Model 2000V Machine Model200VSoldering process must comply with National Semiconductor’s Reflow Temperature Profilespecifications.Refer to /packaging.(Note 4)Operating Ratings(Note 2)Specified Temperature Range T MIN ≤T A ≤T MAX -40˚C ≤T A ≤+150˚CSupply Voltage Range (V DD )+2.7V to +5.5VTemperature-to-Digital Converter CharacteristicsUnless otherwise noted,these specifications apply for V DD =2.7V to 5.5V.Boldface limits apply for T A =T J =T MIN to T MAX ;all other limits T A =T J =+25˚C,unless otherwise noted.T A is the ambient temperature.T J is the junction temperature.ParameterConditionsTypical Limits Units (Note 6)(Note 7)(Limit)Accuracy (Note 8)V DD =2.7V to V DD =4.5V T A =−10˚C to 80˚C ±1.0˚C (max)T A =−25˚C to 115˚C ±1.5˚C (max)T A =−40˚C to 150˚C ±2.0˚C (max)V DD >4.5V to V DD =5.5VT A =−10˚C to 80˚C ±1.5˚C (max)T A =−25˚C to 115˚C ±2.0˚C (max)T A =−40˚C to 150˚C±2.5˚C (max)ResolutionRES1Bit =0,RES0Bit =011Bits 0.25˚C/LSB RES1Bit =0,RES0Bit =112Bits 0.125˚C/LSB RES1Bit =1,RES0Bit =013Bits 0.0625˚C/LSB RES1Bit =1,RES0Bit =114Bits 0.03125˚C/LSB Temperature Conversion Time (Note 9)RES1Bit =0,RES0Bit =010.114ms (max)RES1Bit =0,RES0Bit =120.228ms (max)RES1Bit =1,RES0Bit =040.456ms (max)RES1Bit =1,RES0Bit =180.8112ms (max)Quiescent CurrentContinuous Conversion Mode,SMBus inactive 320495µA (max)Shutdown,bus-idle timers on 120175µA (max)Shutdown,bus-idle timers off1.98µA (max)Power-On Reset ThresholdMeasured on V DD input,falling edge0.9V (min)L M 73 4Logic Electrical CharacteristicsDIGITAL DC CHARACTERISTICSUnless otherwise noted,these specifications apply for V DD=2.7V to5.5V.Boldface limits apply for T A=T J=T MIN to T MAX; all other limits T A=T J=+25˚C,unless otherwise noted.T A is the ambient temperature.T J is the junction temperature.Symbol Parameter Conditions Typical Limits Units(Note6)(Note7)(Limit) SMBDAT,SMBCLK INPUTSV IH Logical“1”Input Voltage0.7*V DD V(min)V IL Logical“0”Input Voltage0.3*V DD V(max)V IN;HYST SMBDAT and SMBCLK Digital InputHysteresis0.07*V DD VI IH Logical“1”Input Current V IN=V DD0.012µA(max) I IL Logical“0”Input Current V IN=0V–0.01–2µA(max) C IN Input Capacitance5pF SMBDAT,ALERT OUTPUTSI OH High Level Output Current V OH=V DD0.012µA(max) V OL SMBus Low Level Output Voltage I OL=3mA0.4V(max) ADDRESS INPUTV IH;ADDRESS Address Pin High Input Voltage V DD minus0.100V(min)V IL;ADDRESS Address Pin Low Input Voltage0.100V(max)I IH;ADDRESS Address Pin High Input Current V IN=V DD0.012µA(max) I IL;ADDRESS Address Pin Low Input Current V IN=0V–0.01–2µA(max) SMBus DIGITAL SWITCHING CHARACTERISTICSUnless otherwise noted,these specifications apply for V DD=+2.7V to+5.5V,C L(load capacitance)on output lines=400pF. Boldface limits apply for T A=T J=T MIN to T MAX;all other limits T A=T J=+25˚C,unless otherwise noted.Symbol Parameter Conditions Typical Limits Units(Note6)(Note7)(Limit)f SMB SMBus Clock Frequency400100kHz(max) Hz(min)t LOW SMBus Clock Low Time300ns(min) t HIGH SMBus Clock High Time300ns(min) t F;SMBO Output Fall Time(Note10)C L=400pFI PULL-UP≤3mA250ns(max)t TIMEOUT SMBDAT and SMBCLK Time Low for Reset of Serial Interface(Note11)1545ms(min)ms(max)t SU;DAT Data In Setup Time to SMBCLK High100ns(min)t HD;DATI Data Hold Time:Data In Stable after SMBCLKLow0ns(min)t HD;DATO Data Hold Time:Data Out Stable afterSMBCLK Low30ns(min)t HD;STA Start Condition SMBDAT Low to SMBCLKLow(Start condition hold before the first clockfalling edge)60ns(min)t SU;STO Stop Condition SMBCLK High to SMBDATLow(Stop Condition Setup)50ns(min)t SU;STA SMBus Repeated Start-Condition Setup Time,SMBCLK High to SMBDAT Low50ns(min)t BUF SMBus Free Time Between Stop and StartConditions1.2µs(min)t POR Power-On Reset Time(Note12)1ms(max)LM735SMBus Communication20147809Note 2:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.DC and AC electrical specifications do not apply when operating the device beyond its rated operating conditions.Note 3:When the input voltage (V I )at any pin exceeds the power supplies (V I <GND or V I >V DD ),the current at that pin should be limited to 5mA.Note 4:Reflow temperature profiles are different for lead-free and non-lead-free packages.Note 5:Human body model,100pF discharged through a 1.5k Ωresistor.Machine model,200pF discharged directly into each pin.Note 6:Typicals are at T A =25˚C and represent most likely parametric norm.Note 7:Limits are guaranteed to National’s AOQL (Average Outgoing Quality Level).Note 8:Local temperature accuracy does not include the effects of self-heating.The rise in temperature due to self-heating is the product of the internal power dissipation of the LM73and the thermal resistance.Note 9:This specification is provided only to indicate how often temperature data is updated.The LM73can be read at any time without regard to conversion state (and will yield last conversion result).Note 10:The output fall time is measured from (V IL;MAX -0.15V)to (V IH;MIN +0.15V).Note 11:Holding the SMBDAT and/or SMBCLK lines Low for a time interval greater than t TIMEOUT will reset the LM73’s SMBus state machine,setting SMBDAT and SMBCLK pins to a high impedance state.Note 12:Represents the time from V DD reaching the power-on-reset level to the LM73communications being functional.After an additional time equal to one temperature conversion time,valid temperature will be available in the Temperature Register.Note 13:A write to an invalid pointer address is not allowed.If the master writes an invalid address to the Pointer Register,(1)the LM73will not acknowledge the address and (2)the Pointer Register will continue to contain the last value stored in it.L M 73 6Typical Performance CharacteristicsAccuracy vs.TemperatureOperating Current vs.Temperature2014782020147821Shutdown Current vs.Temperature Typical Output Noise2014782220147823LM7371.0Functional DescriptionThe LM73is a digital temperature sensor that senses the temperature of its die using a sigma-delta analog-to-digital converter and stores the temperature in the Temperature Register.The LM73’s 2-wire serial interface is compatible with SMBus 2.0and I 2C.Please see the SMBus 2.0speci-fication for a detailed description of the differences between the I 2C bus and SMBus.The temperature resolution is programmable,allowing the host system to select the optimal configuration between sensitivity and conversion time.The LM73can be placed in shutdown to minimize power consumption when tempera-ture data is not required.While in shutdown,a 1-shot con-version mode allows system control of the conversion rate for ultimate flexibility.The LM73features the following registers.See Section 2.0for a complete list of the pointer address,content,and reset state of each register.1.Pointer Register2.Temperature Register3.Configuration Register4.T HIGH Register5.T LOW Register6.Control/Status Register7.Identification Register1.1POWER-ON RESETThe power-on reset (POR)state is the point at which the supply voltage rises above the power-on reset threshold (specified in the electrical specifications table),generating an internal reset.Each of the registers contains a defined value upon POR and this data remains there until any of the following occurs:1.The first temperature conversion is completed,causing the Temperature Register and various status bits to be updated internally,depending on the value of the mea-sured temperature2.The master writes different data to any R/W bits3.The LM73is powered down1.2ONE-SHOT CONVERSIONThe LM73features a one-shot conversion bit,which is used to initiate a single conversion and comparison cycle when the LM73is in shutdown mode.While the LM73is in shut-down mode,writing a "1"to the One-Shot bit in the Configu-ration Register will cause the LM73to perform a single temperature conversion and update the Temperature Regis-ter and the affected status bits.Operating the LM73in this one-shot mode allows for extremely low average-power con-sumption,making it ideal for low-power applications.When the One-Shot bit is set,the LM73initiates a tempera-ture conversion.After this initiation,but before the comple-tion of the conversion and resultant register updates,the LM73is in a "one-shot"state.During this state,the Data Available (DAV)flag in the Control/Status register is "0"and the Temperature Register contains the value 8000h (-256˚C).All other registers contain the data that waspresent before initiating the one-shot conversion.After the temperature measurement is complete,the DAV flag will be set to "1"and the temperature register will contain the result-ant measured temperature.1.3TEMPERATURE DATA FORMATThe resolution of the temperature data and the size of the data word are user-selectable through bits RES1and RES0in the Control/Status Register.By default,the LM73tem-perature stores the measured temperature in an 11-bit (10bits plus sign)word with one least significant bit (LSB)equal to 0.25˚C.The maximum word size is 14bits (13-bits plus sign)with a resolution of 0.03125˚C/LSB.CONTROL BIT DATA FORMATRES1RES0WORD SIZE RESOLUTION 0011bits 0.25˚C/LSB 0112bits 0.125˚C/LSB 1013bits 0.0625˚C/LSB 1114bits0.03125˚C/LSBThe temperature data is reported in 2’s complement format.The word is stored in the 16-bit Temperature Register and is left justified in this register.Unused temperature-data bits are always reported as "0".11-bit (10-bit plus sign)Temperature Digital Output BinaryHex +150˚C 01001011000000004B00h +25˚C 00001100100000000C80h +1˚C 00000000100000000080h +0.25˚C 00000000001000000020h 0˚C 00000000000000000000h −0.25˚C 1111111111100000FFE0h −1˚C 1111111110000000FF80h −25˚C 1111001110000000F380h −40˚C1110110000000000EC00h12-bit (11-bit plus sign)Temperature Digital Output BinaryHex +150˚C 01001011000000004B00h +25˚C 00001100100000000C80h +1˚C 00000000100000000080h +0.125˚C 00000000000100000010h 0˚C 00000000000000000000h −0.125˚C 1111111111110000FFF0h −1˚C 1111111110000000FF80h −25˚C 1111001110000000F380h −40˚C1110110000000000EC00h L M 73 81.0Functional Description(Continued)13-bit(12-bit plus sign)Temperature Digital OutputBinary Hex +150˚C01001011000000004B00h+25˚C00001100100000000C80h+1˚C00000000100000000080h +0.0625˚C00000000000010000008h 0˚C00000000000000000000h −0.0625˚C1111111111111000FFF8h −1˚C1111111110000000FF80h−25˚C1111001110000000F380h−40˚C1110110000000000EC00h14-bit(13-bit plus sign)Temperature Digital OutputBinary Hex +150˚C01001011000000004B00h+25˚C00001100100000000C80h+1˚C00000000100000000080h +0.03125˚C00000000000001000004h 0˚C00000000000000000000h −0.03125˚C1111111111111100FFFCh −1˚C1111111110000000FF80h−25˚C1111001110000000F380h−40˚C1110110000000000EC00h1.4SMBus INTERFACEThe LM73operates as a slave on the SMBus.The SMBDAT line is bidirectional.The SMBCLK line is is an input only.The LM73never drives the SMBCLK line and it does not support clock stretching.The LM73uses a7-bit slave address.It is available in two versions.Each version can be configured for one of three unique slave addresses,for a total of six unique address.Part NumberAddress PinDevice AddressLM73-0FloatGroundV DD 1001000 1001001 1001010LM73-1FloatGroundV DD 100110010011011001110The SMBDAT output is an open-drain output and does nothave internal pull-ups.A“high”level will not be observed onthis pin until pull-up current is provided by some externalsource,typically a pull-up resistor.Choice of resistor valuedepends on many system factors but,in general,the pull-upresistor should be as large as possible without effecting theSMBus desired data rate.This will minimize any internaltemperature reading errors due to internal heating of theLM73.The LM73features an integrated low-pass filter on both theSMBCLK and the SMBDAT line.These filters increase com-munications reliability in noisy environments.If either the SMBCLK or SMBDAT line is held low for a timegreater than t TIMEOUT(see Logic Electrical Characteristicsfor the value of t TIMEOUT),the LM73state machine will resetto the SMBus idle state,releasing the data line.Once theSMBDAT is released high,the master may initiate an SMBusstart.1.5ALERT FUNCTIONThe ALERT output is an over-temperature indicator.At theend of every temperature conversion,the measured tem-perature is compared to the value in the T HIGH Register.Ifthe measured temperature exceeds the value stored inT HIGH,the ALERT output goes active(see Figure Figure1).This over-temperature condition will also cause the ALRT-_STAT bit in the Control/Status Register to change value(this bit mirrors the logic level of the ALERT pin).The ALERT pin and the ALRT_STAT bit are cleared whenany of the following occur:1.The measured temperature falls below the value storedin the T LOW Register2.A"1"is written to the ALERT Reset bit in the Configura-tion Register3.The master resets it through an SMBus Alert ResponseAddress(ARA)procedureIf ALERT has been cleared by the master writing a"1"to theALERT Reset bit,while the measured temperature still ex-ceeds the T HIGH setpoint,ALERT will go active again afterthe completion of the next temperature conversion.Each temperature reading is associated with a TemperatureHigh(THI)and a Temperature Low(TLOW)flag in theControl/Status Register.A digital comparison determineswhether that reading is above the T HIGH setpoint or belowthe T LOW setpoint.If so,the corresponding flag is set.Alldigital comparisons to the T HIGH,and T LOW values are basedon an11-bit temperature comparison.Regardless of theresolution setting of the LM73,the lower three temperatureLSBs will not affect the state of the ALERT output,THI flag,and TLOW flag.LM7391.0Functional Description(Continued)1.6COMMUNICATING with the LM73The data registers in the LM73are selected by the Pointer Register.At power-up the Pointer Register is set to “00h”,the location for the Temperature Register.The Pointer Register latches the last location it was set to.Note that all Pointer Register bits are decoded;any incorrect pointer values will not be acknowledged and will not be stored in the Pointer Register (Note 13).A Write to the LM73will always include the address byte and the pointer byte.A Read from the LM73can take place either of two ways:1.If the location latched in the Pointer Register is correct (that is,the Pointer Register is pre-set prior to the read),then the read can simply consist of an address byte,followed by retrieving the data byte.Most of the time it is expected that the Pointer Register will point to Tempera-ture Registers because that will be the data most fre-quently read from the LM73.2.If the Pointer Register needs to be set,then an address byte,pointer byte,repeat start,and another address byte will accomplish a read.The data byte is read out of the LM73by the most significant bit first.At the end of a read,the LM73can accept either an Acknowledge or No Acknowledge bit from the Master.No Acknowledge is typically used as a signal to the slave that the Master has read its last byte.20147816FIGURE 1.ALERT Temperature Response clearedwhen temperature crosses T LOW20147817FIGURE 2.ALERT Temperature Response cleared bywriting a "1"to the ALERT Reset Bit.L M 73 101.0Functional Description(Continued)20147810(a)Typical Read from a 2-Byte Register with Preset Pointer20147811(b)Typical Pointer Set Followed by Immediate Read of a 2-Byte Register20147812(c)Typical Read from a 1-Byte Register with Preset Pointer20147813(d)Typical Pointer Set Followed by Immediate Read of a 1-Byte Register.FIGURE 3.Reading from the LM73LM73111.0Functional Description(Continued)20147814(a)Typical 1-Byte Write20147815(b)Typical 2-Byte Write FIGURE 4.Writing to the LM73L M 73 12LM73 2.0LM73RegistersThe LM73’s internal registers are selected by the Pointer register.The Pointer register latches the last location that it was set to.The pointer register and all internal registers are described below.All registers reset at device power up.2.1POINTER REGISTERThe diagram below shows the Pointer Register,the six internal registers to which it points,and their associated pointer addresses.20147807P7P6P5P4P3P2P1P000000Register SelectBits Name Description7:3Not Used Must write zeros only.2:0Register Select Pointer address.Points todesired register.See tablebelow.P2P1P0REGISTER(Note13)000Temperature001Configuration010T HIGH011T LOW100Control/Status111Identification132.0LM73Registers(Continued)2.2TEMPERATURE DATA REGISTER Pointer Address 00h (Read Only)Reset State:7FFCh (+255.96875˚C)One-Shot State:8000h (-256˚C)D15D14D13D12D11D10D9D8SIGN 128˚C 64˚C 32˚C 16˚C 8˚C 4˚C 2˚C D7D6D5D4D3D2D1D01˚C 0.5˚C0.25˚C 0.125˚C0.0625˚C0.03125˚CreservedreservedBits NameDescription15:2Temperature DataRepresents the temperature that was measured by the most recent temperature conversion.On Power-up,this data is invalid until the Data Available (DAV)bit in the Control/Status register is high (after the completion of the first temperature conversion).The resolution is user-progammable from 11-bit resolution (0.25˚C/LSB)through 14-bit resolution (0.03125˚C/LSB).The desired resolution is programmed with bits 5and 6of the Control/Status register.1:0Not UsedReturn zeros upon read.2.3CONFIGURATION REGISTER Pointer Address 01h (R/W)Reset State:40hD7D6D5D4D3D2D1D0PD reservedALRT EN ALRT POLALRT RSTONE SHOTreservedBits NameDescription7Full Power Down Writing a 1to this bit puts the LM73in shutdown mode for power conservation.Writing a 0puts the LM73into normal mode.6reserved User must write only a 1to this bit5ALERT EnableA 0in this location enables the ALERT output.A 1disables it.This bit also controls the ALERT Status bit (the Control/Status Register,Bit 3)since that bit reflects the state of the Alert pin.4ALERT Polarity When set to 1,the ALERT pin and ALERT Status bit are active-high.When 0,it is active-low.3ALERT Reset Writing a 1to this bit resets the ALERT pin and the ALERT Status bit.It will always be 0when read.2One ShotWhen in shutdown mode (Bit 7is 1),initiates a single temperature conversion and update of the temperature register with new temperature data.Has no effect when in continuous conversion mode (i.e.,when Bit 7is 0).Always returns a 0when read.1:0ReservedUser must write only a 0to these bits.2.4T HIGH UPPER-LIMIT REGISTER Pointer Address 02h (R/W)Reset State:7FE0h (+255.75˚C)D15D14D13D12D11D10D9D8SIGN 128˚C 64˚C 32˚C 16˚C 8˚C 4˚C 2˚C D7D6D5D4D3D2D1D01˚C 0.5˚C0.25˚C reservedBits Name Description15:5Upper-Limit Temperature If the measured temperature that is stored in this register exceeds this user-programmable upper temperature limit,the ALERT pin will go active and the THIGH flag in the Control/Status register will be set to 1.Two’s complement format.4:0ReservedReturns zeros upon read.Recommend writing zeros only in these bits.L M 73142.0LM73Registers(Continued)2.5T LOW LOWER-LIMIT REGISTERPointer Address03h(R/W)Reset State:8000h(–256˚C)D15D14D13D12D11D10D9D8 SIGN128˚C64˚C32˚C16˚C8˚C4˚C2˚C D7D6D5D4D3D2D1D0 1˚C0.5˚C0.25˚C reservedBits Name Description15:5Lower-LimitTemperature If the measured temperature that is stored in the temperature register falls below thisuser-programmable lower temperature limit,the ALERT pin will be deactivated and the T LOW flag in the Control/Status register will be set to1.Two’s complement format.4:0Reserved Returns zeros upon read.Recommend writing zeros only in these bits.2.6CONTROL/STATUS REGISTERPointer Address04h(R/W)Reset State:08hD7D6D5D4D3D2D1D0 TO_DIS RES1RES0reserved ALRT_STAT THI TLOW DAV Bits Name Description7Time-Out Disable Disable the time-out feature on the SMBDAT and SMBCLK lines if set to1.Setting this bitturns off the bus-idle timers,enabling the LM73to operate at lowest shutdown current.6:5TemperatureResolution Selects one of four user-programmable temperature data resolutions 00:0.25˚C/LSB,11-bit word(10bits plus sign)01:0.125˚C/LSB,12-bit word(11bits plus sign)10:0.0625˚C/LSB,13-bit word(12bits plus sign)11:0.03125˚C/LSB,14-bit word(13bits plus sign)4reserved Always returns zero when read.Recommend customer write zero only.3ALERT Pin Status Value is0when ALERT output is low.Value is1when ALERT output is high.The ALERToutput is reset under any of the following conditions:(1)Cleared by writing a1to the ALERTReset bit in the configuration register,(2)Measured temperature falls below the T LOW limit,or(3)cleared via the ARA sequence.Recommend customer write zero only.2Temperature HighFlag Bit is set to1when the measured temperature exceeds the T HIGH limit stored in the programmable T HIGH register.Flag is reset to0when both of the following conditions are met:(1)measured temperature no longer exceeds the programmed T HIGH limit and(2)upon reading the Control/Status register.If the temperature is not longer above the T HIGH limit,this status bit remains set until it is read by the master so that the system can check the history of what caused the ALERT output to go active.This bit is not cleared after every read if the measured temperature is still above the T HIGH limit.1Temperature LowFlag Bit is set to1when the measured temperature falls below the T LOW limit stored in the programmable T LOW register.Flag is reset to0when both of the following conditions are met:(1)measured temperature is no longer below the programmed T LOW limit and(2)upon reading the Control/Status register.If the temperature is no longer below the T LOW limit,the status bit remains set until it is read by the master so that the system can check the history of what cause the ALERT output to go active.This bit is not cleared after every read if temperature is still below T LOW limit.0Data Available Flag This bit is0when the LM73is in the process of converting a new temperature.It is1whenthe conversion is done.After initiating a temperature conversion while operating in theone-shot mode,this status bit can be monitored to indicate when the conversion is done.After triggering the one-shot conversion,the data in the temperature register is invalid untilthis bit is high(that is,after completion of the conversion).On power-up,the LM73is incontinuous conversion mode;while in continuous conversion mode(the default mode afterpower-on reset)this bit will always be high.Recommend customer write zero only.LM7315。

SP73贴片电感规格书

Reviesd: 07/14/2020

3/8

SMD Power Inductor

SP73 Series

SHENZHEN CODACA ELECTRONIC CO., LTD

This product is not authorized for use in any application related to safety. Specification subject to change without notice.Please check web site for latest information.

■ All data is tested based on 25℃ ambient temperature. 所有数据基于环境温度 25℃条件下测试。

※1 Inductance measure condition at 1kHz, 0.25V. 电感测试条件为 1kHz, 0.25V。

※2 Saturation current:the actual value of DC current when the inductance decrease 20% of its initial value. 饱和电流:电感值下降其初始值的 20%时所加载的实际直流电流值。

Inductance (μH) 电感值 ※1

1.00 ±20% 2.20 ±20% 3.30 ±20% 4.70 ±20% 6.80 ±20% 8.20 ±20% 10.0 ±10% 12.0 ±10% 15.0 ±10% 18.0 ±10% 22.0 ±10% 27.0 ±10% 33.0 ±10% 39.0 ±10% 47.0 ±10% 56.0 ±10% 68.0 ±10% 82.0 ±10% 100 ±10% 120 ±10% 150 ±10% 180 ±10% 220 ±10% 270 ±10% 330 ±10% 390 ±10% 470 ±10% 560 ±10% 680 ±10% 820 ±10% 1,000 ±10%

IRLML0100TRPBF;中文规格书,Datasheet资料

0.1

TJ = 25°C

VDS = 50V ≤60µs PULSE WIDTH

0.01

1.5

2.0

2.5

3.0

3.5

VGS, Gate-to-Source Voltage (V)

Fig 3. Typical Transfer Characteristics

RDS(on) , Drain-to-Source On Resistance (Normalized)

/

ID , Drain Current (A)

IRLML0100TRPbF

2.0

RD

VDS

1.5

VGS RG

D.U.T.

+-VDD

1.0

VGS

Pulse Width ≤ 1 µs

Duty Factor ≤ 0.1 %

0.5

Fig 10a. Switching Time Test Circuit

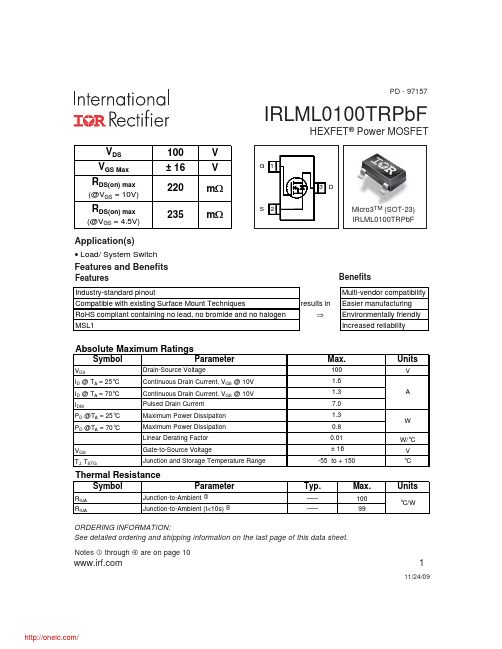

Application(s) • Load/ System Switch Features and Benefits Features

Industry-standard pinout Compatible with existing Surface Mount Techniques RoHS compliant containing no lead, no bromide and no halogen MSL1

PD - 97157

IRLML0100TRPbF

HEXFET® Power MOSFET

VDS

100

V

VGS Max

± 16

V

G1

RDS(on) max

博布里克洗手间设备产品数据手册说明书

The manufacturer reserves the right to, and does from time to time, make changes and improvements in designs and dimensions. © 2008 by Bobrick Washroom Equipment, Inc.materialS:Stiles c—3/4'' (19mm) thick, Solid Color Reinforced Composite with GraffitiOff ™ surface thermoset and integrally fused into one homogenous piece. Surface, edge, core are to be the same color. Leveling device: 7 gauge, 3/16" (5mm) thick, corrosion-resistant, chromate-treated, double zinc-plated steel angle leveling bar bolted to stile; furnished with 3/8'' (10mm) stainless steel diameter threaded wedge anchor, hex nuts, lock washer, flat washers, and shoe retainers. Shoe: 18-8 S, type-304, 22-gauge (0.8mm) stainless steel with satin finish; 4'' (102mm) high.Panels —1/2'' (13mm) thick, Solid Color Reinforced Composite with GraffitiOff ® surface thermoset and integrally fused into one homogeneous piece. Surface, edge, core are to be the same color.doors —3/4'' (19mm) thick, Solid Color Reinforced Composite with GraffitiOff ® surface thermoset and integrally fused into one homogeneous piece. Surface, edge, core are to be the same color.Posts (for 1093 Series screens only) — 1-1/4'' (32mm) square tubing; 18-8 S, type-304, 18-gauge (1.2mm) stainless steel with satin finish. Floor and ceiling connections are constructed of 18-8 S, type-304, heavy-gauge stainless steel. Furnished in 10-ft (305-cm) lengths; to be cut in field to job specifications.Headrail (for 1092 Series compartments only) —Extruded anodized aluminum with satin finish. Enclosed construction with sloping top. Face has raised grip-resistant edge.Designer's Notes: Headrails with integral curtain tracks and hooks are available for compartments without doors. Optional vinyl curtains are available.Wall Posts —1" x 1-1/2" (25 x 38mm) tubing; 18-8 S, type-304, 16-gauge (1.6mm) stainless steel with satin-finish. 58" (147cm) high, pre-drilled for door hardware.Heavy-duty Hardware (standard) — Hinges, door latches, door keepers, clothes hooks, door stop plates, and mounting brackets are constructed of 18-8 S, type-304, heavy-gauge stainless steel with satin finish. Threaded inserts are factory installed for securing hinges, door stop plates, and door latches. Theft-resistant, stainless steel pin-in-head Torx screws are furnished for door hardware and all mounting brackets. Barrel hinge is adjustable to adjust door swing of unoccupied toilet compartment from partially open to fully closed. Toilet compartment door is locked from inside by sliding door latch into keeper. Threaded inserts are factory installed to secure door hinges, latch and door stops. Two door stops prevents door from being kicked in/out beyond stile by vandals. Mounting screws for stile to panel bracket, latch keeper, and coat hook connections are through-bolted.institutional Hardware (.67 option) —Hinges, door latches, door keepers, clothes hook, U-channels, door stop plates and angle brackets are constructed of 18-8 S, type-304, heavy-gauge stainless steel with satin finish: one-piece, full-height hinge is 16 gauge (1.6mm); one-piece door keeper is 11 gauge (3.2mm);one-piece, full-height U-channels and angle brackets are 18 gauge (1.2mm). U-channels secure panels to stiles, and angle brackets secure panels and stiles to walls. Door latch slides on a shock-resistant nylon track. Two door stops prevent door from being kicked in/out beyond stile by vandals. Theft-resistant, stainless steel pin-in-head Torx screws are furnished for door hardware, U-channels, and angle brackets. Doors are equipped with a self-closing hinge. Threaded inserts are factory installed to secure door hinge, latch, and doorstops. Mounting screws for stile-to-panel brackets and latch keeper connections are through-bolted. To specify institutional hardware, add suffix .67 to series number. Example: specify 1092.67 for overhead-braced partitions furnished with institutional hardware, including factory-installed threaded inserts for door hardware attachment.inStallation:Bobrick installation instructions are packed with each shipment and are available also in advance on request.notes:1. Ceiling-hung and floor-to-ceiling toilet compartments require structural members (not furnished by Bobrick) in ceiling. For suggested types of ceiling supportsystems, see Bobrick Advisory Bulletin TB-32.2. Wall backing is required to secure the mounting brackets of panels, stiles, and wall posts. For suggested wall backing, see Bobrick Advisory Bulletin TB-46.3. Floor-anchored stiles are furnished with expansion shields and threaded rods. The expansion shields require minimum 2'' (50mm) penetration into minimum3'' (75mm) thick structural concrete.4. Bobrick stainless steel partition-mounted washroom accessories are available for mounting in panels between two compartments. See current Bobrick Catalogfor description of accessories. Cutouts in panels can be pre-cut for Bobrick models at factory if location and size of all cutouts and Bobrick model numbers are furnished at time of order.GUarantee:Bobrick toilet partitions including all hardware and mounting brackets are guaranteed to be free from defects in material and workmanship for a period of one year from date of purchase. Any products returned to Bobrick under this guarantee will be repaired or replaced at no charge. 10-Year Warranty: Bobrick ex-tends a ten-year limited warranty from date of purchase for SierraSeries® Solid Color Reinforced Composite partition panels, doors, and stiles against breakage, warpage, delamination and corrosion when materials are properly installed, and normally used.SpeCiFiCation:Water-resistant, solid color reinforced composite ____________________ (insert one: toilet partitions, dressing compartments, shower dividers, urinal screens) shall be _______________ (insert one: overhead-braced toilet partition or floor anchored, wall-hung, post-to-ceiling urinal screens). Stiles, panels and doors shall be constructed of Solid Color Reinforced Composite with GraffitiOff ® surface thermoset and integrally fused into one homogeneous piece. Surface, edges and core are to be same color. Solid Color Reinforced Composite material shall be covered by a 10-year limited warranty against breakage, warpage, corrosion, and delamination. Stiles and doors shall be 3/4'' (19mm) thick; panels shall be 1/2'' (13mm) thick. All units shall meet ICC and NFPA Class B or UBC Class II, ASTME 84 Fire-Resistance Standards. Stiles shall have leveling device that is concealed by a one-piece, type-304, satin-finish stainless steel shoe that is 4'' (102mm) high.Stiles, panels and doors shall be __________ (insert color name and number from current Bobrick catalog). Headrails for overhead-braced compartments shall be anodized aluminum with satin finish. **All door hardware and mounting brackets shall be type-304 stainless steel with satin finish. All doors shall be supplied with three hinges. Threaded inserts shall be factory installed for securing door hinges, latches and door stops. Theft-resistant, stainless steel pin-in-head Torx screws shall be furnished for door hardware and all mounting brackets. Through bolts shall be used for securing latch keeper, clothes hook and panel-to-stile brackets. A clothes hook shall be furnished for each door with heavy duty hardware option. Hinges shall be adjustable to hold doors of unoccupied compartments partially open or fully closed. Two door stops shall be furnished for each door to prevent it from being kicked in/out beyond stile by vandals. Manufacturer's service and parts manual shall be provided to the building owner/manager upon completion of project.**To specify Institutional hardware, replace end of specification paragraph with: .67 option All door hardware, U-channels, and angle brackets shall be type-304 stainless steel with satin finish: one-piece, full-height hinges shall be 16 gauge (1.6mm); one-piece door keepers shall be 11 gauge (3.2mm); one-piece, full-height U-channels and angle brackets shall be 18 gauge (1.2mm). U-channels shall be furnished to secure panels to stiles, and angle brackets furnished to secure panels and stiles to walls. Doors shall be equipped with a self-closing hinge. Two door stops shall be furnished for each door to prevent it from being kicked in/out beyond stile by vandals. A clothes hook shall be furnished for each door. Theft-resistant, stainless steel pin-in-head, Torx screws shall be furnished for door hardware, U-channels, and angle brackets. Through bolts shall be used for securing latch keeper and panel- to-stiles brackets. Threaded inserts shall be factory installed to secure all door hinges, latches, and doorstops. Manufacturer's service and parts manual shall be provided to the building owner/manager upon request._________________ (insert one: toilet Partitions, dressing Compartments, Shower dividers, Urinal Screens) shall be ____________________ Series (insert series number) of Bobrick Washroom equipment, inc., Clifton Park, new York; Jackson, tennessee; Los Angeles, California; Bobrick Washroom equipment Company, Scarborough, ontario; Bobrick Washroom equipment Pty. Ltd., Australia; and Bobrick Washroom equipment Limited, United Kingdom.The illustrations and descriptions herein are applicable to production as of the date of this Technical Data Sheet. 1090 Revised 8/08 Printed in U.S.A. The manufacturer reserves the right to, and does from time to time, make changes and improvements in designs and dimensions. © 2008 by Bobrick Washroom Equipment, Inc.。

LG iGX样本(中文版)

-Solution Leader in Electrics& Automation

STARVERT G X

紧凑高性能变频器

0.4~22kW 3Phase 380~480Volts

Automatiom Equipment

New Name of

小心选择电流断路器. 当变频器上电的时候,可能有大 的浪涌电流涌入

为了使变频器长时间运行在高性能状态下,请把变频器安 装在正确的方向的适当的位置,留出适当的空间.不正确的 端子接线会导致设备的损坏.

有必要的情况下再安装。 如果安装了,不要用它来 启动和停止变频器。否则, 容易缩短产品的使用寿命。

控制连线

安全警告

为了您的安全,请在操作前先阅读说明书 请联系授权的服务人员进行检查、维修、调整 请由专业人员进行拆除维修

LS产电的30年

LS产电在不断地变革和成长中积累了丰富的经验。 同时具备了面临激烈竞争及挑战时也能生存并发展的强大组织力量。

取得飞跃和成长的企业 1974年 金星机电(株)创立 1987年 金星产电(株)设立 1994年 企业上市

电气及自动化领域的领先者 1995年 商号变更为LG产电(株) 1996年 取得了韩国最早变频器领域

的ISO9001认证 1998年 低压电器生产突破1亿台

第二次质的飞跃 1999年 合并LG金属(株) 1999年 转让铜管和自动销售机事业 2003年 内部调整,归属于LG电缆 2005年 更名为LS产电

动能缓冲

电源突降或瞬时掉电的情况下,变频器会出现欠压故障并保护停机。使 用此功能后,变频器在电源出现问题时会根据减速方式或直流电压参考方式 控制输出频率,利用电机产生的回馈能量维持直流侧电压以延长出现欠压保 护的时间,实现电源突降或瞬时掉电的情况下变频器能持续工作。

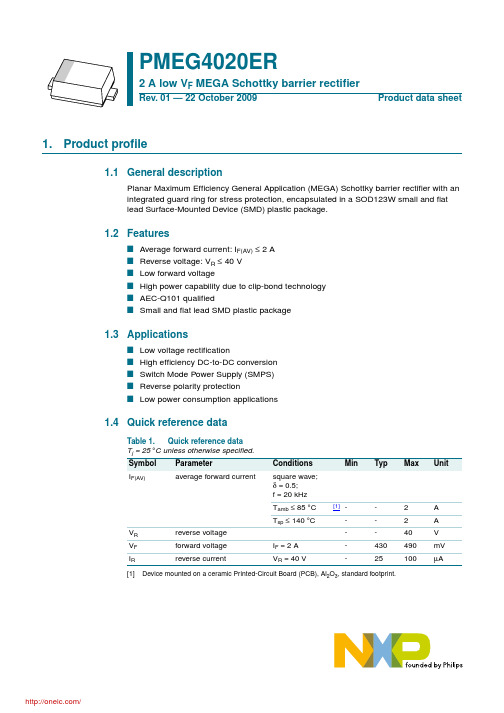

PMEG4020ER,115;中文规格书,Datasheet资料

PMEG4020ER_1

Product data sheet

/

Rev. 01 — 22 October 2009

© NXP B.V. 2009. All rights reserved.

4 of 13

NXP Semiconductors

PMEG4020ER

2 A low VF MEGA Schottky barrier rectifier

7. Characteristics

Table 7. Characteristics Tj = 25 °C unless otherwise specified.

Symbol Parameter

Conditions

VF

forward voltage

IF = 0.1 A

IF = 1 A

IF = 2 A

IR

Version SOD123W

4. Marking

Table 4. Marking codes Type number PMEG4020ER

Marking code BE

5. Limiting values

Table 5. Limiting values In accordance with the Absolute Maximum Rating System (IEC 60134).

2 A low VF MEGA Schottky barrier rectifier

2. Pinning information

Table 2. Pin 1 2

Pinning Description cathode anode

[1] The marking bar indicates the cathode.

PMEG2005AEL,315;中文规格书,Datasheet资料

1.Product profile1.1General descriptionPlanar Maximum Efficiency General Application (MEGA) Schottky barrier diode with an integrated guard ring for stress protection encapsulated in a SOD882 leadless ultra small plastic package.1.2FeaturesForward current: 0.5AReverse voltage: 20V Ultra low forward voltageLeadless ultra small plastic packagePower dissipation comparable to SOT231.3ApplicationsUltra high-speed switching Voltage clamping Protection circuitsLow voltage rectificationHigh efficiency DC-to-DC conversionLow power consumption applications1.4Quick reference dataPMEG2005AEL0.5A ultra low V F MEGA Schottky barrier rectifier in leadless ultra small SOD882 packageRev. 03 — 15 January 2010Product data sheetTable 1.Quick reference dataSymbol Parameter Value Unit I F forward current 0.5A V Rreverse voltage20V2.Pinning information[1]The marking bar indicates the cathode.3.Ordering information4.Marking5.Limiting valuesTable 2.Discrete pinningPin Description Simplified outline Symbol1cathode [1]2anode001aaa332Bottom viewTop view21sym00112Table 3.Ordering informationType number Package NameDescriptionVersion PMEG2005AEL-leadless ultra small plastic package; 2 terminals; body 1.0×0.6×0.5mmSOD882Table 4.MarkingType number Marking code PMEG2005AELF2Table 5.Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134).Symbol Parameter Conditions Min Max Unit V R continuous reverse voltage -20V I F continuous forward current-0.5A I FRM repetitive peak forward current t p ≤1ms; δ≤0.25- 2.5A I FSM non-repetitive peak forward currentt =8ms square wave-3A T j junction temperature[1]-150°C T amb operating ambient temperature [1]−65+150°C T stgstorage temperature−65+150°C[1]For Schottky barrier diodes thermal run-away has to be considered, as in some applications the reverse power losses P R are a significant part of the total power losses. Nomograms for determining the reverse power losses P R and I F(AV) rating will be available on request.6.Thermal characteristics[1]Refer to SOD882 standard mounting conditions (footprint), FR4 with 60μm copper strip line.[2]For Schottky barrier diodes thermal run-away has to be considered, as in some applications the reverse power losses P R are a significant part of the total power losses. Nomograms for determining the reverse power losses P R and I F(AV) rating will be available on request.7.Characteristics[1]Pulse test: t p ≤300μs; δ≤0.02.Table 6.Thermal characteristics Symbol ParameterConditions Value Unit R th(j-a)thermal resistance from junction to ambientin free air[1][2]500K/WTable 7.CharacteristicsT amb =25°C unless otherwise specified.Symbol Parameter Conditions Typ Max Unit V Fcontinuous forward voltagesee Figure 1;I F =0.1mA 2560mV I F =1mA 75110mV I F =10mA 135190mV I F =100mA 220290mV I F =500mA375440mV I Rcontinuous reverse currentsee Figure 2;[1]V R =10V 210600μA V R =20V3701500μA C ddiode capacitanceV R =1V; f =1MHz; see Figure 31925pF8.Package outlineLeadless ultra small plastic package; 2 terminals; body 1.0 x 0.6 x 0.5 mm SOD882Fig 4.Package outline9.Revision historyTable 8.Revision historyDocument ID Release date Data sheet status Change notice SupersedesPMEG2005AEL_320100115Product data-PMEG2005AEL_2 Modifications:•This data sheet was changed to reflect the new company name NXP Semiconductors,including new legal definitions and disclaimers. No changes were made to the technicalcontent.PMEG2005AEL_220040427Product data-PMEG2005AEL_1 PMEG2005AEL_120040419Product data--10.Legal information10.1Data sheet status[1]Please consult the most recently issued document before initiating or completing a design. [2]The term ‘short data sheet’ is explained in section “Definitions”.[3]The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL .10.2DefinitionsDraft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness ofinformation included herein and shall have no liability for the consequences of use of such information.Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.10.3DisclaimersGeneral — Information in this document is believed to be accurate andreliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including withoutlimitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure ormalfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmentaldamage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer’s own risk.Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in theCharacteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.Terms and conditions of sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at /profile/terms , including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unlessexplicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.Export control — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.Quick reference data — The Quick reference data is an extract of theproduct data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.10.4TrademarksNotice: All referenced brands, product names, service names and trademarks are the property of their respective owners.11.Contact informationFor more information, please visit: For sales office addresses, please send an email to: salesaddresses@Document status [1][2]Product status [3]DefinitionObjective [short] data sheet Development This document contains data from the objective specification for product development. Preliminary [short] data sheet Qualification This document contains data from the preliminary specification. Product [short] data sheetProductionThis document contains the product specification.12.Contents1Product profile. . . . . . . . . . . . . . . . . . . . . . . . . . 11.1General description . . . . . . . . . . . . . . . . . . . . . 11.2Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11.3Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . 11.4Quick reference data . . . . . . . . . . . . . . . . . . . . 12Pinning information. . . . . . . . . . . . . . . . . . . . . . 23Ordering information. . . . . . . . . . . . . . . . . . . . . 24Marking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 26Thermal characteristics . . . . . . . . . . . . . . . . . . 37Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . 38Package outline. . . . . . . . . . . . . . . . . . . . . . . . . 59Revision history. . . . . . . . . . . . . . . . . . . . . . . . . 610Legal information. . . . . . . . . . . . . . . . . . . . . . . . 710.1Data sheet status . . . . . . . . . . . . . . . . . . . . . . . 710.2Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 710.3Disclaimers. . . . . . . . . . . . . . . . . . . . . . . . . . . . 710.4Trademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . . 711Contact information. . . . . . . . . . . . . . . . . . . . . . 712Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8Please be aware that important notices concerning this document and the product(s)described herein, have been included in section ‘Legal information’.© NXP B.V.2010.All rights reserved.For more information, please visit: For sales office addresses, please send an email to: salesaddresses@分销商库存信息: NXPPMEG2005AEL,315。

LG变频器iGA说明书

海拔, 振动 大气压力

最大海拔高度 1,000m 以下,最大 5.9m/sec2 (0.6G) 或更低 70 ~ 106 kPa

(2) 接线

不要安装电力电容器,浪涌抑制器,或 RFI 滤波器在变频器的输出侧。 连接到电机的输出电缆(U, V, W) 的连接方式将会影响到电机的旋转方向。 不正确的端子接线可能引起设备的损坏。 端子的正负极接反可能会损坏变频器。 只有熟悉 LG 变频器的人员才可以对变频器进行接线和检查。 先安装变频器再进行接线,否则,你可能受到电击或人身伤害。

CHAPTER 3 - 配线 ............................................................................................. 错误!未定义书签。 3.1 端子配线 .................................................................................................... 错误!未定义书签。 3.2 电源端子块连线说明................................................................................... 错误!未定义书签。 3.3 控制端子说明 ............................................................................................. 错误!未定义书签。 3.4 PNP/NPN 选择和通讯项的连接 ...........................................................................................3-6

MUR2100EG;MUR2100ERLG;中文规格书,Datasheet资料

1.0E−07

25°C 1.0E−08

1000

0

200

400

600

800

VR, REVERSE VOLTAGE (V) Figure 4. Typical Reverse Current

1000

PF(AV), AVERAGE POWER DISSIPATION (A)

4.0 3.5 3.0 2.5 2.0 1.5 1.0 0.5

MUR2100E

NOTE 3. − AMBIENT MOUNTING DATA

Data shown for thermal resistance, junction−to−ambient

(RqJA) for the mountings shown is to be used as typical guideline values for preliminary engineering or in case the tie point temperature cannot be measured.

Unit

Maximum Thermal Resistance, Junction−to−Ambient

RqJA (Note 3) °C/W

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability. 1. Pulse Test: Pulse Width = 300 ms, Duty Cycle ≤ 2.0%.

NYC0102BLT1G;中文规格书,Datasheet资料

IGT

−

−

200

mA

Gate Trigger Voltage (VD = 12 V, RL = 100 W, TC = 25°C)

VGT

−

−

0.8

V

Holding Current (IT = 50 mA, RGK = 1 kW, TC = 25°C)

IH

−

−

6.0

mA

Gate Non−Trigger Voltage (VD = VDRM, RL = 3.3 kW, TC = 125°C)

TJ

−40 to

°C

+125

Storage Temperature Range

Tstg

−40 to

°C

+150

THERMAL CHARACTERISTICS

Characteristic

Symbol Max

Unit

Total Device Dissipation FR− 5 Board TA = 25°C

PD

225

mW

Thermal Resistance, Junction−to−Ambient RqJA

380

°C/W

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

TPS65910AA1RSLR;中文规格书,Datasheet资料

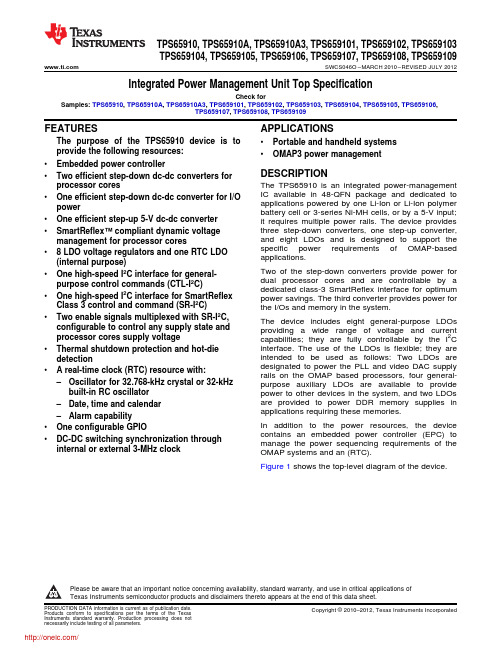

TPS65910,TPS65910A,TPS65910A3,TPS659101,TPS659102,TPS659103TPS659104,TPS659105,TPS659106,TPS659107,TPS659108,TPS659109 SWCS046O–MARCH2010–REVISED JULY2012 Integrated Power Management Unit Top SpecificationCheck forSamples:TPS65910,TPS65910A,TPS65910A3,TPS659101,TPS659102,TPS659103,TPS659104,TPS659105,TPS659106,TPS659107,TPS659108,TPS659109FEATURES APPLICATIONSThe purpose of the TPS65910device is to•Portable and handheld systemsprovide the following resources:•OMAP3power management•Embedded power controllerDESCRIPTION•Two efficient step-down dc-dc converters forThe TPS65910is an integrated power-management processor coresIC available in48-QFN package and dedicated to •One efficient step-down dc-dc converter for I/Oapplications powered by one Li-Ion or Li-Ion polymer powerbattery cell or3-series Ni-MH cells,or by a5-V input;•One efficient step-up5-V dc-dc converter it requires multiple power rails.The device providesthree step-down converters,one step-up converter,•SmartReflex™compliant dynamic voltageand eight LDOs and is designed to support the management for processor coresspecific power requirements of OMAP-based •8LDO voltage regulators and one RTC LDOapplications.(internal purpose)Two of the step-down converters provide power for •One high-speed I2C interface for general-dual processor cores and are controllable by a purpose control commands(CTL-I2C)dedicated class-3SmartReflex interface for optimum •One high-speed I2C interface for SmartReflex power savings.The third converter provides power for Class3control and command(SR-I2C)the I/Os and memory in the system.•Two enable signals multiplexed with SR-I2C,The device includes eight general-purpose LDOs configurable to control any supply state and providing a wide range of voltage and current processor cores supply voltage capabilities;they are fully controllable by the I2Cinterface.The use of the LDOs is flexible;they are •Thermal shutdown protection and hot-dieintended to be used as follows:Two LDOs are detectiondesignated to power the PLL and video DAC supply •A real-time clock(RTC)resource with:rails on the OMAP based processors,four general-–Oscillator for32.768-kHz crystal or32-kHz purpose auxiliary LDOs are available to provide built-in RC oscillator power to other devices in the system,and two LDOsare provided to power DDR memory supplies in –Date,time and calendarapplications requiring these memories.–Alarm capabilityIn addition to the power resources,the device •One configurable GPIOcontains an embedded power controller(EPC)to •DC-DC switching synchronization through manage the power sequencing requirements of the internal or external3-MHz clock OMAP systems and an(RTC).Figure1shows the top-level diagram of the device.Please be aware that an important notice concerning availability,standard warranty,and use in critical applications ofTexas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.PRODUCTION DATA information is current as of publication date.Copyright©2010–2012,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasPSWCS046-001Ci Co Ci Ci Ci (VCCIO)Ci (VCC2)Ci (VCC1)TPS65910,TPS65910A,TPS65910A3,TPS659101,TPS659102,TPS659103TPS659104,TPS659105,TPS659106,TPS659107,TPS659108,TPS659109SWCS046O –MARCH 2010–REVISED JULY 2012Figure 1.48-QFN Top-Level Diagram2Submit Documentation Feedback Copyright ©2010–2012,Texas Instruments IncorporatedTPS65910,TPS65910A,TPS65910A3,TPS659101,TPS659102,TPS659103TPS659104,TPS659105,TPS659106,TPS659107,TPS659108,TPS659109 SWCS046O–MARCH2010–REVISED JULY2012 Table1.SUPPORTED PROCESSORS AND CORRESPONDING PART NUMBERSCompatible Processor(1)Part Number(1)TI processor-AM335x with DDR2TPS65910AA1RSLTI processor-AM335x with DDR3TPS65910A3A1RSL TI processors-AM1705/07,AM1806/08,AM3505/17,AM3703/15,DM3730/25,TPS65910A1RSL OMAP-L137/38,OMAP3503/15/25/30,TMS320C6742/6/8Samsung-S5PV210,S5PC110TPS659101A1RSLRockchip-RK29xx TPS659102A1RSLSamsung-S5PC100TPS659103A1RSLSamsung-S5P6440TPS659104A1RSLTI processors-DM643x,DM644x TPS659105A1RSLReserved TPS659106A1RSLFreescale-i.MX27,Freescale-i.MX35TPS659107A1RSLFreescale-i.MX508TPS659108A1RSLFreescale-i.MX51TPS659109A1RSL(1)The RSL package is available in tape and reel.See for details for corresponding part numbers,quantities and ordering information. ABSOLUTE MAXIMUM RATINGSover operating free-air temperature range(unless otherwise noted)Stresses beyond those listed under below may cause permanent damage to the device.These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated below are not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.The absolute maximum ratings for the TPS65910device are listed below:PARAMETER MIN MAX UNITVoltage range on pins/balls VCC1,VCC2,VCCIO,VCC3,VCC4,–0.37VVCC5,VCC6,VCC7Voltage range on pins/balls VDDIO–0.3 3.6VVoltage range on pins/balls OSC32KIN,OSC32KOUT,BOOT1,–0.3VRTC MAX+0.3VBOOT0Voltage range on pins/balls SDA_SDI,SCL_SCK,SDASR_EN2,–0.3VDDIO MAX+0.3VSCLSR_EN1,SLEEP,INT1,CLK32KOUT,NRESPWRONVoltage range on pins/balls PWRON–0.37VVoltage range on pins/balls PWRHOLD(1)GPIO_CKSYNC(2)–0.37V Functional junction temperature range–45150°CPeak output current on all other terminals than power resources–55mA(1)I/O supplied from VDDIO but which can be driven from to a VBAT voltage level(2)I/O supplied from VRTC but can be driven to a VBAT voltage levelTHERMAL CHARACTERISTICSover operating free-air temperature range(unless otherwise noted)DERATINGTA<25°C Power FACTOR ABOVE TA=70°C Power TA=85°C Power Package Rθja(°C/W)Rating(W)25°C(W)Rating(W)(mW/°C)RSL48-QFN37 2.637 1.481The thermal resistance RθJP junction-to-power PAD of the RSL package is1.1°C/WThe value of thermal resistance RθJA junction-to-ambient was measured on a high K.Copyright©2010–2012,Texas Instruments Incorporated Submit Documentation Feedback3TPS65910,TPS65910A,TPS65910A3,TPS659101,TPS659102,TPS659103TPS659104,TPS659105,TPS659106,TPS659107,TPS659108,TPS659109SWCS046O–MARCH2010–REVISED RECOMMENDED OPERATING CONDITIONSover operating free-air temperature range(unless otherwise noted)Lists of the recommended operating maximum ratings for the TPS65910device are given below.Note1:VCC7should be connected to the highest supply that is connected to the device VCCx pin.The exception is thatVCC2and VCC4can be higher than VCC7.Note2:VCC2and VCC4must be connected together(to the same voltage).Note3:If VDD3boost is used,VAUX33must be set to2.8V or higher and enabled before VDD3.PARAMETER TEST CONDITIONS MIN NOM MAX UNITV CC:Input voltage range on pins/balls VCC1,VCC2,VCCIO,VCC3,VCC4,VCC5,2.73.6 5.5VVCC7V CCP:Input voltage range on pins/balls VCC6 1.7 3.6 5.5VInput voltage range on pins/balls VDDIO 1.65 1.8/3.3 3.45VInput voltage range on pins/balls PWRON0 3.6 5.5VInput voltage range on pins/balls SDA_SDI,SCL_SCK,SDASR_EN2,SCLSR_EN1,1.65VDDIO 3.45V SLEEPInput voltage range on pins/balls PWRHOLD,GPIO_CKSYNC 1.65VDDIO 5.5VInput voltage range on balls BOOT1,BOOT0,OSC32KIN 1.65VRTC 1.95VOperating free-air temperature,T A–402785°CJunction temperature T J–4027125°CStorage temperature range–6527150°CLead temperature(soldering,10s)260°CPower ReferencesVREF filtering capacitor C O(VREF)Connected from VREF to REFGND100nFVDD1SMPSInput capacitor C I(VCC1)X5R or X7R dielectric10µFFilter capacitor C O(VDD1)X5R or X7R dielectric41012µFC O filter capacitor ESR f=3MHz10300mΩInductor L O(VDD1) 2.2µHL O inductor dc resistor DCR L125mΩVDD2SMPSInput capacitor C I(VCC2)X5R or X7R dielectric10µFFilter capacitor C O(VDD2)X5R or X7R dielectric41012µFC O filter capacitor ESR f=3MHz10300mΩInductor L O(VDD2) 2.2µHL O inductor dc resistor DCR L125mΩVIO SMPSInput capacitor C I(VIO)X5R or X7R dielectric10µFFilter capacitor C O(VIO)X5R or X7R dielectric41012µFC O filter capacitor ESR f=3MHz10300mΩInductor L O(VIO) 2.2µHL O inductor dc resistor DCR L125mΩVDIG1LDOInput capacitor C I(VCC6)X5R or X7R dielectric 4.7µFFiltering capacitor C O(VDIG1)0.8 2.2 2.64µFC O filtering capacitor ESR0500mΩVDIG2LDOFiltering capacitor C O(VDIG2)0.8 2.2 2.64µFC O filtering capacitor ESR0500mΩVPLL LDOInput capacitor C I(VCC5)X5R or X7R dielectric 4.7µFFiltering capacitor C O(VPLL)0.8 2.2 2.64µF4Submit Documentation Feedback Copyright©2010–2012,Texas Instruments IncorporatedTPS65910,TPS65910A,TPS65910A3,TPS659101,TPS659102,TPS659103TPS659104,TPS659105,TPS659106,TPS659107,TPS659108,TPS659109 SWCS046O–MARCH2010–REVISED JULY2012 RECOMMENDED OPERATING CONDITIONS(continued)over operating free-air temperature range(unless otherwise noted)Lists of the recommended operating maximum ratings for the TPS65910device are given below.Note1:VCC7should be connected to the highest supply that is connected to the device VCCx pin.The exception is thatVCC2and VCC4can be higher than VCC7.Note2:VCC2and VCC4must be connected together(to the same voltage).Note3:If VDD3boost is used,VAUX33must be set to2.8V or higher and enabled before VDD3.PARAMETER TEST CONDITIONS MIN NOM MAX UNITC O filtering capacitor ESR0500mΩVDAC LDOFiltering capacitor C O(VDAC)0.8 2.2 2.64µFC O filtering capacitor ESR0500mΩVMMC LDOInput capacitor C I(VCC4)X5R or X7R dielectric 4.7µFFiltering capacitor C O(VMMC)0.8 2.2 2.64µFC O filtering capacitor ESR0500mΩVAUX33LDOFiltering capacitor C O(VAUX33)0.8 2.2 2.64µFC O filtering capacitor ESR0500mΩVAUX1LDOInput capacitor C I(VCC3)X5R or X7R dielectric 4.7µFFiltering capacitor C O(VAUX1)0.8 2.2 2.64µFC O filtering capacitor ESR0500mΩVAUX2LDOFiltering capacitor C O(VAUX2)0.8 2.2 2.64µFC O filtering capacitor ESR0500mΩVRTC LDOInput capacitor C I(VCC7)X5R or X7R dielectric 4.7µFFiltering capacitor C O(VRTC)0.8 2.2 2.64µFC O filtering capacitor ESR0500mΩVDD3SMPSInput capacitor C I(VDD3)X5R or X7R dielectric 4.7µFFilter capacitor C O(VDD3)X5R or X7R dielectric41012µFC O filter capacitor ESR f=1MHz10300mΩInductor L O(VDD3) 2.8 4.7 6.6µHL O inductor DC resistor DCR L50500mΩBackup BatteryBattery or superCap supplying VBACKUP5102000mF Backup battery capacitor C BBCapacitor supplying VBACKUP140µF5to15mF101500Series resistorsΩ100to2000mF515I2C InterfacesSDA_SDI,SCL_SCK,SDASR_EN2,Connected to VDDIO 1.2kΩSCLSR_EN1external pull-up resistorCrystal Oscillator(connected from OSC32KIN to OSC32KOUT)Crystal frequency@specified load cap value32.768kHzCrystal tolerance@27°C–20020ppmOscillator contribution(not including crystalFrequency Temperature coefficient.–0.50.5ppm/°Cvariation)Secondary temperature coefficient–0.04–0.035–0.03ppm/°C2Voltage coefficient–22ppm/V Copyright©2010–2012,Texas Instruments Incorporated Submit Documentation Feedback5TPS65910,TPS65910A,TPS65910A3,TPS659101,TPS659102,TPS659103TPS659104,TPS659105,TPS659106,TPS659107,TPS659108,TPS659109SWCS046O–MARCH2010–REVISED RECOMMENDED OPERATING CONDITIONS(continued)over operating free-air temperature range(unless otherwise noted)Lists of the recommended operating maximum ratings for the TPS65910device are given below.Note1:VCC7should be connected to the highest supply that is connected to the device VCCx pin.The exception is thatVCC2and VCC4can be higher than VCC7.Note2:VCC2and VCC4must be connected together(to the same voltage).Note3:If VDD3boost is used,VAUX33must be set to2.8V or higher and enabled before VDD3.PARAMETER TEST CONDITIONS MIN NOM MAX UNIT Max crystal series resistor@Fundamental frequency90kΩCrystal load capacitor According to crystal data sheet612.5pFLoad crystal oscillator Coscinparallel mode Including parasitic PCB capacitor1225pF,CoscoutQuality factor800080000ESD SPECIFICATIONSover operating free-air temperature range(unless otherwise noted)TI STANDARD ESD METHOD STANDARD REFERENCE PERFORMANCEREQUIREMENTS Human body model(HBM)EIA/JESD22-A114D2000V2000VCharge device model(CDM)EIA/JESD22-C101C500V500V6Submit Documentation Feedback Copyright©2010–2012,Texas Instruments IncorporatedTPS65910,TPS65910A,TPS65910A3,TPS659101,TPS659102,TPS659103TPS659104,TPS659105,TPS659106,TPS659107,TPS659108,TPS659109 SWCS046O–MARCH2010–REVISED JULY2012 I/O PULLUP AND PULLDOWN CHARACTERISTICSover operating free-air temperature range(unless otherwise noted)(1)PARAMETER TEST CONDITIONS MIN TYP MAX UNITSDA_SDI,SCL_SCK,SDASR_EN2,SCLSR_EN1Programmable pullup(DFT,default Grounded,VDDIO=1.8V–45%8+45%kΩinactive)SLEEP programmable pulldown(default active)@1.8V,VRTC=1.8V2 4.510µA@1.8V,VRTC=1.8V,VCC7=2.72 4.510VPWRHOLD programmable pulldown(defaultµA active)@5.5V,VRTC=1.8V,VCC7=5.571430VBOOT0,BOOT1programmable pulldown(default@1.8V,VRTC=1.8V2 4.510µA active)NRESPWRON pulldown@1.8V,VCC7=5.5V,OFF state2 4.510µA32KCLKOUT pulldown(disabled in Active-sleep@1.8V,VRTC=1.8V,OFF state2 4.510µA state)PWRON programmable pullup(default active)Grounded,VCC7=5.5V–40–31–15µAGPIO_CKSYNC programmable pullup(defaultGrounded,VRTC=1.8V–27–18–9µA active)(1)The internal pullups on the CTL-I2C and SR-I2C balls are used for test purposes or when the SR-I2C interface is not used.Discretepullups to the VIO supply must be mounted on the board in order to use the I2C interfaces.The internal I2C pullups must not be used for functional applicationsCopyright©2010–2012,Texas Instruments Incorporated Submit Documentation Feedback7TPS65910,TPS65910A,TPS65910A3,TPS659101,TPS659102,TPS659103TPS659104,TPS659105,TPS659106,TPS659107,TPS659108,TPS659109SWCS046O–MARCH2010–REVISED DIGITAL I/O VOLTAGE ELECTRICAL CHARACTERISTICSover operating free-air temperature range(unless otherwise noted)PARAMETER MIN TYP MAX UNITRelated I/O:PWRONLow-level input voltage V IL0.3x VCC7V High-level input voltage V IH0.7x VCC7VRelated I/Os:PWRHOLD,GPIO_CKSYNCLow-level input voltage V IL0.45VVDDIO/VHigh-level input voltage V IH 1.3VCC7VCC7Related I/Os:BOOT0,BOOT1,OSC32KINLow-level input voltage V IL0.35x VRTC V High-level input voltage V IH0.65x VRTC VRelated I/Os:SLEEPLow-level input voltage V IL0.35x VDDIO V High-level input voltage V IH0.65x VDDIO VRelated I/Os:NRESPWRON,INT1,32KCLKOUTLow-level output voltage V OL I OL=100µA0.2VI OL=2mA0.45V High-level output voltage V OH I OH=100µA VDDIO–0.2VI OH=2mA VDDIO–0.45VRelated Open-Drain I/Os:GPIO0Low-level output voltage V OL I OL=100µA0.2VI OL=2mA0.45VI2C-Specific Related I/Os:SCL,SDA,SCLSR_EN1,SDASR_EN2Low-level input voltage V IL–0.50.3x VDDIO V High-level input voltage V IH0.7x VDDIO V Hysteresis0.1x VDDIO VLow-level output voltage V OL@3mA(sink current),VDDIO=1.8V0.2×VDDIO VLow-level output voltage V OL@3mA(sink current),VDDIO=3.3V0.4x VDDIO V8Submit Documentation Feedback Copyright©2010–2012,Texas Instruments IncorporatedTPS65910,TPS65910A,TPS65910A3,TPS659101,TPS659102,TPS659103TPS659104,TPS659105,TPS659106,TPS659107,TPS659108,TPS659109 SWCS046O–MARCH2010–REVISED JULY2012 I2C INTERFACE AND CONTROL SIGNALSover operating free-air temperature range(unless otherwise noted)NO.PARAMETER TEST CONDITIONS MIN TYP MAXINT1rise and fall times,C L=5to35pF510nsNRESPWRON rise and fall times,C L=5to35pF510nsSLAVE HIGH–SPEED MODESCL/SCLSR_EN1and SDA/SDASR_EN2rise and fall1080nstime,C L=10to100pFData rate 3.4MbpsI3t su(SDA-SCLH)Setup time,SDA valid to SCL high10nsI4t h(SCLL-SDA)Hold time,SDA valid from SCL low070nsI7t su(SCLH-SDAL)Setup time,SCL high to SDA low160nsI8t h(SDAL-SCLL)Hold time,SCL low from SDA low160nsI9t su(SDAH-SCLH)Setup time,SDA high to SCL high160nsSLAVE FAST MODESCL/SCLSR_EN1and SDA/SDASR_EN2rise and fall20+250nstime,C L=10to400pF0.1×C LData rate400KbpsI3t su(SDA-SCLH)Setup time,SDA valid to SCL high100nsI4t h(SCLL-SDA)Hold time,SDA valid from SCL low00.9µsI7t su(SCLH-SDAL)Setup time,SCL high to SDA low0.6µsI8t h(SDAL-SCLL)Hold time,SCL low from SDA low0.6µsI9t su(SDAH-SCLH)Setup time,SDA high to SCL high0.6µsSLAVE STANDARD MODESCL/SCLSR_EN1and SDA/SDASR_EN2rise and fall250nstime,C L=10to400pFData rate100KbpsI3t su(SDA-SCLH)Setup time,SDA valid to SCL high250nsI4t h(SCLL-SDA)Hold time,SDA valid from SCL low0µsI7t su(SCLH-SDAL)Setup time,SCL high to SDA low 4.7µsI8t h(SDAL-SCLL)Hold time,SCL low from SDA low4µsI9t su(SDAH-SCLH)Setup time,SDA high to SCL high4µsSWITCHING CHARACTERISTICSSLAVE HIGH–SPEED MODEI1t w(SCLL)Pulse duration,SCL low160nsI2t w(SCLH)Pulse duration,SCL high60nsSLAVE FAST MODEI1t w(SCLL)Pulse duration,SCL low 1.3µsI2t w(SCLH)Pulse duration,SCL high0.6µsSLAVE STANDARD MODEI1t w(SCLL)Pulse duration,SCL low 4.7µsI2t w(SCLH)Pulse duration,SCL high4µs Copyright©2010–2012,Texas Instruments Incorporated Submit Documentation Feedback9TPS65910,TPS65910A,TPS65910A3,TPS659101,TPS659102,TPS659103TPS659104,TPS659105,TPS659106,TPS659107,TPS659108,TPS659109SWCS046O–MARCH2010–REVISED POWER CONSUMPTIONover operating free-air temperature range(unless otherwise noted)All current consumption measurements are relative to the FULL chip,all VCC inputs set to VBAT voltage.PARAMETER TEST CONDITIONS MIN TYP MAX UNITDevice BACKUP state VBAT=2.4V,VBACKUP=0V,1116µA VBAT=0V,VBACKUP=3.2V69Device OFF state VBAT=3.6V,CK32K clock runningBOOT[1:0]=00:32-kHz RC oscillator16.523BOOT[1:0]=01:32-kHz quartz or bypass oscillator,BOOT0P1520=0µA BOOT[1:0]=01,Backup Battery Charger on,VBACKUP=3.23242VVBAT=5V,CK32K clock running:2028BOOT[1:0]=00:RC oscillatorDevice SLEEP state VBAT=3.6V,CK32K clock running,PWRHOLDP=0BOOT[1:0]=00,3DC-DCs on,5LDOs and VRTC on,no load295µA BOOT[1:0]=01,3DC-DCs on,3LDOs and VRTC on,no load,279BOOT0P=0Device ACTIVE state VBAT=3.6V,CK32K clock running,PWRHOLDP=0BOOT[1:0]=00,3DC-DCs on,5LDOs and VRTC on,no load1BOOT[1:0]=01,3DC-DCs on,3LDOs and VRTC on,no load,0.9mABOOT0P=0BOOT[1:0]=00,3DC-DCs on PWM mode(VDD1_PSKIP=VDD2_PSKIP=VIO_PSKIP=0),5LDOs and VRTC on,no21loadPOWER REFERENCES AND THRESHOLDSover operating free-air temperature range(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNITOutput reference voltage(VREFDevice in active or low-power mode–1%0.85+1%V terminal)Main battery charged Measured on VCC7terminalthreshold VMBCH(programmable)Triggering monitored through NRESPRWONVMBCH_VSEL=11,BOOT[1:0]=11or003VMBCH_VSEL=10 2.9VVMBCH_VSEL=01 2.8VMBCH_VSEL=00bypassedMain battery discharged Measured on VCC7terminal(MTL prg)VMBCH–V threshold VMBDCH(programmable)Triggering monitored through INT1100mVMain battery low threshold VMBLO Measured on VCC7terminal(Triggering2.5 2.6 2.7V (MB comparator)monitored on terminal NRESPWRON)VBACKUP=0V,measured on terminal VCC7Main battery high threshold VMBHI 2.6 2.753(MB comparator)VVBACKUP=3.2V,measured on terminal VCC7 2.5 2.553Main battery not present threshold Measured on terminal VCC71.92.1 2.2V VBNPR(Triggering monitored on terminal VRTC)V CC=3.6VGround current(analog references+comparators+backup battery Device in OFF state8µA switch)Device in ACTIVE or SLEEP state2010Submit Documentation Feedback Copyright©2010–2012,Texas Instruments Incorporated分销商库存信息: TITPS65910AA1RSLR。

FSL106MR;中文规格书,Datasheet资料

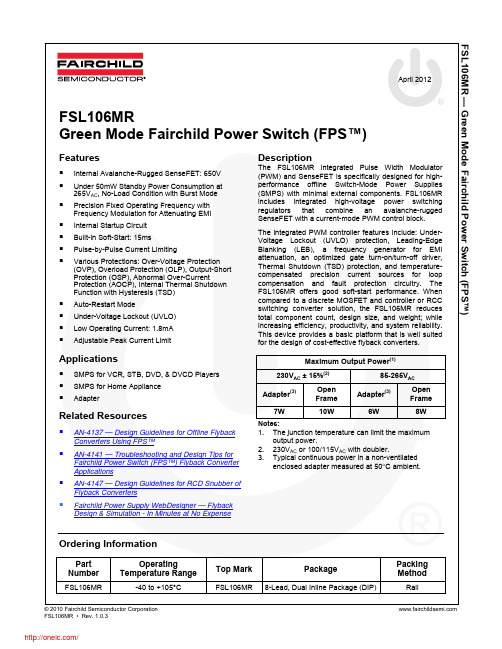

Description

The FSL106MR integrated Pulse Width Modulator (PWM) and SenseFET is specifically designed for highperformance offline Switch-Mode Power Supplies (SMPS) with minimal external components. FSL106MR includes integrated high-voltage power switching regulators that combine an avalanche-rugged SenseFET with a current-mode PWM control block. The integrated PWM controller features include: UnderVoltage Lockout (UVLO) protection, Leading-Edge Blanking (LEB), a frequency generator for EMI attenuation, an optimized gate turn-on/turn-off driver, Thermal Shutdown (TSD) protection, and temperaturecompensated precision current sources for loop compensation and fault protection circuitry. The FSL106MR offers good soft-start performance. When compared to a discrete MOSFET and controller or RCC switching converter solution, the FSL106MR reduces total component count, design size, and weight; while increasing efficiency, productivity, and system reliability. This device provides a basic platform that is well suited for the design of cost-effective flyback converters. Maximum Output Power(1) 230VAC ± 15%(2) Adapter(3) 7W

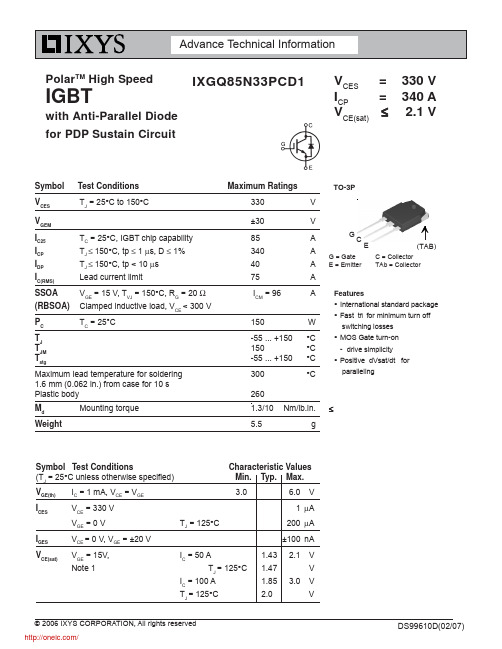

IXGQ85N33PCD1;中文规格书,Datasheet资料

TJ - Degrees Centigrade

Fig. 6. Input Adm ittance

I C - Amperes

140 120 100 80 60 40 20 0 TJ = 125 ºC 25 ºC - 40 ºC 4 4.5 5 5.5 6 6.5 7 7.5 8 8.5 9 9.5

V C E - Volts

4

6

8

10

12

14

16

18

20

22

24

25

50

75

100

125

150

R G - Ohms

T J - Degrees Centigrade

IXYS reserves the right to change limits, test conditions and dimensions.

4.0 3.5 3.0 2.5 2.0 1.5 1.0 5 6 7 8 9

10

11

12

13

14

15

V G E - V olts

V G E - V olts

© 2006 IXYS CORPORATION, All rights reserved /

IXGQ85N33PCD1

TO-3P

TC = 25°C, IGBT chip capability TJ ≤ 150°C, tp ≤ 1 μs, D ≤ 1% TJ ≤ 150°C, tp < 10 μs Lead current limit VGE = 15 V, TVJ = 150°C, RG = 20 Ω Clamped inductive load, VCE < 300 V TC = 25°C

LM395T;中文规格书,Datasheet资料

LM195,LM395LM195/LM395 Ultra Reliable Power TransistorsLiterature Number: SNOSBO4BLM195/LM395Ultra Reliable Power TransistorsGeneral DescriptionThe LM195/LM395are fast,monolithic power integrated circuits with complete overload protection.These devices,which act as high gain power transistors,have included on the chip,current limiting,power limiting,and thermal over-load protection making them virtually impossible to destroy from any type of overload.In the standard TO-3transistor power package,the LM195will deliver load currents in ex-cess of 1.0A and can switch 40V in 500ns.The inclusion of thermal limiting,a feature not easily avail-able in discrete designs,provides virtually absolute protec-tion against overload.Excessive power dissipation or inad-equate heat sinking causes the thermal limiting circuitry to turn off the device preventing excessive heating.The LM195offers a significant increase in reliability as well as simplifying power circuitry.In some applications,where protection is unusually difficult,such as switching regulators,lamp or solenoid drivers where normal power dissipation is low,the LM195is especially advantageous.The LM195is easy to use and only a few precautions need be observed.Excessive collector to emitter voltage can de-stroy the LM195as with any power transistor.When the device is used as an emitter follower with low source imped-ance,it is necessary to insert a 5.0k resistor in series with the base lead to prevent possible emitter follower oscilla-tions.Although the device is usually stable as an emitter follower,the resistor eliminates the possibility of trouble with-out degrading performance.Finally,since it has good high frequency response,supply bypassing is recommended.For low-power applications (under 100mA),refer to the LP395Ultra Reliable Power Transistor.The LM195/LM395are available in the standard TO-3,Kovar TO-5,and TO-220packages.The LM195is rated for opera-tion from −55˚C to +150˚C and the LM395from 0˚C to +125˚C.Featuresn Internal thermal limitingn Greater than 1.0A output current n 3.0µA typical base current n 500ns switching time n 2.0V saturationn Base can be driven up to 40V without damage n Directly interfaces with CMOS or TTL n100%electrical burn-inSimplified Circuit006009011.0Amp Lamp Flasher00600916©2004National Semiconductor Corporation TO-3Metal Can Package 00600902Bottom ViewOrder Number LM195K/883See NS Package Number K02A(Note 5)TO-220Plastic Package00600903Case is EmitterTop ViewOrder Number LM395T See NS Package Number T03BTO-5Metal Can Package00600904Bottom ViewOrder Number LM195H/883See NS Package Number H03B(Note 5)L M 19 2please contact the National Semiconductor Sales Office/ Distributors for availability and specifications. Collector to Emitter VoltageLM19542V LM39536V Collector to Base VoltageLM19542V LM39536V Base to Emitter Voltage(Forward)LM195 LM39542V36VPower Dissipation Internally LimitedOperating Temperature RangeLM195−55˚C to+150˚CLM3950˚C to+125˚CStorage Temperature Range−65˚C to+150˚CLead Temperature(Soldering,10sec.)260˚CPreconditioning100%Burn-In In Thermal LimitElectrical Characteristics(Note2)Parameter Conditions LM195LM395UnitsMin Typ Max Min Typ MaxCollector-Emitter Operating Voltage I Q≤I C≤I MAX4236V (Note4)Base to Emitter Breakdown Voltage0≤V CE≤V CEMAX423660V Collector CurrentTO-3,TO-220V CE≤15V 1.2 2.2 1.0 2.2ATO-5V CE≤7.0V 1.2 1.8 1.0 1.8A Saturation Voltage I C≤1.0A,T A=25˚C 1.8 2.0 1.8 2.2V Base Current0≤I C≤I MAX3.0 5.0 3.010µA0≤V CE≤V CEMAXQuiescent Current(I Q)V be=02.0 5.0 2.010mA0≤V CE≤V CEMAXBase to Emitter Voltage I C=1.0A,T A=+25˚C0.90.9V Switching Time V CE=36V,R L=36Ω,500500nsT A=25˚CThermal Resistance Junction to TO-3Package(K) 2.3 3.0 2.3 3.0˚C/W Case(Note3)TO-5Package(H)12151215˚C/WTO-220Package(T)46˚C/WNote1:“Absolute Maximum Ratings”indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the device is functional,but do not guarantee specific performance limits.Note2:Unless otherwise specified,these specifications apply for−55˚C≤T j≤+150˚C for the LM195and0˚C≤+125˚C for the LM395.Note3:Without a heat sink,the thermal resistance of the TO-5package is about+150˚C/W,while that of the TO-3package is+35˚C/W.Note4:Selected devices with higher breakdown available.Note5:Refer to RETS195H and RETS195K drawings of military LM195H and LM195K versions for specifications.3Collector Characteristics Short Circuit Current0060093300600934Bias Current Quiescent Current0060093500600936Base Emitter Voltage Base Current0060093700600938L M 19 4Saturation Voltage Response Time0060093900600940 Response Time10V Transfer Function006009410060090736V Transfer Function Transconductance00600908006009095Small Signal FrequencyResponse00600910Schematic Diagram0060091L M 19 61.0Amp Voltage Follower00600912*Solid TantalumPower PNP Time Delay00600913*Protects against excessive base drive**Needed for stability006009141.0MHz Oscillator0060091571.0Amp Negative Regulator00600917†Solid Tantalum1.0Amp Positive Voltage Regulator00600918†Solid TantalumL M 19 8Fast Optically Isolated Switch Optically Isolated Power Transistor0060091900600920CMOS or TTL Lamp Interface Two Terminal Current Limiter006009210060092240V Switch00600923*Drive Voltage 0V to ≥10V ≤42V6.0V Shunt Regulator with Crowbar Two Terminal 100mA Current Regulator00600924006009259分销商库存信息: NATIONAL-SEMICONDUCTOR LM395T。

ADA-4643 Datasheet说明书