TMS320C6455 硬件设计 PCB Layout

基于TMS320C6455的高速数字信号处理系统设计

p oc sor o ytm an p o es ra G A sc r e s . i a e e cist ea lc t n ei fDS eihey cruti e fc n d tiTh r es , rs se m i r c so ,ndFP f a opoc sor Th sp p rd srb h ppiai a d d sg o on n P p rp r i i ra ei eal e c nt .

处理 能力 最强 的定 . DS 芯 片T 3 0 6 5 为 系统 主 处理 器 ,P A 为协 处理 器。 细论 述 了Ds 外 围接 口电路 的应 用和设 计 ,  ̄ P . MS 2 C 4 5 FG 作 详 P 系统设 计 电路

简洁 、 现 方便 , 靠性 强 。 实 可

关键词 : MS 2 C 4 5 P A 数 字信号 处理 系统设 计 T 3 0 6 5 F G 中图分 类 号: P 9 .1 T31 4 文献标识码 : A 文章 编号 :0 79 1(0 11—0 70 10 —4 62 1)20 9 —3

( p r n f o v lp n , iaP t lu L g igCo,t h a i Xi n7 0 7 De at t l me o To De e me t n er e m o gn . d S anx ’a 1 0 7) o Ch o L

Ab ta t crigt h einn eso hg — p e a—i ii lin l rc sn s m.h ae us owadads no hg —p e i tl src: odn ted s ed f ih sedr l t dgt g apo es gs t T epp r tfr r ei f ih seddg a Ac o g e me as i ye p g i

TMS320C54X 硬件设计

复位状态

复位:芯片内寄存器初始化复位,

只要芯片引脚RS/为低,芯片始终处 于复位状态,仅当RS/变为高电平后, 芯片内的程序才可从FF80H地址开

始执行

DSP要求复位信号从低到高之前,时钟必

须已经稳定工作了若干时间(100-200ms).

寄存器:主要有ST0、ST1、PMST的状态

AT89C51

OE

74HC245 A7 A6 A5 A4 A3 A0

P2.7 P2.6 P2.5 P2.4 P2.3 P2.2 P2.1 P2.0

B7 B6 B5 B4 B3 DIR

ST0=1800H,ST1=2900H,PMST=FFE0H

复位电路

硬件复位

上电复位电路

手动复位电路

自动复位电路 软件复位 RESET指令 CCS环境中,debug---reset

CPU

时钟电路

DSP芯片的工作时间基准,工作频率

如100MHz等,可通过软件编程调整 DSP芯片引脚:

C54X系列大多数DSP芯片的电 源电压为5V、3.3V或2.5V。 内核电压(CVdd)和I/O电压 (DVdd)分开

Hale Waihona Puke CVdd:工作电压为3.3V或2.5V或1.8V DVdd:工作电压一般为3.3V

电源设计

从5V电源产生,图8.2.2 从3.3V电源产生,图8.2.3

复位电路

总体设计确定软硬件分工

软件设计说明书 硬件设计说明书

软件编程与调试

系统集成

硬件(.sch / .pcb )

硬件调试

系统测试、样机完成、中试、产品测试与生产

DSP基本硬件系统

基于TMS320C6455 DSP的PCI接口设计

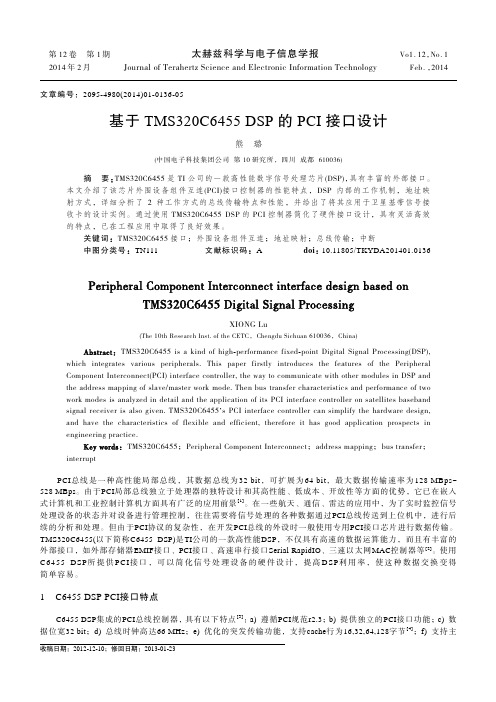

第12卷 第1期 太赫兹科学与电子信息学报Vo1.12,No.1 2014年2月 Journal of Terahertz Science and Electronic Information Technology Feb.,2014 文章编号:2095-4980(2014)01-0136-05基于TMS320C6455 DSP的PCI接口设计熊 璐(中国电子科技集团公司 第10研究所,四川 成都 610036)摘 要:TMS320C6455是TI公司的一款高性能数字信号处理芯片(DSP),具有丰富的外部接口。

本文介绍了该芯片外围设备组件互连(PCI)接口控制器的性能特点,DSP内部的工作机制,地址映射方式,详细分析了2种工作方式的总线传输特点和性能,并给出了将其应用于卫星基带信号接收卡的设计实例。

通过使用TMS320C6455 DSP的PCI控制器简化了硬件接口设计,具有灵活高效的特点,已在工程应用中取得了良好效果。

关键词:TMS320C6455接口;外围设备组件互连;地址映射;总线传输;中断中图分类号:TN111文献标识码:A doi:10.11805/TKYDA201401.0136Peripheral Component Interconnect interface design based onTMS320C6455 Digital Signal ProcessingXIONG Lu(The 10th Research Inst. of the CETC,Chengdu Sichuan 610036,China)Abstract:TMS320C6455 is a kind of high-performance fixed-point Digital Signal Processing(DSP), which integrates various peripherals. This paper firstly introduces the features of the PeripheralComponent Interconnect(PCI) interface controller, the way to communicate with other modules in DSP andthe address mapping of slave/master work mode. Then bus transfer characteristics and performance of twowork modes is analyzed in detail and the application of its PCI interface controller on satellites basebandsignal receiver is also given. TMS320C6455’s PCI interface controller can simplify the hardware design,and have the characteristics of flexible and efficient, therefore it has good application prospects inengineering practice.Key words:TMS320C6455;Peripheral Component Interconnect;address mapping;bus transfer;interruptPCI总线是一种高性能局部总线,其数据总线为32 bit,可扩展为64 bit,最大数据传输速率为128 MBps~ 528 MBps。

(完整版)TMS320C6455高速SRIO接口设计

TMS320C6455高速SRIO接口设计引言数字信号处理技术已广泛应用于通信、雷达、声纳、遥感、图形图像处理和语音处理等领域。

随着现代科技的发展,尤其是半导体工艺的进入深亚微米时代,新的功能强劲的高性能数字信号处理器(DSP)也相继推出,如ADI(美国模拟器件)公司的TigerSHARC系列和TI(德州仪器)公司的C6000系列,但是,要实现对运算量和实时性要求越来越高的DSP 算法,如对基于分数阶傅立叶变换的Chirp信号检测与估计,合成孔径雷达(SAR)成像,高频地波雷达中的自适应滤波和自适应波束形成等算法,单片DSP 仍然显得力不从心。

这些挑战主要涉及两个主题:一是计算能力,指设备、板卡和系统中分别可用的处理资源。

采用多DSP、多FPGA系统,将是提高运算能力的一个有效途径。

二是连接性,从本质上说就是实现不同设备、板卡和系统之间的“快速”数据转移。

对于一些复杂的信息系统,对海量数据传输的实时性提出了苛刻的要求,多DSP之间、DSP与高速AD采集系统、DSP与FPGA间的高速数据传输,是影响信号处理流程的主要瓶颈之一。

TI公司最新推出的高性能TMS320C6455(下文称C6455)处理器,具有高速运算能力的同时集成了高速串行接口SRIO,方便多DSP以及DSP与FPGA之间的数据传输,在一定程度上满足了高速实时处理和传输的要求。

本文在多DSP+FPGA通用信号处理平台的基础上,深入研究了多DSP间,DSP与FPGA间的SRIO 的数据通信和加载技术的软硬件设计与实现。

这些技术包括了目前SRIO接口的各种应用方式,可作为SRIO接口及C6455开发提供参考[1-3]。

1 C6455特性及SRIO标准介绍C6455是目前单片处理能力最强的新型高性能定点DSP,它是TI 公司基于第三代先进VeloviTI VLIW(超长指令字)结构开发出来的新产品。

最高主频为1.2GHz,16位定点处理能力为9600MMAC/s。

TMS320C54xTM DSP应用系统的软硬件设计

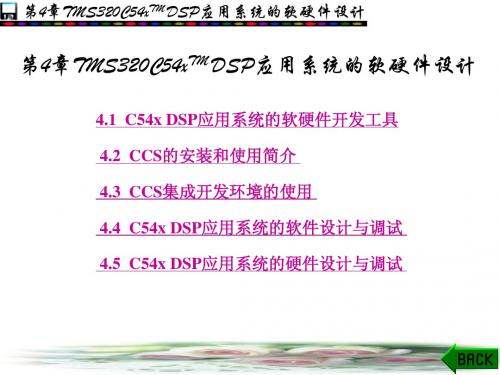

第4章TMS320C54xTM DSP应用系统的软硬件设计 表4.1 File菜单

菜单命令 Source File DSP/BIOS Config New Visual Linker Recipe ActiveX Document 功 能

新建一个源文件(.c, .asm, .h, .cmd, .gel, .map, .inc 等) 新建一个 DSP/BIOS 配置文件 打开一个 Visual Linker Recipe 向导 在 CCS 中打开一个 ActiveX 文档(如 Microsoft Word 或 Microsoft Excel 等)

第4章TMS320C54xTM DSP应用系统的软硬件设计 第三步:将JTAG仿真电缆正确连接在实验箱的JTAG仿 真口上,启动CCS软件,如果一切正常,则CCS能正确启动, 如果报错,请检查CCS安装和设置以及实验箱的电源、电缆接 线是否正确。

第4章TMS320C54xTM DSP应用系统的软硬件设计

第4章TMS320C54xTM DSP应用系统的软硬件设计 4.2.3 新建一个工程 (1) 如果你的 CCS安装在 C:\ti目录下,请在C:\ti\myproject 目录下新建一个目录,名为hello1; (2) 将C:\ti\c5400\tutorial\hello1下的所有文件拷贝到新目录中;

同的环境支持,下面以C54x DSP开发系统为例说明CCS的安装。

完整地安装CCS软件包括以下两个步骤: (1) 将CCS安装光盘放入到光盘驱动器中,运行CCS安装程 序setup.exe。安装完成后,在桌面上会有“CCS 2 C5000”和 “SETUP CCS 2 C5000”两个快捷方式图标,分别对应CCS应用 程序和CCS配置程序。

基于TMS320C6455 McBSP串口的数据传输的设计与实现

u n s i g n d e c h a r r e c vc h a r: 0 ;

—

5 结 束语

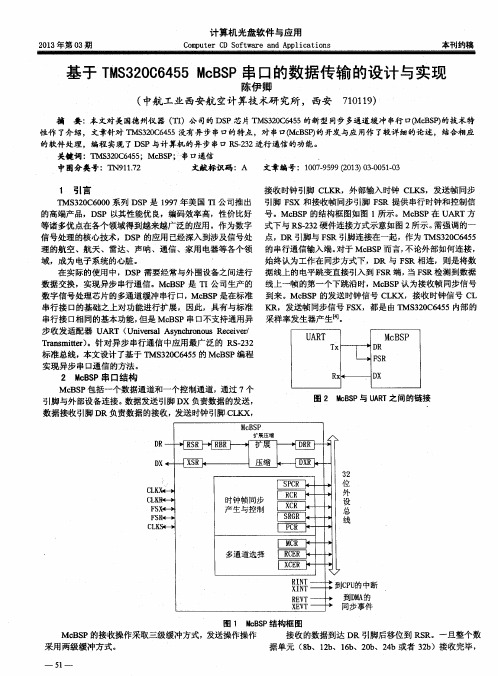

本文针对 T MS 3 2 0 C 6 4 5 5 D S P中的多通道缓冲 串口 ( M c B S P ) 是 一种 同步 串行 接 口, 并不 支持通 用异 步接 收器 / 发 送器 ( UA R T )标准的特点,充分利用 C 6 4 5 5片上硬件资 源,并结合相应的软件处理,将 同步接 口转换为异步 串行 接 口, 很好地解决了 C 6 4 5 5 与UA R T设备实现通信的问题。 作者 已将该方法应用于数字信号处理模块串口文件加载固 化系 统 ,应用 结果表 明,T MS 3 2 0 C 6 4 5 5 通 过 Mc B S P与 计 算机 R S . 2 3 2 可 进行 高速 数据 传输 ,数据 传输 正确 、完 整 , 能够 很好 满足 工程应 用要 求 。

中图分类号:T N 9 1 1 . 7 2

文献标识码 :A 文章鳊号 :1 0 0 7 — 9 5 9 9 ( 2 o 1 3 ) 0 3 — 0 0 5 1 — 0 3

接收 时钟 引脚 C L KR,外 部输 入 时钟 C u ,发送 帧 同步

1 引言 T MS 3 2 0 C 6 0 0 0 系列 D S P是 1 9 9 7年美 国 Ⅱ 公司推 出 的高端产品,DS P 以其性能优 良,编码效率高,性价比好 等诸 多优点在各个领域得到越来越广泛 的应用。作为数字

M c B S P

U A R T

T x

l L

— —

M c B S P

D R

F S R D X

R x

图2 M c B S P与 U A R T之 间的链 接

第七部分 TMS320C54x的软硬件设计

SZU-TI DSPs Lab -

Dr. JI ZHEN

5

等待状态与ta ta的关系 1.4 等待状态与ta的关系 外部器件的存取时间ta 外部器件的存取时间ta ta≤15ns 15ns<ta≤40ns 40ns<ta≤65ns 65ns<ta≤90ns 90ns<ta≤115ns 115ns<ta≤140ns

SZU-TI DSPs Lab -

Dr. JI ZHEN

18

用循环缓冲区实现Z 2.1.4 用循环缓冲区实现Z-1

SZU-TI DSPs Lab -

Dr. JI ZHEN

19

两种实现Z 2.1.5 两种实现Z-1方法的比较

线性缓冲区法

1、新老数据位置直接明了。 新老数据位置直接明了。 需要移动数据。 2、需要移动数据。 要求在一个机器周期中进行一次读和一次写操作, 3、要求在一个机器周期中进行一次读和一次写操作, 因而要求定位在DARAM中。 因而要求定位在DARAM中 DARAM

SZU-TI DSPs Lab -

Dr. JI ZHEN

16

用线性缓冲区实现Z 2.1.3 用线性缓冲区-

Dr. JI ZHEN

17

用循环缓冲区实现Z 2.1.4 用循环缓冲区实现Z-1

滑窗式缓冲区,存放N个最新的样本。 滑窗式缓冲区,存放N个最新的样本。 每次输入新样本时,以新样本改写最老的样本, 每次输入新样本时,以新样本改写最老的样本,滑窗 中的数据不需要移动 循环缓冲区首尾相连 利用片内BK 循环缓冲区长度) BK( 利用片内BK(循环缓冲区长度)寄存器对滑窗寻址 循环缓冲区举例,N=6: 循环缓冲区举例,N=6:

16

CS1 OE WE CS2 A 13 CS1 OE WE CS2 A

第3章+TMS320C54x硬件系统设计

第3章 TMS320C54x硬件系统设计

3.1 TMS320C54x硬件组成部分

HPI 接口 电源回路 时钟回路 复位电路 JTAG 接口 TMS320C54X 芯片 其它 I/O 设备 A/D 及 D/A 接口 存储器扩展

第3章 TMS320C54x硬件系统设计

典型的DSP目标板包括DSP、存储器、模拟控制与处理电路、 各种控制口与通信口、电源处理以及为并行处理提供的同步电路等

TMS320C5402 A(15-0) D(15-0) R/W MSTRB PS GND ≥1 AT29LV1024 A(15-0) I/O(15-0) WE CE OE

TMS320VC5402

37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72

108 107 106 105 104 103 102 101 100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81 80 79 78 77 76 75 74 73

3.3 供电系统设计

C54x系列芯片电源分为两种,即内核电源与I/O电源。I/O电源 一般采用3.3V设计;内核电源采用3.3V、2.5V或1.8V电源

3.3.1 DSP供电电源设计 (1) 3.3V单电源供电。可选用TI公司的TPS7133、TPS7233、 TPS7333芯片,也可以选用Maxim公司的MAX604、MAX748 芯片或LT1117-3.3等芯片。 (2) 采用双电源供电。可以采用TPS73HD301、TPS73HD325、 TPS73HD318等系列芯片。

基于TMS320C6455的视频动目标检测装置设计

e h n e i c- mo —ce s ( MA)a d pn -o g b f r g s ae y t mpe n ih p e aa t n mis n n a c d dr t e me r a cs y ED n igp n u ei t tg o n r i lme thg se d d t r s si . a o

tmem o io n c n . i ntr gs e e i

Ke o d: v g bet eet n bc—ru dud t; MS2 C 5 ; A 7 H yw rs moi jc dtco ; akgon p a T 30 6 5 S A 13 no i e 4 1

鲁 冬

( 南职 业技 术 学 院 信 息 工程 系, 南 郑 ' 5 0 6 河 河 I 。 l 04 ) 4

摘 要 :介 绍一 种 基 于高 速 D P芯 片 T 3 0 6 5 S M¥ 2 C 4 5构 建 的视 频 动 目标检 测装 置 , 效地 利 用 6 5 有 4 5的 大 容 量 内存 空间 等 特 点 , 用 E MA功 能 实现 了高 速 数 据 传 输 的 乒 乓 缓 冲 结 构 设计 , 件 设 计 是 基 于 背 景 更 新 的 动 目标 检 测 算 法 , 采 D 软

第 1 9卷 第 6期

Vo .9 11 No 6 .

电 子 设 计 工 程

El cr ni sg gne rn e to c De in En i e i g

21 0 1年 3月

Ma . 01 r2 J

基于 T 3 0 6 5 MS 2 C 4 5的视频动 目 标检 测 装置设计

文献 标 识 码 : A

文 章 编 号 :1 7 — 2 6 2 1 )6 0 9 ~ 3 6 4 6 3 (0 1 0 — 1 0 0

基于TMS320C6455的高速数据传输系统设计

i n g a l g o r i t h m( S PI HT )i s i mp l e me nt e d . At l a s t ,t h e t e s t e d r e s u l t s o f t h e s y s t e m a r e g i v e n .I t c a n b e f o u n d t h a t t he d e s i g ne d s y s t e m c a n b e

( 1 .Co l l e ge o f El e c t r o n i c I n f o r ma t i o n En g i n e e r i n g,S o u t h - Ce nt e r Un i v e r s i t y f o r Na t i o n a l i t i e s ,W uh a n 43 0 0 7 4) ( 2 .Col l e ge o f El e c t r o ni c I nf o r ma t i o n,W u h a n Un i v e r s i t y,W u h a n 4 3 0 0 7 2 ) ( 3 .W u h a n Di g i t a l En gi n e e r i n g I ns t i t ut e,W u ha n 4 3 0 0 7 4 )

周

( 1 . 中南民族大学电子信息工程学 院

城 田

武汉

昕 王

武汉

鹏。

武汉 4 3 0 0 7 2 )

4 3 0 0 7 4 )

4 3 0 0 7 4 ) ( 2 . 武汉 大学 电子信息学 院

( 3 . 武汉数字工程研究所 摘 要

设计 了 一种 基 于 TMS 3 2 0 C 6 4 5 5的 高 速 数 据 传 输 系 统 。数 据 输 入 和 输 出 分 别 通 过 US B接 口 和 P CI 接 口来 实 现 , 控 制 模 块 通

基于TMS320C6455的高速数字信号处理系统设计

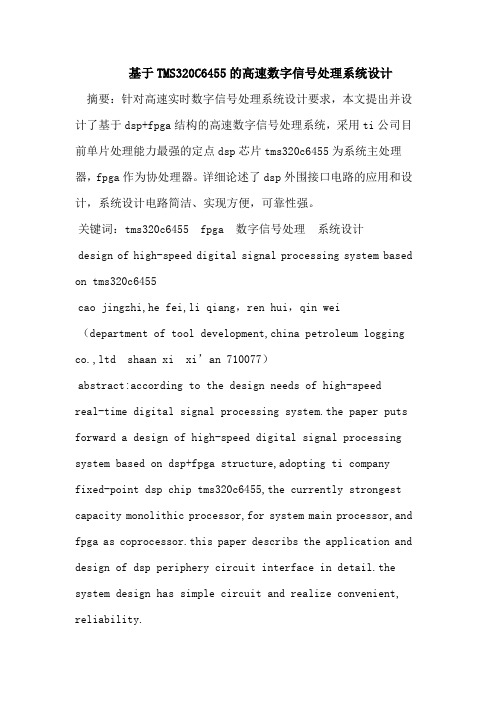

基于TMS320C6455的高速数字信号处理系统设计摘要:针对高速实时数字信号处理系统设计要求,本文提出并设计了基于dsp+fpga结构的高速数字信号处理系统,采用ti公司目前单片处理能力最强的定点dsp芯片tms320c6455为系统主处理器,fpga作为协处理器。

详细论述了dsp外围接口电路的应用和设计,系统设计电路简洁、实现方便,可靠性强。

关键词:tms320c6455 fpga 数字信号处理系统设计design of high-speed digital signal processing system based on tms320c6455cao jingzhi,he fei,li qiang,ren hui,qin wei (department of tool development,china petroleum logging co.,ltd shaan xi xi’an 710077)abstract:according to the design needs of high-speedreal-time digital signal processing system.the paper puts forward a design of high-speed digital signal processing system based on dsp+fpga structure,adopting ti company fixed-point dsp chip tms320c6455,the currently strongest capacity monolithic processor,for system main processor,and fpga as coprocessor.this paper describs the application and design of dsp periphery circuit interface in detail.the system design has simple circuit and realize convenient, reliability.keywords:tms320c6455 fpga digital signal processing system design随着现代电子技术和计算机技术的飞速发展,高性能数字处理器(dsp)的出现,使得高速数字信号处理系统已应用于越来越多的场合,如通信、雷达、智能交通、图像处理等领域,这些信号处理运算量很大、算法结构复杂,且要求高速实时、高性能、灵活地完成各种处理任务。

基于TMS320 C6455的以太网通信程序的设计

基于TMS320 C6455的以太网通信程序的设计摘要:文中介绍了TMS320 C64155 DSP EMAC接口的构成以及工作原理和关键数据结构,参考相关的以太网驱动程序,完成了基于C6455 DSP的以太网通信程序的设计。

该网络通信程序实现了某款信号处理机与上位机之间的高速通信接口。

系统测试结果表明,利用C6455实现的以太网通信接口完全满足系统设计要求,并且系统具有组成简单、系统集成度高等优点。

该方案在其他多功能信号处理设备方面具有一定的应用价值。

关键词:TMS320 C6455;DSP;以太网通信;网络驱动程序随着以太网技术的普及和发展,以太网的通信速率从百兆网逐渐进入了千兆网,甚至万兆网,其通信速率已经满足了常用信号处理机所需要的吞吐率。

而以前仅用来做信号处理的DSP器件逐渐也加入了以太网通信功能,常见的如TI公司的DM642,C6455,C6678等DSP 器件都带有以太网接口,这给一些需要高速通信接口的信号处理板的设计提供了极大的便利。

本文利用某处理板上的TI公司高端DSP器件TMS320 C6455,完成了信号处理板与人机界面之间的高速以太网通信功能。

系统测试结果表明,利用C6455实现的以太网通信接口完全满足系统设计要求,并且系统具有组成简单、系统集成度高等优点。

1 硬件平台信号处理板的主要硬件包括两路高速DAC,两路高速ADC以及一块Xilinx V5的FPGA 和一块TMS320 C6455DSP处理器,其中网络通信接口部分主要包括C6455、PHY芯片和RJ45接口,如图1所示。

C6455的EMAC接口与信号板上的PHY芯片以GMII方式连接,支持千兆双工通信模式。

2 C6455 EMAC接口介绍C6455的EMAC接口主要由3部分构成,包括MDIO模块、EMAC模块、EMAC控制模块。

其中MDIO模块通过802.3协议规定的串行通信接口,完成以太网物理层芯片的配置和管理:EMAC模块负责以太网数据包的发送和接收;EMAC控制模块作为DSP核和EMAC接口之间的桥梁,实现DSP核对EMAC模块和MDIO模块的控制。

2 TMS320C54x数字信号处理器硬件结构

2.2 TMS320C54x的总线结构及流水操作 的总线结构及流水操作 要点

1、为何要设置多内部总线 2、一个机器周期内可完成的存取操作 3、为何要用两个辅助寄存器算术运算单元 4、一个周期内如何执行3操作数指令

2.2.1总线结构 总线结构

TMS320C54x DSP采用先进的哈佛结构并具有 采用先进的哈佛结构并具有 八组总线, 八组总线,其独立的程序总线和数据总线允许同时读 取指令和操作数,实现高度的并行操作。 取指令和操作数,实现高度的并行操作。 采用各自分开的数据总线分别用于读数据和写数 允许CPU在同一个机器周期内进行两次读操作数 据,允许 在同一个机器周期内进行两次读操作数 和一次写操作数。 和一次写操作数。 独立的程序总线和数据总线允许CPU同时访问程 同时访问程 独立的程序总线和数据总线允许 序指令和数据。 序指令和数据。

处理器工作方式状态寄存器(PMST)中的3个状态位与片内存储 器的关系:

MP/MC位 MP/MC位 若MP/MC=0,则片内ROM安排到程序空间 MP/MC=0,则片内ROM安排到程序空间 ROM 则片内ROM ROM不安排到程序空间 若MP/MC=1, 则片内ROM不安排到程序空间 OVLY位 OVLY位 若OVLY=1, 则片内RAM安排到程序和数据空间 RAM安排到程序和数据空间 OVLY=1, 则片内RAM RAM只安排到数据存储空间 若OVLY=0, 则片内RAM只安排到数据存储空间 OVLY=0, 则片内RAM DROM位 DROM位 当DROM=1,则部分片内ROM安排到数据空间 DROM=1,则部分片内ROM安排到数据空间 ROM 当DROM=0,则片内ROM不安排到数据空间 DROM=0,则片内ROM不安排到数据空间 ROM DROM与MP/MC的用法无关 DROM与MP/MC的用法无关

TMS320C6455的DDR2电路的信号完整性设计

TMS320C6455的DDR2电路的信号完整性设计曹亚良;张福洪【摘要】该文利用Ansoft Designer和SIwave配合Cadence Allegro对TMS320C6455的DDR2电路进行信号完整性设计的流程,阐述了高速电路设计过程中如何设定约束规则以及利用仿真工具对PCB进行前仿真和后仿真的方法,有助于硬件设计人员进行高速电路设计.【期刊名称】《杭州电子科技大学学报》【年(卷),期】2012(032)005【总页数】4页(P163-166)【关键词】高速数字信号;数字信号处理器;双倍数据速率;信号完整性【作者】曹亚良;张福洪【作者单位】杭州电子科技大学通信工程学院,浙江杭州310018;杭州电子科技大学通信工程学院,浙江杭州310018【正文语种】中文【中图分类】TN410 引言TMS320C6455是 TI公司的高性能 DSP,在通信、网络、音视频处理等领域有广泛应用。

TMS320C6455带有一个DDR2控制器,由于DDR2的高速性,信号通过传输介质时很容易受到串扰和反射的影响[1]。

为了确保DDR2信号的可靠传输,绘制PCB时必须进行信号完整性设计。

文献2介绍了高速电路设计中处理信号完整性问题的基本方法;文献3给出了TMS320C6455的DDR2电路的布线参考规范;文献4介绍了使用Hyperlynx对DDR2电路进行前仿真和后仿真的过程。

文献5阐述了在Xilinx公司的FPGA平台上设计DDR2控制器,并进行信号完整性仿真和测试的过程,该文中使用的DDR2器件为SO-DIMM接口的内存条。

本文阐述利用Ansoft Designer和SIwave结合Cadence Allegro完成DDR2电路的信号完整性设计的过程,使用的DDR2器件为Micron公司的DDR2颗粒。

1 DDR2简介DDR2即Double Data Rate2(双倍数据速率),是一种在不提高时钟速率的前提下使数据速率提升为原来的两倍的技术。

TMS320C6455

Ar t Co l l e g e S t u d e n t s S wi v e l De s i g n Pr a c t i c e

LI Ya n

( I n d u s t r i a l Vo c a t i o n a l a n d T e c h n i c a l Co l l e g e t o Y a n g z h o u , Y a n g z h o u 2 2 5 1 2 7 , Ch i n a )

目的 。

【 参 考 文 献】

[ 1 1 董伟利. 大学生公寓家具人性化设计 [ J 】 . 内蒙古工业大学学报: 社会科学版 , 2 0 1 3 ( 2 ) . [ 2 ] 于伸, 刘新 明, 杨玲 高校 学生公寓家具研 究( 下) 设计创意部分 [ J ] . 家具与室内装饰, 2 0 0 7 ( 9 ) . [ 3 】 郑伊, 李晶源. 行为模式对大学生公寓室内 空间 设计 的影响[ J ] . 山西建筑, 2 0 0 9 ( 1 1 ) .

An g l e , z h a n g c a n me e t t h e g e n e r a l t h e o r y o f l e a r n i n g , b u t a l s o s h o u l d h a v e p r o f e s s i o n a l c o u r s e a n d t h e f u n c t i o n o f t h e c o mp u t e r g r a p h i c s p r o d u c t i o n n e e d s . T h e d e s i g n o f t h e c h a i r wa n t t o c o n s i d e r t h e c o mf o r t o f l e a r n i n g f o r a l o n g t i me . T h i s b u i l d i n g h a s a v a r i e t y o f f u n c t i o n s , c a n wo r k or f l o n g t i me s t u d y o f c o l l e g e s t u d e n t s t o p r o v i d e a g o o d e n v i r o n me n t . i o n t o me e t s t u d e n t s ’ p h y s i o l o g i c a l a n d p s y c h o l o g i c a l r e q u i r e me n t s o f mu l t i — f u n c t i o n a l n e w— t y p e mul t i — f u n c t i o n a l d e s k s a n d c h a i r s , b o t h c a n s a t i s f y t h e n e e d s o f a r t c o l l e g e

基于TMS320C6455的视频动目标检测装置设计

基于TMS320C6455的视频动目标检测装置设计摘要:介绍一种基于高速DSP 芯片TMS320C6455 构建的视频动目标检测装置,有效地利用6455 的大容量内存空间等特点,采用EDMA 功能实现了高速数据传输的乒乓缓冲结构设计,软件设计是基于背景更新的动目标检测算法,测试结果证明该装置功能完备,实时性好,环境适应性强,在实时监控等领域有很大的应用前景。

关键词:动目标检测;背景更新;TMS320C6455;SAA7113H 视频动目标检测与跟踪技术是当今世界重要的研究课题,它涉及图像处理、自动控制、计算机应用等学科,广泛应用于军事领域的各个方面:预警、火控、制导等;在民用领域的应用也随着该技术的日益成熟,以及成本的大幅度下降而逐渐得到越来越广泛的推广。

所谓视频动目标检测装置是一个可以完成标准制式视频图像的采集和处理,从而实现运动目标识别与跟踪的智能图像处理系统,这类系统具有运行复杂灵活的算法以及处理大数据量视频图像的能力,还要求系统具有实时性,同时体积、功耗、稳定性等也有较严格的要求。

本文从系统设计的角度出发,采用TI 公司的TMS320C6455 高速DSP 芯片,以FPGA、SAA7113H 等高集成度的外围电路构建了一种满足实时性要求的动目标检测装置,该装置体积小、功耗低,在实时监控等领域有很大的应用前景。

1 系统硬件设计1.1 TMS320C6455 简介TMS3206455 是TI 公司推出的最新高速DSP,其主要特点是结构上采用了Veloei(VLIW:Very Long Instruction Word)超长指令字内核结构,最高时钟频率为1.2 GHz,每个周期可以同时执行8 条32 bit 的指令,16 位定点处理能力可达到9 600 MIPS/MMACS(16-bits)。

片内采用2 级高速缓存结构,其中L2 有2 096 K 字节的RAM 数据空间可供使用,6455 还具有强大的外部存储器接口EMIF,可以连接DDR2 等高速外部存储器,同时集成了高速串行接口。

基于TMS320C6455的红外与可见光实时图像融合系统硬件设计

基于TMS320C6455的红外与可见光实时图像融合系统硬件

设计

王鹏;李飚;刘斐

【期刊名称】《重庆理工大学学报(自然科学版)》

【年(卷),期】2013(027)004

【摘要】采用新型高速DSP器件TMS320C6455和高性能的Spartan-6系列FPGA设计了图像融合处理系统.分析了系统的设计原理及硬件结构设计方法,并对系统中各功能模块进行了介绍.实际应用表明:该系统具有实时性和准确性的特点.【总页数】5页(P85-89)

【作者】王鹏;李飚;刘斐

【作者单位】国防科技大学ATR国防重点实验室,长沙410073

【正文语种】中文

【中图分类】TP391.41

【相关文献】

1.基于TMS320C6455的红外与可见光实时图像融合系统硬件设计 [J], 王鹏;李飚;刘斐;

2.红外与可见光图像实时配准融合系统 [J], 刘卫光;郭师红;周利华

3.基于OpenCV的红外与可见光图像实时融合系统 [J], 任贵文;贺行政;康荣学;李旭明

4.基于DSP与FPGA的红外与可见光实时图像融合系统硬件设计 [J], 邢素霞

5.基于异构多核构架的红外与可见光实时融合系统 [J], 熊伟;杨红雨;袁学东;李晓峰

因版权原因,仅展示原文概要,查看原文内容请购买。

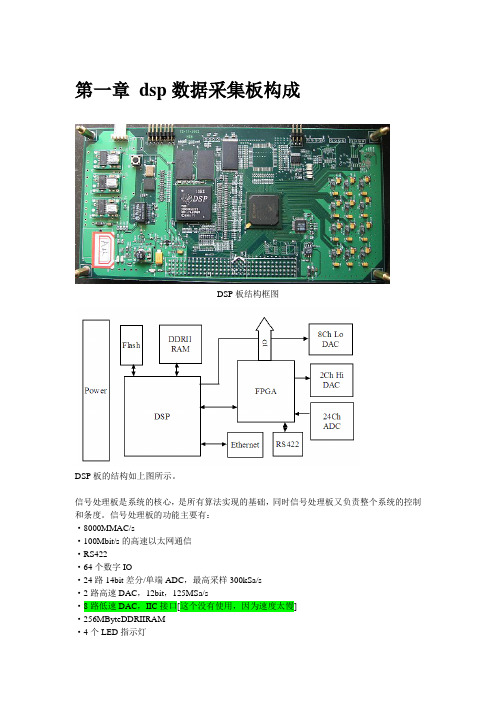

dsp6455板卡资料

第一章dsp数据采集板构成DSP板结构框图DSP板的结构如上图所示。

信号处理板是系统的核心,是所有算法实现的基础,同时信号处理板又负责整个系统的控制和条度。

信号处理板的功能主要有:·8000MMAC/s·100Mbit/s的高速以太网通信·RS422·64个数字IO·24路14bit差分/单端ADC,最高采样300kSa/s·2路高速DAC,12bit,125MSa/s·8路低速DAC,IIC接口[这个没有使用,因为速度太慢]·256MByteDDRIIRAM·4个LED指示灯1、DSPTMS320C6455的功能框图该平台的核心器件数字信号处理器采用德州仪器最新款的高性能数字信号处理器TMS320C6455。

与以往的数字信号处理器相比,TMS320C6455具有更强大的运算能力和更大的IO带宽。

TMS320C6455工作在1GHz,可实现每秒80亿次乘法累加(MAC),TMS320C6455增加了更多的片内存储器,具有256K的一级程序缓存和256K的一级数据缓存,具有2M的可配置的二级缓存和256K的只读存储器。

TMS320C455采用697脚的BGA 封装。

TMS320C6455不但具有强大的处理能力还有丰富的对外接口,来构成一个完整的应用系统,该信号处理平台的大部分器件都是接在TMS320C6455上的。

TMS320C6455的主要接口如下·64位,133-MHz EMIFA接口可以与同步存储器连接,例如SBSRAM、ZBT SRAM。

也可以同异步存储器实现无缝连接,例如SRAM、FLASH和EEPROM。

该接口还可以和标准同步器件和用户逻辑器件连接,例如FPGA、CPLD、ASICs。

·四个高速串行IO接口·32位DDR2内存接口·32(16)位HPI,32位PCI接口·一个Inter-Integrated Circuit接口·两个MCBSP接口·一个10/100/1000MBPs自适应以太网接口·两个64位的定时器·一个UTOPIA接口·16个通用数字IO口2、FPGAVirtexII1000的资源情况FPGA采用Xinlix公司的Virtex II系列的XC2V1000,该器件的密度为100万门。

TMS320C6455高速SRIO接口设计

TMS320C6455高速SRIO接口设计引言数字信号处理技术已广泛应用于通信、雷达、声纳、遥感、图形图像处理和语音处理等领域。

随着现代科技的发展,尤其是半导体工艺的进入深亚微米时代,新的功能强劲的高性能数字信号处理器(DSP)也相继推出,如ADI(美国模拟器件)公司的TigerSHARC系列和TI(德州仪器)公司的C6000系列,但是,要实现对运算量和实时性要求越来越高的DSP 算法,如对基于分数阶傅立叶变换的Chirp信号检测与估计,合成孔径雷达(SAR)成像,高频地波雷达中的自适应滤波和自适应波束形成等算法,单片DSP 仍然显得力不从心。

这些挑战主要涉及两个主题:一是计算能力,指设备、板卡和系统中分别可用的处理资源。

采用多DSP、多FPGA系统,将是提高运算能力的一个有效途径。

二是连接性,从本质上说就是实现不同设备、板卡和系统之间的“快速”数据转移。

对于一些复杂的信息系统,对海量数据传输的实时性提出了苛刻的要求,多DSP之间、DSP与高速AD采集系统、DSP与FPGA间的高速数据传输,是影响信号处理流程的主要瓶颈之一。

TI公司最新推出的高性能TMS320C6455(下文称C6455)处理器,具有高速运算能力的同时集成了高速串行接口SRIO,方便多DSP以及DSP与FPGA之间的数据传输,在一定程度上满足了高速实时处理和传输的要求。

本文在多DSP+FPGA通用信号处理平台的基础上,深入研究了多DSP间,DSP与FPGA间的SRIO 的数据通信和加载技术的软硬件设计与实现。

这些技术包括了目前SRIO接口的各种应用方式,可作为SRIO接口及C6455开发提供参考[1-3]。

1 C6455特性及SRIO标准介绍C6455是目前单片处理能力最强的新型高性能定点DSP,它是TI 公司基于第三代先进VeloviTI VLIW(超长指令字)结构开发出来的新产品。

最高主频为1.2GHz,16位定点处理能力为9600MMAC/s。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1Prerequisites PreliminaryApplication ReportSPRAAA8A–August2006Implementing Serial Rapid I/O PCB Layout on aTMS320C6455Hardware Design Todd Hiers DSP Hardware ApplicationsThis application report contains implementation instructions for the Serial Rapid I/O(SRIO)interface on the TMS320C6455DSP device.The approach to specifyinginterface timing and physical requirements for the SRIO interface is quite different thanprevious approaches for other interfaces.Serial Rapid I/O is an industry-standard high-speed switched-packet interconnect.Physical layer data transmission utilizes analog serializer/deserializers(serdes)to feedlow-output-swing differential CML buffers.Proper printed circuit board(PCB)design forthis interface resembles analog or RF design,and is very different than traditionalparallel digital bus design.Due to this analog nature of SRIO,it is not possible to specify the interface in atraditional DSP digital interface manner.Furthermore,it is undesirable to specify theinterface in terms of the raw physical requirements laid out by the SRIO specification.Understanding the SRIO specification and producing a compliant PCB based on theexplicit and implicit requirements there demands significant time,experience,andexpensive tools.For the TMS320C6455SRIO interface,the approach is to reduce the specification to aset of easy-to-follow PCB routing rules.TI has performed the simulation and systemdesign work to ensure SRIO interface requirements are met.This document describesthe content of this SRIO implementation.Contents1Prerequisites (1)2TMS320C6455Supported Serial RapidIO Devices (2)3Description of the Serial Rapid I/O Hardware Design Files (2)4PCB Routing Rules (2)5Device Settings (7)6References (10)The goal of the C6455collateral is to make system implementation easier for the customer by providing the system solution.For this Serial RapidIO(SRIO)interface,it is not assumed that the system designer is familiar with SRIO,serializer-deserializer(SERDES)technology,or RF/Microwave PCB design.However, it is still expected that the PCB design work be supervised by a knowledgeable high speed digital PCB designer and an assumption is made that the PCB designer is using established high speed design rules.SPRAAA8A–August2006Implementing Serial Rapid I/O PCB Layout on a TMS320C6455Hardware Design1 Submit Documentation Feedback2TMS320C6455Supported Serial RapidIO Devices3Description of the Serial Rapid I/O Hardware Design Files4PCB Routing Rules 4.1Minimum PCB Stackup4.2General Trace/Space and Via SizesPreliminaryTMS320C6455Supported Serial RapidIO DevicesRapidIO is an industry-standard high-speed switched-packet interconnect.The RapidIO specification allows a device to connect to any other device,so long as the two devices conform to a commonphysical-layer specification.TI DSPs support connecting to any Serial RapidIO device that complies with the Serial RapidIO specification revision 1.2or later.The SRIO Hardware Design files included with this report are described inTable 1.Table 1.SRIO Hardware Design FilesThe minimum PCB stackup for routing the TMS320C6455is a six-layer stackup as described in Table 2.Table 2.Minimum PCB StackupLayer Type Description 1Signal Top Routing 2Plane Ground 3Plane Split Power 4Signal Internal Routing5Plane Ground 6SignalBottom RoutingAdditional layers may be added as needed.All layers with SRIO traces must be able to achieve 100ohms differential impedance.Note:The provided sample board file shows a twelve-layer stackup,but not all of these layers are necessary to use the SRIO interface.The key concern for RapidIO signal traces is to achieve 100Ohm differential impedance.This differential impedance is impacted by trace width,trace spacing,distance between planes,and dielectric material.Verify with a proper PCB manufacturing tool that the trace geometry for all SRIO traces results in exactly 100Ohms differential impedance traces.Of secondary concern is the insertion loss caused by the traces.Due to the skin effect,wider traces will have lower losses than narrower ones.Therefore,longer SRIO runs should use wider traces for lower yers in the stackup that are set to 100Ohm differential impedance with wider traces may be less desirable for routing other signals.Table 3shows recommendations for minimum trace width by SRIO signal run lengthImplementing Serial Rapid I/O PCB Layout on a TMS320C6455Hardware Design2SPRAAA8A–August 2006Submit Documentation Feedback4.3Serial RapidIO Interface Routing Requirements4.3.1Receiver EndPreliminaryPCB Routing RulesTable 3.Minimum Trace WidthSignal Run Length,up to Minimum trace width 10in /25cm 4mil /.1mm 20in /50cm 6mil /.15mm 30in /75cm8mil /.2mmThe C6455sample PCB is routed using 4mil traces and 4mil minimum trace spacing.100Ohmsdifferential impedance is achieved with 4mil traces and 10mil spaces on the Top and Bottom layers,and 4mil traces with 5mil spaces on internal layers.Escape and general SRIO routing vias have 8mil holes with 18mil pads.Micro and/or blind/buried vias are neither required nor prohibited.The PCB BGA padC6455by the Flip Chip Ball Grid Array Package Reference Guide available at The C6455is a 0.8mm ball pitch part and should follow the 0.8The PCB for the SRIO link partner device should follow its manufacturer's guidelines.The approach used in this reference design for specifying suitable RapidIO routing breaks the physical connection down into three component pieces:receiver end,transmitter end,and interconnect.The receiver and transmitter end are the pieces closest to the packages of the connected devices.The receiver end goes from the BGA pads to the capacitors.The transmitter end is simply the BGA escape paths for the differential pairs.Those two pieces of the reference layout are designed to be copied exactly into the target board.The interconnect joins the receiver and transmitter ends,and it is not intended to be copied directly,as board placements will vary from the sample.Figure 1below shows the connection on the receiver end.The trace from the BGA pad to the capacitor be on the top layer.On the other side of the capacitor,it is recommended to via to another layer.The BGA breakout should be implemented exactly as shown.The trace widths and separation should be altered based on the board stackup to meet the 100Ωdifferential impedance requirement.Also,traces may be necked down to escape the BGA,if necessary.An 0402or smaller size,0.1µf capacitor is recommended for AC coupling of the data lines.SPRAAA8A–August 2006Implementing Serial Rapid I/O PCB Layout on a TMS320C6455Hardware Design 3Submit Documentation FeedbackPreliminary PCB Routing RulesFigure1.Receiver END BGA Breakout4.3.2Transmitter EndFigure2below shows the connection on the transmitter end.This trace may be on any signal layer the top.Internal layers are recommended for their superior shielding characteristics.The BGA breakout should be implemented exactly as shown.The trace widths and separation should be altered based on the board stackup to meet the100Ωdifferential impedance requirement.Also,traces may be necked down to escape the BGA,if necessary.4Implementing Serial Rapid I/O PCB Layout on a TMS320C6455Hardware Design SPRAAA8A–August2006Submit Documentation Feedback4.3.3Interconnect4.3.4Length MatchingPreliminaryPCB Routing RulesFigure 2.Transmitter End BGA BreakoutThe geometry of the traces to link the transmitter and receiver ends is determined by the placement in the target system.Therefore,it is not possible to specify an exact layout for the interconnect.Instead,the trace may be placed as required,so long as it meets the following requirements:•Edge-coupled,matched-length (±50mils)differential pair •No stubs•No more than 30inches (75cm)pin-to-pin,for 8-mil (.2mm)wide traces over FR4material •100Ωdifferential impedance•No more than 3sets of vias (not including via for BGA breakout on transmit end)•Other signals are separated by at least 2x the differential spacing •Internal layers are strongly preferred.Avoid top and bottom layers•If connectors are used,they must be of a suitable 100ohm differential-impedance,high-speed type,and count as 1”of trace for each connector pair•If cabling is used,it must be of a suitable controlled-impedance type (100ohm differential or 50ohm single ended),and counts as 1"of trace for each 1'of cable.•If a mid bus probe is used,it must follow both TI’s and the probe manufacturer’s guidelines,and counts as 2”of traceIf the SRIO peripheral will be used in 1x mode,then there is no lane-to-lane length matching requirement.If the SRIO peripheral will be used in 4x mode,then:•All TX lanes connected to a device must all be +/-5inches (12.5cm)in length from each other •All RX lanes connected to a device must all be +/-5inches (12.5cm)in length from each other •There is no requirement that the TX lengths match the RX lengthsSPRAAA8A–August 2006Implementing Serial Rapid I/O PCB Layout on a TMS320C6455Hardware Design5Submit Documentation Feedback4.3.5Mid Bus Probe (Optional)4.3.6Connectors (Optional)4.3.7Cabling (Optional)PreliminaryPCB Routing RulesA mid bus probe can be used to observe traffic flowing down a link.Because the probe requires a special attachment point,it can degrade signal quality.The following rules must be observed to include a mid bus probe:•Follow the Probe manufacturer’s guidelines for probe pads and layout•If the stubs can be kept under 250mils (6.35mm)then connecting the probe lands as stubs to the transmission line is acceptable•If the stubs cannot be kept under 250mils (6.35mm)then the probe lands should be connected in-line with the rest of the transmission lineAny connectors used must be controlled impedance (50Ohm single ended or 100Ohm differential)and suitable for microwave transmissions.Suitable connectors are typically categorized as “backplane”type connectors.The connectors should have less than 1dB insertion loss below 6GHz.Some suggested connectors are:•CN074–AMC Connector •Tyco Z-DOK•Tyco Z-PAK HM ZdAny cabling used must be controlled impedance (50Ohm single ended or 100Ohm differential)and suitable for microwave transmissions.Recommended cable types are listed below:•50Ohm Coaxial –Commonly used with SMA connectors,4cables required for 1x link,16for 4x link q RG142q RG316q RG178•Infiniband –assembled cables available in 1x and 4x widthsImplementing Serial Rapid I/O PCB Layout on a TMS320C6455Hardware Design6SPRAAA8A–August 2006Submit Documentation Feedback4.4Power SupplyRequirements5Device SettingsPreliminaryDevice SettingsThe power supply and bypassing requirements foras part of the TMS320C6455Design Guide and Comparisons to TMS320TC6416T Figure 3.Power Plane SplitsSome of the SERDES register values should be set based on parameters from the physical PCB.Others are not dependent on the PCB,but are set based on the SRIO electrical specification.The following sections describe the recommended settings for the receivers and transmitters.More these registers can be found in the TMS320C645x Serial Rapid IO (SRIO)User’s Guide SPRAAA8A–August 2006Implementing Serial Rapid I/O PCB Layout on a TMS320C6455Hardware Design 7Submit Documentation Feedback5.1Receive Channel ConfigurationPreliminaryDevice SettingsTable 4lists the recommended settings for receiver channels that can be set in the SERDES Receive Channel Configuration Registers (SERDES_CFGRXn_CNTL).Table 4.SERDES Receive Channel Configuration Register SettingsBits Field Setting Description19:22EQ 0001Fully Adaptive Equalization 18:16CDR000First Order.Sufficient for SRIO clocking scheme(asynchronous with low frequency offset)15:14LOS 00Disabled.Loss of Signal detection not used in SRIO 13:12ALIGN01Comma Alignment.SRIO uses comma alignment during lane initialization10:8TERM 001Common point is 80%ofVDDT.This is the appropriate setting for AC coupled lines 7INVPAIR 0Non-inverted –use when TXP connects to RXP and TXN connects to RXN1Inverted –use when TXP connects to RXN and TXN connects to RXP (1)6:5RATE 00Full –Use for 3.125GHz and 2.5GHz line rates01Half –Use for 1.25GHz line rate4:2BUS-WIDTH 00010-bit.SRIO uses 10-bit character groups.ENRX0Disabled –for unused lanes 1Enabled –for active lanes(1)On inverted pairs,polarity inversion can be done at the receiver end or the transmitter end,but not bothImplementing Serial Rapid I/O PCB Layout on a TMS320C6455Hardware Design8SPRAAA8A–August 2006Submit Documentation Feedback5.2Transmit Channel Configuration PreliminaryDevice SettingsTable5lists the recommended settings for transmitter channels that can be set in the SERDES Transmit Channel Configuration Registers(SERDES_CFGTXn_CNTL).Table5.SERDES Transmit Channel Configuration Register Settings Bits Field Setting Description16ENFTP1Fixed Phase.Required for4xmode.Do not care in1x mode.15:e for lines up to10inches(25cm)e for lines up to14inches(35cm)e for lines up to18inches(45cm)e for lines up to22inches(55cm)e for lines up to26inches(65cm)e for lines up to30inches(75cm) 11:e for lines up to10inches(25cm)e for lines up to20inches(50cm)e for lines up to30inches(75cm) 8CM1Raised Common Mode.Helpfulin preventing signal distortionat SWING amplitudes over750mV 7INVPAIR0Non-inverted–use when TXPconnects to RXP and TXNconnects to RXN1Inverted–use when TXPconnects to RXN and TXNconnects to RXP(1) 6:5RATE00Full–Use for3.125GHz and2.5GHz line rates01Half–Use for1.25GHz linerate4:2BUS WIDTH00010-bit.SRIO uses10-bitcharacter groups.0ENTX0Disabled–for unused lanes1Enabled–for active lanes(1)On inverted pairs,polarity inversion can be done at the receiver end or the transmitter end,but not bothSPRAAA8A–August2006Implementing Serial Rapid I/O PCB Layout on a TMS320C6455Hardware Design9 Submit Documentation Feedback6ReferencesPreliminaryReferencesmay be downloaded from the RapidIO Trade Association’s web site,The TMS320C645x Serial Rapid IO (SRIO)User’s Guide explains the functional operation of the SRIO peripheral.The TMS320C6455Design Guide and Comparisons to TMS320TC6416T (SPRAA89)containsinformation related to powering,clocking,and configuring the C6455,including the SRIO peripheral.The High Speed DSP Systems Design Guide (SPRU889)contains general guidance on many matters of high performance DSP system design.The Flip Chip Ball Grid Array Package Reference Guide provides guidance with respect to PCB design and Texas Instruments BGA packages.It rules,PCB assembly parameters,rework process,thermal management,troubleshooting tips plus other critical information.10Implementing Serial Rapid I/O PCB Layout on a TMS320C6455Hardware DesignSPRAAA8A–August 2006Submit Documentation FeedbackIMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityLow Power Wireless /lpw Telephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2006, Texas Instruments Incorporated。