SMDT-60I-12中文资料

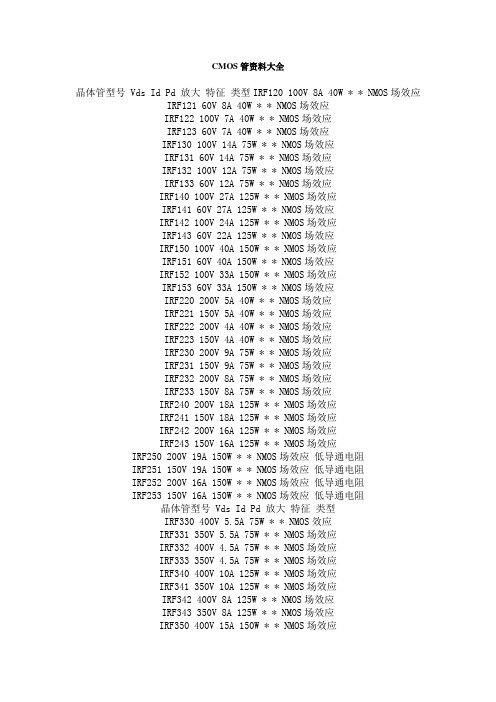

CMOS管资料大全

CMOS管资料大全晶体管型号 Vds Id Pd 放大特征类型IRF120 100V 8A 40W * * NMOS场效应IRF121 60V 8A 40W * * NMOS场效应IRF122 100V 7A 40W * * NMOS场效应IRF123 60V 7A 40W * * NMOS场效应IRF130 100V 14A 75W * * NMOS场效应IRF131 60V 14A 75W * * NMOS场效应IRF132 100V 12A 75W * * NMOS场效应IRF133 60V 12A 75W * * NMOS场效应IRF140 100V 27A 125W * * NMOS场效应IRF141 60V 27A 125W * * NMOS场效应IRF142 100V 24A 125W * * NMOS场效应IRF143 60V 22A 125W * * NMOS场效应IRF150 100V 40A 150W * * NMOS场效应IRF151 60V 40A 150W * * NMOS场效应IRF152 100V 33A 150W * * NMOS场效应IRF153 60V 33A 150W * * NMOS场效应IRF220 200V 5A 40W * * NMOS场效应IRF221 150V 5A 40W * * NMOS场效应IRF222 200V 4A 40W * * NMOS场效应IRF223 150V 4A 40W * * NMOS场效应IRF230 200V 9A 75W * * NMOS场效应IRF231 150V 9A 75W * * NMOS场效应IRF232 200V 8A 75W * * NMOS场效应IRF233 150V 8A 75W * * NMOS场效应IRF240 200V 18A 125W * * NMOS场效应IRF241 150V 18A 125W * * NMOS场效应IRF242 200V 16A 125W * * NMOS场效应IRF243 150V 16A 125W * * NMOS场效应IRF250 200V 19A 150W * * NMOS场效应低导通电阻IRF251 150V 19A 150W * * NMOS场效应低导通电阻IRF252 200V 16A 150W * * NMOS场效应低导通电阻IRF253 150V 16A 150W * * NMOS场效应低导通电阻晶体管型号 Vds Id Pd 放大特征类型IRF330 400V 5.5A 75W * * NMOS效应IRF331 350V 5.5A 75W * * NMOS场效应IRF332 400V 4.5A 75W * * NMOS场效应IRF333 350V 4.5A 75W * * NMOS场效应IRF340 400V 10A 125W * * NMOS场效应IRF341 350V 10A 125W * * NMOS场效应IRF342 400V 8A 125W * * NMOS场效应IRF343 350V 8A 125W * * NMOS场效应IRF350 400V 15A 150W * * NMOS场效应IRF352 400V 13A 150W * * NMOS场效应IRF353 350V 13A 150W * * NMOS场效应IRF360 400V 25A 300W * * NMOS场效应IRF420 500V 2.5A 40W * * NMOS场效应IRF421 450V 2.5A 40W * * NMOS场效应IRF422 500V 2.5A 40W * * NMOS场效应IRF423 450V 2.5A 40W * * NMOS场效应IRF430 500V 4.5A 75W * * NMOS场效应IRF431 450V 4.5A 75W * * NMOS场效应IRF432 500V 4A 75W * * NMOS场效应IRF433 450V 4A 75W * * NMOS场效应IRF440 500V 8A 125W * * NMOS场效应IRF441 450V 8A 125W * * NMOS场效应IRF442 500V 7A 125W * * NMOS场效应IRF443 450V 7A 125W * * NMOS场效应IRF450 500V 8A 150W * * NMOS场效应IRF451 450V 8A 150W * * NMOS场效应IRF452 500V 7A 150W * * NMOS场效应IRF453 450V 7A 150W * * NMOS场效应IRF460 500V 21A 300W * * NMOS场效应IRF510 100V 2.5A 20W * * NMOS场效应IRF511 60V 2.5A 20W * * NMOS场效应IRF512 100V 2A 20W * * NMOS场效应IRF513 60V 2A 20W * * NMOS场效应IRF520 100V 8A 40W * * NMOS场效应IRF521 60V 8A 40W * * NMOS场效应IRF522 100V 7A 40W * * NMOS场效应IRF523 60V 7A 40W * * NMOS场效应IRF530 100V 14A 75W * * NMOS_GDS场效应IRF531 60V 14A 75W * * NMOS场效应IRF532 100V 12A 75W * * NMOS场效应IRF533 60V 12A 75W * * NMOS场效应IRF540 * 100V 27A 125W * * NMOS场效应IRF541 60V 27A 125W * * NMOS场效应IRF542 100V 24A 125W * * NMOS场效应IRF543 60V 22A 125W * * NMOS场效应塑封2006-12-26 10:47 音频晶体管型号 Vds Id Pd 放大特征类型IRF610 200V 3.3A 43W * * NMOS场效应IRF611 150V 2.5A 20W * * NMOS场效应IRF612 200V 2A 20W * * NMOS场效应IRF613 150V 2A 20W * * NMOS场效应IRF620 200V 5A 40W * * NMOS场效应IRF621 150V 5A 40W * * NMOS场效应IRF622 200V 4A 40W * * NMOS场效应IRF623 150V 4A 40W * * NMOS场效应IRF630 200V 9A 75W * * NMOS场效应IRF631 150V 9A 75W * * NMOS场效应IRF632 200V 8A 75W * * NMOS场效应IRF633 150V 8A 75W * * NMOS场效应IRF640 * 200V 18A 125W * * NMOS场效应IRF641 150V 18A 125W * * NMOS场效应IRF642 200V 16A 125W * * NMOS场效应IRF643 * 150V 16A 125W * * NMOS场效应晶体管型号 Vds Id Pd 放大特征类型IRF710 400V 1.5A 20W * * NMOS场效应IRF711 350V 1.5A 20W * * NMOS场效应IRF712 400V 1.3A 20W * * NMOS场效应IRF713 350V 1.3A 20W * * NMOS场效应IRF720 400V 3.3A 50W * * NMOS场效应IRF730 400V 5.5A 75W * * NMOS场效应IRF731 350V 5.5A 75W * * NMOS场效应IRF732 400V 4.5A 75W * * NMOS场效应IRF733 350V 4.5A 75W * * NMOS场效应IRF740 400V 10A 125W * * NMOS场效应IRF741 350V 10A 125W * * NMOS场效应IRF742 400V 8A 125W * * NMOS场效应IRF743 350V 8A 125W * * NMOS场效应IRF830 500V 4.5A 75W * * NMOS场效应IRF831 450V 4.5A 75W * * NMOS场效应IRF832 500V 4A 75W * * NMOS场效应IRF833 450V 4A 75W * * NMOS场效应IRF841 450V 8A 125W * * NMOS场效应IRF842 500V 7A 125W * * NMOS场效应IRF843 * 450V 7A 125W * * NMOS场效应晶体管型号 Vds Id Pd 放大特征类型IRF9530 100V 12A 75W * * PMOS场效应IRF9531 60V 12A 75W * * PMOS场效应IRF9541 60V 19A 125W * * PMOS场效应IRF9610 200V 1A 20W * * PMOS场效应IRF9630 200V 6.5A 75W * * PMOS场效应晶体管型号 Vds Id Pd 放大特征类型IRFF110 100V 3.5A 15W * * NMOS场效应IRFF111 100V 3.5A 15W * * NMOS场效应IRFF112 100V 3A 15W * * NMOS场效应IRFF113 100V 3A 15W * * NMOS场效应IRFF120 100V 6A 24W * * NMOS场效应IRFF121 60V 6A 24W * * NMOS场效应IRFF122 100V 5A 20W * * NMOS场效应IRFF123 60V 5A 20W * * NMOS场效应IRFF130 100V 8A 25W * * NMOS场效应IRFF131 60V 8A 25W * * NMOS场效应IRFF132 100V 7A 25W * * NMOS场效应IRFF133 60V 7A 25W * * NMOS场效应IRFBC20 600V 2.5A 50W * * NMOS场效应IRFBC30 600V 3.6A 74W * * NMOS场效应IRFBC40 600V 6.2A 125W * * NMOS场效应IRFBE30 800V 2.8A 75W * * NMOS场效应IRFD113 60V 0.8A 1W * * NMOS场效应IRFD120 100V 1.3A 1W * * NMOS场效应IRFD123 80V 1.1A 1W * * NMOS场效应IRFD9120 100V 1A 1W * * NMOS场效应IRFI730 400V 4A 32W * * NMOS场效应IRFI744 400V 4A 32W * * NMOS场效应晶体管型号 Vds Id Pd 放大特征类型IRFP054 60V 65A 180W * * NMOS场效应IRFP140 100V 30A 150W * * NMOS场效应IRFP150 100V 40A 180W * * NMOS场效应IRFP240 200V 19A 150W * * NMOS场效应IRFP250 200V 33A 180W * * NMOS场效应IRFP340 400V 10A 150W * * NMOS场效应IRFP350 400V 16A 180W * * NMOS场效应IRFP353 350V 14A 180W * * NMOS场效应IRFP440 500V 8A 150W * * NMOS场效应IRFP450 500V 14A 180W * * NMOS场效应IRFP460 500V 20A 250W * * NMOS场效应IRFP9140 100V 19A 150W * * PMOS场效应IRFP9240 200V 12A 150W * * PMOS场效应IRFPF40 900V 4.7A 150W * * NMOS场效应IRFPG42 1000V 4A 150W * * NMOS场效应IRFS9630 200V 6.5A 75W * * PMOS场效应IRFU020 50V 15A 42W * * NMOS场效应晶体管型号 Vds Id Pd 放大特征类型K707 120W 25A 250V NMOSK719 120W 5A 900V NMOSK1120 150W 8A 1000V NMOSK1271 ? ? 1200V* NMOS 塑封 550V开关电源K1518 120W 20A 500V NMOSK2101 NMOS 全塑 30W开关电源2006-12-26 10:49 音频品名功率电流导阻电压封装单价购买备注(W)(A)(Ω)(V)(元)TP15N06 40 15 0.08 50 T0251 1.0BUZ11 75 30 0.05 60 TO220 2.5 SMP60N06 125 60 0.018 60 TO220 3.0V40AT 40 3 1 60 TO220 1.8V40BT 40 3 1.5 120 TO220 2.0V40DT 40 2 3 500 TO220 2.8V75AT 75 5 0.35 60 TO220 2V75BT 75 4.5 0.5 120 TO220 2.3V75CT 75 4 2 300 TO220 3.0V75DT 75 5 1 500 TO220 3.5品名功率电流导阻电压封装单价购买备注(W)(A)(Ω)(V)(元)IRFBC40 125 6.2 12 600 TO220 2.5IRF510 43 5.6 0.41 100 TO220 1.5IRF610 43 3.3 1.2 200 TO220 1.5IRF710 36 2 3. 3 400 TO220 1.5IRF520 60 9.2 0.25 100 TO220 2.0IRF620 40 5 0.5 200 TO220 2.0IRF720 50 3.3 1.6 400 TO220 2.0IRF820 50 2.5 2.9 500 TO220 2.0IRF530 79 14 0.12 100 TO220 2.5IRF630 75 9 0.25 200 TO220 2.5IRF730 74 5.5 0.93 400 TO220 2.5IRF830 74 4.5 1.4 500 TO220 2.5IRF540 150 28 0.06 100 TO220 3.0IRF640 125 18 0.18 200 TO220 3.0IRF740 125 10 0.42 400 TO220 3.0IRF840 125 8 0.85 500 TO220 3.0TO220NP配对品名功率电流导阻电压封装单价购买备注(W)(A)(Ω)(V)(元)IRF520 9520对 60 9.2 0.25 +/-100 T0220 5.0 IRF530 9530对 79 14 0.12 +/-100 TO220 6.0 IRF540 9540对 150 28 0.06 +/-100 TO220 8.0 IRF640 9640对 125 18 0.18 +/-200 TO220 10T03P封装VMOS管品名功率电流导阻电压封装单价购买备注(W)(A)(Ω)(V)(元)IRFP150 180 41 0.055 100 T03P 12IRFP250 180 31 0.085 200 T03P 12IRFP350 180 16 0.3 400 T03P 8.0IRFP450 180 14 0.35 500 T03P 8.0IRFP360 250 23 0.2 400 T03P 12IRFP460 250 20 0.27 500 T03P 12 IRFP264 280 38 0.075 250 TO3P 14 拆机保用IRFP064 300 98 0.018 60 TO3P 14 拆机保用IRFPE20 125 2.5 0.5 1000 TO3P 6SMW40N10 125 40A 0.055 100 TO3P 14SMW60N10 180 60 0.02 100 TO3P 16SMW60N06 180 60 0.018 60 TO3P 14TO3封装 VMOS管品名功率电流导阻电压封装单价购买备注(W)(A)(Ω)(V)(元)IRF150 150 40 0.055 100 T03 10 拆机品保用IRF250 150 30 0.085 200 TO3 14 拆机品保用IRF350 150 15 0.35 400 TO3 8.0 拆机品保用IRF450 150 13 0.4 500 T03 8.0 拆机品保用IRF460 300 21 0.27 500 T03 16 拆机品保用MTM20N45 250 20 0.25 450 TO3 12.0MTM20N50 250 20 0.27 500 T03 8.0IRF130 75 12 0.18 100 T03 8.0IRF132 75 10 0.2 100 TO3 8.0TO3NP配对VMOS管品名功率电流导阻电压封装单价购买备注(W)(A)(Ω)(V)(元)IRF150 150 40 0.055 100 TO3 24IRF9150 150 30 0.085 100 TO3 24IRF130 75 12 0.18 100 TO3 14IRF9130 75 10 0.3 100 TO3 24特种耐高温VMOS管品名功率电流导阻电压封装单价购买备注(W)(A)(Ω)(V)(元)2N6660 6.25 2 60 TO39 352N6800 25 3 400 TO39 40西门子智能感温VMOS管品名功率电流导阻电压封装单价购买备注(W)(A)(Ω)(V)(元)BTS130 75 30 0.04 50 TO220 6BTS131 75 27 0.005 50 TO220 4BTS132 75 TO220 5BTS240 125 58 1.8 50 TO3P 10西门子公司VMOS管品名功率电流导阻电压封装单价购买备注(W)(A)(Ω)(V)(元)BUZ331 125 8 0.8 500 TO3P 5BUZ347 125 40 0.03 50 TO3P 5BUZ349 125 32 0.08 100 TO3P 6BUZ350 125 22 0.1 200 TO3P 8BUZ355 125 8 1.5 800 TO3P 8BUZ357 125 5 2 1000 TO3P 9BUZ380 125 5.5 2 1000 TO3P 10BUZ385 125 10 0.7 500 TO3P 6BUK426 125 40 0.04 50 TO3P 4 菲利普公司BUK627 125 10 0.8 500 TO3P 5 菲利普公司笔记:IRF型场效应管:一般情况下均为高速管。

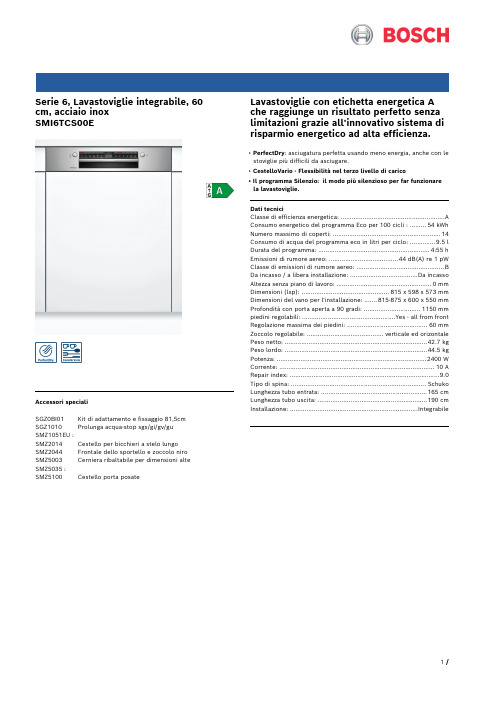

SMI6 60cm 无菌洗衣机说明书

Serie 6, Lavastoviglie integrabile, 60 cm, acciaio inoxSMI6TCS00EAccessori specialiSGZ0BI01 Kit di adattamento e fissaggio 81,5cmSGZ1010 Prolunga acqua-stop sgs/gi/gv/guSMZ1051EU :SMZ2014 Cestello per bicchieri a stelo lungoSMZ2044 Frontale dello sportello e zoccolo niroSMZ5003 Cerniera ribaltabile per dimensioni alte SMZ5035 :SMZ5100 Cestello porta posate Lavastoviglie con etichetta energetica A che raggiunge un risultato perfetto senza limitazioni grazie all'innovativo sistema di risparmio energetico ad alta efficienza.• PerfectDry: asciugatura perfetta usando meno energia, anche con le stoviglie più difficili da asciugare.• CestelloVario - Flessibilità nel terzo livello di carico• Il programma Silenzio: il modo più silenzioso per far funzionarela lavastoviglie.Dati tecniciClasse di efficienza energetica: .........................................................A Consumo energetico del programma Eco per 100 cicli : .........54 kWh Numero massimo di coperti: .. (14)Consumo di acqua del programma eco in litri per ciclo: ..............9.5 l Durata del programma: .............................................................4:55 h Emissioni di rumore aereo: ......................................44 dB(A) re 1 pW Classe di emissioni di rumore aereo: ................................................B Da incasso / a libera installazione: .....................................Da incasso Altezza senza piano di lavoro: ....................................................0 mm Dimensioni (lxp): ................................................815 x 598 x 573 mm Dimensioni del vano per l'installazione: .......815-875 x 600 x 550 mm Profondità con porta aperta a 90 gradi: ...............................1150 mm piedini regolabili: ...................................................Yes - all from front Regolazione massima dei piedini: ............................................60 mm Zoccolo regolabile: ..........................................verticale ed orizontale Peso netto: ..............................................................................42.7 kg Peso lordo: ..............................................................................44.5 kg Potenza: ..................................................................................2400 W Corrente: .....................................................................................10 A Repair index: ..................................................................................9.0 Tipo di spina: ..........................................................................Schuko Lunghezza tubo entrata: ..........................................................165 cm Lunghezza tubo uscita: ............................................................190 cm Installazione: ......................................................................IntegrabileSerie 6, Lavastoviglie integrabile, 60cm, acciaio inoxSMI6TCS00ELavastoviglie con etichetta energetica A che raggiunge un risultato perfetto senza limitazioni grazie all'innovativo sistema di risparmio energetico ad alta efficienza. Prestazioni e consumo- Classe di efficienza energetica¹: A- Energia² / Acqua³: 54 kWh / 9.5 litri- Capacità: 14 coperti- Durata del programma⁴: 4:55 (h:min)- Livello sonoro: 44 dB(A) re 1 pW- Classe di efficienza di rumore: B- Livello di rumore programma Silence: 42(A) re 1 pWProgrammi e opzioni- 6 Programmi: Eco 50 °C, Auto 45-65°, Intensive 70 °C, Express 60°, Silence- Prelavaggio- 4 Programmi supplementari: Home Connect, Asciugatura extra, Mezzo carico, SpeedPerfect+- Home Connect-capibile via WLAN- Programma manutenzione- Silence on demand (tramite App)Tecnologia lavaggio- Asciugatura Zeolite- Sistema di risparmio energetico ad alta efficienza- Scambiatore di calore e EfficientDry- DosageAssist- EcoSilence Drive- Automatismo di pulizia- Sistema di filtri autopulenti con ondulazione a 3 livelli- Contenitore interno: Materiale della vasca interna in acciaio inox Sistema Cestelli- Cestelli Flex- VarioCestello- Cestello superiore regolabile in altezza con Rackmatic (3 livelli)- Ruote con scorrimento facile sul cestello inferiore- Cestello inferiore con blocco (rackStopper) per evitare che fuoriesca dalle guide.- Griglie abbattibili nel cestello superiore (2x)- Griglie abbattibili nel cestello inferiore (2x)- Ripiani per tazze nel cestello superiore (2x)- Carrello inferiore con ripiani per tazze (2x)Indicazione e funzionamento- Iscrizioni di testo in chiaro (inglese)- Indicazione tempo residuo (min.)- Programmatore inizio lavaggio (1-24 h)Sicurezza- AquaStop: una garanzia Bosch per danni causati dall'acqua - durata del dispositivo*- Sicurezza bambini (Tasti)- Tecnologia di protezione del vetro- Aiuto per il riempimento del sale (Imbuto)- Protezione contro il vaporeDimensioni- Dimensioni del prodotto (HxLxP): 81.5 x 59.8 x 57.3 cm¹ In una scala di classi di efficienza energetica da A a G² Consumo di energia in kWh per 100 cicli (nel programma Eco 50°C)³ Consumo di acqua in litiri per ciclo (nel programma Eco 50 °C)⁴ Durata del programma Eco 50 °C* Verificare i termini di garanzia al link/ch/it/condizioni-generali-di-garanziaSerie 6, Lavastoviglie integrabile, 60 cm, acciaio inoxSMI6TCS00E。

SMS12中文资料

u EIAJ SOT23-6L package u Molding compound flammability rating: UL 94V-0 u Marking : Marking Code u Packaging : Tape and Reel per EIA 481

Applications

u Cell phone Handsets and Accessories u Microprocessor Based Equipment u Personal Digital Assistants (PDAs) and Pagers u Desktops PC and Servers u Notebook, Laptop, and Palmtop Computers u Portable Instrumentation u Peripherals u MP3 Players u Cordless Phones

Symbol Ppk IPP VPP TL TJ TSTG

Value 350 24 >25 260 (10 sec.) -55 to +125 -55 to +150

Units Watts

A kV °C °C °C

Electrical Characteristics

SMS05

Parameter

Symbol

PROTECTION PRODUCTS Applications Information

Device Connection for Protection of Four Data Lines The SMSxx is designed to protect up to four unidirectional data lines. The device is connected as follows:

微尔西半导体1微秒微电子公司2014年产品说明书

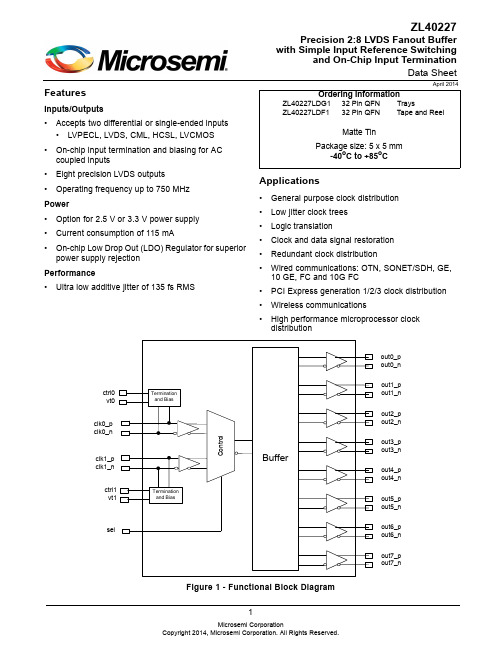

1FeaturesInputs/Outputs •Accepts two differential or single-ended inputs •LVPECL, LVDS, CML, HCSL, LVCMOS •On-chip input termination and biasing for AC coupled inputs•Eight precision LVDS outputs •Operating frequency up to 750 MHzPower •Option for 2.5 V or 3.3 V power supply •Current consumption of 115 mA•On-chip Low Drop Out (LDO) Regulator for superior power supply rejectionPerformance •Ultra low additive jitter of 135 fs RMSApplications•General purpose clock distribution •Low jitter clock trees •Logic translation•Clock and data signal restoration •Redundant clock distribution•Wired communications: OTN, SONET/SDH, GE, 10 GE, FC and 10G FC•PCI Express generation 1/2/3 clock distribution •Wireless communications•High performance microprocessor clock distributionApril 2014Figure 1 - Functional Block DiagramZL40227Precision 2:8 LVDS Fanout Buffer with Simple Input Reference Switchingand On-Chip Input TerminationData SheetOrdering InformationZL40227LDG1 32 Pin QFN TraysZL40227LDF132 Pin QFNTape and ReelMatte TinPackage size: 5 x 5 mm-40o C to +85o CTable of ContentsFeatures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Change Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41.0 Package Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52.0 Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73.1 Clock Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73.1.1 Clock Input Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73.1.2 Clock Input Terminations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73.2 Clock Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123.3 Device Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.4 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.1 Sensitivity to power supply noise. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.2 Power supply filtering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.3 PCB layout considerations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .164.0 AC and DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175.0 Performance Characterization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .196.0 Typical Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .207.0 Package Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .218.0 Mechanical Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22List of FiguresFigure 1 - Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - Pin Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Figure 3 - Simplified Diagram of Input Stage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 4 - Clock Input - LVPECL - DC Coupled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 5 - Clock Input - LVPECL - AC Coupled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 6 - Clock Input - LVDS - DC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 7 - Clock Input - LVDS - AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 8 - Clock Input - CML- AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 9 - Clock Input - HCSL- AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 10 - Clock Input - AC-coupled Single-Ended . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 11 - Clock Input - DC-coupled 3.3V CMOS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 12 - Simplified LVDS Output Driver. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 13 - LVDS DC Coupled Termination (Internal Receiver Termination). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 14 - LVDS DC Coupled Termination (External Receiver Termination) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 15 - LVDS AC Coupled Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 16 - LVDS AC Output Termination for CML Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 17 - Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 18 - Decoupling Connections for Power Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 19 - Differential Voltage Parameter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 20 - Input To Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18Change SummaryBelow are the changes from the February 2013 issue to the April 2014 issue:Page Item Change1Applications Added PCI Express clock distribution.6Pin Description Added exposed pad to Pin Description.8Figure 4 and Figure 5Removed 22 Ohm series resistors from Figure 4 and 5. Theseresistors are not required; however there is no impact toperformance if the resistors are included.18Figure 19Clarification of V ID and V OD.Below are the changes from the November 2012 issue to the February 2013 issue:Page Item Change8Figure 4Changed text to indicate the circuit is not recommended forVDD_driver=2.5V.12Figure 12Changed gate values to +/+ on the left and -/- on the right.1.0 Package DescriptionThe device is packaged in a 32 pin QFNFigure 2 - Pin Connections2.0 Pin DescriptionPin DescriptionPin # Name Description1,3, 6, 8clk0_p, clk0_n,clk1_p, clk1_nDifferential Input (Analog Input). Differential input signals.30, 29, 28, 27, 26, 25, 24, 23, 18, 17, 16, 15, 14, 13, 12, 11 out0_p, out0_nout1_p, out1_nout2_p, out2_nout3_p, out3_nout4_p, out4_nout5_p, out5_nout6_p, out6_nout7_p, out7_nDifferential Output (Analog Output). Differential outputs.9, 19,22, 32vdd Positive Supply Voltage. 2.5V DC or 3.3 V DC nominal.20, 21gnd Ground. 0 V.2, 7vt0, vt1On-Chip Input Termination Node (Analog).Center tap between internal 50 Ohmtermination resistors.For a DC coupled LVPECL input connect this pin through a resistor to ground; 50 Ohmsfor 3.3V LVPECL or 20 Ohms for 2.5V LVPECL.For a DC coupled LVDS input or for an AC coupled differential input, leave this pinunconnected.4, 5ctrl0, ctrl1Digital Control for On-Chip Input Termination (Input). Selects differential input mode;0: DC coupled LVPECL or LVDS modes1: AC coupled differential modesThese pins are internally pulled down to GND.10NC No Connection. Leave unconnected.31sel Input Select (Input). Selects the reference input that is buffered;0: clk01: clk1This pin is internally pulled down to GND.Exposed Pad Device GND.3.0 Functional DescriptionThe ZL40227 is an LVDS clock fanout buffer with eight output clock drivers capable of operating at frequencies up to 750 MHz.The ZL40227 provides an internal input termination network for DC and AC coupled inputs; optional input biasing for AC coupled inputs is also provided. The ZL40227 can accept DC coupled LVPECL or LVDS and AC coupled LVPECL and LVDS input signals, AC coupled CML or HCSL input signals, and single ended signals. A pin compatible device with external termination is also available.The ZL40227 is designed to fan out low-jitter reference clocks for wired or optical communications applications while adding minimal jitter to the clock signal. An internal linear power supply regulator and bulk capacitors minimize additive jitter due to power supply noise. The device operates from 2.5V+/-5% or 3.3V+/-5% supply. Its operation is guaranteed over the industrial temperature range -40°C to +85°C.The device block diagram is shown in Figure 1; its operation is described in the following sections.3.1 Clock InputsThe device has a differential input equipped with two on-chip 50 Ohm termination resistors arranged in series with a center tap. The input can accept many differential and single-ended signals with AC or DC coupling as appropriate. A control pin is available to enable internal biasing for AC coupled inputs. A block diagram of the input stage is in Figure 3.Receiverclk_n 50clk_pVt 50BiasctrlFigure 3 - Simplified Diagram of Input Stage3.1.1 Clock Input SelectionThe select line chooses which input clock is routed to the outputs.Table 1 - Input SelectionSel Active Input0 clk01clk13.1.2 Clock Input TerminationsThis following figures give the components values and configuration for the various circuits compatible with the input stage and the use of the Vt and ctrl pins in each case.In the following diagrams where the ctrl pin is "1" and the Vt pin is not connected, the Vt pin can be instead connected to V DD with a capacitor. A capacitor can also help in Figure 4 between Vt and V DD. This capacitor will minimize the noise at the point between the two internal termination resistors and improve the overall performance of the device.Figure 4 - Clock Input - LVPECL - DC CoupledFigure 5 - Clock Input - LVPECL - AC CoupledFigure 6 - Clock Input - LVDS - DC CoupledFigure 7 - Clock Input - LVDS - AC CoupledFigure 8 - Clock Input - CML- AC CoupledFigure 9 - Clock Input - HCSL- AC CoupledFigure 10 - Clock Input - AC-coupled Single-EndedFigure 11 - Clock Input - DC-coupled 3.3V CMOS3.2 Clock OutputsLVDS has lower signal swing than LVPECL which results in a low power consumption. A simplified diagram for the LVDS output stage is shown in Figure 12.Figure 12 - Simplified LVDS Output DriverThe methods to terminate the ZL40227 drivers are shown in the following figures.Figure 15 - LVDS AC Coupled TerminationFigure 16 - LVDS AC Output Termination for CML Inputs3.3 Device Additive JitterThe ZL40227 clock fanout buffer is not intended to filter clock jitter. The jitter performance of this type of device is characterized by its additive jitter. Additive jitter is the jitter the device would add to a hypothetical jitter-free clock as it passes through the device. The additive jitter of the ZL40227 is random and as such it is not correlated to the jitter of the input clock signal.The square of the resultant random RMS jitter at the output of the ZL40227 is equal to the sum of the squares of the various random RMS jitter sources including: input clock jitter; additive jitter of the buffer; and additive jitter due to power supply noise. There may be additional deterministic jitter sources, but they are not shown in Figure 17.Figure 17 - Additive Jitter3.4 Power SupplyThis device operates with either a 2.5V supply or 3.3V supply.3.4.1 Sensitivity to power supply noisePower supply noise from sources such as switching power supplies and high-power digital components such as FPGAs can induce additive jitter on clock buffer outputs. The ZL40227 is equipped with a low drop out (LDO) linear power regulator and on-chip bulk capacitors to minimize additive jitter due to power supply noise. The on-chip regulation, recommended power supply filtering, and good PCB layout all work together to minimize the additive jitter from power supply noise.3.4.2 Power supply filteringFor optimal jitter performance, the ZL40227 should be isolated from the power planes connected to its power supply pins as shown in Figure 18.•10 µF capacitors should be size 0603 or size 0805 X5R or X7R ceramic, 6.3 V minimum rating•0.1 µF capacitors should be size 0402 X5R ceramic, 6.3 V minimum rating•Capacitors should be placed next to the connected device power pinsFigure 18 - Decoupling Connections for Power Pins3.4.3 PCB layout considerationsThe power supply filtering shown in Figure 18 can be implemented either as a plane island, or as a routed power topology with the same performance.4.0 AC and DC Electrical CharacteristicsAbsolute Maximum Ratings*Parameter Sym.Min.Max.Units 1Supply voltage V DD_R-0.5 4.6V 2Voltage on any digital pin V PIN-0.5V DD V 4LVPECL output current I out30mA 5Soldering temperature T260 °C 6Storage temperature T ST-55125 °C 7Junction temperature T j125 °C 8Voltage on input pin V input V DD V 9Input capacitance each pin C p500fF * Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.* Voltages are with respect to ground (GND) unless otherwise statedRecommended Operating Conditions*Characteristics Sym.Min.Typ.Max.Units1Supply voltage 2.5 V mode V DD25 2.375 2.5 2.625V2Supply voltage 3.3 V mode V DD33 3.135 3.3 3.465V3Operating temperature T A-402585°C* Voltages are with respect to ground (GND) unless otherwise statedDC Electrical Characteristics - Current ConsumptionCharacteristics Sym.Min.Typ.Max.Units Notes 1Supply current LVDS drivers - loadedI dd_load115mA(all outputs are active)DC Electrical Characteristics - Inputs and Outputs - for 2.5/3.3 V SupplyCharacteristics Sym.Min.Typ.Max.Units Notes1CMOS control logic high-level inputV CIH0.7*V DD V voltageV CIL0.3*V DD V2CMOS control logic low-level inputvoltage3CMOS control logic Input leakageI IL1µA V I = V DD or 0 Vcurrent4Differential input common modeV ICM 1.1 1.6V for 2.5 voltageV ICM 1.1 2.0V for 3.35Differential input common modevoltage* The VOD parameter was measured from 125 MHz to 750 MHz.Figure 19 - Differential Voltage Parameter* Supply voltage and operating temperature are as per Recommended Operating ConditionsInputt Pt PWLt pdt PWHOutputFigure 20 - Input To Output Timing6Differential input voltage difference V ID 0.251V 7Differential input resistance V IR 80100120ohm 8LVDS output differential voltage*V OD 0.250.300.40V 9LVDS output common mode voltageV CM1.11.25 1.375VAC Electrical Characteristics* - Inputs and Outputs (see Figure 20) - for 2.5/3.3 V Supply.CharacteristicsSym.Min.Typ.Max.Units Notes1Maximum Operating Frequency 1/t p 750MHz 2Input to output clock propagation delay t pd 012ns 3Output to output skew t out2out 80150ps 4Part to part output skewt part2part 120300ps 5Output clock Duty Cycle degradation t PWH / t PWL-55Percent 6LVDS Output slew rate r sl 0.55V/ns 7Reference transition timet switch23usDC Electrical Characteristics - Inputs and Outputs - for 2.5/3.3 V SupplyCharacteristicsSym.Min.Typ.Max.Units NotesAdditive Jitter at 2.5 V*Output Frequency (MHz)Jitter MeasurementFilterTypical RMS (fs)Notes112512 kHz - 20 MHz 1842212.512 kHz - 20 MHz 1743311.0412 kHz - 20 MHz 157442512 kHz - 20 MHz 152550012 kHz - 20 MHz 1396622.0812 kHz - 20 MHz 138775012 kHz - 20 MHz135Additive Jitter at 3.3 V*Output Frequency (MHz)Jitter MeasurementFilterTypical RMS (fs)Notes112512 kHz - 20 MHz 1872212.512 kHz - 20 MHz 1763311.0412 kHz - 20 MHz 156442512 kHz - 20 MHz 153550012 kHz - 20 MHz 1406622.0812 kHz - 20 MHz 139775012 kHz - 20 MHz1375.0 Performance Characterization*The values in this table were taken with an approximate slew rate of 0.8 V/ns*The values in this table were taken with an approximate slew rate of 0.8 V/nsAdditive Jitter from a Power Supply Tone*Carrier frequencyParameterTypicalUnitsNotes125MHz 25 mV at 100 kHz 33fs RMS 750MHz25 mV at 100 kHz33fs RMS* The values in this table are the additive periodic jitter caused by an interfering tone typically caused by a switching power supply. For this test, measurements were taken over the full temperature and voltage range for V DD = 3.3 V. The magnitude of the interfering tone is measured at the DUT.6.0 Typical BehaviorTypical Waveform at 155.52 MHzV OD vs FrequencyPower Supply Tone Frequency versus PSRRPower Supply Tone Magnitude versus PSRRPropagation Delay versus TemperatureNote:This is for a single device. For more details, see thecharacterization section.7.0 Package CharacteristicsThermal DataParameter Symbol Test Condition Value UnitJunction to Ambient Thermal Resistance ΘJA Still Air1 m/s2 m/s 37.433.131.5o C/WJunction to Case Thermal Resistance ΘJC24.4o C/W Junction to Board Thermal Resistance ΘJB19.5o C/W Maximum Junction Temperature*T jmax125o C Maximum Ambient Temperature T A85o C© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense and security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world’s standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 3,400 employees globally. Learn more at .Microsemi Corporate Headquarters One One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (800) 713-4113Outside the USA: +1 (949) 380-6100Sales: +1 (949) 380-6136Fax: +1 (949) 215-4996E-mail: ***************************Information relating to products and services furnished herein by Microsemi Corporation or its subsidiaries (collectively “Microsemi”) is believed to be reliable. However, Microsemi assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Microsemi or licensed from third parties by Microsemi, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Microsemi, or non-Microsemi furnished goods or services may infringe patents or other intellectual property rights owned by Microsemi.This publication is issued to provide information only and (unless agreed by Microsemi in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Microsemi without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user’s responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical and other products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Microsemi’s conditions of sale which are available on request.For more information about all Microsemi productsvisit our website at TECHNICAL DOCUMENTATION – NOT FOR RESALE。

MAV-11SM中文资料

ABSOLUTE MAXIMUM RATING7

DC POWER at Pin 3

THERMAL RESISTANCE 6

θ jc °C/W 115 105 115 100 120 120 140 110 100 110 95 85 125

CAPD DATA

(see RF/IF Designer Handbook)

2000 — 11.0 10.5 — 11.0 11.0 — — 10.0** 10.0** — 6.5** —

note 5 note 1 Typ. Output Input (1 dB (no Comp.) damage) MIN. 13.0 8.5 8.0 7.0 9.0 8.5 19.0 12.5 7.5 7.5 7.0 5.5 9.0 +1.5 +4.5 +10.0 +12.5 +2.0 +5.5 +12.5 +1.5 +4.5 +10.0 +11.5 +18.0 +17.5 +13 +13 +13 +13 +13 +13 +13 +13 +13 +13 +13 +20 +13

cb cb cb cb

3.0 +14.5 5.0 +19.0 3.3 +27.0 5.5 +14.0 6.5 +17.0 6.0 +23.0 7.0 +24.5 6.5 +29.0 3.6 +30.0

WW107 cb WW107 cb WW107 cb RRR137 cb ቤተ መጻሕፍቲ ባይዱRR137 cb RRR137 cb RRR137 cb RRR137 cb RRR137 cb

MOSFET数据手册说明书

Characteristic / Test ConditionsDrain-Source Breakdown Voltage (V GS = 0V, I D = 250µA)On State Drain Current 2 (V DS > I D(on) x R DS(on) Max, V GS = 10V)Drain-Source On-State Resistance 2 (V GS = 10V, 0.5 I D[Cont.])Zero Gate Voltage Drain Current (V DS = V DSS , V GS= 0V)Zero Gate Voltage Drain Current (VDS = 0.8 V DSS , V GS = 0V, T C = 125°C)Gate-Source Leakage Current (V GS = ±30V, V DS = 0V)Gate Threshold Voltage (V DS = V GS , I D = 1.0mA)050-5519 R e v CMAXIMUM RATINGSAll Ratings: T C = 25°C unless otherwise specified.Symbol V DSS I D I DM V GS V GSM P D T J ,T STGT L IAR E AR E ASParameterDrain-Source VoltageContinuous Drain Current @ T C = 25°C Pulsed Drain Current 1Gate-Source Voltage Continuous Gate-Source Voltage Transient Total Power Dissipation @ T C = 25°C Linear Derating FactorOperating and Storage Junction Temperature Range Lead Temperature: 0.063" from Case for 10 Sec.Avalanche Current 1 (Repetitive and Non-Repetitive)Repetitive Avalanche Energy 1Single Pulse Avalanche Energy 4UNIT Volts AmpsVolts Watts W/°C°C Amps mJSTATIC ELECTRICAL CHARACTERISTICSSymbol BV DSS I D(on)R DS(on)I DSS I GSS V GS(th)UNIT Volts AmpsOhms µA nA VoltsMIN TYP MAX 200560.04525250±10024APT20M45SVR20056224±30±403002.4-55 to 15030056301300APT20M45SVR200V56A 0.045ΩCAUTION: These Devices are Sensitive to Electrostatic Discharge. Proper Handling Procedures Should Be Followed.USA405 S.W. Columbia StreetBend, Oregon 97702-1035Phone: (541) 382-8028FAX: (541) 388-0364EUROPEAvenue J.F. Kennedy Bât B4 Parc Cadéra NordF-33700 Merignac - FrancePhone: (33)557921515FAX: (33)556479761APT Website - Power MOS V ® is a new generation of high voltage N-Channel enhancement mode power MOSFETs. This new technology minimizes the JFET effect,increases packing density and reduces the on-resistance. Power MOS V ®also achieves faster switching speeds through optimized gate layout.•Faster Switching •100% Avalanche Tested •Lower Leakage•Surface Mount D 3PAK PackagePOWER MOS V ®Symbol I S I SM V SD t rr Q rrDYNAMIC CHARACTERISTICSSymbol C iss C oss C rss Q g Q gs Q gd t d(on)t r t d(off)t fTest ConditionsV GS = 0V V DS = 25V f = 1 MHz V GS = 10V V DD = 0.5 V DSS I D = I D[Cont.] @ 25°CV GS = 15V V DD = 0.5 V DSS I D = I D[Cont.] @ 25°CR G = 1.6ΩMINTYPMAX40504860980137530045013019530455580122414284370714UNITpFnC ns APT20M45SVRCharacteristic Input Capacitance Output CapacitanceReverse Transfer Capacitance Total Gate Charge 3Gate-Source Charge Gate-Drain ("Miller") Charge Turn-on Delay Time Rise TimeTurn-off Delay Time Fall Time050-5519 R e v CCharacteristic / Test Conditions Continuous Source Current (Body Diode)Pulsed Source Current 1 (Body Diode)Diode Forward Voltage 2 (V GS = 0V, I S = -I D[Cont.])Reverse Recovery Time (I S = -I D[Cont.], dl S /dt = 100A/µs)Reverse Recovery Charge (I S = -I D[Cont.], dl S /dt = 100A/µs)SOURCE-DRAIN DIODE RATINGS AND CHARACTERISTICSUNIT Amps Volts ns µCMINTYPMAX562241.32803.51Repetitive Rating: Pulse width limited by maximum junction3See MIL-STD-750 Method 3471temperature.4Starting T j = +25°C, L = 0.83mH, R G = 25Ω, Peak I L= 56A2Pulse Test: Pulse width < 380 µS, Duty Cycle < 2%APT Reserves the right to change, without notice, the specifications and information contained herein.THERMAL CHARACTERISTICSSymbol R θJC R θJAMINTYPMAX0.4240UNIT °C/WCharacteristic Junction to Case Junction to AmbientZ θJ C , T H E R M A L I M P E D A N C E (°C /W )10-510-410-310-210-1 1.010RECTANGULAR PULSE DURATION (SECONDS)FIGURE 1, MAXIMUM EFFECTIVE TRANSIENT THERMAL IMPEDANCE, JUNCTION-TO-CASE vs PULSE DURATION0.50.10.050.010.0050.001V DS , DRAIN-TO-SOURCE VOLTAGE (VOLTS)V DS , DRAIN-TO-SOURCE VOLTAGE (VOLTS)FIGURE 2, TYPICAL OUTPUT CHARACTERISTICS FIGURE 3, TYPICAL OUTPUT CHARACTERISTICSV GS , GATE-TO-SOURCE VOLTAGE (VOLTS)I D , DRAIN CURRENT (AMPERES)FIGURE 4, TYPICAL TRANSFER CHARACTERISTICS FIGURE 5, R DS (ON) vs DRAIN CURRENTT C , CASE TEMPERATURE (°C)T J , JUNCTION TEMPERATURE (°C)FIGURE 6, MAXIMUM DRAIN CURRENT vs CASE TEMPERATURE FIGURE 7, BREAKDOWN VOLTAGE vs TEMPERATURE T J , JUNCTION TEMPERATURE (°C)T C , CASE TEMPERATURE (°C)FIGURE 8, ON-RESISTANCE vs. TEMPERATURE FIGURE 9, THRESHOLD VOLTAGE vs TEMPERATURER D S (O N ), D R A I N -T O -S O U R C E O N R E S I S T A N C E I D , D R A I N C U R R E N T (A M P E R E S )I D , D R A I N C U R R E N T (A M P E R E S )I D , D R A I N C U R R E N T (A M P E R E S )(N O R M A L I Z E D )V G S (T H ), T H R E S H O L D V O L T A G E B V D S S , D R A I N -T O -S O U R C E B R E A K D O W N R D S (O N ), D R A I N -T O -S O U R C E O N R E S I S T A N C EI D , D R A I N C U R R E N T (A M P E R E S )(N O R M A L I Z E D )V O L T A G E (N O R M A L I Z E D)255075100125150-50-250255075100125150-50-250255075100125150APT20M45SVR100806040201.61.41.21.00.81.151.101.051.000.950.901.21.11.00.90.80.70.61008060402010080604020060504030201002.52.01.51.00.50.0050-5519 R e v CV DS , DRAIN-TO-SOURCE VOLTAGE (VOLTS)V DS , DRAIN-TO-SOURCE VOLTAGE (VOLTS)FIGURE 10, MAXIMUM SAFE OPERATING AREAFIGURE 11, TYPICAL CAPACITANCE vs DRAIN-TO-SOURCE VOLTAGE Q g , TOTAL GATE CHARGE (nC)V SD , SOURCE-TO-DRAIN VOLTAGE (VOLTS)FIGURE 12, GATE CHARGES vs GATE-TO-SOURCE VOLTAGEFIGURE 13, TYPICAL SOURCE-DRAIN DIODE FORWARD VOLTAGEV G S , G A T E -T O -S O U R C E V O L T A G E (V O L T S )I D , D R A I N C U R R E N T (A M P E R E S )I D R , R E V E R S E D R A I N C U R R E N T (A M P E R E S )C , C A P A C I T A N C E (p F )APT20M45SVR3001005010512016128410,0005,0001,000500100300100501051050-5519 R e v CAPT's devices are covered by one or more of the following U.S.patents:4,895,8105,045,9035,089,4345,182,2345,019,5225,262,3365,256,5834,748,1035,283,2025,231,4745,434,0955,528,058Dimensions in Millimeters (Inches)and Leads are PlatedSource D 3PAK Package Outline。

中日金属材料对照表

42CrMo,代用42SiMnMo 20CrMnTi,代用20CrMo 18Cr2Ni4W

34CrNi3MoA.代用30CrMn2MoB

代50SiMnMoV, 代用18CrMn2MoB

18Cr2Ni4W

34FCrNiMoA代用37SiMn2MoB

耐磨钢SCMnH SCMnH1 SCMnH2 高温结构钢SCPH SCPH11 Cr-HSNC-H.SNCM-H SCM418H SCM420H(SCM22H) SCM435H(SCM3H) SCM440H(SCM4H) SCM445H(SCM5H) SCM822H(SCM24H) SNC415H(SNC21H) SNC531H SNC631H(SNC2H) SNC815H(SNC22H) SNC220H(SNC21H) SNC420H(SNC23H)

中日金属材料对照表

日本牌号 普通碳素钢琴 SS,SM-A 中国牌号 A2,AY2,AJ2,A2F,AY2F,AJ2F SS34 B2,BY2,B2b2,B2F,B2F SM41A A3b,C3F SM41B AY3,C3 A3,A3F,AY3F,B3,BY3,B3F,A4 SS41 B3b,BY3F,A4F, SS50 A5,AY5,AJ5,A6 优质碳素结构钢琴 S-C,S-CK,SUP S09CK 08F,10 S10C 08,10,10F S12C S15C 15,15F S15CK 15 S17C S20C 20,20F S20CK 20 S22C 20,20F S25C S28C 25 S30C S33C 30 S35C S38C 35 S40C S43C 40 S45C S48C 45 S50C S53C 50 S55C 56 S58C 55.6 SUP3 85 铬钼合金钢材 STC,STB,STT,SCM STC STT STB 15CrMo,20CrMo SCM418 20CrMo SCM420(SCM22) 20CrMo,30CrNo,20CrMnMo SCM421(SCM23) 20CrMnMO,20C代用50CrVA

步进电机规格书(英文)

BLK

1

–

+

+

–

2

–

+

–

+

3

+

–

–

+

4

+

–

+

–

A BRW

BI POLAR

B

B

ORG

YEL

CW Rotation Facing Mounting End

Coil Connectors attached to the motor are force inserted and cannot be removed.

Torque (10-4 N.m)

MS70 P/O

MS70 P/I 10

8

6

4

2

0

0

500

1000

1500 2000

2500

3000

Frequency (PPS)

NMB Technologies Corporation 41

pm PM15S-020

Note: See page 38 for options on pin exit angle (θ).

Cutaway used to show internal components

7

3

3. Three different types of permanent

magnets are available.

Ferrite Plastic Magnet

5

Ferrite Sintered Magnet

Nd-Fe-B Bonded Magnet

Model Specifications

Reference Characteristics

德州仪器(TI)LM3S1960系列 规格书,Datasheet 资料

S T E L L A R I S E R R A T AStellaris ®LM3S1960RevA2ErrataThis document contains known errata at the time of publication for the Stellaris LM3S1960microcontroller.The table below summarizes the errata and lists the affected revisions.See the data sheet for more details.See also the ARM®Cortex™-M3errata,ARM publication number PR326-PRDC-009450v2.0.Table 1.Revision HistoryDescription Revision Date ■Added issue “Standard R-C network cannot be used on RST to extend POR timing”on page 5.■Clarified issue “General-purpose timer 16-bit Edge Count or Edge Time mode does not load reload value”on page 8to include Edge-Time mode.3.0August 2011■Added issue “Hibernation module does not operate correctly”on page 6,replacing previous Hibernation module errata items.■Minor edits and clarifications.2.10September 2010■Added issue “The RTRIS bit in the UARTRIS register is only set when the interrupt is enabled”on page 9.2.9July 2010■Added issue “External reset does not reset the XTAL to PLL Translation (PLLCFG)register”on page 5.2.8June 2010■Removed issue "Hibernation Module 4.194304-MHz oscillator supports a limited range of crystal load capacitance values"as it does not apply to this part.■Minor edits and clarifications.2.7May 2010■Removed issue "Writes to Hibernation module registers sometimes fail"as it does not apply to this part.■Added issue "Hibernation Module 4.194304-MHz oscillator supports a limited range of crystal load capacitance values."■Minor edits and clarifications.2.6April 2010■Removed issue "Setting Bit 7in I2C Master Timer Period (I2CMTPR)register may have unexpected results".The data sheet description has changed such that this is no longer necessary.■Minor edits and clarifications.2.5April 2010■Added issue “The General-Purpose Timer match register does not function correctly in 32-bit mode”on page 8.■Added issue "Setting Bit 7in I2C Master Timer Period (I2CMTPR)register may have unexpected results".2.4February 2010■"Hard Fault possible when waking from Sleep or Deep-Sleep modes and Cortex-M3Debug Access Port (DAP)is enabled"has been removed and the content added to the LM3S1960data sheet.2.3Jan 2010Started tracking revision history.2.2Dec 2009Stellaris LM3S1960A2Errata Table2.List of ErrataStellaris LM3S1960A2Errata1JTAG and Serial Wire Debug1.1JTAG pins do not have internal pull-ups enabled at power-on resetDescription:Following a power-on reset,the JTAG pins TRST,TCK,TMS,TDI,and TDO(PB7and PC[3:0])donot have internal pull-ups enabled.Consequently,if these pins are not driven from the board,twothings may happen:■The JTAG port may be held in reset and communication with a four-pin JTAG-based debugger may be intermittent or impossible.■The receivers may draw excess current.Workaround:There are a number of workarounds for this problem,varying in complexity and impact:1.Add external pull-up resistors to all of the affected pins.This workaround solves both issues ofJTAG connectivity and current consumption.2.Add an external pull-up resistor to TRST.Firmware should enable the internal pull-ups on theaffected pins by setting the appropriate PUE bits of the appropriate GPIO Pull-Up Select(GPIOPUR)registers as early in the reset handler as possible.This workaround addresses theissue of JTAG connectivity,but does not address the current consumption other than to limitthe affected period(from power-on reset to code execution).3.Pull-ups on the JTAG pins are unnecessary for code loaded via the SWD interface or via theserial boot loader.Loaded firmware should enable the internal pull-ups on the affected pins bysetting the appropriate PUE bits of the appropriate GPIOPUR registers as early in the resethandler as possible.This method does not address the current consumption other than to limitthe affected period(from power-on reset to code execution).Silicon Revision Affected:A21.2JTAG INTEST instruction does not workDescription:The JTAG INTEST(Boundary Scan)instruction does not properly capture data.Workaround:None.Silicon Revision Affected:A2Stellaris LM3S1960A2Errata2System Control2.1Clock source incorrect when waking up from Deep-Sleep mode insome configurationsDescription:In some clocking configurations,the core prematurely starts executing code before the main oscillator(MOSC)has stabilized after waking up from Deep-Sleep mode.This situation can cause undesirablebehavior for operations that are frequency dependent,such as UART communication.This issue occurs if the system is configured to run off the main oscillator,with the PLL bypassedand the DSOSCSRC field of the Deep-Sleep Clock Configuration(DSLPCLKCFG)register set touse the internal12-MHz oscillator,30-KHz internal oscillator,or32-KHz external oscillator.Whenthe system is triggered to wake up,the core should wait for the main oscillator to stabilize beforestarting to execute code.Instead,the core starts executing code while being clocked from thedeep-sleep clock source set in the DSLPCLKCFG register.When the main oscillator stabilizes,theclock to the core is properly switched to run from the main oscillator.Workaround:Run the system off of the main oscillator(MOSC)with the PLL enabled.In this mode,the clocksare switched at the proper time.If the main oscillator must be used to clock the system without the PLL,a simple wait loop at thebeginning of the interrupt handler for the wake-up event should be used to stall thefrequency-dependent operation until the main oscillator has stabilized.Silicon Revision Affected:A22.2PLL may not function properly at default LDO settingDescription:In designs that enable and use the PLL module,unstable device behavior may occur with the LDOset at its default of2.5volts or below(minimum of2.25volts).Designs that do not use the PLLmodule are not affected.Workaround:Prior to enabling the PLL module,it is recommended that the default LDO voltage setting of2.5Vbe adjusted to2.75V using the LDO Power Control(LDOPCTL)register.Silicon Revision Affected:A22.3I/O buffer5-V tolerance issueDescription:GPIO buffers are not5-V tolerant when used in open-drain mode.Pulling up the open-drain pinabove4V results in high current draw.Stellaris LM3S1960A2ErrataWorkaround:When configuring a pin as open drain,limit any pull-up resistor connections to the3.3-V power rail.Silicon Revision Affected:A22.4PLL Runs Fast When Using a3.6864-MHz CrystalDescription:If the PLL is enabled,and a3.6864-MHz crystal is used,the PLL runs4%fast.Workaround:Use a different crystal whose frequency is one of the other allowed crystal frequencies(see thevalues shown for the XTAL bit in the RCC register).Silicon Revision Affected:A22.5External reset does not reset the XTAL to PLL Translation(PLLCFG)registerDescription:Performing an external reset(anything but power-on reset)reconfigures the XTAL field in theRun-Mode Clock Configuration(RCC)register to the6MHz setting,but does not reset the XTALto PLL Translation(PLLCFG)register to the6MHz setting.Consider the following sequence:1.Performing a power-on reset results in XTAL=6MHz and PLLCFG=6MHz2.Write an8MHz value to the XTAL field results in XTAL=8MHz and PLLCFG=8MHz3.RST asserted results in XTAL=6MHz and PLLCFG=8MHzIn the last step,PLLCFG was not reset to its6MHz setting.If this step is followed by enabling thePLL to run from an attached6-MHz crystal,the PLL then operates at300MHz instead of400MHz.Subsequently configuring the XTAL field with the8MHz setting does not change the setting ofPLLCFG.Workaround:Set XTAL in PLLCFG to an incorrect value,and then to the desired value.The second changeupdates the register correctly.Do not enable the PLL until after the second change.Silicon Revision Affected:A22.6Standard R-C network cannot be used on RST to extend POR timingDescription:The standard R-C network on RST does not work to extend POR timing beyond the10ms on-chipPOR.Instead of following the standard capacitor charging curve,RST jumps straight to3V at powerStellaris LM3S1960A2Errataon.The capacitor is fully charged by current out of the RST pin and does not extend or filter thepower-on condition.As a result,the reset input is not extended beyond the POR.Workaround:Add a diode to block the output current from RST.This helps to extend the RST pulse,but alsomeans that the R-C is not as effective as a noise filter.Silicon Revision Affected:A23Hibernation Module3.1Hibernation module does not operate correctlyDescription:The Hibernation module on this microcontroller does not operate correctly.Workaround:This errata item does not apply to many Stellaris devices,including the LM3S1166,LM3S1636,LM3S1969,and LM3S2919.Refer to the Stellaris Product Selector Guide(/stellaris_search)and Errata documents to find an alternative microcontroller that meetsthe design requirements for your application.Silicon Revision Affected:A24Flash Controller4.1MERASE bit of the FMC register does not erase the entire FlasharrayDescription:The MERASE bit of the Flash Memory Control(FMC)register does not erase the entire Flash array.If the contents of the Flash Memory Address(FMA)register contain a value less than0x20000,only the first128KB of the Flash array are erased.If bit17(value of0x20000)is set,then only theupper address range of Flash(greater than128KB)is erased.Workaround:If the entire array must be erased,the following sequence is recommended:1.Write a value of0x00000000to the FMA register.2.Write a value of0xA4420004to the FMC register,and poll bit2until it is cleared.3.Write a value of0x00020000to the FMA register.4.Write a value of0xA4420004to the FMC register,and poll bit2until it is cleared.The entire array can also be erased by individually erasing all of the pages in the array.Stellaris LM3S1960A2ErrataSilicon Revision Affected:A25GPIO5.1GPIO input pin latches in the Low state if pad type is open drainDescription:GPIO pins function normally if configured as inputs and the open-drain configuration is disabled.Ifopen drain is enabled while the pin is configured as an input using the GPIO Alternate FunctionSelect(GPIOAFSEL),GPIO Open Drain Select(GPIOODR),and GPIO Direction(GPIODIR)registers,then the pin latches Low and excessive current(into pin)results if an attempt is made todrive the pin High.The open-drain device is not controllable.A GPIO pin is not normally configured as open drain and as an input at the same time.A user maywant to do this when driving a signal out of a GPIO open-drain pad while configuring the pad as aninput to read data on the same pin being driven by an external device.Bit-banging a bidirectional,open-drain bus(for example,I2C)is an example.Workaround:If a user wants to read the state of a GPIO pin on a bidirectional bus that is configured as anopen-drain output,the user must first disable the open-drain configuration and then change thedirection of the pin to an input.This precaution ensures that the pin is never configured as an inputand open drain at the same time.A second workaround is to use two GPIO pins connected to the same bus signal.The first GPIOpin is configured as an open-drain output,and the second is configured as a standard input.Thisway the open-drain output can control the state of the signal and the input pin allows the user toread the state of the signal without causing the latch-up condition.Silicon Revision Affected:A25.2GPIO pins may glitch during power supply ramp upDescription:Upon completing a POR(power on reset)sequence,the GPIO pins default to a tri-stated inputcondition.However,during the initial ramp up of the external V DD supply from0.0V to3.3V,theGPIO pins are momentarily configured as output drivers during the time the internal LDO circuit isalso ramping up.As a result,a signal glitch may occur on GPIO pins before both the external V DDsupply and internal LDO voltages reach their normal operating conditions.This situation can occurwhen the V DD and LDO voltages ramp up at significantly different rates.The LDO voltage ramp-uptime is affected by the load capacitance on the LDO pin,therefore,it is important to keep this loadat a nominal1µF value as recommended in the data sheet.Adding significant more capacitanceloading beyond the specification causes the time delay between the two supply ramp-up times togrow,which possibly increases the severity of the glitching behavior.Workaround:Ensuring that the V DD power supply ramp up is a fast as possible helps minimize the potential forGPIO glitches.Follow guidelines for LDO pin capacitive loading documented in the electrical sectionStellaris LM3S1960A2Errataof the data sheet.System designers must ensure that,during the V DD supply ramp-up time,possibleGPIO pin glitches can cause no adverse effects to their systems.Silicon Revision Affected:A26General-Purpose Timers6.1General-purpose timer Edge Count mode count error when timeris disabledDescription:When a general-purpose timer is configured for16-Bit Input Edge Count Mode,the timer(A or B)erroneously decrements by one when the Timer Enable(TnEN)bit in the GPTM Control(GPTMCTL)register is cleared(the timer is disabled).Workaround:When the general-purpose timer is configured for Edge Count mode and software needs to“stop”the timer,the timer should be reloaded with the current count+1and restarted.Silicon Revision Affected:A26.2General-purpose timer16-bit Edge Count or Edge Time mode doesnot load reload valueDescription:In Edge Count or Edge Time mode,the input events on the CCP pin decrement the counter until thecount matches what is in the GPTM Timern Match(GPTMTnMATCHR)register.At that point,aninterrupt is asserted and then the counter should be reloaded with the original value and countingbegins again.However,the reload value is not reloaded into the timer.Workaround:Rewrite the GPTM Timern Interval Load(GPTMTnILR)register before restarting.Silicon Revision Affected:A26.3The General-Purpose Timer match register does not functioncorrectly in32-bit modeDescription:The GPTM Timer A Match(GPTMTAMATCHR)register triggers a match interrupt when the lower16bits match,regardless of the value of the upper16bits.Workaround:None.Stellaris LM3S1960A2ErrataSilicon Revision Affected:A27UART7.1The RTRIS bit in the UARTRIS register is only set when the interruptis enabledDescription:The RTRIS(UART Receive Time-Out Raw Interrupt Status)bit in the UART Raw Interrupt Status(UARTRIS)register should be set when a receive time-out occurs,regardless of the state of theenable RTIM bit in the UART Interrupt Mask(UARTIM)register.However,currently the RTIM bitmust be set in order for the RTRIS bit to be set when a receive time-out occurs.Workaround:For applications that require polled operation,the RTIM bit can be set while the UART interrupt isdisabled in the NVIC using the IntDisable(n)function in the StellarisWare Peripheral Driver Library,where n is21,22,or49depending whether UART0,UART1or UART2is used.With thisconfiguration,software can poll the RTRIS bit,but the interrupt is not reported to the NVIC.Silicon Revision Affected:A28PWM8.1PWM pulses cannot be smaller than dead-band timeDescription:The dead-band generator in the PWM module has undesirable effects when receiving input pulsesfrom the PWM generator that are shorter than the dead-band time.For example,providing a4-clock-wide pulse into the dead-band generator with dead-band times of20clocks(for both risingand falling edges)produces a signal on the primary(non-inverted)output that is High except for40clocks(the combined rising and falling dead-band times),and the secondary(inverted)output isalways Low.Workaround:User software must ensure that the input pulse width to the dead-band generator is greater thanthe dead-band delays.Silicon Revision Affected:A28.2PWM interrupt clear misses in some instancesDescription:It is not possible to clear a PWM generator interrupt in the same cycle when another interrupt fromthe same PWM generator is being asserted.PWM generator interrupts are cleared by writing a1to the corresponding bit in the PWM Interrupt Status and Clear(PWMnISC)register.If a write toclear the interrupt is missed because another interrupt in that PWM generator is being asserted,Stellaris LM3S1960A2Erratathe interrupt condition still exists,and the PWM interrupt routine is called again.System problemscould result if an interrupt condition was already properly handled the first time,and the softwaretries to handle it again.Note that even if an interrupt event has not been enabled in the PWMInterrupt and Trigger Enable(PWMnINTEN)register,the interrupt is still asserted in the PWMRaw Interrupt Status(PWMnRIS)register.Workaround:In most instances,performing a double-write to clear the interrupt greatly decreases the chancethat the write to clear the interrupt occurs on the same cycle as another interrupt.Because eachgenerator has six possible interrupt events,writing the PWMnISC register six times in a rowguarantees that the interrupt is cleared.If the period of the PWM is small enough,however,thismethod may not be practical for the application.Silicon Revision Affected:A28.3PWM generation is incorrect with extreme duty cyclesDescription:If a PWM generator is configured for Count-Up/Down mode,and the PWM Load(PWMnLOAD)register is set to a value N,setting the compare to a value of1or N-1results in steady state signalsinstead of a PWM signal.For example,if the user configures PWM0as follows:■PWMENABLE=0x00000001–PWM0Enabled■PWM0CTL=0x00000007–Debug mode enabled–Count-Up/Down mode–Generator enabled■PWM0LOAD=0x00000063–Load is99(decimal),so in Count-Up/Down mode the counter counts from zero to99and back down to zero(200clocks per period)■PWM0GENA=0x000000b0–Output High when the counter matches comparator A while counting up–Output Low when the counter matches comparator A while counting down■PWM0DBCTL=0x00000000–Dead-band generator is disabledIf the PWM0Compare A(PWM0CMPA)value is set to0x00000062(N-1),PWM0should output a2-clock-cycle long High pulse.Instead,the PWM0output is a constant High value.If the PWM0CMPA value is set to0x00000001,PWM0should output a2-clock-cycle long negative(Low)pulse.Instead,the PWM0output is a constant Low value.Stellaris LM3S1960A2ErrataWorkaround:User software must ensure that when using the PWM Count-Up/Down mode,the compare valuesmust never be1or the PWMnLOAD value minus one(N-1).Silicon Revision Affected:A28.4PWMINTEN register bit does not function correctlyDescription:In the PWM Interrupt Enable(PWMINTEN)register,the IntPWM0(bit0)bit does not functioncorrectly and has no effect on the interrupt status to the ARM Cortex-M3processor.This bit shouldnot be used.Workaround:PWM interrupts to the processor should be controlled with the use of the PWM0-PWM2Interruptand Trigger Enable(PWMnINTEN)registers.Silicon Revision Affected:A28.5Sync of PWM does not trigger"zero"actionDescription:If the PWM Generator Control(PWM0GENA)register has the ActZero field set to0x2,then theoutput is set to0when the counter reaches0,as expected.However,if the counter is cleared bysetting the appropriate bit in the PWM Time Base Sync(PWMSYNC)register,then the"zero"actionis not triggered,and the output is not set to0.Workaround:None.Silicon Revision Affected:A28.6PWM"zero"action occurs when the PWM module is disabledDescription:The zero pulse may be asserted when the PWM module is disabled.Workaround:None.Silicon Revision Affected:A2August04,2011/Rev.3.011Texas Instruments9QEI 9.1QEI index resets position when index is disabledDescription:When the QEI module is configured to not reset the position on detection of the index signal (thatis,the ResMode bit in the QEI Control (QEICTL)register is 0),the module resets the position whenthe index pulse occurs.The position counter should only be reset when it reaches the maximumvalue set in the QEI Maximum Position (QEIMAXPOS)register.Workaround:Do not rely on software to disable the index pulse.Do not connect the index pulse if it is not needed.Silicon Revision Affected:A29.2QEI hardware position can be wrong under certain conditionsDescription:The QEI Position (QEIPOS)register can be incorrect if the QEI is configured for quadrature phasemode (SigMode bit in QEICTL register =0)and to update the position counter of every edge ofboth PhA and PhB (CapMode bit in QEICTL register =1).This error can occur if the encoder isstepped in the reverse direction,stepped forward once,and then continues in the reverse direction.The following sequence of transitions on the PhA and PhB pins causes the error:PhBAssuming the starting position prior to the above PhA and PhB sequence is 0,the position after thefalling edge on PhB should be -3,however the QEIPOS register will show the position to be -1.Workaround:Configure the QEI to update the position counter on every edge on PhA only (CapMode bit in QEICTLregister =0).The effective resolution is reduced by 50%.If full resolution position detection is requiredby updating the position counter on every edge of both PhA and PhB ,no workaround is available.Hardware and software must take this into account.Silicon Revision Affected:A2August 04,2011/Rev.3.0Texas Instruments12Stellaris LM3S1960A2ErrataCopyright©2007-2011Texas Instruments Incorporated All rights reserved.Stellaris and StellarisWare are registered trademarks of Texas Instruments Incorporated.ARM and Thumb are registered trademarks and Cortex is a trademark of ARM Limited.Other names and brands may be claimed as the property of others.Texas Instruments Incorporated108Wild Basin,Suite350Austin,TX78746/stellaris/sc/technical-support/product-information-centers.htmAugust04,2011/Rev.3.0Texas Instruments13IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAudio /audio Communications and Telecom /communicationsAmplifiers Computers and Peripherals /computersData Converters Consumer Electronics /consumer-appsDLP®Products Energy and Lighting /energyDSP Industrial /industrialClocks and Timers /clocks Medical /medicalInterface Security /securityLogic Space,Avionics and Defense /space-avionics-defense Power Mgmt Transportation and Automotive /automotiveMicrocontrollers Video and Imaging /videoRFID OMAP Mobile Processors /omapWireless Connctivity /wirelessconnectivityTI E2E Community Home Page Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2011,Texas Instruments Incorporated。

艾特顿 199160 商品说明说明书

Eaton 199160Eaton Moeller® series PKZM0 Motorschutzschalter, 9 kW, 16 - 20 A, Push-in-KlemmenAllgemeine spezifikationEaton Moeller® series PKZM0 Motor-protective circuit-breaker19916075 mm109 mm 45 mm 0.349 kgIEC/EN 60947 VDE 0660 UL CSAIEC/EN 60947-4-1 UL 60947-4-1CSA-C22.2 No. 60947-4-1-14 CEUL File No.: E36332UL Category Control No.: NLRV CSA File No.: 165628 CSA Class No.: 3211-05 UL CSA4015081972449PKZM0-20-PIProduktnameKatalognummer Produkt Länge/Tiefe Produkthöhe Produktbreite Produktgewicht Zertifikat(e)EANModellcodeDrehknopfPhasenausfallempfindlichkeit (gemäß IEC/EN 60947-4-1, VDE 0660 Teil 102)MotorschutzPhasenausfallempfindlich3-polig 100.000 Schaltvorgänge100.000 SchaltvorgängeHutschienenmontage optionalAufschnappbar auf Hutschiene IEC/EN 60715 mit 7,5 oder 15 mm Höhe.40 Schaltspiele/hIII3MotorschutzschalterFinger- und handrückensicher, Berührungsschutz bei senkrechter Betätigung von vorne (EN 50274)6000 V AC25 g, Mechanisch, entsprechend IEC/EN 60068-2-27, Halbsinusstoß 10 msAuch Motoren mit Effizienzklasse IE3Nebenstromkreis: Manueller Typ E bei Einsatz mit Klemme, oder geeignet für Gruppeninstallationen, (UL/CSA)≤ 0,25 %/K, Restfehler für T > 40°-25 - 55 °C, Arbeitsbereich-5 - 40 °C gemäß IEC/EN 60947, VDE 0660Motorstarterkombinationen Typ MSC…Stellgliedtyp Merkmale Funktionen Polzahl Lebensdauer, elektrischLebensdauer, mechanisch MontagemethodeEinbaulageBetriebsfrequenzÜberspannungskategorie VerschmutzungsgradProduktkategorieSchutzBemessungsstoßspannungsfestigkeit (Uimp) SchockfestigkeitGeeignet fürTemperaturkompensationVerwendet mitMax. 2000 m-25 °C55 °C25 °C40 °C40 °C80 °CFeuchte Wärme, zyklisch, nach IEC 60068-2-30 Feuchte Wärme, konstant, nach IEC 60068-2-781 x (1 - 6) mm²18 - 812 mm50 Hz60 Hz20 A5.5 kW9 kW690 V690 V20 A18 kA, 240 V, SCCR (UL/CSA) mit Leistungsschütz DILM25 18 kA, 480 Y/277 V, SCCR (UL/CSA) mit Leistungsschütz DILM25310 A, Irm, Einstellbereich max.± 20% Toleranz, AuslöserblöckeGrundgerät befestigt 15,5 x lu, Auslöserblöcke 1.5 HP 5 HP 3 HP 15 HPHöheUmgebungsbetriebstemperatur – min Umgebungsbetriebstemperatur – max Umgebungsbetriebstemperatur (gekapselt) – min Umgebungsbetriebstemperatur (gekapselt) – max Umgebungstemperatur Lagerung - min Umgebungstemperatur Lagerung - max Klimafestigkeit Anschlusskapazität (feindrähtig)Anschlusskapazität (ein-/mehrdrähtig AWG)Abisolierlänge (Hauptleiter)Bemessungsfrequenz - minBemessungsfrequenz - max Bemessungsbetriebsstrom (Ie) Bemessungsbetriebsleistung bei AC-3, 220/230 V, 50 Hz Bemessungsbetriebsleistung bei AC-3, 380/400 V, 50 Hz Bemessungsbetriebsspannung (Ue) - min Bemessungsbetriebsspannung (Ue) - max Bemessungsdauerstrom (Iu)Bemessungskurzschlussstrom (Typ E) Kurzschlussauslöser Zugeor. Motorleist. b. 115/120 V, 60 Hz, 1-phasig Zugeordnete Motorleistung bei 200/208 V, 60 Hz, 3-phasig Zugeordnete Motorleistung bei 230/240 V, 60 Hz, 1-phasig Zugeordnete Motorleistung bei 575/600 V, 60 Hzm 3-phasigPush-In Klemmen020 A20 AÜberlastauslöser: Auslöseklasse 10 A 5.82 W0 W0 W0 WAnforderungen der Produktnorm sind erfüllt.Anforderungen der Produktnorm sind erfüllt.Anforderungen der Produktnorm sind erfüllt.Anforderungen der Produktnorm sind erfüllt.Anforderungen der Produktnorm sind erfüllt.Unzutreffend, da die gesamten Schaltgeräte überprüft werden müssen.Unzutreffend, da die gesamten Schaltgeräte überprüft werden müssen.Anforderungen der Produktnorm sind erfüllt.Verbindung Anzahl der Hilfskontakte (Wechsler)Anzahl der Hilfskontakte (Öffner)Anzahl Hilfskontakte (Schließer)Überlastauslösestromeinstellung - min Überlastauslösestromeinstellung - max Auslösecharakteristik Geräteverlustleistung, stromabhängig pvid Verlustleistungskapazität PdissVerlustleistung pro Pol, stromabhängig, PvidStatische Verlustleistung, stromunabhängig PVS10.2.2 Korrosionsbeständigkeit10.2.3.1 Wärmebeständigkeit von Umhüllung10.2.3.2 Widerstandsfähigkeit Isolierstoffe gewöhnliche Wärme 10.2.3.3 Widerst. Isolierstoffe abnorm. Wärme/Feuer durch int. elektr. Auswirk.10.2.4 Beständigkeit gegen UV-Strahlung10.2.5 Heben10.2.6 Schlagprüfung10.2.7 BeschriftungenUnzutreffend, da die gesamten Schaltgeräte überprüft werden müssen.Anforderungen der Produktnorm sind erfüllt.Unzutreffend, da die gesamten Schaltgeräte überprüft werden müssen.Unzutreffend, da die gesamten Schaltgeräte überprüft werden müssen.Liegt in der Verantwortung des Schaltanlagenbauers.Liegt in der Verantwortung des Schaltanlagenbauers.Liegt in der Verantwortung des Schaltanlagenbauers.Liegt in der Verantwortung des Schaltanlagenbauers.Liegt in der Verantwortung des Schaltanlagenbauers.Die Erwärmungsberechnung liegt in der Verantwortung des Schaltanlagenbauers. Eaton stellt Verlustleistungsdaten der Geräte bereit.Liegt in der Verantwortung des Schaltanlagenbauers. Die Spezifikationen für die Schaltgeräte müssen beachtet werden.Liegt in der Verantwortung des Schaltanlagenbauers. Die Spezifikationen für die Schaltgeräte müssen beachtet werden.Das Gerät erfüllt die Anforderungen, wenn die Informationen in der Montageanweisung (IL) beachtet werden.DA-DC-00004889.pdfDA-DC-00004919.pdfETN.PKZM0-20-PI.edzIL122024ZUWIN-WIN mit Push-in-TechnikProduktübersicht für den Maschinenbau Sortimentskatalog Motoren schalten und schützenpkzm0_pi.stpmotorschutzschalter_bis_32a_pi.dwgeaton-manual-motor-starters-pkz-dimensions.epseaton-manual-motor-starters-pkz-dimensions-002.eps eaton-manual-motor-starters-pkzm-pkzm0-dimensions.eps 121X042121X00210.3 Schutzart von Baugruppen10.4 Luft- und Kriechstrecken10.5 Schutz gegen elektrischen Schlag10.6 Einbau von Betriebsmitteln10.7 Innere Stromkreise und Verbindungen10.8 Anschlüsse für von außen eingeführte Leiter 10.9.2 Betriebsfrequente Spannungsfestigkeit 10.9.3 Stoßspannungsfestigkeit10.9.4 Prüfung von Umhüllungen aus Isolierstoff 10.10 Erwärmung10.11 Kurzschlussfestigkeit10.12 Elektromagnetische Verträglichkeit10.13 Mechanische Funktion Declarations of conformity eCAD model Installationsanleitung Installationsvideos KatalogemCAD model ZeichnungenEaton Konzern plc Eaton-Haus30 Pembroke-Straße Dublin 4, Irland © 2023 Eaton. Alle Rechte vorbehalten. Eaton ist eine eingetrageneMarke.Alle anderen Warenzeichen sindEigentum ihrer jeweiligenBesitzer./socialmedia。

IGBT

STGW40N120KD

STGW40NC60WD

FGH60N60UFDTU

FSAM15SM60A

STGY50NC60WD

HGTG27N120BN

IRG4PC30FDPBF

IRGP4066DPBF

HGTG40N60A4

STGD7NC60HT4

STGW20NC60VD

FGA25N120ANTDTU

2SC0435T2A0-17

STGF7NB60SL

FNA41560

STGW60H65F

STGB20NC60V

STGIPL14K60

STGW35NC120HD

HGTP10N120BN

STGIPS14K60T

IRG7PH46UDPBF

IRG4RC10UTRPBF

IRGP4062DPBF

FGPF4533

SKW15N60

IRG7I313UPBF

IRG4PC40UD-EPBF

FGH80N60FD2TU

IRG4PC30FPBF

STGP18N40LZ

IRG7PH42U-EP

IRGP4066-EPBF

HGTG10N120BND

IRGP4063DPBF

FGH75N60UFTU

STGD10NC60KT4

STGIPL20K60

STGIPS20K60

STGWA45HF60WDI

FGL60N100BNTD

STGD18N40LZT4

STGIPS10K60T

IRG7PH42UPBF

HGTG30N60A4

STGW45HF60WD

SM6451AVNIPPON资料