基于单片机与CPLD的综合应用设计

毕业设计137基于单片机+CPLD体系结构的信标机设计

基于单片机+CPLD体系结构的信标机设计摘要在机场的无线电通信导航设备中,信标机是一种重要的导航设备,因此对信标机的研究和设计具有十分重要的战略意义。

我撰写的论文题目是基于“单片机+CPLD体系结构的信标机设计”,此论文主要针对现在使用的信标机设计技术及元器件类型相对陈旧,实现功能过于手工化、分离元件过多,体积大、重量大、维修困难等问题,为实现设备的小型化、模块化和标准化,进一步提高设备的集成度和可靠性,提高智能化,为此,我根据目前广泛应用于各类仪器、设备中的单片机、CPLD器件,对基于单片机+CPLD体系结构的信标机设计方法进行了浅显的探讨。

设计的主要内容如下:1.对单片机、CPLD和FPGA性能特点进行分析,提出了基于“单片机+CPLD体系结构”的信标机设计方案;2.在CPLD中实现音频信号分频的计算方法,给出了设计原理图;3.单片机与CPLD接口以总线方式实现译码、数据和控制锁存功能的VHDL设计;4.信标发射机的设计;5.给出了整机监控流程图和单片机监控程序的编制。

本文详细介绍了信标机的实现方法,对实现信标机的小型化、微机化进行了有益的尝试,具有一定意义。

关键词单片机信标机 CPLDBased on “MCU+CPLD Architecture”to design beacon tranmitterAbstractBeacon transmitter is an important device to the wired comunication and navigation in airport,so it's of great strategic value to make applied researches.This paper's name is baseed on "MCU+CPLD Architecture" to design beacon transmitter. this thess points out some disadvantages of device ,such as technology backward in technique and type of components obsolete,manual operations,many absolute components,very large size and weight,operating and maintaining diffculty. In order to small size and modules and standardization ,and improve the device's intergrated and very high enough realiability ,intelligence, I explored the methodof beacon transmitter's designing based on "MCU+CPLD Architecture",according to MCU,CPLD components applied to the many instrument and device.The major work of this dissertation is as follows.1. Analysising the feature of MCU,CPLD, FPGA, I provided the method of beacon transmitter basee on "MCU+CPLD Architecture".2. Audio signal frequency is implemented in CPLD,give the schematic of the designing.3. Decording,latching data controlling signals are implemented in CPLD by interface between MCU and CPLD.4. Beacon transmitter's designing.S. Drawing the flow chart and making the MCU controlling and monitered programe.This paper introduced the method of the beacon transmitter, and gived the advantage tastes bymaking beacon transmitter very small size and controlled by computer.Key words MCU beacon transmitter CPLD目录第一章绪论 (1)1.3研究背境 (2)第二章解决方案、设计内容和技术难点 (3)2. 1解决方案 (3)2.1.1 CPLD/FPGA器件及EDA设计技术 (3)2.1.2“单片机+CPLD体系结构”的特点 (5)2.2设计内容 (7)2.2.1信标机的系统结构框图 (7)2.3技术难点 (8)2. 3. 1 CPLD与单片机的接口方式 (8)2. 3. 2 CPLD片内功能的实现 (8)2.3.3可编程逻辑器件的选型 (8)第三章CPLD片内逻辑功能设计 (9)3. 1 CPLD选型 (9)3. 1. 1 CPL。

一种实用单片机和CPLD最小应用系统的设计

Technical Communications

《自动化技术与应用》2009 年第 28 卷第 8 期

一种实用单片机和 CPLD 最小应用系统的设计

毕立恒, 刘玉宾 (黄河水利职业技术学院 自动化工程系,河南 开封 453002)

摘 要:单片机应用系统中,通常由程序存储器、A/D 电路、D/A 电路、数据存储器、键盘、显示器、通信接口等部分组成。传统 的设计要用到一些专用的可编程接口器件或多片标准逻辑器件设计接口电路,器件多必然带来 PCB 面积大、布线困难、可靠 性减低等缺点,难以实现产品达小型化、集成化和高可靠性。随着 F P G A 和 C P L D 的发展, 用 F P G A 和 C P L D 取代 TTL/COMS 逻辑电路在嵌入式应用设计中得到越来越多的应用。

Abstract: In single-chip application system, the system is composed of memorizer, A/D, D/A, and some special programmable devices. This paper discusses the design of the system by using the FPGA and CPLD devices to replace the TTL/COMS devices.

Key word: single-chip; CPLD; bus

1 引言

CPLD(复杂可编程逻辑电路)是一种具有丰富的可编 程 I / O 引脚的可编程逻辑器件, 具有在系统可编程、使 用方便灵活的特点; 可实现常规的逻辑器件功能和复杂 的时序逻辑功能。单片机具有功能灵活、易于人机对 话、良好的数据处理能力、和很高的性价等特点。在功 能上,单片机与 CPLD 有很强的互补性。CPLD 同单片机 接口,可以作为单片机的一个外设,实现单片机所要求的 功能。通过把数字部分做进 CPLD 中,省去了绝大多数 中规模集成电路, 例如, 实现常用的地址译码、锁存器、 8255 等功能;也可实现扩展串行口等单片机所要求的特 殊功能。实现嵌入式应用系统的灵活性, 也提高了嵌入 式应用系统的性能。把 C P L D 应用于嵌入式应用系统, 同单片机结合起来, 更能体现其在系统可编程、使用方 便灵活的特点。以此两类器件相结合的电路结构在很多

单片机与CPLD的应用

璐

删ⅧC

Q】(QD

业一/P00

7432四L D{ Ql

跑

观

婵

p0B

DB

QB

P04

D4

饼

P05 P06

Ⅸ Ⅸ

Q5 Q6

Ⅵ

I=

勉L

盟!

咝

一

j

迦

逖

迹 迹

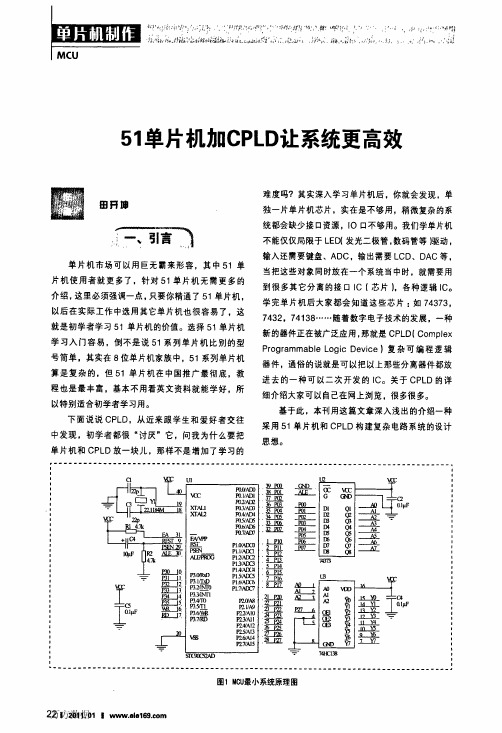

模式。各个对象采用的三总线连接.根据这种电路

结构。这里给出一种单片机同CPLD的总线接口模

式。如图4所示。 MCU

CPLD

卅

卜

P0 弋双向数据总线y; Io

图6原理图输入设计CPLD 该原理图编译成功后,我们还需要根据实际电 路连接图分配绑定引脚,引脚绑定如图7所示。再 编译就可以得到可供下载的文件’.pof了,最后只 需要将下载电缆连接到电路板上,仍然通过该软件 即可完成下载。

万方数据 24 l 2011.01 I WWW.elel69.corn

正因为CPLD的IO脚是可以随意分配的,通 常我们会结合实际的PCB板设计布线的便利来调整 引脚分配。引脚分配更改后,只需要重新分配引脚 再编译下载即可。

首先从熟悉的最小系统电路电路说起。如图1 所示。图中用网络标号实现电路连接,这样绘制的 电路图清晰整洁。U1是经典的51单片机lC.复 位电路和晶振电路是传统电路,这里C5电容是靠 近单片机VCC引脚的。用来对电源滤波.图中其 它芯片VCC附近都有相同功能的滤波电容。U2是 经典的低八位地址锁存电路,这里的74373也可 以用74573代替,U3是地址译码电路,74138实 现连续8个地址(1#井####静##样##000~1##静 样样样样###{lf撑111,{If是无关位。可以是0也可以是1, 取决于电路其它部分的需要)对象扩展。这些电路 教科书上都有详细介绍,如果不能理解,请参考笔 者在本刊2007年12期撰写的文章《51系列单片 机总线时序分析与编址技术》o

单片机与CPLD综合应用技术

其实就业的问题,对于一个努力的人来说是何等地简单。我面试了300多名本科生,我只对其中几个成绩中等的本科生感兴趣。他们都是参加过2001年全国电子大赛,利用平时业余时间、暑假及寒假都在跟老师干活的学生。与他们聊天真是一种莫大的享受和欣慰,对于我来说真的是如获至宝。于是,我就立即劝他们,成绩中等确实难以考上好的学校和导师,还不如不考研究生以免浪费时间;同时也充满自信告诉他们:“我就是伯乐!我愿意给您机会和花钱培养您”。事实上,即便考上研究生,如果没有遇上具有超前眼光和经费充足的导师,读了也白读。更何况现在的研究生扩招得这么多?一个导师带那么多研究生,有那么多课题吗?即便有的话,他应付得过来吗?可能残酷的现实将会让您看到,毕业之后回头一看,还远远不如当年一道毕业的同班同学。确实也是,人家的机会比您好得多,关键是人家对待机会比您把握得好,可以说:恰到火候。难道非要读研究生,理论水平才能提高吗?不!我们知道电子与计算机技术的发展日新月异,大学的更新速度一定就快吗?回答是否定的。比如说推广PHILIPS的最新单片机和USB技术吧!他们的更新速度肯定比一个可持续发展的企业要慢得多。难道说我们的人才水平不够高吗?我们公司就有这样一批在各个领域里出类拔萃的年轻专家。从2003年开始,我们将会有一系列的专著在北京航空航天大学出版社出版,大多数的著作都源于我们长期的基础研究和应用开发。可以毫不夸张地说,这些都是我们这个年轻团队合作的结晶。他们是卓越的人才,他们没有就业的压力,他们不怕炒鱿鱼。相反我倒要想尽办法加强公司的管理,从工资、奖金、福利、生活和事业成就感等各个方面绞尽脑汁善待人才和留住人才,这么努力的人才根本就不需要过多地为工作和生活发愁。对于这个问题,当然是仁者见仁,智者见智,也就是下面我要讲到的问题:一个人如何根据自己的特点、条件和机遇对自己定位的问题,这也是至关重要的。

基于单片机的CPLD通信系统设计

CPLD 可以实现高效的运转、在线对程序进行修改,而单机 片能够结合多个任务进行操作,将两者进行结合后可以实现应用 范围广泛、造价低、实用性强、性价比高、驱动能力强等特点。 CPLD 具备速度快,做功消耗低、保密性强、抗干扰、连接方便 等特点,而单机片适合比较复杂的操控计算的环境,因此将两者 进行结合将是一个比较好的选择。 2 硬件设计

图1 硬件连接框图 EPM3256ATC144-7 与 STC89LE52RC 建议一个通信桥梁,使 用三个总线的形式 :总线、数据总线、控制总线,数据总线和地 址总线低 8 位均由 PO 接口提供,地址总线高 8 位由 P2 提供接口, 因为 PO 接口属于数据,所以 PO 连接口输出的低 8 位地址应该用 锁存器对其锁存,EPM3256ATC144-7 就是为了实现他的锁存。 STC89LE52RC 锁 存 是 允 许 ALE 接 EPM3256ATC144-7 的 JP2-5 引脚,如果 ALE 出现了变时,PO 接口继续讲低 8 位的地址 锁存,如果应该读操作,那么 PO 接口成为数据输入的方式,当 读到 PD 有效,EPM3256ATC144-7相对应的内容在 PO 接口线之上, 并且由 CPU 读入逻辑器中 A ;如果是要进行操作书写,那么 PO 接口成为数据输出方式,如果 WR 有效,就需要讲 PO 接口上出 现的累加器 A 里面的内容写到 EPM3256ATC144-7 相对应的位置。 在对拨号开关的值进行设置的时候,EPM3256ATC144-7 实 施锁存,并且把拨号开关的值锁存,如果读取 STC89LE52R 有效, 通过 PO 将数据读入,在写信号有效的时候,通过数据总线从 PO 接口写出,到达 EPM3256ATC144-7,EPM3256ATC144-7 将数据 进行处理,然后表达呈现开关值。如图 1 所示为 EPM3256ATC1447 STC89LE52RC 流程图。

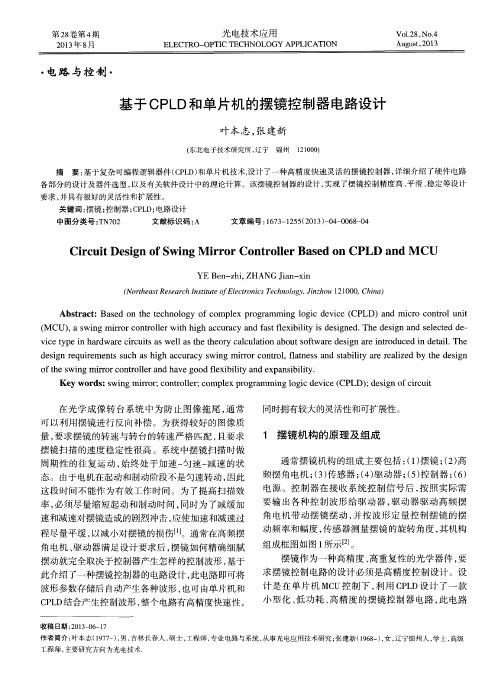

基于CPLD和单片机的摆镜控制器电路设计

同时拥 有较大的灵活性和可扩展性 。

1 摆 镜 机构 的原 理 及 组成

通 常摆镜 机构 的组 成 主要包 括 : ( 1 ) 摆镜 ; ( 2 ) 高 频摆 角 电机 ; ( 3 ) 传感 器 ; ( 4 ) 驱 动器 ; ( 5 ) 控制 器 ; ( 6 )

要求 , 并 具 有 很好 的灵 活 性 和扩 展 性 。 关键 词 : 摆镜 ; 控制器 ; C P L D; 电路设 计 中 图分 类 号 : T N 7 0 2 文 献标 识 码 : A 文章编号: 1 6 7 3 — 1 2 5 5 ( 2 0 1 3 ) 一 0 4 — 0 0 6 8 — 0 4

Ab s t r a c t : Ba s e d o n t h e t e c h n o l o g y o f c o mp l e x p r o g r a mmi n g l o g i c d e v i c e( CP L D)a n d mi c r o c o n t r o l u n i t

在 光 学成 像 转 台系统 中为 防止 图像 拖尾 , 通 常

可 以利用 摆镜 进行 反 向补 偿 。为获 得较好 的图像质 量, 要 求摆 镜 的转速 与转 台 的转 速严 格 匹配 , 中摆镜 扫 描时做 周期 性 的往 复运 动 , 始 终处 于 加 速一 匀速一 减 速 的状

这段 时 间不能作 为有效工 作 时间 。为 了提高 扫描效

率, 必须 尽量缩 短起 动 和制动 时 间 , 同时为 了减缓 加 速和减 速对摆镜造 成的剧烈 冲击 , 应使 加速和减速 过 程尽量 平缓 , 以减 小对摆 镜 的损 伤【 ¨ 。通 常在高频 摆 角 电机 、 驱动器 满 足设计 要求 后 , 摆 镜 如何精 确细 腻 摆动就 完全取决 于控制器 产生怎样 的控制波形 , 基于

基于单片机和CPLD的无刷直流电机系统

速控制 , 给 出了该控 制 系统的硬件 结构设计和软件 流程设计 。试 验结果表 明: 该无刷 直流 电机控制 系统 能够较好地 实现

( 1 . 中国科学院长春光学精 密机械 与物理研 究所 , 吉林长春 1 3 0 0 3 3 ; 2 . 中国科学院研究生院 , 北京 2 1 5 1 6 3 ) 1 0 0 0 3 9; 3 . 中国科学院苏州生物医学工程技术研究所 , 江苏苏州

摘要 : D ) 设计 了一种具有霍 尔位置传感器接 口电路 、 电流采样 电路 以及

( 1 . C h a n g c h u n I n s i t t u t e o f Op i t c s , F i n e Me c h a n i c s a n d P h y s i c s , C h i n e s e Ac a d e my o f S c i e n c e s , C h a n g c h u n 1 3 0 0 3 3 , C h i n a ; 2 . Gr a d u a t e C o l l e g e o f t h e C h i n e s e A c a d e my o f S c i e n c e s , B e i j i n g 1 0 0 0 3 9 , C h i n a ;

BLDCM Co n t r o l S y s t e m De s i g n Ba s e d o n M CU a n d CP LD

基于CPLD的PIC32单片机大容量存储系统设计

CL P D内部采用模块化设计原则 , 分别建立 PC 2 I 3 接

基于CL P D设计 的 PC 2 I 3 单片机 大容量存储 扩展系统可

口模块 、 IO模块 和 Fah 写模 块 。FF FF l 读 s IO由 C L P D片

内配置 编写 , 这样 既可 以最 大化地利用 C L P D内部 资源 以实现系统微 型化 , 又可以节省使用外部 FF IO芯片 的成

u i n r e o c i v soa e n r t e a o h c l ce e p r n a ih s e d ag - a a i d t .T e c mp st n o n t o d r t a h e e t rg a d er v l f t e ol td x ei i i e me tl h g - p e lr e c p ct aa y h o o ii f o

c re t e s a d fa i i t f s se d sg . o r cn s n e sb l y o y tm e in i

【 y w rs I3 U trg esrmet f s m r;C L Ke o d 】PC 2 MC ;s aem aue n; ah me oy P D o l

te s se h ytm po rms a d h r wae nefc ic i a w l a d s n d a f CP D o t l ntmo ua r nrd cd h rga n ad r itr e crut s el s ei ie s o L c nr u i a g o d lr ae it u e .T e o

0 引言

美 国微芯 ( coh ) 司推 出的3 位单 片机 PC 2 Mi c i 公 r p 2 I3