第8章DSP应用系统设计

[互联网]8 DSP系统设计

![[互联网]8 DSP系统设计](https://img.taocdn.com/s3/m/3fb87156f08583d049649b6648d7c1c708a10b87.png)

4). 供电方式 •多电源, 电压供电 在一块板子上可能有多电源, 5v, 3.3v, 2.5v, 1.8v, 这些电压都可能存在, 在有A/D, D/A时, 还 要考虑模拟电源, 最好将模拟和数字电源分开。模 拟电源采用DC-DC方式, 为了防止高频干扰, 最好采 用稳压方式。

•电流供电 最经典的方式是恒流源方式, 如电话机的供 电方式。 电池供电 如手机, MP3等便携方式 耦合供电 如鼠标的供电方式

在设计外部存储器的接口时主要考虑两个问 题:一是速度问题,二是DMA(直接存储器访问) 接口问题。

先讨论存储器接口的速度问题。对于快速的 存 储 器 , 即 存 取 时 间 < 20ns 的 器 件 , 可 以 直 接 与’54x系列DSP接口;而对于慢速存储器器件, 则DSP在访问时需要插入等待状态。由于’54x系 列具有内部的可编程等待状态发生器,所以不需 要外接其它的逻辑电路便可与慢速存储器接口。 与其它系列的DSP相比,’54x与存储器的接口更 方便、更简洁。下图为DSP与存储器接口的电路。

具有“看门狗”的复位电路

2. 时钟电路

DSP提供时钟的最简单、常用的方法是利用DSP芯片内部提供的 时钟振荡电路。在DSP芯片的引脚Xl和X2/CLKIN之间接一枚晶 体,如图所示,即可为DSP产生稳定的时钟信号。但应该注意 的是,时钟电路的走线应尽量地短,以避免产生高频辐射干扰。 另一种更简单可靠的方法是采用成品的晶体振荡器电路。这是 一种厚膜电路,其内部已封装好晶体和电容以及相应的电路, 只需要加上电源,在其输出端就可以得到所需的时钟。用于 DSP系统时,从引脚X2/CLKIN输入时钟信号,引脚X1悬空即可。 电路如图所示。

DSP系统的设计过程

1. 根据应用系统的目 标确定系统的性能 指标、信号处理的 要求用数据流程图 等来描述;

DSP原理及应用-绪论

1982年问世的第一个定点DSP芯片是TMS320C10 同一代TMS320系列DSP产品的CPU结构是相同的, 但片内存储器及外设电路的配置不一定相同

15

TI的三大主力芯片

TMS320C2000系列 用于数字控制系统 TMS320C5000系列 用于低功耗、便携的无线通信终端产品 TMS320C6000系列

2

要求:

不迟到、不早退、更不能无故旷课 按时完成作业,决不容许抄袭现象

课堂上积极回答问题,积极参与讨论

3Leabharlann 第1章 绪论1.1 数字信号处理概述

4

数字信号处理:滤波、参数提取、频谱分析、压缩等

Digital Signal Processing 广义理解 DSP Digital Signal Processor 狭义理解

美国Inmos公司的:IMSA100卷积/相关器

14

TMS320 DSP芯片(通用型)

定点型

TMS320C1x、 TMS320C2x、 TMS320C2xx、 TMS320C5x、 、 TMS320C54x、 TMS320C62x

浮点型

TMS320C3x、 TMS320C4x、 TMS320C67x

外部可扩展的程序和数据空间,总线接口,I/O接口等。

不同的DSP芯片所提供的硬件资源是不相同的,应根据系统的 实际需要,考虑芯片的硬件资源。

27

4.DSP芯片的运算精度

运算精度取决于DSP芯片的字长。定点DSP芯片的字长通常

为16位和24位。浮点DSP芯片的字长一般为32位。

5.DSP芯片的开发工具 快捷、方便的开发工具和完善的软件支持是开发大型、复杂 DSP应用系统的必备条件。

DSP系统设计

INT3 有 ? 效 否

有 并 效 行 自 ? 举 否

是 传 数 输 据

是 装 代 载 码 A

A

初 化 行 始 串 口 拉 XF 低

I/O 自 举 准 行 自 标 串 口 举

McB P1 S ? 否 是 有 效 数 ? 据 否 传 输 数 据 是 是 否 否 B IO 低 ? 是 有 效 数 ? 据 传 输 数 据

W =0x--A ? A 是 8位 式 模

否

-1个 以 读 取R 字 初 始 寄 器 化 存 。 8位 式 , 个 模 下 每 字 按 节 取 要 字 读 两 。 次 读 起 地 的 取 始 址 X PC 读 起 地 的 取 始 址 PC

读 段 大 取 的 小R 是

R =0? 否 读 段 标 址 取 目 地 读 段 内 并 取 的 容 放 到 标 址 置 目 地

标准串行自举 标准串行口方式McBSP1(8位模式)

B IN R T1=1 否

D R R =0x08? 是 读 一 节 下 字

检 M SP0 测 cB 自 举

D R R =0xA ? A 是 8位 式 模 读4 个 元 哑 传 代 输 码

否

标准串行自举(续) 标准串行口方式McBSP0(16位模式)

复位周期TRP

TRP = 3.125 × CRP

看门狗周期TWP

TWP = 25 × CWP

带手动复位和电压监控 TPS3808 主要特性:

复位延迟时间可设(1.25ms~10s); 小尺寸SOT23;

上电顺序连接

带手动复位和电压监控(TPS3808)

复位过程时序(tD电容预设)

带手动复位和电压监控(TPS3808)

跳 到 始 址 转 起 地 开 运 始 行

DSP原理与应用 第三版

运算速度 以上。TMS320C6201执行1024点复数FFT运算时间只有66uS。

高度集成化

集滤波、A/D、D/A、ROM、RAM和DSP内核于一体的

运算精度和动态范围

模拟混合式DSP芯片已有较大的发展和应用。 DSP字长从8位已增到64位,累加器长度也增到40位,

开发工具

提高了运算精度。同时,采用超长字指令字(VLIW)结构和

2. TMS320C55x概况

目前C55x系列芯片主要有:

C5501/2(主频300MHz, McBSP,HPI接口), C5503/6/7/9A (主频200MHz, McBSP, HPI,

优点:成本低廉 缺点:性能差、

速度慢

DSP处理器

优点:速度高、大规模生产成本低; 缺点:开发成本高、通用性差。

针对数字信号处理的要求而设计,是数 字信号处理系统设计中采用的主流芯片。 优点:灵活、高速、便于嵌入式应用

7

1.2 DSP芯片简介

1.2.1 DSP芯片的发展历史、现状和趋势 1.2.2 DSP芯片的特点 1.2.3 DSP芯片的分类 1.2.4 DSP芯片的应用领域 1.2.5 选择DSP芯片考虑的因素

可同时进行取指令和多个数据存取操作,使CPU

在一个机器周期内可多次对程序空间和数据空

采用哈佛结构 间进行访问, 大大地提高了DSP的运行速度。

采用多总线结构

T1

T2

T3

T4

时钟

采用流水线结构

取指令

N

N+1

N+2

N+3

指令译码

N-1

N

N+1

N+2

配有专用的硬件乘法-累加器 取操作数 N-2

第八章 F28335DSP硬件设计

2. 3.

4.

DSP原理与应用 原理与应用

2010年10月21日 年 月 日

11

三、TMS320F28xxx最小系统设计

DSP最小系统包括以下几个部分: 最小系统包括以下几个部分: 最小系统包括以下几个部分 1. 电源系统 电源系统(Power) 2. 复位和时钟电路 复位和时钟电路(Reset & Clock) 3. 存储器接口(ROM or RAM) 存储器接口( ) 4. 外设接口(串行通信、并行通信、I/O扩展) 外设接口(串行通信、并行通信、 扩展 扩展) 5. JTAG(Joint Test Action Group)接口 ( ) 6. 开关电源或电机控制典型电路设计 7. 逻辑电路设计思路和探讨

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 A17 A18 A19 A20 RESET NC WP/ACC RY/BY BYTE

DQ0 DQ1 AM29LV320D DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15/A-1 OE WE CE VDD VSS VSS

R90 10K WDO WDRESET VCXF1 PFO 100 R47

a)基本复位电路 )

b)带看门狗和电源监控的复杂复位电路 )

DSP原理与应用 原理与应用

2010年10月21日 年 月 日

15

2) 时钟电路设计

Y1 X2 X1/XCLKIN C126 10pF 30M C127 10pF

a) 无源时钟电路

2010年10月21日 年 月 日

5

TMS320F28xxx接口时序图 (热复位) 接口时序图2(热复位) 接口时序图10月21日 年 月 日

第8章 DSP应用系统设计举例

#include <math.h> #include <tms320.h> /*调用库*/ #include <dsplib.h> #define NX 256 /*FFT运算的长度*/

short scale=1; /*归一化*/ short noscale=0; /*非归一化*/ short x[512]; /*数据大小*/

下面以8~1024复数点FFT算法为例,介绍用DSP芯 片实现的方法。 1.FFT运算序列的存储分配 (了解或者不要求) FFT运算时间是衡量DSP芯片性能的一个重要指标, 在用DSP芯片实现FFT算法时,合理地安排好所使用的 存储空间是十分重要的。

1.FFT运算序列的存储分配

程序存储器

┇

(1) 程序空间的分配

8.1.1 FFT算法的简介

1.离散傅氏变换DFT 对于长度为N的有限长序列x(n),它的离散傅里 叶变换为: N 1 X (k ) x(n)WNnk k = 0,1,…,N-1

n0

WN = e-j2/N,称为旋转因子,或蝶形因子。

在x(n)为复数序列的情况下,计算X(k):

对某个k值,需要N次复数乘法、(N-1)次复数加法; 对所有N个k值,需要N2次复数乘法和N(N-1)次复数加法。

2.快速傅氏变换FFT 按时间抽取的FFT——DIT FFT FFT算法 按频率抽取的FFT——DIF FFT DIT FFT算法:是在时域内将每一级输入序列依次按 奇/偶分成2个短序列进行计算。 DIF FFT算法:是在频域内将每一级输入序列依次按 奇/偶分成2个短序列进行计算。

假定序列x(n)的点数N是2的幂,按照DIT FFT算法 可分解为: 偶序列:x(0),x(2),x(4),…,x(N -2) 即x1(r) = x(2r),r = 0,1,…,N 1 奇序列:x(1),x(3),x(5),…,x(N -1)

《DSP应用系统设计》课件

DSP应用系统广泛应用于通信、多媒体、 工业控制等领域。

DSP应用系统的设计需要考虑到性能、成 本、功耗等多个因素。

DSP应用系统的特点

高性能:处理速度快,计 算能力强

灵活性:可编程,可定制, 可扩展

实时性:实时处理数据, 响应速度快

稳定性:可靠性高,抗干 扰能力强

应用广泛:应用于通信、 信号处理、图像处理等领 域

01 02

03 04

05

DSP芯片的分类:根据应用领域和功能,可以分为通用型DSP芯片、 专用型DSP芯片和混合型DSP芯片。

通用型DSP芯片:具有较高的灵活性和可编程性,适用于多种应用 领域。

专用型DSP芯片:针对特定应用领域进行优化设计,具有较高的性 能和效率。

混合型DSP芯片:结合了通用型和专用型DSP芯片的优点,具有较 高的灵活性和性能。

常用数字信号处理算法

快速傅里叶变换(FFT):用于信号频谱分析 离散小波变换(DWT):用于信号去噪和压缩 自适应滤波器:用于信号处理和系统辨识 卡尔曼滤波器:用于信号估计和预测 神经网络:用于模式识别和预测 遗传算法:用于优化问题和参数估计

算法设计流程与优化

确定算法目标:明确算法需要解决的问题和性能要求

应用实例:包括图像处理、信号处 理、语音识别等

调试与测试方法

单元测试:对每个模块进行独立测试,确保其功能正确

集成测试:将各个模块集成在一起进行测试,确保系统整体功能正确

压力测试:对系统进行高负载测试,确保系统在高负载情况下仍能正常 运行

性能测试:对系统的性能进行测试,确保系统满足性能要求

稳定性测试:对系统进行长时间运行测试,确保系统在长时间运行下仍 能保持稳定

硬件设计需要遵循一定的规 范和标准,如IEEE、ISO等

dsp课程设计

dsp课程设计一、课程目标知识目标:1. 理解数字信号处理(DSP)的基本概念,掌握其基本原理和算法;2. 学会使用数学工具进行信号的时域、频域分析,并能够解释分析结果;3. 掌握滤波器的设计方法,能够运用所学知识对实际信号进行处理。

技能目标:1. 能够运用DSP技术对实际信号进行采集、处理和分析,解决实际问题;2. 熟练使用DSP软件和硬件平台,进行算法的实现和验证;3. 培养创新意识和团队协作能力,通过小组合作完成综合性的DSP项目。

情感态度价值观目标:1. 培养学生对数字信号处理技术的兴趣和热情,激发其主动探索精神;2. 培养学生严谨的科学态度,注重实践与理论相结合,提高问题解决能力;3. 增强学生的团队合作意识,培养沟通、交流和协作能力。

课程性质:本课程为专业选修课,旨在帮助学生掌握数字信号处理的基本理论和方法,提高实际问题解决能力。

学生特点:学生已具备一定的电子技术和数学基础,对信号处理有一定了解,但实践经验不足。

教学要求:注重理论与实践相结合,强调学生动手实践,培养解决实际问题的能力。

通过本课程的学习,使学生能够独立完成DSP相关项目的设计与实现。

二、教学内容1. 数字信号处理基础:信号与系统、离散时间信号与系统、线性时不变系统、卷积运算等;2. 离散傅里叶变换:傅里叶级数、离散傅里叶变换(DFT)、快速傅里叶变换(FFT)等;3. 数字滤波器设计:滤波器原理、无限长冲激响应(IIR)滤波器设计、有限长冲激响应(FIR)滤波器设计等;4. 数字信号处理应用:数字信号处理在语音、图像、通信等领域的应用案例分析;5. 实践教学:使用DSP软件和硬件平台进行算法实现和验证,开展综合性的DSP项目。

教学大纲安排:第一周:数字信号处理基础第二周:离散时间信号与系统第三周:线性时不变系统与卷积运算第四周:离散傅里叶变换第五周:快速傅里叶变换第六周:数字滤波器设计原理第七周:IIR滤波器设计第八周:FIR滤波器设计第九周:数字信号处理应用案例分析第十周:实践教学与项目开展教学内容与教材关联性:本课程教学内容依据教材章节进行安排,涵盖数字信号处理的基本理论、方法和应用,确保学生系统掌握DSP相关知识。

【课件】第8章DSP应用系统设计精编版

山东大学控制学院 张东亮

281x DSP最小系统的电源、时钟、JTAG电路

10/14/2019

DSP应用系统基本电路

• 电源电路

• 复位电路 山东大学控制学院 张东亮

• 时钟电路

• JTAG电路

• 存储器扩展

• 电平转换

• CAN接口电路

• RS232/485接口电路

• 指示灯电路, A/D, D/A电路

以永磁同步电机为控制对象的数字交流伺服系统在 数控机床、机器人等运动控制领域获得了广泛应用。交 流伺服系统是电流、速度和位置三环控制系统。

功率 电源

功率 逆变器

传感器

传感器

电机

负载

逆变器 驱动信号

软件数字 控制系统

电量

机械量

命令输入

数字运动控制系统

10/14/210.19永磁同步电机矢量控制原理

id= iα cosθ+ iβ sinθ iq=-iα sinθ+ iβ cosθ

10/1外4/2部019存储器及I/O扩展 XINTF Zone0/1, Zone2, Zone6/7,

1M+32K。

数据线 XD0-XD15。 山东大学控制学院 张东亮

DSP应用系统的设计

器件选型 原理图设计

硬件实现方案。

第二步:器件的选择;

PCB 图设计

一个DSP硬件系统除了DSP芯片外,

硬件调试

还包括ADC、DAC、存储器、电源、逻辑控制、通信、人机

接口、总线等基本部件。

2020年1月3日

5

DSP 应用系统设计

1 硬件设计概述

第二步:器件的选择;

① DSP芯片的选择

选?择首D先SP要芯根片据要系综统合对多运种算因量素的,需折求衷来考选虑择。;

基准电源、多路选择器、输出运放等因素来选择。

2020年1月3日

6

DSP 应用系统设计

1 硬件设计概述

第二步:器件的选择;

③ 存储器的选择 常用的存储器有SRAM、EPROM、E2PROM和FLASH等。 可以根据工作频率、存储容量、位长 (8/16/32位)、

接口方式(串行还是并行)、工作电压(5V/3V)等来选择。

可以根据使用的场合、数据传输要求、总线的宽度、传

输频率和同步方式等来选择。

2020年1月3日

8

DSP 应用系统设计

1 硬件设计概述

第二步:器件的选择;

⑦ 人机接口 常用的人机接口主要有键盘和显示器。

? 通过与其他单片机的通信构成; ? 与DSP芯片直接构成。 ⑧ 电源的选择 主要考虑电压的高低和电流的大小。 既要满足电压的匹配,又要满足电流容量的要求。

第二步:器件的选择;

⑤ 通信器件的选择

通常系统都要求有通信接口。

? 首先要根据系统对通信速率的要求来选择通信方式。

一?般然串后行根口据只通能信达方到式1来9k选b/择s,通而信并器行件口。可达到1Mb/s以 上⑥,总若线要的求选过择高可考虑通过总线进行通信;

电子技术应用《数电》教案

电子技术应用《数电》教案第一章:数字电路基础1.1 数字电路概述了解数字电路的定义、特点和应用领域熟悉数字电路与模拟电路的区别1.2 数制和码制学习二进制、八进制、十六进制的表示方法掌握不同码制(如ASCII码、BCD码)的转换方法1.3 逻辑门学习与门、或门、非门、异或门等基本逻辑门电路掌握逻辑门的功能和真值表第二章:组合逻辑电路2.1 组合逻辑电路概述了解组合逻辑电路的定义和特点熟悉组合逻辑电路的分类和应用2.2 常用组合逻辑电路学习译码器、编码器、多路选择器、多路分配器等电路掌握组合逻辑电路的设计方法2.3 组合逻辑电路的设计实例设计一个4x1多路选择器设计一个全加器第三章:时序逻辑电路3.1 时序逻辑电路概述了解时序逻辑电路的定义和特点熟悉时序逻辑电路的分类和应用3.2 触发器学习SR触发器、JK触发器、T触发器、CTR触发器等电路掌握触发器的真值表、时序图和功能3.3 时序逻辑电路的设计实例设计一个2位同步计数器设计一个顺序检测器第四章:数字电路仿真4.1 数字电路仿真概述了解数字电路仿真的定义和意义熟悉数字电路仿真工具的使用4.2 常用数字电路仿真工具学习Multisim、Proteus等仿真工具的基本操作掌握仿真工具中元器件的选型和连接方法4.3 数字电路仿真实例利用仿真工具验证组合逻辑电路的功能利用仿真工具验证时序逻辑电路的功能第五章:数字电路实验5.1 数字电路实验概述了解数字电路实验的目的和意义熟悉数字电路实验步骤和注意事项5.2 数字电路实验器材和仪器学习数字电路实验所需的器材和仪器使用方法掌握实验器材和仪器的连接和调试方法5.3 数字电路实验实例完成一个组合逻辑电路的实验完成一个时序逻辑电路的实验第六章:数字电路测试与维护6.1 数字电路测试概述理解数字电路测试的目的和方法熟悉测试用例的设计和测试过程6.2 数字电路测试方法学习静态测试和动态测试两种方法掌握测试电路的搭建和测试结果的分析6.3 数字电路维护与故障排除了解数字电路维护的基本原则学习故障排除的步骤和方法第七章:数字系统设计流程7.1 数字系统设计概述理解数字系统设计的基本流程熟悉各个设计阶段的任务和目标7.2 需求分析与规格说明学习如何进行需求分析掌握编写数字系统规格说明书的方法7.3 数字系统设计实现学习数字系统设计的具体步骤掌握硬件描述语言(如Verilog)的使用第八章:数字信号处理器(DSP)8.1 DSP概述理解DSP的定义、特点和应用熟悉DSP与其他处理器的比较8.2 DSP的结构与工作原理学习DSP的内部结构和工作流程掌握DSP的指令集和编程方法8.3 DSP应用实例学习DSP在音频处理、图像处理等领域的应用设计一个简单的DSP应用系统第九章:数字电路与系统的安全与保护9.1 数字电路与系统的安全了解数字电路与系统的安全问题学习加密算法和数字签名技术9.2 硬件安全措施学习物理不可克隆功能(PUF)和硬件安全模块(HSM)掌握安全启动和安全存储的实现方法9.3 系统保护与版权保护了解系统保护的重要性学习数字版权管理(DRM)和软件保护的方法第十章:未来数字电路技术的发展趋势10.1 新兴数字电路技术了解量子计算、神经形态计算等新兴技术学习这些技术对传统数字电路的影响10.2 数字电路设计的未来趋势分析数字电路设计的发展方向探讨可持续发展和环保在数字电路设计中的作用10.3 教育与培训强调终身学习在数字电路技术发展中的重要性探讨在线教育和虚拟实验室在数字电路教学中的应用重点和难点解析一、数字电路基础:理解不同数制和码制之间的转换,以及逻辑门的功能和真值表。

DSP技术及应用课程设计

DSP技术及应用课程设计一、教学目标本课程的教学目标是使学生掌握数字信号处理(DSP)技术的基本原理和应用方法。

通过本课程的学习,学生应能理解DSP技术的基本概念,熟悉DSP芯片的结构和编程方法,掌握DSP技术在信号处理、通信、控制等领域的应用。

具体来说,知识目标包括:掌握DSP技术的基本原理,了解DSP芯片的结构和工作原理,熟悉DSP编程方法和算法。

技能目标包括:能够使用DSP芯片进行信号处理和算法实现,具备DSP系统的调试和优化能力。

情感态度价值观目标包括:培养学生对DSP技术的兴趣和好奇心,提高学生解决实际问题的能力,培养学生的创新意识和团队合作精神。

二、教学内容本课程的教学内容主要包括DSP技术的基本原理、DSP芯片的结构和编程方法,以及DSP技术在信号处理、通信、控制等领域的应用。

具体包括以下几个部分:1.DSP技术的基本原理:包括数字信号处理的概念、特点和基本算法,如离散傅里叶变换(DFT)、快速傅里叶变换(FFT)和小波变换等。

2.DSP芯片的结构和工作原理:包括DSP芯片的内部结构、指令系统、编程方法和中断管理等内容。

3.DSP编程方法和算法实现:包括C语言编程、汇编语言编程和算法实现,如数字滤波器设计、信号去噪和特征提取等。

4.DSP技术在信号处理、通信、控制等领域的应用:包括数字音频处理、数字图像处理、无线通信系统和控制系统等。

三、教学方法为了实现本课程的教学目标,我们将采用多种教学方法,包括讲授法、讨论法、案例分析法和实验法等。

1.讲授法:通过教师的讲解和演示,向学生传授DSP技术的基本原理和应用方法。

2.讨论法:通过小组讨论和课堂讨论,引导学生深入思考和探讨DSP技术的相关问题。

3.案例分析法:通过分析具体的DSP应用案例,使学生更好地理解和掌握DSP技术的应用。

4.实验法:通过实验操作和调试,让学生亲自动手实践,提高学生的实际操作能力和解决问题的能力。

四、教学资源为了支持本课程的教学内容和教学方法的实施,我们将选择和准备适当的教学资源,包括教材、参考书、多媒体资料和实验设备等。

第8章应用系统设计举例

B 1

C sin(T )

其振荡频率由系数A、B和C来决定。因此,设计振荡器主要就

第8章:应用系统设计举例—— 正弦信号发生器 设初始值为0,数字振荡器的二阶差分方程形式为:

y[k ] Ay[k 1] By[k 2] Cx[k 1]

利用单位冲击函数性质,即仅当k=1时,x[k-1]=1,得:

为了便于定点DSP处理, 将所有系数除以2,用16位定点表示:

第8章:应用系统设计举例—— 正弦信号发生器

定时器的初值计算

要求:定时器产生25s时间间隔,获得40kHz的采样频率。

定时器的初值计算由下式决定

f clk fS (TDDR 1)(PRD 1)

式中 f clk 为DSP时钟频率, f S 为采样频率。

第8章:应用系统设计举例—— 正弦信号发生器

内存定位文件清单如下:

MEMORY { PAGE 0: VEC: origin = 1000h, length = 0ffh PROG: origin = 1100h, length = 8000h PAGE 1: DATA: origin = 080h, length = 0807fh

第8章:应用系统设计举例——设计基本步骤

第8章:应用系统设计举例——设计基本步骤

8.1 DSP应用系统设计基本步骤

一个DSP应用系统设计包括硬件设计和软件设计两 部分。 硬件设计又称为目标板设计,考虑算法需求分析和 成本、体积、功耗核算等。 软件设计是指设计包括信号处理算法的程序,用DSP 汇编语言或通用的高级语言(C/C++)编写出来并进行调 试。这些程序要放在DSP片内或片外存储器中运行,在 程序执行时,DSP会执行与DSP外围设备传递数据或互相 控制的指令。 DSP的软件与硬件设计调试是密不可分的。

DSP系统软件设计

DSP芯片的内部初始化 DSP芯片的内部初始化

•影响 影响CPU的运作和整个 的运作和整个DSP系统的使用 影响 的运作和整个 系统的使用 •在所有应用程序开始执行前应对 在所有应用程序开始执行前应对DSP芯片内部进行初始 在所有应用程序开始执行前应对 芯片内部进行初始 化 •DSP的复位状态 的复位状态

;

初始化寄存器: 初始化寄存器:init_54x.asm .mmregs .include "init_54x.inc" .def init_54

; contains all the initial ; values of ST0, ST1,PMST,SWWSR,BSCR

.text init_54: SSBX STM STM STM STM STM .end

状态控制寄存器ST0 状态控制寄存器

位 名称 复位值 说明 当前辅助寄存器号Arx,x=0~7 , = ~ 当前辅助寄存器号 测试位,受指令BIT、CMPM、SFTC 测试位,受指令 、 、 等影响 进位位 累加器A溢出标志 累加器 溢出标志 累加器B溢出标志 累加器 溢出标志 9位页指针,形成数据空间的高9位地 位页指针,形成数据空间的高 位地 位页指针 址以进行直接寻址

中断矢量表、片内外设的初始化举例: 中断矢量表、片内外设的初始化举例: .ref _c_int00 .global _time

; C entry point

.sect ".vectors" RESET: ; reset vector BD _c_int00 ; branch to C entry point STM #200,SP ; stack size of 200 nmi: RETE ;enable interrupts and return from

DSP应用系统设计及论文基本要求

DSP 处理器系统设计

1

一般来说, 一般来说,DSP应用系统设计应该包括 应用系统设计应该包括 硬件设计 程序设计 两部分内容。 两部分内容。

2

7.1 设计过程

7.1.1 确定功能和性能指标 (1)任务给定的功能和性能指标 ) 用户定制,或者上级确定好所要求的功能和性能, 用户定制,或者上级确定好所要求的功能和性能,我 们设计的产品需要满足这些功能、 们设计的产品需要满足这些功能、性能指标要求 (2)自主确定功能或性能指标 ) 自主设计一种新产品——按照市场发展需要、我们自 按照市场发展需要、 自主设计一种新产品 按照市场发展需要 己来确定所设计的产品应该具有什么功能、性能。 己来确定所设计的产品应该具有什么功能、性能。 通常会分析现有类似产品的优缺点, 通常会分析现有类似产品的优缺点,市场需求的预测 分析,来确定。 分析,来确定。

24

迭代法——由递推公式计算 迭代法——由递推公式计算sin(x) 由递推公式计算sin(x)

sin(nx) = 2cos( x)sin([(n − 1) x] − sin[(n − 2) x]

我们需要知道前两个正弦值 sin[(n-2)x]、 sin[(n-2)x]、 sin[(nsin[(n-2)x] 以及一个余弦值 cos(x) 用这种方法产生连续的正弦信号, 用这种方法产生连续的正弦信号,可能会造成比较大的积 累误差。 累误差。

dsp原理及应用课程设计

dsp原理及应用 课程设计一、课程目标知识目标:1. 理解数字信号处理(DSP)的基本原理,掌握其核心概念,如采样、量化、滤波器设计等。

2. 掌握DSP技术在音频、视频和通信领域的应用,了解不同应用场景下的技术特点和要求。

3. 学习DSP相关算法,如快速傅里叶变换(FFT)、数字滤波器设计等,并能运用所学知识解决实际问题。

技能目标:1. 能够运用所学知识分析实际问题,提出基于DSP技术的解决方案。

2. 掌握使用DSP开发工具和软件,如MATLAB、Python等,进行算法仿真和实现。

3. 培养团队协作和沟通能力,通过项目实践,提高解决实际问题的综合能力。

情感态度价值观目标:1. 培养学生对数字信号处理技术的兴趣和热情,激发其探索精神和创新意识。

2. 增强学生对我国在DSP领域取得的成果的自豪感,培养其爱国主义情怀。

3. 培养学生严谨、务实的学术态度,提高其面对挑战、克服困难的信心和勇气。

课程性质分析:本课程为专业核心课程,旨在使学生掌握数字信号处理的基本原理、方法和应用,培养具备实际工程能力的专业人才。

学生特点分析:学生已具备一定的数学基础和编程能力,具有较强的逻辑思维和动手实践能力,但对DSP技术的了解相对有限。

教学要求:1. 结合实际案例,深入浅出地讲解DSP原理,注重理论与实践相结合。

2. 采用项目驱动教学法,引导学生主动探索,培养其解决实际问题的能力。

3. 注重培养学生的团队协作和沟通能力,提高其综合素质。

二、教学内容1. 数字信号处理基础:包括采样定理、量化原理、信号的表示与处理等基本概念,参照教材第一章内容。

2. 离散傅里叶变换(DFT):讲解DFT的基本原理、性质、应用,以及快速傅里叶变换(FFT)算法,涉及教材第二章。

3. 数字滤波器设计:包括数字滤波器的基本类型、设计方法、性能分析,参照教材第三章。

4. DSP应用案例分析:分析音频处理、图像处理、通信系统等领域的DSP技术,结合教材第四章内容。

DSP与智能化系统------第8章 dsp硬件设计基础

二、DSP系统的设计思路

输

输

入 抗混

DSP

平滑 出

叠滤 A/D 芯片 D/A 滤波

波器

器

典型的DSP系统

20

1.总体方案设计

DSP应用

DSP系统设计前:

定义系统性能指标

•明确设计任务 •给出设计任务书

选择DSP芯片

功能描述准确

软件编程

硬件设计

功能描述清楚 描述的方式

软件调试

硬件调试

人工语言

系统集成

29

器件的选型原则 4

逻辑控制

先 确 定 所 用 器 件 , 如 PLD 、 EPLD或FPGA;

再根据自己的特长和公司芯片 的特点决定采用哪家公司的哪一 系列产品;

最 后 根 据 DSP 芯 片 的 频 率 决 定 芯片的工作频率,并以此来确定 使用的芯片。

30

器件的选型原则 5

通信接口

根据与其他系 统通信的速率 决定采用的通 信方式: 串口 并口 总线

INTEL&AD 的新DSP CORE 15

选择芯片考虑的因素

1.DSP芯片的运算速度 MAC时间:一次乘法和一次加法的时间。大部分 DSP芯片可在一个指令周期内完成一次乘法和一次 加法操作。 FFT执行时间:运行一个N点FFT程序所需时间。 由于FFT运算在数字信号处理中很有代表性,因此 FFT运算时间常作为衡量DSP芯片运算能力的一个指 标。 MIPS:每秒执行百万条指令。 MOPS:每秒执行百万次操作。 MFLOPS:每秒执行百万次浮点操作。 BOPS:每秒执行十亿次操作。

Target Application (目标应用)

» Digital Cres (双核心)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

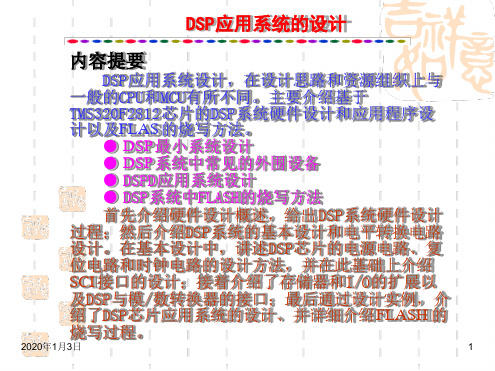

第8章 DSP应用系统设计 本章主要内容:Ø 2812 DSP系统硬件设计 (Hardware Design for 2812 DSP Systems)Ø 基于DSP的数字运动控制系统(A DSP Based Digital Motion Control System)Ø 快速傅里叶变换与FIR数字滤波器(Fast Fourier Transform and FIR Digital Filters) 8.1 2812 DSP系统硬件设计 DSP系统硬件设计一般包括根据系统要求选择合适的DSP芯片、选择外围芯片、设计原理图与设计印刷电路板(PCB)图等过程。

一个典型的2812 DSP应用系统如图8-1所示。

如果不包括外部扩展的存储器等芯片,就构成一个单片DSP系统(Single Chip Solution),即DSP最小系统。

除DSP芯片外,最小系统主要包括电源电路、时钟电路、复位电路、JTAG接口电路、通信接口驱动电路与应用电路等。

根据需要,还可以扩展外部存储器、D/A转换器等电路。

图8-1 2812 DSP系统1. 电源电路2812 DSP系统至少需要两组电源供电,内核电源VDD为1.8V(或1.9V),片内外设电源VDDIO为3.3V。

2812 DSP的Flash编程电压VDD3VFL、ADC模拟电路电源VDDA1、VDDA2也为3.3V,有时需要独立的模拟电源。

一般3.3V、1.8V电源可以通过对5V电源进行变换得到。

常用的电源芯片如表8-1所示。

表8-1常用的电源芯片型号规格备注TPS767D318PWP 1.8V 3.3V 1A 双电压输出+3.3V和+1.8V253254TPS767D301PWP 1.5~5.5V 可调 3.3V 1A 双电压输出+3.3V 和可调TPS7133Q 3.3 V 0.5A 单电压输出+3.3V TPS7233Q 3.3 V 0.25A 单电压输出+3.3V TPS7333Q 3.3 V 0.5A 单电压输出+3.3V TPS76801Q1.8 V 1A单电压输出+1.8V3.3V 、1.8V 电源可以通过一个芯片TPS767D318PWP 得到,也可以分别采用两个芯片TPS7333Q 与TPS76801Q 实现。

图8-2为一个采用TPS767D318芯片的电源电路。

图8-2采用TPS767D318芯片的DSP 电源电路2. 时钟电路2812 DSP 的时钟电路有内部振荡器方式和外部振荡器方式两种,即无源晶振和有源晶振方式。

有源晶振驱动能力较强,频率范围很宽,在1Hz~400MHz 之间。

无源晶体价格便宜,但是它的驱动能力较差,一般不能提供给多个器件共享,且频率范围较窄,一般在10kHz~60MHz 之间。

2812 DSP 的时钟电路如图8-3所示,可以选择30MHz 的振荡频率,通过内部锁相环实现5倍频,实现150MHz 的CPU 系统时钟。

注意应选择1.8V 供电的有源晶振,这样其输出端可以与DSP 的X1/XCLKIN 直接相连。

X1/XCLKIN 为振荡器输入信号,X2为振荡器输出信号。

图8-3(a)为无源振荡时钟电路,图中的电容C1、C2可取20~30pF 。

图8-3(b)为有源晶体振荡时钟电路,此时不使用DSP 的内部振荡器,时钟来自于X1/XCLKIN 输入的外部时钟信号,X2引脚悬空。

255(a) 内部振荡器方式(b) 外时钟源方式X1/XCLKINX2C1C230MHzDSP图8-3 2812 DSP 时钟电路3. 复位电路可靠的复位电路是DSP 系统必不可少的。

2812 DSP 为低电平复位。

由于内部有复位电路,所以直接在复位引脚接一个10k Ω的上拉电阻即可。

通常的复位电路设计有RC 电路法和专用芯片法。

图8-4为RC 复位电路,图中的74LVT14非门起到抗干扰的作用。

图8-4 RC 复位电路图8-5为采用芯片MAX811的复位电路。

MAX811主要用于处理器电源电压监测,在上电和电源电压超限时产生复位信号。

芯片的3脚为手动复位输入,该引脚为低时,会在2脚产生一个复位输出,复位输出信号一直有效,直到MR 引脚变为高电平180ms 后才变为高电平。

MAX811图8-5 MAX811复位电路另外,图8-2给出的电源芯片TPS767D318也具有复位输出引脚,可直接用于DSP 复位。

4. JTAG接口对DSP的仿真调试需要通过仿真器进行,仿真器通过DSP芯片提供的扫描仿真(JTAG)引脚实现仿真功能。

DSP仿真头采用14根信号线,符合JTAG IEEE1149.1标准。

图8-6给出了DSP的仿真接口电路。

其中的信号EMU0、EMU1引脚通常接5.1kΩ的上拉电阻,电源信号PD(Vcc)连接+5V,用于给仿真器提供信号电源,引脚6不接,用于仿真头定位。

图8-6 JTAG仿真接口5. 存储器扩展2812 DSP片内有4M字(Word, W)存储器地址空间,有128K字的Flash存储器、1K 字的OTP型ROM、18K字RAM、4K字的引导(Boot) ROM。

用户程序可以烧写入128K字的Flash存储器,但在开发调试过程中,程序需要不断修改,反复写入Flash存储器显得不方便。

可以将被调试的程序放入片内18K字RAM。

18K字片内RAM包括1KW的M0(0000~03FFH)、1KW的M1(0400~07FFH)、4KW的L0(8000~8FFFH)、4KW的L1(9000~9FFFH)和8KW的H0(3F 8000~3F BFFFH)。

由于DSP 越来越多地采用C语言编程,程序占用存储器较大,所以往往扩展片外RAM存储器用于程序调试。

在开发阶段,将程序放入RAM存储器(称为仿真RAM),可以方便地进行单步执行、设置断点及连续执行等调试操作。

当然,扩展的片外RAM也可以用作数据存储器。

2812 DSP具有1M+32K字的外部存储器(包括外部I/O)空间、可编程软件等待状态、三个独立的片选。

2812外部存储器接口(XINTF)有关的引脚为(1) 19根外部地址总线XA18~XA0。

(2) 16根外部数据总线XD15~XD0。

(3) 微处理器/微计算机方式选择信号MCXMP/。

该引脚为高电平时,为微处理器方式,外部存储器接口Zone7区使能;低电平时为微计算机方式,外部存储器接口空间Zone7区禁止,可以直接访问片内引导ROM。

(4) 外部DMA保持请求信号XHOLD。

该引脚为低电平时,请求XINTF释放外部总线,并将所有的总线和片选信号都置为高阻态。

256(5) 外部DMA保持应答信号XHOLDA。

当XINTF已经应答了XHOLD的请求信号时,XHOLDA有效(低电平)。

所有的XINTF总线和片选信号将变为高阻态。

(6) XINTF的Zone0和Zone1区选择信号XZCS0AND1。

该信号为低电平时,允许访问XINTF的Zone0和Zone1区。

(7) XINTF的Zone2区选择信号XZCS2。

该信号为低电平时,允许访问Zone2区。

(8) XINTF的Zone6和Zone7区选择信号XZCS6AND7。

该信号为低电平时,允许访问Zone6和Zone7区。

(9) 写使能信号XWE。

低电平有效的写选通信号。

写信号波形以每一个区为基础,通过寄存器XTIMINGx(x=0,1,2,6,7)设定。

(10) 读使能信号XRD。

低电平有效的读选通信号。

读信号波形以每一个区为基础,通过XTIMINGx寄存器设定。

(11) 读/写选择信号WXR/。

正常情况下为高电平。

为低电平时表示写有效;为高电平时表示读有效。

(12) 准备好信号XREADY。

当为高电平时,表示外设模块已经做好了访问的准备。

2812 DSP的最小指令周期为6.67ns(150MHz),为了不影响系统访问外部存储器的速度,通常选择存取时间快的RAM芯片,以提高系统的工作速度。

表8-2给出了一些高速RAM芯片的指标。

表8-2部分高速RAM芯片及其指标器件型号存储容量引脚封装速度/ns 公司电源电压/V TC55V1664 64KW 44 SOJ 15~17 Toshiba 3.3IS61LV6416 64KW 44 TSOP 8~12 ISSI 3.3 CY7C1021V33 64KW 44 SOJ/TSOP 10~15 Cypress 3.3 CY7C1041V33 256KW 44 SOJ/TSOP 10~15 Cypress 3.3IS61C6416 64KW 44 SOJ/TSOP 10~20 ISSI 5CY7C1021 64KW 44 SOJ/TSOP 10~20 Cypress 5IDT71016 64KW 44 SOJ/TSOP 12~20 IDT 5片外存储器存取速度达不到高速的CPU时序要求时,可以采用软件设置时序寄存器XTIMINGx(x=0,1,2,6,7)配置等待状态,也可以由外部存储器通过控制XREADY信号来实现对访问时序的匹配。

图8-7为扩展64KW (1片IS61LV6416,64K×16)存储器电路图。

257图8-7 DS P存储器扩展扩展存储器的地址为0x80000~0x8FFFF。

由于该电路地址关系简单,所以选择了74系列逻辑电路。

如果需要较复杂的系统扩展,例如进一步扩展A/D、D/A电路、LCD显示电路等,可以采用74138译码器、PAL、GAL可编程逻辑电路、CPLD、FPGA电路等进行译码。

采用CPLD、FPGA的优点是可以单片实现复杂的逻辑功能,且保密性好,缺点是功耗较大,增加了系统的复杂性。

6. 其他电路扩展(1) 电平转换电路。

DSP的工作电压为3.3V、1.8V,而目前仍有许多5V电源的逻辑器件,因此有的系统会有3.3V逻辑器件和5V逻辑器件共存。

3.3V的DSP芯片与5V供电芯片一般可以直接连接,但在3.3V低电压器件(LVTTL, LVCMOS)驱动5V CMOS器件的情况下,无法满足后者高电平的最小输入电压3.5V的要求,所以3.3V DSP器件不能直接驱动5V CMOS器件。

这种情况下可以采用专门的电平转换芯片如SN74LVC164245、SN74LVC4245。

这类芯片采用双电压供电,一边是3.3V供电,另一边是5V供电,可以解决3.3V器件与5V CMOS器件的电平转换问题。

另外,I/O接口经常通过光电耦合器件实现电压隔离与电平转换。

(2) RS-232接口、CAN接口驱动电路。

(3) 串行接口的芯片。

DSP可以扩展许多采用I2C, SPI接口的芯片。

采用不带外部并行总线接口(XINTF)的DSP芯片如2810, 可以见减少芯片引脚数量,提高可靠性。