1790445中文资料

UPA1790资料

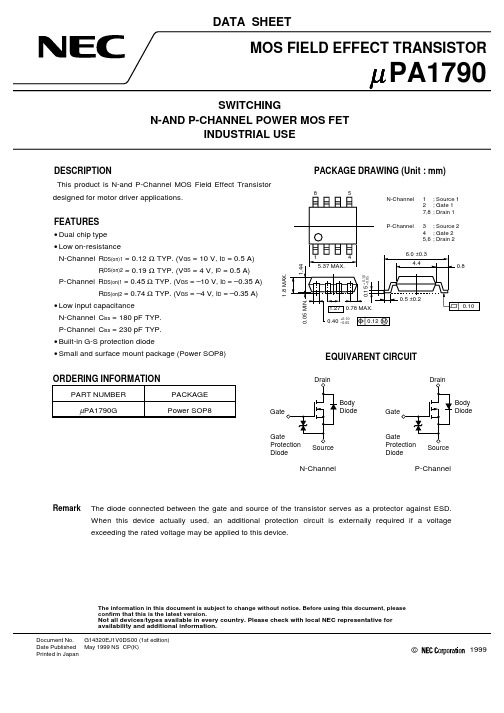

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.DATA SHEETDocument No.G14320EJ1V0DS00 (1st edition)DESCRIPTIONThis product is N-and P-Channel MOS Field Effect Transistor designed for motor driver applications.FEATURES•Dual chip type •Low on-resistanceN-Channel R DS(on)1 = 0.12 Ω TYP. (V GS = 10 V, I D = 0.5 A)R DS(on)2 = 0.19 Ω TYP. (V GS = 4 V, I D = 0.5 A)P-Channel R DS(on)1 = 0.45 Ω TYP. (V GS = –10 V, I D = –0.35 A)R DS(on)2 = 0.74 Ω TYP. (V GS = –4 V, I D = –0.35 A)•Low input capacitance N-Channel C iss = 180 pF TYP.P-Channel C iss = 230 pF TYP.•Built-in G-S protection diode•Small and surface mount package (Power SOP8)ORDERING INFORMATIONPART NUMBERPACKAGE µPA1790GPower SOP8Remark The diode connected between the gate and source of the transistor serves as a protector against ESD.When this device actually used, an additional protection circuit is externally required if a voltage exceeding the rated voltage may be applied to this device.PACKAGE DRAWING (Unit : mm)1.8 MA X .EQUIVARENT CIRCUITBody DiodeDiodeDiodeP-ChannelN-ChannelABSOLUTE MAXIMUM RATINGS (T A = 25°C, All terminals are connected.)PARAMETER SYMBOL N-CHANNEL P-CHANNEL UNIT Drain to Source Voltage (V GS = 0 V)V DSS60–60V Gate to Source Voltage (V DS = 0 V)V GSS±20#20V Drain Current (DC)I D(DC)±1.0#0.7A Drain Current (pulse) Note1I D(pulse)±4.0#2.8A Total Power Dissipation (1 unit) Note2P T 1.7W Total Power Dissipation (2 unit) Note2P T 2.0W Channel Temperature T ch150°C Storage Temperature T stg–55 to +150°CNotes1.PW ≤ 10 µs, Duty Cycle ≤ 1 %2.Mounted on ceramic substrate of 2000mm2 x 2.25mm23ELECTRICAL CHARACTERISTICS (T A = 25 °C, All terminals are connected.)N-CHANNELCHARACTERISTICSSYMBOL TEST CONDITIONSMIN.TYP.MAX.UNIT Drain to Source On-state ResistanceR DS(on)1V GS = 10 V, I D = 0.5 A 0.120.26ΩR DS(on)2V GS = 4 V, I D = 0.5 A 0.190.34ΩGate to Source Cut-off Voltage V GS(off)V DS = 10 V, I D = 1 mA 1.0 1.7 2.5V Forward Transfer Admittance | yfs |V DS = 10 V, I D = 0.5 A1.0 1.7SDrain Leakage CurrentI DSS V DS = 60 V, V GS = 0 V 10µA Gate to Source Leakage Current I GSS V GS = ±16 V, V DS = 0 V ±10µA Input Capacitance C iss V DS = 10 V 180pF Output CapacitanceC oss V GS = 0 V 100pF Reverse Transfer Capacitance C rss f = 1 MHz 35pF Turn-on Delay Time t d(on)ID = 0.5 A 1ns Rise Timet r V GS(on) = 10 V 1.4ns Turn-off Delay Time t d(off)V DD = 30 V 23ns Fall Timet f R G = 10 Ω17ns Total Gate Charge Q G I D = 1.0 A 8nC Gate to Source Charge Q GS V DD = 48 V 1nC Gate to Drain Charge Q GD V GS = 10 V3.5nC Body Diode Forward Voltage V F(S-D)I F = 1.0 A, V GS = 0 V 0.75V Reverse Recovery Time t rr I F = 1.0 A, V GS = 0 V 30ns Reverse Recovery ChargeQ rrdi/dt = 100 A / µs33nCTEST CIRCUIT 1 SWITCHING TIMETEST CIRCUIT 2 GATE CHARGEPG.V LDDτ = 1 s µDuty Cycle ≤ 1 %PG.L DD4CHARACTERISTICSSYMBOL TEST CONDITIONSMIN.TYP.MAX.UNIT Drain to Source On-state ResistanceR DS(on)1V GS = –10 V, I D = –0.35 A 0.450.6ΩR DS(on)2V GS = –4 V, I D = –0.35 A 0.74 1.1ΩGate to Source Cut-off Voltage V GS(off)V DS = –10 V, I D = –1 mA –1.0–1.7–2.5V Forward Transfer Admittance | yfs|V DS = –10 V, I D= –0.35 A 5.0SDrain Leakage CurrentI DSS V DS = –60 V, V GS = 0 V –10µA Gate to Source Leakage Current I GSS V GS = #16 V, V DS = 0 V #10µA Input Capacitance C iss V DS = –10 V 230pF Output CapacitanceC oss V GS = 0 V 100pF Reverse Transfer Capacitance C rss f = 1 MHz 25pF Turn-on Delay Time t d(on)ID = –0.35 A 1.9ns Rise Timet r V GS(on) = –10 V 1.7ns Turn-off Delay Time t d(off)V DD = –30 V 30ns Fall Timet f R G = 10 Ω15ns Total Gate Charge Q G I D = –0.7 A 7.6nC Gate to Source Charge Q GS V DD = –48 V 1nC Gate to Drain Charge Q GD V GS = –10 V 2nC Body Diode Forward Voltage V F(S-D)I F = 0.7 A, V GS = 0 V 0.85V Reverse Recovery Time t rr I F = 0.7 A, V GS = 0 V 58ns Reverse Recovery ChargeQ rrdi/dt = 100 A / µs130nCTEST CIRCUIT 1 SWITCHING TIMETEST CIRCUIT 2 GATE CHARGEPG.V LDDτ = 1 s µDuty Cycle ≤ 1 %PG.L DD567• The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.• No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.• NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual propertyrights of third parties by or arising from use of a device described herein or any other liability arising from useof such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or otherintellectual property rights of NEC Corporation or others.• Descriptions of circuits, software, and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits,software, and information in the design of the customer's equipment shall be done under the full responsibilityof the customer. NEC Corporation assumes no responsibility for any losses incurred by the customer or third parties arising from the use of these circuits, software, and information.• While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices,the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons orproperty arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.• NEC devices are classified into the following three quality grades:"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on acustomer designated "quality assurance program" for a specific application. The recommended applications ofa device depend on its quality grade, as indicated below. Customers must check the quality grade of each devicebefore using it in a particular application.Standard: Computers, office equipment, communications equipment, test and measurement equipment,audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robotsSpecial: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disastersystems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)Specific: Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, lifesupport systems or medical equipment for life support, etc.The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.M7 98. 8。

HA17904AFP中文资料

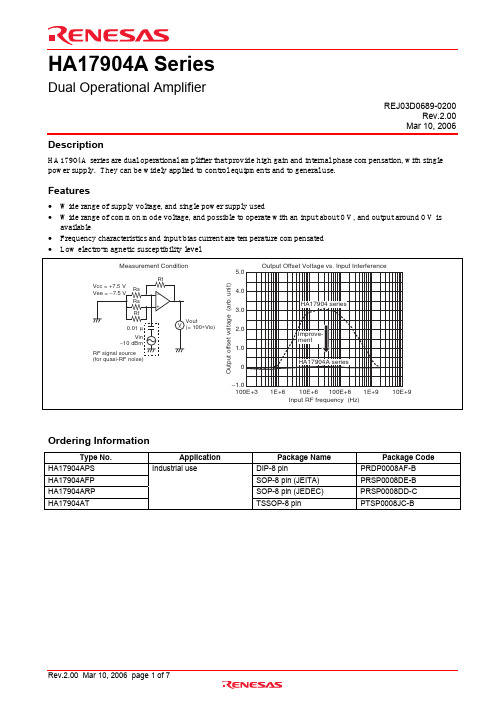

HA17904A SeriesDual Operational AmplifierREJ03D0689-0200Rev.2.00 Mar 10, 2006DescriptionHA17904A series are dual operational amplifier that provide high gain and internal phase compensation, with single power supply. They can be widely applied to control equipments and to general use.Features• Wide range of supply voltage, and single power supply used• Wide range of common mode voltage, and possible to operate with an input about 0 V, and output around 0 V is available• Frequency characteristics and input bias current are temperature compensated • Low electro-magnetic susceptibility levelOrdering InformationType No. Application Package Name Package CodeHA17904APS DIP-8 pin PRDP0008AF-B HA17904AFP SOP-8 pin (JEITA) PRSP0008DE-B HA17904ARP SOP-8 pin (JEDEC) PRSP0008DD-C HA17904AT Industrial use TSSOP-8 pinPTSP0008JC-BPin ArrangementCircuit Schematic (1/2)Note: If Input/Output terminals voltage over the absolute maximum ratings, there is possibility of mis-operation, characteristics deterioration and destruction, because of the current’s flowing to parasitic diode in IC.The Input/Output terminals are recommended to be protected with the clamp circuit which using the diode with low forward voltage (like schottky barrier diode) when there is a possibility for the Input/Output terminalsvoltage exceeds the absolute maximum ratings.Absolute Maximum Ratings(Ta = 25°C)Item Symbol Ratings UnitPower supply voltage V CC 32 V Output sink current Iosink 50 mA Common mode input voltage V CM −0.3 to +V CC V Differential input voltage Vin(diff) ±V CC V Output voltage Vout −0.3 to +V CC V DIP 570 *1 SOP 385 *2 Allowable power dissipation TSSOP P T 192 *3mWOperating temperature Topr −40 to +85 °C Storage temperature Tstg −55 to +125 °C Notes: 1. HA17904APS:This is the allowable values up to Ta = 50°C. Derate by 8.3 mW/°C.2. HA17904AFP/ARP:These are the allowable values up to Ta = 25°C mounting in air.When it is mounted on glass epoxy board of 40 mm × 40 mm × 1.5 mmt with 30% wiring density, the allowable value is 570 mW up to Ta = 45°C. If Ta > 45°C, derate by 7.14 mW/°C.3. HA17904AT:These are the allowable values up to Ta = 25°C. Derate by 1.92 mW/°C above that temperature.Electrical Characteristics(V CC = +15 V, Ta = 25°C)Item Symbol Min Typ Max Unit Test ConditionsInput offset voltage V IO — 3 7 mV V CM = 7.5V, R S = 50Ω, Rf = 50k Ω Input offset current I IO — 5 50 nA V CM = 7.5V, I IO = | I I (+) – I I (–) | Input bias current I IB — 30 250nA V CM = 7.5V Power source rejection ratio PSRR — 93 — dB R S = 1k Ω, Rf = 100k Ω Voltage gain A VD 75 90 — dB R L = ∞, R S = 1k Ω, Rf = 100k Ω Common mode rejection ratio CMR — 80 — dB R S = 50Ω, Rf = 5k Ω V CM (+) 13.5— — V R S = 1k Ω, Rf = 100k ΩCommon mode input voltage range V CM (–) — — –0.3V R S = 1k Ω, Rf = 100k ΩPeak-to-peak output voltage V OP-P — 13.6— V f = 100Hz, R L = 20k Ω, R S = 1k Ω,Rf = 100k ΩOutput source current Iosource 20 40 — mA V IN + = 1V, V IN – = 0V, V OH = 10V 10 20 — mA V IN – = 1V, V IN + = 0V, V OL = 2.5VOutput sink current Iosink 15 50 — µA V IN – = 1V, V IN + = 0V, Vout = 200mV Supply current I CC — 0.8 2 mA V IN = GND, R L = ∞ Slew rateSR — 0.2 — V/µs R L = ∞, V CM = 7.5V, f = 1.5kHz Channel separation *1 CS — (120)— dB f = 1kHzNote: 1. Design spec.Characteristic CurvesPackage Dimensions RENESAS SALES OFFICESRefer to "/en/network" for the latest and detailed information.Renesas Technology America, Inc.450 Holger Way, San Jose, CA 95134-1368, U.S.ATel: <1> (408) 382-7500, Fax: <1> (408) 382-7501Renesas Technology Europe LimitedDukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900Renesas Technology (Shanghai) Co., Ltd.Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7898Renesas Technology Hong Kong Ltd.7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong KongTel: <852> 2265-6688, Fax: <852> 2730-6071Renesas Technology Taiwan Co., Ltd.10th Floor, No.99, Fushing North Road, Taipei, TaiwanTel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999Renesas Technology Singapore Pte. Ltd.1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632Tel: <65> 6213-0200, Fax: <65> 6278-8001Renesas Technology Korea Co., Ltd.Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, KoreaTel: <82> (2) 796-3115, Fax: <82> (2) 796-2145Renesas Technology Malaysia Sdn. BhdUnit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, MalaysiaTel: <603> 7955-9390, Fax: <603> 7955-9510© 2006. Renesas Technology Corp., All rights reserved. Printed in Japan.。

1754478中文资料

Extract from the onlinecatalogMSTB 2,5/ 4-GOrder No.: 1754478The figure shows a 10-position version of the producthttp://eshop.phoenixcontact.de/phoenix/treeViewClick.do?UID=1754478Header, nominal current: 12 A, rated voltage: 250 V, pitch: 5.0 mm, no. of positions: 4, mounting: Solderinghttp://Please note that the data givenhere has been taken from theonline catalog. For comprehensiveinformation and data, please referto the user documentation. TheGeneral Terms and Conditions ofUse apply to Internet downloads. Technical dataDimensions / positionsPitch 5 mmDimension a15 mmNumber of positions4Pin dimensions 1 x 1 mmHole diameter 1.4 mmTechnical dataInsulating material group IIIaRated surge voltage (III/3) 4 kVRated surge voltage (III/2) 4 kVRated surge voltage (II/2) 4 kVRated voltage (III/2)320 VRated voltage (II/2)400 VConnection in acc. with standard EN-VDENominal current I N12 ANominal voltage U N250 VMaximum load current12 AInsulating material PBTInflammability class acc. to UL 94V0Certificates / ApprovalsApproval logoCSANominal voltage U N300 VNominal current I N10 ACULNominal voltage U N300 VNominal current I N10 AULNominal voltage U N300 VNominal current I N10 ACertification CB, CSA, CUL, GOST, UL, VDE-PZIAccessoriesItem Designation DescriptionAssembly1759981MSTB-BF Mounting flange, for fixing both ends of the header onto the PCB,green insulating material, with M 2 x 14 screws and nuts.1755477MSTB-BL Keying cap, for forming sections, plugs onto header pin, greeninsulating materialMarking0804183SK 5/3,8:FORTL.ZAHLEN Marker card, printed horizontally, self-adhesive, 12 identicaldecades marked 1-10, 11-20 etc. up to 91-(99)100, sufficient for120 terminal blocksPlug/Adapter1734401CR-MSTB Coding section, inserted into the recess in the header or theinverted plug, red insulating materialAdditional productsItem Designation DescriptionAssembly1909236FKCT 2,5/ 4-ST Plug component, nominal current: 12 A, rated voltage: 250 V,pitch: 5.0 mm, no. of positions: 4, type of connection: Spring-cageconnection1779851MSTBT 2,5/ 4-ST Plug, nominal current: 12 A, rated voltage: 250 V, pitch: 5 mm, no.of positions: 4, type of connection: screw connectionGeneral1910377FKC 2,5/ 4-ST Plug component, nominal current: 12 A, rated voltage: 250 V,pitch: 5.0 mm, no. of positions: 4, type of connection: Spring-cageconnection1909731FKCVR 2,5/ 4-ST Plug component, nominal current: 12 A, rated voltage: 250 V,pitch: 5.0 mm, no. of positions: 4, type of connection: Spring-cageconnection1910050FKCVW 2,5/ 4-ST Plug component, nominal current: 12 A, rated voltage: 250 V,pitch: 5.0 mm, no. of positions: 4, type of connection: Spring-cageconnection1779437FRONT-MSTB 2,5/ 4-ST Plug component, nominal current: 12 A, rated voltage: 250 V,pitch: 5.0 mm, no. of positions: 4, type of connection: Screwconnection1754481MSTB 2,5/ 4-ST Plug component, nominal current: 12 A, rated voltage: 250 V,pitch: 5.0 mm, no. of positions: 4, type of connection: Screwconnection1765797MSTBP 2,5/ 4-ST Plug component, nominal current: 12 A, rated voltage: 250 V,pitch: 5.0 mm, no. of positions: 4, type of connection: Screwconnection1792032MVSTBR 2,5/ 4-ST Plug component, nominal current: 12 A, rated voltage: 250 V,pitch: 5.0 mm, no. of positions: 4, type of connection: Screwconnection1792540MVSTBW 2,5/ 4-ST Plug component, nominal current: 12 A, rated voltage: 250 V,pitch: 5.0 mm, no. of positions: 4, type of connection: Screwconnection1768781SMSTB 2,5/ 4-ST Plug component, nominal current: 12 A, rated voltage: 250 V,pitch: 5.0 mm, no. of positions: 4, type of connection: ScrewconnectionDrawingsDrilling diagramDimensioned drawingAddressPHOENIX CONTACT GmbH & Co. KGFlachsmarktstr. 832825 Blomberg,GermanyPhone +49 5235 3 00Fax +49 5235 3 41200http://www.phoenixcontact.de© 2008 Phoenix ContactTechnical modifications reserved;。

1-747945-5中文资料

1-747945-5 Product DetailsHome | Customer Support | Suppliers | Site Map | Privacy Policy | Browser Support© 2008 Tyco Electronics Corporation All Rights Reserved SearchProducts Documentation Resources My Account Customer Support Home > Products > By Type > D Subminiature > Product Feature Selector > Product Details1-747945-5Active Standard Cable ConnectorsAlways EU RoHS/ELV Compliant (Statement of Compliance)Product Highlights:?Connector Kit?Product Series = HDE-20 (IDC)?Number of Positions = 15?Shielded?ReceptacleView all Features | Find SimilarProductsCheck Pricing &AvailabilitySearch for ToolingView MatingProducts (88)Product FeatureSelectorContact Us AboutThis ProductQuick LinksDocumentation & Additional InformationProduct Drawings:?SHIELDING ENCLOSURE KIT, RCPT, SIZE 2, 15 POSN, AMPL...(PDF, English)Catalog Pages/Data Sheets:?None AvailableProduct Specifications:?Connector, AMPLIMITE HDE-20, Insulation Displacement(PDF, English)?Connector, AMPLIMITE, Shielding Hardware(PDF, English) Application Specifications:?AMPLIMITE HDE-20 IDC Connectors(PDF, English)?AMPLIMITE HDE-20 Shielding Hardware Kits With and Wi...(PDF, English)Instruction Sheets:?AMPLIMITE High Den. (HDE-20) Insulation Displacement...(PDF, English)?Shielding Hardware Enc Kits w/AMPLIMITE HDE-20 HDP-2...(PDF, English)CAD Files:?None AvailableList all Documents Additional Information:?Product Line InformationRelated Products:?Tooling?Mating Products (88)Product Features (Please use the Product Drawing for all design activity)Product Type Features:?Product Type = Connector Kit?Product Series = HDE-20 (IDC)?Number of Positions = 15?Shielded = Yes?Gender = Receptacle?Wire/Cable Type = Discrete Wire, RoundJacketed Cable?Wire Termination Type = InsulationDisplacement Crimp (IDC)?Wire Insulation Diameter (mm [in]) = 1.52[0.060]?Mating Connector Lock = With?Mating Connector Lock Type = Jackscrews?Shell Size = 2?Shell Type = Front Metal Shell?Grounding Indents = Without?Insulation Support = Yes?Grade = Standard?Enclosure Material = PVC?Jackscrew Material = Zinc Alloy?Color = Black?Shell Material = Steel?Shield Material = Steel?Comment = Maximum cable diameter afterjacket and braid removed.; There is a maximumCable O.D. of 9.02 [.355] for ShieldingEnclosure Expansion Tool 58241-4. Termination Related Features:?Solder Tail Contact Plating = Tin over Nickel Body Related Features:?Wire Range (mm²[AWG]) = 0.05 -0.15 [30-26]?Pre-Assembled = No?Cable Insulation Diameter (mm [in]) = 4.83 –9.53 [0.190 –0.375]?Shell Plating = Tin?Shield Plating = Tin?Insert Material = Thermoplastic?Insert Flammability Rating = UL 94V-0?Cable Diameter (Max.) (mm [in]) = 9.53[0.375]Contact Related Features:?Contacts = With?Contact Mating Area Plating Material = Gold(30)?Contact Size = 20?Contact Material = Phosphor BronzeIndustry Standards:?RoHS/ELV Compliance = RoHS compliant, ELVcompliant?Lead Free Solder Processes = Not relevant forlead free process?RoHS/ELV Compliance History = Always wasRoHS compliantPackaging Related Features:?Packaging Method = BulkOther:?Brand = AMPProvide Website Feedback | Contact Customer Support。

HA17903AFP中文资料

Vin

1V

0.01 µF −10 dBm RF signal source (for quasi-RF noise)

6.0 5.0 4.0

Vout (V)

HA17903 Vout vs. Vin

3.0 2.0 1.0 0.0 −1.0 0.85 0.90 0.95 1.00 Vin (V) HA17903 (0 Hz) HA17903 (10 MHz) HA17903 (100 MHz) 1.05 1.10 1.15

Rev.1.00 Mar 10, 2006 page 2 of 8

元器件交易网

HA17903A Series

Pin Arrangement

Vout1 Vin(−)1 Vin(+)1 1 1 − + 2 + − 8 VCC Vout2 Vin(−)2 Vin(+)2

2

7

3

Rev.1.00 Mar 10, 2006 page 1 of 8

元器件交易网

HA17903A Series • Low electro-magnetic susceptibility

Measurement Condition

Vcc = 5 V 1k 1k + − Vcc 5.1 kΩ

Electrical Characteristics

(VCC = 5 V, Ta = 25°C)

Item Input offset voltage *1 Input offset current Input bias current *2 Common mode input voltage *3 Symbol Min Typ Max Unit Test Conditions VIO 2 5 mV IIO 3 50 nA IIN (+) − IIN (−) IIB 25 250 nA IIN (+) or IIN (−) + VCM 3.5 V VCM− 0 V Supply current ICC 0.8 2.0 mA All comparators: RL = ∞, All channels on 5 Voltage gain * AVD (200) V/mV VCC = 15V, RL ≥ 15kΩ Response time *4,5 tR (1.3) µs VRL = 5V, RL = 5.1kΩ 5 Large signal response time * tRI (300) ns VIN = TTL Threshold width, VREF = 1.4V Output sink current IO(sink) 6 16 mA VIN (−) ≥ 1V, VIN (+) = 0, VO ≤ 1.5V Output saturation voltage VO(sat) 400 mV VIN (−) ≥ 1V, VIN (+) = 0, Iosink = 4mA Output leak current *5 ILO (0.1) nA VIN (−) = 0, VIN (+) ≥ 1V, VO = 5V Notes: 1. VREF = 1.4 V and RS = 50 Ω, when VO = 1.4 V at output switching point. 2. Under linear operation. 3. Common mode input voltage or each one of the input signal should not be less than −0.3 V. 4. This is a value to 100 mV input step voltage with 5 mV over drive. 5. Design spec.

XCS05XL-4PC144I中文资料

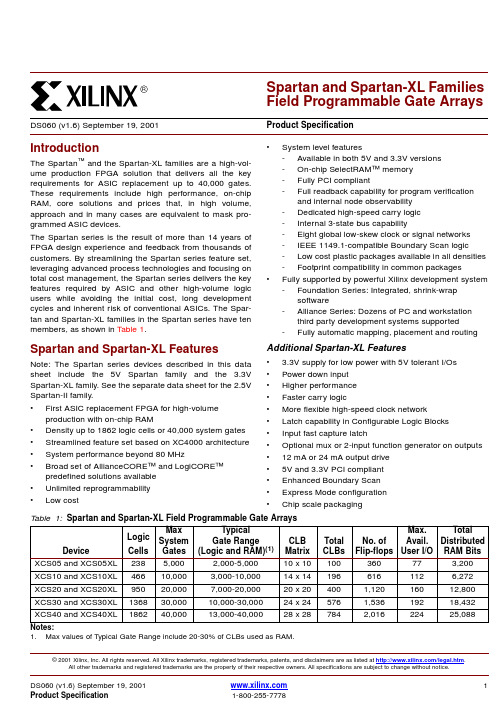

© 2001 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at /legal.htm .All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.IntroductionThe Spartan ™ and the Spartan-XL families are a high-vol-ume production FPGA solution that delivers all the key requirements for ASIC replacement up to 40,000 gates.These requirements include high performance, on-chip RAM, core solutions and prices that, in high volume,approach and in many cases are equivalent to mask pro-grammed ASIC devices.The Spartan series is the result of more than 14 years of FPGA design experience and feedback from thousands of customers. By streamlining the Spartan series feature set,leveraging advanced process technologies and focusing on total cost management, the Spartan series delivers the key features required by ASIC and other high-volume logic users while avoiding the initial cost, long development cycles and inherent risk of conventional ASICs. The Spar-tan and Spartan-XL families in the Spartan series have ten members, as shown in T able 1.Spartan and Spartan-XL FeaturesNote: The Spartan series devices described in this data sheet include the 5V Spartan family and the 3.3V Spartan-XL family. See the separate data sheet for the 2.5V Spartan-II family.•First ASIC replacement FPGA for high-volume production with on-chip RAM•Density up to 1862 logic cells or 40,000 system gates •Streamlined feature set based on XC4000 architecture •System performance beyond 80MHz•Broad set of AllianceCORE ™ and LogiCORE ™ predefined solutions available •Unlimited reprogrammability •Low cost•System level features-Available in both 5V and 3.3V versions -On-chip SelectRAM ™ memory -Fully PCI compliant-Full readback capability for program verificationand internal node observability -Dedicated high-speed carry logic -Internal 3-state bus capability-Eight global low-skew clock or signal networks -IEEE 1149.1-compatible Boundary Scan logic -Low cost plastic packages available in all densities -Footprint compatibility in common packages•Fully supported by powerful Xilinx development system -Foundation Series: Integrated, shrink-wrapsoftware-Alliance Series: Dozens of PC and workstationthird party development systems supported-Fully automatic mapping, placement and routing Additional Spartan-XL Features• 3.3V supply for low power with 5V tolerant I/Os •Power down input •Higher performance •Faster carry logic•More flexible high-speed clock network•Latch capability in Configurable Logic Blocks •Input fast capture latch•Optional mux or 2-input function generator on outputs •12 mA or 24 mA output drive •5V and 3.3V PCI compliant •Enhanced Boundary Scan •Express Mode configuration •Chip scale packagingSpartan and Spartan-XL Families Field Programmable Gate ArraysDS060 (v1.6) September 19, 2001Product Specification T able 1: Spartan and Spartan-XL Field Programmable Gate Arrays1.Max values of Typical Gate Range include 20-30% of CLBs used as RAM.2DS060 (v1.6) September 19, 2001General OverviewSpartan series FPGAs are implemented with a regular, flex-ible, programmable architecture of Configurable Logic Blocks (CLBs), interconnected by a powerful hierarchy of versatile routing resources (routing channels), and sur-rounded by a perimeter of programmable Input/Output Blocks (IOBs), as seen in Figure 1. They have generous routing resources to accommodate the most complex inter-connect patterns.The devices are customized by loading configuration data into internal static memory cells. Re-programming is possi-ble an unlimited number of times. The values stored in thesememory cells determine the logic functions and intercon-nections implemented in the FPGA. The FPGA can either actively read its configuration data from an external serial PROM (Master Serial mode), or the configuration data can be written into the FPGA from an external device (Slave Serial mode).Spartan series FPGAs can be used where hardware must be adapted to different user applications. FPGAs are ideal for shortening design and development cycles, and also offer a cost-effective solution for production rates well beyond 50,000 systems per month.Figure 1: Basic FPGA Block DiagramSpartan series devices achieve high-performance, low-cost operation through the use of an advanced architecture and semiconductor technology. Spartan and Spartan-XL devices provide system clock rates exceeding 80MHz and internal performance in excess of150MHz. In contrast to other FPGA devices, the Spartan series offers the most cost-effective solution while maintaining leading-edge per-formance. In addition to the conventional benefit of high vol-ume programmable logic solutions, Spartan series FPGAs also offer on-chip edge-triggered single-port and dual-port RAM, clock enables on all flip-flops, fast carry logic, and many other features.The Spartan/XL families leverage the highly successful XC4000 architecture with many of that family’s features and benefits. T echnology advancements have been derived from the XC4000XLA process developments.Logic Functional DescriptionThe Spartan series uses a standard FPGA structure as shown in Figure1, page2. The FPGA consists of an array of configurable logic blocks (CLBs) placed in a matrix of routing channels. The input and output of signals is achieved through a set of input/output blocks (IOBs) forming a ring around the CLBs and routing channels.•CLBs provide the functional elements for implementing the user’s logic.•IOBs provide the interface between the package pins and internal signal lines.•Routing channels provide paths to interconnect the inputs and outputs of the CLBs and IOBs.The functionality of each circuit block is customized during configuration by programming internal static memory cells. The values stored in these memory cells determine the logic functions and interconnections implemented in the FPGA.Configurable Logic Blocks (CLBs)The CLBs are used to implement most of the logic in an FPGA. The principal CLB elements are shown in the simpli-fied block diagram in Figure2. There are three look-up tables (LUT) which are used as logic function generators, two flip-flops and two groups of signal steering multiplexers. There are also some more advanced features provided by the CLB which will be covered in the Advanced Features Description, page13.Function GeneratorsTwo 16x1 memory look-up tables (F-LUT and G-LUT) are used to implement 4-input function generators, each offer-ing unrestricted logic implementation of any Boolean func-tion of up to four independent input signals (F1 to F4 or G1 to G4). Using memory look-up tables the propagation delay is independent of the function implemented.A third 3-input function generator (H-LUT) can implement any Boolean function of its three inputs. Two of these inputs are controlled by programmable multiplexers (see box "A" of Figure2). These inputs can come from the F-LUT or G-LUT outputs or from CLB inputs. The third input always comes from a CLB input. The CLB can, therefore, implement cer-tain functions of up to nine inputs, like parity checking. The three LUTs in the CLB can also be combined to do any arbi-trarily defined Boolean function of five inputs.4DS060 (v1.6) September 19, 2001A CLB can implement any of the following functions:•Any function of up to four variables, plus any second function of up to four unrelated variables, plus any third function of up to three unrelated variablesNote: When three separate functions are generated, one of the function outputs must be captured in a flip-flop internal to the CLB. Only two unregistered function generator outputs are available from the CLB.•Any single function of five variables•Any function of four variables together with some functions of six variables•Some functions of up to nine variables.Implementing wide functions in a single block reduces both the number of blocks required and the delay in the signal path, achieving both increased capacity and speed. The versatility of the CLB function generators significantly improves system speed. In addition, the design-software tools can deal with each function generator independently.This flexibility improves cell usage.Flip-FlopsEach CLB contains two flip-flops that can be used to regis-ter (store) the function generator outputs. The flip-flops and function generators can also be used independently (see Figure 2). The CLB input DIN can be used as a direct input to either of the two flip-flops. H1 can also drive either flip-flop via the H-LUT with a slight additional delay.The two flip-flops have common clock (CK), clock enable (EC) and set/reset (SR) inputs. Internally both flip-flops are also controlled by a global initialization signal (GSR) which is described in detail in Global Signals: GSR and GTS ,page 20.Latches (Spartan-XL only)The Spartan-XL CLB storage elements can also be config-ured as latches. The two latches have common clock (K)and clock enable (EC) inputs. Functionality of the storage element is described in Table 2.Figure 2: Spartan/XL Simplified CLB Logic Diagram (some features not shown)Clock InputEach flip-flop can be triggered on either the rising or falling clock edge. The CLB clock line is shared by both flip-flops.However, the clock is individually invertible for each flip-flop (see CK path in Figure 3). Any inverter placed on the clock line in the design is automatically absorbed into the CLB. Clock EnableThe clock enable line (EC) is active High. The EC line is shared by both flip-flops in a CLB. If either one is left discon-nected, the clock enable for that flip-flop defaults to the active state. EC is not invertible within the CLB. The clock enable is synchronous to the clock and must satisfy the setup and hold timing specified for the device.Set/ResetThe set/reset line (SR) is an asynchronous active High con-trol of the flip-flop. SR can be configured as either set or reset at each flip-flop. This configuration option determines the state in which each flip-flop becomes operational after configuration. It also determines the effect of a GSR pulse during normal operation, and the effect of a pulse on the SR line of the CLB. The SR line is shared by both flip-flops. If SR is not specified for a flip-flop the set/reset for that flip-flop defaults to the inactive state. SR is not invertible within the CLB.CLB Signal Flow ControlIn addition to the H-LUT input control multiplexers (shown in box "A" of Figure 2, page 4) there are signal flow control multiplexers (shown in box "B" of Figure 2) which select the signals which drive the flip-flop inputs and the combinatorial CLB outputs (X and Y).Each flip-flop input is driven from a 4:1 multiplexer which selects among the three LUT outputs and DIN as the data source.Each combinatorial output is driven from a 2:1 multiplexer which selects between two of the LUT outputs. The X output can be driven from the F-LUT or H-LUT, the Y output from G-LUT or H-LUT .Control SignalsThere are four signal control multiplexers on the input of the CLB. These multiplexers allow the internal CLB control sig-nals (H1, DIN, SR, and EC in Figure 2 and Figure 4) to be driven from any of the four general control inputs (C1-C4 in Figure 4) into the CLB. Any of these inputs can drive any of the four internal control signals.T able 2: CLB Storage Element FunctionalityLegend:XDon ’t careRising edge (clock not inverted).SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)Figure 3: CLB Flip-Flop Functional Block Diagram6DS060 (v1.6) September 19, 2001The four internal control signals are:•EC: Enable Clock•SR: Asynchronous Set/Reset or H function generator Input 0•DIN: Direct In or H function generator Input 2•H1: H function generator Input 1.Input/Output Blocks (IOBs)User-configurable input/output blocks (IOBs) provide the interface between external package pins and the internal logic. Each IOB controls one package pin and can be con-figured for input, output, or bidirectional signals. Figure 6shows a simplified functional block diagram of the Spar-tan/XL IOB.IOB Input Signal PathThe input signal to the IOB can be configured to either go directly to the routing channels (via I1 and I2 in Figure 6) or to the input register. The input register can be programmed as either an edge-triggered flip-flop or a level-sensitive latch. The functionality of this register is shown in Table 3,and a simplified block diagram of the register can be seen in Figure 5.Figure 4: CLB Control Signal InterfaceFigure 5: IOB Flip-Flop/Latch Functional BlockDiagramTable 3: Input Register FunctionalityX Don ’t care.Rising edge (clock not inverted).SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)The register choice is made by placing the appropriate library symbol. For example, IFD is the basic input flip-flop (rising edge triggered), and ILD is the basic input latch (transparent-High). Variations with inverted clocks are also available. The clock signal inverter is also shown in Figure5 on the CK line.The Spartan IOB data input path has a one-tap delay ele-ment: either the delay is inserted (default), or it is not. The Spartan-XL IOB data input path has a two-tap delay ele-ment, with choices of a full delay, a partial delay, or no delay. The added delay guarantees a zero hold time with respect to clocks routed through the global clock buffers. (See Glo-bal Nets and Buffers, page12 for a description of the glo-bal clock buffers in the Spartan/XL families.) For a shorter input register setup time, with positive hold-time, attach a NODELAY attribute or property to the flip-flop.The output of the input register goes to the routing channels (via I1 and I2 in Figure6). The I1 and I2 signals that exit the IOB can each carry either the direct or registered input signal.The 5V Spartan input buffers can be globally configured for either TTL (1.2V) or CMOS (VCC/2) thresholds, using an option in the bitstream generation software. The Spartan output levels are also configurable; the two global adjust-ments of input threshold and output level are independent. The inputs of Spartan devices can be driven by the outputs of any 3.3V device, if the Spartan inputs are in TTL mode. Input and output thresholds are TTL on all configuration pins until the configuration has been loaded into the device and specifies how they are to be used. Spartan-XL inputs are TTL compatible and 3.3V CMOS compatible. Supported sources for Spartan/XL device inputs are shown in Table4.Spartan-XL I/Os are fully 5V tolerant even though the V CC is 3.3V. This allows 5V signals to directly connect to the Spar-tan-XL inputs without damage, as shown in Table4. In addi-tion, the 3.3V V CC can be applied before or after 5V signals are applied to the I/Os. This makes the Spartan-XL devices immune to power supply sequencing problems.Figure 6: Simplified Spartan/XL IOB Block Diagram8DS060 (v1.6) September 19, 2001Spartan-XL V CC ClampingSpartan-XL FPGAs have an optional clamping diode con-nected from each I/O to V CC . When enabled they clamp ringing transients back to the 3.3V supply rail. This clamping action is required in 3.3V PCI applications. V CC clamping is a global option affecting all I/O pins.Spartan-XL devices are fully 5V TTL I/O compatible if V CC clamping is not enabled. With V CC clamping enabled, the Spartan-XL devices will begin to clamp input voltages to one diode voltage drop above V CC . If enabled, TTL I/O com-patibility is maintained but full 5V I/O tolerance is sacrificed.The user may select either 5V tolerance (default) or 3.3V PCI compatibility. In both cases negative voltage is clamped to one diode voltage drop below ground.Spartan-XL devices are compatible with TTL, LVTTL, PCI 3V, PCI 5V and LVCMOS signalling. The various standards are illustrated in Table 5.Additional Fast Capture Input Latch (Spartan-XL only)The Spartan-XL IOB has an additional optional latch on the input. This latch is clocked by the clock used for the output flip-flop rather than the input clock. Therefore, two different clocks can be used to clock the two input storage elements.This additional latch allows the fast capture of input data,which is then synchronized to the internal clock by the IOB flip-flop or latch.T o place the Fast Capture latch in a design, use one of the special library symbols, ILFFX or ILFLX. ILFFX is a trans-parent-Low Fast Capture latch followed by an active High input flip-flop. ILFLX is a transparent Low Fast Capture latch followed by a transparent High input latch. Any of the clock inputs can be inverted before driving the library element,and the inverter is absorbed into the IOB.IOB Output Signal PathOutput signals can be optionally inverted within the IOB,and can pass directly to the output buffer or be stored in an edge-triggered flip-flop and then to the output buffer. The functionality of this flip-flop is shown in T able 6.T able 4: Supported Sources for Spartan/XL InputsT able 5: I/O Standards Supported by Spartan-XL FPGAsTable 6: Output Flip-Flop Functionality X Don ’t careRising edge (clock not inverted). SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)Z3-stateOutput Multiplexer/2-Input Function Generator (Spartan-XL only)The output path in the Spartan-XL IOB contains an addi-tional multiplexer not available in the Spartan IOB. The mul-tiplexer can also be configured as a 2-input function generator, implementing a pass gate, AND gate, OR gate, or XOR gate, with 0, 1, or 2 inverted inputs.When configured as a multiplexer, this feature allows two output signals to time-share the same output pad, effec-tively doubling the number of device outputs without requir-ing a larger, more expensive package. The select input is the pin used for the output flip-flop clock, OK.When the multiplexer is configured as a 2-input function generator, logic can be implemented within the IOB itself. Combined with a Global buffer, this arrangement allows very high-speed gating of a single signal. For example, a wide decoder can be implemented in CLBs, and its output gated with a Read or Write Strobe driven by a global buffer. The user can specify that the IOB function generator be used by placing special library symbols beginning with the letter "O." For example, a 2-input AND gate in the IOB func-tion generator is called OAND2. Use the symbol input pin labeled "F" for the signal on the critical path. This signal is placed on the OK pin — the IOB input with the shortest delay to the function generator. Two examples are shown in Figure7.Output BufferAn active High 3-state signal can be used to place the out-put buffer in a high-impedance state, implementing 3-state outputs or bidirectional I/O. Under configuration control, the output (O) and output 3-state (T) signals can be inverted. The polarity of these signals is independently configured for each IOB (see Figure6, page7). An output can be config-ured as open-drain (open-collector) by tying the 3-state pin (T) to the output signal, and the input pin (I) to Ground.By default, a 5V Spartan device output buffer pull-up struc-ture is configured as a TTL-like totem-pole. The High driver is an n-channel pull-up transistor, pulling to a voltage one transistor threshold below V CC. Alternatively, the outputs can be globally configured as CMOS drivers, with additional p-channel pull-up transistors pulling to V CC. This option, applied using the bitstream generation software, applies to all outputs on the device. It is not individually programma-ble.All Spartan-XL device outputs are configured as CMOS drivers, therefore driving rail-to-rail. The Spartan-XL outputs are individually programmable for 12mA or 24mA output drive.Any 5V Spartan device with its outputs configured in TTL mode can drive the inputs of any typical 3.3V device. Sup-ported destinations for Spartan/XL device outputs are shown in Table7.Three-State Register (Spartan-XL Only)Spartan-XL devices incorporate an optional register control-ling the three-state enable in the IOBs. The use of the three-state control register can significantly improve output enable and disable time.Output Slew RateThe slew rate of each output buffer is, by default, reduced, to minimize power bus transients when switching non-criti-cal signals. For critical signals, attach a FAST attribute or property to the output buffer or flip-flop.Spartan/XL devices have a feature called "Soft Start-up," designed to reduce ground bounce when all outputs are turned on simultaneously at the end of configuration. When the configuration process is finished and the device starts up, the first activation of the outputs is automatically slew-rate limited. Immediately following the initial activation of the I/O, the slew rate of the individual outputs is deter-mined by the individual configuration option for each IOB. Pull-up and Pull-down NetworkProgrammable pull-up and pull-down resistors are used fortying unused pins to V CC or Ground to minimize power con-sumption and reduce noise sensitivity. The configurablepull-up resistor is a p-channel transistor that pulls to V CC.The configurable pull-down resistor is an n-channel transis-tor that pulls to Ground. The value of these resistors is typi-cally 20KΩ − 100KΩ (See "Spartan DC Characteristics Figure 7: AND and MUX Symbols in Spartan-XL IOB10DS060 (v1.6) September 19, 2001Over Operating Conditions" on page 43.). This high value makes them unsuitable as wired-AND pull-up resistors.After configuration, voltage levels of unused pads, bonded or unbonded, must be valid logic levels, to reduce noise sensitivity and avoid excess current. Therefore, by default,unused pads are configured with the internal pull-up resistor active. Alternatively, they can be individually configured with the pull-down resistor, or as a driven output, or to be driven by an external source. To activate the internal pull-up, attach the PULLUP library component to the net attached to the pad. To activate the internal pull-down, attach the PULL-DOWN library component to the net attached to the pad.Set/ResetAs with the CLB registers, the GSR signal can be used to set or clear the input and output registers, depending on the value of the INIT attribute or property. The two flip-flops can be individually configured to set or clear on reset and after configuration. Other than the global GSR net, no user-con-trolled set/reset signal is available to the I/O flip-flops (Figure 5). The choice of set or reset applies to both the ini-tial state of the flip-flop and the response to the GSR pulse.Independent ClocksSeparate clock signals are provided for the input (IK) and output (OK) flip-flops. The clock can be independently inverted for each flip-flop within the IOB, generating eitherfalling-edge or rising-edge triggered flip-flops. The clock inputs for each IOB are mon Clock EnablesThe input and output flip-flops in each IOB have a common clock enable input (see EC signal in Figure 5), which through configuration, can be activated individually for the input or output flip-flop, or both. This clock enable operates exactly like the EC signal on the Spartan/XL CLB. It cannot be inverted within the IOB.Routing Channel DescriptionAll internal routing channels are composed of metal seg-ments with programmable switching points and switching matrices to implement the desired routing. A structured,hierarchical matrix of routing channels is provided to achieve efficient automated routing.This section describes the routing channels available in Spartan/XL devices. Figure 8 shows a general block dia-gram of the CLB routing channels. The implementation soft-ware automatically assigns the appropriate resources based on the density and timing requirements of the design.The following description of the routing channels is for infor-mation only and is simplified with some minor details omit-ted. For an exact interconnect description the designer should open a design in the FPGA Editor and review the actual connections in this tool.The routing channels will be discussed as follows;•CLB routing channels which run along each row and column of the CLB array.•IOB routing channels which form a ring (called a VersaRing) around the outside of the CLB array. It connects the I/O with the CLB routing channels.•Global routing consists of dedicated networks primarily designed to distribute clocks throughout the device with minimum delay and skew. Global routing can also be used for other high-fanout signals.CLB Routing ChannelsThe routing channels around the CLB are derived from three types of interconnects; single-length, double-length,and longlines. At the intersection of each vertical and hori-zontal routing channel is a signal steering matrix called a Programmable Switch Matrix (PSM). Figure 8 shows the basic routing channel configuration showing single-length lines, double-length lines and longlines as well as the CLBs and PSMs. The CLB to routing channel interface is shown as well as how the PSMs interface at the channel intersec-tions.T able 7: Supported Destinations for Spartan/XL OutputsNotes:1.Only if destination device has 5V tolerant inputs.CLB InterfaceA block diagram of the CLB interface signals is shown in Figure9. The input signals to the CLB are distributed evenly on all four sides providing maximum routing flexibility. In general, the entire architecture is symmetrical and regular. It is well suited to established placement and routing algo-rithms. Inputs, outputs, and function generators can freely swap positions within a CLB to avoid routing congestion during the placement and routing operation. The exceptions are the clock (K) input and CIN/COUT signals. The K input is routed to dedicated global vertical lines as well as four single-length lines and is on the left side of the CLB. The CIN/COUT signals are routed through dedicated intercon-nects which do not interfere with the general routing struc-ture. The output signals from the CLB are available to drive both vertical and horizontal channels.Programmable Switch MatricesThe horizontal and vertical single- and double-length lines intersect at a box called a programmable switch matrix (PSM). Each PSM consists of programmable pass transis-tors used to establish connections between the lines (see Figure10).For example, a single-length signal entering on the right side of the switch matrix can be routed to a single-length line on the top, left, or bottom sides, or any combination thereof, if multiple branches are required. Similarly, a dou-ble-length signal can be routed to a double-length line on any or all of the other three edges of the programmable switch matrix.Single-Length LinesSingle-length lines provide the greatest interconnect flexibil-ity and offer fast routing between adjacent blocks. There are eight vertical and eight horizontal single-length lines associ-ated with each CLB. These lines connect the switching matrices that are located in every row and column of CLBs. Single-length lines are connected by way of the program-mable switch matrices, as shown in Figure10. Routing con-nectivity is shown in Figure8.Single-length lines incur a delay whenever they go through a PSM. Therefore, they are not suitable for routing signals for long distances. They are normally used to conduct sig-nals within a localized area and to provide the branching for nets with fanout greater than one.Figure 8: Spartan/XL CLB Routing Channels and Interface Block DiagramFigure 9: CLB Interconnect Signals。

1714955资料

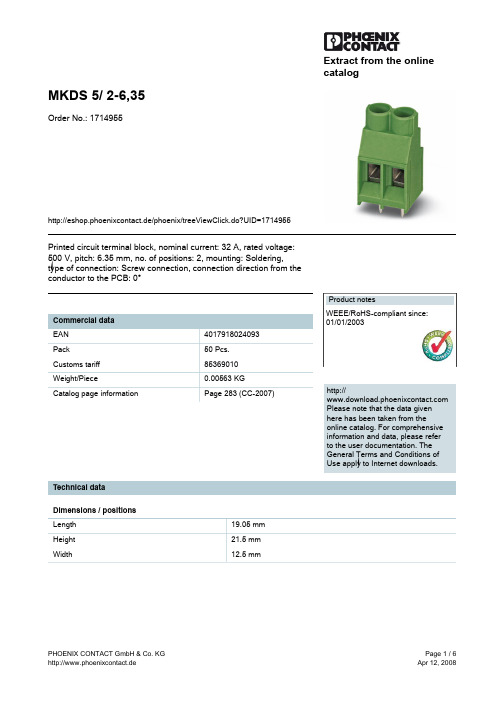

Extract from the onlinecatalogMKDS 5/ 2-6,35Order No.: 1714955http://eshop.phoenixcontact.de/phoenix/treeViewClick.do?UID=1714955Printed circuit terminal block, nominal current: 32 A, rated voltage: 500 V, pitch: 6.35 mm, no. of positions: 2, mounting: Soldering, type of connection: Screw connection, connection direction from the conductor to the PCB: 0°http://Please note that the data givenhere has been taken from theonline catalog. For comprehensiveinformation and data, please referto the user documentation. TheGeneral Terms and Conditions ofUse apply to Internet downloads. Technical dataDimensions / positionsLength19.05 mmHeight21.5 mmWidth12.5 mmPitch 6.35 mm Dimension a 6.35 mm Number of positions2Pin dimensions0,9 x 0,9 mm Hole diameter 1.3 mm Screw thread M 3 Tightening torque, min0.5 NmTechnical dataInsulating material group IRated surge voltage (III/3) 6 kVRated surge voltage (III/2) 6 kVRated surge voltage (II/2) 6 kVRated voltage (III/2)630 V Rated voltage (II/2)1000 V Connection in acc. with standard EN-VDE Nominal current I N32 A Nominal voltage U N500 V Nominal cross section 4 mm2 Maximum load current32 A Insulating material PA Inflammability class acc. to UL 94V0Internal cylindrical gage A4 Stripping length8 mmConnection dataConductor cross section solid min.0.2 mm2 Conductor cross section solid max. 6 mm2 Conductor cross section stranded min.0.2 mm2 Conductor cross section stranded max. 4 mm2 Conductor cross section stranded, with ferrule0.25 mm2 without plastic sleeve min.Conductor cross section stranded, with ferrule4 mm2 without plastic sleeve max.Conductor cross section stranded, with ferrule0.25 mm2 with plastic sleeve min.Conductor cross section stranded, with ferrule with plastic sleeve max.4 mm 2Conductor cross section AWG/kcmil min.24Conductor cross section AWG/kcmil max 102 conductors with same cross section, solid min.0.2 mm 22 conductors with same cross section, solid max. 1.5 mm 22 conductors with same cross section, stranded min.0.2 mm 22 conductors with same cross section, stranded max.1.5 mm22 conductors with same cross section, stranded,ferrules without plastic sleeve, min.0.25 mm 22 conductors with same cross section, stranded,ferrules without plastic sleeve, max.0.75 mm 22 conductors with same cross section, stranded,TWIN ferrules with plastic sleeve, min.0.5 mm 22 conductors with same cross section, stranded,TWIN ferrules with plastic sleeve, max. 2.5 mm2Certificates / ApprovalsCSANominal voltage U N 300 V Nominal current I N 10 A AWG/kcmil 28-10CULNominal voltage U N 300 V Nominal current I N 10 A AWG/kcmil 30-10ULNominal voltage U N 300 V Nominal current I N 10 A AWG/kcmil 30-10CertificationCCA, CSA, CUL, GL, GOST, RS, SEV, ULAccessoriesItem Designation DescriptionMarking1051993B-STIFT Marker pen, for manual labeling of unprinted Zack strips, smear-proof and waterproof, line thickness 0.5 mm0804374SK 6,2/3,8:FORTL.ZAHLEN Marker card, printed horizontally, self-adhesive, 12 identicaldecades marked 1-10, 11-20 etc. up to 91-(99)100, sufficient for120 terminal blocks0805425SK 6,2/3,8:UNBEDRUCKT Marker cards, unprinted, with pitch divisions, self-adhesive, 10-section marker strips, 12 strips per card, can be labeled with M-PENTools1205053SZS 0,6X3,5Screwdriver, bladed, matches all screw terminal blocks up to 4.0mm² connection cross section, blade: 0.6 x 3.5 mm, without VDEapprovalDrawingsDrilling diagramDimensioned drawingAddressPHOENIX CONTACT GmbH & Co. KGFlachsmarktstr. 832825 Blomberg,GermanyPhone +49 5235 3 00Fax +49 5235 3 41200http://www.phoenixcontact.de© 2008 Phoenix ContactTechnical modifications reserved;。

MAX1409CAP+;MAX1414CAI+;MAX1407CAI+;MAX1409CAP+T;MAX1407CAI+T;中文规格书,Datasheet资料

General DescriptionThe MAX1407/MAX1408/MAX1409/MAX1414 are low-power, general-purpose, multichannel data-acquisition systems (DAS). These devices are optimized for low-power applications. All the devices operate from a sin-gle +2.7V to +3.6V power supply and consume a maximum of 1.15mA in Run mode and only 2.5µA in Sleep mode.The MAX1407/MAX1408/MAX1414 feature a differential 8:1 input multiplexer to the ADC, a programmable three-state digital output, an output to shutdown an external power supply, and a data ready output from the ADC. The MAX1408 has eight auxiliary analog inputs, while the MAX1407/MAX1414 include four auxil-iary analog inputs and two 10-bit force/sense DACs.The MAX1414 features a 50mV trip threshold for the signal-detect comparator while the others have a 0mV trip threshold. The MAX1409 is a 20-pin version of the DAS family with a differential 4:1 input multiplexer to the ADC, one auxiliary analog input, and one 10-bit force/sense DAC.The MAX1407/MAX1408/MAX1414 are available in space-saving 28-pin SSOP packages, while the MAX1409 is available in a 20-pin SSOP package.ApplicationsMedical Instruments Industrial Control Systems Portable Equipment Data-Acquisition System Automatic Testing RoboticsFeatureso +2.7V to +3.6V Supply Voltage Range in Standby,Idle, and Run Mode (Down to 1.8V in Sleep Mode) o 1.15mA Run Mode Supply Currento 2.5µA Sleep Mode Supply Current (Wake-Up, RTC,and Voltage Monitor Active)o Multichannel 16-Bit Sigma-Delta ADC±1.5 LSB (typ) Integral Nonlinearity30Hz or 60Hz Continuous Conversion Rate Buffered or Unbuffered Mode Gain of +1/3, +1, or +2V/V Unipolar or Bipolar Mode On-Chip Offset Calibration o 10-Bit Force/Sense DACso Buffered 1.25V, 18ppm/°C (typ) Bandgap Reference Outputo SPI™/QSPI™or MICROWIRE™-Compatible Serial Interface o System Support FunctionsRTC (Valid til 9999) and AlarmHigh-Frequency PLL Clock Output (2.4576MHz)+1.8V and +2.7V RESET and Power-Supply Voltage MonitorsSignal Detect ComparatorInterrupt Generator (INT and DRDY )Three-State Digital Output Wake-Up Circuitry o 28-Pin SSOP (MAX1407/MAX1408/MAX1414), 20-Pin SSOP (MAX1409)MAX1407/MAX1408/MAX1409/MAX1414Low-Power, 16-Bit Multichannel DAS with Internal Reference,10-Bit DACs, and RTC________________________________________________________________Maxim Integrated Products 119-2229; Rev 0; 10/01Pin Configurations continued at end of data sheet.Typical Operating Circuit appears at end of data sheet.SPI and QSPI are trademarks of Motorola, Inc.MICROWIRE is a trademark of National Semiconductor Corp.Ordering InformationPin ConfigurationsFor pricing, delivery, and ordering information,please contact Maxim/Dallas Direct!at 1-888-629-4642, or visit Maxim’s website at .M A X 1407/M A X 1408/M A X 1409/M A X 1414Low-Power, 16-Bit Multichannel DAS with Internal Reference,10-Bit DACs, and RTC 2_______________________________________________________________________________________ABSOLUTE MAXIMUM RATINGSStresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.AV DD to AGND.........................................................-0.3V to +6V AV DD to DV DD ......................................................-0.3V to +0.3V Analog Inputs to AGND.........................-0.3V to +(AV DD + 0.3V)Digital Inputs to DGND.............................................-0.3V to +6V Maximum Current Input Into Any Pin..................................50mA Continuous Power Dissipation (T A = +70°C)20-Pin SSOP (derate 8.0mW/°C above +70°C)...........640mW 28-Pin SSOP (derate 9.52mW/°C above +70°C).........762mW DV DD to DGND.........................................................-0.3V to +6V AGND to DGND.....................................................-0.3V to +0.3VAnalog Outputs to AGND......................-0.3V to +(AV DD + 0.3V)Digital Outputs to DGND.......................-0.3V to +(AV DD + 0.3V)REF to AGND.........................................-0.3V to +(AV DD + 0.3V)Operating Temperature Range:MAX14__CA_......................................................0°C to +70°C MAX14__EA_...................................................-40°C to +85°C Lead Temperature (soldering, 10s)................................+300 °C Storage Temperature Range.............................-65°C to +150°C Junction Temperature......................................................+150°CELECTRICAL CHARACTERISTICS(DV DD = AV DD = +2.7V to 3.6V, 4.7µF at REF, internal V REF , 18nF between CPLL and AV DD , 32.768kHz crystal across CLKIN and CLKOUT, T A = T MIN to T MAX , unless otherwise noted. Typical values are at T A = +25°C.)MAX1407/MAX1408/MAX1409/MAX1414Low-Power, 16-Bit Multichannel DAS with Internal Reference,10-Bit DACs, and RTCELECTRICAL CHARACTERISTICS (continued)M A X 1407/M A X 1408/M A X 1409/M A X 1414Low-Power, 16-Bit Multichannel DAS with Internal Reference,10-Bit DACs, and RTC 4_______________________________________________________________________________________ELECTRICAL CHARACTERISTICS (continued)MAX1407/MAX1408/MAX1409/MAX1414Low-Power, 16-Bit Multichannel DAS with Internal Reference,10-Bit DACs, and RTC_______________________________________________________________________________________5ELECTRICAL CHARACTERISTICS (continued)(DV= AV = +2.7V to 3.6V, 4.7µF at REF, internal V , 18nF between CPLL and AV , 32.768kHz crystal across CLKIN andM A X 1407/M A X 1408/M A X 1409/M A X 1414Low-Power, 16-Bit Multichannel DAS with Internal Reference,10-Bit DACs, and RTC 6_______________________________________________________________________________________ELECTRICAL CHARACTERISTICS (continued)(DV DD = AV DD = +2.7V to 3.6V, 4.7µF at REF, internal V REF , 18nF between CPLL and AV DD , 32.768kHz crystal across CLKIN and CLKOUT, T A = T MIN to T MAX , unless otherwise noted. Typical values are at T A = +25°C.)TIMING CHARACTERISTICSMAX1407/MAX1408/MAX1409/MAX1414Low-Power, 16-Bit Multichannel DAS with Internal Reference,10-Bit DACs, and RTC_______________________________________________________________________________________7Note 2:DNL and INL are measured between code 010hex and 3FFhex.Note 3:Offset error is referenced to code 010hex.Note 4:Output swing is a function of external gain-setting feedback resistors and REF voltage.Note 5:Measured with no load on FOUT, DOUT, and the DAC amplifiers. SCLK is idle, and all digital inputs are at DGND or DV DD .Note 6:SHDN stays high if the PLL is on.Note 7:Actual worst-case performance is ±2.5LSB. Guaranteed limit of ±3.5LSB is due to production test limitation.Note 8:Guaranteed by design. Not production tested.TIMING CHARACTERISTICS (continued)(MAX1407/MAX1408/MAX1409/MAX1414: AV DD = DV DD = 2.7V to 3.6V, T A = T MIN to T MAX,unless otherwise noted.)M A X 1407/M A X 1408/M A X 1409/M A X 1414Low-Power, 16-Bit Multichannel DAS with Internal Reference,10-Bit DACs, and RTC 8_______________________________________________________________________________________Typical Operating Characteristics(A VDD = D VDD = 3V, MAX1407 used, T A = +25°C, unless otherwise noted.)02001004003006005007002.703.003.152.853.303.453.60SUPPLY CURRENT vs.SUPPLY VOLTAGESUPPLY VOLTAGE (V)S U P P L Y C U R R E N T (µA)200100400300600500700-401035-156085SUPPLY CURRENT vs.TEMPERATURETEMPERATURE (°C)S U P P L Y C U R R E N T (µA )1.02.01.53.02.53.54.01.802.802.303.30SLEEP CURRENT vs. FALLING V DDM A X 1407 t o c 03SUPLLY VOLTAGE (V)S L E E PC U R R E N T (µA )01.00.52.01.52.53.0-4010-15356085SLEEP MODE SUPPLY CURRENTvs. TEMPERATURETEMPERATURE (°C)S U P P L Y C U R R E N T (µA )Load CircuitsMAX1407/MAX1408/MAX1409/MAX1414Low-Power, 16-Bit Multichannel DAS with Internal Reference,10-Bit DACs, and RTC_______________________________________________________________________________________9Typical Operating Characteristics (continued)(A VDD = D VDD = 3V, MAX1407 used, T A = +25°C, unless otherwise noted.)0132452.73.12.93.33.5MAXIMUM INL vs. V DD (UNIPOLAR MODE, T = +25°C,PSEUDO-DIFFERENTIAL INPUT)V DD (V)M A X I M U M I N L (L S B )A: GAIN = 1, UNBUFFERED MODE, 60sps B: GAIN = 1, UNBUFFERED MODE, 30sps01.51.00.52.02.53.03.54.04.55.02.73.12.93.33.5MAXIMUM INL vs. V DD (BIPOLAR MODE, T = +25°C,FULLY DIFFERENTIAL INPUT)M A X 1407 t o c 06V DD (V)M A X I M U M I N L (L S B )ABA: GAIN = 2, BUFFERED MODE, 60sps B: GAIN = 2, BUFFERED MODE, 30sps01.51.00.52.02.53.03.54.04.55.0040206080MAXIMUM INL vs. TEMPERATURE (UNIPOLAR MODE, V DD = 3V,PSEUDO-DIFFERENTIAL INPUT)M A X 1407 t o c 07TEMPERATURE (°C)M A X I M U M I N L (L S B )ABA: GAIN = 1, UNBUFFERED MODE, 60sps B: GAIN = 1, UNBUFFERED MODE, 30sps1.51.00.52.02.53.03.54.04.55.0040206080MAXIMUM INL vs. TEMPERATURE (BIPOLAR MODE, V DD = 3V,FULLY DIFFERENTIAL INPUT)M A X 1407 t o c 08TEMPERATURE (°C)M A X I M U M I N L (L S B )AB A: GAIN = 2, BUFFERED MODE, 60sps B: GAIN = 2, BUFFERED MODE, 30spsM A X 1407/M A X 1408/M A X 1409/M A X 1414Low-Power, 16-Bit Multichannel DAS with Internal Reference,10-Bit DACs, and RTC 10______________________________________________________________________________________Typical Operating Characteristics (continued)(A VDD = D VDD = 3V, MAX1407 used, T A = +25°C, unless otherwise noted.)01.00.52.01.52.53.00.30.70.50.91.1MAXIMUM INL vs. COMMON-MODE INPUT VOLTAGE (BIPOLAR MODE,BUFFERED MODE, V DD = 2.7V, 30sps,FULLY DIFFERENTIAL INPUT, T = +25°C)M A X 1407 t o c 09COMMON-MODE INPUT VOLTAGE (V)M A X I M U M I N L (L S B )A: GAIN = 1B: GAIN = 2AB-2.0-1.5-1.0-0.500.51.01.52.0-1.25-0.75-0.250.250.751.25INL vs. FULLY DIFFERENTIAL INPUT VOLTAGE (BIPOLAR MODE,GAIN = 1, UNBUFFERED MODE,V CM = 0.625V, V DD = 3V, T = +25°C)M A X 1407 t o c 10DIFFERENTIAL INPUT VOLTAGE (V)I N L (L S B )-2.0-1.5-1.0-0.500.51.01.52.00.20.40.81.0INL vs. PSEUDO-DIFFERENTIAL INPUT VOLTAGE RANGE (UNIPOLAR MODE,GAIN = 1, UNBUFFERED MODE,V NEG = 0, V DD = 3V, T = +25°C)M A X 1407 t o c 11DIFFERENTIAL VOLTAGE (V)I N L (L S B )1.20.601.51.00.52.02.53.03.54.04.55.040206080UNCORRECTED OFFSET ERRORvs. TEMPERATURE(UNBUFFERED MODE, V DD = 3V)M A X 1407 t o c 12TEMPERATURE (°C)O F F S E T E R R O R (L S B )ABA: GAIN = 1, UNIPOLAR MODE B: GAIN = 2, BIPOLAR MODE分销商库存信息:MAXIMMAX1409CAP+MAX1414CAI+MAX1407CAI+ MAX1409CAP+T MAX1407CAI+T MAX1414CAI+T。

1954702资料

Extract from the onlinecatalogCC 2,5/ 3-GF-5,08 P26THROrder No.: 1954702The figure shows a 10-position version of the producthttp://eshop.phoenixcontact.de/phoenix/treeViewClick.do?UID=1954702Headers, with screw flange, pin length: 2.6 mm, 5.08 mm pitch, 3-pos.http://Please note that the data givenhere has been taken from theonline catalog. For comprehensiveinformation and data, please referto the user documentation. TheGeneral Terms and Conditions ofUse apply to Internet downloads. Technical dataDimensions / positionsPitch 5.08 mmDimension a10.16 mmNumber of positions3Pin dimensions 1 x 1 mmPin spacing 5.08 mmHole diameter 1.4 mmTechnical dataInsulating material group IIIaRated surge voltage (III/3) 4 kVRated surge voltage (III/2) 4 kVRated surge voltage (II/2) 4 kVRated voltage (III/2)320 VRated voltage (II/2)400 VConnection in acc. with standard EN-VDENominal current I N12 ANominal voltage U N250 VMaximum load current12 A (per position)Insulating material LCPInflammability class acc. to UL 94V0Certificates / ApprovalsApproval logoCULNominal voltage U N300 VNominal current I N10 AULNominal voltage U N300 VNominal current I N10 ACertification CUL, ULAccessoriesItem Designation DescriptionGeneral1954362CR-MSTB NAT HT HT coding section, is pushed into the recess on the header beforethe reflow process, made of highly temperature-resistant, beigeinsulating materialMarking1051993B-STIFT Marker pen, for manual labeling of unprinted Zack strips, smear-proof and waterproof, line thickness 0.5 mm0804293SK 5,08/3,8:FORTL.ZAHLEN Marker card, printed horizontally, self-adhesive, 12 identicaldecades marked 1-10, 11-20 etc. up to 91-(99)100, sufficient for120 terminal blocks0805085SK 5,08/3,8:SO Marker card, special printing, self-adhesive, labeled acc. tocustomer requirements, 12 identical marker strips per card, max.25-position labeling per strip, color: white0805412SK 5,08/3,8:UNBEDRUCKT Marker cards, unprinted, with pitch divisions, self-adhesive, 10-section marker strips, 12 strips per card, can be labeled with theM-PENPlug/Adapter1734401CR-MSTB Coding section, inserted into the recess in the header or theinverted plug, red insulating materialDrawingsApplication drawingDrilling diagramDimensioned drawingBottom view, free space for solder paste, 0.5mm deepAddressPHOENIX CONTACT GmbH & Co. KGFlachsmarktstr. 832825 Blomberg,GermanyPhone +49 5235 3 00Fax +49 5235 3 41200http://www.phoenixcontact.de© 2008 Phoenix ContactTechnical modifications reserved;。

1809446资料

Extract from the onlinecatalogMSTBC 2,5/19-STZFD-5,08Order No.: 1809446The illustration shows a 15-position versionhttp://eshop.phoenixcontact.de/phoenix/treeViewClick.do?UID=1809446Plug component, nominal current: 12 A, rated voltage: 320 V, pitch:5.08 mm, no. of positions: 19, type of connection: Crimp connectionhttp://Please note that the data givenhere has been taken from theonline catalog. For comprehensiveinformation and data, please referto the user documentation. TheGeneral Terms and Conditions ofUse apply to Internet downloads. Technical dataDimensions / positionsHeight10.7 mmPitch 5.08 mmDimension a91.44 mmNumber of positions19Technical dataInsulating material group IRated surge voltage (III/3) 4 kVRated surge voltage (III/2) 4 kVRated surge voltage (II/2) 4 kVRated voltage (III/2)320 VRated voltage (II/2)630 VConnection in acc. with standard EN-VDENominal current I N12 ANominal voltage U N320 VNominal cross section 2.5 mm2Insulating material PAInflammability class acc. to UL 94V0Connection dataConductor cross section stranded min.0.5 mm2Conductor cross section stranded max. 2.5 mm2Conductor cross section AWG/kcmil min.20Conductor cross section AWG/kcmil max14Certificates / ApprovalsApproval logoCSANominal voltage U N300 VNominal current I N10 AAWG/kcmil20-14CULNominal voltage U N300 VNominal current I N10 AAWG/kcmil20-14ULNominal voltage U N300 VNominal current I N10 AAWG/kcmil20-14Certification CB, CSA, CUL, UL, VDE-PZIAccessoriesItem Designation DescriptionMarking0804293SK 5,08/3,8:FORTL.ZAHLEN Marker card, printed horizontally, self-adhesive, 12 identicaldecades marked 1-10, 11-20 etc. up to 91-(99)100, sufficient for120 terminal blocksPlug/Adapter1734634CP-MSTB Coding profile, is inserted into the slot on the plug or invertedheader, red insulating material3190564MSTBC-MT 0,5-1,0Module female contact, is inserted into the plug housing MSTBCafter crimping the conductor, for conductors from 0.5 to 1.0 mm²3190645MSTBC-MT 0,5-1,0 BA Module female contact, is inserted into the MSTBC connectorshell after the conductor has been crimped, for conductors from0.5 - 1.0 mm², ribbon contact3190551MSTBC-MT 1,5-2,5Module female contact, is inserted into the plug housing MSTBCafter crimping the conductor, for conductors from 1.5 to 2.5 mm²3190658MSTBC-MT 1,5-2,5 BA Module female contact, is inserted into the MSTBC connectorshell after the conductor has been crimped, for conductors from1.5 -2.5 mm², ribbon contact1810529STZ 2-MSTBC-5,08Strain relief for snapping into the latching chambers of the plugcomponents, 2-pos., labeling with ZB 61810532STZ 4-MSTBC-5,08Strain relief for snapping into the latching chambers of the plugcomponents, 4-pos., labeling with ZB 61810516STZ 8-MSTBC-5,08Strain relief for snapping into the latching chambers of the plugcomponents, 8-pos., labeling with ZB 61810503STZ 12-MSTBC-5,08Strain relief for snapping into the latching chambers of the plugcomponents, 12-pos., labeling with ZB 6Tools1204038CRIMPFOX MT 2,5Crimping pliers, for crimping conductors to the module femalecontacts STG-MTN, crimp range: 0.5-2.5 mm², AWG: 20-14 1205037SZS 0,4X2,5Screwdriver, bladed, matches all screw terminal blocks up to 1.5mm² connection cross section, blade: 0.4 x 2.5 mm Additional productsItem Designation DescriptionGeneral1825488IC 2,5/19-STF-5,08Plug component, nominal current: 12 A, rated voltage: 250 V,pitch: 5.08 mm, no. of positions: 19, type of connection: Screwconnection1823558ICC 2,5/19-STZF-5,08Plug component, nominal current: 12 A, rated voltage: 250 V,pitch: 5.08 mm, no. of positions: 19, type of connection: CrimpconnectionDrawingsDrilling diagramDimensioned drawingAddressPHOENIX CONTACT GmbH & Co. KGFlachsmarktstr. 832825 Blomberg,GermanyPhone +49 5235 3 00Fax +49 5235 3 41200http://www.phoenixcontact.de© 2008 Phoenix ContactTechnical modifications reserved;。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Printed circuit terminal block, nominal current: 17.5 A, rated voltage: 500 V, pitch: 7.62 mm, no. of positions: 1, mounting: Soldering, type of connection: Spring-cage connection, connection direction from the conductor to the PCB: 90°

元器件交易网

Extract from the online catalog

FKDSVA-7,62/SA-10,16

Order No.: 1790445

http://eshop.phoenixcontact.de/phoenix/treeViewClick.do?UID=1790445

PHOENIX CONTACT GmbH & Co. KG http://www.phoenixcontact.de

Page 2 / 3 Mar 2, 2008

元器件交易网

FKDSVA-7,62/SA-10,16 Order No.: 1790445

http://eshop.phoenixcontact.de/phoenix/treeViewClick.do?UID=1ቤተ መጻሕፍቲ ባይዱ90445

Product notes Commercial data EAN Pack Customs tariff Weight/Piece 4017918044329 50 Pcs. 85369010 0.00271 KG http:// Please note that the data given here has been taken from the online catalog. For comprehensive information and data, please refer to the user documentation. The General Terms and Conditions of Use apply to Internet downloads. Certificates / Approvals WEEE/RoHS-compliant since: 01/01/2003

Tools 1204517 SZF 1-0,6X3,5 Screwdriver, blade: 0.6 x 3.5 x 100 mm, length 180 mm

Additional products Item General 1790555 FKDSVA1-7,62/SA-10,16 Designation Description

Approval logo

CSA Nominal voltage UN Nominal current IN AWG/kcmil 300 V 10 A 16

PHOENIX CONTACT GmbH & Co. KG http://www.phoenixcontact.de

Page 1 / 3 Mar 2, 2008

元器件交易网

FKDSVA-7,62/SA-10,16 Order No.: 1790445

http://eshop.phoenixcontact.de/phoenix/treeViewClick.do?UID=1790445

CUL Nominal voltage UN Nominal current IN AWG/kcmil UL Nominal voltage UN Nominal current IN AWG/kcmil Certification Accessories Item General 1790555 Marking 0804552 SK 7,62/5:FORTL.ZAHLEN Marker card, printed horizontally, self-adhesive, 10-section marker strip, 10 identical decades marked 1-10, 11-20 etc. up to 91-100, sufficient for 100 terminal blocks FKDSVA1-7,62/SA-10,16 Designation Description 300 V 10 A 22-16 CCA, CSA, CUL, GOST, SEV, UL 300 V 10 A 22-16

Address

PHOENIX CONTACT GmbH & Co. KG Flachsmarktstr. 8 32825 Blomberg,Germany Phone +49 5235 3 00 Fax +49 5235 3 41200 http://www.phoenixcontact.de

© 2008 Phoenix Contact Technical modifications reserved;

PHOENIX CONTACT GmbH & Co. KG http://www.phoenixcontact.de

Page 3 / 3 Mar 2, 2008