一种基于FPGA的DDS算法的简化实现[1]

基于fpga的dds正弦信号发生器的设计和实现

基于fpga的dds正弦信号发生器的设计和实现

基于FPGA的DDS正弦信号发生器可以使用数字信号处理技术实现。

下面是一个基本的设计和实现步骤:

1. 确定系统需求:首先,确定所需的输出信号频率范围、分辨率和采样率等系统参数。

这些参数可以根据实际应用来确定。

2. 设计正弦表:根据系统需求,设计一个包含所需频率范围内所有可能的正弦波的正弦表。

可以使用固定小数点表示法来表示正弦表中的采样值。

3. 设计相位累加器:使用一个32位计数器作为相位累加器,其计数速度由所需的输出信号频率和FPGA时钟频率决定。

每个时钟周期,计数器值自动增加到下一个相位值。

4. 选择相位值:使用相位累加器的值在正弦表中查找对应的相位值,并将其作为输出信号的采样值。

5. 数字输出:将采样值经过DAC(数字模拟转换器)转换为模拟信号,并将其输出。

6. 配置FPGA:将设计好的数字电路加载到FPGA芯片中,并配置FPGA内部的寄存器、时钟和IO管脚等。

7. 测试和调试:对设计好的系统进行测试和调试,确保输出信号的频率、精确度和稳定性符合要求。

这是一个基本的设计和实现步骤,具体的实现方法和细节可能因FPGA型号、工具和应用需求而异。

在实际应用中,还可以加入滤波器、幅度控制、相位调制等功能以满足更多需求。

一种基于FPGA的DDS算法的简化实现

而结束一个周期 , 导致一个周期只有 4个脉冲 , 最后 留下 4个单位 的误 差。 当相位 累加 器 的字长为 8 时, 经过计算可以得 到 , F W 的取值在 5 当 C 2到 6 3

时 , 一个 周期 均 为 5个脉 冲 , 每 最后 得到 的正 弦 波 的 周 期也 是相 同的 。

示 。它利 用 可 溢 出 的 L位 累 加 器 ( 称 相 位 累 加 或 器 ) 生 正弦 函数 的相位 变 量 。相位 累 加器 每 溢 出 产

一

频率切换时间、 极高的频率精度和分辨率以及易于

控制 各种 调 制 方 式 等 优 点 , 年 来 在 通 信 、 达 和 近 雷

次, 就代表正弦波形的一个周期 。相位累加器输

文章 编号 :6 3— 0 7 20 )5— 30— 4 17 25 (06 0 04 0

一

种基 于 F G P A的 D S算 法 的简 化 实现 D

常春 波

( 太原科技 大学电子信息工程学院, 太原 00 2 ) 304

摘

要: 在分析 了传统的 D S D 算法的基础上 , 出了一种改进 方案 , 提 使得 系统的复杂

度 降低 , 趋 于模块化 , 生 的波 形频率 更 准确 。输 出采 用一 个周期 8个采样 点 的定 点输 更 产

出, 系统 时钟 频 率 为 8 MHz信 号的谐 波 小于 7 d 。输 出信 号 的 范 围为 D 0 , 0B C到 1 MH , 0 z信

号频 率 的步长 为 0 1 z相应 的 转换 速 度 为 1.n。 .H , 25 s

入的频率控制字 ( C 来控制生成 的正弦波形的 F W) 频率 , 累加器 的高位输出作为 R M查找表 的地 址 O 信号。R M 查找表是存 有正 弦采样值 的存储器 。 O 这种频率合成方法可 以在不增加 R M查找表容量 O 的情况下 , 获得较高 的频 率精度 。相 位累加器每增 加一位 , 频率精度就提高 2倍 。直接数字频率合 成 器的输 出频率 f t o 可以由下式确定 : u

基于FPGA的两种DDS实现

基于FPGA的两种DDS实现直接数字频率合成(Direct Digital Synthesis,DDS)是一种基于数字信号处理的频率合成方法,通过将一个连续的幅度和相位可调的数字信号与一个时钟信号相乘,可以产生高精度的频率信号。

在FPGA(Field Programmable Gate Array)中,DDS可以通过数字逻辑实现。

本文将介绍两种基于FPGA的DDS实现方法。

LUT是FPGA中常用的存储组件,可以用于存储预先生成的数字信号样本。

基于LUT的DDS实现方法是将一个固定的正弦波样本表存储在LUT 中,然后通过改变LUT的读指针位置来产生不同频率的正弦波信号。

具体实现步骤如下:1)根据需要生成的信号频率,计算出每一个时钟周期对应的读指针步进量,即相位步进量。

2)初始化读指针位置为0,以时钟信号为基准,每一个时钟周期将读指针位置加上相位步进量。

3)将读指针位置作为索引,从LUT中读取相应的正弦波样本值。

4)将读取到的正弦波样本值输出为DDS的输出信号。

基于LUT的DDS实现有以下优点:-简单易于实现,适合低频率应用。

-输出信号的频率可精确控制,具有较高的频率精度。

-可以通过修改LUT中的正弦波表,实现不同幅度和相位的输出信号。

另一种常见的DDS实现方法是基于相位累加器。

相位累加器是一个用于存储和计算相位信息的寄存器,通过不断累加相位步进量来产生不同频率的输出信号。

具体实现步骤如下:1)根据需要生成的信号频率,计算出每一个时钟周期对应的相位步进量。

2)初始化相位累加器为0,在每一个时钟周期将相位步进量加到累加器中。

3)将相位累加器的高位作为正弦波LUT的读指针,将读取到的正弦波样本值输出为DDS的输出信号。

基于相位累加器的DDS实现有以下优点:-输出信号的频率可精确控制,具有较高的频率精度。

-可以通过修改相位步进量,实现不同频率的输出信号。

-相位累加器可以很容易地实现相位调制和频率调制等功能,具有较高的灵活性。

基于FPGA的DDS的设计和实现[1]

![基于FPGA的DDS的设计和实现[1]](https://img.taocdn.com/s3/m/b785b53387c24028915fc30f.png)

94相位寄存器的输出与相位控制字相加,结果作为正弦查找表的地址。

查找表由ROM构成,其内部存有一个完整周期正弦波的数字幅度信息,每个查找表的地址对应正弦波中的一个相位点。

查找表把输入地址信息映射成正弦波幅度信号,同时输出到D/A转换器的输入端,通过D/A可将数字量形式的波形幅值转换成所要求的合成频率模拟量形式信号。

低通滤波器用于衰减和滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。

2基于FPGA 的DDS 设计随着微电子技术的发展,现场可编程门阵列(FPGA) 器件得到了飞速发展。

由于该器件具有工作速度快,集成度高和现场可编程等优点,因而在数字信号处理中得到了广泛应用。

本设计采用的器件是Altera公司的FLEX EPF10K40。

它的典型门数为40000门,逻辑单元有2304个,逻辑阵列块有200个,嵌入系统块有8个,因此,可完全符合使用单片来实现DDS电路的基本要求。

选用的设计工具为Altera公司的设计工具MAX+plusⅡ。

FLEX10K是工业界第一个嵌入式可编程逻辑器件,采用可重构的CMOS SRAM工艺,把连续的快速通道互连与独特的嵌入式阵列结构相结合,同时也结合了众多可编程器件的优点来完成普通门阵列的宏功能,它具有以下特点:(1)高密度:1 ̄25万个可用门。

高达40960位内部RAM(每个EAB有2048位),所有这些都可在不减少逻辑能力的情况下使用。

(2)系统级特点:支持多电压接口;低功耗(维持状态小于0.5mA) ;遵守PCI总线规定;内带JTAG边界扫描测试电路。

(3)灵活的内部连接:快速、可预测连线延时的快速通道连续式布线结构;实现快速加法器、计数器和比较器的专用进位链;实现高速、多输入逻辑函数的专用级联链;实现内部三态总线的三态模拟;多达六个全局时钟信号和四个全局清除信号。

在使用FPGA设计DDS电路时,相位累加器是决定DDS性能的一个关键部分。

本设计中定义累加器位数为10,如果使用传统的加法器设计结构,速度有可能达不到设计要求,不适应在实际情况中使系统工作在尽可能高的频率上。

DDS原理及基于FPGA的实现

DDS 原理及基于FPGA 的实现

直接数字频率合成技术(Direct Digital Synthesis,DDS)是一种从相位概念出发直接合成所需要的波形的新的全数字频率合成技术,该技术具有频

率分辨率高、频率变化速度快、相位可连续性变化等特点,在数字通信系统

中被广泛采用,是信号生成的最佳选择。

目前市场上可以见到很多集成的、

多功能的专用DDS 芯片,像AD9835、AD9954、AD9959 等。

但是在某些场合,专用DDS 芯片在控制方式、频率控制等方面与系统的要求差别很大,现场可编程门阵列(FPGA)器件具有工作速度快、集成度高、可靠性高和现场可编程等优点。

利用它来设计符合自己需要的DDS 电路是一个很好的解决方法。

1 DDS 的基本原理

DDS 的主要思想是从相位的概念出发合成所需要的波形,其结构由相位累加器、波形存储器、数模转换器、低通滤波器和参考时钟五部分组成,

其基本原理框图如图1 所示。

以FPGA为基础的DDS控制电路设计方案详解

以FPGA为基础的DDS控制电路设计方案详解FPGA是一种可编程逻辑设备,可以实现数字电路的设计和控制。

FPGA可用于设计频率合成器,其中直接数字频率合成(DDS)是一种常见的应用。

DDS是一种用于产生多种频率信号的技术,它使用数字控制寄存器来生成高精度的数字频率控制。

以下是以FPGA为基础的DDS控制电路设计方案的详细解释:1. 整体架构设计:FPGA DDS控制电路的整体架构包括一个相位累加器(phase accumulator)、一个频率控制字寄存器(frequency control word register)和一个查找表(look-up table)。

相位累加器用于生成相位控制信号,频率控制字寄存器用于存储频率控制信息,查找表用于将相位信息转换为实际的输出信号。

2.相位累加器设计:相位累加器是DDS控制电路的核心部分,它通过累加相位控制字来生成输出信号。

相位累加器通常由一个计数器和一个累加器组成。

计数器用于产生一个固定的时钟信号,累加器用于累加相位控制字。

相位控制字决定了相位累加器的累加速度,从而决定了输出信号的频率。

相位累加器的输出信号将作为查找表的输入信号。

3.频率控制字寄存器设计:频率控制字寄存器用于存储频率控制信息。

频率控制信息可以来自外部输入或来自FPGA内部的控制逻辑,例如通过串行接口输入到FPGA中。

频率控制字寄存器将频率控制信息转换为相位控制字,并将相位控制字输入到相位累加器中。

4.查找表设计:查找表用于将相位信息转换为实际的输出信号。

查找表是一个存储器单元,其中包含了预先计算好的正弦波形数据。

查找表根据输入的相位信息,从存储器中读取对应的正弦波形数据,并将数据作为输出信号输出。

查找表的大小取决于输出信号的需求精度,较大的查找表会提供更高的输出精度。

5.时钟和状态控制:DDS控制电路通常需要一个高精度的时钟信号来驱动相位累加器和频率控制字寄存器。

时钟信号的频率和相位可以通过FPGA内部的时钟控制器进行调整。

基于FPGA的DDS信号发生器的简单实现

[ 关键词 ] 直接数 字频率合 成( S ; DD )现场可编程逻辑器件 (P A)硬件描述语言( HDL FG ; V ) [ 作者简介 ] 谢立锋 , 宁泼 大学信息学院电气工程及 自动化专业 , 江 宁波 ,12 1 浙 3 5 1 [ 中图分类号 ] P 3 T 3 [ 文献标识码 ] A [ 文章编号 ] 0 7 72 (o 7 1 一 o 3 00 10 — 7 3 2o )2 o 5 — 0 3

系统 输 出波 形 的频 率 , 以 ,E 所 L D显 示 的也 是波形 的频 率 。此模 块 主要 的功 能是 将外 部键 盘 的 8 位 二进制 数转换 成三 位 B D码 。 C BN码 与 B D码 转换 的思想 是采 取与 4比较 I C

前

Hale Waihona Puke 言 用 于大步 进频 率合 成技 术 中 。

3D S 直接数字合成 o D ( .D ( S 直接数字合成 ) D 用 ,一种从参考频率源生成多种频率的数字控制 是 近 年 来 迅 速 发 展 起 来 的 一 种 新 的 频 率 合 成 方 控制方便 , 且具有很高的 方法应运而生 , 这种技术就是 D S 即直接数字合 法。这种方法简单可靠 、 D( 成) D S 。 D 技术是一种从相位概念出发直接合成所 频率分辨率和转换速度 ,非常适合快速跳频通信 需波形的一种新的全数字频率合成技术 。目 , 前 各 的要 求 。

/ O资源 , 并行处理数据。 具有高密度 、 高 该方法频率转换时间快 ( 小于 10 s ,但是体积 其丰富的 I 0n) 速度 、 多功能 、 低功耗 、 设计灵活方便 、 可无限次反 大、 功耗大 。

P AC L 2锁 相环合成 法 。 . 锁相 环合 成法 通 过锁相 环完 复编程等特点 ,由 F G /P D完成信号的产生 、 L D显示等。该方案的系统方框图如图 成频率的加、 、 、 减 乘 除运算 。该方法结构简化 、 便 频率控制 、E

DDS原理及基于FPGA的实现

DDS原理及基于FPGA的实现DDS(Direct Digital Synthesis)全称直接数字合成,是一种数字合成功能信号发生器的工作原理。

它是通过根据一些固定的参考信号,加上一个可控的数字增量,形成一个频率可调的数字信号。

DDS工作原理及路线图:DDS的核心是一个数字控制的累加器和一个查找表。

其具体实现如下所示:1.预先存储波形表:首先,需要在DSP处理器或FPGA中事先存储好波形表(一般是一个周期的波形值),该波形表由特定的设计方法生成,例如正弦函数合成、加窗等。

2.相位累加器:DDS在每个时钟周期内累加相位增量。

具体来说,它将前一周期的相位值与当前周期的相位增量相加,并将结果存储在一个相位累加器中。

3.相位查找:相位查找操作通过查找表来实现。

在每个时钟周期中,DDS从查找表中根据相位累加器的值来获取对应的波形数值。

4.数字输出:DDS将查找表中获取的波形数值直接转换为模拟输出信号的幅度。

基于FPGA的DDS实现:DDS在FPGA上实现具有以下优点:灵活性高、资源利用率高、功耗低、随机存取等。

基于FPGA的DDS实现主要包括以下几个关键步骤:1.数字波形表生成:使用FPGA的片上RAM(BRAM)或外部存储器存储一个周期的数字波形表。

2.相位累加器:DDS的核心是一个相位累加器,可以使用FPGA的片上计数器或者DSP48E资源实现,实现相位的累加。

3.查找表选择:DDS使用查找表来获取波形数值,可以根据需求选择合适的查找表,如ROM、LUT等,FPGA提供了不同的资源来实现查找表。

4.数字输出:DDS通过数字转模拟转换器(DAC)将输出信号转换为模拟信号。

FPGA通常具有丰富的IO资源,可直接与DAC连接。

5.控制接口:DDS通常需要提供一些控制接口,允许外部调整频率、相位、振幅等参数。

FPGA可以提供适当的接口,如基于UART或SPI的串行接口、基于GPIO的并行接口等。

总结:DDS是一种基于数字合成的信号发生器原理,通过累加器和查找表实现信号的频率可调。

基于FPGA的DDS信号发生器设计

基于FPGA的DDS信号发生器设计一、引言随着科技的不断发展,数字信号处理(Digital Signal Processing,简称DSP)在各个领域得到广泛应用。

其中,一种常见的应用是通过数字直接合成(Digital Direct Synthesis,简称DDS)来生成各种信号。

DDS信号发生器能够快速准确地产生高质量的信号,被广泛应用于通信、电子测量、医疗器械等领域。

本文将阐述基于现场可编程门阵列(Field-Programmable Gate Array,简称FPGA)的DDS信号发生器设计。

二、FPGA的简介FPGA是一种可编程的逻辑器件,其内部包含了大量可编程的逻辑单元和存储单元。

FPGA具有灵活性高、可重构性强等特点,可以根据设计者的需求,灵活地实现各种数字电路。

因此,FPGA成为DDS信号发生器设计的理想平台。

三、DDS技术原理DDS技术通过数字控制相位累加器和振荡器来实现信号的直接合成。

其中,相位累加器用于控制振荡器输出频率的连续调节,振荡器则根据相位累加器的输出产生正弦波。

DDS信号发生器的主要步骤如下:1. 初始化相位累加器:将初始相位值存入相位累加器。

2. 累加相位值:相位累加器根据设定的增量值不断累加,得到一个新的相位值。

3. 查表获得振荡器的输出值:通过查表法,根据相位值获得振荡器的输出幅度。

4. 输出信号:根据振荡器的输出幅度,形成DDS信号。

四、1. 系统架构设计:本设计采用基于FPGA的硬件逻辑实现DDS信号发生器。

系统由相位累加器、振荡器、幅度调节模块和输出模块组成。

其中,相位累加器使用FPGA中的计数器实现,振荡器采用三角函数计算逼近的方式实现,幅度调节模块用于调节振荡器的输出幅度,输出模块将DDS信号输出到外部。

2. 相位累加器设计:相位累加器是DDS信号发生器的核心模块。

本设计采用基于FPGA的计数器实现相位累加器,通过控制计数器的计数速度来调节信号的频率。

一种基于FPGA的DDS设计方案与仿真实现

一种基于FPGA的DDS设计方案与仿真实现作者:徐燕华来源:《硅谷》2009年第21期[摘要]介绍DDS的组成原理,利用VHDL语言在Altera公司的QuartusII 6.0软件平台上,采用VHDL语言利用元件例化的方法,设计并实现DDS的相位累加器和波形存储器两个主要数字环节。

软件仿真和开发板仿真试验结果均表明,该方法的DDS输出波形正确且效果好。

[关键词]DDSVHDL语言仿真中图分类号:TP3文献标识码:A文章编号:1671-7597(2009)1110056-02目前,波形发生器的设计方法主要包括三种:传统直接频率合成技术(DS,Direct frequency Synthesis)、锁相式频率合成技术(PLL,Phase-Locked Loop)、直接数字频率合成技术(DDS,Direct Digital Frequency Synthesis)。

经过多年的研究,对这三种主要的频率合成技术性能也得到了一些重要的结论[1-3]。

其中,DDS方法具有高频率稳定度、高频率分辨率、频率转换时间极短、全数字化结构便于集成等优点。

本文首先介绍了DDS的基本原理和控制方式等,同时针对FPGA开发系统及其主要描述语言VHDL语言进行了简要介绍,根据DDS产生原理设计了一种简单易实现的DDS实现方法,为信息技术教育的进一步发展提供了技术基础。

一、DDS原理与FPGA开发系统(一)DDS基本原理根据DDS的产生原理,其在结构上可以分为两个主要部分,即数字控件和模拟控件。

DDS的基本结构如图1所示。

数字控件主要包括:相位累加器、ROM波形查询表;模拟控件主要包括:数模转换器DAC、低通滤波器LPF。

图1中,相位累加器在参考时钟的控制下,以步长作累加输出;相位累加器输出的位二进制码作为波形存储器的地址,对波形ROM进行寻址;波形ROM输出的正弦幅度量化序列经D/A转换成包络为正弦波的阶梯波;此时的频谱中除了主频外,还存在分布在, …,两边±处的非谐波分量[4],幅值包络为辛格函数,因此,为了取出主频必须在DAC的输出端接入截止频率为的低通滤波器(LPF,Low Pass Filter)。

基于FPGA的DDS设计实验

基于FPGA的DDS设计实验1.1 DDS的基本原理直接数字频率合成技术(Direct Digital Frequency Synthesis,即DDFS,一般简称DDS)是从相位概念出发直接合成所需波形的一种新的频率合成技术。

近年来,技术和器件水平不断发展,这使DDS 合成技术也得到了飞速的发展,它在相对带宽、频率转换时间、相位连续性、正交输出、高分辨力以及集成化等一系列性能指标方面已远远超过了传统的频率合成技术所能达到的水平,完成了频率合成技术的又一次飞跃,是目前运用最广泛的频率合成技术。

1.1.1DDS的基本原理和优化构想DDS的主要思想是从相位的概念出发合成所需的波形,其结构由相位累加器,正弦ROM查找表, D/A转换器和低通滤波器组成。

它的基本原理框图如图1.1所示。

图1.1 DDS原理图图1.1中, fc为时钟频率, K为频率控制字, N为相位累加器的字长, m为ROM地址线位数, n为ROM的数据线宽度(一般也为D/A转换器的位数) , fo为输出频率, 输出频率fo由fC和K共同决定: fo = fC×K/2N。

又因为DDS遵循奈奎斯特(Nyquist)取样定律:即最高的输出频率是时钟频率的一半,即fo = fC/2。

实际中DDS的最高输出频率由允许输出的杂散水平决定,一般取值为fo≤40% fC。

对DDS进行优化设计,目的是在保持DDS原有优点的基础上,尽量减少硬件复杂性,降低芯片面积和功耗,提高芯片速度等。

为了减小DDS的设计成本, 对其结构进行优化,优化后DDS的核心结构框图如下所示。

图1.2优化后的DDS核心框图其中的地址转换器是根据adri[14]的数值判断数值是增长(0~π/2)或减少(π/2~π) ,数据转换器是根据adri[15]的数值判断生成波形的前半个周期(0~π)或者后半个周期(π~2π) 。

1.1.2 DDS的工作原理图1.3所示是一个基本的DDS电路工作原理框图。

基于FPGA的DDS信号发生器的设计与实现

基于FPGA的DDS信号发⽣器的设计与实现⼀、实现环境 软件:Quartus II 13.0 硬件:MP801⼆、DDS基本原理 DDS(Direct Digital Synthesizer)即数字合成器,是⼀种新型的频率合成技术,具有相对带宽⼤,频率转换时间短,分辨率⾼和相位连续性好等优点。

较容易实现频率、相位及幅度的数控调制,⼴泛应⽤于通信领域。

DDS的实现⽰意图如下图所⽰: 1、将需要合成的信号的数据存储在rom中,合成待输出信号的⽅法请参考: 2、dds_control实现的功能是将存储在rom中的待合成的信号的数据按照⼀定的规则取出来: dds_control主要由相位累加和频率累加来实现,简单的说,通过控制相位累加和频率累加来实现从rom中取出不同时刻的数据。

(1)相位累加器位数为N位(24~32),相位累加器把正弦信号在相位上的精度定义为N位,其分辨率位1/2N ,决定⼀个波形的起始时刻在哪个点; (2)频率累加器⽤来控制每隔⼏个点从rom中取⼀个数据,决定⼀个波形的频率; (3)若DDS的时钟频率为F clk ,频率控制字fword = 1,则输出频率为 F out = F clk/2N,这个频率相当于“基频”,若fword = B,则输出频率 F out = B * F clk/2N。

因此理论上由以上三个参数就可以得出任意的 f o 输出频率,且可以得出频率分辨率由时钟频率和累加器的位数决定的结论。

当参考时钟频率越⾼,累加器位数越⾼,输出频率分辨率就越⾼。

3、从FPGA中出来的信号都是数字信号(dds_control输出的信号都为数字信号),需要通过dac芯⽚来将数字信号转换为模拟信号,这样将dac芯⽚输出的信号接⼊到⽰波器中,才能看到波形; 4、举例说明频率控制和相位控制: 如上图所⽰,这个是⼀个由33个点构成的正弦波信号,(rom_addr,rom_data),纵坐标为存储在rom中的正弦波信号,横坐标为dds_control ⽣成的地址信号。

基于FPGA的DDS实验报告

基于FPGA的DDS实现实验报告1.1. 实验目的1.课程目标通过以多种方法设计并制作一个直接数字合成器,借以增强骨干班同志科研工作能力,学会具体制作实现DDS的实践技能,达到锻炼并提高学员解决实际问题能力的目的。

2.具体目的(1)信息技术资料和科技文档的搜集、编写、翻译、处理能力,采用办公应用软件如OCR、CAT、FDF-WORD、PPT等。

(2)DDS芯片硬件与软件的设计、制作及编程能力,包括信号放大、衰减、匹配和变换能力,EDA软件仿真设计能力,FPGA编程应用能力。

(3)微机应用能力,仪器仪表知识和测量方法、技术。

1.2. 实验原理直接数字频率合成器(Direct Digital Synthesizer)是从相位概念出发直接合成所需波形的一种频率合成技术。

DDS以较高的频率通过相位累加来产生给定频率的数字化波形。

根据抽样理论,产生的最高频率不能超过1/2时钟频率(Nyquist速率)。

图1、正弦波形的采样及系统时钟频率形成图1所示的是产生频率为1/8时钟频率的正弦波形的相位累加过程。

圆周表示每个时钟周期 /4相位累加过程,圆周上的各点表示给定时刻的相位值,正弦波表示相应的幅度,相位到幅度的转化是通过查表来实现的。

具体地说就是,在每个时钟周期内,存储在输入频率寄存器中的相位值和相位累加器中的值相加,利用得到的结果相位值查表,得到相应的正弦幅度值,最后输出该值。

DDS系统的基本原理图2:图2 DDS系统的原理图由图2可知,我们用FPGA实现N位相位累加器和波形存储器,DAC芯片实现数模转换,模拟电路实现滤波器。

相位累加器可对频率控制字的2进制码进行累加运算,产生的累加结果作为ROM查找表的取样地址值,而此查找表中储存了一个周期的正弦波幅度值。

存储器ROM在参考时钟驱动下输出正弦波幅度值,直到相位累加器加满产生溢出,从而完成一个周期,用ROM的输出值来驱动DAC,然后经滤波即可转换成所需要的模拟正弦波形,也就是DDS信号的频率周期。

基于fpga的dds正弦信号发生器的设计和实现

基于fpga的dds正弦信号发生器的设计和实现

基于FPGA的DDS正弦信号发生器可以使用两种常见的实现

方法:Look-Up Table (LUT) 方法和相位累积器方法。

1. LUT方法:

- 首先,定义一个存储正弦波样本值的LUT (Look-Up Table),LUT的大小取决于所需的精度和波形频率范围。

- 使用一个计数器来生成一个相位值,该相位值是一个0到LUT大小之间的数字。

- 将该相位值作为索引,通过查找LUT来获取对应的正弦波

样本值。

- 将该正弦波样本值通过数字-模拟转换器(DAC)转换为模拟

信号输出。

2. 相位累积器方法:

- 使用一个固定频率的时钟作为参考信号输入,例如50 MHz。

- 使用一个相位累积器累积每个时钟周期的相位值。

- 计算相位值对应的正弦波样本值,并通过DAC转换为模拟信号输出。

- 相位累积器的更新频率由所需的输出频率确定,可以通过

增加或减小相位值的增量来调节输出频率。

需要注意的是,FPGA上实现DDS正弦信号发生器时,需要

一个高速的DAC来将数字信号转换为模拟信号输出。

同时,

为了提高性能和减少功耗,可以采用流水线技术,通过并行处理来提高输出频率的精度和速度。

此外,还可以通过添加相位调制、振幅调制等功能来进一步扩展DDS正弦信号发生器的

功能。

要设计和实现基于FPGA的DDS正弦信号发生器,可以使用硬件描述语言如Verilog或VHDL编写相应的代码,并使用FPGA开发工具进行综合、布局以及生成比特流文件。

最后,将比特流文件加载到目标FPGA芯片上,就可以实现DDS正弦信号发生器的功能。

基于FPGA实现DDS的设计

基于FPGA实现DDS的设计作者:赵霞李书领来源:《电脑知识与技术》2013年第17期摘要:数字频率合成技术是近代通信系统的重要的一个组成部分,在电子系统以及无线电技术中的应用都是非常广泛的。

为了满足现代电子技术迅猛的发展,电子系统对信号源的要求指标也变的越来越高,在满足高频率分辨率等基本指标体系的同时也要满足快速变频、低功耗的指标,该文对DDS进行了一些简单的探讨。

关键词:寄存器;FPGA;DDS;D/A中图分类号:TP311 文献标识码:A 文章编号:1009-3044(2013)17-4130-02数字频率合成器DDS(Direct Digital Frequency Synthesizer)是多用及专用芯片的形式实现。

目前很多公司都自己生产出了具有优越性能的频率合成器的专用的芯片,由于目前一些许多公司自己成产出来的具有专用功能的芯片在大多数使用的情况下都不能够再满足广大的使用者的要求,因而我们现在研究采用大规模集成电路FPGA来进行去实现能够具备有特定功能的数字频率合成器是具有着非常重要的意义。

1 DDS的概述在现代的工业自动化系统中,往往需要采用一些信号来作为测量的基准信号或者是输出的信号。

为了满足现代电子技术迅猛的发展,现代的电子测量技术在对信号频率的精确度和稳定度的要求上已经变得越来越严格。

因而对信号源采用直接数字频率合成器DDS(Direct Digital Frequency Synthesizer)来进行实现,以这种方法设计出来的信号源能够满足在调制状态的工作下,能够对输出电平的进行调节。

数字频率合成器的基本结构包括:相位累加器、正弦查找表、数模转换器以及低通滤波器。

1.1 频率合成器的基本概念以及主要的技术指标频率合成器的基本概念就是指从一个或者多个高稳定和准确的参考频率,经过多种技术的处理,生成大量的频率输出。

技术处理的方法:可以用传统的硬件实现频率的加、减、乘、除等基本运算,也可以采用锁相技术或者是各种数字技术和计算技术。

基于fpga的dds信号发生器实现方法

基于fpga的dds信号发生器实现方法基于FPGA的DDS信号发生器可以实现高精度、高速率、高可靠性的信号发生。

DDS即直接数字频率合成技术,通过数字控制实现对信号的精确控制,从而生成各种复杂的信号。

其基本原理是将频率可调的数字信号直接进行混频、加权求和等数学处理,得到所需的复杂信号。

在实现基于FPGA的DDS信号发生器时,需要进行如下步骤:

1. 确定FPGA芯片型号和开发环境:根据需求选择合适的FPGA 芯片,同时选择相应的开发环境,如Quartus II、Xilinx ISE等。

2. 编写Verilog/VHDL代码:根据DDS原理,编写相应的Verilog/VHDL代码,实现数字控制和信号处理等功能。

3. 设计电路板:根据芯片的引脚布局,设计相应的电路板,包括时钟电路、功率供应电路、信号输入/输出接口等。

4. 调试和验证:对设计好的电路板进行调试和验证,确保实现的DDS信号发生器能够正常工作。

5. 优化和扩展:根据需求,对实现的DDS信号发生器进行优化和扩展,如增加信号处理模块、扩大频率范围等。

综上所述,基于FPGA的DDS信号发生器是一种高效、高精度、高可靠性的信号发生器,可广泛应用于通信、电子、航空、军事等领域。

其实现方法包括选型、编写代码、设计电路板、调试验证和优化扩展等步骤。

- 1 -。

简述DDS原理及其基于FPGA的实现

简述DDS原理及其基于FPGA的实现

DDS 同DSP(数字信号处理)一样,是一项关键的数字化技术。

DDS 是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写。

与传统的频率合成器相比,DDS 具有低成本、低功耗、高分辨率和快速转换时间等优点,广泛使用在电信与电子仪器领域,是实现设备全数字化的一个关键技术。

在各

行各业的测试应用中,信号源扮演着极为重要的作用。

但信号源具有许多不同

的类型,不同类型的信号源在功能和特性上各不相同,分别适用于许多不同的

应用。

目前,最常见的信号源类型包括任意波形发生器,函数发生器,RF 信

号源,以及基本的模拟输出模块。

信号源中采用DDS 技术在当前的测试测量

行业已经逐渐称为一种主流的做法。

利用它来设计符合自己需要的DDS 电路

是一个很好的解决方法。

1 DDS 的基本原理

DDS 的主要思想是从相位的概念出发合成所需要的波形,其结构由相位累加器、波形存储器、数模转换器、低通滤波器和参考时钟五部分组成,其基本原

理框图如图1 所示。

综上所述,在采样频率一定的情况下,可以通过控制频率控制字K 来控制所得离散序列的频率,经保持、滤波之后可唯一地恢复出此频率的模拟信号。

tips:感谢大家的阅读,本文由我司收集整编。

仅供参阅!。

基于FPGA的DDS设计及实现

基于FPGA的DDS设计及实现0 引言随着现代电子技术的不断发展,在通信系统中往往需要在一定频率范围内提供一系列稳定和准确的频率信号,一般的振荡器己不能满足要求,这就需要频率合成技术。

直接数字频率合成(Direct Digital Frequency Synthesis,DDS)是把一系列数据量形式的信号通过D/A 转换器转换成模拟量形式的信号合成技术。

DDS 具有相对带宽宽、频率转换时间短、频率分辨率高、输出相位连续、可产生宽带正交信号及其他多种调制信号等优点,已成为现代频率合成技术中的姣姣者。

目前在高频领域中,专用DDS 芯片在控制方式、频率控制等方面与系统的要求差距很大,利用FPGA 来设计符合自己需要的DDS 系统就是一个很好的解决方法。

现场可编程门阵列(FPGA)器件具有工作速度快、集成度高、可靠性高和现场可编程等优点,并且FPGA 支持系统现场修改和调试,由此设计的DDS 电路简单,性能稳定,也基本能满足绝大多数通信系统的使用要求。

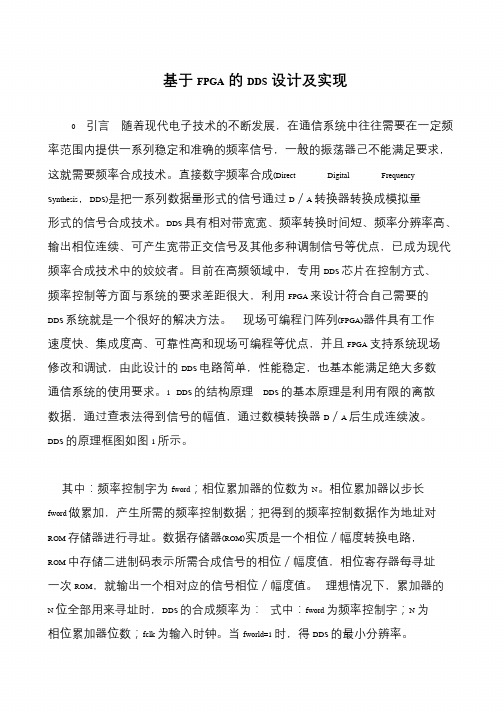

1 DDS 的结构原理DDS 的基本原理是利用有限的离散数据,通过查表法得到信号的幅值,通过数模转换器D/A 后生成连续波。

DDS 的原理框图如图1 所示。

其中:频率控制字为fword;相位累加器的位数为N。

相位累加器以步长fword 做累加,产生所需的频率控制数据;把得到的频率控制数据作为地址对ROM 存储器进行寻址。

数据存储器(ROM)实质是一个相位/幅度转换电路,ROM 中存储二进制码表示所需合成信号的相位/幅度值,相位寄存器每寻址一次ROM,就输出一个相对应的信号相位/幅度值。

理想情况下,累加器的N 位全部用来寻址时,DDS 的合成频率为:式中:fword 为频率控制字;N 为相位累加器位数;fclk 为输入时钟。

当fworld=1 时,得DDS 的最小分辨率。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

收稿日期:2006203209作者简介:常春波(1979-),研究方向为数字信号处理算法在FPG A 上的实现及应用。

第27卷 第5期太原科技大学学报Vol .27 No .52006年10月JOURNAL OF T A I Y UAN UN I V ERSI TY OF SC I E NCE AND TECHNOLOGYOct .2006文章编号:1673-2057(2006)05-0340-04一种基于FPG A 的DDS 算法的简化实现常春波(太原科技大学电子信息工程学院,太原030024) 摘 要:在分析了传统的DDS 算法的基础上,提出了一种改进方案,使得系统的复杂度降低,更趋于模块化,产生的波形频率更准确。

输出采用一个周期8个采样点的定点输出,系统时钟频率为80MHz,信号的谐波小于70d B 。

输出信号的范围为DC 到10MHz,信号频率的步长为0.1Hz,相应的转换速度为12.5ns 。

关键词:FPG A;DDS;循环相位累加器中图分类号:T N91413 文献标识码:A 由于DDS (D irect D igital Synthesizer )具有快速频率切换时间、极高的频率精度和分辨率以及易于控制各种调制方式等优点,近年来在通信、雷达和软件无线电等现代通信系统中得到了愈来愈广泛的应用。

但是很多DDS 专用芯片不具备LF M 功能,而且只能在固定的工作方式下使用。

随着VLSI 技术的进步,现在FPG A (Field Pr o 2gra mmable Gate A rray )的性能和硬件资源已经可以构成一个系统。

如果用FPG A 来实现DDS,则可以根据用户需要进行设计,而且能在系统上灵活地改变系统结构。

但是传统的基于FPG A 的DDS 算法在某些应用中资源利用率不高,输出频率不够精准,需要加以改进或简化。

1 传统的DD S 结构及缺陷1.1 结构传统的直接数字频率合成器的核心采用的结构最先由Tierney 、Rader 和Gold 提出[2],如图1所示。

它利用可溢出的L 位累加器(或称相位累加器)产生正弦函数的相位变量。

相位累加器每溢出一次,就代表正弦波形的一个周期。

相位累加器输入的频率控制字(FC W )来控制生成的正弦波形的频率,累加器的高位输出作为ROM 查找表的地址信号。

ROM 查找表是存有正弦采样值的存储器。

这种频率合成方法可以在不增加ROM 查找表容量的情况下,获得较高的频率精度。

相位累加器每增加一位,频率精度就提高2倍。

直接数字频率合成器的输出频率fout 可以由下式确定:图1 传统的DD S 核心结构F i g .1The core structure of trad iti ona l DD Sf ou t =f clk ・FC W2L(1) 其中,FC W 为频率控制字,f clk 为时钟频率,L 为相位累加器的字长。

最小频率精度Δf 为:Δf =f clk2L(2) 当相位累加器字长为32位,最高时钟频率为80MHz 时,最小频率精度约为0.0186Hz,两个频率之间的转换时间为一个时钟,对于80MHz,转换时间为12.5ns 。

1.2 传统DD S 结构的缺陷(1)频率的最小步进值的尾数不是零。

在上文的计算中,最小频率只是取四舍五入值约为0.0186Hz,这种情况的出现,会给以后频率的合成带来很大的不便。

例如,如果要求产生频率为0.2Hz 的正弦波,当FC W =10时,f ou t =0.186Hz ;当FC W =11时,f ou t =0.205Hz 。

出现误差的原因在于公式当中f clk 不能被2L整除,使得最后的计算值也不是整数。

(2)传统DDS 结构中的RO M 表,即正弦采样数据的存储一般有两种方式:一种采用整周期存储,这样除了需要大容量的RO M 外,还会降低系统速度;另一种运用一定的算法,只存储1/4波形的数据,这样节省了RO M 的空间,却增加了系统的复杂度。

(3)经过分析,在一定条件下,传统DDS 结构可能会发生两个不同的FC W 产生同一频率正弦波的现象。

为作图方便,设相位累加器的字长为4,当FC W 的值分别为4和5时,波形如图2,3所示。

图2 FCW =4时累加器的状态F i g .2The st a te of adder when FC W =4图3 FCW =5时累加器的状态F i g .3The st a te of adder when FC W =5 由于相位累加器的溢出表示正弦波一个周期的结束,从图中可以看到,当FC W 为4或5时,每一个周期均为4个脉冲,这样,最后生成的正弦波的周期或频率是相同的。

进一步分析,当FC W =5时,累加器在15加5时,只加一个单位,就会发生溢出,从而结束一个周期,导致一个周期只有4个脉冲,最后留下4个单位的误差。

当相位累加器的字长为8时,经过计算可以得到,当FC W 的取值在52到63时,每一个周期均为5个脉冲,最后得到的正弦波的周期也是相同的。

2 改进的DD S 结构改进后的DDS 结构如图4所示,主要由循环相位累加器、地址信号发生器和ROM 查找表组成。

图4 改进后DD S 的核心结构F i g .4The core structure of opti m i zed DD S2.1 循环相位累加器循环相位累加器与传统的相位累加器的功能类似,但又有三点不同:(1)以循环相位累加器的溢出信号作为其后地址信号发生器的时钟,而不用累加器的高位输出作为地址信号。

这样作,既可以避免因累加器高位输出信号不同步引起的竞争冒险问题,同时也降低了系统的复杂度,使其组成更趋于模块化。

(2)累加器加到最大值溢出后,以余值而不是零作为下一次累加的起始值。

例如,当FC W =3,最大值为100时,加到99时,再加3,累加器溢出,输出一个脉冲的同时,以2作为下一次累加的起始值,依次循环。

这样可以源头上避免因舍掉余值而引起的频率误差。

(3)循环相位累加器设置一个可调的最大值,而不是满偏值作为溢出值。

例如,当累加器的字长为4时,可以设置10而不是16作为溢出值。

这样设计,可以灵活地改变最大值,也就是累加器的模值,使得最后的步进值成为一个尾数为零的数,不需要四舍五入,从而避免在合成频率时,频率余数的产生,使得到的频率更加精准。

一个简单的循环相位累加器的工作波形如图5所示。

图5中分别为FC W 为3,4,5时的循环相位累143第27卷第5期 常春波:一种基于FPG A 的DDS 算法的简化实现加器的状态和溢出信号。

由图可以看到,当FC W 分别为3,4,5时,每10个脉冲,将分别会有3,4,5个脉冲从累加器输出,且当累加器溢出时有余值时,将以余值作为下一次累加的起始值,不会出现因舍掉余数而引起的误差。

这种设计方式,可以从源头上避免频率误差的产生。

图5 模值为10的循环相位累加器的工作波形Fi g .5The wavefor m of cycle pha se adder with M ode 102.2 DD S 频率输出的计算公式改进后的DDS 输出频率的计算公式如下:f ou t =f clk ・FC WMode ・N(3) 其中,FC W 为频率控制字,Mode 为循环相位累加器的最大值,即模值,这个模值是可预先设定的,可以为任意数,但一般选取以使最小步进频率为尾数为零的数,N 为正弦波一个周期所包含的采样点数,本文设计中,最高时钟频率是80MHz,Mode 为1×108,N 为8,则:f ou t=80×106・FC W1×108×8=0.1FC W (4)最小频率精度Δf 为:Δf =0.1Hz 。

当FC W =2时,得到频率为0.2Hz 的正弦波,显然没有误差。

当FC W=1×108时,得到输出的最高频率10MHz 。

若想提高输出的最高频率,需要减少N 的值。

例如当N =4时,最高频率为20MHz 。

当然,不能超过采样定理的极限,即,输出的最高频率为40MHz 。

若想提高最小频率精度Δf,则需增大Mode 的值。

例如当Mode =1×109时,Δf =0.01Hz 。

3 编程实现依据改进后的算法在A ltera 公司的Quarters Ⅱ5.0软件中进行编译、综合、仿真,其中核心的循环相位累加器的程序如下,为了便于仿真,将最大模值设为50。

library ieee;use ieee .std_l ogic_1164.all;entity adder isport (clk:in std_l ogic; f word:in integer range 0t o 100; out put:out integer range 0t o 100; outte mp:out integer range 0t o 100; clkout:out std_l ogic );end adder;architecture one of adder issignal con:integer range 0t o 100:=0;signal conte mp:integer range 0t o 100;beginp r ocess (clk,f word,con )variable tup,tdown:std_l ogic;begin conte mp <=con +f word; if (clk’event and clk =’1’)then if conte mp >50then con <=conte mp -50;tup:=’1’; elsif conte mp =50then con <=0;tup:=’1’; else con <=conte mp;tup:=’0’; end if; end if; if (clk’event and clk =’0’)then if conte mp >=50then tdown:=’1’; else tdown:=’0’; end if; end if; clkout <=tup and clk and tdown; out put <=con; outte mp <=conte mp;end p r ocess;end one;仿真图如下:图6 循环相位累加器的仿真图F i g .6The si m ul a ti on of cycle pha se adder243 太原科技大学学报 2006年 由图6可以看到,当模值为50,频率字为20时,每输入50个脉冲,输出20个脉冲,输出频率的计算公式如下:f ou t =f clk ・2050・N=25・f clkN(5)所设计的循环相位累加器的功能符合要求,将编译好的文件下载到Cycl one 系列器件EP1C6TC 144中图7 输出信号的频率特性F i g .7The frequency character isti cs of output si gna l进行验证,其中的数字输出可以输出到板上的SRAM 芯片中,然后上载到计算机进行数字信号分析;模拟输出则通过HP 示波器测试。