AEC-Q100 G 中文版

恩智浦推出带中断和复位功能且符合AEC-Q100标准的GP10

自I m a g i n a t i o n于今 年初 完 成 M I P S并 购交 易

后, 便 已将 其 C P U工程团队纳入编制 , 并 以将近一 倍的资源投入先进的 M I P S C P U开发。该公司正准 备大量投资 于 M I P S 开发 , 包括工具 、 编译器 、 除错 器、 操作系统 、 软件以及其他 。( 来 自I m a g i n a t i o n )

自上 海光 芯 )

2 0 n m S o C 测试芯 片成功流 片

C a d e n c e 设 计 系统公 司 日前 宣布 , 设计 服 务公 司

创意 电子 ( G U C) 使用 C a d e n c e  ̄E n c o u n t e r  ̄ 数字

实 现系统 ( E D I ) 和C a d e n c e光刻物 理 分析器 成 功完 成2 0 n m 系统 级 芯 片 ( S o C) 测 试芯 片 流 片 。双方 工 程师 通 过 紧密合 作 ,运 用 C a d e n c e解决 方案 克 服实 施和 可制 造 性设计 ( D F M) 验 证挑 战 , 并 最终 完成 设

C a d e n c e L i t h o P h y s i c a l A n a l y z e r( 光刻 物 理分 析器 ) 用于 D F M 验证 , 将 2 0 n m工 艺变 化 的不 确定 性 变 成 可 预见 影 响从 而有 助 于缩 短 设 计周 期 。 ( 来 自

2020年AECQ100详解:起源、包含项目及目的作用

2020年AECQ100详解:起源、包含项⽬及⽬的作⽤AECQ100的起源AEC全称:Automotive Electronics Council ,中⽂名:汽车电⼦协会。

由Chrysler(克莱斯勒)、Ford(福特)、GM(通⽤)发起并于1994年创⽴。

AEC⽬的:针对车载应⽤,汽车零部件,汽车车载电⼦实施标准规范,建⽴车载电⼦部件的可靠性及认定标准规格化质量控制标准,提⾼车载电⼦的稳定性和标准化。

AECQ即国际汽车电⼦协会车规验证标准。

包括AEC-Q100(集成电路IC)、AEC-Q101(离散组件)、AEC-Q102(离散光电LED)、AEC-Q104(多芯⽚组件)、AEC-Q200(被动组件)。

进⼊汽车领域,则必须取得汽车电⼦协会的AECQ可靠度标准,以及零失效(Zero Defect)的供应链质量管理标准IATF16949规范。

AEC-Q100包含项⽬对汽车车载电⼦零部件测试标准以AEC-Q100-(001~012),AEC-Q101,AEC-Q200为最常见。

其中AEC-Q100是AEC的第⼀个标准,于1994年6⽉⾸次发表,现经过了⼗多年的发展,AEC-Q100已经成为汽车电⼦系统的通⽤标准。

对于车⽤芯⽚来说AEC-Q100也是最常见的应⼒测试(Stress Test)认证规范。

AEC-Q100详细规定了⼀系列的测试,同时定义了应⼒测试驱动型认证的最低要求以及IC认证的参考测试条件。

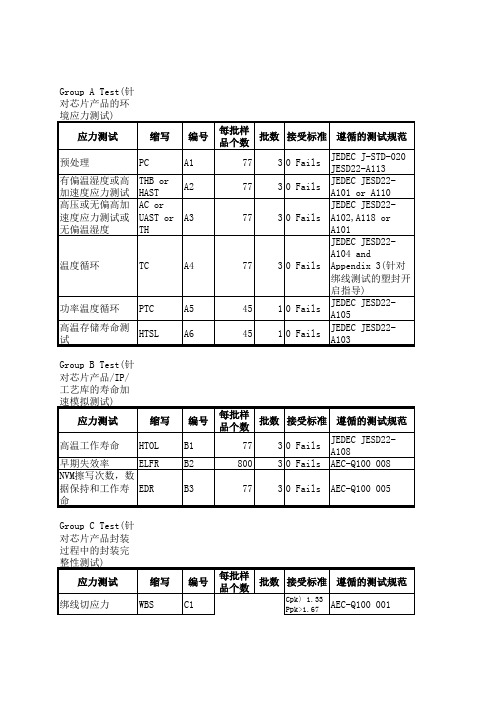

这些测试包括7个测试群组:测试群组A(环境压⼒加速测试,Accelerated Environment Stress)测试群组B(使⽤寿命模拟测试,Accelerated Lifetime Simulation)测试群组C(封装组装整合测试,Package Assembly Integrity)测试群组D(芯⽚晶圆可靠度测试,Die Fabrication Reliability)测试群组E(电⽓特性确认测试,Electrical Verification)测试群组F(瑕疵筛选监控测试,Defect Screening)测试群组G(封装凹陷整合测试,Cavity Package Integrity)此外,为了达到汽车电⼦产品对⼯作温度、耐久性与可靠度的⾼标准要求,组件供货商必须采⽤更先进的技术和更苛刻的测试程序来达成最佳化的设计⽅法。

AEC-Q100_Rev_G_EN

AEC - Q100 - Rev-GMay 14, 2007FAILURE MECHANISM BASED STRESS TEST QUALIFICATIONFORINTEGRATED CIRCUITSComponent Technical CommitteeAutomotive Electronics CouncilComponent Technical CommitteeTABLE OF CONTENTSAEC-Q100 Failure Mechanism Based Stress Test Qualification for Integrated Circuits Appendix 1: Definition of a Qualification FamilyAppendix 2: Q100 Certification of Design, Construction and QualificationAppendix 3: Plastic Package Opening for Wire Bond TestingAppendix 4: Minimum Requirements for Qualification Plans and ResultsAppendix 5: Part Design Criteria to Determine Need for EMC TestingAppendix 6: Part Design Criteria to Determine Need for SER TestingAttachmentsAEC-Q100-001: WIRE BOND SHEAR TESTAEC-Q100-002: HUMAN BODY MODEL (HBM) ELECTROSTATIC DISCHARGE (ESD) TEST AEC-Q100-003: MACHINE MODEL (MM) ELECTROSTATIC DISCHARGE (ESD) TESTAEC-Q100-004: IC LATCH-UP TESTAEC-Q100-005: NONVOLATILE MEMORY WRITE/ERASE ENDURANCE, DATA RETENTION, AND OPERATIONAL LIFE TESTAEC-Q100-006: ELECTRO-THERMALLY INDUCED PARASITIC GATE LEAKAGE (GL) TEST AEC-Q100-007: FAULT SIMULATION AND TEST GRADINGAEC-Q100-008: EARLY LIFE FAILURE RATE (ELFR)AEC-Q100-009: ELECTRICAL DISTRIBUTION ASSESSMENTAEC-Q100-010: SOLDER BALL SHEAR TESTAEC-Q100-011: CHARGED DEVICE MODEL (CDM) ELECTROSTATIC DISCHARGE (ESD) TESTAEC-Q100-012: SHORT CIRCUIT RELIABILITY CHARACTERIZATION OF SMART POWER DEVICES FOR 12V SYSTEMSComponent Technical CommitteeAcknowledgmentAny document involving a complex technology brings together experience and skills from many sources. The Automotive Electronics Council would especially like to recognize the following significant contributors to the revision of this document:Sustaining Members:Mark A. Kelly Delphi CorporationJean Clarac Siemens VDOBrian Jendro Siemens VDOHadi Mehrooz Siemens VDORobert V. Knoell Visteon CorporationAssociate Members: Guest Members:Tim Haifley Altera David Locker AMRDECDaniel Vanderstraeten AMI Semiconductor Jeff Jarvis AMRDECEarl Fischer AutolivMike Klucher Cirrus LogicXin Miao Zhao Cirrus LogicJohn Timms Continental Automotive SystemsRoy Ozark Continental Automotive SystemsNick Lycoudes FreescaleKenton Van Klompenberg GentexWerner Kanert Infineon TechnologiesElfriede Geyer Infineon TechnologiesJohn Bertaux International RectifierGary Fisher Johnson ControlsTom Lawler Lattice SemiconductorSohail Malik Lattice SemiconductorScott Daniels MaximTom Tobin MaximMike Buzinski MicrochipRob Horton MicrochipAnnette Nettles NEC ElectronicsMasamichi Murase NEC ElectronicsZhongning Liang NXP SemiconductorsMark Gabrielle ON SemiconductorKen Berry Renesas TechnologyBruce Townsend SpansionAdam Fogle SpansionBrian Mielewski STMicroelectronicsJames Williams Texas InstrumentsDiana Siddall Texas InstrumentsAnca Voicu XilinxOther Contributors:Lewis Venters Cirrus LogicPeter Kowalczyk Delphi CorporationJoe Wurts MaximDon Pecko XilinxComponent Technical CommitteeNOTICEAEC documents contain material that has been prepared, reviewed, and approved through the AEC Technical Committee.AEC documents are designed to serve the automotive electronics industry through eliminating misunderstandings between manufacturers and purchasers, facilitating interchangeability and improvement of products, and assisting the purchaser in selecting and obtaining with minimum delay the proper product for use by those other than AEC members, whether the standard is to be used either domestically or internationally.AEC documents are adopted without regard to whether or not their adoption may involve patents or articles, materials, or processes. By such action AEC does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the AEC documents. The information included in AEC documents represents a sound approach to product specification and application, principally from the automotive electronics system manufacturer viewpoint. No claims to be in Conformance with this document shall be made unless all requirements stated in the document are met.Inquiries, comments, and suggestions relative to the content of this AEC document should be addressed to the AEC Technical Committee on the link .Published by the Automotive Electronics Council.This document may be downloaded free of charge, however AEC retains the copyright on this material. By downloading this file, the individual agrees not to charge for or resell the resulting material.Printed in the U.S.A.All rights reservedCopyright © 2007 by Delphi, Siemens VDO, and Visteon Corporation. This document may be freely reprinted with this copyright notice. This document cannot be changed without approval from the AEC Component Technical Committee.Component Technical CommitteeFAILURE MECHANISM BASED STRESS TEST QUALIFICATIONFOR PACKAGED INTEGRATED CIRCUITSText enhancements and differences made since the last revision of this document are shown as underlined areas. Several figures and tables have also been revised, but changes to these areas have not been underlined.1. SCOPEThis document contains a set of failure mechanism based stress tests and defines the minimum stress test driven qualification requirements and references test conditions for qualification of integrated circuits (ICs). These tests are capable of stimulating and precipitating semiconductor device and package failures. The objective is to precipitate failures in an accelerated manner compared to use conditions.This set of tests should not be used indiscriminately. Each qualification project should be examined for:a. Any potential new and unique failure mechanisms.b. Any situation where these tests/conditions may induce failures that would not be seen in theapplication.c. Any extreme use condition and/or application that could adversely reduce the acceleration.Use of this document does not relieve the IC supplier of their responsibility to meet their own company's internal qualification program. In this document, "user" is defined as all customers using a device qualified per this specification. The user is responsible to confirm and validate all qualification data that substantiates conformance to this document. Supplier usage of the device temperature grades as stated in this specification in their part information is strongly encouraged.1.1 PurposeThe purpose of this specification is to determine that a device is capable of passing the specified stress tests and thus can be expected to give a certain level of quality/reliability in the application.1.2 Reference DocumentsCurrent revision of the referenced documents will be in effect at the date of agreement to the qualification plan. Subsequent qualification plans will automatically use updated revisions of these referenced documents.1.2.1 AutomotiveAEC-Q001 Guidelines for Part Average TestingAEC-Q002 Guidelines for Statistical Yield AnalysisAEC-Q003 Guidelines for Characterizing the Electrical PerformanceAEC-Q004 Zero Defects Guideline (DRAFT)SAE J1752/3 Integrated Circuits Radiated Emissions Measurement Procedure1.2.2 MilitaryMIL-STD-883 Test Methods and Procedures for MicroelectronicsComponent Technical Committee1.2.3 IndustrialJEDEC JESD-22 Reliability Test Methods for Packaged DevicesEIA/JESD78 IC Latch-Up TestUL-STD-94 Tests for Flammability of Plastic materials for parts in Devices and AppliancesIPC/JEDEC J-STD-020 Moisture/Reflow Sensitivity Classification for Plastic Integrated Circuit Surface Mount DevicesJESD89 Measurement and Reporting of Alpha Particle and Terrestrial Cosmic Ray-Induced Soft Errors in Semiconductor DevicesJESD89-1 System Soft Error Rate (SSER) Test MethodJESD89-2 Test Method For Alpha Source Accelerated Soft Error RateJESD89-3 Test Method for Beam Accelerated Soft Error Rate1.3 Definitions1.3.1 AEC Q100 QualificationSuccessful completion and documentation of the test results from requirements outlined in this document allows the supplier to claim that the part is “AEC Q100 qualified”. The supplier, in agreement with the user, can perform qualification at sample sizes and conditions less stringent than what this document requires. However, that part cannot be considered “AEC Q100 qualified” until such time that the unfulfilled requirements can be completed.1.3.2 Approval for Use in an Application"Approval" is defined as user approval for use of a part in their application. The user's method of approval is beyond the scope of this document.1.3.3 Definition of Part Operating Temperature GradeThe part operating temperature grades are defined below:Grade 0: -40°C to +150°C ambient operating temperature rangeGrade 1: -40°C to +125°C ambient operating temperature rangeGrade 2: -40°C to +105°C ambient operating temperature rangeGrade 3: -40°C to +85°C ambient operating temperature rangeGrade 4: 0°C to +70°C ambient operating temperature range2. GENERAL REQUIREMENTS2.1 ObjectiveThe objective of this specification is to establish a standard that defines operating temperature grades for integrated circuits based on a minimum set of qualification requirements.Component Technical Committee2.1.1 Zero DefectsQualification and some other aspects of this document are a subset of, and contribute to, theachievement of the goal of Zero Defects. Elements needed to implement a zero defects program can be found in AEC-Q004 Zero Defects Guideline.2.2 Precedence of RequirementsIn the event of conflict in the requirements of this standard and those of any other documents, the following order of precedence applies:a. The purchase orderb. The individual device specificationc. This documentd. The reference documents in section 1.2 of this documente. The supplier's data sheetFor the device to be considered a qualified part per this specification, the purchase order and/or the individual device specification cannot waive or detract from the requirements of this document.2.3 Use of Generic Data to Satisfy Qualification and Requalification Requirements2.3.1 Definition of Generic DataThe use of generic data to simplify the qualification process is strongly encouraged. Generic data can be submitted to the user as soon as it becomes available to determine the need for any additional testing. To be considered, the generic data must be based on a matrix of specific requirements associated with each characteristic of the device and manufacturing process as shown in Table 3 and Appendix 1. If the generic data contains any failures, the data is not usable as generic data unless the supplier has documented and implemented corrective action or containment for the failure condition that is acceptable to the user.Appendix 1 defines the criteria by which components are grouped into a qualification family for the purpose of considering the data from all family members to be equal and generically acceptable for the qualification of the device in question. For each stress test, two or more qualification families can be combined if the reasoning is technically sound (i.e., supported by data).Component Technical CommitteeTable 1: Part Qualification/Requalification Lot Requirements Part Information Lot Requirements for Qualification New device, no applicable generic data. Lot and sample size requirements per Table 2.A part in a family is qualified. The part to be qualified is less complex and meets the Family Qualification Definition per Appendix 1. Only device specific tests as defined in section 4.2 are required. Lot and sample size requirements per Table 2 for the required tests.A new part that has some applicable generic data. Review Appendix 4 to determine required tests from Table 2. Lot and sample sizes per Table 2 for the required tests.Part process change. Review Table 3 to determine which tests from Table 2 are required. Lot and sample sizes per Table 2 for the required tests.Part was environmentally tested to all the test extremes, but was electrically end-point tested at a temperature less than the Grade required. The electrical end-point testing on at least 1 lot (that completed qualification testing) must meet or exceed the temperature extremes for the device Grade required. Sample sizes shall be per Table 2.Qualification/Requalification involving multiplesites.Refer to Appendix 1, section 3.Qualification/Requalification involving multiplefamilies.Refer to Appendix 1, section 3.With proper attention to these qualification family guidelines, information applicable to other devices in the family can be accumulated. This information can be used to demonstrate generic reliability of a device family and minimize the need for device-specific qualification test programs. This can be achieved through qualification and monitoring of the most complex (e.g., more memory, A/D, larger die size) device in the qualification family and applying this data to less complex devices that subsequently join this family. Sources of generic data should come from supplier-certified test labs, and can include internal supplier's qualifications, cell structure/standard circuit characterization and testing, user-specific qualifications, and supplier's in-process monitors. The generic data to be submitted must meet or exceed the test conditions specified in Table 2. End-point test temperatures must address the worst case temperature extremes for the device operating temperature grade being qualified on at least one lot of data. Failure to do so will result in the supplier testing 1 lot or, if there is no applicable or acceptable existing generic data, 3 lots for the stress test(s) in question on the device to be qualified. The user(s) will be the final authority on the acceptance of generic data in lieu of test data.Table 3 defines a set of qualification tests that must be considered for any changes proposed for the component. The Table 3 matrix is the same for both new processes and requalification associated with a process change. This table is a superset of tests that the supplier and user should use as a baseline for discussion of tests that are required for the qualification in question. It is the supplier's responsibility to present rationale for why any of the recommended tests need not be performed.Component Technical Committee2.3.3Time Limit for Acceptance of Generic DataThere are no time limits for the acceptability of generic data as long as all reliability data taken since the initial qualification is submitted to the user for evaluation. This data must come from the specific part or a part in the same qualification family, as defined in Appendix 1. This data includes any customer specific data (if customer is non-AEC, withhold customer name), process change qualification, and periodic reliability monitor data (see Figure 1).HistoryPresentPeriodic Reliability Monitor TestsQ u a l i f i c a t i o n d a t a + P r o c e s s c h a n g e q u a l i f i c a t i o n d a t a +R e l i a b i l i t y m o n i t o r d a t a =a c c e p t a b l e g e n e r i c d a t aP r o c e s s C h a n g e Q u a l i f i c a t i o nC u s t o m e r #2S p e c i f i c Q u a l i f i c a t i o nP r o c e s s C h a n g e Q u a l i f i c a t i o nC u s t o m e r #1S p e c i f i c Q u a l i f i c a t i o nI n t e r n a l D e v i c e C h a r a c t e r i z a t i o nS u p p l i e r I n t e r n a l Q u a l i f i c a t i o nS u p p l i e r S t a r t o f P r o d u c t i o nNote:Some process changes (e.g., die shrink) will affect the use ofgeneric data such that data obtained before these types of changes will not be acceptable for use as generic data.Figure 1: Generic Data Time Line2.4 Test Samples2.4.1 Lot RequirementsTest samples shall consist of a representative device from the qualification family. Where multiple lot testing is required due to a lack of generic data, test samples as indicated in Table 2 must be composed of approximately equal numbers from non-consecutive wafer lots, assembled in non-consecutive molding lots. That is, they must be separated in the fab or assembly process line by at least one non-qualification lot.2.4.2 Production RequirementsAll qualification devices shall be produced on tooling and processes at the manufacturing site that will be used to support part deliveries at production volumes. Other electrical test sites may be used for electrical measurements after their electrical quality is validated.Component Technical Committee2.4.3 Reusability of Test SamplesDevices that have been used for nondestructive qualification tests may be used to populate other qualification tests. Devices that have been used for destructive qualification tests may not be used any further except for engineering analysis.2.4.4 Sample Size RequirementsSample sizes used for qualification testing and/or generic data submission must be consistent with the specified minimum sample sizes and acceptance criteria in Table 2.If the supplier elects to use generic data for qualification, the specific test conditions and results must be recorded and available to the user (preferably in the format shown in Appendix 4). Existing applicable generic data should first be used to satisfy these requirements and those of section 2.3 for each test requirement in Table 2. Device specific qualification testing should be performed if the generic data does not satisfy these requirements.2.4.5 Pre- and Post-stress Test RequirementsEnd-point test temperatures (room, hot and/or cold) are specified in the "Additional Requirements" column of Table 2 for each test. The specific value of temperature must address the worst case operating temperature grade extremes on at least one lot of data (generic or device specific) submitted per test. For example, if a supplier designs a device intended solely for use in an operating temperature Grade 3 environment (e.g., -40°C to +85°C), the end-point test temperature extremes need only address those application limits. Qualification to applications in higher operating temperature grade environments (e.g., -40°C to +125°C for Grade 1) will require testing of at least one lot using these additional end-point test temperature extremes.2.5 Definition of Test Failure After StressingTest failures are defined as those devices not meeting the individual device specification, criteria specific to the test, or the supplier's data sheet, in the order of significance as defined in section 2.2. Any device that shows external physical damage attributable to the environmental test is also considered a failed device. If the cause of failure is agreed (by the manufacturer and the user) to be due to mishandling, ESD, or some other cause unrelated to the test conditions, the failure shall be discounted, but reported as part of the data submission.3. QUALIFICATION AND REQUALIFICATION3.1 Qualification of a New DeviceThe stress test requirement flow for qualification of a new device is shown in Figure 2 with the corresponding test conditions defined in Table 2. For each qualification, the supplier must have data available for all of these tests, whether it is stress test results on the device to be qualified or acceptable generic data. A review shall also be made of other devices in the same generic family to ensure that there are no common failure mechanisms in that family. Justification for the use of generic data, whenever it is used, must be demonstrated by the supplier and approved by the user.For each device qualification, the supplier must have available the following:• Certificate of Design, Construction and Qualification (see Appendix 2)• Stress Test Qualification data (see Table 2 & Appendix 4)• Data indicating the level of fault grading of the software used for qualification (when applicable to the device type) per Q100-007 that will be made available to the customer upon requestAEC - Q100 - REV-GMay 14, 2007 Automotive Electronics CouncilComponent Technical Committee3.1.1 Qualification of a New Device Manufactured in a Currently Qualified FamilyIf justified by the supplier and agreed to by the user, new or redesigned products (die revisions) manufactured in a currently qualified family may be qualified using one (1) wafer/assembly lot.3.2 Requalification of a Changed DeviceRequalification of a device is required when the supplier makes a change to the product and/or process that impacts (or could potentially impact) the form, fit, function, quality and/or reliability of the device (see Table 3 for guidelines).3.2.1 Process Change NotificationThe supplier will meet the user requirements for product/process changes.3.2.2 Changes Requiring RequalificationAs a minimum, any change to the product, as defined in Appendix 1, requires performing the applicable tests listed in Table 2, using Table 3 to determine the requalification test plan. Table 3 should be used asa guide for determining which tests are applicable to the qualification of a particular part change orwhether equivalent generic data can be submitted for that test(s).3.2.3 Criteria for Passing RequalificationAll requalification failures shall be analyzed for root cause, with corrective and preventive actions established as required. The device and/or qualification family may be granted “qualification status” if, as a minimum, proper containment is demonstrated and approved by the user, until corrective and preventative actions are in place.3.2.4 User ApprovalA change may not affect a device's operating temperature grade, but may affect its performance in anapplication. Individual user authorization of a process change will be required for that user’s particular application(s), and this method of authorization is outside the scope of this document.4. QUALIFICATION TESTS4.1 General TestsTest flows are shown in Figure 2 and test details are given in Table 2. Not all tests apply to all devices.For example, certain tests apply only to ceramic packaged devices, others apply only to devices with NVM, and so on. The applicable tests for the particular device type are indicated in the “Note” column of Table 2. The “Additional Requirements” column of Table 2 also serves to highlight test requirements that supersede those described in the referenced test method. Any unique qualification tests or conditions requested by the user and not specified in this document shall be negotiated between the supplier and user requesting the test.Page 7 of 32AEC - Q100 - REV-GMay 14, 2007 Automotive Electronics CouncilComponent Technical Committee4.2 Device Specific TestsThe following tests must be performed on the specific device to be qualified for all hermetic and plastic packaged devices. Generic data is not allowed for these tests. Device specific data, if it already exists, is acceptable.1. Electrostatic Discharge (ESD) - All product.2. Latch-up (LU) - All product.3. Electrical Distribution - The supplier must demonstrate, over the operating temperature grade,voltage, and frequency ranges, that the device is capable of meeting the parametric limits of thedevice specification. This data must be taken from at least three lots, or one matrixed (or skewed)process lot, and must represent enough samples to be statistically valid, see Q100-009. It is stronglyrecommended that the final test limits be established using AEC-Q001 Guidelines For Part AverageTesting.4. Other Tests - A user may require other tests in lieu of generic data based on his experience with aparticular supplier.4.3 Wearout Reliability TestsTesting for the failure mechanisms listed below must be available to the user whenever a new technology or material relevant to the appropriate wearout failure mechanism is to be qualified. The data, test method, calculations, and internal criteria need not be demonstrated or performed on the qualification of every new device, but should be available to the user upon request.• Electromigration• Time-Dependent Dielectric Breakdown (or Gate Oxide Integrity Test) - for all MOS technologies• Hot Carrier Injection - for all MOS technologies below 1 micron• Negative Bias Temperature Instability• Stress MigrationPage 8 of 32AEC - Q100 - REV-GMay 14, 2007 Automotive Electronics CouncilComponent Technical CommitteeFigure 2: Qualification Test FlowPage 9 of 32AEC - Q100 - REV-GMay 14, 2007Component Technical CommitteeAutomotive Electronics CouncilPage 10 of 32Table 2: Qualification Test MethodsA D D I T I O N A L R E Q U I R E M E N T SP e r f o r m e d o n s u r f a c e m o u n t d e v i c e s o n l y . P C p e r f o r m e d b e f o r e T H B /H A S T , A C /U H S T , T C , a n d P T C s t r e s s e s . I t i s r e c o m m e n d e d t h a t J -S T D -020 b e p e r f o r m e d t o d e t e r m i n e w h a t p r e c o n d i t i o n i n g l e v e l t o p e r f o r m i n t h e a c t u a l P C s t r e s s p e r J A 113. T h e m i n i m u m a c c e p t a b l e l e v e l f o r q u a l i f i c a t i o n i s l e v e l 3 p e r J A 113. W h e r e a p p l i c a b l e , p r e c o n d i t i o n i n g l e v e l a n d P e a k R e f l o w T e m p e r a t u r e m u s t b e r e p o r t e d w h e n p r e c o n d i t i o n i n g a n d /o r M S L i s p e r f o r m e d . D e l a m i n a t i o n f r o m t h e d i e s u r f a c e i n J A 113/J -S T D -020 i s a c c e p t a b l e i f t h e d e v i c e p a s s e s t h e s u b s e q u e n t Q u a l i f i c a t i o n t e s t s . A n y r e p l a c e m e n t o f d e v i c e s m u s t b e r e p o r t e d . T E S T b e f o r e a n d a f t e r P C a t r o o m t e m p e r a t u r e .F o r s u r f a c e m o u n t d e v i c e s , P C b e f o r e T H B (85o C /85%R H f o r 1000 h o u r s ) o r H A S T (130o C /85%R H f o r 96 h o u r s , o r 110o C /85%R H f o r 264 h o u r s ). T E S T b e f o r e a n d a f t e r T H B o r H A S T a t r o o m a n d h o t t e m p e r a t u r e .F o r s u r f a c e m o u n t d e v i c e s , P C b e f o r e A C (121o C /15p s i g f o r 96 h o u r s ) o r u n b i a s e d H A S T (130°C /85%R H f o r 96 h o u r s , o r 110o C /85%R H f o r 264 h o u r s ). F o r p a c k a g e s s e n s i t i v e t o h i g h t e m p e r a t u r e s a n d p r e s s u r e (e .g ., BG A ), P C f o l l o w e d b y TH (85o C /85%R H ) f o r 1000 h o u r s m a y b e s u b s t i t u t e d . T E S T b e f o r e a n d a f t e r A C o r U H S T a t r o o m t e m p e r a t u r e .T E S T M E T H O D J E D E C J -S T D -020 J E S D 22-A 113J E D E C J E S D 22-A 101 o r A 110J E D E C J E S D 22-A 102, A 118, o r A 101A C C E P T C R I T E R I A 0 F a i l s 0 F a i l s 0 F a i l sN U M B E R O F L O T S 333S A M P L E S I Z E / L O T 77 77 77 N O T E S P , B , S , N , GP , B , D , GP , B , D , G# A 1A 2A 3A B VP C T H B o r H A S TA C o r U H S T o r T HT E S T G R O U P A – A C C E L E R A T E D E N V I R O N M E N T S T R E S S T E S T SS T R E S SP r e c o n d i t i o n i n gT e m p e r a t u r e -H u m i d i t y -B i a s o r B i a s e d H A S T A u t o c l a v e o r U n b i a s e d H A S T o r T e m p e r a t u r e -H u m i d i t y (w i t h o u t B i a s )。

aec q标准

aec q标准

AEC-Q标准是一套车规元器件产品验证标准,由克莱斯勒、福特和通用汽

车为建立一套通用的零件资质及质量系统标准而设立的汽车电子委员会(AEC)制定。

AEC-Q标准包括多个子标准,如AEC-Q100(集成电路IC)、AEC-Q101(离散半导体元件,如二极管,三极管)、AEC-Q102(离散光电LED)、AEC-Q104(多芯片组件)和AEC-Q200(被动元器件)等。

AEC-Q标准是国际通用的车规元器件产品验证标准,通过AEC-Q认证意味着产品能够应用于汽车上。

供应商只有在通过元器件相应标准中规定的所有测试项目后,才能声称产品已通过AEC-Q认证。

完整的AEC-Q验证项目

数量众多,且周期较长,因此指定时间表是为了确保测试按计划进行。

此外,AEC-Q100的工作温度等级分4个等级(AEC_Q100_Rev_H规范),AEC-Q100要求器件能够承受2KV人体放电模式 (HBM),在边角引脚上能承受750V的带电器件模式 (CDM),而在所有其它引脚上则能承受500V

的电压。

以上内容仅供参考,如需了解更多信息,建议查阅AEC-Q标准相关文献或

咨询该标准业内人士。

AEC-Q100 G 中文版

基于集成电路应力测试认证的失效机理内容列表AEC-Q100 基于集成电路应力测试认证的失效机理附录1:认证家族的定义附录2:Q100设计、架构及认证的证明附录3:邦线测试的塑封开启附录4:认证计划和结果的最低要求附录5:决定电磁兼容测试的零件设计标准附录6:决定软误差测试的零件设计标准附件AEC-Q100-001 邦线切应力测试AEC-Q100-002 人体模式静电放电测试AEC-Q100-003 机械模式静电放电测试AEC-Q100-004 集成电路闩锁效应测试AEC-Q100-005 可写可擦除的永久性记忆的耐久性、数据保持及工作寿命的测试 AEC-Q100-006 热电效应引起的寄生闸极漏电流测试AEC-Q100-007 故障仿真和测试等级AEC-Q100-008 早期寿命失效率(ELFR)AEC-Q100-009 电分配的评估AEC-Q100-010 锡球剪切测试AEC-Q100-011 带电器件模式的静电放电测试AEC-Q100-012 12V系统灵敏功率设备的短路可靠性描述感谢任何涉及到复杂技术的文件都来自于各个方面的经验和技能,为此汽车电子委员会由衷承认并感谢以下对该版文件有重要贡献的人:固定会员:准会员:特邀会员:其他支持者:注意事项AEC文件中的材料都是经过了AEC技术委员会所准备、评估和批准的。

AEC文件是为了服务于汽车电子工业,无论其标准是用在国内还是国际上,都可排除器件制造商和采购商之间各方面的不一致性,推动产品的提高和可交换性,还能帮助采购商在最小的时间耽搁内选择和获得来自那些非AEC成员的合适的产品。

AEC文件并不关注其采纳的内容是否涉及到专利、文章、材料或工艺。

AEC 没有认为对专利拥有者承担责任,也没有认为要对任何采用AEC文件者承担义务。

汽车电子系统制造商的观点主要是AEC文件里的信息能为产品的说明和应用提供一种很完美的方法。

如果没有在本文件见到所陈述的要求,就不能声称与本文件具有一致性。

AEC-Q100是什么

AEC-Q100为AEC组织所制订的车用可靠性测试标准,为3C&IC厂商打进国际车用大厂模块的重要入场卷,也是提高台湾IC可靠性质量的重要技术,此外,目前国际大厂已经通过车用安全性标准(ISO-26262),而AEC-Q100则为通过该标准的基本要求。

车用电子件区分为三大类别,包括IC元件、离散半导体元件与被动元件。

其余有关连接器、印刷电路板、机件等,通常由使用公司自行设计测试规范予供应商参考为多。

在AEC建议中,一部汽车应该就零件使用位置区分为引擎区与乘坐区两部份,其基本耐温要求不同,故对于测试温度建议规格也不同。

由于零件种类繁多,因此在试验条件上,AEC 已进行分门别类,亦即依照属性设定建议的试验条件,此与多数传统规范明显不同,也较无争议。

亿博检测提供全方位汽车电子及零组件一站式整合验证服务。

车用电子测试不仅着重于产品寿命测试相关,更重要的是将产品结构或产品组装品质的观念带入试验之中,例如考量到推拉力测试、锡球接合强度测试、弯曲测试等,将传统对于电子零件着重于电性与环境温湿度关联度的试验范畴扩展到应力与机构考量点,属于先期验证作法。

在试验规格中另一较为特殊的是,需将EMC的考量纳入,其认知为终端产品的EMC多由IC所贡献,因此IC须进行先期验证,降低终端产品设计时的风险。

服务范畴:汽车零组件领域(Automotive Parts) 电子控制模组领域(ECU Module) 电路板领域(PCB/ PCBA) IC/元件领域(IC/ Component)服务项目:电磁兼容测试(EMC Test) 可靠度验证(Reliability Test) 失效分析(Failure Analysis) 材料测试(Material Test) 化学分析(Chemical Test)AEC-Q100类别与测试:说明:AEC-Q100规范7大类别共41项的测试群组A-加速环境应力测试(ACCELERATED ENVIRONMENT STRESS TESTS)共6项测试,包含:PC、THB、HAST、AC、UHST、TH、TC、PTC、HTSL群组B-加速生命周期模拟测试(ACCELERATED LIFETIME SIMULATION TESTS)共3项测试,包含:HTOL、ELFR、EDR群组C-封装组装完整性测试(PACKAGE ASSEMBLY INTEGRITY TESTS)共6项测试,包含:WBS、WBP、SD、PD、SBS、LI群组D-芯片制造可靠性测试(DIE FABRICATION RELIABILITY TESTS)共5项测试,包含:EM、TDDB、HCI、NBTI、SM群组E-电性验证测试(ELECTRICAL VERIFICATION TESTS)共11项测试,包含:TEST、FG、HBM/MM、CDM、LU、ED、CHAR、GL、EMC、SC、SER群组F-缺陷筛选测试(DEFECT SCREENING TESTS)共11项测试,包含:PAT、SBA群组G-腔封装完整性测试(CAVITY PACKAGE INTEGRITY TESTS)共8项测试,包含:MS、VFV、CA、GFL、DROP、LT、DS、IWVAEC-Q100与AEC-Q200差别AEC-Q100是汽车集成电路(IC)的重要应力测试标准。

AEC_Q100-001C 焊线剪切测试WIRE BOND SHEAR TEST-中文版

三.步骤

汇报人:秋枫扫落叶

3.5 剪切过的线键的检验 Examination of Sheared Wire Bonds ➢所有线键应按计划/定义的顺序剪切,以便以后的视觉检查可以确定哪些因为剪切不当应消除剪切值的。应使用至少30 倍的放大倍数检查线键,以确定剪切工具是否跳过线键(5型)或剪切工具刮取或犁入芯片表面(4型)。焊接剪切类型 和图示见图3。 ➢应从剪切数据中消除出现键剪切类型4或5缺陷剪切条件的读数。焊接剪切类型1、2、3和6应被认为是可接受的,并包 含在剪切数据中。 ➢应进一步研究发生了焊接剪切3型弹坑状况的剪切键,以确定开裂和/或弹坑是否由于WB过程或WB剪切试验的行为。 ➢WB剪切试验操作前产生的弹坑不可接受。由WB剪切试验行为产生的弹坑应被认为是可接受的,并包含在剪切数据中。 3.6 铝楔形/针形键印记检查Footprint Inspection of Aluminum Wedge/Stitch Bonds ➢所有与芯片和封装焊接表面的铝线焊接工艺都应进行焊接足迹检查。 ➢对于太小的线无法进行WB剪切试验(压紧焊接区域高度小于1.25mil),从焊接表面,使用锋利的小刀片在楔形/针形 焊接位置拆除线。去除铝线应足够,以便目测线焊接界面,并确定冶金线焊接区域。 ➢对于较大的导线(压紧焊接区域高度大于1.25mil),应在WB剪切试验后进行检查,以检查失效模式,并确定楔形/针 形焊接足迹的覆盖范围。 3.7 键剪切数据Bond Shear Data 应维护每个WB剪切的数据。数据应确定线键(位置、球键和/或导线直径、线材料、键合方法和焊接的材料)、抗剪强度 和键剪切类型(如第1.3.4节和图3中定义)。

化合物在焊接表面。有证据表明焊接表面的球形、契形或针形键有收到化学攻击损坏及有金属化物残留不可以用于WB剪

e-lins H900 工业级2G3G4G5G蜂窝网络路由器 用户手册说明书

工业级2G 3G 4G 5G蜂窝网络路由器用户手册H900系列深圳市伊林思科技有限公司电话:+ 86-755-29230581电子邮件:官网:地址:深圳市龙华新区民治新牛路U创谷B12-33深圳市伊林思科技有限公司内容1配置前准备工作 (4)1.1了解您的路由器版本和功能 (4)1.2准备SIM卡和工作状态 (6)1.3推荐配置 (6)2硬件安装 (7)2.1总体尺寸 (7)2.2端口 (9)2.3安装 (13)2.4安装SIM / UIM卡 (13)2.5安装端子座 (13)2.6接地 (15)2.7供电 (15)2.8 LED和检查网络状态 (15)3软件配置 (16)3.1概览 (16)3.2如何登录路由器 (16)3.2.1计算机的网络配置 (16)3.2.2登录路由器 (19)3.3路由器状态 (20)3.3.1状态概述 (20)3.3.2模块状态 (21)3.3.3防火墙状态 (22)3.3.4路由表 (23)3.3.5系统日志 (23)3.3.6内核日志 (24)3.3.7实时图 (24)3.3.8 VPN (25)3.4系统配置 (27)3.4.1安装向导 (27)3.4.2系统 (29)3.4.3密码 (31)3.4.4 NTP (31)3.4.5备份/恢复 (32)3.4.6升级 (33)3.4.7复位 (34)3.4.8重启 (35)3.5服务配置 (35)3.5.1网络检查(ICMP) (35)3.5.2 VRRP (37)3.5.3失效备援(链路备份) (38)3.5.4 DTU (40)3.5.5 SNMP (42)深圳市伊林思科技有限公司**************:****************深圳市伊林思科技有限公司************** :**************** 3.5.6 GPS ....................................................................................................................................................................... 44 3.5.7短信 ........................................................................................................................................................................ 45 3.5.8 VPN ....................................................................................................................................................................... 51 3.5.8.1 IPSEC ................................................................................................................................................................ 51 3.5.8.2 PPTP .................................................................................................................................................................. 52 3.5.8.3 L2TP ................................................................................................................................................................... 55 3.5.8.4 OpenVPN .......................................................................................................................................................... 57 3.5.8.5 GRE 通道 ........................................................................................................................................................... 60 3.5.9 动态DNS ............................................................................................................................................................. 61 3.5.10连接无线电模块.................................................................................................................................................. 66 3.6网络配置 ................................................................................................................................................................... 67 3.6.1操作模式 ................................................................................................................................................................ 67 3.6.1.1如何获取H900五个LAN 以太网端口 ........................................................................................................... 68 3.6.2 Mobile 配置 ........................................................................................................................................................... 68 3.6.3数据流量限制 ........................................................................................................................................................ 72 3.6.4 局域网设置 ........................................................................................................................................................... 73 3.6.5 有线广域网 ........................................................................................................................................................... 77 3.6.6 WiFi 设置 ............................................................................................................................................................... 80 3.6.6.1 Wifi 通用配置 ..................................................................................................................................................... 81 3.6.6.2 WiFi 高级配置 ................................................................................................................................................... 82 3.6.6.3 WiFi 接口配置 ................................................................................................................................................... 83 3.6.6.4 WiFi AP 客户端 ................................................................................................................................................ 85 3.6.7接口概述 ................................................................................................................................................................ 87 3.6.8防火墙 .................................................................................................................................................................... 88 3.6.8.1通用设置 ............................................................................................................................................................ 88 3.6.8.2端口转换 ............................................................................................................................................................ 88 3.6.8.3流量规则 ............................................................................................................................................................ 89 3.6.8.4 DMZ .................................................................................................................................................................... 93 3.6.8.5安全 .................................................................................................................................................................... 94 3.6.9静态路由 ................................................................................................................................................................ 95 3.6.10交换机 ................................................................................................................................................................. 96 3.6.11 DHCP 和 DNS .................................................................................................................................................. 97 3.6.12诊断 ..................................................................................................................................................................... 99 3.6.13环回接口 ........................................................................................................................................................... 100 3.6.14动态路由 ........................................................................................................................................................... 100 3.6.15 QoS ................................................................................................................................................................... 103 3.6.16 游客 LAN (游客 WiFi ) . (105)深圳市伊林思科技有限公司**************:**************** 11配置前准备工作1.1了解您的路由器版本和功能1) H900系列包含不同的版本和选项功能。

AEC-Q100简表

附加要求 仅用于表面贴器件

附加要求

ESD22-A108

附加要求

附加要求

附加要求

附加要求

附加要求

NVM)集成电路或带有NVM的集成电路进行预处理

的温度和极限参数范围内进行

物理尺寸

PD

C4

10 最少10 个器件 中的5个 锡球 5个零件 每一个 的10个 引线

3

Cpk>1.33 JEDEC JESD22Ppk>1.67 B100 and B108 Cpk>1.33 AEC-Q100 010 Ppk>1.67

锡球切应力

SBS

C5

3

引线完整性

LI

C6

1

无破损或 JEDEC JESD22开裂 B105

Group A Test(针对芯片产品的环境应力测试) 每批样 应力测试 缩写 编号 批数 接受标准 遵循的测试规范 品个数 JEDEC J-STD-020 预处理 PC A1 77 3 0 Fails JESD22-A113 有偏温湿度或高 THB or JEDEC JESD22A2 77 3 0 Fails 加速度应力测试 HAST A101 or A110 高压或无偏高加 AC or JEDEC JESD22速度应力测试或 UAST or A3 77 3 0 Fails A102,A118 or 无偏温湿度 TH A101 JEDEC JESD22A104 and 温度循环 TC A4 77 3 0 Fails Appendix 3(针对 绑线测试的塑封开 启指导) JEDEC JESD22功率温度循环 PTC A5 45 1 0 Fails A105 高温存储寿命测 JEDEC JESD22HTSL A6 45 1 0 Fails 试 A103 Group B Test(针对芯片产品/IP/工艺库的寿命加速模拟测试) 每批样 应力测试 缩写 编号 批数 接受标准 遵循的测试规范 品个数 高温工作寿命 HTOL B1 77 3 0 Fails JEDEC JESD22-A108 早期失效率 ELFR B2 800 3 0 Fails AEC-Q100 008 NVM擦写次数,数 据保持和工作寿 EDR B3 77 3 0 Fails AEC-Q100 005 命 Group C Test(针对芯片产品封装过程中的封装完整性测试) 每批样 应力测试 缩写 编号 批数 接受标准 遵循的测试规范 品个数 绑线切应力 WBS C1

AECQ100 G 中文版.pdf

基于集成电路应力测试认证的失效机理内容列表AEC-Q100 基于集成电路应力测试认证的失效机理附录1:认证家族的定义附录2:Q100设计、架构及认证的证明附录3:邦线测试的塑封开启附录4:认证计划和结果的最低要求附录5:决定电磁兼容测试的零件设计标准附录6:决定软误差测试的零件设计标准附件AEC-Q100-001 邦线切应力测试AEC-Q100-002 人体模式静电放电测试AEC-Q100-003 机械模式静电放电测试AEC-Q100-004 集成电路闩锁效应测试AEC-Q100-005 可写可擦除的永久性记忆的耐久性、数据保持及工作寿命的测试 AEC-Q100-006 热电效应引起的寄生闸极漏电流测试AEC-Q100-007 故障仿真和测试等级AEC-Q100-008 早期寿命失效率(ELFR)AEC-Q100-009 电分配的评估AEC-Q100-010 锡球剪切测试AEC-Q100-011 带电器件模式的静电放电测试AEC-Q100-012 12V系统灵敏功率设备的短路可靠性描述感谢任何涉及到复杂技术的文件都来自于各个方面的经验和技能,为此汽车电子委员会由衷承认并感谢以下对该版文件有重要贡献的人:固定会员:准会员:特邀会员:其他支持者:注意事项AEC文件中的材料都是经过了AEC技术委员会所准备、评估和批准的。

AEC文件是为了服务于汽车电子工业,无论其标准是用在国内还是国际上,都可排除器件制造商和采购商之间各方面的不一致性,推动产品的提高和可交换性,还能帮助采购商在最小的时间耽搁内选择和获得来自那些非AEC成员的合适的产品。

AEC文件并不关注其采纳的内容是否涉及到专利、文章、材料或工艺。

AEC 没有认为对专利拥有者承担责任,也没有认为要对任何采用AEC文件者承担义务。

汽车电子系统制造商的观点主要是AEC文件里的信息能为产品的说明和应用提供一种很完美的方法。

如果没有在本文件见到所陈述的要求,就不能声称与本文件具有一致性。

AEC-Q100-基于集成电路应力测试认证的失效机理-G中文版

基于集成电路应力测试认证的失效机理内容列表AEC-Q100 基于集成电路应力测试认证的失效机理附录1:认证家族的定义附录2:Q100设计、架构及认证的证明附录3:邦线测试的塑封开启附录4:认证计划和结果的最低要求附录5:决定电磁兼容测试的零件设计标准附录6:决定软误差测试的零件设计标准附件AEC-Q100-001 邦线切应力测试AEC-Q100-002 人体模式静电放电测试AEC-Q100-003 机械模式静电放电测试AEC-Q100-004 集成电路闩锁效应测试AEC-Q100-005 可写可擦除的永久性记忆的耐久性、数据保持及工作寿命的测试 AEC-Q100-006 热电效应引起的寄生闸极漏电流测试AEC-Q100-007 故障仿真和测试等级AEC-Q100-008 早期寿命失效率(ELFR)AEC-Q100-009 电分配的评估AEC-Q100-010 锡球剪切测试AEC-Q100-011 带电器件模式的静电放电测试AEC-Q100-012 12V系统灵敏功率设备的短路可靠性描述感谢任何涉及到复杂技术的文件都来自于各个方面的经验和技能,为此汽车电子委员会由衷承认并感谢以下对该版文件有重要贡献的人:固定会员:准会员:特邀会员:其他支持者:注意事项AEC文件中的材料都是经过了AEC技术委员会所准备、评估和批准的。

AEC文件是为了服务于汽车电子工业,无论其标准是用在国内还是国际上,都可排除器件制造商和采购商之间各方面的不一致性,推动产品的提高和可交换性,还能帮助采购商在最小的时间耽搁内选择和获得来自那些非AEC成员的合适的产品。

AEC文件并不关注其采纳的内容是否涉及到专利、文章、材料或工艺。

AEC 没有认为对专利拥有者承担责任,也没有认为要对任何采用AEC文件者承担义务。

汽车电子系统制造商的观点主要是AEC文件里的信息能为产品的说明和应用提供一种很完美的方法。

如果没有在本文件见到所陈述的要求,就不能声称与本文件具有一致性。

AEC-Q100简表

附加要求 仅用于表面贴器件

附加要求

ESD22-A108

附加要求

附加要求

附加要求

附加要求

附加要求

NVM)集成电路或带有NVM的集成电路进行预处理

的温度和极限参数范围内进行

故障分级 特性描述 电热效应引起的 栅漏 电磁兼容 短路特性描述 软错误率

FG CHAR GL EMC SC SER

E6 E7 E8 E9 E10 E11

6 1 10 3

-

见AECQ100-007 AEC-Q100-007 第4节 AEC-Q003 1 0 Fails 13 0 Fails 1AEC-Q100-006 SAE J1752/3-辐射 AEC-Q100-012 JEDEC 无加速:JESD89-1 加速:JESD89-2或 JESD89-3

Cpk〉1.33 Ppk>1.67

AEC-Q100 001

绑线拉力

WBP

C2

可焊性

SD

C3

Cpk〉 1.33 最少5个器件中 Ppk>1.67 的30个绑线 或温度循 环 (#A4) 后0 Fails >95%引脚 15 1 覆盖

MIL-STD883 method 2011

JEDEC JESD22B102

Group F Test(针对芯片产品测试过程的缺陷筛选指南) 每批样 应力测试 缩写 编号 批数 接受标准 遵循的测试规范 品个数 部件平均测试 PAT F1 AEC-Q001 统计良率分析 SBA F2 AEC-Q002 Group G Test(针对芯片产品封装过程后的封装完整性测试) 每批样 应力测试 缩写 编号 批数 接受标准 遵循的测试规范 品个数 JEDEC JESD22机械冲击 MS G1 39 3 0 Fails B104 JEDEC JESD22变频振动 VFV G2 39 3 0 Fails B103 MIL-STD883 恒加速应力 CA G3 39 3 0 Fails Method 2001 MIL-STD883 粗/细气漏 GFL G4 39 3 0 Fails Method 1014 跌落测试 DROP G5 5 1 0 Fails MIL-STD883 盖板扭力测试 LT G6 5 1 0 Fails Method 2024 MIL-STD883 芯片切断 DS G7 5 1 0 Fails Method 2019 MIL-STD883 内部水蒸气含量 IWV G8 3 1 0 Fails Method 1018

汽车IC测试认证AEC-Q100解析

汽车IC测试认证AEC-Q100解析汽车电子的品质标准一直以来都比一般消费型电子产品要严格。

试想一下,一辆汽车要使用到一万多个零件,假如任何一个零件出现问题,对于消费者而言都有可能造成极大的困扰,甚至有可能危及到生命安全。

AEC-Q100是由美国汽车电子协会(automotive electronics council,AEC)所制定的规范,主要是针对车载应用的集成电路产品所设计出的一套应力测试标准,此规范对于提升产品信赖性品质保证相当重要。

AEC-Q100规范一辆汽车在使用过程中可能会面临严苛的使用环境,例如一辆汽车可能销售到沙漠气候的高温环境中使用,也可能卖给北欧冰天雪地的极地气候客户,严苛的高温、低温、高湿度环境将对汽车甚至汽车内部的集成电路组件造成冲击。

因此,有必要定义出一系列应力测试流程来评估汽车电子集成电路组件的寿命以及潜在的失误风险。

在AEC-Q100文件中,定义出以下几类不同任务的测试群组:Test Group A:Accelerated Environment Stress Tests;Test Group B:Accelerated Lifetime Simulation Tests;Test Group C:Package Assembly Integrity Tests;Test Group D:Die Fabrication Reliability Tests;Test Group E:Electrical Verification Tests;Test Group F:Defect Screening Tests;Test Group G:Cavity Package Integrity。

每一个测试群组会再细化定义出几项测试项目,并说明这些测试项目的测试理论参考何项半导体业界所使用的认证规范(例如:JEDEC、MIL-STD883、SAE或者AEC-Q100本身所定义并且于附件里所定义的规则);每一个测试项目也同时会定义测试样品单一批次数量、测试批次量以及判断合格标准,若有额外的规范也会定义在每一项测试规范当中。

汽车电子元器件AECQ认证资料大全

以下资料由华碧实验室收集整理汽车电子元器件AEC-Q系列认证AEC的历史AEC是“Automotive Electronics Council:汽车电子协会”的简称。

1992年,GeraldServais会见了Jerry Jennings(克莱斯勒),谈话内容包括在电子零件资格认证领域遇到的一些共同困难,提到了共同资格规格的概念,认为这是改善这种情况的一种可能办法。

在随后的JEDEC会议上,Servais讨论了与Robert Knoell(福特)的这种可能的合作。

这些初步讨论表明,这一概念可能是可行的。

Knoell先生和他的老板EarlFischer讨论了这个想法,并于1993年1月在DelcoElectronics召开了一次会议。

在这次会议上,讨论了各公司采用的各种资格认证办法。

它决定,共同资格规格的想法是可行的,并开始工作的Q100(集成电路的压力测试资格)不久。

在开发Q100期间,主要的IC供应商有机会对该文件进行评论。

在1994年6月于丹佛举行的一次会议上,向我们所有的IC供应商提交了最初的版本AECQ100。

AEC Founders from L-R Earl Fischer(Ford),Gerald Servais(Delco Electronics-GM),Jerry Jennings (Chrysler),Robert Knoell(Ford)AEC-Q认证的概念克莱斯勒、福特和通用汽车为建立一套通用的零件资质及质量系统标准而设立了汽车电子委员会(AEC),是主要汽车制造商与美国的主要部件制造商汇聚一起成立的、以车载电子部件的可靠性以及认定标准的规格化为目的的团体,AEC 建立了质量控制的标准。

同时,由于符合AEC规范的零部件均可被上述三家车厂同时采用,促进了零部件制造商交换其产品特性数据的意愿,并推动了汽车零件通用性的实施,为汽车零部件市场的快速成长打下基础。

主要的汽车电子成员有:Autoliv(奥托立夫),Continental(大陆),Delphi(德尔福),Johnson Controls (江森自控)和Visteon(伟世通)。

AEC_Q100-001_rev_C

AEC - Q100-001 - REV-COctober 8, 1998 Automotive Electronics CouncilComponent Technical CommitteeATTACHMENT 1AEC - Q100-001 REV-CWIRE BOND SHEAR TESTAEC - Q100-001 - REV-COctober 8, 1998 Automotive Electronics CouncilComponent Technical CommitteeAcknowledgmentAny document involving a complex technology brings together experience and skills from many sources. The Automotive Electronics Counsel would especially like to recognize the following significant contributors to the development of this document:James T. Peace DaimlerChryslerRobert V. Knoell Visteon CorporationGerald E. Servais Delphi Delco Electronics Systems - RetiredMark A. Kelly Delphi Delco Electronics SystemsOctober 8, 1998 Automotive Electronics CouncilComponent Technical CommitteeChange NotificationThe following summary details the changes incorporated into AEC-Q100-001 Rev-C:•Section 1.3.4.4, Type 4 - Die Surface Contact: Corrected wording to reflect bond shear type where the shear tool contacts the die surface, rather than the bonding surface asstated in Rev - B.•Added new Section 1.3.5, Footprint: Added new definition for “footprint”; changed numbers of subsequent sections to reflect the addition.•Section 3.6 step b, Footprint Inspection of Aluminum Wedge/Stitch Bonds: Added wording to clarify method used to remove wire for footprint inspection.•Figure 3, Wire Bond Shear Types: Updated figure to reflect wording correction made to Type 4 - Die Surface Contact.•Minor wording changes were made to the following: Section 1.1, 1.3.1, 1.3.4.1, 1.3.4.5, 2.2,2.5,3.2, and 3.5.Component Technical CommitteeMETHOD - 001WIRE BOND SHEAR TESTText enhancements and differences made since the last revision of thisdocument are shown as underlined areas. Several figures have also beenrevised, but changes to these areas have not been underlined.1.SCOPE1.1DescriptionThis test establishes a procedure for determining the strength of the interface between a gold ball bond and a package bonding surface, or an aluminum wedge/stitch bond and a package bonding surface, on either pre-encapsulation or post-encapsulation devices. This strength measurement is extremelyimportant in determining two features:1)the integrity of the metallurgical bond which has been formed.2)the reliability of gold and aluminum wire bonds to die or package bonding surfaces.This test method can be used only when the ball height and diameter for ball bonds, or the wire height(1.25 mils and larger at the compressed bond area) for wedge/stitch bonds, are large enough andadjacent interfering structures are far enough away to allow suitable placement and clearance (e.g.,above the bonding surface and between adjacent bonds) when performing the wire bond shear test.The wire bond shear test is destructive. It is appropriate for use in process development, processmonitoring, and/or quality assurance.1.2Reference DocumentsNot Applicable1.3Terms and DefinitionsThe terms and definitions shall be in accordance with the following sections.1.3.1Ball BondThe welding of a thin wire, usually gold, to a die bonding surface, usually an aluminum alloy bond pad, using a thermal compression or thermosonic wire bonding process. The ball bond includes the enlarged spherical portion of the wire (sometimes referred to as the nail head and formed by the flame-off and first bonding operation in thermal compression and thermosonic process), the underlying bonding surface,and the intermetallic weld interface. For the purposes of this document, all references to ball bonds are applicable to gold ball bonds on die bonding surfaces; other ball bond material combinations mayrequire a new set of failure criteria (see section 4.1).Component Technical Committee 1.3.2Bonding SurfaceEither 1) the die surface (e.g., die bond pad) or 2) the package bonding surface (e.g., plated leadframe post or finger, downbond to the flag or paddle, etc.) to which the wire is ball, wedge, or stitch bonded.1.3.3Bond ShearA process in which an instrument uses a chisel shaped tool to shear or push a ball or wedge/stitch bond off the bonding surface (see Figure 1). The force required to cause this separation is recorded and is referred to as the bond shear strength. The bond shear strength of a gold ball bond, when correlated to the diameter of the ball bond, is an indicator of the quality of the metallurgical bond between the gold ball bond and the die bonding surface metallization. The bond shear strength of an aluminumwedge/stitch bond, when compared to the manufacturer’s bond wire tensile strength, is an indicator of the integrity of the weld between the aluminum wire and the die or package bonding surface.Shear Tool h Specimen ClampTest SpecimenBondingBond Weld Area Bond C LSurface Figure 1: Bond Shear set-up1.3.4Definition of Bond Shear Types for Ball and Wedge/Stitch Bonds (see Figure 3)1.3.4.1Type 1 - Bond LiftA separation of the entire wire bond from the bonding surface with only an imprint being left on the bonding surface. There is very little evidence of intermetallic formation or welding to the bonding surface metallization.1.3.4.2Type 2 - Bond ShearA separation of the wire bond where: 1) A thin layer of bonding surface metallization remains with the wire bond and an impression is left in the bonding surface, or 2) Intermetallics remain on the bonding surface and with the wire bond, or 3) A major portion of the wire bond remains on the bonding surface.Component Technical Committee1.3.4.3Type 3 - CrateringA condition under the bonding surface metallization in which the insulating layer (oxide or interlayerdielectric) and the bulk material (silicon) separate or chip out. Separation interfaces which show pits ordepressions in the insulating layer (not extending into the bulk) are not considered craters. It should be noted that cratering can be caused by several factors including the wire bonding operation, the post-bonding processing, and even the act of wire bond shear testing itself. Cratering present prior to theshear test operation is unacceptable.1.3.4.4Type 4 - Die Surface ContactThe shear tool contacts the die surface and produces an invalid shear value. This condition may be due to improper placement of the specimen, a die surface not parallel to the shearing plane, a low shearheight, or instrument malfunction. This bond shear type is not acceptable and shall be eliminated fromthe shear data.1.3.4.5Type 5 - Shearing SkipThe shear tool removes only the topmost portion of the ball or wedge/stitch bond. This condition may be due to improper placement of the specimen, a die surface not parallel to the shearing plane, a high shear height, or instrument malfunction. This bond shear type is not acceptable and shall be eliminated from the shear data.1.3.4.6Type 6 - Bonding Surface LiftA separation between the bonding surface metallization and the underlying substrate or bulk material.There is evidence of bonding surface metallization remaining attached to the ball or wedge/stitch bond.1.3.5FootprintAn impression of the compressed wedge/stitch bond area created in the bonding surface during theultrasonic wire bonding process. The bond footprint area is normally larger than the actual metallurgical weld interface.1.3.6Shear Tool or ArmA tungsten carbide, or equivalent, chisel with specific angles on the bottom and back of the tool toinsure a shearing action.1.3.7Wedge/Stitch BondThe welding of a thin wire, usually aluminum, to a die or package bonding surface using an ultrasonicwire bonding process. The wedge bond, sometimes referred to as a stitch bond, includes thecompressed (ultrasonically bonded) area of the bond wire and the underlying bonding surface. Whenwedge/stitch bonding to an aluminum alloy bonding surface, no intermetallic exists because the twomaterials are of the same composition; but rather the two materials are combined and recrystallized bythe ultrasonic energy of the welding process. For the purposes of this document, all references towedge/stitch bonds are applicable to aluminum wedge/stitch bonds only; gold wedge/stitch bonds arenot required to be wire bond shear tested.Component Technical Committee2.APPARATUS AND MATERIALThe apparatus and materials required for wire bond shear testing shall be as follows:2.1Inspection EquipmentAn optical microscope system or scanning electron microscope providing a minimum of 30Xmagnification.2.2Measurement EquipmentAn optical microscope or measurement system capable of measuring the wire bond diameter to within ±0.1 mil.2.3WorkholderFixture used to hold the device being tested parallel to the shearing plane and perpendicular to theshear tool. The fixture shall also eliminate device movement during wire bond shear testing. If using a caliper controlled workholder, place the holder so that the shear motion is against the positive stop ofthe caliper. This is to insure that the recoil movement of the caliper controlled workholder does notinfluence the wire bond shear test.2.4Wire Bond Shear EquipmentThe wire bond shear equipment must be capable of precision placement of the shear tool approximately0.1 mil above the topmost part of the bonding surface. This distance (h) shall insure the shear tool doesnot contact the die or package bonding surface and shall be less than the distance from the topmostpart of the bonding surface to the center line (C L) of the ball or wedge/stitch bond.2.5Bond Shear ToolRequired shear tool parameters include but are not limited to: flat shear face, sharp shearing edge, and shearing width of 1.5 to 2 times (1.5X to 2X) the bond diameter or bond length. The shear tool should be designed to prevent plowing and drag during wire bond shear testing. The shear tool should be cleanand free of chips (or other defects) that may interfere with the wire bond shear test.3.PROCEDURE3.1CalibrationBefore performing the wire bond shear test, it must be determined that the equipment has beencalibrated in accordance with the manufacturer's specifications and is presently in calibration.Recalibration is required if the equipment is moved to another location.Component Technical Committee3.2Visual Examination of Wire Bonds to be Shear Tested After DecapsulationBefore performing wire bond shear testing on a device which has been opened using wet chemicaland/or dry etch techniques, the bonding surfaces shall be examined to insure there is no absence ofmetallization on the bonding surface area due to chemical etching. Ball or wedge/stitch bonds onbonding surfaces with evidence of degradation from chemical attack or absence of metallization shallnot be used for wire bond shear testing. Wire bonds on bonding surfaces without degradation fromchemical attack may not be attached to the bonding surface due to other causes (e.g., packagestress). These wire bonds are considered valid and shall be included in the shear data as a zero (0)gram value. Wire bonds must also be examined to ensure adjacent interfering structures are far enough away to allow suitable placement and clearance (above the bonding surface and between adjacent wire bonds) when performing the wire bond shear test.3.3Measurement of the Ball Bond Diameter to Determine the Ball Bond Failure CriteriaOnce the bonding surfaces have been examined and prior to performing wire bond shear testing, thediameter of all ball bonds (from at least one representative sample to be tested) shall be measured and recorded. For asymmetrical ball bonds, determine the average using both the largest (d large) and the smallest diameter (d small) values (see Figure 2). These ball bond diameter measurements shall beused to determine the mean, or average, diameter value. The resulting mean, or average, ball bonddiameter shall then be used to establish the failure criteria as defined in section 4.1. If process-monitor data has established the nominal ball bond diameter, then that value may be used to determine thefailure criteria as defined in section 4.1.SYMMETRICALASYMMETRICALFigure 2: Ball bond diameter measurement (symmetrical vs. asymmetrical)Component Technical Committee3.4Wire Bond Shear Test ProcedureThe wire bond shear testing procedure shall be performed as follows:a.The wire bond shear equipment shall pass all self diagnostic tests prior to performing the wirebond shear test.b.The wire bond shear equipment and test area shall be free of excessive vibration or movement.Examine the shear tool to verify it is in good condition and is not bent or damaged. Check theshear tool to verify it is in the up position.c.Adjust the workholder to match the device being tested. Secure the device to the workholder.Make sure the die or package bonding surface is parallel to the shearing plane of the shear tool.It is important that the shear tool does not contact the bonding surface or adjacent structuresduring the shearing operation as this will give incorrect high readings.d.Position the device so that the wire bond to be tested is located adjacent to the shear tool.Lower the shear tool (or raise the device depending upon wire bond shear equipment used) toapproximately the die or package bonding surface but not contacting the surface (approximatelythe thickness of the wire bond above the die or package bonding surface).e.For ball bond shear testing, position the ball bond to be tested so that the shear motion willtravel perpendicular to the die edge. Wire bond shear testing is required for ball bonds locatedat the die bonding surface interface only.f.For aluminum wedge/stitch bond shear testing, a wire height at the compressed bond area of1.25 mils and larger is required. For wires too small for wire bond shear testing (less than 1.25mils in height at the compressed bond area), only a footprint inspection is required (see section3.6). Position the wedge/stitch bond to be tested so that the shear motion will travel toward thelong side of the wedge/stitch bond and is free of any interference (i.e. shear the outsidewedge/stitch bond first and then shear toward the previously sheared wedge/stitch bond). Wirebond shear testing is required for aluminum wedge/stitch bonds located at die and packagebonding surfaces; gold wedge/stitch bonds are not required to be wire bond shear tested.g.Position the shear tool a distance of approximately one ball bond diameter (or one aluminumwire diameter for wedge/stitch bonds) from the wire bond to be shear tested and shear the wirebond.3.5Examination of Sheared Wire BondsAll wire bonds shall be sheared in a planned/defined sequence so that later visual examination candetermine which shear values should be eliminated due to an improper shear. The wire bonds shall be examined using at least 30X magnification to determine if the shear tool skipped over the wire bond(type 5) or the shear tool scraped or plowed into the die surface (type 4). See Figure 3 for bond shear types and illustrations.Readings in which either a bond shear type 4 or 5 defective shear condition occurred shall be eliminated from the shear data. Bond shear type 1, 2, 3, and 6 shall be considered acceptable and included in the shear data.Component Technical CommitteeSheared wire bonds in which a bond shear type 3 cratering condition has occurred shall be investigated further to determine whether the cracking and/or cratering is due to the wire bonding process or the act of wire bond shear testing. Cratering caused prior to the wire bond shear test operation isunacceptable. Cratering resulting from the act of wire bond shear testing shall be consideredacceptable and included in the shear data.3.6Footprint Inspection of Aluminum Wedge/Stitch Bondsa.All aluminum wire bonding processes to both die and package bonding surfaces shall have abond footprint inspection performed.b.For wires too small for wire bond shear testing (less than 1.25 mils in height at the compressedbond area), the wires shall be removed at the wedge/stitch bond location using a small sharpblade to peel or pluck the wire bond from the bonding surface. The removal of the aluminumwire shall be sufficient such that the wire bond interface can be visually inspected and themetallurgical wire bond area determined.c.For larger wires (greater than 1.25 mils in height at the compressed bond area), the wires shallbe inspected after wire bond shear testing to examine the failure mode and to determine thewedge/stitch bond footprint coverage.3.7Bond Shear DataData shall be maintained for each wire bond sheared. The data shall identify the wire bond (location,ball bond and/or wire diameter, wire material, method of bonding, and material bonded to), the shearstrength, and the bond shear type (as defined in section 1.3.4 and Figure 3).4.FAILURE CRITERIAThe following failure criteria are not valid for devices that have undergone environmental stress testing or have been desoldered from circuit boards.4.1Failure Criteria for Gold Ball BondsThe gold ball bonds on a device shall be considered acceptable if the minimum individual and sampleaverage ball bond shear values are greater than or equal to the values specified in Figure 4 and Table 1.This criteria is applicable for gold wire ball bonds on aluminum alloy bonding surfaces. Other material combinations may require a new set of failure criteria.Alternate minimum ball bond shear values may be proposed by the supplier if supporting data justifies the proposed minimum values.4.2Failure Criteria for Aluminum Wedge/Stitch BondsThe aluminum wedge/stitch bonds on a device shall be considered acceptable if the minimum shearvalues are greater than or equal to the manufacturer’s bond wire tensile strength.In addition, the percent of the wedge/stitch bond footprint in which bonding occurs shall be greater than or equal to 50%. If it is necessary to control the wire bonding process using SPC for percent coverage,a C pk value can be calculated to this limit.Component Technical CommitteeComponent Technical CommitteeMINIMUM SHEAR VALUESBALL BOND DIAMETER (mils)2.25 2.53.0 3.25 3.5 3.754.25 4.5 4.755.0 5.252.0S H E A R S T R E N G T H (g r a m s )1.7501020304050607080901001102.75 4.0Figure 4: Minimum acceptable individual and sample average ball bond shear values *, see Table 1for exact ball bond shear values ** (Shear values are applicable for gold wire ball bonds on aluminum alloy bonding surfaces)Component Technical CommitteeTable 1: Minimum acceptable individual and sample average ball bond shear values ** (Shear values are applicable for gold wire ball bonds on aluminum alloy bonding surfaces)Ball Bond Diameter(mils)MinimumSample Average(grams)Minimum IndividualShear Reading(grams)2.012.6 5.7 2.114.0 6.8 2.215.58.1 2.317.19.5 2.418.810.9 2.520.612.4 2.622.414.0 2.724.415.6 2.826.517.42.928.619.23.030.821.1 3.133.223.1 3.235.625.1 3.338.127.2 3.440.729.4 3.543.431.7 3.646.234.1 3.749.136.5 3.852.139.13.955.241.74.058.344.3 4.161.647.1 4.265.050.0 4.368.452.9 4.471.955.8 4.575.659.0 4.679.362.1 4.783.165.3 4.887.068.64.991.072.05.095.175.5October 8, 1998 Component Technical CommitteeAutomotive Electronics CouncilRevision HistoryRev #-A BC Date of changeJune 9, 1994May 19, 1995Sept. 6, 1996Oct. 8, 1998Brief summary listing affected sectionsInitial Release.Added copyright statement.Deleted old Sections 1.3.4, 1.3.5, 3.3, 3.9, and 5.0. Added new Sections1.3.1, 1.3.2, 1.3.6, 3.4 (steps a through g), and 3.6 (steps a through c).Revised the following: Sections 1.1, 1.2, 1.3.1, 1.3.2, 1.3.3, 1.3.4(1.3.4.1 through 1.3.4.6), 1.3.5, 1.3.6, 2.1, 2.2, 2.4, 2.5, 3.1, 3.2, 3.3, 3.4(a, b, c, d, e, f, and g), 3.5, 3.6 (a, b, and c), 3.7, 4.0, 4.1, and 4.2; Table1; Figures 1, 3, and 4.Added new Section 1.3.5. Revised the following: Sections 1.1, 1.3.1,1.3.4.1, 1.3.4.4, 1.3.4.5,2.2, 2.5,3.2, 3.5, 3.6 (b), Figure 3.。

AEC_Q100-012

1.1

Purpose The purpose of this specification is to determine the reliability of "protected" drivers when operating in a continuous short circuit condition. This document is not intended to address soft short circuit failures seen in incandescent lamp applications (e.g., external lighting). These applications will be considered in a separate document. Additional protection strategies and operating voltages that are currently outside the scope of this document are also being evaluated for future documents.

AEC - Q100-012 - REVSeptember 14, 2006

Automotive Electronics uncil

Component Technical Committee

NOTICE

AEC documents contain material that has been prepared, reviewed, and approved through the AEC Technical Committee. AEC documents are designed to serve the automotive electronics industry through eliminating misunderstandings between manufacturers and purchasers, facilitating interchangeability and improvement of products, and assisting the purchaser in selecting and obtaining with minimum delay the proper product for use by those other than AEC members, whether the standard is to be used either domestically or internationally. AEC documents are adopted without regard to whether or not their adoption may involve patents or articles, materials, or processes. By such action AEC does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the AEC documents. The information included in AEC documents represents a sound approach to product specification and application, principally from the automotive electronics system manufacturer viewpoint. No claims to be in conformance with this document shall be made unless all requirements stated in the document are met. Inquiries, comments, and suggestions relative to the content of this AEC document should be addressed to the AEC Technical Committee on the link . Published by the Automotive Electronics Council. This document may be downloaded free of charge, however AEC retains the copyright on this material. By downloading this file, the individual agrees not to charge for or resell the resulting material. Printed in the U.S.A. All rights reserved Copyright © 2006 by Delphi, Siemens VDO, and Visteon Corporation. This document may be freely reprinted with this copyright notice. This document cannot be changed without approval from the AEC Component Technical Committee.

AEC_Q100-011_rev_B