【精品】PPT课件 Viterbi译码

应用于LTE通信系统中专用Viterbi译码器实现

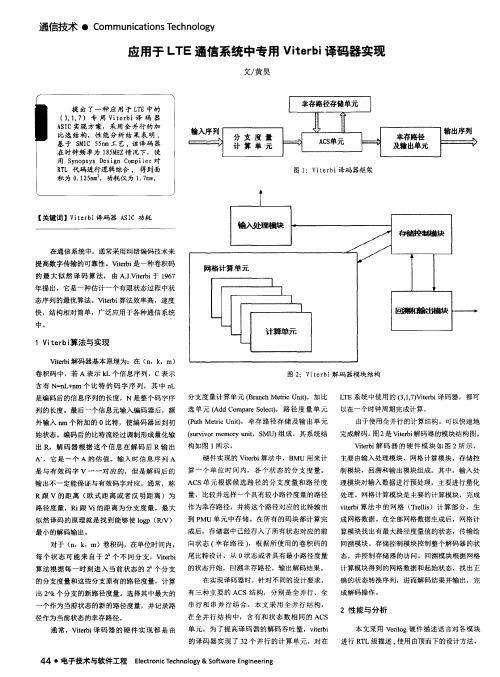

构如图 1所示。

硬件实现 的 V i t e r b i 算法 中 ,BMU 用 来 计

有 效码 字 V 一一对 应 的,但 是解 码后 的

算 一个单 位 时间 内,各 个状态 的 分支度 量。

C S 主要进行量化 5 不 一定 能保证 与有效码 字对应 。通 常,称 A

态 , 并控 制 存 储 器 的访 问 。 回溯 模 块 根 据 网格

对于 ( n ,k ,m)卷积码,在单位时间 内,

状 态 可能 来 自于 2 个 不 同 分支 ,V i t e r b i 尾 比特 设 计 ,从 0状 态 或 者 具 有 最 小 路 径 度 量 根 据每 一时刻 进入 当前状 态的 2 个 分支 的状态开始,回溯 幸存路径 ,输 出解码结 果。 在实现译码器时,针对不 同的设计要求 ,

计算模块得到 的网格数据和起始状态 ,找 出正 确 的状态转换序列 ,进而解码结果 并输 出,完

成解 码 操 作 。

r 支度量和这些分支原有 的路径度量 ,计算

,

k个分支的新路径度量 。选择其 中最大 的 有 三 种 主 要 的 ACS结 构 , 分 别 是 全 并 行 、 全

作为当前状态的新的路径度量 ,并记录路

t e r b i 算法与实现

Vi t e r b i 解 码 器 基 本 原 理 为: 在 ( n ,k ,m )

{ 码 中,若 A表 示 k L个 信息序列 ,C表示 N ̄L + n m 个 比特 的码 字序 列 ,其 中 n L 5 码 后的信息序列的长度 ,N 是整个 码字序 】 长度。最后一个信息元输入编码器后 ,额

P a t h Me t r i c U n i t ) ,幸存路 径存储 及输 出单元 入n n 1 个 附加的 0 比特 ,使编码器 回到初 f

卷积码的维特比译码

卷积码的维特比译码卷积编码器自身具有网格结构,基于此结构我们给出两种译码算法:Viterbi 译码算法和BCJR 译码算法。

基于某种准则,这两种算法都是最优的。

1967 年,Viterbi 提出了卷积码的Viterbi 译码算法,后来Omura 证明Viterbi 译码算法等效于在加权图中寻找最优路径问题的一个动态规划(Dynamic Programming)解决方案,随后,Forney 证明它实际上是最大似然(ML,Maximum Likelihood)译码算法,即译码器选择输出的码字通常使接收序列的条件概率最大化。

BCJR 算法是1974 年提出的,它实际上是最大后验概率(MAP,Maximum A Posteriori probability)译码算法。

这两种算法的最优化目标略有不同:在MAP 译码算法中,信息比特错误概率是最小的,而在ML 译码算法中,码字错误概率是最小的,但两种译码算法的性能在本质上是相同的。

由于Viterbi 算法实现更简单,因此在实际应用比较广泛,但在迭代译码应用中,例如逼近Shannon 限的Turbo 码,常使用BCJR 算法。

另外,在迭代译码应用中,还有一种Viterbi 算法的变种:软输出Viterbi 算法(SOV A,Soft-Output Viterbi Algorithm),它是Hagenauer 和Hoeher 在1989 年提出的。

为了理解Viterbi 译码算法,我们需要将编码器状态图按时间展开(因为状态图不能反映出时间变化情况),即在每个时间单元用一个分隔开的状态图来表示。

例如(3,1,2)非系统前馈编码器,其生成矩阵为:G(D)=[1+D1+D21+D+D2](1)图1 (a)(3,1,2)编码器(b)网格图(h=5)假定信息序列长度为h=5,则网格图包含有h+m+1=8 个时间单元,用0 到h+m=7 来标识,如图1(b)所示。

假设编码器总是从全0 态S0 开始,又回到全0 态,前m=2 个时间单元对应于编码器开始从S0“启程”,最后m=2 个时间单元对应于向S0“返航”。

卷积码的Viterbi译码设计设计

摘要在数字通信系统中,通常采用差错控制编码来提高系统的可靠性。

自P.Elias 首次提出卷积码编码以来,这一编码技术至今仍显示出强大的生命力。

目前,卷积码已广泛应用在无线通信标准中,如GSM,CDMA2000和IS-95等无线通信标准中。

针对N-CDMA数据传输过程中的误码问题,本文论述了旨在提高数据传输质量的维特比译码器的设计。

虽然Viterbi译码复杂度较大,实现较为困难,但效率高,速度快。

因此本文着重分析和讨论了1/2速率的(2,1,9)卷积码编码和其Viterbi译码算法。

深入研究卷积码编码原理和Viterbi算法原理后,提出了(2,1,9)卷积码编码以及Viterbi算法的初始化、加—比—选和回溯设计方案,运用查表的方法,避免了大量繁琐计算,使得译码简洁迅速,译码器的实时性能良好。

并充分利用TMS320C54X系列DSP芯片,用汇编语言完成了(2,1,9)卷积码编码和Viterbi 译码的程序。

关键词:差错控制编码、卷积码、Viterbi译码、TMS320C54X、DSPAbstractIn digital communication systems, error control coding is usually used to improve system reliability. Since P.Elias put forward the convolutional coding the first time, the coding is still showing strong vitality.,has become widely used in satellite communications, wireless communications and many other communication systemsas a kind of channel coding method. such as GSM, CDMA2000 and has been a wireless communication standards of IS-95.In view of the error problem in the process of N-CDMA data transmission, this paper discusses the aims to improve the quality of data transmission of victor design than the decoder.Although Viterbi decoding complexity is bigger, more difficult to achieve, but high efficiency and fast speed. So this article emphatically analyzed and discussed the 1/2 rate (2,1,9) convolution code coding and its Viterbi decoding algorithm. In-depth study on principle of convolution code coding and Viterbi algorithm, proposed the convolution code coding and Viterbi algorithm (2,1,9) initialization, add - than - choose and back design, using look-up table method, to avoid a large amount of tedious calculation, the decoding and quick, good real-time performance of the decoder. Make full use of the series of TMS320C54X DSP chip, using assembly language to complete the(2,1,9)convolution code coding and Viterbi decoding process.Keywords: error control coding, convolutional code, Viterbi decoding, TMS320C54X目录摘要 (1)Abstract (2)目录 (3)1.绪论 (1)1.1 移动通信及N-CDMA背景 (1)1.2 数字通信概述 (1)1.3 卷积编码与译码的发展 (3)1.4 主要研究工作 (3)2.DSP与CCS简介 (5)2.1 DSP概述 (5)2.1.1 DSP的主要特点 (5)2.1.2 CSSU单元概述 (7)2.2 CCS概述 (8)2.3 本章小结 (8)3.卷积码的理论基础 (9)3.1 卷积码的概述 (9)3.1.1 卷积码基本原理 (9)3.1.2 卷积码的纠错能力 (9)3.1.3 卷积码的表示方法 (10)3.2 Viterbi译码的概述 (11)3.3 本章小结 (14)4.卷积编码的实现 (15)4.1 (2,1,9)卷积码编码 (15)4.1.1 (2,1,9)卷积码编码设计方案 (15)4.1.2 (2,1,9)卷积码编码流程图 (16)4.1.3 (2,1,9)卷积编码程序实现 (16)4.1.4 (2,1,9)的程序仿真 (17)4.2 (2,1,9)卷积码状态转换表 (17)4.2.1 (2,1,9)卷积码状态转换表的设计算法 (18)4.2.2 (2,1,9)卷积码状态转换表的流程图 (18)4.2.3 (2,1,9)卷积码状态表 (18)4.2.4 (2,1,9)卷积码状态表的蝶形结构 (21)4.3 本章小结 (22)5. Viterbi译码的实现 (23)5.1 Viterbi译码基础 (23)5.2 Viterbi译码算法 (23)5.3 变量定义情况 (25)5.4 初始化 (26)5.4.1 初始化流程图 (27)5.4.2 初始化程序仿真 (27)5.5 加-比-选 (28)5.5.1加-比-选流程图 (29)5.5.2加-比-选程序仿真 (30)5.6 回溯 (31)5.6.1 回溯流程图 (32)5.6.2 回溯仿真图 (33)5.7 Viterbi纠错测试 (34)5.8 本章小结 (34)总结 (36)致谢 ............................................................................ 错误!未定义书签。

动态规划:卷积码Viterbi译码算法

动态规划:卷积码的Viterbi译码算法学院:网研院姓名:xxx 学号:xxx 一、动态规划原理动态规划(dynamic programming)是运筹学的一个分支,是求解决策过程(decision process)最优化的数学方法。

动态规划算法通常用于求解具有某种最优性质的问题。

在这类问题中,可能会有许多可行解,每一个解都对应于一个值,我们希望找到具有最优值的解。

动态规划算法与分治法类似,其基本思想也是将待求解问题分解成若干个子问题,先求解子问题,然后从这些子问题的解得到原问题的解。

与分治法不同的是,适合于用动态规划求解的问题,经分解得到子问题往往不是互相独立的。

若用分治法来解这类问题,则分解得到的子问题数目太多,有些子问题被重复计算了很多次。

如果我们能够保存已解决的子问题的答案,而在需要时再找出已求得的答案,这样就可以避免大量的重复计算,节省时间。

动态规划程序设计是对解最优化问题的一种途径、一种方法,而不是一种特殊算法。

不象搜索或数值计算那样,具有一个标准的数学表达式和明确清晰的解题方法。

动态规划程序设计往往是针对一种最优化问题,由于各种问题的性质不同,确定最优解的条件也互不相同,因而动态规划的设计方法对不同的问题,有各具特色的解题方法,而不存在一种万能的动态规划算法,可以解决各类最优化问题。

二、卷积码的Viterbi译码算法简介在介绍维特比译码算法之前,首先了解一下卷积码编码,它常常与维特比译码结合使用。

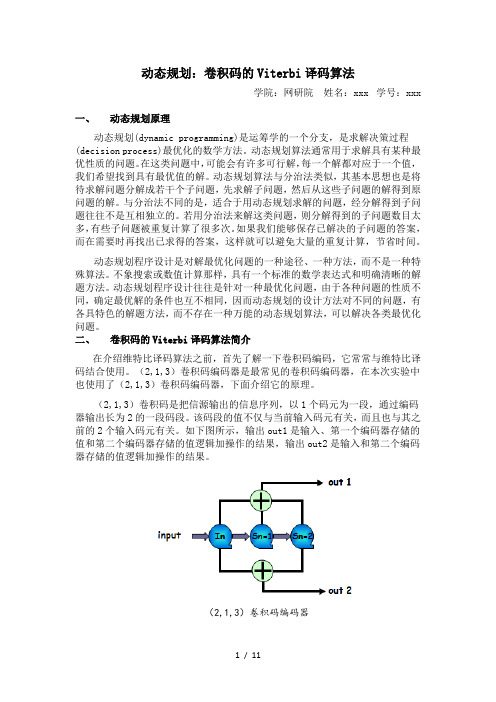

(2,1,3)卷积码编码器是最常见的卷积码编码器,在本次实验中也使用了(2,1,3)卷积码编码器,下面介绍它的原理。

(2,1,3)卷积码是把信源输出的信息序列,以1个码元为一段,通过编码器输出长为2的一段码段。

该码段的值不仅与当前输入码元有关,而且也与其之前的2个输入码元有关。

如下图所示,输出out1是输入、第一个编码器存储的值和第二个编码器存储的值逻辑加操作的结果,输出out2是输入和第二个编码器存储的值逻辑加操作的结果。

《编码与译码》课件

1

视频编码与解码

2

将视频信号编码为数字数据,通过解码

还原为可视的图像,用于视频通话和媒

体播放。

3

语音编码与解码

将声音信号编码为数字数据,通过解码 还原为可听的声音,用于电话和语音通 信。

数据加密与解密

将敏感数据进行编码保护,通过解码实 现数据的解密和恢复,用于保护信息安 全。

总结

编码与译码是信息传输和存储的核心过程。通过编码,信息得以转化和传递; 通过译码,信息得以理解和应用。了解不同的编码和译码方式,可以更好地 处理和利用信息。

作用

译码使得信息能够被人类理解和处理,实现有效的交流和应用。

常见的译码方式

摩尔斯电码

通过短促和长促的信号,以点和 划的形式表达字母和数字,用于 电报通信。

盲文

条形码

用凹凸感知方式表示字母和数字, 提供给盲人阅读和书写。

一维或二维图案,用线条和空白 表示信息,应用于商品标识和追 踪。

编码与译码的应用举例

《编码与译码》PPT课件

编码与译码是信息传输和存储中不可或缺的环节。本课件将介绍编码与译码 的定义、作用,以及常见的编码和译码方式。还将通过举例展示它们在实际 应用中的重要性。

编码的定义和作用

定义

编码是将信息转化为特定形式的过程,以实现准确传递和存储。

作用

编码可以提高信息传输的可靠性、安全性和效率,减少存储和传输的成本。

常见的编码方式

1

红绿蓝编码

将颜色信息编码成红、绿、蓝三个分量,

ASCII编码

2

用于显示器和数字图像处理。

使用的文本通信。

3

哈夫曼编码

根据字符出现的概率进行编码,提高数 据的压缩率,用于网络传输和存储。

高速Viterbi译码器的优化和实现

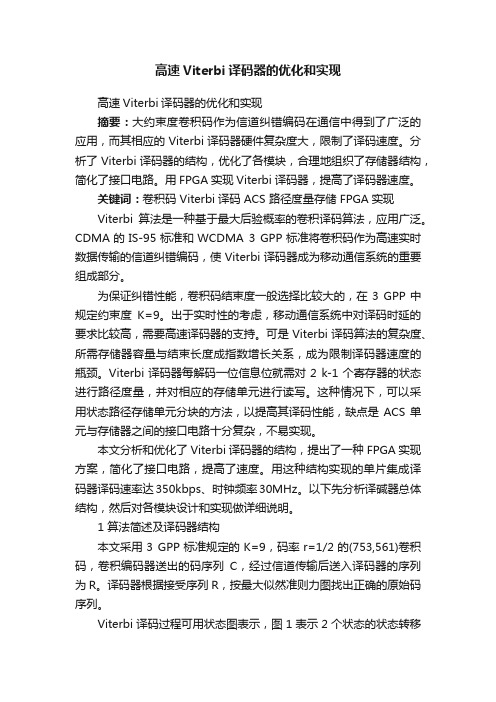

高速Viterbi译码器的优化和实现高速Viterbi译码器的优化和实现摘要:大约束度卷积码作为信道纠错编码在通信中得到了广泛的应用,而其相应的Viterbi译码器硬件复杂度大,限制了译码速度。

分析了Viterbi译码器的结构,优化了各模块,合理地组织了存储器结构,简化了接口电路。

用FPGA实现Viterbi译码器,提高了译码器速度。

关键词:卷积码 Viterbi译码 ACS 路径度量存储 FPGA实现Viterbi算法是一种基于最大后验概率的卷积译码算法,应用广泛。

CDMA的IS-95标准和WCDMA 3 GPP标准将卷积码作为高速实时数据传输的信道纠错编码,使Viterbi译码器成为移动通信系统的重要组成部分。

为保证纠错性能,卷积码结束度一般选择比较大的,在3 GPP中规定约束度K=9。

出于实时性的考虑,移动通信系统中对译码时延的要求比较高,需要高速译码器的支持。

可是Viterbi译码算法的复杂度、所需存储器容量与结束长度成指数增长关系,成为限制译码器速度的瓶颈。

Viterbi译码器每解码一位信息位就需对2 k-1个寄存器的状态进行路径度量,并对相应的存储单元进行读写。

这种情况下,可以采用状态路径存储单元分块的方法,以提高其译码性能,缺点是ACS单元与存储器之间的接口电路十分复杂,不易实现。

本文分析和优化了Viterbi译码器的结构,提出了一种FPGA实现方案,简化了接口电路,提高了速度。

用这种结构实现的单片集成译码器译码速率达350kbps、时钟频率30MHz。

以下先分析译碱器总体结构,然后对各模块设计和实现做详细说明。

1 算法简述及译码器结构本文采用3 GPP标准规定的K=9,码率r=1/2的(753,561)卷积码,卷积编码器送出的码序列C,经过信道传输后送入译码器的序列为R。

译码器根据接受序列R,按最大似然准则力图找出正确的原始码序列。

Viterbi译码过程可用状态图表示,图1表示2个状态的状态转移图。

第9章 Viterbi译码及其实现

“黑色经典”系列之《DSP嵌入式系统开发典型案例》第9章Viterbi译码及其实现华清远见<ARM开发培训班>培训教材在通信系统中,信息传输的可靠性和有效性是相当重要的。

信息在传输时是经由信道(Channel)传输。

当其在信道传输过程中会受到各种干扰,使得传输信息掺杂各种错误序列在其中。

因此,在通信系统中,良好的纠错码可以有效地应用在信息传输过程中,以降低信息的误码率。

信息在传输时,先由信源发出消息,如语言、图像、文字等,消息进入通信系统后,经由信源编码器编码成信息序列1。

编码过程中,为了使传输有效,还加上一些与传输信息无关的冗余度。

接着信息序列1经过信道编码器编码成信息序列2,序列2是将信息序列1加入了更多的冗余数据(Redundancy Data),以抵抗信道中的各种干扰。

数字信号一般不适合直接在信道上传输,所以调制器是将数字信号转变成模拟信号,使其在信道中传输。

而信道中难免会受到噪声干扰,使信道的输出序列不同于信道的输入序列。

解调器将信道的输出序列由原来的模拟信号转化成数字信号,既是接收序列3,信息序列中因噪声干扰会掺杂一些错误的码元在其中。

信道译码器利用序列中的冗余码元去纠正错误,并且根据信道译码器的结果,产生接近于信息序列1的接收序列1。

整个译码过程是根据信道编码的结果和噪声在信道中的特性所得到的。

理想的结果是所有的错误都被更正回来,即接收序列等同于发送序列。

9.1 Viterbi译码概述在众多的纠错码中,卷积码(Convolutional Code)是一种在实际中得到广泛应用、性能很好的纠错码。

卷积码是不同于分组码的另一种码,它虽然也是把k个信息比特编成n个比特,但k和n都很小,延时小,特别适宜于以串行形式传输信息。

与分组码不同,卷积码中编码后的n个码元不但与当前段的众个信息码元有关,而且与前面(N−1)段的信息有关,编码过程中相互关联的码元为Nn个。

在编码器复杂程度相同的情况下,卷积码的性能优于分组码。

卷积码Viterbi译码的FPGA实现

中国新通信2009.11卷积码及其Viterbi 算法的简介卷积码是1955年由Elias 提出,它与分组码不同,分组码是把k 个信息比特的序列编成n 个比特的码组,每个码组的n-k 个校验位仅与本码组k 个信息位有关,而与其他码组无关。

为了达到一定的纠错能力和编码效率,分组码的码组长度一般都比较大。

编译码时必须把整个信息码组存储起来,由此产生的译码延时随n 的增加而增加。

卷积码编码的一般结构如图1所示。

卷积码的概率译码最早始于1961年由Wozencraft 提出的序列译码,1963年由Fano 进行了改进,提出了Fano 算法。

1967年由Viterbi 提出了另外一种概率译码算法Viterbi 译码算法,它是一种最大似然译码算法,在码的约束度较小时,它比序列译码算法效率更高、速度更快,译码器也较简单。

因此,自Viterbi 译码算法提出以来,无论在理论上,还是在实践上都得到了极其迅速的发展。

Viterbi 算法并不等价于最大似然算法,但是,在一定的条件下,Viterbi 算法就是最大似然译码和最佳译码算法。

2Viterbi 算法的FPGA 实现2.1FPGA 的结构和特点随着半导体器件技术的快速发展,专用集成电陈健李广华(天津工业大学信息与通信工程学院天津300160)摘要本文根据卷积码编码的方式,和Viterbi 译码算法,认真分析了Viterbi 译码算法各部分的功能、特点。

采用硬件描述语言Verilog HDL ,编写了(2,1,7)卷积码的编译码程序,进行了Viterbi 译码器的FPGA 设计。

关键词卷积码Viterbi 算法现场可编程门阵列卷积码Vit e rb i 译码的FP GA 实现1k1n输出图1卷积码编码的一般结构图中国新通信经验与交流EXPERIENCE AND EXCHANGE53CHINA NEW TELECOMMUNICATIONS January 2009路(ASIC )的设计技术也随之不断提高和进步,现场可编程门阵列(FPGA )的出现使得系统级集成电路的设计开发成为可能,电子设计自动化(EDA )技术正给整个电子设计领域带来一场新的革命。

卷积编码和Viterbi译码-ZCL.SPACE

卷积编码和Viterbi译码zcl.space目录1引言1 2编码1 3译码2 4回溯4 5回溯深度6 6软译码61引言1965年,Peter Elias发明卷积码。

1967年,Andrew J.Viterbi(高通的创始人之一)发明了一种高效的译码算法:Viterbi算法。

Viterbi译码器可能是当前应用最广泛的一种卷积译码器。

2005年,G.David Forney在南加州大学的Viterbi Conference上提到:每秒,全世界的Viterbi译码器恢复的的二进制比特数是1015。

今天,我们来看看viterbi译码器如何实现译码。

2编码译码之前,先看如何卷积编码。

描述卷积编码器的方法有很多,按照每种描述,我们都可以实现卷积编码。

以约束长度为3,码率为1/2,生成多项式为g0=[111],g1=[101]的卷积码为例,图1左侧给出了移位寄存器电路图表示,图1右侧的表格是左侧的等价描述,显然左侧的表示更直观,右侧的表述更具体。

图1:卷积编码器的两种描述:移位寄存器和输入输出状态表卷积编码器还有一种描述:篱笆图描述。

篱笆图让Viterbi译码过程生动了许多,我认为是一个很伟大的发明,其作用和法拉力用磁感线表示磁场的存在一样,让难以理解的抽象过程瞬间活灵活现。

另外,在Turbo码的译码分析过程中,篱笆图也发挥着非常重要的作用。

图1右侧的表格可以表示如图2所示。

图2:卷积编码器篱笆图描述通过对篱笆图2进行时间上的延展,给定输入,我们可以很容易获得输出。

假设输入为(010111001010001)2(2.1)则编码输出为(001110000110011111100010110011)2(2.2)输出的获得过程如图3所示。

值得注意的是,在图3中,t=16和t=17时刻依然有0输入。

这两个0的作用是冲洗编码器,使得编码器的状态归零。

这样做的好处是Viterbi译码器知道编码器的最后一个状态是零状态。

卷积编码及基于DSP的Viterbi译码器设计

卷积编码及基于DSP的Viterbi译码器设计卷积编码是一种在通信领域中常用的技术,它通过将输入序列与一组固定的卷积核进行卷积运算,将输入序列转换为更长的输出序列。

在传输过程中,由于信号受到噪声和其他干扰的影响,传输信号可能会出现错误。

为了提高传输的可靠性,需要对接收到的信号进行译码,以纠正传输中的错误。

Viterbi译码器是一种常用的译码器,它基于Viterbi算法进行工作。

Viterbi算法是一种动态规划算法,通过计算各个状态的最大路径度量值,来确定最可能的传输序列。

Viterbi译码器主要用于卷积编码的解码过程,可以有效地纠正传输中的错误。

在设计Viterbi译码器时,基于DSP(数字信号处理器)的实现方式可以提供更高的性能和灵活性。

DSP是一种专门用于数字信号处理的芯片或处理器,其高性能的并行计算能力和丰富的算法库使得它成为译码器设计的理想选择。

基于DSP的Viterbi译码器设计需要考虑以下几个关键因素:首先,需要确定卷积编码的参数,包括卷积核的个数、每个卷积核的长度和生成多项式的系数。

这些参数会直接影响译码器的性能和复杂度。

其次,需要对Viterbi算法进行实现和优化。

由于Viterbi算法涉及到大量的状态转移和度量计算,需要充分利用DSP的并行计算能力和高效的算法实现方式,以提高译码器的运行速度和效率。

此外,还需要考虑DSP的资源和功耗限制。

通过合理地分配DSP的计算和存储资源,可以在保证性能的同时,降低功耗和成本。

最后,还可以考虑引入其他的优化技术,如迭代译码和软信息反馈等。

这些技术可以进一步提高译码器的性能和抗干扰能力。

基于DSP的Viterbi译码器设计是一项复杂而关键的工作,它在提高通信系统可靠性和性能方面起着重要的作用。

通过合理的设计和优化,可以实现高效、可靠的译码功能,为通信系统的发展和应用提供有力的支持。

支持不同约束长度VITERBI译码器的设计实现与重构【控制理论与控制工程..

知识水坝为您整理

知识水坝为您整理

第四章Viterbi译码器重构策略研究

V'lrtex支持的重构方式有两种,一是按列重构,图4一H为其局部动态重构的示意图,它要求设计时必须有严格的模块划分,将电路划分为固定的逻辑块(FixedLogic)和重构的逻辑块口artialReconfiguredLogic),模块之间的数据必须通过磁总线∞usMacro)进行交换。

微总线保证了重构时各个模块之间的数据正常交换。

还有一种是小比特流的重构方式,使用于对设计改动比较小的场合,重构时仅仅比较电路前后的差别,产生相应的bit流,修改设计完成重构。

图4.11VirtexFPGA局部重构示意

对于第一种方法,可重构逻辑的划分有如下一些规则:

①重构模块必须占满FPGA的一整列,即是按列重构;

②重构模块的边界是不可改变的,重构模块所占据的位置和面积在一次划分好后,

再不可随意改变。

③重构模块与其他重构模块及固定模块之间必须通过微总线来实现信号的传递。

4.1.4重构技术的应用和性能

动态重构技术运用于系统设计中是一种对灵活性和速度的一种设计方法,与传统的纯软件设计和硬件设计方法相比较,既有软件的灵活性,又有纯硬件系统的速度,如图4—12所示:

灵活件

软件

可重构件

硬件速度

图4—12可重构技术与软、硬件设计性能对比

可重构系统主要适用于如下系统设计:①最新通信系统:DR-FPGA的动态重构特性正好可以适应不同制式和不同标准的通信要求,满足软件无线电技术的发展和第三代移动通信系统(3G)的需要,本文主要是针对此项应用,设计了不同参数的

45。