74HC138中文资料 免费下载

M74HC138B1R中文资料

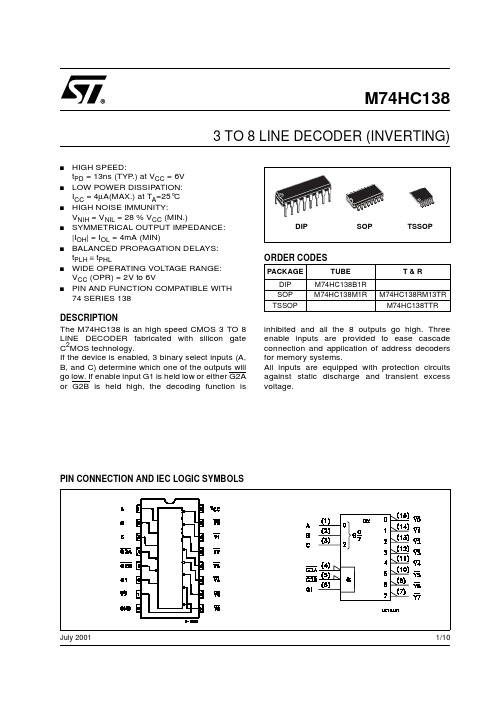

1/10July 2001sHIGH SPEED:t PD = 13ns (TYP .) at V CC = 6V sLOW POWER DISSIPATION:I CC = 4µA(MAX.) at T A =25°C sHIGH NOISE IMMUNITY:V NIH = V NIL = 28 % V CC (MIN.)sSYMMETRICAL OUTPUT IMPEDANCE:|I OH | = I OL = 4mA (MIN)sBALANCED PROPAGATION DELAYS:t PLH ≅ t PHLsWIDE OPERATING VOLTAGE RANGE:V CC (OPR) = 2V to 6VsPIN AND FUNCTION COMPATIBLE WITH 74 SERIES 138DESCRIPTIONThe M74HC138 is an high speed CMOS 3 TO 8LINE DECODER fabricated with silicon gate C 2MOS technology.If the device is enabled, 3 binary select inputs (A,B, and C) determine which one of the outputs will go low. If enable input G1 is held low or either G2A or G2B is held high, the decoding function isinhibited and all the 8 outputs go high. Three enable inputs are provided to ease cascade connection and application of address decoders for memory systems.All inputs are equipped with protection circuits against static discharge and transient excess voltage.M74HC1383 TO 8 LINE DECODER (INVERTING)PIN CONNECTION AND IEC LOGIC SYMBOLSORDER CODESPACKAGE TUBE T & RDIP M74HC138B1R SOP M74HC138M1RM74HC138RM13TR TSSOPM74HC138TTRM74HC1382/10INPUT AND OUTPUT EQUIVALENT CIRCUITPIN DESCRIPTIONTRUTH TABLEX : Don’t CareLOGIC DIAGRAMPIN No SYMBOL NAME AND FUNCTION 1, 2, 3A, B, C Address Inputs 4, 5G2A, G2BEnable Inputs 6G1Enable Input 9, 10, 11, 12, 13, 14, 15,7Y0 to Y7Data Outputs8GND Ground (0V)16V CCPositive Supply VoltageINPUTSOUTPUTS ENABLE SELECTG2B G2A G1C B A Y0Y1Y2Y3Y4Y5Y6Y7X X L X X X H H H H H H H H X H X X X X H H H H H H H H H X X X X X H H H H H H H H L L H L L L L H H H H H H H L L H L L H H L H H H H H H L L H L H L H H L H H H H H L L H L H H H H H L H H H H L L H H L L H H H H L H H H L L H H L H H H H H H L H H L L H H H L H H H H H H L H LLHHHHHHHHHHHLM74HC1383/10ABSOLUTE MAXIMUM RATINGSAbsolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied(*) 500mW at 65 °C; derate to 300mW by 10mW/°C from 65°C to 85°CRECOMMENDED OPERATING CONDITIONSSymbol ParameterValue Unit V CC Supply Voltage -0.5 to +7V V I DC Input Voltage -0.5 to V CC + 0.5V V O DC Output Voltage -0.5 to V CC + 0.5V I IK DC Input Diode Current ± 20mA I OK DC Output Diode Current ± 20mA I O DC Output Current ± 25mA I CC or I GND DC V CC or Ground Current± 50mA P D Power Dissipation 500(*)mW T stg Storage Temperature -65 to +150°C T LLead Temperature (10 sec)300°CSymbol ParameterValue Unit V CC Supply Voltage 2 to 6V V I Input Voltage 0 to V CC V V O Output Voltage 0 to V CC V T op Operating Temperature -55 to 125°C t r , t fInput Rise and Fall TimeV CC = 2.0V 0 to 1000ns V CC = 4.5V 0 to 500ns V CC = 6.0V0 to 400nsM74HC1384/10DC SPECIFICATIONSAC ELECTRICAL CHARACTERISTICS (C L = 50 pF, Input t r = t f = 6ns)SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.V IHHigh Level Input Voltage2.0 1.5 1.5 1.5V 4.53.15 3.15 3.156.04.24.24.2V ILLow Level Input Voltage2.00.50.50.5V4.5 1.35 1.35 1.356.0 1.81.81.8V OHHigh Level Output Voltage2.0I O =-20 µA 1.9 2.0 1.9 1.9V4.5I O =-20 µA 4.4 4.5 4.4 4.46.0I O =-20 µA5.96.0 5.9 5.94.5I O =-4.0 mA 4.18 4.31 4.13 4.106.0I O =-5.2 mA 5.685.8 5.635.60V OLLow Level Output Voltage2.0I O =20 µA 0.00.10.10.1V 4.5I O =20 µA 0.00.10.10.16.0I O =20 µA 0.00.10.10.14.5I O =4.0 mA 0.170.260.330.406.0I O =5.2 mA 0.180.260.330.40I I Input Leakage Current6.0V I = V CC or GND ± 0.1± 1± 1µA I CCQuiescent Supply Current6.0V I = V CC or GND44080µA SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.t TLH t THL Output TransitionTime 2.0307595110ns 4.581519226.07131619t PLH t PHL Propagation DelayTime (A, B, C - Y) 2.060125155190ns4.5152531386.013212632t PLH t PHL Propagation DelayTime (G, G - Y)2.0561********ns4.5142430366.012202631M74HC1385/10CAPACITIVE CHARACTERISTICS1) C PD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load. (Refer to Test Circuit). Average operating current can be obtained by the following equation. I CC(opr) = C PD x V CC x f IN + I CCTEST CIRCUITL R T = Z OUT of pulse generator (typically 50Ω)WAVEFORM 1: PROPAGATION DELAYS FOR INVERTING OUTPUTS (f=1MHz; 50% duty cycle)SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.C IN Input Capacitance 5.05101010pF C PDPower Dissipation Capacitance (note 1)5.047pFM74HC138WAVEFORM 2: P ROPAGATION D ELAYS F OR N ON-INVERTING O UTPUTS(f=1MHz; 50% d uty c ycle)6/10M74HC138Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.© The ST logo is a registered trademark of STMicroelectronics© 2001 STMicroelectronics - Printed in Italy - All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - MoroccoSingapore - Spain - Sweden - Switzerland - United Kingdom© 10/10。

sn74hc138

PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)5962-8406201VEA ACTIVE CDIP J161TBD A42N/A for Pkg Type 5962-8406201VFA ACTIVE CFP W161TBD A42N/A for Pkg Type 84062012A ACTIVE LCCC FK201TBD POST-PLATE N/A for Pkg Type 8406201EA ACTIVE CDIP J161TBD A42N/A for Pkg Type 8406201FA ACTIVE CFP W161TBD A42N/A for Pkg Type JM38510/65802B2A ACTIVE LCCC FK201TBD POST-PLATE N/A for Pkg Type JM38510/65802BEA ACTIVE CDIP J161TBD A42N/A for Pkg Type SN54HC138J ACTIVE CDIP J161TBD A42N/A for Pkg Type SN74HC138D ACTIVE SOIC D1640Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC138DBR ACTIVE SSOP DB162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC138DBRE4ACTIVE SSOP DB162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC138DBRG4ACTIVE SSOP DB162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC138DE4ACTIVE SOIC D1640Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC138DG4ACTIVE SOIC D1640Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC138DR ACTIVE SOIC D162500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC138DRE4ACTIVE SOIC D162500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC138DRG4ACTIVE SOIC D162500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC138DT ACTIVE SOIC D16250Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC138DTE4ACTIVE SOIC D16250Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC138DTG4ACTIVE SOIC D16250Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC138N ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU N/A for Pkg Type SN74HC138N3OBSOLETE PDIP N16TBD Call TI Call TISN74HC138NE4ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeSN74HC138NSR ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC138NSRG4ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC138PW ACTIVE TSSOP PW1690Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC138PWE4ACTIVE TSSOP PW1690Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC138PWG4ACTIVE TSSOP PW1690Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC138PWLE OBSOLETE TSSOP PW16TBD Call TI Call TIOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)SN74HC138PWR ACTIVE TSSOP PW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC138PWRE4ACTIVE TSSOP PW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC138PWRG4ACTIVE TSSOP PW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC138PWT ACTIVE TSSOP PW16250Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC138PWTE4ACTIVE TSSOP PW16250Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC138PWTG4ACTIVE TSSOP PW16250Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SNJ54HC138FK ACTIVE LCCC FK201TBD POST-PLATE N/A for Pkg Type SNJ54HC138J ACTIVE CDIP J161TBD A42N/A for Pkg Type SNJ54HC138W ACTIVE CFP W161TBD A42N/A for Pkg Type (1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS),Pb-Free(RoHS Exempt),or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free(RoHS Exempt):This component has a RoHS exemption for either1)lead-based flip-chip solder bumps used between the die and package,or2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free(RoHS compatible)as defined above.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.OTHER QUALIFIED VERSIONS OF SN54HC138,SN54HC138-SP,SN74HC138:•Automotive:SN74HC138-Q1NOTE:Qualified Version Definitions:•Automotive-Q100devices qualified for high-reliability automotive applications targeting zero defectsTAPE AND REEL INFORMATION*All dimensions are nominalDevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant SN74HC138DBR SSOP DB 162000330.016.48.2 6.6 2.512.016.0Q1SN74HC138DR SOIC D 162500330.016.4 6.510.3 2.18.016.0Q1SN74HC138NSR SO NS 162000330.016.48.210.5 2.512.016.0Q1SN74HC138PWRTSSOPPW162000330.012.47.05.61.68.012.0Q1*All dimensions are nominalDevice Package Type Package Drawing Pins SPQ Length(mm)Width(mm)Height(mm) SN74HC138DBR SSOP DB162000346.0346.033.0 SN74HC138DR SOIC D162500333.2345.928.6 SN74HC138NSR SO NS162000346.0346.033.0 SN74HC138PWR TSSOP PW162000346.0346.029.0IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers AudioData Converters AutomotiveDLP®Products BroadbandDSP Digital ControlClocks and Timers MedicalInterface MilitaryLogic Optical NetworkingPower Mgmt SecurityMicrocontrollers TelephonyRFID Video&ImagingRF/IF and ZigBee®Solutions WirelessMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2009,Texas Instruments Incorporated。

单片机74HC138三八译码器的原理及应用方法

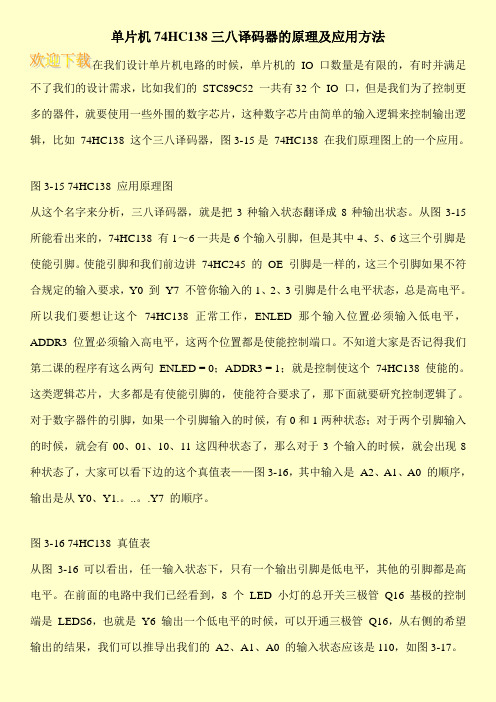

单片机74HC138三八译码器的原理及应用方法在我们设计单片机电路的时候,单片机的IO 口数量是有限的,有时并满足不了我们的设计需求,比如我们的STC89C52 一共有32个IO 口,但是我们为了控制更多的器件,就要使用一些外围的数字芯片,这种数字芯片由简单的输入逻辑来控制输出逻辑,比如74HC138 这个三八译码器,图3-15是74HC138 在我们原理图上的一个应用。

图3-15 74HC138 应用原理图从这个名字来分析,三八译码器,就是把3种输入状态翻译成8种输出状态。

从图3-15所能看出来的,74HC138 有1~6一共是6个输入引脚,但是其中4、5、6这三个引脚是使能引脚。

使能引脚和我们前边讲74HC245 的OE 引脚是一样的,这三个引脚如果不符合规定的输入要求,Y0 到Y7 不管你输入的1、2、3引脚是什么电平状态,总是高电平。

所以我们要想让这个74HC138 正常工作,ENLED 那个输入位置必须输入低电平,ADDR3 位置必须输入高电平,这两个位置都是使能控制端口。

不知道大家是否记得我们第二课的程序有这么两句ENLED = 0;ADDR3 = 1;就是控制使这个74HC138 使能的。

这类逻辑芯片,大多都是有使能引脚的,使能符合要求了,那下面就要研究控制逻辑了。

对于数字器件的引脚,如果一个引脚输入的时候,有0和1两种状态;对于两个引脚输入的时候,就会有00、01、10、11这四种状态了,那么对于3个输入的时候,就会出现8种状态了,大家可以看下边的这个真值表——图3-16,其中输入是A2、A1、A0 的顺序,输出是从Y0、Y1.。

..。

.Y7 的顺序。

图3-16 74HC138 真值表从图3-16可以看出,任一输入状态下,只有一个输出引脚是低电平,其他的引脚都是高电平。

在前面的电路中我们已经看到,8个LED 小灯的总开关三极管Q16 基极的控制端是LEDS6,也就是Y6 输出一个低电平的时候,可以开通三极管Q16,从右侧的希望输出的结果,我们可以推导出我们的A2、A1、A0 的输入状态应该是110,如图3-17。

译码器74HC138中文资料

译码器74HC138中文资料2010-01-01 08:00集成电路介绍:译码器74HC138中文资料74hc138 3-8线译码器,译码器也称解码器,译码过程实际上是一种翻译过程,即编码的逆过程。

译码器的输入是n位二值代码,输出是m个表征代码原意的状态信号(或另一种代码)。

一般情况下有m小于等于2的n次方,即译码器输入线比输出线要少。

译码器按其功能可分为三大类:(1)变量译码器:将输入的二进制代码还原为原始输入信号。

例如有两位二进制代码(0 ,1),可经译码器还原为四个信号状态(0,0)(0,1)(1,0) (1,1)(2)代码变换译码器:用于将一个数据的不同代码之间的相互转换。

例如二-十进制译码器可将8421码转换为十个状态。

(3)显示译码器:将数字、文字或符号的代码还原成相应的数字、文字、符号并显示出来的电路74hc138 3-8线译码器/CD74HC138 ,CD74HC238和CD74HCT138 , CD74HCT238是高速硅栅CMOS解码器,适合内存地址解码或数据路由应用。

hc138 作用原理于高性能的存贮译码或要求传输延迟时间短的数据传输系统,在高性能存贮器系统中,用这种译码器可以提高译码系统的效率。

将快速赋能电路用于高速存贮器时,译码器的延迟时间和存贮器的赋能时间通常小于存贮器的典型存取时间,这就是说由肖特基钳位的系统译码器所引起的有效系统延迟可以忽略不计。

HC138 按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个低电平输出。

两个低电平有效的赋能输入端和一个高电平有效的赋能输入端减少了扩展所需要的外接门或倒相器,扩展成24 线译码器不需外接门;扩展成32 线译码器,只需要接一个外接倒相器。

在解调器应用中,赋能输入端可用作数据输入端。

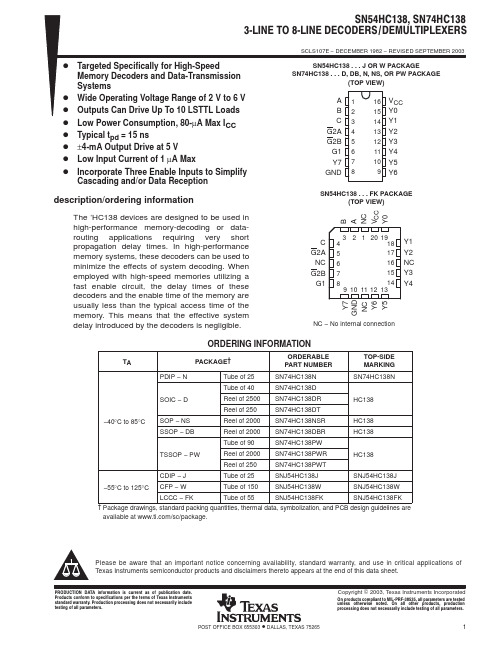

H L L L H H H H H L H H H H L L H L L H H H H L H H H L L H L H H H H H H L H H L L H H L H H H H H H L H L L H H H H H H H H H HCD74HC238, CD74HCT238 T1TRUTH TABLE真值表INPUTS 输入Outputs输出ENABLE 使能ADDRESS地址E3 E2 E1 A2 A1 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 X X H X X X L L L L L L L L X X X X X L L L L L L L X H X X X X L L L L L L L H L L L L L H L L L L L L H L L L L H L H L L L L L H L L L H L L L H L L L L H L L L H H L L L H L L L H L L H L L L L L L H L L H L L H L H L L L L L H L H L L H H L L L L L L L H H L L H H H L L L L L L L图1 引脚图图2 功能图图3 测试电路和波形应用电路:图4 舞台发光二极管灯光图5 可编程时钟定时器电路由上表可见74HC138译码器输出低电平有效。

74hc138的应用原理

74HC138的应用原理介绍74HC138是一种三到八线解码器,通常被用于数字电路设计中。

它具有识别三个输入信号,并将其映射到八个输出之一的功能。

本文将介绍74HC138的工作原理及其应用。

工作原理74HC138由三个二输入正逻辑门和一个三输入与非门组成。

它的三个输入(A0,A1和A2)可以表示八个不同的输入组合,输出由Y0到Y7表示。

通过设置三个输入信号中的不同组合,可以选择要激活的输出。

接下来,我们将详细介绍74HC138的应用原理。

使用示例以下是一个使用74HC138的示例电路图:python +—–+ +—–+ A0 —-| |————–| | | 74HC138 Y0 —- | A1 —-| |————–| | + +—–+ + +—–+ A2 —-| | | | | Decoder | | Register | | | | | E1 —-| | | | E2 —-| | | | E3 —-| | | | +————+ +————+ | | | | | 74LS138 | | 74LS175 | | | | | | | | | +————+ +————+ ```在上述电路中,输入A0,A1和A2信号用于选择要激活的输出。

74HC138芯片将输入信号和输出互相连接,并通过输出信号将电流传递到68LS175寄存器芯片。

功能以下是74HC138的功能:1.选择输出信号:通过设置输入A0,A1和A2的不同组合,可以选择激活的输出。

共有八个输出(Y0到Y7)。

2.输入信号:74HC138接收三个输入信号(A0,A1和A2)。

3.解码功能:74HC138将输入信号解码为对应的输出信号。

4.数字电路集成:74HC138是一个数字电路集成芯片,通过一片芯片就能实现数字信号的输入和输出。

应用领域74HC138广泛应用于以下领域:1.数字系统设计:74HC138用于基于数字信号的系统设计,如计算机、电子设备等。

74138的工作原理如下图所示

74138的工作原理如下图所示:从上图可看出,74138有三个输入端:A0、A1、A2和八个输出端Q0~Q7。

当输入端A0、A1、A2的编码为000时,译码器输出为Q0=0,而Q1~Q7=1。

即Q0对应于A0、A1、A2为000状态,低电平有效。

A0、A1、A2的另外7种组合见后面的真值表。

图中S1、S2、S3为使能控制端,起到控制译码器是否能进行译码的作用。

只有S1为高电平,S2、S3均为低电平时,才能进行译码,否则不论输入羰输入为何值,每个输出端均为1。

下图是输入端A0、A1、A2为000,控制端S1=1、S1=0、S2=0的电平示意图(红色数字为端口电平),大家可按下图进行分析,也可以分析输出端另外七种组合时的输出情况。

74138 三线-八线译码器真值表:一、译码器的定义及功能1. 定义:具有译码功能的逻辑电路称为译码器。

译码即编码的逆过程,将具有特定意义的二进制码进行辨别,并转换成控制信号。

2. 分类:3. 功能:二进制译码器一般原理图一个n→2n译码器结构如上图,n个输入端,2n个输出端。

它是一个多输出逻辑组合电路,对每种可能的输入条件,有且仅有一个输出信号为逻辑“1”,所以我们可以把它当作最小项产生器,一个输出就相应于提取一个最小项。

4. 译码器电路结构:首先我们先来分析两输入译码器结构,由于2输入变量A、B共有4种不同状态的组合,因而可以译出4个输出信号,所以简称为2/4线译码器。

2线-4线译码器逻辑图由图可以写出输出端逻辑表达式:根据输出逻辑表达式可以列出功能表。

由表可知,时无论A、B 为何种状态,输出全为1,译码器处于非工作状态。

而当时,对应于AB 的某种状态组合,其中只有一个输出量为0,其余各输出量均为1。

例如:AB=0时,输出Y0=0,Y1~Y3=1,由此可见,译码器是通过输出端的逻辑电平来识别不同的代码。

在我们讲述的这种结构中,输出0表示有效电平,所以就叫做低电平有效。

2线-4线译码器功能表输入输出EI A B Y0Y1Y2Y31 x X 1 1 10 0 0 0 1 1 10 0 1 1 0 1 10 1 0 1 1 0 10 1 1 1 1 0二、集成电路译码器1.74138集成译码器下图为常用的集成译码器74LS138的逻辑图和引脚图。

74HC138译码器实验

74HC138译码器实验74HC138译码器实验一、实验目的掌握74138电路的基本知识及由软件编译的译码器控制方式。

二、实验说明译码器是可以将输入二进制代码的状态翻译成输出信号,以表示其原来含义的电路。

三、实验步骤由软件控制138译码器的工作方式,可以改变A,B,C 的端口而改变其译码输出JD6口接8位发光二极管JD10,显示译码输出值。

本实验要用到单片机最小应用系统(F1区)、八位逻辑电平输出(B1区)、十六位逻辑电平显示(I4区)和译码器模块(C5区)。

1、单片机最小应用系统CPU 的P1口JD1F 接138译码器上的JD2C,而138译码器的JD3C 接到十六位逻辑显示JD2I ,A 、B 、C 接八位逻辑电平输出的K2,K1,K0。

(K2为低位,K0为高位如要选择Y1,K2、K1、K0对应的值为001)2、用串行数据通信线连接计算机与仿真器,把仿真器插到模块的锁紧插座中,请注意仿真器的方向:缺口朝上。

3、打开Keil uVision2仿真软件,首先建立本实验的项目文件,接着添加“TH27_74138译码程序.ASM ”源程序,进行编译,直到编译无误。

4、编译无误后,全速运行程序。

改变K0,K1,K2的状态观察发光二极管的显示,是否与控制端口的对应。

5、也可以把源程序编译成可执行文件,用ISP 烧录器烧录到89S52/89S51芯片中。

(ISP 烧录器的使用查看附录二)四、实验程序(见光盘中的程序文件夹)五、原理图A 1B 2C3G2A 4G2B 5G16Y77Y69Y510Y411Y312Y213Y114Y015U6C 74LS13812345678JD2C12345678JD3C Y0-7ABC。

74HC138D

4. Ordering information

Table 2: Ordering information Package Temperature range Name 74HC138 74HC138N 74HC138D 74HC138DB 74HC138PW 74HC138BQ −40 °C to +125 °C −40 °C to +125 °C −40 °C to +125 °C −40 °C to +125 °C −40 °C to +125 °C DIP16 SO16 SSOP16 TSSOP16 plastic dual in-line package; 16 leads (300 mil); long body plastic small outline package; 16 leads; body width 3.9 mm plastic shrink small outline package; 16 leads; body width 5.3 mm plastic thin shrink small outline package; 16 leads; body width 4.4 mm SOT38-1 SOT109-1 SOT338-1 SOT403-1 Description Version Type number

5. Functional diagram

Y0 1 1 2 3 A0 A1 A2 Y0 Y1 Y2 Y3 4 5 6 E1 E2 E3 Y4 Y5 Y6 Y7

mna370

15 14 13 12 11 10 9 7

A0 A1 A2 3-to-8 DECODER ENABLE EXITING

Y1 Y2 Y3 Y4 Y5 Y6 Y7

HD74HC138P中文资料

HD74HC1383-to-8-line Decoder/Demultiplexer with Address LatchREJ03D0570-0200(Previous ADE-205-444)Rev.2.00Oct 11, 2005 DescriptionThe HD74HC138 has 3 binary select inputs (A, B and C). If the device is enabled these inputs determine which one of the eight normally high outputs will go low. Two active low and one active high enables (G1, G2A and G2B) are provided to ease the cascading of decoders.Features• High Speed Operation: t pd (A, B, C to Y) = 16.5 ns typ (C L = 50 pF)• High Output Current: Fanout of 10 LSTTL Loads• Wide Operating Voltage: V CC = 2 V to 6 V• Low Input Current: 1 µA max• Low Quiescent Supply Current: I CC (static) = 4 µA max (Ta = 25°C)• Ordering InformationPart Name Package TypePackage Code(Previous Code)PackageAbbreviationTaping Abbreviation(Quantity)HD74HC138P DILP-16pin PRDP0016AE-B(DP-16FV)P —HD74HC138FPEL SOP-16 pin (JEITA) PRSP0016DH-B(FP-16DAV)FP EL (2,000 pcs/reel)HD74HC138TELL TSSOP-16pin PTSP00016JB-A(TTP-16DAV)T ELL (2,000 pcs/reel)Note: Please consult the sales office for the above package availability.Function TableInputsEnable SelectOutputs G1 G 2A G 2B C B A Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7X X H X X X H H H H H H H H X H X X X X H H H H H H H H L X X X X X H H H H H H H H H L L L L LL H H H H H H H H L L L L H H L H H H H H H H L L L H L H H L H H H H H H L L L H H H H H L H H H H H L L H L L H H H H L H H H H L L H L H H H H H H L H H H L L H H L H H H H H H L H H L L H H H H H H H H H H L H : High level L : Low level X : IrrelevantPin ArrangementAbsolute Maximum RatingsItem Symbol Rating UnitSupply voltage range V CC –0.5 to +7.0 V Input voltage V IN –0.5 to V CC + 0.5 V Output voltage V OUT –0.5 to V CC + 0.5 V Output current I OUT ±25 mA DC current drain per V CC , GND I CC , I GND ±50 mA DC input diode current I IK ±20 mA DC output diode current I OK ±20 mA Power dissipation per package P T 500 mW Storage temperature Tstg –65 to +150 °C Note: The absolute maximum ratings are values, which must not individually be exceeded, and furthermore, no two ofwhich may be realized at the same time.Recommended Operating ConditionsItem Symbol Ratings Unit ConditionsSupply voltage V CC 2 to 6 V Input / Output voltage V IN , V OUT 0 to V CC V Operating temperature Ta –40 to 85 °C0 to 1000 V CC = 2.0 V0 to 500 V CC = 4.5 VInput rise / fall time *1t r , t f 0 to 400 ns V CC = 6.0 V Note: 1. This item guarantees maximum limit when one input switches.Waveform: Refer to test circuit of switching characteristics.Electrical CharacteristicsTa = 25°C Ta = –40 to+85°CItem Symbol V CC (V) Min Typ Max Min Max UnitTest Conditions2.0 1.5 — — 1.5 — 4.53.15 — — 3.15 — V IH6.0 4.2 — — 4.2 — V2.0 — — 0.5 — 0.5 4.5 — — 1.35 — 1.35 Input voltageV IL6.0 — — 1.8 — 1.8V 2.0 1.9 2.0 — 1.9 — 4.5 4.4 4.5 — 4.4 — 6.0 5.9 6.0 — 5.9 — I OH = –20 µA4.5 4.18 — — 4.13 — I OH = –4 mAV OH6.0 5.68 — — 5.63 —V Vin = V IH or V IL I OH = –5.2 mA2.0 — 0.0 0.1 — 0.1 4.5 — 0.0 0.1 — 0.1 6.0 — 0.0 0.1 — 0.1 I OL = 20 µA4.5 — — 0.26 — 0.33 I OL = 4 mA Output voltage V OL 6.0 — — 0.26 — 0.33VVin = V IH or V IL I OL = 5.2 mAInput current Iin 6.0 — — ±0.1 — ±1.0 µAVin = V CC or GNDQuiescent supplycurrent I CC 6.0— — 4.0 — 40 µA Vin = V CC or GND, Iout = 0 µASwitching Characteristics (C L = 50 pF, Input t r = t f = 6 ns)Ta = 25°C Ta = –40 to +85°CItem Symbol V CC (V) Min Typ Max Min Max UnitTest Conditions2.0 — — 175 — 220 4.5 — 17 35 — 44 t PHL6.0 — — 30 — 37 ns 2.0 — — 150 — 190 4.5 — 16 30 — 38 t PLH6.0 — — 26 — 33 ns A, B or C to Y 2.0 — — 150 — 190 4.5 — 16 30 — 38 t PHL6.0 — — 26 — 33 ns 2.0 — — 150 — 190 4.5 — 17 30 — 38 t PLH6.0 — — 26 — 33 ns G 1 to Y 2.0 — — 175 — 220 4.5 — 15 35 — 44 t PHL6.0 — — 30 — 37 ns 2.0 — — 150 — 190 4.5 — 17 30 — 38 Propagation delaytimet PLH6.0 — — 26 — 33 ns G 2A or G 2B to Y 2.0 — — 75 —90 4.5 — 5 15 — 19 Output rise/falltimet TLH , t THL6.0 — — 13 — 16 ns Input capacitance Cin— — 5 10—10 pFTest CircuitWaveformsPackage Dimensions RENESAS SALES OFFICESRefer to "/en/network" for the latest and detailed information.Renesas Technology America, Inc.450 Holger Way, San Jose, CA 95134-1368, U.S.ATel: <1> (408) 382-7500, Fax: <1> (408) 382-7501Renesas Technology Europe LimitedDukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900Renesas Technology (Shanghai) Co., Ltd.Unit 205, AZIA Center, No.133 Yincheng Rd (n), Pudong District, Shanghai 200120, ChinaTel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7898Renesas Technology Hong Kong Ltd.7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong KongTel: <852> 2265-6688, Fax: <852> 2730-6071Renesas Technology Taiwan Co., Ltd.10th Floor, No.99, Fushing North Road, Taipei, TaiwanTel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999Renesas Technology Singapore Pte. Ltd.1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632Tel: <65> 6213-0200, Fax: <65> 6278-8001Renesas Technology Korea Co., Ltd.Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, KoreaTel: <82> (2) 796-3115, Fax: <82> (2) 796-2145Renesas Technology Malaysia Sdn. BhdUnit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, MalaysiaTel: <603> 7955-9390, Fax: <603> 7955-9510© 2005. Renesas Technology Corp., All rights reserved. Printed in Japan.。

74HC138DR2G;74HC138DTR2G;中文规格书,Datasheet资料

16 1

16 1

MARKING DIAGRAMS

16

SOIC−16 D SUFFIX CASE 751B

HC138G AWLYWW

1

TSSOP−16 DT SUFFIX CASE 948F

16

HC 138 ALYW G

G

1

HC138 = Device Code

A

= Assembly Location

Standard No. 7A

• ESD Performance: HBM > 2000 V; Machine Model > 200 V • Chip Complexity: 100 FETs or 29 Equivalent Gates • These are Pb−Free Devices

Features

• Output Drive Capability: 10 LSTTL Loads • Outputs Directly Interface to CMOS, NMOS and TTL • Operating Voltage Range: 2.0 to 6.0 V • Low Input Current: 1.0 mA • High Noise Immunity Characteristic of CMOS Devices • In Compliance with the Requirements Defined by JEDEC

level (e.g., either GND or VCC). Unused outputs must be left open.

TL Lead Temperature, 1 mm from Case for 10 SecSSOP Package)

单片机课件设计—74HC138译码器实验

单片机课件设计—74HC138译码器实验设计者:王凡(20070901140)蒋太明(20070901136)设计者所在班级:计算机科学系应用0703班51单片机74HC138译码器实验设计流程一.实验目的熟悉译码器的使用方法,灵活应用74HC138进行电路设计。

二.实验设备及器件IBM PC 机一台DP-51PROC 单片机综合仿真实验仪一台三.实验内容1. 编写程序,通过单片机的P1 口控制74HC138的数据输入端,从而选通相应的数据输出位。

2. 将译码数据输出端口连接到8 个LED 指示灯,验证译码的正确性。

四.实验要求通过实验掌握译码器的工作原理和实际应用方法。

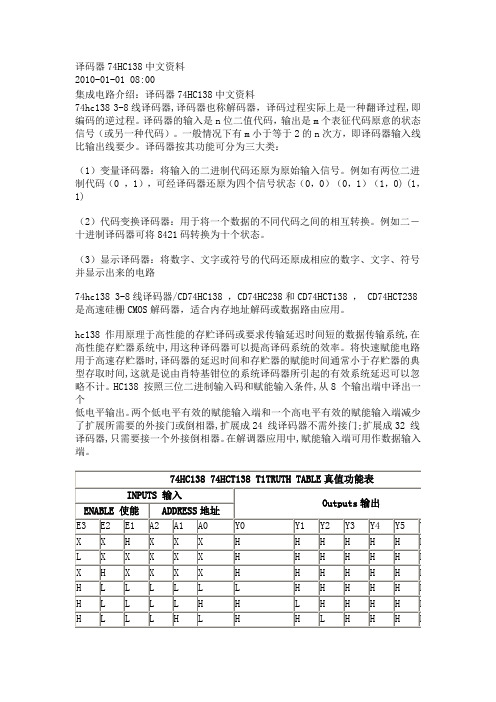

表3.3 74HC138真值表和管脚图五.实验步骤1. 短接A3 区JP4 接口上的短路帽,将A3 区A、B、C、/G1、/G2A、/G2B 与A2区的P10~P15相连。

如图3.9 所示。

图3.9 实验9 原理图2. 将D1 区的LED1、LED2、LED3 分时连接到A3 区译码数据输出接口/Y0~/Y7。

3. 打开程序调试软件,下载运行编写好的软件程序,查看程序运行结果是否正确。

六.实验预习要求认真阅读本书这一节的实验内容,提前做好实验准备工作。

七.实验参考程序ORG 8000H ;此为硬件仿真程序,使用软件仿真或直接运行,应改为0000HLJMP MainORG 8100H ;此为硬件仿真程序,使用软件仿真或直接运行,应改为0100HMAIN:MOV SP,#60HMOV R4,#0DJNZ R4,$;设置译码器使能CLR P1.5CLR P1.4SETB P1.3;译码数据输入CLR P1.0 ;设置A=0CLR P1.1 ;设置B=0SETB P1.2 ;设置C=1SJMP $;END。

利用74HC138制作4线—16线译码器

《组合逻辑电路的分析与设计》————利用74HC138制作4线—16线译码器院系:电子与信息工程学院利用74HC138制作4线—16线译码器一、实验目的1、掌握译码器的测试方法。

2、了解中规模集成译码器的功能,管脚分布,掌握其逻辑功能。

3、掌握用译码器构成组合电路的方法。

二、实验仪器1、数字电路实验箱2、74HC138 3-8线译码器 2片三、实验原理1、CMOS器件74HC138的逻辑功能及应用74HC138译码器可接受3位二进制加权地址输入(A0, A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC138特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。

除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。

利用这种复合使能特性,仅需4片74HC138芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到32线)译码器。

任选一个低有效使能输入端作为数据输入,而把其余的使能输入端作为选通端,则74HC138亦可充当一个8输出多路分配器,未使用的使能输入端必须保持绑定在各自合适的高有效或低有效状态。

其引脚排列如下图(一)所示图(一)74HC138功能表如下表(一)所示:表(一)3、用两个3线-8线译码器构成4线-16线译码器。

利用使能端能方便地将两个 3/8译码器组合成一个4/16译码器,如下图图(二)所示。

图(二)四、实验结果记录:1、74HC138逻辑功能测试结果记录如下表表(二)所示:输入输出E 1E2+E3A2A1AY0(非)Y1(非)Y2(非)Y3(非)Y4(非)Y5(非)Y6(非)Y7(非)1 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 1 1 0 1 1 1 1 1 1 1 0 0 1 0 1 1 0 12 1 1 1 1 1 0 0 1 1 1 1 1 0 1 1 1 1 1 0 1 0 0 1 1 1 1 0 1 1 1 1 0 1 0 1 1 1 1 1 1 0 1 11 0 1 1 0 1 1 1 1 1 1 0 1 1 0 1 1 1 1 1 1 1 1 1 1 0 0 X X X X 1 1 1 1 1 1 1 1 X 1 X X X 1 1 1 1 1 1 1 1表(二)2、测试部分图片如下图图(三)、图(四)、图(五)、图(六)图(七)所示:图(三)图(四)图(五)图(六)图(七)五、实验心得:通过这次试验,使我学到了不少实用的知识,更重要的是,做实验的过程,思考问题的方法,这与做其他的实验是通用的,真正使我受益匪浅。

74HC138中文资料_数据手册_参数

74HCT138 3至8行解码器/解复用器;反相 [1] 对于DIP16封装:P TOT 线性降低12 MW / K以上70 C. [2] 对于SO16封装:P TOT 线 性降低至70 MW / K以上 C. [3] 对于SSOP16和TSSOP16封装:P TOT 线性降低 至 5.5 MW / K以上 C. [4] 对于DHVQFN16封装:P TOT 线性降低 至 4.5 MW / K,高于60 C. 8.推荐工作条件 9.静态特性 P TOT总功耗 DIP16封装 [1] - 750 SO16封装 [2] - 500毫瓦 SSOP16包 [3] - 500毫瓦 TSSOP16包 [3] - 500毫瓦 DHVQFN16包 [4] - 500毫瓦表4 限制值 ...继续根据绝对大额定值系统(IEC 60134).电压以GND为参考(地= 0 V).符号参数条件敏马克斯单元表5推荐工作条件电压以GND为参考(地= 0 V)符号参数 条件 74HC138 74HCT138单元敏典型马克斯敏典型马克斯 V CC电源电压 2.0 5 6 4.5 5 5.5 V V 我输入电压 0 - V CC 0- V CC V V O 输出电压 0 - V CC 0- V CC V T AMB环境温度 -40 +25 +125 -40 +25 +125 C ΔT/ΔV输入转换升降率 V CC = 2.0 V - - 625 - - - NS / V V CC = 4.5V - 1.67 139 - 1.67 139 NS / V V CC = 6.0 V - - 83 - - - NS / V表6静态特性在推荐的操作条件下;电压参考GND(地= 0 V).符号参数条件 T AMB = 25 C T AMB = -40°C至 + 85 C T AMB = -40°C至 +125 C单元敏典型马克斯敏马克斯敏马克斯 74HC138 V IH高水平输入电压 产品数据表 2012年6月4日至27日 17之19恩智浦半导体 74HC138; 74HCT138 3至8行解码器/解复用器;反相 15.法律信息 15.1数据表 状态 [1]请在启动或完成设计之前查阅近发布的文档. [2]术语“短数据表”在“定义”一节中进行了解释. [3]本文档中描述的设 备的产品状态可能在本文档发布后发生变化,并且在多个设备的情况下可能会有所不同.新的产品状态有关信息可以在网址 上找到. 15.2定义草案 - 文件仅为草案版本.内容还在内部审查和正式批准,可能会导致修改或添加.恩 智浦半导体不给任何陈述或保证的准确性或完整性包含在这里的信息,并且对后果不承担任何责任使用这些信息.简短的数据 表 - 简短的数据表是来自完整数据表的摘录具有相同的产品型号和标题.一个简短的数据表是打算仅供快速参考,不应依赖于 详细说明完整的信息.有关详细和完整的信息,请参阅相关的完整数据可通过当地恩智浦半导体销售部门索取办公室.如果与短 数据表有任何不一致或冲突,应以完整的数据表为准.产品规格 - 产品中提供的信息和数据数据表应按照约定的方式定义产品 的规格恩智浦半导体及其客户,除非恩智浦半导体和客户已经以书面形式明确表示同意.然而,在任何情况下,恩智浦半导体 产品的协议应是有效的被视为提供了超出上述范围之外的功能和品质产品数据表. 15.3免责声明有限保修和责任 - 本文件中的信 息被认为是准确可靠.但是,恩智浦半导体并没有给予任何陈述或保证,明示或暗示,准确性或这些信息的完整性,对此不承 担任何责任使用这些信息的后果.恩智浦半导体不采纳如果信息提供,则对本文件中的内容负责恩智浦半导体以外的来源.恩智 浦半导体不对任何间接的,附带的,惩罚性的,特殊的或相应的损害赔偿(包括但不限于 - 损失利润,

74HC138系列单片机控制LED数码管的原理图解析

74HC138系列单片机控制LED数码管的原理图解析LED小灯是一种简单的LED,只能通过亮和灭来表达简单的信息。

而这节课我们要来学习一种能表达更复杂信息的器件——LED数码管。

先给大家提供一张原理图看一下,如图5-3所示。

这是比较常见的数码管的原理图,我们板子上一共有6个数码管。

前边有了 LED 小灯的学习,数码管学习就会轻松的多了。

从图5-3可以看出来,数码管共有 a、b、c、d、e、f、g、dp 这么8个段,而实际上,这8个段每一段都是一个LED 小灯,所以一个数码管就是由8个LED 小灯组成的。

我们看一下数码管内部结构的示意图,如图5-4。

数码管分为共阳和共阴两种,共阴数码管就是8只 LED 小灯的阴极是连接在一起的,阴极是公共端,由阳极来控制单个小灯的亮灭。

同理,共阳数码管就是阳极接在一起,大家可以认真研究下图5-4。

细心的同学会发现,图5-3的数码管上边有2个com,这就是我们数码管的公共端。

为什么有2个呢,一方面是2个可以起到对称的效果,刚好是10个引脚,另外一个方面,公共端通过的电流较大,我们初中就学过,并联电路电流之和等于总电流,用2个 com 可以把公共电流平均到2个引脚上去,降低单条线路承受的电流。

从我们开发板的电路图上能看出来,我们所用的数码管都是共阳数码管,一共有6个,如图5-5所示。

6个数码管的 com 都是接到了正极上,当然了,和 LED 小灯电路一样,也是由74HC138 控制三极管的导通来控制整个数码管的使能。

先来看最右边的DS1 这个数码管,原理图上可以看出,控制DS1 的三极管是 Q17,控制 Q17 的引脚是 LEDS0,对应到 74HC138 上边就是 U3 的 Y0 输出,如图5-6所示。

我们现在的目的是让 LEDS0 这个引脚输出低电平,相信大家现在可以根据前边学过的知识独立把ADDR0、ADDR1、ADDR2、ADDR3、ENLED 这4个所需输入的值写出来了,现在大家不要偷懒,根据74HC138 的手册去写一下,不需要你记住这些结论,但是遇到就写一次,锻炼过几次后,遇到同类芯片自己就知道如何去解决问题了。

74HC138级联

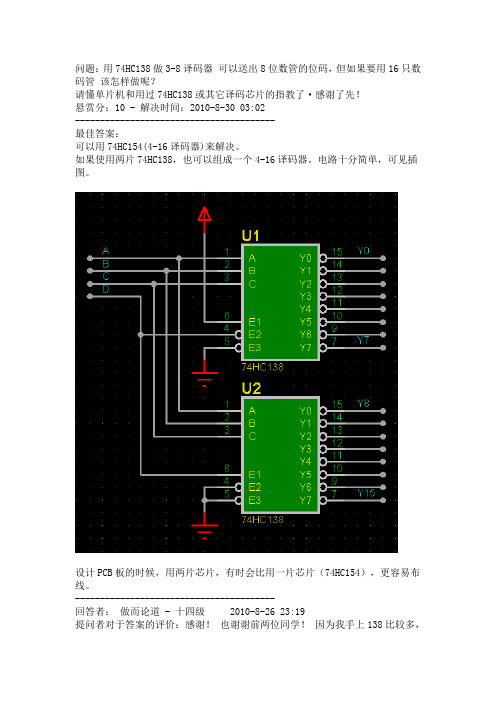

问题:用74HC138做3-8译码器可以送出8位数管的位码,但如果要用16只数码管该怎样做呢?请懂单片机和用过74HC138或其它译码芯片的指教了·感谢了先!悬赏分:10 - 解决时间:2010-8-30 03:02----------------------------------------最佳答案:可以用74HC154(4-16译码器)来解决。

如果使用两片74HC138,也可以组成一个4-16译码器。

电路十分简单,可见插图。

设计PCB板的时候,用两片芯片,有时会比用一片芯片(74HC154),更容易布线。

----------------------------------------回答者:做而论道 - 十四级 2010-8-26 23:19提问者对于答案的评价:感谢!也谢谢前两位同学!因为我手上138比较多,所以考虑用这个组合下。

原题网址:/question/178416038.html----------------------------------------后记:使用一块74HC154,就是把16条译码输出引线都集中在一块芯片,然后还需要把它们再分散到16个目标地点。

这在PCB上布线的时候,十分的不便。

用两个74HC138芯片,就方便多了。

呵呵,必须是有实践经验的人,才能理解这个观点。

另外,做而论道还用三块74HC138芯片设计过5-24的译码电路,电路也十分简单,可见下图。

当时是用在24×192点阵的LED显示屏幕上,分成24行显示8个24×24点阵的汉字。

/* 点阵显示屏为16*64条屏,可级联,上下屏由两个74HC138分别控制1/8扫 *//* 屏接口为20针,1:A0,3:A1,5:A2,7:下半屏,9:RCK,11:SCK,13:SI,15:下一屏接口17:下半屏,19,2-20:地*//* 李于浙江2011.5.3 */#include<reg52.h>#define uchar unsigned char#define uint unsigned int/*************************************************/sbit hc595_SI = P0^0;//串行移位数据输入sbit hc595_SCK = P0^1;//595移位时钟,上升沿触发sbit hc595_RCK = P0^2;//595数据锁存信号,上升沿触发,输出锁存器控制sbit LS138_A0 = P1^0;//行选择1-8 行sbit LS138_A1 = P1^1;//行选择sbit LS138_A2 = P1^2;//行选择sbit LS138_G_S = P1^3;//上半屏显示允许控制信号端口,138行扫描使能端,高电平有效sbit LS138_G_X = P1^4;//下半屏显示允许控制信号端口,138行扫描使能端,高电平有效// 11110000 上屏第1行,且亮,下屏全不亮0xf0// 11111000void delay(uint dt){uchar bt;for(;dt;dt--)for(bt=0;bt<200;bt++);}/**********************74HC595驱动************************/void hc595_write_data(uchar data_ds){uchar n_bit;//n位for(n_bit=0;n_bit<8;n_bit++) //1个字节{hc595_SCK=0;if(data_ds&0x01) //低位在前{hc595_SI=1;}else{hc595_SI=0;}data_ds = data_ds>>1;//数据在上升沿移位hc595_SCK=1;delay(1);}}/*************74HC595数据锁存输出*********/void hc595_display(){hc595_RCK=0;delay(1);hc595_RCK=1;}uchar sw[16]={0xf0,0xf1,0xf2,0xf3,0xf4,0xf5,0xf6,0xf7,0x88,0x89,0x8a,0x8b,0x8c,0x8d,0x8e,0x8f,};//138的驱动代码,根据138的真值表计算而来。

利用74HC138制作4线—16线译码器

《组合逻辑电路的分析与设计》————利用74HC138制作4线—16线译码器院系:电子与信息工程学院利用74HC138制作4线—16线译码器一、实验目的1、掌握译码器的测试方法。

2、了解中规模集成译码器的功能,管脚分布,掌握其逻辑功能。

3、掌握用译码器构成组合电路的方法。

二、实验仪器1、数字电路实验箱2、74HC138 3-8线译码器 2片三、实验原理1、CMOS器件74HC138的逻辑功能及应用74HC138译码器可接受3位二进制加权地址输入(A0, A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC138特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。

除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。

利用这种复合使能特性,仅需4片74HC138芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到32线)译码器。

任选一个低有效使能输入端作为数据输入,而把其余的使能输入端作为选通端,则74HC138亦可充当一个8输出多路分配器,未使用的使能输入端必须保持绑定在各自合适的高有效或低有效状态。

其引脚排列如下图(一)所示图(一)74HC138功能表如下表(一)所示:输入输出E1(非)E2(非)E3A2A1A0Y0(非)Y1(非)Y2(非)Y3(非)Y4(非)Y5(非)Y6(非)Y7(非)H L H L L L L H H H H H H HH L H L L H H L H H H H H HH L H L H L H H L H H H H HH L H L H H H H H L H H H HH L H H L L H H H H L H H HH L H H L H H H H H H L H HH L H H H L H H H H H H L HL L H H H H H H H H H H H L L X X X X X H H H H H H H H X H X X X X H H H H H H H H表(一)3、用两个3线-8线译码器构成4线-16线译码器。

74HC138应用-讲得真的很清楚、很明白。

74HC138资料及应用一、74HC138管脚图E3、E2、E1是使能输入端,E1和E2低电平有效,E3高电平有效。

A0、A1和A3是控制输入端,由他们的组合决定Y的输出。

Y0——Y7是输出端,输出低电74HC138图平,同一时刻八个Y之中只有一个输出有效。

二、真值表三、引脚接法及应用举例(一)74HC138连接图(1)接法如上图中所示,一般1.E3 接电源、E2、E1接地;2.管脚A、B、C接单片机P口的控制信号;3.Y0——Y7接输出对象。

(2)应用举例上图中,输入管脚A、B、C分别由P1.0、P1.1、P1.2信号控制,Y0——Y7输出做其他芯片的片选信号。

根据真值表,当P1.0=0、P1.1=0 、P1.2=0时,Y0=0,CS1=0,选通62256芯片;同理,当P1.0=1、P1.1=0 、P1.2=0时,Y1=0,CS2=0,选通DS12887芯片。

其他依次类推。

(二)E3 接高、E2、E1接地。

一个简易程序:138译码器实验控制跑马灯#include <reg51.h>sbit HC138A = P2^2; //定义译码器输入端A 在P2.2 管脚上sbit HC138B = P2^3; //定义译码器输入端B 在P2.3 管脚上sbit HC138C = P2^4; //定义译码器输入端C 在P2.4 管脚上void delay(unsigned int i){unsigned char j;for(i; i > 0; i--)for(j = 255; j > 0; j--);}main(){// 点亮第一个LED灯HC138C = 0; HC138B = 0; HC138A = 0; delay(1500); //延时// 点亮第二个LED灯HC138C = 0; HC138B = 0; HC138A = 1; delay(1500); //延时// 点亮第三个LED灯HC138C = 0; HC138B = 1; HC138A = 0; delay(1500);// 点亮第四个LED灯HC138C = 0; HC138B = 1; HC138A = 1; delay(2000);// 点亮第五个LED灯HC138C = 1; HC138B = 0; HC138A = 0; delay(1500);// 点亮第六个LED灯HC138C = 1; HC138B = 0; HC138A = 1; delay(1500);HC138C = 1; HC138B = 1; HC138A = 0; delay(1500);HC138C = 1; HC138B = 1; HC138A = 1; delay(1500);}。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

74HC138中文资料

默认分类 2009-11-10 12:38:48

阅读1084 评论

0 字号:大中小

引脚布局

74HC138 概述

74HC138是一款高速CMOS器件,74HC138引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC138译码器可接受3位二进制加权地址输入(A0, A1和A3),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC138特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。

除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。

利用这种复合使能特性,仅需4片74HC138芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到32线)译码器。

任选一个低有效使能输入端作为数据输入,而把其余的使能输入端作为选通端,则74HC138亦可充当一个8输出多路分配器,未使用的使能输入端必须保持绑定在各自合适的高有效或低有效状态。

74HC138与74HC238逻辑功能一致,只不过74HC138为反相输出。

74HC138 特性

•多路分配功能

•复合使能输入,轻松实现扩展

•兼容JEDEC标准no.7A

•存储器芯片译码选择的理想选择

•低有效互斥输出

•ESD保护

o HBM EIA/JESD22-A114-C超过2000 V

o MM EIA/JESD22-A115-A超过200 V

•温度范围

o-40~+85 ℃

o-40~+125 ℃

引脚布局74HC138 参数

74HC138 基本参数

电压 2.0~6.0V

驱动电流+/-5.2 mA

传输延迟12 ns@5V

74HC138 其他特性

逻辑电平CMOS

功耗考量低功耗或电池供电应用

74HC138 封装与引脚

SO16, SSOP16, DIP16, TSSOP16

74HC165 概述

74HC165是一款高速CMOS 器件,74HC165遵循JEDEC 标准no.7A 。

74HC165引脚兼容低功耗肖特基TTL (LSTTL )系列。

74HC165是8位并行读取或串行输入移位寄存器,可在末级得到互斥的串行输出(Q7Q7),当并行读取(PL )输入为低时,从D0到D7口输入的并行数据将被异步地读取进寄存器内。

和

而当PL 为高时,数据将从DS 输入端串行进入寄存器,在每个时钟脉冲的上升沿向右动一位(Q0 → Q1 → Q2,等等)。

利用这种特性,只要把Q7输出绑定到下一级的DS 输入,即实现并转串扩展。

移可 74HC165的时钟输入是一个“门控或”结构,允许其中一个输入端作为低有效时钟使能(CE )输入。

CP 和CE 的引脚分配是独立的并且在必要时,为了布线的方便可以互换。

只有在CP 为高时,才允许CE 由低转高。

在PL 上升沿来临之前,不论是CP 还是CE ,都应当置高,以防止数据在PL 的活动状态发生位移。

74HC165 特性

• 异步8位并行读取 • 同步串行输入

• 兼容JEDEC 标准no.7A •

ESD 保护

o HBM EIA/JESD22-A114E 超过2000 V o MM EIA/JESD22-A115-A 超过200 V

•

温度范围

o -40~+85 ℃ o -40~+125 ℃

引脚布局

74HC165 参数 74HC165 基本参数 电压

2.0~6.0V 驱动电流

+/-5.2 mA

传输延迟 16 ns@5V

74HC165 其他特性 最高频率 56 MHz

逻辑电平 CMOS

功耗考量 低功耗或电池供电应用

74HC165 封装与引脚

SO16, SSOP16, DIP16, TSSOP16

74HC164 概述

74HC164是一款高速CMOS器件,74HC164引脚兼容低功耗肖特基TTL (LSTTL)系列。

74HC164遵循JEDEC标准no.7A。

74HC164是带有串行数据输入和并行输出的8位边沿触发移位寄存器。

数据通过两个输入端(DSA和DSB)中的任一个串行输入。

当其中一端作为数据输入时,另一端可作为高有效使能端。

两输入端必须连接在一起,或者把未使用的端口绑定为高。

在时钟脉冲(CP)的每个上升沿,数据将向右移动一位,并输入至Q0,Q0是两个数据输入端(DSA和DSB)进行逻辑与运算后的结果,在时钟脉冲上升沿来临之前存在一段就绪时间。

如果74HC164的主复位(MR)输入为低电平,所有其他输入将被无视,并且异步清零寄存器,强制所有输出为低电平。

74HC164 特性

•门控串行数据输入

•异步主复位

•兼容JEDEC标准no.7A

•ESD保护

o HBM EIA/JESD22-A114-B超过2000 V

o

o MM EIA/JESD22-A115-A超过200 V

•可选多种封装类型

•温度范围

o-40~+85 ℃

o-40~+125 ℃

74HC164 参数

74HC164 基本参数

电压 2.0~6.0V

驱动电流+/-5.2 mA

传输延迟12 ns@5V

74HC164 其他特性

最高频率78 MHz

逻辑电平CMOS

功耗考量低功耗或电池供电应用

74HC164 封装与引脚

SO14, SSOP14, DIP14, TSSOP14。