Tanner Pro集成电路设计(CMOS倒相器的版图)

清华大学《数字集成电路设计》周润德 第5章 CMOS反相器

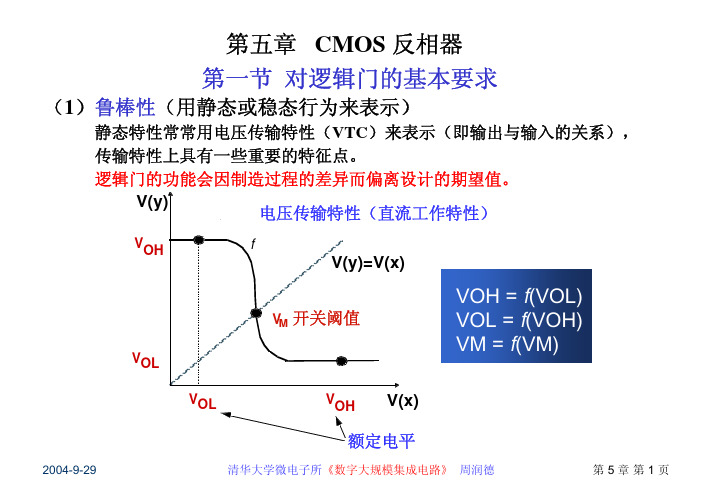

第五章 CMOS 反相器 第一节 对逻辑门的基本要求(1)鲁棒性(用静态或稳态行为来表示)静态特性常常用电压传输特性(VTC)来表示(即输出与输入的关系), 传输特性上具有一些重要的特征点。

逻辑门的功能会因制造过程的差异而偏离设计的期望值。

V(y) 电压传输特性(直流工作特性)VOH fV(y)=V(x)VM开关阈值VOL VOL VOHVOH = f(VOL) VOL = f(VOH) VM = f(VM)V(x)额定电平2004-9-29 清华大学微电子所《数字大规模集成电路》 周润德 第5章第1页(2)噪声容限:芯片内外的噪声会使电路的响应偏离设计的期望值 (电感、电容耦合,电源与地线的噪声)。

一个门对于噪声的敏感程度由噪声容限表示。

可靠性―数字集成电路中的噪声v(t) i(t)V DD电感耦合电容耦合电源线与地线噪声噪声来源: (1)串扰 (2)电源与地线噪声 (3)干扰 (4)失调 应当区分: (1)固定噪声源 (2)比例噪声源 浮空节点比由低阻抗电压源驱动的节点更易受干扰 设计时总的噪声容限分配给所预见的噪声源2004-9-29 清华大学微电子所《数字大规模集成电路》 周润德 第5章第2页噪声容限(Noise Margin)V“1” V OH V IHout OH 斜率 = -1V不确定区 斜率 = -1ILV “0” VVOLOL V IL V IH V in2004-9-29清华大学微电子所《数字大规模集成电路》 周润德第5章第3页噪声容限定义"1"噪声容限(Noise Margin) 容许噪声的限度V IH高电平 噪声容限VOHNM H未定义区 低电平 噪声容限V OL "0" NM L V IL抗噪声能力(Noise Immunity) 抑止噪声的能力门输出门输入2004-9-29清华大学微电子所《数字大规模集成电路》 周润德第5章第4页理想逻辑门V outg=∞Ri = ∞ Ro = 0 Fanout = ∞ NMH = NML = VDD/2V in2004-9-29清华大学微电子所《数字大规模集成电路》 周润德第5章第5页早期的逻辑门5.0 4.0 3.0 2.0 VM 1.0 NM H NM L0.01.02.03.0 V in (V)4.05.02004-9-29清华大学微电子所《数字大规模集成电路》 周润德第5章第6页(3) “再生”特性:逻辑门的“再生”特性使被干扰的信号能恢复到名义 的逻辑电平。

TannerPro13.0使用说明

TannerPro13.0使⽤说明专⽤集成电路设计Tanner Pro⼯具使⽤介绍Tanner Pro⼯具使⽤介绍Tanner Tools Pro是⼀套集成电路设计软件,包含以下⼏种⼯具:S-Edit(编辑电路图)T-Spice(电路分析与模拟)W-Edit(显⽰T-Spice模拟结果)L-Edit(编辑布局图,⾃动布局布线,DRC,电路转化)LVS(版图和电路图对⽐)Tanner数字ASIC设计流程图最后将L-Edit设计好的版图输出成GDSII⽂件,交由⼯⼚制作掩膜版S-Edit13.0界⾯S-Edit范例-lights 打开S-Edit程序打开⽰范设计Lights.tanner寻找引⽤到的单元:Cell-Open View。

打开Core单元。

S-Edit范例-lights切换模式:电路模式、符号模式。

View-Cell ViewS-Edit范例-lights可以继续在Core模块中继续寻找更低⼀级的模块,直⾄到MOS晶体管。

⽂件输出:S-Edit绘制的电路图,可以输出成⼏种形式的⽂件,有EDIF⽂件(*.edf,*.edn,*.eds)、SPICE⽂件(*.sp)、TPR⽂件(*.tpr)、VHDL、Verilog⽂件等。

⽂件输⼊,S-Edit可以输⼊EDIF、SPICE、Verilog等⽂件。

S-Edit范例-Buses and ArraysSimple BusesS-Edit范例-Buses and ArraysSplitting BusesT-Spice范例T-Spice是电路仿真与分析的⼯具,⽂件内容除了有元件与节点的描述外,还必须加上其他的设定。

有包含⽂件(include file)、端点电压源设置、分析设定、输出设置。

模拟结果可以通过W-Edit观看。

以invert_tran.cir为例进⾏⽰范。

L-Edit范例L-Edit是⼀个布局图的编辑环境。

以lights.tdb为例进⾏L-Edit基本结构的介绍。

硅栅P阱CMOS反相器版图设计举例刻NMOS管S

n+区/保护带

P+区保护环

版图分解: 1. 刻P阱 2. 刻P+区/保护环 3. 刻n+区/保护带 4. 刻栅、预刻接触孔 5. 刻接触孔 6. 刻Al 7. 刻纯化孔

图2 铝栅CMOS反相器版图示意图

版图分解: 1. 刻P阱 2. 刻P+区/环 3. 刻n+区 4. 刻栅、预刻接触孔 5. 刻接触孔 6. 刻Al 7. 刻纯化孔

3

版图分解: 1. 刻P阱 2. 刻P+区/环 3. 刻n+区 4. 刻栅、预刻接触孔 5. 刻接触孔 6. 刻Al 7. 刻纯化孔

4

4) 硅栅MOS版图举例 E/E NMOS反相器 刻有源区 刻多晶硅栅 刻NMOS管S、D 刻接触孔 反刻Al

图5 E/E NMOS反相器版图示意图

5. 刻NMOS管 S、 D T1 W/L=1/1

Poly Diff Al con

Vdd

P阱

Vi

Vo

6. 刻接触孔 7. 反刻Al (W/L)p=3(W/L)n

Vss

1. 刻P阱

2. 刻有源区

3. 刻多晶硅栅

4. 刻PMOS管S、D

5. 刻NMOS管S、D

6. 刻接触孔

VDD

7. 反刻Al

VDD

E/D NMOS 反相器

刻有源区 刻耗尽注入区 刻多晶硅栅 刻NMOS管S、D 刻接触孔 反刻Al

图6 E/D NMOS 反相器版图

制备耗尽型MOS管

在MOS集成电路中,有些设计需要 采用耗尽型MOS管,这样在MOS工艺过 程中必须加一块光刻掩膜版,其目的是 使非耗尽型MOS管部分的光刻胶不易被 刻蚀,然后通过离子注入和退火、再分 布工艺,改变耗尽型MOS管区有源区的 表面浓度,使MOS管不需要栅电压就可 以开启工作。 然后采用干氧-湿氧-干氧的方法 进行场氧制备,其目的是使除有源区部 分之外的硅表面生长一层较厚的SiO2层, 防止寄生MOS管的形成。

CMOS集成电路版图 Tanner L-Edit设计入门

铝条间距最小10um Metal1 to Metal1 Spacing=10um

铝条对铝引线孔最小覆盖2.5um Metal1 surround Contact=2.5um

引线孔距扩散区最小距离5um Metal1 Contact to P-Select spacing=5um Metal1 Contact to N-Select spacing=5um

4、编辑组件,进行环境设定:选择setup—design 命令对单位格点等进行设定;

2020/2/11

5、选取图层:

2020/2/11

6、选择绘图形状:

2020/2/11

7、设计规则检查:

2020/2/11

设计规则检查

2020/2/11

2020/2/11

8、检查错误:选择file—open命令打开错误记 录文件cell0.drc进行查看错误,利用tools— clear error layer命令可清除错误符号;

9、设计规则检查:版图必须配合设计规 则进行绘制,利用DRC可以确保流程效 率。

2020/2/11

10、绘制P Select图层:定义P型掺杂的 范围, P Select图层和Active交集处定 义为pdiff,设计里有源区后,需要加上 N select 或P select与Active图层重叠;

双极集成电路版图设计

2020/2/11

MOS集成电路版图设计

2020/2/11

电压比较器

2020/2/11

运算放大器

2020/2/11

2020/2/11

2020/2/11

版图设计流程

Tanner的CMOS标准反相器交直流特性分析

CMO标准反相器交直流特性分析--- 基于Tanner Pro 的实现2012年12月一Tanner Pro软件介绍Tanner Pro 是一套集成电路设计软件,包括S-Edit, T-Spice, W-Edit,L-Edit与LVS,各软件的主要功能整理如表1.1所示。

表各软件的主要功能Tanner Pro的设计流程可以用图1.1来表示。

将要设计的电路先以S-Edit 编辑出电路图,再将该电路图输出成SPICE文件。

接着利用T-Spice将电路图模拟并输出成SPICE文件,如果模拟结果有错误,N回S-Edit检查电路图,如果T-Spice模拟结果无误,则以L-Edit进行布局图设计。

用L-Edit进行布局图设计后要以DRC功能做设计规则检查,若违反设计规则,再将布局图进行修改直到设计规则检查无误为止。

将验证过的布局图转化成SPICE文件,再利用T-Spice模拟,若有错误,再回到L-Edit修改布局图。

最后利用LVS将电路图输出的SPICE 文件与布局图转化的SPICE文件进行对比,若对比结果不相等,则回去修正L-Edit或S-Edit的图。

直到验证无误后,将L-Edit设计好的布局图输出成GDSII文件类型,再交由工厂去制作。

笔者此次论文为CMOSS准反相器的交直流特性分析,主要使用S-Edit和T-Spice分别进行电路编辑与分析仿真。

下面先简单介绍下这两个软件的使用。

S-Edit 提供一个电路图编辑的环境,它主要是通过各种模块如Lights模块、Core 模块、IPAD 模块、OPAD莫块等,每一个模块可以是一个电路或组件符号,模块的设计又可以引用其他模块,而形成层次式的结构。

所以S-Edit十分方便,具有极大的用户便利性。

T-Spice是电路模拟与分析的工具,它能方便的对文件设定,使用某种制程的参数进行模拟。

也可以对组件节点与组件参数值进行设定,还可以设定模拟时所用的电压值,同时能设定模拟方式为瞬时分析或其它分析方式,并输出模拟结果。

CMOS反向器版图设计实验报告

上海电力学院VLSI原理和设计报告题目:CMOS反向器的版图设计院系:电子与信息工程学院专业:电子科学与技术年级:姓名:学号:指导老师:刘伟景一、实验目的1、熟悉virtuoso editing、LSW设计窗口及操作2、熟练掌握设计快捷键的操作3、培养CMOS数字集成电路设计中减小芯片面积的设计技巧和方法的能力4、认识版图数据文件二、实验设备硬件环境:英特尔I5 PC机、SUN BLADE工作站软件环境:solaris操作系统、Cadence集成电路设计软件三、实验内容实验一UNIX上机实验(1)实验内容及步骤:1.在主目录/home/student/stu231 或/home/student/stu231创建自己的子目录(姓名全拼)。

注意:以后的新建文件和目录全部都在子目录中进行。

2.对根目录进行详细列表并将结果存入自己的子目录下新文件lsl.log中,并用cat命令显示该文件内容,再用file命令查看该文件类型。

3.用cat命令将自己建立的lsl.log文件扩展3次形成一个新文件ls2.log,并用more命令显示该文件内容,统计该文件的行数,并将此信息追加到文件末尾。

4.对自己的子目录打包后压缩,查看形成的新文件信息后,在进行解压和解包。

5.为自己创建一个新的目录new,将自己原目录下的文件拷贝到新目录new中。

6.删除新目录及其下的所有文件。

7.用定向的方法把who命令形成的结果保存到文件who.log中,并查看该文件内容。

8.用chmod命令修改文件who.log的可执行权限使其成为可执行文件,并运行该文件查看结果。

9.进入VI编辑器再次修改文件who.log的内容,其内容为对目录的详细列表,并使改变who.log的可执行权限,使得其权限形式为“r w x r- x r - -”。

并执行之。

实验二:UNIX上机实习(续)10.进入VI编辑器修改lsl.log文件内容,利用全局替换命令将“root”修改为“stu”。

tanner设计规则

Tanner版图流程举例(反相器)集成电路设计近年来发展相当迅速,许多设计需要借助计算机辅助设计软件。

作为将来从事集成电路设计的工作人员,至少需要对版图有所了解,但是许多软件(如cadence)实在工作站上执行的,不利于初学者。

L-Edit软件是基于PC上的设计工具,简单易学,操作方便,通过学习,掌握版图的设计流程。

Tanner Pro简介:Tanner Pro是一套集成电路设计软件,包括S-EDIT,T-SPICE,W-EDIT,L-EDIT,与LVS ,他们的主要功能分别如下:1、S-Edit:编辑电路图2、T-Spice:电路分析与模拟3、W-Edit:显示T-Spice模拟结果4、L-Edit:编辑布局图、自动配置与绕线、设计规则检查、截面观察、电路转化5、LVS:电路图与布局结果对比设计参数的设置Setup>Design •该对话框共有六页,分别是:Technology(工艺参数)、Grid(网格参数)、Selection(选择参数)、Drawing(绘图参数)、Curves(曲线参数)、Xref files(外部交叉引用参数)•网格分为显示网格、鼠标网格(跳跃、平滑)、定位器网格设计规则的作用•设计规则规定了生产中可以接受的几何尺寸的要求和达到的电学性能。

•对设计和制造双方来说,设计规则既是工艺加工应该达到的规范,也是设计必循遵循的原则•设计规则表示了成品率和性能的最佳折衷设计规则的设置(一)、设计的类型•Minimum Width•Exact Width•Not Exist•Spacing•Surround•Overlap•Extension•Density(1)Minimum Width 该层上所有object在任意方向上的宽度(2) Exact width 该层上所有object在特定方向上的准确宽度(3)Not Exist在指定的层上,所有object都不能存在.这是唯一不含距离的规则(4)Spacing在指定的层上或者在指定的两层之间的object的最小间距(5)Surround 一个层上的物体,在每个方向上,被另一层上的物体至少要环绕x各单位(6)Overlap 一个层上的物体必须与另一个层上的物体交叠的最小尺寸。

精品文档-集成电路版图设计与TannerEDA工具的使用(王颖)-第6章

第6章 使用L-Edit设计版图实例

6.1 使用版图编辑器画PMOS晶体管的版图 6.2 使用版图编辑器画NMOS晶体管的版图 6.3 使用版图编辑器画反相器的版图 6.4 使用版图编辑器画并联晶体管的版图 6.5 使用版图编辑器画串联晶体管的版图 习题

第6章 使用L-Edit设计版图实例

后点击鼠标左键,然后点击Generate Cross-Section对话框

中的确认键(OK),最后得到的版图与横截面窗口如图6.13所

示。

第6章 使用L-Edit设计版图实例

图6.12 产生横截面观察对话框

பைடு நூலகம்

第6章 使用L-Edit设计版图实例

图6.13 版图与横截面图

第6章 使用L-Edit设计版图实例

第6章 使用L-Edit设计版图实例

图6.6 绘制P Select层

第6章 使用L-Edit设计版图实例

③ 画Active层。在DRC文件中规定有源区的最小宽度 (Active Minimum Width)为0.35微米,PMOS晶体管的有源区 到N阱之间的最小距离(PMOS Source/Drain spacing to Well Edge)为0.75微米。在选择了有源区绘图层和方框绘图工具后, 在版图区域中画一个高0.55微米、宽1.55微米的有源区,即 PMOS晶体管的沟道宽度为0.55微米,如图6.7所示。

第6章 使用L-Edit设计版图实例

第6章 使用L-Edit设计版图实例

图6.11 DRC相关窗口

第6章 使用L-Edit设计版图实例

(7) 进行晶体管的横截面观察。Tanner的版图编辑器配

有版图横截面观察功能,利用此功能可以观察所画版图与实际

专用集成模拟电路(上机步骤及考试复习)

复习:一.基本概念—第1、2、3、4、5章。

1)摩尔定理2)设计规则;特征尺寸3)ASIC;IC4)氧化;光刻;扩散;淀积5)深亚微米集成电路6)CIF格式;GDSП格式;7)DRC; ERC; LPE; LVS;8)PN 结9)方块电阻10)噪声容限;高电平噪声容限;低电平噪声容限11)CMOS反向器的功耗;静态功耗;动态功耗;功耗周期延迟积12)你自己认为的Digital/Analog/SOC IC设计过程二、集成电路工艺按制作工艺主要分为哪几大类,并简述各工艺的主要特点及应用范围三、画出双极晶体管(NPN、横向PNP及纵向PNP)的剖面图、版图及给出简化的标准双极工艺流程四、版图检查与验证主要包括什么?五、简述版图设计规则包括了那些内容?六、选择工艺的主要依据是什么?七、集成电路中常用的电阻类型及其特点、;电容类型;八、单管MOS开关及CMOS传输门的特点;并画出CMOS传输门的电路结构。

九、画出CMOS反相器的剖面图和版图。

十、用你自己的话解释微电子学、集成电路、A S I C的概念,并列举出你见到的、想到的不同类型的集成电路及其主要作用十一、集成电路设计的一般流程十二、简述反向器的上升时间、下降时间、延迟时间。

十三、采用传输门构成D触发器的电路结构十四、恒流源的电路结构及特点十五、集成运算放大器电路结构及基本的跨导运算放大器电路十六、简述带隙基准电压源的实现原理,并给出一种简化的CMOS 实现结构图。

十七、上机作业((30分)必做题目:(1)自己设计一个简单的数字电路,如D触发器或全加器。

要求用S-edit画图、Ledit/SPR自动布局布线、T-spice功能仿真。

(2)手工画出CMOS结构Nand2或Nor2版图选做题目:(1)对一个模拟电路如差分对完成S-edit画图、T-spice 功能仿真、Ledit手工画出版图。

(3)必须交上机试验报告(也为一道考题),可以是手写的。

包括详细设计过程、电路图、仿真波形示意图及工作原理和结果分析。

反相器链电路图和版图基于TannerPro软件的设计与仿真

集成电路课程设计报告基于Tanner Pro软件的反相器链设计与仿真院系:材料与光电物理学院专业:微电子学三班学号:2008700531姓名:张靖指导教师:唐明华教授报告提交日期:2011 年9 月目录摘要 (1)关键词 (1)1 引言 (2)1.1 本课题的主要目的 (2)1.2 近几年来国内外研究现状 (2)1.3 版图设计流程与方法 (3)2 关于Tanner Pro的设计和仿真 (5)2.1 Tanner Pro软件简介 (5)2.2 Tanner Pro 使用方法 (5)2.3 利用Tanner Pro进行电路图和版图设计的具体过程 (5)3 反相器简介 (7)3.1反相器功能概述 (7)3.2反相器电路图及版图概述 (7)4 反相器电路图与版图的整体设计 (9)4.1反相器电路图和符号的设计与仿真 (9)4.1.1反相器的电路图设计 (9)4.1.2反相器的符号设计 (11)4.1.3反相器的瞬时分析 (13)4.1.4反相器的直流分析 (17)4.2 反相器的版图设计 (21)4.2.1 PMOS的版图设计 (22)4.2.2 NMOS的版图设计 (24)4.2.3反相器的版图设计 (25)4.3 反相器版图与电路图的对比 (28)4.4 反相器级比值项目分析 (30)5 结论 (36)6 体会与心得 (37)参考文献 (38)致谢 (39)基于Tanner Pro软件的反相器链设计与仿真摘要:首先,本文对Tanner Pro中的5种软件进行了简单的介绍,包括S-Edit、L-Edit、T-Spice、W-Edit和LVS,然后介绍了常见的反相器和反相器链,并对它们的基本原理和电路结构作了简要分析。

接着在这些基础上,本文根据自上向下(top-down)设计思想,应用Tanner Pro软件依次设计和仿真了NMOS、PMOS、INV等电路模块,然后设计出整体电路并对其进行了对比与仿真,给出了所需的电路图符号、电路图、版图以及仿真结果等。

CMOS反相器版图流程

7. 通孔——两层金属连线之间连接的端子

10

CMOS反相器版图流程(8)

Metal 2

8. 金属线2——做金属连线,封闭图形处保留铝

11

inverter: Schematic: Layout:

input

VDD m1 m2 GND VDD

output

GND

m2

m1

12

须解释的问题:

1. 有源区和场区是互补的,晶体管做在有源 区处,金属和多晶连线多做在场区上。 2. 有源区和P+,N+注入区的关系:有源区即 无场氧化层,在这区域中可做N型和P型各种 晶体管,此区一次形成。 3. 至于以后何处是NMOS晶体管,何处是 PMOS晶体管,要由P+注入区和N+注入区那 次光刻决定。

CMOS反相器 版图流程

1

CMOS反相器版图流程(1)

N well

P well

1. 阱——做N阱和P阱封闭图形, 窗口注入形成P管和N管的衬底

2

CMOS反相器版图流程(2)

N diffusion

2. 有源区——做晶体管的区域(G、D、S、B区), 封闭图形处是氮化硅掩蔽层,该处不会长场氧化层

3

CMOS反相器版图流程(2)

wellcmos阱做n阱和p阱封闭图形窗口注入形成p管和n管的衬底diffusioncmos有源区做晶体管的区域gdsb区封闭图形处是氮化硅掩蔽层该处不会长场氧化层diffusioncmos有源区做晶体管的区域gdsb区封闭图形处是氮化硅掩蔽层该处不会长场氧化层polygatecmos多晶硅做硅栅和多晶硅连线

13

6

CMOS反相器版图流程(4)

P+ implant

CMOS集成电路版图TannerL-Edit设计入门

2019/10/19

2019/10/19

2019/10/19

2019/10/19

设计参数的设Βιβλιοθήκη Setup>Design 该对话框共有六页,分别是: Technology(工艺参数)、Grid(网格参数)、 Selection(选择参数)、Drawing(绘图参数)、 Curves(曲线参数)、Xref files(外部交叉引 用参数)

2019/10/19

(7)Extension

一个层上的物体必 须超过另一个层上 的物体的边界的最 小尺寸。当:距离 超过指定数字、 只有一边刚好重合, 其他都在物体之外、 被完全surround 的时候,不算是违 背规则

2019/10/19

(8)Density

2019/10/19

The density rule finds and flags objects on the derived density layer specified in Layer1.

(一)、设计的类型

Minimum Width Exact Width Not Exist Spacing Surround Overlap Extension Density

2019/10/19

(1)Minimum Width

2019/10/19

该层上所有object在任意方向上的宽度

The layer specified must be a Density type derived layer. Violations to the rule include any polygons output to a density layer. 按照规则,查找layer1下拉选框中制定的密度推导层 中的对象,并对其加以标志。Layer1下拉选框中制定 的图层必须是密度类型的推导层。如有多变性输出到 密度层,就构成违规。

一种CMOS伪随机序列信号发生器的版图设计

一种CMOS伪随机序列信号发生器的版图设计保慧琴【摘要】集成电路版图设计是实现集成电路制造必不可少的设计环节,版图设计的优劣直接关系到芯片的工作性能和制造成本.采用CMOS 2μm的λ设计规则,利用Tanner Pro软件设计了一种CMOS伪随机序列信号发生器.Tanner Pro软件是一套集成电路设计软件,利用S-edit完成伪随机序列信号发生器的原理图设计,利用L-edit完成伪随机序列信号发生器的版图设计,并通过T-spice软件进行仿真,仿真结果表明,所产生的伪随机序列信号循环长度为6,伪随机序列信号由D触发器的初始状态决定.%IC layout design is the indispensable design link of integrated circuit manufacturing, the quality of layout design are directly related to the working performance and manufacturing cost of chip. By using CMOS 2μm λ design rules and Tanner Pro software, a CMOS Pseudo-random sequence signal generator is designed. Tanner Pro software is a set of integrated circuit design software, using S-edit to complete the schematic diagram design, and using L-edit to complete the Layout design. By the T-spice software , simulation is performed and its results show that the cycle length of this Pseudo-random sequence signal generator is six, and the sequence signal is determined by the initial state of D flip-flops.【期刊名称】《微处理机》【年(卷),期】2017(038)004【总页数】4页(P7-10)【关键词】集成电路;版图;伪随机序列;版图设计规则;触发器;循环长度【作者】保慧琴【作者单位】西北工业大学明德学院,陕西西安,710124【正文语种】中文【中图分类】TN79伪随机序列良好的随机性和接近于白噪声的相关函数,使其易于从信号或干扰中分离出来,广泛应用于密码学、通信、雷达、导航等多个领域,常用的产生伪随机序列信号的电路是线性反馈移位寄存器,所产生的序列只与寄存器的初始状态和反馈方式有关。

二输入与非门、或非门版图设计

课程名称Course 集成电路设计技术项目名称Item二输入与非门、或非门版图设计与非门电路的版图:.spc文件(瞬时分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\yufeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:03.include H:\ml2_125.mdVPower VDD GND 5va A GND PULSE (0 5 0 5n 5n 100n 200n)vb B GND PULSE (0 5 0 5n 5n 50n 100n).tran 1n 400n.print tran v(A) v(B) v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6.5)* 4 = F (42.5,6.5)* 6 = GND (25,-22)M1 VDD B F VDD PMOS L=2u W=9u AD=99p PD=58u AS=54p PS=30u* M1 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M2 F A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=99p PS=58u* M2 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M3 F B 5 GND NMOS L=2u W=9.5u AD=52.25p PD=30u AS=57p PS=31u * M3 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)M4 5 A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=52.25p PS=30u * M4 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END与非门电路仿真波形图(瞬时分析):.spc文件(直流分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\yufeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:03.include H:\ml2_125.mdVPower VDD GND 5va A GND 5vb B GND 5.dc va 0 5 0.02 vb 0 5 0.02.print dc v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6.5)* 4 = F (42.5,6.5)* 6 = GND (25,-22)M1 VDD B F VDD PMOS L=2u W=9u AD=99p PD=58u AS=54p PS=30u* M1 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M2 F A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=99p PS=58u* M2 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M3 F B 5 GND NMOS L=2u W=9.5u AD=52.25p PD=30u AS=57p PS=31u * M3 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)M4 5 A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=52.25p PS=30u * M4 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END与非门电路仿真波形图(直流分析):或非门电路的版图:.spc文件(瞬时分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\huofeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:04.include H:\CMOS\ml2_125.mdVPower VDD GND 5va A GND PULSE (0 5 0 5n 5n 100n 200n)vb B GND PULSE (0 5 0 5n 5n 50n 100n).tran 1n 400n.print tran v(A) v(B) v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <Pad Comment>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6)* 4 = F (42.5,6.5)* 5 = GND (25,-22)M1 6 A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=49.5p PS=29u* M1 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M2 F B 6 VDD PMOS L=2u W=9u AD=49.5p PD=29u AS=54p PS=30u* M2 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M3 F A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=104.5p PS=60u * M3 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)M4 GND B F GND NMOS L=2u W=9.5u AD=104.5p PD=60u AS=57p PS=31u * M4 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END或非门电路仿真波形图(瞬时分析):.spc文件(直流分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\huofeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:04.include H:\CMOS\ml2_125.mdVPower VDD GND 5va A GND 5vb B GND 5.dc va 0 5 0.02 vb 0 5 0.02.print dc v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <Pad Comment>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6)* 4 = F (42.5,6.5)* 5 = GND (25,-22)M1 6 A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=49.5p PS=29u* M1 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M2 F B 6 VDD PMOS L=2u W=9u AD=49.5p PD=29u AS=54p PS=30u* M2 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M3 F A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=104.5p PS=60u * M3 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)M4 GND B F GND NMOS L=2u W=9.5u AD=104.5p PD=60u AS=57p PS=31u * M4 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END或非门电路仿真波形图(直流分析):内容(方法、步骤、要求或考核标准及所需工具、设备等)一、实训设备与工具1.PVI计算机一台;2.Tanner Pro集成电路设计软件二、实训方法、步骤与要求1.二输入与非门电路的线路结构2.二输入或非门电路的线路结构3.CMOS倒相器电路的版图4.根据与非门、或非门线路结构,在一个工程中,重新新建两个新CELL,分别对应与非门和或非门版图,并设计与非门、或非版图结构。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

组件PMOS:组件CONTACTN:*.spc文件(瞬时分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: H:\cmos\cmos, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 06/29/2011 - 00:18.include H:\ml2_125.mdVPower VDD GND 5va A GND PULSE (0 5 0 1n 1n 50n 100n).tran 1n 400n.print tran v(A) v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (21.5,66)* 2 = F (32,36)* 3 = A (18,35.5)* 4 = GND (18.5,6)M1 F A VDD VDD PMOS L=2u W=10u AD=55p PD=31u AS=55p PS=31u* M1 DRAIN GATE SOURCE BULK (29 47 31 57)M2 F A GND GND NMOS L=2u W=5u AD=27.5p PD=21u AS=27.5p PS=21u* M2 DRAIN GATE SOURCE BULK (29 10 31 15)* Total Nodes: 4* Total Elements: 2* Extract Elapsed Time: 1 seconds.END瞬时分析仿真波形图:*.spc文件(直流分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: H:\cmos\cmos, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 06/29/2011 - 00:18.include H:\ml2_125.mdVPower VDD GND 5va A GND 1.dc va 0 5 0.02.print dc v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (21.5,66)* 2 = F (32,36)* 3 = A (18,35.5)* 4 = GND (18.5,6)M1 F A VDD VDD PMOS L=2u W=10u AD=55p PD=31u AS=55p PS=31u* M1 DRAIN GATE SOURCE BULK (29 47 31 57)M2 F A GND GND NMOS L=2u W=5u AD=27.5p PD=21u AS=27.5p PS=21u * M2 DRAIN GATE SOURCE BULK (29 10 31 15)* Total Nodes: 4* Total Elements: 2* Extract Elapsed Time: 1 seconds.END直流分析仿真波形图:课程名称Course 集成电路设计技术项目名称ItemCMOS倒相器的版图设计与仿真目的Objective 1、掌握在L-EDIT中进行IC版图设计的方法与规则;2、掌握CMOS倒相器版图设计时,所涉及各层的物理意义;3、掌握CMOS倒相器中各MOS管尺寸的选取以及按设计规则决定的其他各层的尺寸;4、掌握CMOS倒相器版图设计时各层之间的嵌套关系;5、掌握将版图设计成果转化为T-Spice文件(*.spc)的方法;6、掌握利用T-SPICE和版图*.spc文件进行电路直流和瞬时仿真的方法与步骤;7、学习对电路时序图的理解。

内容(方法、步骤、要求或考核标准及所需工具、设备等)一、实训设备与工具1.PVI计算机一台;2.Tanner Pro集成电路设计软件二、实训方法、步骤与要求1.在进行版图设计前,应先将屏幕显示改为256色2.利用L-EDIT设计CMOS倒相器1)进入L-EDIT程序,打开COMPON文件2)取代设定3)新建组件CELL,命名为INV4)组件复制:打开组件NMOS,CELL COPY,复制INV中打开组件PMOS,CELL COPY,复制INV中打开组件CONTACTP,CELL COPY,复制INV中打开组件CONTACTN,CELL COPY,复制INV中5)连接NMOS管与PMOS管的栅极6)连接NMOS管与PMOS管的漏极7)绘制电源线8)标出Vdd和Gnd节点9)连接NMOS管的源与Gnd,PMOS管的源与Vdd10) 加入输入、输出端口11)进行设计规则检查:TOOLS DRC,如有错误,应根据规则进行修改12)截面观察:TOOLS CROSS-SECTION13)观察CMOS倒相器版图设计成果,可单独显示某一图层,或某些特定图层14)将反相器布局图转化成T-SPICE文件选取TOOL EXTRACTGENERAL选项:EXTRACT DEFINITION FILE项为C:\TANNER\SPR\EXAMPLE1\lights.extSPICE EXTRACT OUTPUT FILE项为D:\inv.spcOUTPUT选项:WRITE NODE NAMES选中WRITE LAYER CAPACITANCE AND RESITANCE WARNING选中WRITE VERBOSE SPICE STATEMENTS选中WRITE EMPTY SUBCIRCUIT DEFINITIONS选中WRITE .END STATEMENT选中在SPICE INCLUDE STATEMENT框中加入:.include c:\Tanner\models\ml2_125.md3.T-SPICE模拟采用前面有关线路图设计与仿真的方法,在得到的inv.spc文件中,插入相应的命令,进行CMOS倒相器版图的瞬时和直流模拟。

下图为一CMOS倒相器的版图,可作为参考。

4.版图设计常用规则1)有源区 N区 5umP区 10um2)多晶硅栅宽度(即MOS管沟道长度) 2um3)N-Select to Active 2umP-Select to Active 2um4)Poly to Active Spacing 1umPoly to Poly Spacing 2umPoly Contact Exact Size 2umPoly Minimum Width 2um5)Active to Active Spacing 3umActive Contact to Gate Spacing 2um 6)Via Exact Size 2umMetal1 Overlap of Via 1umVia to Poly Contact Spacing 2umVia to Poly Spacing 2um7)Metal1 Overlap of Active-contact 1umSource/Drain Active to Well Edge 5umWell contact to Well Edge 3um5.版图仿真所需程序1)将反相器版图成果转化为T-SPICE文件Tool ExtractGeneral选项Extract Definition File:c:\Tanner\spr\morbn20.extSpice Extract Output File:d:\layout\inv.spcOutput选项Comment:√ Write Node name٠ Names√ Write Verbose Spice Statement√ Label All DevicesPlace Device Labels on METEL1Spice Include Statement. Include c:\tanner\models\ml2_125.md 2)将得到的*.spc文件在T-SPICE中打开3)按照原理图得到的*.sp文件的仿真方法,即插入电压源设置指令(CONSTANT、PULSE)插入分析指令(瞬时和直流)插入输出信号指令再进行仿真。