FPGA高速串行收发器,GTP,GTX

Xilinx FPGA 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_#用户IO引脚XX代表某个Bank内唯一得一对引脚,Y=[P|N]代表对上升沿还就是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_#多功能引脚ZZZ代表在用户IO得基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚.D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0就是数据得最低位,在Bit—serial模式下,DIN就是信号数据得输入;在SPI模式下,MISO就是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1就是SPI总线得第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1与D2就是数据总线得低位;在SPI*4模式下,MISO2与MISO3就是SPI总线得MSBs.An:O,A[25:0]为BPI模式得地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式得状态输出引脚。

SUSPEND就是一个专用引脚,AW A KE就是一个多功能引脚。

除非SUSPEND模式被使能,AW AKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B就是一个低电平有效得片选信号;在SPI*2或者SPI*4得模式下,MISO0就是SPI总线得第一位数据。

FCS_B:O,BPI flash 得片选信号.FOE_B:O,BPI flash得输出使能信号FWE_B:O,BPIflash 得写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

Xilinx FPGA 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank 号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

fpga间gtx原理

fpga间gtx原理FPGA是现代计算机系统中一种重要的可编程逻辑设备,而GTX则是一种高速串行收发器。

本文将探讨FPGA与GTX之间的原理和关联。

我们来了解一下FPGA的基本概念。

FPGA全称为Field-Programmable Gate Array,即现场可编程门阵列。

它是一种可编程逻辑器件,可以在制造完成后进行现场编程。

FPGA内部由大量的逻辑单元和可编程的连线网络组成,可以实现各种数字电路的功能。

GTX是NVIDIA公司开发的高速串行收发器。

它是一种用于高速数据传输的接口技术,可以实现数据在设备之间的快速传输。

GTX被广泛应用于高性能计算、数据中心和通信领域。

FPGA与GTX之间存在紧密的关系,主要体现在以下几个方面。

FPGA可以通过GTX接口与其他设备进行高速数据通信。

由于GTX 采用了串行传输方式,可以在保证数据传输速率的同时,减少传输线的数量,提高系统的可靠性和稳定性。

FPGA通过配置GTX接口,可以与其他设备进行高速数据交换,满足实时数据处理和传输的需求。

FPGA内部的逻辑单元可以通过GTX接口与外部设备进行通信。

FPGA中的逻辑单元可以实现各种功能,如数据处理、算法运算等。

通过配置GTX接口,FPGA可以将处理结果传输给外部设备,或者接收外部设备的数据输入,实现与外部设备的交互。

FPGA还可以通过GTX接口与其他FPGA进行通信。

在某些应用场景下,需要多个FPGA之间进行数据交换和协同计算。

通过配置GTX接口,多个FPGA可以通过高速串行通信进行数据传输,实现分布式计算和并行处理。

需要注意的是,FPGA与GTX之间的通信需要遵循一定的协议。

GTX接口支持多种通信协议,如PCI Express、Ethernet等。

在设计FPGA与GTX接口时,需要根据具体的应用需求选择合适的通信协议,并进行相应的配置和调试。

总的来说,FPGA与GTX之间的原理是通过配置GTX接口实现高速数据通信和交互。

Xilinx_7_Series_GTX简介

GTX transceivers

QPLL和CPLL

适用范围: CPLL: 1.6Ghz-3.3Ghz QPLL: 5.9Ghz-12.5Ghz QPLL可以输出频率更高、 抖动更小的时钟,CPLL允 许对每个通道的时钟进行 灵活的配置。可以通过 SYSCLKSEL来选择使用 CPLL或者是QPLL,并且 支持动态切换。

GTX transceivers

主要内容

GTX简介 发送通道的结构

接收通道的结构

GTX的应用

GTX transceivers

GTX简介

发送通道的结构 接收通道的结构

GTX的应用

GTX transceivers

GTX是一种低功耗的吉比特收发器,配置灵活,功能强大,与FPGA内部其他逻 辑紧密联系,可用于实现多种高速串行接口(如PCIE、SATA等)。GTX发送和接收方向 均由PCS和PMA两部分组成。GTX还提供动态重配置接口,用于动态修改GTX的配置。 Group 8B/10B编解码 64B/66B编解码 Feature 内部数据宽度可以设置成2byte或4byte以支持不同的数据速率

② Near-End PMA Loopback

③ Far-End PMA Loopback ④ Far-End PCS Loopback

GTX transceivers

GTX简介

发送通道的结构 接收通道的结构

SATA应用中GTX时钟方案

GTX transceivers

Xilinx FPGA高速资源合理利用的一种思路

电子技术与软件工程Electronic Technology & Software Engineering网络通信技术Network Com m unication TechnologyXilinx F P G A高速资源合理利用的一种思路杨见1陈伟1许杰2陈少林2(1.四川九洲空管科技有限责任公司四川省绵阳市621000 2.空装驻綿阳地区某军事代表室四川省綿阳市621000 )摘要:本文主要结合实际工程案例,遵照X ilin x高速收发器使用规则,对如何充分利用其硬件资源进行高速应用设计,提出一种 相对于常规设计思路更为合理的方式。

关键词:FPG A;高速资源;X ilin x高速收发器随着CML(CurrentModeLogic)、CDR、8b l0b 编码/64b66b 编码技术、预加重/去加重、时钟补偿等技术的出现,能够极大地 减小时钟抖动、收发时钟频偏、信号衰减和线路噪声对接收性能的 影响,从而使高速串行传输方式得到极为广泛的应用,而其接口信 号线数量少、应用成本低等优点,更是让开发人员相比并行数据传 输接口而言,更愿意选择高速串行传输方式。

Xilinx FPGA集成了 可实现不同线速率的高速串行收发器硬核资源,开发人员只需要进 行简单的配置即可实现高速串行应用。

基于成本考虑,在工程应用 中,开发人员依然遵循通过调用尽量少的资源去完成足够多的功能 这一准则展开设计。

本文就针对这一点对Xilinx FPGA高速串行资 源的利用提出一种设计思路进行分析并验证。

1设计需求QUAD116搭建4条常规的10G高速链路与目标设备三通信,QUAD115搭建3条10G高速链路与目标设备二通信,以及一条 千兆网链路与目标设备一通信。

链路设计要求如图1所示。

2设计思路Xilinx 7系列G T X每四个Channel组合成一个QUAD,每个 Q UAD有两组参考时钟输入,一个QPLL,4个CPLL,CPLL输出 时钟频率最高3.125Ghz,通信链路线速率最高6.25Gbps,QPLL输出时钟频率则在5.93Ghz〜12.5G h z范围内。

GTX技术——精选推荐

GTX技术你应该知道点⾼速GTX技术eSATA接⼝只有⼏根线为什么那么快?连上⽹线显⽰的1Gbps是不是很令⼈兴奋!没错他们都⽤了⾼速GTX技术,GTX全称为Gigabit Transceiver即吉bit收发器,是为了满⾜现代数字处理技术和计算技术庞⼤数据的⾼速、实时的传输,⽬前主要应⽤在⽚间通信(两⽚FPGA之间,FPGA与DSP之间等)、板间通信(电脑主板与交换机,硬盘与主板等)等。

传统的并并⾏传输技术存在抗⼲扰能⼒低,同步能⼒差,传输速率低和信号质量差等问题。

GTX⽬前的线速度范围为1Gbps~12Gbps,有效负载范围为0.8Gbps~10Gbps,⽬前GTX已经应⽤于光纤通道(FC),PCI Express,RapidIO,串⾏ATA,千兆以太⽹,万兆以太⽹等,GTX技术已经充斥我们周围很久了,作为⼀个技术⼈员,你是不是该知道点关于⾼速GTX呢?。

本⽂引⽤地址:/article/246023.htm GTX线路实现 GTX收发器采⽤的是差分信号对数据进⾏传输,其中LVDS(Low Voltage Different Signal)和CML(Current Mode Logic)是常⽤的两种差分信号标准。

在普通单⽚机(如51单⽚机中)不包含差分接⼝,均是以地作为参考,差分信号时有两根⼏乎完全相同的线路来组成⼀对等值、反相信号,接收端通过⽐较两端电压差值来确定传输的是“0”还是“1”,如果正参考电压⽐负参考电压低,则信号为⾼;如果负参考⽐正参考电压⾼,则信号为低。

因为线路上受到的噪声⼲扰⼏乎完全相同,在计算差值时相减从⽽达到抵消的效果,这就使得差分信号抗⼲扰能⼒特别强,⾼速传输时不易出错。

如图1所⽰为差分信号传输模式。

图 1 差分传输 除了利⽤差分信号外,GTX采⽤⾃同步技术来解决时钟同步问题。

⽬前常⽤同步⽅式有系统同步,源同步和⾃同步。

三种同步⽅式的结构如图2所⽰。

系统同步利⽤⽚外的晶振进⾏同步,由于板间线路的长度不⼀致,以及⽚内延迟不⼀致,在时钟速度较⾼时可能存在较⼤误差。

Xilinx不同FPGA集成的GTx及性能

10 Gb Attachment Unit Interface (XAUI), Reduced Pin eXtended Attachment Unit Interface (RXAUI), 100 Gb Attachment Unit Interface (CAUI), 40 Gb Attachment Unit Interface (XLAUI); Common Packet Radio Interface (CPRI™)/Open Base StaTIon ; Architecture IniTIaTIve (OBSAI); OC-48/192; OTU-1, OTU-2, OTU-3, OTU-4; Serial RapidIO (SRIO); Serial Advanced Technology Attachment (SATA)/Serial Attached SCSI (SAS); Serial Digital Interface (SDI); SFF-8431 (SFP+)。 GTx 收发器采用的是差分信号对数据进行传输,其中 LVDS(Low Voltage Different Signal)和 CML(Current Mode Logic)是常用的两种差分信号标准。

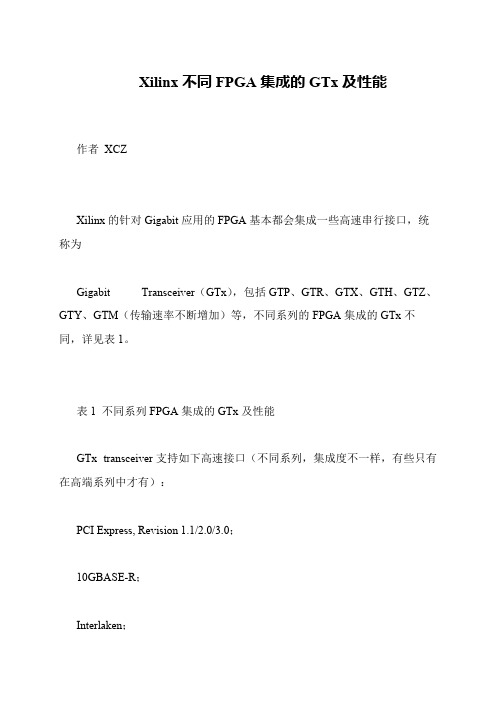

Xilinx 不同 FPGA 集成的 GTx 及性能

作者 XCZ

Xilinx 的针对 Gigabit 应用的 FPGA 基本都会集成一些高速串行接口,统

称为

Gigabit

Transceiver(GTx),包括 GTP、GTR、GTX、GTH、GTZ、

GTY、GTM(传输速率不断增加)等,不同系列的 FPGA 集成的 GTx 不

同,详见表 1。

表 1 不同系列 FPGA 集成的 GTx 及性能

vivado中各个资源模块的意思

vivado中各个资源模块的意思Vivado是Xilinx公司推出的一款集成设计环境,广泛应用于数字信号处理、数字逻辑设计等领域。

在使用Vivado进行FPGA设计时,了解各个资源模块的含义对于高效利用FPGA内部资源具有重要意义。

本文将详细介绍Vivado中各个资源模块的意思,帮助您更好地进行FPGA设计。

一、逻辑资源模块1.LUT(查找表):LUT是FPGA中基本的逻辑资源,可以用来实现组合逻辑或时序逻辑。

在Vivado中,LUT可以配置为不同大小的查找表,如6输入LUT、5输入LUT等。

2.FF(触发器):触发器是实现时序逻辑的基本单元。

在Vivado中,触发器可以配置为D触发器、T触发器等。

3.Carry Chain(进位链):进位链用于实现算术逻辑单元(ALU)中的加法器、减法器等。

在Vivado中,进位链可以提高运算速度和资源利用率。

二、存储资源模块1.Block RAM(块RAM):块RAM是FPGA中的存储资源,可用于实现数据存储、缓存等功能。

Vivado支持不同大小的块RAM配置,如18K、36K 等。

2.Distributed RAM(分布式RAM):分布式RAM是一种较小的存储资源,可用于实现小型缓存、寄存器等功能。

与块RAM相比,分布式RAM的访问速度更快,但容量较小。

三、数字信号处理资源模块1.DSP48(数字信号处理单元):DSP48是FPGA中用于实现数字信号处理功能的资源。

在Vivado中,DSP48可以配置为乘法器、累加器、滤波器等。

2.FFT(快速傅里叶变换):FFT是数字信号处理中常用的算法,Vivado提供了FFT IP核,方便用户在FPGA上实现高速的FFT运算。

四、时钟资源模块1.PLL(锁相环):锁相环是FPGA中的时钟管理资源,用于生成、分频、倍频等时钟信号。

Vivado提供了丰富的PLL IP核,以满足不同设计需求。

2.MMCM(混合模式时钟管理):MMCM是FPGA中的一种高级时钟管理资源,具有更低的相位噪声和更高的频率稳定性。

基于Nand Flash的星载综合数据固态记录系统

基于Nand Flash的星载综合数据固态记录系统杨海峰;柴霖;胡建平【摘要】在星载平台资源受限条件下,采用以FPGA+CPU为控制核心、Nand Flash为固态存储阵列的系统架构,实现了高速、大容量、高可靠的数据记录.针对传统双Plane操作与并行扩展对存储速度提升有限、芯片使用较多的问题,采用4级流水线方式控制Flash阵列.为解决标准传输协议传输效率低的问题,设计了一种自定义高速串行传输协议.为减缓空间辐射环境对存储数据的影响,采用了三模冗余、配置回读与部分重构等容错机制.对所提出系统进行的实验验证结果表明,该星载记录系统存储容量达36 Tbit,记录与回放速度分别达到16 Gbit/s与8 Gbit/s,传输误码率为10-12,传输包效率为96.7%,可作为通用存储系统以满足航天应用需求.%In order to realize the high-speed,large capacity,high reliability data recording system under the condition of the limited resources of satellite platform,the FPGA+CPU is chosen as the core control unit,and the system uses the Nand Flash as solid state memory chips.To address the problem that the traditional dual plane operation and parallel expansion have limited storage speed and more chips,the 4-stage pipeline is introduced to control the Flash array.To solve the low data transmission efficiency of standard transmission protocol,a user-defined high-speed serial transmission protocol is designed.To reduce the influence of the space environment on the data storage,such tolorance mechanisms as triple modular redundancy (TMR),configuration read back and partial reconstruction are introduced.Test of a prototype demonstrates that the storage capacity is up to 36 Tbit,recording and playback speeds reach 16Gbit/s and 8 Gbit/s,respectively,and the error rate is 10-12,the transmission packet efficiency is 96.7%.This comprehensive data solid state recorder can be adopted as a universal storage system to meet the demand for aerospace applications.【期刊名称】《电讯技术》【年(卷),期】2017(057)006【总页数】8页(P716-723)【关键词】卫星有效载荷;固态记录系统;Nand Flash存储器;现场可编程门阵列;三模冗余【作者】杨海峰;柴霖;胡建平【作者单位】中国西南电子技术研究所,成都610036;中国西南电子技术研究所,成都610036;中国西南电子技术研究所,成都610036【正文语种】中文【中图分类】TN802星载存储系统是航天飞行平台电子系统的重要组成部分,随着深空探测及载人航天等任务的大力发展,飞行器往往需要同时执行多种任务,探测任务的数据来源与复杂度增加,各类任务对星载存储系统的存储容量、存储管理、数据记录速率、数据回放速率、适应恶劣的空间环境的能力提出了更高的要求。

基于FPGA的高速光纤通信数据传输技术的实现

基于FPGA的高速光纤通信数据传输技术的实现摘要:基于FPGA,对高速光纤通信数据传输技术进行研究,了解其层次结构、工作原理及其应用效果。

为了更好的满足高速数据传输的需求,进行科学、合理的设计,提高测控通信系统数据传输高速性和准确性。

本文通过对高速光纤通信数据传输技术的研究,探讨基于 FPGA 高速光纤通信系统的设计方法,对于高速光纤通信数据传输的实现具有重要意义和价值。

关键词:FPGA;高速光纤通信;数据传输技术前言:现代测控通信系统中集合了计算机技术、通信技术和微电子技术等,能够更加高效、高速的处理复杂的数据,保证数据交换、传输的实时与准确,在雷达探测、导弹制导、卫星遥感等多个领域当中发挥着重要的作用。

高速光纤通信数据传输技术是现代测控通信系统重要支撑,其应用是高速数据传输的基础条件,充分满足大数据量和数据传输带宽增大条件下的数据传输要求。

基于FPGA 实现高速光纤通信数据传输技术的应用,进一步提升了传输数据量和可靠性。

1.高速光纤通信数据传输技术1.1光纤通信技术在现代测控通信系统中,光纤通信技术是不可或缺的通信技术手段,在高速数据传输当中发挥着十分重要的作用。

随着光电器件性能的进一步提升和完善,在很大程度上促进了光纤通信技术的发展,其传输速度更快,且传输容量更大。

在光电通信系统当中,经由发射端发送信号,发送前需经过光发射机进行电光转换,经光纤传输至接收端,其过程中需要中继器来补偿光损耗,进而增加驱动能力。

由光接收机再行光电转换,进而传输信号再次转换为原始信号,将恢复的信号进行输出[1]。

光纤通信系统的工作流程如图1所示:图1:光纤通信系统的工作流程光纤通信协议主要包括光纤分布式数据接口(FDDI)、吉比特光纤以太网(GBE)光纤通道(FC),其层次结构如图2(a)、2(b)和2(c)所示:图2(a):FDDI层次结构图2(b):GBE层次结构图2(c):FC层次结构光纤通信技术的应用,其信道带宽更宽,进而增大了传输容量,同时也增加了中继距离,其具有抗干扰性强、保密性好的优点。

xilinxfpga引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AW AKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE 是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

xilinxfpga引脚功能详细介绍

Xilinx F PGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户10引脚XX代表某个Bank内唯一的一对引脚,Y=[PIN]代表对上升沿还是下降沿敏感,#代表bank 号2.IO_LXXY_ZZZ_#多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn: I/O (在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出曰。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISOl: I,在并口模式(SelectMAP/BPI)下,DO 是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_M1SO2, D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBsoAn: 0, A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O 口。

AWAKE: O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE 是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISOO: I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下, CSI_B 是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISOO是SPI总线的第一位数据。

FCS_B: 0, BPI flash 的片选信号。

FOE_B: O, BPI flash的输出使能信号FWE_B: O, BPI flash的写使用信号LDC: O, BPI模式配置期间为低电平HDC: O, BPI模式配置期间为高电平CSO_B: O,在并口模式下,工具链片选信号。

FPGA高速串行收发器,GTP,GTX

FPGA高速串行收发器,GTP,GTX第1节高速数据连接功能简介10.1.1高速数据传输的背景由于现代通信以及各类多媒体技术对带宽的需求迅猛增长,促使一系列基于差分、源同步、时钟数据恢复(clockanddatarecovery,cdr)等先进技术的互连方式应运而生。

在传统设计中,单端互连方式易受干扰、噪声的影响,传输速率最高只能达到200~250mbps/line;在更高速率的接口设计中,多采用包含有源同步时钟的差分串行传输方式(如lvds、lvpecl等),但在传输过程中时钟与数据分别发送,传输过程中各信号瞬时抖动不一致,破坏了接收数据与时钟之间的定时关系,因而传输速率很难超越1gbps/通道。

因此迫切需要新的高速数据传输技术。

在当前系统级互联速率达到Gbps的设计中,先进的高速串行技术迅速取代了传统的并行技术,成为业界的主流。

高速串行技术不仅可以带来更高的性能、更低的成本和更简化的设计,克服并行速度瓶颈,还可以节省I/O资源,简化印制板的布线。

因此,它被越来越广泛地应用于各种系统设计中,包括PC、消费电子、大容量存储、服务器、通信网络、工业计算与控制、测试设备等。

高速串行传输一般采用差分线路。

到目前为止,业界已经制定了各种串行系统接口标准,如千兆以太网、万兆以太网、PCI Express、串行RapidIO、串行ATA等。

10.1.2xiLinux的高速连接功能解决方案基于高速的需求和传统技术的弊端,xilinx公司在virtex2pro以及更高系列的部分fpga内部集成了能实现高速数据收发rocketi/o模块,采用了cml(currentmodelogic)、cdr、线路编码(8b/10b)和预加重等技术的rocketi/o硬核模块,可极大地减小时钟扭曲、信号衰减和线路噪声对接收性能的影响,从而使传输速率进一步提高,最高可达10gbps以上,可用于实现吉比特以太网、pci-express等常用接口。

基于FPGA实现的高速串口传输技术与实现

(5)将配置位流文件下载到FPGA芯片中,进行实际运行和测试。

4、结论

本次演示设计和实现了一种基于FPGA的以太网和串口数据传输系统,实现了 高速、高效的数据传输和共享。本系统的优点在于具有高度的灵活性和可扩展性, 可以方便地根据实际需要进行功能扩展和优化。由于采用了FPGA技术,本系统还 具有体积小、功耗低、可靠性高等优点,可以广泛应用于各种嵌入式系统和智能 设备中。

为了更好地实现基于FPGA的高速光纤通信数据传输技术,需要以下几个方面:

1.优化硬件设计:根据具体的应用场景和需求,选择合适的FPGA芯片和硬件 组件,并对其进行优化设计,以实现更高效的数据传输和处理。

2.完善软件算法:利用FPGA的并行处理能力和数字信号处理算法,进一步完 善软件算法,提高数据处理速度和可靠性。

最后,为了提高稳定性和可靠性,可以研究更为高效的错误检测和纠正算法, 以及研究如何提高数据传输的鲁棒性。

总结

本次演示介绍了基于FPGA实现的高速串口传输技术与实现。通过利用FPGA的 灵活性和高效性,我们成功地实现了高速串口传输技术,并在速度测试中验证了 其优势。然而,也需要注意到这种技术存在的不足和挑战。未来,高速串口传输 技术将会朝着更高速度、更低成本、更稳定可靠的方向发展。

参考内容

随着信息时代的到来,数据传输的速度和可靠性成为了关键的要素。光纤通 信作为一种现代化的数据传输方式,具有传输速度快、容量大、抗干扰能力强等 优点,被广泛应用于各个领域。为了进一步提升光纤通信的性能,基于FPGA(现 场可编程门阵列)的高速光纤通信数据传输技术得到了广泛的研究与实现。

FPGA是一种高度灵活的芯片,可以由用户进行编程配置,实现各种不同的逻 辑功能。在光纤通信领域,FPGA可以被用于实现数据编解码、信号调制解调、误 码纠正等功能,从而提升数据传输的速度和可靠性。

基于FPGA实现JESD204B高速接口设计

基于FPGA实现JESD204B高速接口设计作者:曹鹏飞来源:《无线互联科技》2018年第23期摘要:JESD204B接口是高速ADC和DAC芯片采用的数据通信接口之一,具有传输速率高,抗干扰能力强,芯片间同步方便等优点。

目前国内JESD204B 接口应用多由国外集成芯片提供,缺乏自主性和灵活性。

为了加强JESD204B 接口自主设计,文章阐述了基于FPGA GTX 高速收发器实现JESD204B接口通信的方法,详细说明了JESD204B接口的FPGA设计实现方案、同步化处理机制等内容。

利用多通道JESD204B接口实现高速串行数据的传输,有效解决了传统并行数据采集存在的问题,满足实际工程的应用需求。

关键词:JESD204B;FPGA;高速串行传输;数据采集模数转换器(Analog-to-Digital Converter,ADC)和数模转换器(Digital to Analog Converter,DAC)在众多领域中应用非常广泛,随着工艺的发展和实际应用的需要,采样速率和采样精度越来越高,采用传统的CMOS接口和LVDS接口已经无法满足设计的要求,而采用基于CML的JESD204B接口可以很好地解决这一问题,接口单通道速率可达12.5 Gb/s。

在ADC/DAC与FPGA处理芯片之间实现JESD204B接口,可以有效完成芯片间的高速数据传输,并且具有减少器件管脚和封装尺寸,减少占用布局空间,降低功耗等优点。

1 JESD204B概述JESD204B接口包括3个子类,分别为子类0、子类1和子类2。

JESD204B接口包括3个子类,分别为子类0、子类1和子类2。

3个子类的区别主要体现在同步方式各不相同。

子类0不支持确定性延迟,而子类1和子类2能够支持确定性延迟,可实现片间的数据同步。

子类1通过SYSREF信号在芯片内部产生帧时钟和本地多帧时钟(Local Multiframe Clock,LMFC),同步传输数据并在数字信道上实现已知和确定性延迟。

基于Aurora协议的万兆串行数据传输研究

摘 要随着网络通信技术的飞速发展和数据信息量的不断增加,信息传输系统速度和吞吐量日趋提升,人们对数据传输的速度和可靠性也提出了更高的要求。

并行传输技术因为存在信号偏移、时钟抖动以及抗干扰能力不足等问题,不能满足高速传输系统的需求。

而高速串行传输技术凭借其速率快、抗干扰能力强和接口简单等优势,逐步取代了传统的并行传输技术,成为了主流的高速数据传输方式。

本文以现场可编程门阵列(Field Programmable Gate Array, FPGA)为平台设计了万兆串行数据传输系统,利用Xilinx公司Virtex-7系列FPGA中的高速串行收发器GTH为主要传输手段来实现,数据传输速率能达到10Gbps。

高速数据传输接口使用Aurora协议来处理。

利用Xilinx配套Vivado开发软件对FPGA进行设计,首先对万兆以太网和万兆数据串行传输技术进行认真研究,深入分析Aurora协议和内嵌的高速串行收发器GTH的结构。

然后通过Aurora协议结合FPGA内部逻辑设计出万兆串行数据传输系统,包括数据传输系统总体框架和内部各个具体功能模块,并对设计内容进行详细阐述,给出对应的工程实现方法。

最后对各个功能模块进行了功能仿真和实际板级测试验证,在FPGA开发平台上进行了实际系统测试,通过Vivado 中的Set up debug工具和思博伦Spirent网络测试仪以及配套软件对系统功能、性能进行测试验证,测试结果均能满足系统要求。

关键词通信技术;万兆串行数据;Aurora协议;数据传输;FPGAAbstractWith the rapid development of network communication technology and the increasing amount of data information, the speed and the throughput of information transmission systems have been increasing, and people have put forward higher requirements for the speed and the reliability of data transmission. The parallel transmission technology cannot meet the requirements of high-speed transmission systems because of the problems such as signal offset, clock jitter, and insufficient anti-interference ability. The high-speed serial transmission technology has gradually replaced the traditional parallel transmission technology by virtue of its high speed, strong anti-interference ability and simple interface, and has become the mainstream high-speed data transmission method.In this paper, a 10 Gigabit serial data transmission system is designed based on Field Programmable Gate Array (FPGA). The high-speed serial transceiver GTH in Xilinx Virtex-7 series FPGA is used as the main transmission means. The data transfer rate can reach 10Gbps. The high speed data transfer interface is handled using the Aurora protocol. Using Xilinx's Vivado development software to design FPGAs, we first studied the 10 Gigabit Ethernet and 10 Gigabit data serial transmission technologies, and analyzed the Aurora protocol and the embedded high-speed serial transceiver GTH. Then, the Aurora protocol is combined with the FPGA internal logic to design a 10G serial data transmission system, including the overall framework of the data transmission system and various internal functional modules. The design content is elaborated and the corresponding engineering implementation method is given. Finally, the function simulation and actual board level test verification of each function module were carried out. The actual system test is carried out on the FPGA development platform. The system function is implemented by the Set up debug tool in Vivado and the Spirent network tester and supporting software. The performance is tested and verified, and the test results can meet the system requirements.Key words Communication technology;10 Gigabit serial data;Aurora protocol;Data transmission;FPGA目 录摘要 (I)Abstract ............................................................................................... I II 第1章绪论 .. (1)1.1 课题的研究背景 (1)1.2 万兆以太网技术 (2)1.3 万兆以太网发展趋势 (2)1.4 论文内容及章节安排 (3)第2章万兆串行数据传输相关技术 (5)2.1 万兆串行传输技术概述 (5)2.1.1 常见万兆串行技术协议 (5)2.1.2 GTX/GTH高速收发器 (6)2.2 Aurora协议 (9)2.2.1 Aurora数据传输模式介绍 (10)2.2.2 Aurora结构与接口定义 (12)2.2.3 Aurora通道初始化分析 (15)2.2.4 Aurora时钟架构与BUFG资源利用 (17)2.2.5 Aurora协议的优势 (19)2.3 本章小结 (19)第3章系统硬件平台设计 (21)3.1 硬件设计总体方案 (21)3.2 FPGA芯片选型 (22)3.2.1 7系列FPGA芯片简介 (22)3.2.2 具体芯片选型 (22)3.3 时钟电路设计部分 (23)3.4 电源模块设计方案 (25)3.5 其他部分单元电路 (27)3.5.1 RS422串口及配置单元电路设计 (27)3.5.2 LED部分 (29)3.6 本章小结 (30)第4章万兆串行数据传输系统的FPGA设计与实现 (31)4.1 开发环境及开发语言简介 (31)4.1.1 开发环境简介 (31)4.1.2 开发语言简介 (31)4.2 总体方案设计 (32)4.3 详细功能模块设计 (33)4.3.1 系统处理带宽考虑 (33)4.3.2 Aurora模块设计 (34)4.3.3 通道分接模块 (37)4.3.4 交换矩阵模块 (41)4.3.5 通道复接模块 (42)4.4 本章小结 (45)第5章系统测试结果与分析 (47)5.1 测试环境搭建 (47)5.1.1 硬件测试环境 (47)5.1.2 软件测试环境 (47)5.2 系统测试结果与数据分析 (48)5.2.1 Set Up Debug测试 (48)5.2.2 万兆数据传输测试与分析 (49)5.2.3 交换矩阵大容量数据交换测试 (50)5.3 本章小结 (52)结论 (53)参考文献 (55)攻读硕士学位期间所发表的论文 (59)致谢 (61)第1章绪论1.1课题的研究背景随着现代通信技术的不断发展和应用领域的日益深化,以往的通信速率和手段已不能满足人们的需求,更高速度的通信不断彰显出来,人们对数据的传输速度有了更高的要求。

Xilinx7系列FPGA高速收发器GTXGTH的一些基本概念

Xilinx7系列FPGA⾼速收发器GTXGTH的⼀些基本概念

本来写了⼀篇关于⾼速收发器的初步调试⽅案的介绍,给出⼀些遇到问题时初步的调试建议。

但是发现其中涉及到很多概念。

逐⼀解释会导致⽂章过于冗长。

所以单独写⼀篇基本概念的介绍,基于Xilinx 7系列的GTX。

需要说明,⽂本只是初步介绍基本概念,会尽量使⽤通俗浅显的描述⽽避免使⽤专业词汇,也只会描述⼀些基本的、常⽤的内容,不能保证全⾯型。

所以从专业⾓度看,可能部分⽤词和原⼚⽂档有出⼊,同时覆盖⾯不够,请见谅。

GTP、GTX、GTH和GTZ:

这四个是Xilinx 7系列FPGA全系所⽀持的GT,GT的意思是Gigabyte Transceiver,G⽐特收发器。

通常称呼为Serdes、⾼速收发器,GT,或者⽤具体型号(例如GTX)来称呼。

7系列中,按⽀持的最⾼线速率排序,GTP是最低的,GTZ是最⾼的。

GTP被⽤于A7系列,GTZ被⽤于少数V7系列。

从K7到V7,最常见的是GTX和GTH。

GTH的最⾼线速率⽐GTX稍微⾼⼀点点。

GTX和GTH的⽂档都是UG476。

从这⾥就能看出来,这两个GT的基本结构⼤同⼩异。

所以掌握⼀个,另⼀个基本也就熟悉了。

基于FPGA的高速串行通信之GTX收发器——差分IO信号

基于FPGA的高速串行通信之GTX收发器——差分IO信号高速差分IO信号的基础知识:1、初步认识GTX当你接触到FPGA的高速串行通信时,比如GTX收发器,一条TX 发送线,一条RX接收线,这时候你肯定会联想到UART串口,UART 串口通信多么简单方便,只要两个通信的设备或者说器件按照一个协议进行传输就OK咯,数据是一位一位的传送的,类似的GTX收发器也是一位一位的传输数据,那么问题来了,UART就问GTX:“凭啥你的传输速率能飙到Gb/s级别,而我的却只能达到Mb/s”,GTX便安慰UART:“兄弟,咱们各有所长噻,我呢,虽然传输速率高,但你传输距离远噻,咱们都是造福人类通信,不过我传的快,其中一个原因就是我的RX、TX都是采用的差分信号,你用一根线,我就要用两根线的”。

2、差分I/O传输技术为什么要抛弃传统的单端信号传输呢,因为随着数据通信速率飞快、供电电压逐渐降低以及对于一个系统越来越“短小精悍”,那么这个单端信号就会相对比较脆弱,再加上周围噪声的干扰,那么这个单端信号就容易受到干扰,信号完整性就会受到破坏,那么差分信号就可以来救驾咯。

先来个书面上的定义:差分信号就是用两条互补的信号线a, b进行传输,而实际需要的信号的这两个信号电位差a-b,这个差值就叫做差分信号。

那为什么差分信号收到青睐呢,一对差分信号如同一对互补的情侣,因为两个人经常处于同一种环境下,当外界噪声到来时,对两个人的干扰程度是一样的,比如噪声为c,a-c和b-c做差后,c 不久消失了么,就是这么神奇……差分传输线具有抗噪声、抗干扰、有效抑制返回路径引起的地噪声和电磁耦合干扰及信号失真的优点。

因为我们关心的是两信号的差值,所以外界的共模噪声被完全消除。

3、第三点辣么我们就要简单地介绍一下,给出差分信号,如何得到原始信号呢?或者说,给出原始信号,如何得到差分信号?差分信号时有两根几乎完全相同的线路来组成一对等值、反相信号,接收端通过比较两端电压差值来确定传输的是“0”还是“1”,如果正参考电压比负参考电压低,则信号为低;如果正参考比负参考电压高,则信号为高。

Xilinx 7系列GTX具体的调试步骤

Xilinx 7系列GTX具体的调试步骤随着需求的多样化,FPGA的功能也进一步的增强。

其中,高速收发器从本来是只有高端FPGA才有的模块,已经变为相对普及的甚至必备的功能模块。

而10G的线速率也从多年前的少数FPGA支持,变为目前的主流线速率。

由于FPGA的最大特点就是灵活,所以FPGA的高速收发器也拥有非常繁琐的配置选项,目的就是为了灵活地支持各种传输协议。

之所以称之为繁琐,就是灵活性带来的弊端,即想要理清楚诸多的功能,就需要非常多时间在高速收发器上。

不过对于大部分的用户来说,需要使用高速收发器的接口通常是相对固定的,这样功能也就相对固定。

这样就没有必要理解高速收发器全部的功能,只要理解需要使用的配置含义即可。

这样可以快速进行尝试/测试,在尝试/测试过程中结合文档进行深入理解。

这样比强行读完文档再动手实践,学习效果上有可能更好。

所以Xilinx的高速收发器中默认就带了一些常用接口的配置,便于用户的学习/使用。

Xilinx 7系列FPGA芯片配置四种高速收发器,按照支持的最高线速率从低到高排列分别是GTP,GTX,GTH,GTZ。

GTP由于结构问题,使用起来灵活性较差,同时支持的最高线速率也只有6.x个G。

GTZ 属于7系列中最高端的高速收发器,集成GTZ的FPGA很少,同时也是用了多die技术,物理上和FPGA主体是两个部分。

对这两种GT,本文不做更多的介绍。

与GTX相比,GTH整体结构几乎一样,只是在个别细节有更多的配置或者更强大的性能。

考虑到文档都是同一篇文档,所以本文以GTX为例。

本文所有内容,除非特别注明,都同时适用于GTX和GTH。

对于高速收发器GTX来说,虽然可以通过IP中的默认配置来进行初步的学习,而且有一定基础之后,可以手动配置GTX参数。

但是如果不充分理解GTX的各个功能,最常见的被卡住的地方,就是不能/不知道如何进行正确的问题定位。

所以文本的主题就是介绍一些常用的调试手段和步骤,便于使用者初步定位问题。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第1节高速数据连接功能简介10.1.1 高速数据传输的背景由于现代通信以及各类多媒体技术对带宽的需求迅猛增长,促使一系列基于差分、源同步、时钟数据恢复(clock and data recovery,CDR)等先进技术的互连方式应运而生。

在传统设计中,单端互连方式易受干扰、噪声的影响,传输速率最高只能达到200~250Mbps/Line;在更高速率的接口设计中,多采用包含有源同步时钟的差分串行传输方式(如LVDS、LVPECL等),但在传输过程中时钟与数据分别发送,传输过程中各信号瞬时抖动不一致,破坏了接收数据与时钟之间的定时关系,因而传输速率很难超越1Gbps/通道。

因此迫切需要新的高速数据传输技术。

在目前系统级互连速率已达到Gbps的设计中,先进的高速串行技术迅速取代传统的并行技术,成为业界的主流。

高速串行技术不仅能够带来更高的性能、更低的成本和更简化的设计,克服了并行的速度瓶颈,还节省了I/O资源,使印制板的布线更简单。

因此,被越来越广泛地应用于各种系统设计中,包括PC、消费电子、海量存储器、服务器、通信网络、工业计算和控制、测试设备等。

高速串行传输一般采用差分线,迄今业界已经发展出了多种串行系统接口标准,例如千兆以太网、万兆以太网、PCI-Express、串行RapidIO、串行ATA 等。

10.1.2 Xilinx公司高速连接功能的解决方案基于高速的需求和传统技术的弊端,Xilinx公司在Virtex 2 Pro以及更高系列的部分FPGA部集成了能实现高速数据收发Rocket I/O模块,采用了CML(CurrentMode Logic)、CDR、线路编码(8B/10B)和预加重等技术的Rocket I/O硬核模块,可极减小时钟扭曲、信号衰减和线路噪声对接收性能的影响,从而使传输速率进一步提高,最高可达10Gbps以上,可用于实现吉比特以太网、PCI-Express等常用接口。

除了底层的物理层技术,Xilinx还提供带32 bit LocalLink用户接口的Aurora协议引擎参考设计。

Aurora 协议是为私有上层协议或标准上层协议提供透明接口的串行互连协议,它允许任何数据分组通过Aurora协议封装,并在芯片间电路板间甚至机箱间传输。

Aurora链路层协议在物理层采用千兆位串行技术,每物理通道的传输波特率可从622Mbps扩展到3.125 Gbps。

Aurora还可将1至16个物理通道绑定在一起,形成一个16个通道绑定而成的虚拟链路,可提供50Gbps的传输波特率和最大40Gbps的全双工数据传输速率。

Aurora可支持广泛的应用围,如:路由器和交换机、远程接入交换机、HDTV广播系统、分布式服务器和存储子系统。

在协议中,每个高速串行被称为“弄”。

协议引擎通过与高速收发器配合,可创建带LocalLink用户接口逻辑的串并、并串收发器。

通过这一串行接口方案,用户无须自己设计有关串行接口所涉及的编解码、同步、速率匹配等问题。

用户接口部分包含了所有必要的信号,如协议引擎的状态信号等。

Xilinx通过高品质的技术支持材料来支持其先进的芯片产品,这些材料包括广泛的知识产权核、参考设计、模拟电路模块、信号完整性(SI)设计套件、数字仿真的质量行为模型等。

此外,Xilinx还提供了众多设计服务、开发平台以及最佳的FPGA实现工具,可确保用户的所有设计需求都能获得最佳产品和技术支持。

第2节实现吉比特高速串行I/O的相关技术10.2.1 吉比特高速串行I/O的特点和应用吉比特收发器(MGT)是吉比特级串行器/解串器(SERDES)的别名。

1.优点1)速度高。

高速串行I/O的线速可超过吉比特,甚至数十吉位。

而并行传输线速不可能超越吉比特。

吉比特串行I/O的主要优势是速度。

在从片/片外、板/板外或盒/盒外获取数据时,没有任何技术可以超越高速串行链路。

高速串行链路的线速围为1Gb/s~ 12Gb/s,有效负载围为0.8Gb~10Gb。

2)节省管脚数。

将大量数据传入/出芯片或电路板时所遇到的第一个问题是引脚数,电路板设计时间和成本会随着管脚数的增加而急剧增加。

在大数据量应用下,串行I/O可节省大量的管脚(在低速以及小数据量应用中,MGT比传统并行模式需要更多的电源和接地引脚)。

3)简化同步转换输出。

采用单端并行总线时,设计者应考虑同步转换输出(SSO,即大量寄存器的值在某一时刻同时翻转,会对电源和地平面产生一定的影响,甚至影响到器件部时钟和逻辑的正常工作)。

如果出现太多的同步转换,触地反弹会产生大量噪声。

设计者还可以在所有I/O上都使用差分信号处理技术,以此来消除SSO问题,但是这样做就会使引脚数翻倍。

如果数据流需求比较适中,设计者可以使用具有适当引脚数的并行接口。

4)EMI指标优。

经验表明:时钟越快,放射测试就越难进行,因此,吉比特设计的EMI测试看起来是不可能实现的。

但是,通常高速串行链路的辐射量比以较低速度工作的大型总线低。

这是因为运行时的吉比特链路需要出色的信号完整性,正如经典论断“辐射问题实际上就是信号完整性问题”所言,因此吉比特串行IO具有更好的EMI指标。

5)成本低。

采用MGT通常会降低系统总成本。

连接器采用较小、较经济的封装时,引脚数较少,电路板设计也更简单。

6)预设协议。

采用MGT的另一个好处是可以使用预先定义好的协议和接口标准。

如Xilinx提供了从Aurora到XAUI的多种协议,满足不同的用户需求。

2.缺点吉比特高速串行I/O的最大缺点在于对信号完整性的严格要求。

而且,阻抗控制的PC(印刷电路)板、高速连接器和电缆的费用较高。

因此,必须处理数字仿真中的复杂性和时基较小的问题。

并且,在利用预设协议的时候,必须为集成过程计划时间,以及为协议的开销安排额外的逻辑电路或CPU时钟周期。

3.应用围起初,吉比特级串行器/解串器(SERDES)仅局限于用在电信行业和少数缝隙市场(如广播视频)。

如今,MGT应用出现在电子行业的各个角落——军事、医疗、网络、视频、通信等等。

MGT也可以用于背板或机箱之间的PCB上。

对于电子行业的发展前景而言,MGT至关重要。

下面是采用吉比特级SERDES的行业标准示例。

•光纤通道(FC)•PCI Express•RapidIO串行•先进的交换互连(Advanced Switching Interface)•串行ATA•1Gb以太网•10Gb以太网(XAUI)•Infiniband 1X、4X、12X吉比特级通信似乎强加了一些苛刻限制。

串行设计者必须考虑信号完整性、较小的时基以及可能出现的对额外门电路和CPU周期的需求。

但是,在盒间以及芯片间通信中采用吉比特级技术的优势远远超过了那些可以察觉到的缺点。

例如:高速、引脚数少、低EMI和低成本等,这些都使它成为了众多高速设计的理想之选,并保证了其在未来通信系统中得到广泛的使用。

10.2.2 吉比特串行I/O系统的组成吉比特串行传输是一种通用的传输标准,虽然不同FPGA厂家的模块和组件名不同,但其关键技术都具备下列共同点。

1.系统整体结构吉比特串行传输的系统整体结构如图10-1所示。

下面对其中的主要模块进行简要介绍。

图10-1 吉比特高速串行I/O的系统结构示意图串行器:将速率为y的n位宽并行数据转变成速率为n*y的串行数据。

解串器:将速率为n*y的串行数据转变成速率为y的n位宽并行数据。

Rx(接收)对齐:将接收的数据对齐到合适的字边界。

可以使用不同的方法,从自动检测和对齐特殊的预留比特序列(通常也称作comma字符),到用户控制的比特调整。

时钟管理器:管理各种时钟操作,包括时钟倍频,时钟分频,时钟恢复。

发送FIFO(先进先出):在输入数据发送之前,暂时保存数据。

接收FIFO:在接收数据被提取之前,暂时保存数据。

在需要时钟修正的系统中,接收FIFO是必须的。

接收线路接口:模拟接收电路,包括差分接收器,还可能包括有源或者无源均衡电路。

发送线路接口:模拟发送电路,可以支持多种驱动负荷。

通常还带有转换的预加重部分。

线路编码器:将数据编码成适应不同线路的格式。

编码器通常会消除长的无转变位的序列,同时还可以平衡数据中0、1的出现次数。

需要注意的是,线路编码器是一个可选模块,某些SERDES可能没有。

线路译码器:将线路上的编码数据分解成原始数据。

(这是一个可选模块,编码可能在SERDES外完成)。

时钟修正和通道绑定:修正发送时钟和接收时钟之间的偏差,同时也可实现多通道间的歪斜修正。

(通道绑定是可选的,并不一定包含在SERDES中)。

其他可能包括的功能模块有:循环冗余检测(CRC)码生成器、CRC检测器、多种编码和解码(4b/5b、8b/10b、64b/66b)、可调的扰码器、各种对齐和菊花链选项、可配置的时钟前端和后端以及不同等级的自环。

2.参考时钟的要求1)时钟精度吉比特级收发器的输入时钟、或是参考时钟的规格定义是非常严格的。

其中包含非常严格的频率要求,通常用每百万次容许频率错误的单位PPM来定义。

抖动要求也是十分严格的,通常用时间(皮秒)或者时间间隔(UI)定义。

下面给出这些相关定义。

•PPM:百万分之一;用来描述非常小的比率。

•UI:时间间隔;等价于一个符号的时间长度,例如:0.2UI = 20%的符号时间。

•抖动:理想传输位置的偏差。

如此严格的规定才使得PLL和时钟提取电路能够正常工作。

通常系统的每一个印刷电路板都需要有一个精确石英晶体振荡器供MGT使用。

这些晶体振荡器的精确度比大多数用在数字系统中的晶体振荡器要高一个级别,而且价格也要高出一截。

很多情况下,一般的时钟发生芯片和PLL因为带有很大的抖动,而不能用于MGT。

2)时钟修正策略传输时钟有非常严格的抖动要求,所以吉比特SERDES通常不能将恢复时钟作为传输时钟。

每一个PCB集合都有唯一的振荡器和唯一的频率。

如果两个1GHz的振荡器仅仅有1PPM的频差,同时我们提供1/20的参考时钟,则数据流的时钟每秒钟可能会增加或者缺失20,000个周期。

因此,在8b/10b 编码的系统中,每秒将会额外增加或者损失2万个符号。

大多数的SERDES都有时钟修正选项。

时钟修正需要使用唯一的符号或者符号序列,它们在数据流中是不会出现的。

因为时钟修正是对齐的后续处理,所以可以比较容易地通过保留一个K字符、或者一组有序的K字符、或者一个时钟修正数据序列来实现。

时钟修正进行的频数必须足够多,从而可以通过丢弃或者重复来补偿时钟的差异。

当然,有些系统并不需要时钟修正。

例如,相同的参考时钟和相同的速率意味着不需要进行时钟修正。

同样,如果所有接收电路的时钟都来自恢复时钟,那么时钟修正也是不需要的。

如果FIFO的写入速率和读出速率相等,也没有必要进行时钟修正。