ISE教程5

ISE使用指南基础篇

ISE使⽤指南基础篇第4章ISE开发环境使⽤指南第1节ISE套件的介绍与安装4.1.1ISE简要介绍Xilinx是全球领先的可编程逻辑完整解决⽅案的供应商,研发、制造并销售应⽤范围⼴泛的⾼级集成电路、软件设计⼯具以及定义系统级功能的IP(Intellectual Property)核,长期以来⼀直推动着FPGA技术的发展。

Xilinx 的开发⼯具也在不断地升级,由早期的Foundation系列逐步发展到⽬前的ISE9.1i系列,集成了FPGA开发需要的所有功能,其主要特点有:包含了Xilinx新型SmartCompile技术,可以将实现时间缩减2.5倍,能在最短的时间内提供最⾼的性能,提供了⼀个功能强⼤的设计收敛环境;全⾯⽀持Virtex-5系列器件(业界⾸款65nm FPGA);集成式的时序收敛环境有助于快速、轻松地识别FPGA设计的瓶颈;可以节省⼀个或多个速度等级的成本,并可在逻辑设计中实现最低的总成本。

Foundation Series ISE具有界⾯友好、操作简单的特点,再加上Xilinx的FPGA芯⽚占有很⼤的市场,使其成为⾮常通⽤的FPGA⼯具软件。

ISE作为⾼效的EDA设计⼯具集合,与第三⽅软件扬长补短,使软件功能越来越强⼤,为⽤户提供了更加丰富的Xilinx平台。

4.1.2ISE功能简介ISE的主要功能包括设计输⼊、综合、仿真、实现和下载,涵盖了FPGA开发的全过程,从功能上讲,其⼯作流程⽆需借助任何第三⽅EDA软件。

设计输⼊:ISE提供的设计输⼊⼯具包括⽤于HDL代码输⼊和查看报告的ISE⽂本编辑器(The ISE Text Editor),⽤于原理图编辑的⼯具ECS(The Engineering Capture System),⽤于⽣成IP Core的Core Generator,⽤于状态机设计的StateCAD以及⽤于约束⽂件编辑的Constraint Editor等。

综合:ISE的综合⼯具不但包含了Xilinx⾃⾝提供的综合⼯具XST,同时还可以内嵌Mentor Graphics公司的LeonardoSpectrum 和Synplicity公司的Synplify,实现⽆缝链接。

ISE学习教程

1、ISE的安装现以ISE 5.2i为例介绍Xilinx ISE Series的安装过程。

1)系统配置要求ISE 5.2i推荐的系统配置与设计时选用的芯片有关。

因为在综合与实现过程中运算量非常大,所以对系统配置要求很高。

为了提高综合、仿真、实现过程的速度,对于计算机的CPU的主频、主板和硬盘的工作速度,尤其是内存大小配置都有非常高的要求。

在ISE 5.2i支持的所有Xilinx的FPGA/CPLD中,要求最低的Spartan II和XC9500/XL/XV等系列需要的内存和虚拟内存推荐值均达到128MB,而对于Virtex-II XC2V8000来说,需要的内存和虚拟内存推荐值均高达3GB。

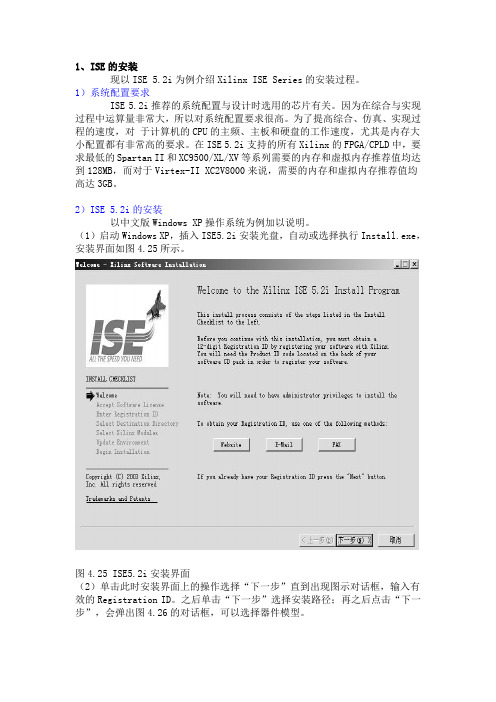

2)ISE 5.2i的安装以中文版Windows XP操作系统为例加以说明。

(1)启动Windows XP,插入ISE5.2i安装光盘,自动或选择执行Install.exe,安装界面如图4.25所示。

图4.25 ISE5.2i安装界面(2)单击此时安装界面上的操作选择“下一步”直到出现图示对话框,输入有效的Registration ID。

之后单击“下一步”选择安装路径;再之后点击“下一步”,会弹出图4.26的对话框,可以选择器件模型。

图4.26 器件模型选择对话框(3)点击“下一步”,如图4.27所示,可以选择器件种类。

图4.27 器件种类选择对话框通过以上步骤后,可根据具体情况来选择,继续“下一步”即可完成安装。

安装完成后,环境变量应作如下描述:若操作系统是Windows NT/2000/XP,选择开始->控制面板->系统->选项->系统->高级->环境变量,在环境变量中加入:变量名:Xilinx变量值:C:Xilinx(即安装路径)具体设置如图4.28所示。

图4.28 环境变量设置操作图3)安装第三方软件在PC上安装完ISE之后,还需要安装第三方仿真软件,如ModelSim等。

ISE使用手册

4.6.1 ISE数据库接口(DBI) ......................................................................... 41 4.6.2 MySQL接口 ....................................................................................... 43 4.6.3 开发更多的数据库接口 ........................................................................... 45 五. ISE编程示例...................................................................................................... 46 5.1 四个简单的TCP协议 ....................................................................................... 46 5.2 简单的HTTP服务 ........................................................................................... 48 5.3 服务状态监视器 ............................................................................................ 48 5.4 工作者线程池 ............................................................................................... 48 5.5 简单的UDP服务端 ......................................................................................... 49 六. 附录 ................................................................................................................ 50 6.1 ISE参数配置................................................................................................ 50 6.2 参考资料 .................................................................................................... 52

第5章 ISE应用基础实验

第5章ISE应用基础实验ISE 是指集成综合环境,本章通过一系列的实验,使学习者对ISE这一工具的应用有较为深刻的认识,并对FPGA的仿真与设计环境有深入的了解,为进一步的工作奠定基础。

5.1 ISE9.1 使用流程实验1. 实验背景知识:了解FPGA的实验、项目研发与设计流程,了解ISE软件在FPGA的项目设计的作用、组成部分和基本操作步骤。

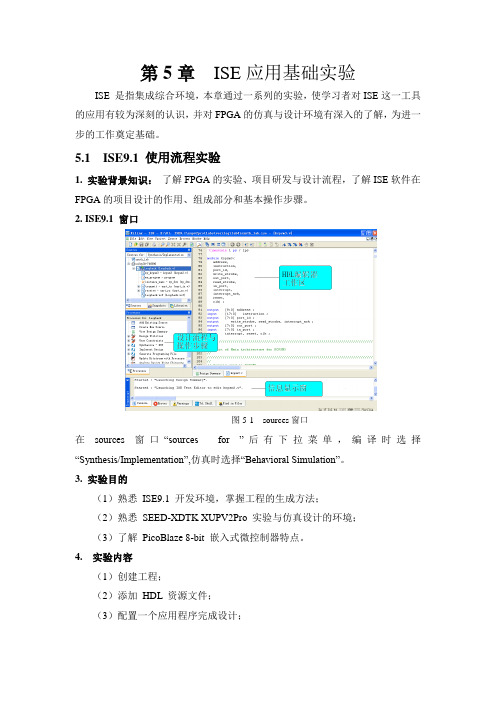

2. ISE9.1 窗口图5-1 sources窗口在sources窗口“sources for ”后有下拉菜单,编译时选择“Synthesis/Implementation”,仿真时选择“Behavioral Simulation”。

3. 实验目的(1)熟悉ISE9.1 开发环境,掌握工程的生成方法;(2)熟悉SEED-XDTK XUPV2Pro 实验与仿真设计的环境;(3)了解PicoBlaze 8-bit 嵌入式微控制器特点。

4. 实验内容(1)创建工程;(2)添加HDL 资源文件;(3)配置一个应用程序完成设计;(4)设计的仿真及实现。

5. 实验准备(1)将光盘下03. Examples of Program 实验程序目录下的01. ISE9.1 文件夹拷贝到E:盘根目录下;(2)将USB 下载电缆与计算机及XUPV2Pro 板的J8 连接好;(3)将RS232 串口线一端与计算机连接好,另一端与板卡的J11 相连接;(4)启动计算机后,将XUPV2Pro 板的电源开关SW11 打开到ON 上。

观察XUPV2Pro 板上的+2.5V,+3.3V,+1.5V 的电源指示灯是否均亮,若有不亮的,请断开电源,检查电源。

6.实验步骤(1)创建工程1)双击桌面Xilinx ISE9.1 快捷方式打开ISE 工程管理器(Project Navigator)。

2)打开Project Navigator 后,选择File → New Project ,弹出新建工程对话框;图5-2 ISE 工程管理器3)在工程路径中单击“…”按钮,将工程指定到如下目录,单击确定。

ISE使用教程(修改稿)

点击project菜单的New Source

设计输入

• 要完成这个计数器模块,可以在ISE自动生成的代 码框架基础上通过自己编写代码完成,也可使用 ISE的语言模板(ISE Language Template)工具 来完成。 • 选择Edit->Language Template或者通过点击工 具栏中最右端的灯泡按钮 来打开语言模板。 在语言模版(Language Template )窗口中,有 很多Xilinx提供的参考代码片断,找到需要的 counter代码片断。

保存后进行功能仿真

仿真结果

下载验证

在生成可用于下载的Bit流文件前,必须生成ucf约 束文件,否则生成的bit流文件将无法在硬件上正 常运行。 约束文件中可包含:时序约束,周期约束,偏移 约束,管脚约束等。其中管脚约束是必不可少的, 它将你设计文件中的I/O与实际硬件管脚进行关联。 管脚约束可调用ISE的PASE工具实现。 最后使用ISE IMPACT工具通过JTAG口下载bit流 至硬件。

管脚约束源文件的建立

管脚约束文件的建立

3.在此编辑窗口进行管脚约束编写 例如:net "ckout(3)" loc="k12"; net "ckout(2)" loc="p14"; net "ckout(1)" loc="l12"; net "ckout(0)" loc="n14"; net "clk" loc= "t9" ; net"direction" loc = "f12";

1.选中

2.双击 编写完成后保存

ISE软件使用说明(两篇)

引言:概述:ISE软件是由Xilinx公司开发的一款集成电路设计工具,使用该软件可以进行数字电路设计、仿真、验证以及实现等多个阶段的工作。

在设计阶段,ISE软件提供了丰富的组件库和设计工具,方便用户进行电路原理图的绘制和逻辑设计。

在验证阶段,ISE软件可以进行功能仿真和时序仿真,以确保设计的正确性和稳定性。

在实现阶段,ISE软件提供了先进的布局与布线工具,能够将设计转化为实际的电路板。

正文内容:1.安装与启动1.1ISE软件安装包1.2安装ISE软件1.3启动ISE软件2.项目管理2.1创建新项目2.2导入已有项目2.3添加设计文件2.4设定项目属性2.5保存和备份项目3.设计流程3.1电路原理图设计3.1.1组件选择3.1.2连接元件3.1.3设置元件属性3.2逻辑设计3.2.1设计约束3.2.2逻辑优化3.2.3时序约束3.3约束文件编辑3.3.1约束规则3.3.2约束语法3.3.3约束检查3.4时序仿真3.4.1创建仿真波形3.4.2设定初始状态3.4.3运行仿真3.5功能仿真3.5.1设置输入信号3.5.2运行仿真3.5.3分析仿真结果4.仿真与验证4.1时序分析4.1.1设定时钟4.1.2时序路径分析4.1.3时序优化4.2时序约束验证4.2.1满足约束4.2.2修复时序错误4.3灵敏度分析4.3.1设定输入敏感性4.3.2分析敏感性4.4逻辑分析4.4.1切换敏感性4.4.2分析逻辑状态5.布局与布线5.1物理约束5.1.1面积约束5.1.2信号完整性约束5.1.3电源与接地约束5.2布局5.2.1网表导入5.2.2管理物理资源5.2.3进行布局布线5.3时序优化5.3.1满足时序约束5.3.2缩短信号传输路径5.3.3优化时钟分配5.4布线5.4.1管理布线资源5.4.2进行布线5.4.3路由与优化5.5设计规约检查5.5.1检查布局布线规约5.5.2修复设计规约错误总结:引言概述:ISE软件是一款功能强大的集成开发环境工具,广泛应用于数字电路设计和实现。

ISE人机操作分析步骤(最新2015)

人机操作分析步骤本模块的主要功能在于通过对某个作业过程中人和机器的作业内容的研究,寻求最佳的人机配合作业方案。

在此模块中,用户可以针对需要分析的作业拍摄1个或者多个视频文件,然后分别分析在这个作业过程中各人和各机在某个特定的生产周期中在任何一个时刻的状态。

当所有对象(人和机)都被依次分析完成之后,系统根据分析的内容自动生成对比表,用户可以通过对比表看到此作业过程中,各个要素之间的配合状况,并针对问题进行改善活动。

打开登录软件,打开方法研究菜单,进入“产品工序数据库”页面,操作参考“标准工时”内的操作,完成产品设置。

切换进入“产品工艺”,然后进行“产品产线“设置和“产品工序”设置,其设置方法参照“标准工时”,另外“产品工序”设置需要注意分析类型及设置人机数量析,如果该工序现状为1人1机,则按上图进行设置。

如果现状是一人2机,或者想改善进行一人2机操作(现状是1人1机),则按上图进行设置。

当产品、产线和工序都设置好后,在方法研究模块中点击“视频管理器”(记住:是方法研究模块中的视频管理器)切换进入视频管理器,参考“标准工时”操作设置视频,如果是进行人机操作分析,则进行勾选相应项。

见下图,然后进行视频和工序“一对一关联”和“移到服务器”,其操作参见标准工时。

(注意:关联前最好把视频备份一份,因为关联后会改变视频名称,造成事后不知道哪个视频是第几序,干什么)对于1人1机,见上图,会出现铣端面打中心孔(第1人);铣端面打中心孔(第1机),事前把要分析的1人1机视频,复制一份,起不同名字,然后和铣端面打中心孔(第1人);铣端面打中心孔(第1机)分别关联,但视频内容是一样的。

关联和移到服务器后,进入方法研究中“人机操作分析”模块切换进入“人机操作”分析,通过输入产品名称或是从浏览数树中选择对应视频分析上图解释:视频选项栏中有2个可选视频,分析对象选项栏中也有2个可选视频;如果选择的是铣端面打中心孔(第1机).WMV视频,分析对象选择的是铣端面打中心孔(第1人)视频(其实这两个视频为同一视频),则对人的所有操作进行分析,不对机器动作分析,人不操作的所有时间都为空闲。

ISE学习教程解析

1、ISE的安装现以ISE 5.2i为例介绍Xilinx ISE Series的安装过程。

1)系统配置要求ISE 5.2i推荐的系统配置与设计时选用的芯片有关。

因为在综合与实现过程中运算量非常大,所以对系统配置要求很高。

为了提高综合、仿真、实现过程的速度,对于计算机的CPU的主频、主板和硬盘的工作速度,尤其是内存大小配置都有非常高的要求。

在ISE 5.2i支持的所有Xilinx的FPGA/CPLD中,要求最低的Spartan II和XC9500/XL/XV等系列需要的内存和虚拟内存推荐值均达到128MB,而对于Virtex-II XC2V8000来说,需要的内存和虚拟内存推荐值均高达3GB。

2)ISE 5.2i的安装以中文版Windows XP操作系统为例加以说明。

(1)启动Windows XP,插入ISE5.2i安装光盘,自动或选择执行Install.exe,安装界面如图4.25所示。

图4.25 ISE5.2i安装界面(2)单击此时安装界面上的操作选择“下一步”直到出现图示对话框,输入有效的Registration ID。

之后单击“下一步”选择安装路径;再之后点击“下一步”,会弹出图4.26的对话框,可以选择器件模型。

图4.26 器件模型选择对话框(3)点击“下一步”,如图4.27所示,可以选择器件种类。

图4.27 器件种类选择对话框通过以上步骤后,可根据具体情况来选择,继续“下一步”即可完成安装。

安装完成后,环境变量应作如下描述:若操作系统是Windows NT/2000/XP,选择开始->控制面板->系统->选项->系统->高级->环境变量,在环境变量中加入:变量名:Xilinx变量值:C:Xilinx(即安装路径)具体设置如图4.28所示。

图4.28 环境变量设置操作图3)安装第三方软件在PC上安装完ISE之后,还需要安装第三方仿真软件,如ModelSim等。

ISE使用教程(修改稿)

点击project菜单的New Source

设计输入

• 要完成这个计数器模块,可以在ISE自动生成的代 码框架基础上通过自己编写代码完成,也可使用 ISE的语言模板(ISE Language Template)工具 来完成。 • 选择Edit->Language Template或者通过点击工 具栏中最右端的灯泡按钮 来打开语言模板。 在语言模版(Language Template )窗口中,有 很多Xilinx提供的参考代码片断,找到需要的 counter代码片断。

4、为元件添加连线(add the wire )

注意:在元件端口拉出一小段线段为以后添加网线名称并 设置I/O管教做准备,否则可能添加不上 5、添加网线名(add the branch) 6、设置I/O管理 7、生成器件符号

8、调用项目生成的器件符号,进行系统设计 9、绘制总线 10、检查

谢谢大家!

ISE软件概述

ISE系列软件特点综述

• Xilinx作为当今世界上最大的FPGA/CPLD生产 商之一,长期以来一直推动着FPGA/CPLD技 术的发展。其开发的软件也不断升级换代,由 早期的Foundation系列逐步发展到目前的 ISE10.x系列。 • ISE是集成综合环境(Integrated Software Environment)的简称,是Xilinx提供的一套工 具集,其集成的工具可以完成FPGA/CPLD从 源码输入、仿真、综合到下板调试的整个开发 过程。

几点需要注意的地方

• 用 ModelSim 进行仿真,包括 行为仿真亦 即功能仿真和布局布线后的仿真亦即时序 仿真(详细可以去参考ModelSim教程)

用ISE自带的仿真工具仿真

• ISE仿真工具设置

ISE--使用教程

第三步: 布局和布线”Place & Route”

第52页,共83页。

基于VHDL语言的ISE设计流程

--查看布局布线后结果

选择Place & Route, 并展开

选择View/Edit Routed Design(FPGA Editor)

第53页,共83页。

基于VHDL语言的ISE设计流程

--查看布局布线后结果

布局和布线(PAR)

适配(Fit)

时序收敛

配置文件加载后,用 示波器、逻辑分析 仪、软件程序观察

时序仿真 设计下载 系统调试与验证

entity lab1 is port(a,b,c : in std_logic;

y : out std_logic); end lab1;

architecture rtl of lab1 is begin y<=a or (c and b); end rtl;

--对该设计文件进行综合

行为级综合可以自动将系统直接从行为级描述综

合为寄存器传输级描述。 行为级综合的输入为系统的行为级描述,输出为

寄存器传输级描述的数据通路。

行为级综合工具可以让设计者从更加接近系统概 念模型的角度来设计系统。同时,行为级综合工具能

让设计者对于最终设计电路的面积、性能、功耗以及

可测性进行很方便地优化。

基于VHDL语言的ISE设计流程

--揭开LUT的秘密

•0 0 0 •0 0 1 •0 1 0 •0 1 1 •1 0 0 •1 0 1 •1 1 0 •1 1 1

双击打开LUT3 双击打开LUT2

终于明白了FPGA的LUT

是怎么实现逻辑功能的

第29页,共83页。

基于VHDL语言的ISE设计流程

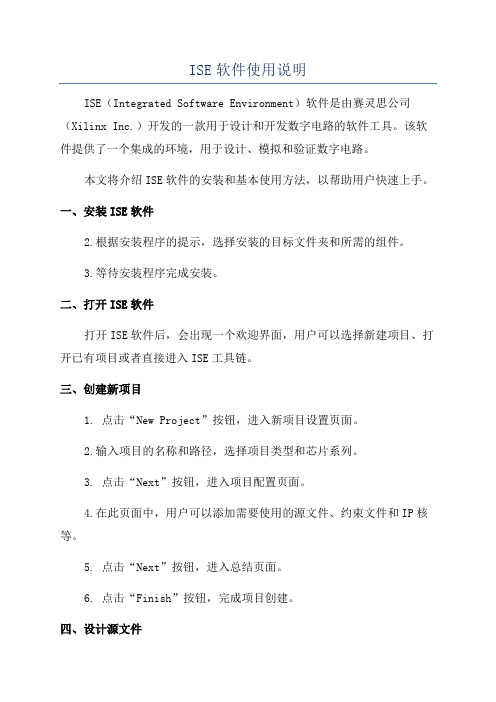

ISE软件使用说明

ISE软件使用说明ISE(Integrated Software Environment)软件是由赛灵思公司(Xilinx Inc.)开发的一款用于设计和开发数字电路的软件工具。

该软件提供了一个集成的环境,用于设计、模拟和验证数字电路。

本文将介绍ISE软件的安装和基本使用方法,以帮助用户快速上手。

一、安装ISE软件2.根据安装程序的提示,选择安装的目标文件夹和所需的组件。

3.等待安装程序完成安装。

二、打开ISE软件打开ISE软件后,会出现一个欢迎界面,用户可以选择新建项目、打开已有项目或者直接进入ISE工具链。

三、创建新项目1. 点击“New Project”按钮,进入新项目设置页面。

2.输入项目的名称和路径,选择项目类型和芯片系列。

3. 点击“Next”按钮,进入项目配置页面。

4.在此页面中,用户可以添加需要使用的源文件、约束文件和IP核等。

5. 点击“Next”按钮,进入总结页面。

6. 点击“Finish”按钮,完成项目创建。

四、设计源文件在ISE软件中,用户可以使用HDL(硬件描述语言)进行设计源文件的编写。

ISE软件支持的HDL语言有VHDL和Verilog。

1. 在项目视图中,右键点击“Source”文件夹,选择“New Source”。

2.在弹出的对话框中,选择源文件类型和语言。

3. 输入文件的名称和路径,点击“Finish”按钮。

五、添加约束文件约束文件用于定义电路的时序、引脚映射等信息,以确保电路的正常工作。

1. 在项目视图中,右键点击“Constraints”文件夹,选择“New Source”。

2.在弹出的对话框中,选择约束文件类型。

3. 输入文件的名称和路径,点击“Finish”按钮。

六、综合与实现在进行综合和实现之前,需要根据设计需求进行一些设置和配置。

1. 在项目视图中,右键点击项目名称,选择“Properties”。

2.在弹出的对话框中,选择“SYNTHESIS”或“IMPLEMENTATION”选项卡。

ISE实例演示步骤

计周期。该套件可供给MicroBlaze微控制器系统(MCS)使

用。支持面向7系列,如Artix7,Kintex7,Spartan3, Virtex4、5、6等。

ISE特点

1.优良的集成环境

ISE是一个集成环境,可以完成整个FPGA/CPLD开发过程

,其集成了很多设计工具,可以大大提高产品设计效率。 2.简洁流畅的界面风格 其界面秉承了可视化编程技术,界面根据设计流程而组织 ,易学易用。

4.自动使用之前创建工程时所设置的器件

单击下一步

ISE具体步骤

5.选择简单的单核系统

a.选择单核

b.单击下一步

ISE具体步骤

6.对处理器进行简单的设置

a.根据硬件主时钟选择晶振 频率 b.系统时钟选择晶振倍频 后的频率 c.内存选择16KB

这是系统默认的最精简内核

d.单击下一步

ISE具体步骤

7. 进行Peripheral添加与简单设置

a.选择器件系列 b.选择具体器件 c.根据习惯,选择工具 d.选择语言

e.单击下一步

ISE具体步骤

4.刚才所建工程的一些信息

核对所设置的信息 无误后,单击完成

ISE具体步骤

第二步 在工程中添加一个嵌入式软核 1. 选中xc6slx9-2ftg256,右键选择New Source

c.选择嵌入式软核 b.软核名称 a.软核所在文件夹 d.单击下一步

单击添加外设

ISE具体步骤

按键,数据位宽为1

IIC总线

LED,数据位宽为1

串口

单击下一步

ISE具体步骤

单击下一步

ISE具体步骤

8.查看内核地址分配信息

单击完成

ISE具体步骤

ISE操作说明

ISE操作说明1、双击打开ISE,选择“file->new project”新建一个工程。

2、修改工程保存路径并输入工程名,然后单击next。

3、选定芯片型号如下图所示。

然后一直单击next直到finish。

4、将源文件拷贝到新建的工程中。

5、单击synthesize进行综合。

6、进行引脚分配。

点开User Constraints,双击Assign Package Pins,弹出如下窗口,单击Yes。

7、弹出以下窗口。

8、按以下窗口进行管脚分配。

9、关闭窗口并保存窗口内容。

10、单击Implement Design 进行编译、布局、布线。

11、单击Generate Programing File生成下载文件。

12、单击Configure Device(iMAPCE),进入下载界面。

13、单击finish14、单击Bypass15、选择对应的模块,把**.bit文件加载进来16、加载完成之后会弹出一个警告,单击OK17、右键单击最后一个模块,选择program18、如图选择,单击OK,就可以下载了19、下载完成后,会出现如下图所示的窗口显示program succeeded。

20、以上操作是直接将二进制文件下载到FPGA中,掉电之后将丢失。

为使其重新上电时可自动配置,需要将配置文件下载到prom中保存。

因此,首先要生成prom配置文件。

双击Generate PROM、ACE or JTAG File,进入生成prom配置文件界面。

21、选择“Prepare a PROM File”,单击next。

22、键入要生成的PROM 名称,如下图所示。

23、单击add,添加prom器件。

单击next,直到finish。

24、单击ok。

25、选择二进制文件26、单击No。

27、单击ok。

28、单击Generate File,生成配置文件29、双击Baundary Scan,然后单击重新进行JTAG链扫描。

ISE基本操作

1 在服务器linux下建立新用户,包括口令和密码。

2 安装exceed网络访问软件,按照提示进行安装。

设置服务器ip地址,192.168.1.883 通过进入进入,输入用户名和密码进入linux操作系统。

Terminal中输入/ISE/bin/GENESISe。

进入/ISE/bin/custom4 将师兄的文件考入自己建的目录下面(否则不能保存,软件问题),打开目录下面所需要的,进入。

点击右键,出现,选择Boundary。

进入mdraw 界面,绘制器件结构。

5首先选择绘制器件结构,选中是“坑”。

在中选择SiC材料,用画矩形,选中,再点击矩形的各个端点,输入坐标位置。

其中,坐标单位默认为um。

依次画出器件的其他部分结构,宽度对器件的性能的影响不大,不需要精确定位。

和调解大小。

使用中的zoom reset也可以达到效果。

(Mdraw中默认的是um 微米)6在中添加新的电极名(cathode,anode),框中存在的电极表示要添加的。

再点击按钮,在图中相应的位置点击下,添加接触。

删除不需要的部分。

Preferences调节相应的参数。

7选择掺杂。

点击(均匀掺杂),在窗口的区域里面划动鼠标,选取掺杂区域,在窗口里面,确定掺杂区域对角线端点坐标,掺杂种类和掺杂浓度。

依次对各个区域进行掺杂。

8划分网格。

点击,在窗口的某个区域里面划动鼠标,出现窗口。

由此,确定划分网格区域的对角坐标,网格划分的最大值和最小值,网格大小的划分直接影响结果的收敛性,所以要不断调整,(一般原则,网格的划分最大值一般取作全长的1/10,最小值取作最大值的一半)。

还要在中添加掺杂种类。

其中还有一点要注意,对于不规则图形,默认区域的网格划分也要设定。

默认区域是指最大的矩形。

在菜单里面选择选择默认区域,设置它的对角线坐标值应该是最大的区域,同时划分网格大小,在中添加掺杂种类点击ok。

点击键,可以查看网格划分和掺杂信息(掺杂点端点,网格点区域)。

ISE软件使用说明

说明这个说明主要介绍了使用开发板可能使用到的3个工具,主要以串口功能的实现作为例子,讲述了ISE, Plantform和EDK的使用方法以及操作的基本流程。

ISE的使用一.启动Xilinx ISE:开始Æ所有程序ÆXilinx ISE 7.1iÆProject Navigator二.新建/打开一个工程:如果已经有了工程,则在FileÆOpen Project弹出的对话框里面选择你的工程。

如果没有合适的工程就需要通过FileÆNew Project来新建一个工程。

具体操作步骤如下:分别在Project Name和Project Location里面填写您想要创建的工程的名称和路径。

在Top-Level Module Type的下拉菜单里面选择您的工程的顶层模块的类型。

本次串口通信的实验的顶层为原理图,所以选择Schematic。

然后点击下一步:在这个对话框的上半部分选择您使用的芯片的族(Spartan3),型号(xc3s400),封装(pq208)和速度(-4)。

下面选择您要使用编译和综合的软件,建议使用ISE自带的软件,一是使用简便,二是Xilinx公司对自己的FPGA了解程度比第三方要高很多,所以使用Xilinx公司自己的软件有的时候会获得意想不到的收获。

具体参数选择如图,然后单击下一步:在这个对话框里面新建工程里面的文件,这步也可以放到后面来实现,这里我们先选择下一步:这一步用来添加已经存在的文件,同样,我们在后面实现这步。

点击下一步:在最后这个对话框里面显示了我们即将建立的工程的详细信息,确认无误以后点击完成,ISE将为您创建一个名字为uart_test的工程:三.为刚创建的工程添加源文件:1.添加已经存在的源文件:选中屏幕右上的xc3s400-4pq208,单击ProjectÆAdd Source,在弹出的对话框里面选择您已经存在的程序文件(.v .vhd)。

ISE使用指南中

4.3.2 基于ISE的仿真在代码编写完毕后,需要借助于测试平台来验证所设计的模块是否满足要求。

ISE提供了两种测试平台的建立方法,一种是使用HDL Bencher的图形化波形编辑功能编写,另一种就是利用HDL语言。

由于后者使用简单、功能强大,所以本节主要介绍基于Verolog语言的测试平台建立方法。

1.测试波形法在ISE中创建testbench波形,可通过HDL Bencher修改,再将其和仿真器连接起来,再验证设计功能是否正确。

首先在工程管理区将Sources for设置为Behavioral Simulation,然后在任意位置单击鼠标右键,在弹出的菜单中选择“New Source”命令,然后选中“Test Bench WaveForm”类型,输入文件名为“test_bench”,点击Next进入下一页。

这时,工程中所有Verilog Module的名称都会显示出来,设计人员需要选择要进行测试的模块。

由于本工程只有一个模块,所以只列出了test,如图4-30所示。

图4-30 选择待测模块对话框用鼠标选中test,点击“Next”后进入下一页,直接点击“Finish”按键。

此时HDL Bencher程序自动启动,等待用户输入所需的时序要求,如图4-31所示。

图4-31 时序初始化窗口时钟高电平时间和时钟低电平时间一起定义了设计操作必须达到的时钟周期,输入建立时间定义了输入在什么时候必须有效,输出有效延时定义了有效时钟延时到达后多久必须输出有效数据。

默认的初始化时间设置如下:∙时钟高电平时间(Clock High Time):100ns∙时钟低电平时间(Clock Low Time):100ns∙输入建立时间(Input Setup):15ns∙输出有效时间(Output Valid):15ns∙偏移时间(Offset):100ns单击“OK”按钮,接受默认的时间设定。

测试矢量波形显示如图4-32所示。

XilinxISE软件简单教程课件

Xilinx ISE软件的优缺点

概述Xilinx ISE软件的优点和 缺点,帮助用户全面评估软 件。

Xilinx ISE软件的应用场 景

介绍Xilinx ISE软件广泛应用 于哪些领域和项目,以及其 在每个领域中的优势。

XilinxISE软件简单教程课 件

Xilinx ISE软件简单教程课件为您提供了入门级的教程,让您了解Xilinx ISE软 件的作用、特点以及使用方法。

简介

Xilinx ISE软件是什么?

介绍Xilinx ISE软件是一款功能强大的FPGA开发工具,可以帮助您设计和验证数字电路。

Xilinx ISE软件的作用

解释下载和仿真之间的区别和各自的用途。

3 下载和仿真的流程

讲解下载和仿真的基本步骤,以便用户正确地验证并调试设计。

实例操作

具体实例操作演示

通过示范一个具体的实例,向用户展示Xilinx ISE软 件的使用方法。

实例的说明和分析

对实例进行逐步解析和分析,帮助用户理解设计过 程和结果。

总结

Xilinx ISE软件的功能

解释综合和实现在FPGA设计流 程中的作用和区别。

综合和实现的关系

讨论综合和实现之间的紧密关 联,以及它们在设计迭代中的 作用。

综合和实现的过程

详细描述综合和实现的步骤, 以及如何将设计转换为可下载 的位文件。

下载和仿真

1 下载和仿真的作用

介绍下载和仿真在FPGA设计验证和调试过程中的重要性。

2 下载和仿真的区别

参考资料

相关书籍和文献

提供与Xilinx ISE软件相关的书籍和文献,以便用户进一步学习和深入研究。

ISE软件使用说明

使用的FPGA的种类

Device

使用的FPGA的型号

Package

使用的FPGA的封装

Speed Grade

使用的FPGA的速度

Top-Level Module Type

顶层模块类型

Synthesis Tool

综合工具

Simulator

仿真工具

Generated Simulation Language

wire

led5;

wire

Hale Waihona Puke led6;wire

led7;

wire [3 :0] sw; reg [7 :0] led;

assign sw ={sw0,sw1,sw2,sw3}; assign {led0,led1,led2,led3,led4,led5,led6,led7}=led;

always @ ( posedge clk or negedge rst) begin if(!rst) led<='b0; else case ( sw ) 4'b0001: led <= 8'b0000_0001; 4'b0010: led <= 8'b0000_0010; 4'b0100: led <= 8'b0000_0100; 4'b1000: led <= 8'b0000_1000; 4'b0011: led <= 8'b0001_0000; 4'b0110: led <= 8'b0010_0000; 4'b1100: led <= 8'b0100_0000; 4'b1001: led <= 8'b1000_0000; default: led <= 8'b0000_0000; endcase end

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Xilinx 工具流程实验Xilinx 工具流程实验介绍本实验介绍ISE 软件结构向导管脚及区域约束编辑器和Xilinx 的工具流程目标完成此实验后你将会• • • 在ISE 的项目导航器中建立一个新的项目 利用结构向导建立一个DCM 例化 将例化置于设计之中• 利用软件的缺省选项实现一个设计• 利用PACE 工具指定管脚位置和区域位置过程注意当用Toolwire来执行实验时所有的软件程序文件和项目都在卷标 U:\ 下而不是在 C:\ 下建立一个新的项目第一步登录到ISE 项目导航器在C:\training\fund\labs\flow 子目录下建立一个名称为FlowLab 的新项目目标器件为xc2v40-4fg256设计流程可以是XST Verilog 或XST VHDL 你可以根据你的喜好选择相应的语言打开Xilinx ISE 5.1 软件从开始菜单里选择程序Programs→ Xilinx ISE5.1 →项目导航器Project Navigator在项目导航器中选择文件File →新项目New Project这时新项目窗口就会打开图 5b-1图5b-1. 新项目窗口对于项目名键入FlowLab对于项目位置使用按钮浏览到C:\training\fund\labs\flow单击 OK选择器件家族 Virtex 2选择器件为xc2v40封装为fg256速度等级为–4选择设计流程XST Verilog 或 XST VHDL单击 OK添加源文件第二步将子目录C:\training\fund\labs\flow\verilog 或C:\training\fund\labs\flow\vhdl 中所有源文件添加到FlowLab 项目中在项目导航器窗口中选择项目Project →添加源文件Add Source在添加已有源文件对话框图 5b-2中用下拉菜单浏览到C:\training\fund\labs\flow子目录然后进入 VHDL 或 Verilog子目录这取决于你在建立项目时所选择的流程选中所有文件单击第一个文件ch_fifo然后在按住Shift键的同时在添加已有源文件对话框中单击文件 pn_correlator图 5b-2. 添加已有源文件对话框点击打开Open对于VHDL 用户每个文件将出现选择源文件类型对话框对于除了ch_fifo_pack.vhd之外的的其它所有文件选择VHDL模块VHDL Module并点击OK对于ch_fifo_pack.vhd 选择VHDL封装VHDL Package并点击OK图5b-3. 选择源文件类型ISE将处理所有的文件并确定设计层次在项目导航器的右下角的进程条显示分析的进程添加的文件被分析后设计文件和层次将反映在项目窗口的源文件中用结构向导建立DCM例化 第三步用结构向导中的DCM向导创建一个名为MyDCM的新的源文件使用CLK0 CLK2X和LOCKED引脚 设定输入时钟频率为100MHz而其它选项为缺省设置在项目导航器中选择项目Project→新源文件New Source在新源文件窗口中选择结构向导(Architecture Wizard)并输入MyDCM作为文件名点击下一步 Next然后在下一个窗口中点击完成Finish在结构向导选择对话框中确定DCM向导已被选择并点击OK (图 5b-4).图 5b-4. 结构向导选择对话框注意Rocket I/O向导在此不可选这是因为我们的目标器件为Virtex-II而 Rocket I/O 能力仅在 Virtex-II PRO 器件中才有在Xilinx DCM 向导 – 通用设置窗口操作如下输入DCM例化名MyDCM_inst选中 CLK 2X输出框去除RST引脚的选择输入输入时钟频率为100 MHz然后点击下一步图 5b-5. Xilinx DCM 向导 – 通用设置窗口注意在DCM向导中指定频率的目的是让向导知道DCM是工作在高频模式还是低频模式基于输入的频率还可以计算输出的频率以确保是否在规定的频率范围之内另外如果选择CLKFX 输出的话输入频率还可以被用来计算在CLKFX上的输出频率以及计算估计的抖动在 Xilinx DCM向导中 – 时钟缓冲器窗口保持选项为缺省设置并点击完成注意一个新的文件(MyDCM.xaw)被添加到项目源文件窗口选择MyDCM.xaw文件进入当前源文件进程窗口双击查看HDL源文件并检查结构向导所产生的源代码将DCM例化置于设计(VHDL)中 第四步注意对于Verilog进入第五步将例化模板中的部件声明部分拷贝到ch_fifo.vhd中的合适位置然后将部件例化从例化模板中拷贝到ch_fifo.vhd 中的合适位置最后分配信号和修改代码以完成例化见本节的子步骤6和7将DCM例化置于设计中)保存修改好的文件在项目源文件窗口双击 ch_fifo.vhd 打开源代码选择文件MyDCM.xawMyDCM.xaw 选中后进入当前源文件进程窗口双击查看HDL例化模板在HDL 例化模板中复制部件声明这一部分 (从 COMPONENT MyDCM开始到 ENDCOMPONENT为止)并粘贴到 ch_fifo.vhd 的第四十行 (在部件fifo_2048x8之后在信号pn_lock, wr, wr_addr_srst : std_logic之前)在HDL 例化模板中复制部件例化这一部分 (从 Inst_MyDCM: MyDCM 直到文件结束为止) 并粘贴到 ch_fifo.vhd 的第五十四行在 begin之后在 pn_correlator_inst:pn_correlator之前按照如下方式完成例化MyDCM_inst: MyDCM PORT MAP(clkin_in => wr_clk_in,locked_out => lock ,clk2x_out => rd_clk,clk0_out => wr_clk);目前设计中有两个时钟信号没有用到DCM既然我们现在已使用了DCM我们需要修改和添加一些信号名以便例化能工作有三个地方需要修改a) 在ch_fifo 实体声明中将wr_clk改为wr_clk_in.b) 在 ch_fifo实体中将 rd_clk 信号删除既然该信号将要由DCM生成c) 在五十三行附近其它信号声明之后begin 行之前添加以下信号声明signal lock, rd_clk, wr_clk : std_logic;选择 文件File→ 保存Save 以保存文件将DCM置于设计(Verilog)中 第五步将部件例化从例化模板中拷贝到ch_fifo.v 中的合适位置最后分配信号和修改代码以完成例化见本节的子步骤4和5将DCM例化置于设计中)保存修改好的文件在项目源文件窗口双击 ch_fifo.vhd 打开源代码现在选择文件MyDCM.xawMyDCM.xaw 选中后进入当前源文件进程窗口双击查看HDL例化模板在HDL例化模板中复制部件声明这一部分 (从 MyDCM 开始一直到最后的 );结束 ) 并粘贴到ch_fifo.v 的第十行(在 wire [7:0] wr_data之后在pn_correlatorpn_correlator_inst之前)按照如下方式修改例化MyDCM MyDCM_inst (.CLKIN_IN(wr_clk_in),.LOCKED_OUT(lock),.CLK2X_OUT(rd_clk),.CLK0_OUT(wr_clk));目前设计中有两个时钟信号没有用到DCM既然我们现在已使用了DCM我们需要修改和添加一些信号名以便例化能工作有四个地方需要修改a) 在ch_fifo模块的端口列表中将 wr_clk 改为 wr_clk_inb) 同样在ch_fifo 模块的端口列表中, 删除 rd_clk端口c) 在 ch_fifo 的端口声明中从输入信号列表中删去 rd_clk信号因为此信号将由DCM产生d) 添加下列wire声明到第七行lock, rd_clk, wr_clk这样整个一行将变成wire pn_lock, wr, wr_addr_srst, lock, wr_clk, rd_clk;选择 文件File→保存Save以保存文件实现设计 第六步选择顶层设计文件ch_fifo.v/vhd, 实现设计.确认在项目源文件窗口中选择的是顶层的设计文件 (如图 5b-6). 顶层设计文件名为 ch_fifo.v/vhd图5b-6. 项目源文件窗口在当前源文件进程窗口如图5b-7中双击实现设计Implement Design注意工具将会执行实现设计所必需的所有进程在本实现中在进入实现之前工具将先执行综合图 5b-7. 当前源文件进程窗口实现期间的观测第七步注意进程条每一个进程旁边的状态符号和控制信息注意项目导航器窗口的右下角显示的是进程和设计实现的完成百分比如图5b-8图5b-8. 进程条在当前源文件进程窗口点击实现设计旁边的+展开实现步骤并查看进程我们称此为展开一个进程每一步完成之后在每一步旁边将出现一个符号 • • • 绿色的对号表示成功黄色的惊叹号表示有警告 红色的X 表示有错误对于这个特定的设计在每一步将会有一个黄色的惊叹号警告但这些警告无碍可以忽略当实现完成时项目导航器窗口底部的控制/信息窗口将会显示以下信息Done: completed successfully.打开PACE第八步在项目导航器中以建立一个新源文件的方式建立一个名为myucf 的UCF 文件然后从当前源文件进程窗口中打开PACE 工具用户约束User Constraints → 指定封装引脚Assign Package Pins在我们能够打开PACE 之前我们必须建立一个UCF 文件按照警告信息要建立一个UCF文件只要选择项目Project →新源文件New Source选择实现约束文件输入 myucf作为文件名点击下一步Next在下一个窗口中确定选择的是 ch_fifo点击下一步然后在最后一个窗口中点击完成如图5b-11)图 5b-11. 关联一个约束文件在当前源文件进程窗口展开用户约束然后双击指定封装管脚以打开PACE如果你不能看到这些进程确认在项目源文件窗口中选择的是ch_fifo测试PACE 第九步检查PACE中的四个窗口检测这些窗口怎样相互作用在PACE窗口中移动器件结构窗口和封装引脚窗口以使它们相邻图 5b-12. 器件结构窗口和封装引脚窗口在封装引脚窗口中点击用户I/O符号这些符号是中间为圆圈的框它们可能是不同颜色的方框圆圈后的不同颜色代表不同的I/O组注意在器件结构窗口中相应的引脚是如何被高亮的在设计层次窗口点击I/O引脚旁的的+号展开I/O引脚子目录你也可以展开全局逻辑和逻辑子目录来检查其中的内容这些名称来自于设计图 5b-13. 设计层次窗口注意设计对象列表窗口是如何跟着设计层次窗口中所选的子目录而变化的建立引脚和区域指配 第十步将所有rd_data<?>信号指定到BANK2上将DCM 元件放置在位置 DCM_X1Y1上将BRAM元件放置在块RAM 位置X1Y1上在设计层次窗口选择 I/O管脚子目录注意可以为每一个信号指配一个实际的引脚位置或为一个信号指定在特定组中的引脚范围在设计对象列表-I/O引脚窗口中将所有rd_data<?>信号指定到BANK2上可以这样操作选择一个信号在位置这一列点击框的右侧使用选择组的下拉菜单然后选择BANK 2图 5b-14. 设计部件列表 – I/O引脚窗口注意你可以在下拉菜单向下滚动时看到其它的位置选择 T, L, R, TL, TR, BL, BR,RT, RB, 等等这些词语是指组它们表示上部 组 硅片顶部的两组左部 组 硅片左部的两组左上部 组 硅片左上部的组等等这在你不了解组号但你又想将引脚指定到器件的那个区域是非常有帮助的在设计层次窗口点击全局逻辑文件夹在接下来的几步中我们将要将它们拖放到器件结构窗口中以便为这些部件指定特定的位置在设计对象列表窗口中选择DCM 元件并将其拖到器件结构窗口中将DCM 放置在右上方的DCM_X1Y1位置上如图所示图 5b-15. 指定一个位置在设计对象列表窗口中选择块RAM fifo_2048x8_inst_fifo_bram并将其拖到硅片的右上方的块RAM 位置X1Y1上图 5b-16. 指定一个位置选择文件 → 保存以保存引脚范围指配和DCM 及块RAM 布局选择 文件 → 退出以关闭PACE 工具在项目导航器的当前源文件进程窗口中在用户约束的下方双击编辑约束文本来查看通过PACE 工具在文件myucf.ucf 中所生成的约束查看文本版本的UCF 文件检查约束是否被写入文件图5b-17. 当前源文件进程窗口实现设计第十一步实现设计确保没有错误或与我们所建约束的冲突确认在项目源文件窗口中选择的是顶层的设计文件 (如图 5b-18)顶层设计文件名为 ch_fifo.v/vhd图 5b-18. 项目源文件窗口在当前源文件进程窗口如图5b-19中双击实现设计 Implement Design注意工具将会执行实现设计所必需的所有进程在本实现中在进入实现之前工具将先执行综合图5b-19. 当前源文件进程窗口结论本实验的目的是熟悉实现进程结构向导和PACE 的使用在本实验中我们在ISE 中将一个设计的主要阶段走了一遍建立项目添加源文件使用结构向导来改进和/或完成我们的代码指定管脚和区域位置实现整个设计。