OV9650内部手册

OV9650摄像头

//上拉无效 //GPE15 为 SIO_D,GPE14 为 SIO_C,都为输出

void delay(int a) {

int k;

for(k=0;k<a;k++) ;

}

//启动 SCCB void __inline SCCB_start(void) {

CLOCK_HIGH(); DATA_HIGH(); delay(10); DATA_LOW(); delay(10); CLOCK_LOW(); delay(10); }

//结束 SCCB void __inline SCCB_end(void) {

DATA_LOW(); delay(10); CLOCK_HIGH(); delay(10); DATA_HIGH(); delay(10); }

//SCCB 发送一个字节 void __inline SCCB_sendbyte(unsigned char data) {

//读操作

unsigned char SCCB_receivedata(unsigned char subaddr) {

unsigned char temp;

//2 相写传输周期 SCCB_start(); SCCB_sendbyte(0x60); SCCB_sendbyte(subaddr); SCCB_end();

{0x11,0x80},{0x6a,0x3e},{0x3b,0x09},{0x13,0xe0},{0x01,0x80},{0x02,0x80},{0x00,0x00},{0x10, 0x00},

{0x13,0xe5},{0x39,0x43},{0x38,0x12},{0x37,0x00},{0x35,0x91},{0x0e,0xa0},{0x1e,0x04},{0xA8, 0x80},

VP9650高清视频会议解决方案

高清视讯系统技术方案北京盛世合创科技有限公司徐凯2016年1月28日目录1前言 (3)1.1概述 (3)1.2高清图像成为时代标准 (3)2视讯系统设计与参考规范 (5)2.11总体设计原则 (5)2.12参考规范和标准 (6)3 视讯系统设计方案 (6)3.11组网说明 (6)3.12系统说明 (6)4高清视频系统主要功能 (7)4.1会议常用功能 (7)4.1.1工作会议 (8)4.1.2个人视频通信 (8)4.1.3主叫呼集功能 (8)4.1.4全景会场特性 (9)4.1.5强大的字幕、横幅功能 (9)4.1.6全方位中文支持 (9)4.1.7Web会议控制功能 (9)5华为高清视频系统主要特点 (10)5.11畅性 (10)5.12高清静态、动态双流 (11)5.13CD音质效果 (11)5.14采用国际标准协议 (12)5.2.2极高的稳定性 (12)5.2.3良好的兼容性。

(12)6产品简介 (13)6.1高清会议终端TE40-1080P30/60FPS (13)6.2多点控制单元VP9650(1080P60fps).............................。

(14)6.3高清摄像头VPC600 (15)6.4全向麦克风VPM220 (516)。

7华为公司简介 (17)7.1华为公司介绍 (18)7.2华为视讯产品的优势 (20)7.3面向客户的服务 (22)8结束语 (25)1 前言1.1概述目前企业随着办公效率提高、提倡低碳环保及能快速的进行有效的大范围工作会议、远程领导协商、指挥等工作,建立一套应用性强、稳定可靠的高清远程视频系统成为必不可少的工作利器。

视讯技术实现了语音、图像、数据等信息综合在一起的远距离传输,使人们在进行异地交流时利用视讯技术既可以听到对方的声音,又可以看到对方的活动图像和胶片内容,大大增强了异地交流的亲切感和临场感。

在“效率至上”的信息社会中,通过视讯系统,进行协同工作时既可听到对方的声音,又可看到对方的图像,大大增强了沟通的效果,在节约宝贵的时间、精力和金钱的同时,又提高了企业的管理和决策效率,充分发挥出视频会议真实、高效、实时的优点,为人们提供了一种简便而有效的协同工作手段。

OV9650 调试总结和寄存器配置表

经过4天的调试摄像头终于可以拍照片保存到电脑上来,ov9650的调试走了不少弯路,一些教训总结如下:1:OV9650是OmniVision公司的COMS摄像头,号称有130万像素,但是实际效果感觉不如CCD的,特别是远处的背景更糟糕。

2:OV9650的datasheet上写的寄存器控制协议是Serial Camera Control Bus (SCCB),还给了个时序图,但是它用的是两线制的SCCB协议;根据它的时序图是可以兼容I2C的,两者在细微之处有点差别,但不影响,但实际应用中,都是后端平台的I2C接camera的SCCB。

可惜我没有仔细分析,愣是用两个GPIO模拟SCCB通信协议。

此乃一错3:对于OV9650,OmniVision公司是提供了参考寄存器配置的!一定要找相关人员要!(可能是他们的datasheet写得太烂的原因吧),可以我过分相信自己,没有找技术支持沟通!此乃二错4:ov9650复位后默认配置是不能收到图像的!(在我的这个模式下:YUV422,VGA),当我在用I2C配置时,有的像的轮廓但颜色偏绿,我以为是没有配置起寄存器,但是实际上是配置起寄存器了,是YUV的顺序有问题!此乃三错5:我们用的是杰得提供的VIA模块控制API,杰得的API多、复杂、有错且没有系统的说明,又由于我没有调试摄像头的相关经验,也没有弄明白杰得的VIA模块API。

所以调试的时候没有图像,到底是摄像头输出问题?还是Z228接收处理的问题?无法判断!调试完摄像头了才知道杰得的库是可以输入4:2:2,输出4:2:0的!我觉得调试步骤应该如下:一:先要保证硬件没有问题!1:首先要看RESET脚和,PDN脚.的电平是否正确,RESET:高电平复位.PDN:低电平工作正常。

2:第一次调试I2C总线的时候,把示波器放在数据线上,抓图分析看OV9650是否应答。

地址应该是60H不要搞错了!3:测试关键信号(这一小步要寄存器配置正确芯片正常工作了才有的):时钟输入信号pin13: 24M正弦波(外部晶振的输入)。

ZST6000光伏逆变器综合测试仪入门手册V1.02

致远电子

安全须知

本仪器的使用涉及到高压,为防止电击或其它危险造成的人员伤亡,在安装、使用或 维修本产品之前,请务必仔细阅读、并完全理解“安全须知”章节的相关内容。 为保证您能正确安全地使用本仪器, 请务必遵守以下注意事项。 如果未遵守本手册指定 的方法操作本仪器, 可能会损坏本仪器的保护功能。 因违反以下注意事项操作仪器所引起的 损伤,广州致远电子股份有限公司概不承担责任。

产品入门手册 << I

致远电子

注意搬运安全

ZST6000 入门手册

为避免仪器在搬运过程中滑落,造成仪器面板上的按键、旋钮或接口等部件损坏,请注 意搬运安全。

警示标志

注意符号表示存在危险。提示用户对某一过程、操作方法或类似情况 进行操作时,如果不能正确执行或遵守规则,则可能对产品造成损坏或者 丢失重要数据。在完全阅读和充分理解注意所要求的事项之前,请不要继 续操作。 警告符号表示存在严重危险。提示用户对某一过程、操作方法或类似 情况进行操作时,如果不能正确执行或遵守规则,则可能造成人身伤害甚 至死亡。在完全阅读和充分理解警告所要求的事项之前,请务必停止操作。

安全信息

光伏逆变器综合测试仪安全符号如下所示。

小心,危险

CE 认证

地端子

小心,电击危险

请勿将使用过的 电池丢入垃圾桶

可回收利用

CAT Ⅱ(1000V)IEC 测量Ⅱ类,输入可连接到归属到Ⅱ类过电压条件下的电源 ( 最大 1000VAC)。 一般注意事项 针对人身安全与设备保护,列出注意事项如下所述: 保护功能有缺陷。在使用仪器之前,请对保护功能进行确认。如发现 保护接地或保险丝有缺陷,请勿继续使用本仪器; 请勿拆卸仪器的机箱。仪器内部有高压,非常危险。若要对仪器内部 进行检查和调试,请咨询广州致远电子股份有限公司; 出现异味或冒烟时。出现机体冒烟或散发异味等异常情况时,请直接 关闭电源,从插座拔掉电源插头,并切断连接在输入端子的测量回路 的电源。发生异常情况时,请咨询致远公司; 勿在易燃环境下操作仪器。请勿在含有易燃易爆液体或气体的环境里 使用本仪器; 请勿损坏电源线。请勿将物品摆放在电源线上,并使电源线远离热源。 将电源插头从插座拔出时,请勿拉扯电线,而应手持插头拔出。电源 线有破损时,请在确认好零件编号后再向经销商订购;

PCS-9654D说明书

为增强或修改现有功能,装置的软硬件均可能升级,请确认此版本使用手册和您购买的产品相兼容。

警告!

电气设备在运行时,这些装置的某些部件可能带有高压。不正确的操作可能导致严重的人身伤害或设备损坏。

只有具备资质的合格专业工作人员才允许对装置或在装置临近工作。工作人员需熟知本手册中所提到的注意事项和工作流程,以及安全规定。

连接电缆

仔细处理连接的电缆避免施加过大的外力。

版权声明©2021NR.南京南瑞继保电气有限公司版权所有

我们对本文档及其中的内容具有全部的知识产权。除非特别授权,禁止复制或向第三方分发。凡侵犯本公司版权等知识产权的,本公司必依法追究其法律责任。

我们定期仔细检查本文档中的内容,在后续版本中会有必要的修正。但不可避免会有一些错误之处,欢迎提出改进的意见。

5)完善的事件报告处理功能,可保存最新64次动作报告、64次故障录波,最新1024次变位报告、1024次自检报告、1024次运行报告、1024次遥控报告。

6)友好的人机界面、汉字显示、中文报告显示。

7)具有灵活的通信方式,配有最多4个独立的以太网接口和最多2个独立的以太网接口+2个独立的RS-485通信接口。可以同时支持站内监控后台、保护信息工作站、调度通讯。

0.30A@110Vdc

0.15A@220Vdc

1.20A@48Vdc

0.50A@110Vdc

0.25A@220Vdc

起动时间

<8ms(典型3ms)

<10ms

返回时间

<5ms(不包括软件延时)

<10ms

电气寿命

10000次

10000次

2

颜色

银灰

装置重量

12kg

OV7670中文版数据手册

OV7670/OV7171 CMOS VGA(OmniPixel ®)CAMERACHIPTM 图像传感器

电器性能 表2 最大额度

-40°C 到+95°C VDD-A VDD-C VDD-IO 输入/输出电压(对地) 无铅,表面加工温度 4.5V 3V 4.5V -0.3V 到 VDD-IO +0.5V 245°C

OmniPixel,VarioPixel,OmniVision 图标已注册为 OmniVision 商标 CameraChip 已注册为 OmniVision 商标 版权所有 版 所有

公司名称:深圳博霖电子有限公司; 联系人:胡生 黄生 ; 电 话:0755-26869655 15011860004; 传 真:0755-26686865 ; 邮 箱:bolinelec@163.com ; 网 址:www.bolin-elec.com

公司名称:深圳博霖电子有限公司; 联系人:胡生 黄生 ; 电 话:0755-26869655 15011860004; 传 真:0755-26686865 ; 邮 箱:bolinelec@163.com ; 网 址:www.bolin-elec.com

OV7670/OV7171 CMOS VGA(OmniPixel ®)CAMERACHIPTM 图像传感器

引脚定

表 1 引脚定义

引脚 A1 A2 A3 A4 A5 B1 B2 B3 B4 B5 C1 C2 D1 D2 E1 E2 E3 E4 E5 F1 F2 F3 F4 F5 名称 AVDD SIO_D SIO_C D1a D3 PWDN VREF2 AGND D0 D2 DVDD VREF1 VSYNC HREF PCLK STROBE XCLK D7 D5 DOVDD RESET# DOGND D6 D4 类型 电源 输入/输出 输入 输出 输出 输入(0)b 参考 电源 输出 输出 电源 参考 输出 输出 输出 输出 输入 输出 输出 电源 输入 电源 输出 输出 功能/说明 模拟电源 SCCB 数据口 SCCB 时钟口 数据位 1 数据位 3 POWER DOWN模式选择 参考电压-并 0.1UF 电容 模拟地 数据位 0 数据位 2 核电压+1.8VDC 参考电压-并 0.1UF 电容 帧同步 行同步 像素时钟 闪光灯控制输出 系统时钟输入 数据位 7 数据位 5 I/O 电源,电压(1.7~3.0) 初始化所有寄存器到默认值 数字地 数据位 6 数据位 4 0:RESET 模式 1:一般模式 0:工作 1:POWER DOWN

OV9650 datasheet

A PPLICATION N OTEO mniTMisionThis document is provided "as is" with no warranties whatsoever, including any warranty of merchantability, non-in-fringement, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification, or sample.OmniVision Technologies, Inc. disclaims all liability, including liability for infringement of any proprietary rights, relating to the use of information in this document. No license, expressed or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.* Third-party brands, names, and trademarks are the property of their respective owners.Note:The information contained in this document is considered proprietary to OmniVision Technologies, Inc. Thisinformation may be distributed only to individuals or organizations authorized by OmniVision Technologies, Inc. to receive said information. Individuals and/or organizations are not allowed to re-distribute said information.OV9650 Color CMOS SXGA (1.3 MegaPixel) CameraChip™Implementation GuideLast Modified: 7 December 2004Document Version: 1.1Revision NumberDateRevision1.011/29/04Initial Release1.112/07/04In Table 4-1 on page 21, changed last six entries under column "Gain."OV9650 Color CMOS SXGA (1.3 MegaPixel) CameraChip™OTable of ContentsSection1, Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61.1Function Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6Section2, Image Sensor Array. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72.1Resolution Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8Section3, Timing Generator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103.1Array Control and Frame Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103.1.1Frame Generation (SXGA, VGA, and lower resolutions). . . . . . . . . 103.2Sync Signal Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103.3Frame Rate Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113.3.1Clock Prescalar (Timing Generator) . . . . . . . . . . . . . . . . . . . . . . . . . . 113.3.2Dummy Pixel Adjustment (Output Formatter) . . . . . . . . . . . . . . . . . . 123.3.3Dummy Line Adjustment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123.4Exposure Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123.4.1Digital Exposure Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123.5Strobe Flash Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193.6RGB Raw Data Output Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20Section4, Analog Processing Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204.1Gain Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204.1.1Manual Gain Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204.1.2Automatic Gain Control (AGC). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224.2White Balance Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234.2.1Automatic White Balance Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244.2.2Manual White Balance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24Section5, Digital Signal Processor (DSP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 255.1Gamma Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 255.1.1Gamma Slope Calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 265.2Color Matrix. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 275.2.1Color Matrix Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 275.3Sharpness Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 305.4Noise-Canceling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 305.5White Pixel Correction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 305.6Digital Black Level Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 305.7Lens Shading Correction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 312Proprietary to OmniVision Technologies Version 1.1, December 7, 2004OSection6, Output Formatter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 336.1Windowing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 346.2Data Formatting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 356.2.1ITU-656 Format Enable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 366.2.2Frame Rate Adjust. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 366.2.3Output Data MSB/LSB Swap Enable . . . . . . . . . . . . . . . . . . . . . . . . . 376.2.4D[9:0] - PCLK Reference Edge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37Section7, Digital Video Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38 Section8, Special Image Effects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38 Section9, Preview Mode to Still Image Capture Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 399.1Exposure Time and Gain Calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40Section10, SCCB Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4010.1Control Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4010.1.1Register Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4110.1.2Standby Mode Enable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4110.1.3Tri-state Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4110.2Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42Section11, Prototyping and Evaluation Modules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5311.1OV9650EAA Prototyping Module. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5311.2OV9650ECX USB 2.0 Evaluation Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53Section12, Lens selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53 Section13, OV9650 Bug List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53 Appendix A, Reference SCCB Settings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54Version 1.1, December 7, 2004Proprietary to OmniVision Technologies3OV9650 Color CMOS SXGA (1.3 MegaPixel) CameraChip™OList of FiguresFigure1-1OV9650 Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Figure3-1Manual Exposure Frame Drop Timing Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure3-2Desired Convergence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Figure3-3SXGA Strobe Flash Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Figure3-4VGA Strobe Flash Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Figure3-5QVGA Strobe Flash Timing Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Figure5-1Gamma Curve. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Figure5-2Lens Shading Correction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 Figure6-1Example of Windowing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 Figure6-2MSB/LSB Output Data Swap . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 374Proprietary to OmniVision Technologies Version 1.1, December 7, 2004OList of TablesTable2-1OV9650 Output Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Table2-2Resolution Register Settings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Table3-1Frame Rate, Pixel Clock Rate, and Input Clock Rate (CLKRC=0x81, 4X PLL) . 11 Table3-2Banding Filter Value (Input Clock Frequency = 12 MHz, 4X PLL). . . . . . . . . . . . . 16 Table3-3AEC Convergence Limits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Table3-4AEC Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Table4-1Total Gain to Control Bit Correlation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Table4-2AGC General Controls. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Table4-3AGC Enable Bit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Table4-4AGC Convergence Limits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 Table4-5AWB Red/Blue Balance Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 Table5-1Related Registers and Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Table5-2Color Matrix Related Registers and Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Table5-3Color Matrix Related Registers and Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Table5-4Lens Shading Correction Registers and Parameters . . . . . . . . . . . . . . . . . . . . . . . 32 Table6-1Output Formatting General Controls . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33 Table6-2RGB:555 and RGB:565 Output Format Controls. . . . . . . . . . . . . . . . . . . . . . . . . . . 33 Table6-3Windowing Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 Table6-4Data Formatting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 Table7-1Output Drive Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38 Table8-1Special Image Effects. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38 Table10-1SCCB Control Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40 Table10-2Device Control Register List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42Version 1.1, December 7, 2004Proprietary to OmniVision Technologies5OV9650 Color CMOS SXGA (1.3 MegaPixel) CameraChip™O仅供试用。

sc网卡接口扩展

s3c2440提供了一个摄像接口,使开发人员很容易地实现摄像、照相等功能。

摄像接口包括8位来自摄像头的输入数据信号,一个输出主时钟信号,三个来自摄像头的输入同步时钟信号和一个输出复位信号。

摄像接口的主时钟信号由USB PLL产生,它的频率为96MHz,再经过分频处理后输出给摄像头,摄像头再根据该时钟信号产生三个同步时钟信号(像素时钟、帧同步时钟和行同步时钟),反过来再输入回s3c2440。

s3c2440仅仅提供了一个摄像接口,因此要实现其功能,还需要摄像头。

在这里,我们使用OV9650。

OV9650内部有大量的寄存器需要配置,这就需要另外的数据接口。

OV9650的数据接口称为SCCB(串行摄像控制总线),它由两条数据线组成:一个是用于传输时钟信号的SIO_C,另一个是用于传输数据信号的SIO_D。

SCCB的传输协议与IIC的极其相似,只不过IIC在每传输完一个字节后,接收数据的一方要发送一位的确认数据,而SCCB一次要传输9位数据,前8位为有用数据,而第9位数据在写周期中是Don’t-Care位(即不必关心位),在读周期中是NA位。

SCCB定义数据传输的基本单元为相(phase),即一个相传输一个字节数据。

SCCB只包括三种传输周期,即3相写传输周期(三个相依次为设备从地址,内存地址,所写数据),2相写传输周期(两个相依次为设备从地址,内存地址)和2相读传输周期(两个相依次为设备从地址,所读数据)。

当需要写操作时,应用3相写传输周期,当需要读操作时,依次应用2相写传输周期和2相读传输周期。

因此SCCB一次只能读或写一个字节。

下面我们就用s3c2440的IIC总线接口分别与OV9650的SIO_C和SIO_D相连接来实现SCCB的功能。

具体的读、写函数为://配置IIC接口rGPEUP = 0xc000。

//上拉无效rGPECON = 0xa0000000。

//GPE15:IICSDA,GPE14:IICSCL//IIC中断void __irq IicISR(void){rSRCPND |= 0x1<<27。

nas965同期使用说明书

您好,尊敬的用户。

恭喜您选择了NAS-965微机自动准同期装置。

贵厂、站配备的这款微机自动准同期装置是我单位开发人员以适合国内电网的运行特点为目的精心设计而成,它融合了以往同期装置的优点并在多项技术方面提出了首创的原理。

该装置简洁明了的操作界面、典雅大方的外型、精巧实用的键盘、可靠的同期性能、多点的同期选择……,必将使您不悔于您的选择。

在仔细阅读了这本用户手册之后,您将对NAS-965微机自动准同期装置的各项菜单操作有深刻了解:全中文菜单具备明显的提示性,辅助功能设置灵活,同期参数修改方便快捷,事件记录记载详细。

NAS-965微机自动准同期装置作为新一代同期产品将为您留下美好深刻的印象。

我们拥有一支优秀的售后服务队伍,您所购买的产品将得到我们时时刻刻的关心。

您的满意是我们国电南自集团的宗旨。

技术咨询请拨打:025-3478110。

国家电力公司南京电力自动化设备总厂南京南自电力控制系统工程公司目录一、概述 (1)二、主要功能及技术参数 (1)2.1 主要功能 (1)2.2 主要技术参数 (1)2.2.1 主要技术数据 (1)2.2.2 大气条件 (2)2.2.3 贮存运输的极限环境温度 (3)2.2.4 周围环境 (3)2.2.5 技术指标 (3)三、安全注意事项 (4)装置上电前接线检查 (4)禁止带电拔插装置插件 (4)禁止带电拔插通信及打印电缆 (4)四、操作说明 (5)4.1 面板布置图 (5)4.2 九键式键盘设置 (5)4.3 菜单结构 (5)4.4 自检 (6)4.5 工作方式介绍 (7)4.5.1试验 (7)4.5.2测量导前时间 (7)4.5.3无压合闸 (7)4.5.4现地同期 (7)4.5.5远方同期 (7)4.6 装置操作 (7)4.7 同期时显示内容及意义 (11)五、输入输出端子及其说明 (12)六、安装与调试 (13)七、维护运行指南 (14)八、订货须知 (16)九、敬告用户 (16)十、附图 (16)一、概述随着计算机技术和超大规模集成电路技术的发展,传统的、模拟的自动准同期装置已远远不能适应当今发电厂、变电站综合自动化的需要,因此,迫切需要一种自动准同期装置,能够配合综合自动化的要求,能够快速地、平稳地、在运行人员不知不觉中将发电机或系统并入运行系统,NAS-965微机自动准同期就是为适应这一要求而设计的。

ov9650芯片原理 -回复

ov9650芯片原理-回复ov9650芯片是一种图像传感器芯片,常用于数字相机、手机摄像头等设备中。

它采用CMOS(Complementary Metal-Oxide-Semiconductor)技术,并具有160万像素的分辨率。

本文将从OV9650芯片的基本原理、工作方式、特性以及应用领域等方面进行介绍。

一、OV9650芯片的基本原理OV9650芯片的基本原理是光电转换技术,也就是将光信号转换成电信号。

光线通过透镜系统进入芯片感光元件,然后感光元件将光线转换成电压信号。

感光元件由很多个光敏元件(也称像素)组成,光线照射在每个像素上时,它们会产生不同程度的电流信号。

这些电流信号会被传感器转换成数字信号,并通过输出接口输出给外部设备。

二、OV9650芯片的工作方式OV9650芯片主要由感光元件、信号处理电路和控制逻辑电路组成。

1. 感光元件:感光元件是芯片的核心部件,它由很多个像素组成,每个像素由光敏元件和微透镜组成。

当光线照射到感光元件上时,光敏元件会产生电荷并积累在各个像素中,电荷的数量与光照强度成正比。

2. 信号处理电路:感光元件产生的电荷信号被传递到信号处理电路进行处理。

信号处理电路主要包括放大器、ADC(Analog-to-Digital Converter)和数字处理单元等。

放大器可放大电荷信号的强度,ADC将模拟信号转换成数字信号,而数字处理单元则对数字信号进行滤波、增强等处理。

3. 控制逻辑电路:控制逻辑电路用于控制芯片的各项功能和工作模式。

它包括时钟控制、时序控制、模式设置等功能。

通过控制逻辑电路,可以调整芯片的曝光时间、图像增益、白平衡等参数。

三、OV9650芯片的特性1. 分辨率高:OV9650芯片具有160万像素的分辨率,可以拍摄出清晰细腻的图像。

2. 低功耗:OV9650芯片采用CMOS技术,功耗较低,适用于移动设备等功耗敏感的应用场景。

3. 高帧率:OV9650芯片支持高达30帧/秒的视频拍摄,可以拍摄出流畅的视频画面。

Camera在linux2.6.35内核下的移植

基于2.6.35内核的OV9650摄像头驱动移植一、移植环境:【移植环境】1、主机:Ubuntu 10.10发行版2、目标机:FS_S5PC100平台3、交叉编译工具:arm-none-linux-gnueabi-4.5.14、摄像头模块:OV96505、Linux文件系统:rootfs. cramfs.6、内核:linux-2.6.35-farsigt二、内核配置1.修改vi drivers/i2c/busses/Kconfig(参考实验二十六I2C驱动编写及测试)修改config I2C_S3C2410tristate "S3C2410 I2C Driver"depends on ARCH_S3C2410 || ARCH_S3C64XXhelpSay Y here to include support for I2C controller in theSamsung S3C2410 based System-on-Chip devices.为:config I2C_S3C2410tristate "S3C2410 I2C Driver"depends on ARCH_S3C2410 || ARCH_S3C64XX || ARCH_S5PC100helpSay Y here to include support for I2C controller in theSamsung S3C2410 based System-on-Chip devices.2.内核配置并重新编译内核$ make menuconfigDevice Drivers ---><*> I2C support ---><*> I2C device interfaceI2C Hardware Bus support ---><*> S3C2410 I2C Driver3.修改vi arch/arm/mach-s5pc100/mach-smdkc100.c查看原理图可以知道我们的摄像头是接在I2C-1上所以修改i2c_devs1添加ov9650的内容,主要是ov9650的地址,这个在芯片手册上可以查到是0x30修改:static struct i2c_board_info i2c_devs1[] __initdata = {};为:static struct i2c_board_info i2c_devs1[] __initdata = {{I2C_BOARD_INFO("ov9650", 0x30),},};添加s5pc100 摄像头控制器平台设备相关内容,这些内容我们可以通过查看S5PC100的芯片手册查到static struct resource s3c_camif_resource[] = {[0] = {.start = 0xEE200000,.end = 0xEE200000 + SZ_1M - 1,.flags = IORESOURCE_MEM,},[1] = {.start = IRQ_FIMC0,.end = IRQ_FIMC0,.flags = IORESOURCE_IRQ,}};static u64 s3c_device_camif_dmamask = 0xffffffffUL;struct platform_device s3c_device_camif = {.name = "s5pc100-camif",.id = 0,.num_resources = ARRAY_SIZE(s3c_camif_resource),.resource = s3c_camif_resource,.dev = {.dma_mask = &s3c_device_camif_dmamask,.coherent_dma_mask = 0xffffffffUL}};EXPORT_SYMBOL(s3c_device_camif);注册摄像头控制平台设备:在smdkc100_devices中添加s3c_device_camifstatic struct platform_device *smdkc100_devices[] __initdata = {&s3c_device_camif, //添加内容};4. 添加驱动(video)Make menuconfigDevice Drivers ---><*> Multimedia support ---><*> Video For Linux[*] Enable Video For Linux API 1 (DEPRECATED) (NEW)[*] Video capture adapters (NEW) --->[*] V4L USB devices (NEW) ---><*> USB Video Class (UVC)[*] UVC input events device support (NEW)<*> USB ZC0301[P] webcam support (DEPRECA TED)三、驱动编写四、网络视频服务器移植对于内核linux-2.6.35,不能再使用servfox,如果要使用的需要修改大量的代码,在此选用新的方法来移植。

OV9650(1.3M)规格书

Advanced Information Preliminary DatasheetO mniTMisionOV9650S1G Color CMOS SXGA (1.3 MegaPixel) with OmniPixel TM TechnologyConcept Camera Module for Socket SolutionGeneral DescriptionKey SpecificationsOV9650S1GColor CMOS SXGA (1.3 MegaPixel) OmniPixel™ Camera ModuleO Functional DescriptionFigure 2 shows the functional block diagram of the OV9650S1G Camera Module. The OV9650S1G includes:•1/4" lens •OV9650 C AMERA C HIP image sensor •Socket connectorFigure 2 Functional Block DiagramFunctional DescriptionOImaging SpecificationsNOTE: OV9650S1G features the OV9650 C AMERA C HIP . Refer to the OV9650 Datasheet for chip-specific information.Table 1Sensor Image FunctionsSensor Imaging Functions DescriptionAuto ExposureModule automatically sets correct exposure time.Auto Exposure ON/OFF Auto exposure can be turned off so the exposure can be set manually.Auto White Balance (AWB)AWB without companion processor interaction.Auto White Balance OFF AWB can be turned off.Color CorrectionIt is possible to adjust for the color filter response of the image sensor as well as for human eye sensitivity.Bayer Pattern Interpolation (Mosaic or equivalent) The interpolation must be done prior to downsizing the image to avoid artifacts due to incorrect interpolation.Electrical Illumination Flicker Elimination Interference from 50Hz or 60Hz illumination can be suppressed with manually set frame rate divider.Gamma Correction Built-in 0.45/1.0Color Space Conversion Bayer raw RGB is converted to YCbCr/YUV color space.Image Size Decimation Size can be altered using the windowing registers. Quarter-format sub-sampling is also provided.Image ON/OFF Image ON/OFF can be controlled by register settings.RGB Output RGB raw data output available.AGC Gain Automatic Gain Control (AGC)White BalanceAutomatic White BalanceTable 2 Output SpecificationsOutput Image FormatsDescriptionOutput Formats SXGA (1280 x 1024 pixels)VGA (640 x 480 pixels)YUV Format 4:2:2 compliant with CCIR656YUV OrderYUYV or UYVYEmbedded Sync Codes Sync signals coded in with data output (CCIR656) or output separately.Data ClippingAccording to CCIR656 or no clipping.Format in Decimation ModePCLK verifies whether or not there is data on every cycle.OV9650S1GColor CMOS SXGA (1.3 MegaPixel) OmniPixel™ Camera ModuleOPin DescriptionNOTE:Y[9:2] for 8-bit YUV or RGB (Y9 MSB, Y2 LSB)Y[9:0] for 10-bit RGB (Y9 MSB, Y0 LSB)Table 3Pin DescriptionPin NumberName Pin Type Function/Description01VSYNC Output Vertical sync output 02HREF Output HREF output 03PCLK Output Pixel clock output04DOVDD Power Digital power supply (V DD-IO = 2.5 to 3.3 VDC) for I/O05RESET Function (default = 0)Clears all registers and resets them to their default values. Active high, internal pull-down resistor.06Y9Output Output bit[9] - MSB for 10-bit RGB and 8-bit YUV 07Y7Output Output bit[7]08Y8Output Output bit[8]09Y6Output Output bit[6]10DGND Power Digital ground11Y1Output Output bit[1] - for 10-bit RGB only 12Y3Output Output bit[3]13Y5Output Output bit[5]14Y4Output Output bit[4]15Y2Output Output bit[2] - LSB for 8-bit YUV 16SIO_D I/O SCCB serial interface data I/O17AVDD Power Analog power supply (V DD-A = 2.45 to 2.8 VDC)18AGND Power Analog ground 19NC–Reserved - no connect20PWDNFunction (default = 0)Power Down Mode Selection - active high, internal pull-down resistor.0:Normal mode1:Power down mode 21SIO_C Input SCCB serial interface clock input22DVDD Power Power supply (V DD-C = 1.8 VDC + 10%) for digital core logic 23XVCLK1Input Crystal clock input24Y0OutputOutput bit[0] - LSB for 10-bit RGB onlyElectrical CharacteristicsOElectrical CharacteristicsNOTE:Exceeding the Absolute Maximum ratings shown above invalidates all AC and DC electrical specifications and may result in permanent device damage.Table 4Absolute Maximum RatingsAmbient Storage Temperature-40ºC to +95ºCSupply Voltages (with respect to Ground)V DD-A4.5 V V DD-C 3 V V DD-IO4.5 VAll Input/Output Voltages (with respect to Ground)-0.3V to V DD-IO +1V Lead Temperature, Surface-mount process +230ºC ESD Rating, Human Body model 2000VTable 5DC Characteristics (-20°C < T A < 70°C)Symbol ParameterConditionMin Typ Max Unit V DD-A DC supply voltage – Analog – 2.45 2.5 2.8V V DD-C DC supply voltage – Core – 1.62 1.8 1.98V V DD-IO DC supply voltage – I/O power – 2.25– 3.6V I DDA Active (Operating) Current See Note a a. V DD-A = 2.5V, V DD-C = 1.8V, V DD-IO = 3.0VI DDA = ∑{I DD-IO + I DD-C + I DD-A }, f CLK = 24MHz at 7.5 fps YUV output, no I/O loading20mA I DDS-SCCB Standby Current See Note b b. V DD-A = 2.5V, V DD-C = 1.8V, V DD-IO = 3.0VI DDS:SCCB refers to a SCCB-initiated Standby, while I DDS:PWDN refers to a PWDN pin-initiated Standby 1mA I DDS-PWDN Standby Current 10µA V IH Input voltage HIGH CMOS0.7 x V DD-IOV V IL Input voltage LOW 0.3 x V DD-IOV V OH Output voltage HIGH CMOS0.9 x V DD-IOV V OL Output voltage LOW 0.1 x V DD-IOV I OH Output current HIGH See Note cc.Standard Output Loading = 25pF, 1.2K Ω8mA I OL Output current LOW 15mA I LInput/Output LeakageGND to V DD-IO ± 1µAOV9650S1G Color CMOS SXGA (1.3 MegaPixel) OmniPixel™ Camera Module OTable 6 Functional and AC Characteristics (-20°C < T A < 70°C)Symbol Parameter Min Typ Max Unit Functional CharacteristicsA/D Differential Non-Linearity+ 1/2LSBA/D Integral Non-Linearity+1LSBAGC Range18dBRed/Blue Adjustment Range12dB Inputs (PWDN, CLK, RESET)f CLK Input Clock Frequency102448MHzt CLK Input Clock Period2142100ns t CLK:DC Clock Duty Cycle455055% t S:RESET Setting time after software/hardware reset1ms t S:REG Settling time for register change (10 frames required)300ms SCCB Timing (see Figure4)f SIO_C Clock Frequency400KHzt LOW Clock Low Period 1.3µs t HIGH Clock High Period600ns t AA SIO_C low to Data Out valid100900ns t BUF Bus free time before new START 1.3µs t HD:STA START condition Hold time600ns t SU:STA START condition Setup time600ns t HD:DAT Data-in Hold time0µs t SU:DAT Data-in Setup time100ns t SU:STO STOP condition Setup time600ns t R, t F SCCB Rise/Fall times300ns t DH Data-out Hold time50ns Outputs (VSYNC, HREF, PCLK, and Y[9:0] (see Figure5, Figure6, Figure7, Figure8, Figure10, and Figure11) t PDV PCLK[↓] to Data-out Valid5ns t SU Y[9:0] Setup time15ns t HD Y[9:0] Hold time8ns t PHH PCLK[↓] to HREF[↑]05ns t PHL PCLK[↓] to HREF[↓]05nsAC Conditions:• V DD: V DD-C = 1.8V, V DD-A = 2.5V, V DD-IO = 3.0V • Rise/Fall Times: I/O: 5ns, MaximumSCCB: 300ns, Maximum • Input Capacitance: 10pf• Output Loading: 25pF, 1.2KΩ to 3V• f CLK: 24MHzTiming SpecificationsOTiming SpecificationsFigure 4 SCCB Timing DiagramOV9650S1G Color CMOS SXGA (1.3 MegaPixel) OmniPixel™ Camera Module OFigure 7 VGA Frame TimingTiming SpecificationsOFigure 10 CIF Frame TimingOV9650S1G Color CMOS SXGA (1.3 MegaPixel) OmniPixel™ Camera Module OFigure 13 RGB 565 Output Timing DiagramRegister Set Table7 shows detailed descriptions of the Device Control registers. The device slave addresses for the OV9650S1G are 60 for write and 61 for read.Table 7 Device Control Register ListAddress (Hex)RegisterNameDefault(Hex)R/W Description00GAIN00RW AGC[7:0] – Gain control gain setting •Range: [00] to [FF]01BLUE80RW AWB – Blue channel gain setting •Range: [00] to [FF]02RED80RW AWB – Red channel gain setting •Range: [00] to [FF]03VREF12RW Vertical Frame ControlBit[7:6]:AGC[9:8] (see register GAIN for AGC[7:0])Bit[5:3]:VREF end low 3 bits (high 8 bits at VSTOP[7:0] Bit[2:0]:VREF start low 3 bits (high 8 bits at VSTRT[7:0]04COM100RW Common Control 1Bit[7]:ReservedBit[6]:CCIR656 formatBit[5]:QQVGA or QQCIF format. Effective only when QVGA or QCIF output is selected (register bit COM7[4]) and relatedHREF skip mode based on format is selected (registerCOM1[3:2])Bit[4]:ReservedBit[3:2]:HREF skip option00:No skip01:YUV/RGB skip every other row for YUV/RGB, skip 2rows for every 4 rows for Raw data1x:Skip 3 rows for every 4 rows for YUV/RGB, skip 6 rowsfor every 8 rows for Raw dataBit[1:0]:AEC low 2 LSB (see registers AECHM for AEC[15:10] and AECH for AEC[9:2])05BAVE00RW U/B Average LevelAutomatically updated based on chip output format06GEAVE00RW Y/Ge Average LevelAutomatically updated based on chip output format07RSVD00–Reserved08RAVE00RW V/R Average LevelAutomatically updated based on chip output format09COM201RW Common Control 2Bit[7:5]:ReservedBit[4]:Soft sleep modeBit[3:2]:ReservedBit[1:0]:Output drive capability00:1x01:2x10:2x11:4x0A PID96R Product ID Number MSB (Read only) 0B VER50R Product ID Number LSB (Read only)0C COM300RW Common Control 3Bit[7]:ReservedBit[6]:Output data MSB and LSB swapBit[5:4]:ReservedBit[3]:Pin selection1:Change RESET pin to EXPST_B (frame exposuremode timing) and change PWDN pin to FREX (frameexposure enable)Bit[2]:VarioPixel for VGA and CIFBit[1]:ReservedBit[0]:Single frame output (used for Frame Exposure mode only)0D COM400RW Common Control 4Bit[7]:VarioPixel for QVGA, QCIF, QQVGA, and QQCIFBit[6]:ReservedBit[5]:Pixels for sub-sampling mode0:Get average neighbor pixel in sub-sampling mode1:Get sum instead of average neghbor pixel insub-sampling modeBit[4:3]:ReservedBit[2]:Tri-state option for output clock at power-down period 0:Tri-state at this period1:No tri-state at this periodBit[1]:Tri-state option for output data at power-down period 0:Tri-state at this period1:No tri-state at this periodBit[0]:Reserved(Hex)Name(Hex)R/W Description0E COM501RW Common Control 5Bit[7]:System clock selection. If the system clock is 48 MHz, this bit should be set to high to get 15 fps for YUV or RGB Bit[6:5]:ReservedBit[4]:Slam mode enable0:Master mode1:Slam mode (used for slave mode)Bit[3]:ADC offset manual control0:Offset is controlled automatically1:Register OFON[7:4] can enable ADC offset addition Bit[2:1]:ReservedBit[0]:Exposure step can be set longer than VSYNC time1:In Normal mode, AEC changes by 1/16 and in Fastmode, AEC changes by double0F COM643RW Common Control 6Bit[7]:Output of optical black line option0:Disable HREF at optical black1:Enable HREF at optical black Bit[6:5]:ReservedBit[4]:HREF is high from optical black lineBit[3]:Enable bias for ADBLCBit[2]:ADBLC offset0:Use 4-channel ADBLC1:Use 2-channel ADBLCBit[1]:Reset all timing when format changes Bit[0]:Enable ADBLC option10AECH40RW Exposure ValueBit[7:0]:AEC[9:2] (see registers AECHM for AEC[15:10] and COM1 for AEC[1:0])11CLKRC00RW Data Format and Internal ClockBit[7]:Digital PLL option0:Disable double clock option, meaning the maximumPCLK can be as high as half input clock1:Enable double clock option, meaning the maximumPCLK can be as high as input clockBit[6]:Use external clock directly (no clock pre-scale available) Bit[5:0]:Internal clock pre-scalarF(internal clock) = F(input clock)/(Bit[5:0]+1)•Range: [0 0000] to [1 1111](Hex)Name(Hex)R/W Description12COM700RW Common Control 7Bit[7]:SCCB Register Reset0:No change1:Resets all registers to default valuesBit[6]:Output format - VGA selectionBit[5]:Output format - CIF selectionBit[4]:Output format - QVGA selectionBit[3]:Output format - QCIF selectionBit[2]:Output format - RGB selectionBit[1]:ReservedBit[0]:Output format - Raw RGB (COM7[2] must be set high)13COM88F RW Common Control 8Bit[7]:Enable fast AGC/AEC algorithmBit[6]:AEC - Step size limit (used only in fast condition and COM5[0] is low)0:Fast condition change maximum step is VSYNC1:Unlimited step sizeBit[5]:Banding filter ON/OFFBit[4]:ReservedBit[3]:Enable AEC time can be less than 1 line optionBit[2]:AGC EnableBit[1]:AWB EnableBit[0]:AEC Enable14COM94A RW Common Control 9Bit[7]:ReservedBit[6:4]:Automatic Gain Ceiling - maximum AGC value000:2x001:4x010:8x011:16x100:32x101:64x110:128xBit[3]:Exposure timing can be less than limit of banding filter when light is too strongBit[2]:Data format - VSYNC drop option0:VSYNC always exists1:VSYNC will drop when frame data drops Bit[1]:Enable drop frame when AEC step is larger than VSYNC Bit[0]:Freeze AGC/AEC(Hex)Name(Hex)R/W Description15COM1000RW Common Control 10Bit[7]:Set pin definition1:Set RESET to SLHS (slave mode horizontal sync) andset PWDN to SLVS (slave mode vertical sync) Bit[6]:HREF changes to HSYNCBit[5]:PCLK output option0:PCLK always output1:No PCLK output when HREF is lowBit[4]:PCLK reverseBit[3]:HREF reverseBit[2]:Reset signal end point optionBit[1]:VSYNC negativeBit[0]:HSYNC negative16RSVD00–Reserved17HSTART1A RW Output Format - Horizontal Frame (HREF column) start high 8-bit (low 3bits are at HREF[2:0])18HSTOP BA RW Output Format - Horizontal Frame (HREF column) end high 8-bit (low 3bits are at HREF[5:3])19VSTRT01RW Output Format - Vertical Frame (row) start high 8-bit (low 2 bits are at VREF[1:0])1A VSTOP81RW Output Format - Vertical Frame (row) end high 8-bit (low 2 bits are at VREF[3:2])1B PSHFT00RW Data Format - Pixel Delay Select (delays timing of the Y[9:0] data relative to HREF in pixel units)•Range: [00] (no delay) to [FF] (256 pixel delay which accounts for whole array)1C MIDH7F R Manufacturer ID Byte – High(Read only = 0x7F) 1D MIDL A2R Manufacturer ID Byte – Low(Read only = 0xA2)1E MVFP00RW Mirror/VFlip EnableBit[7:6]:ReservedBit[5]:Mirror0:Normal image1:Mirror image Bit[4]:VFlip enable0:VFlip disable1:VFlip enable Bit[3:0]:Reserved1F LAEC00RW Reserved20BOS80RW B Channel ADBLC ResultBit[7]:Offset adjustment sign0:Add offset1:Subtract offsetBit[6:0]:Offset value of 10-bit range (high 7 bits)(Hex)Name(Hex)R/W Description21GBOS80RW Gb channel ADBLC resultBit[7]:Offset adjustment sign0:Add offset1:Subtract offsetBit[6:0]:Offset value of 10-bit range22GROS80RW Gr channel ADBLC resultBit[7]:Offset adjustment sign0:Add offset1:Subtract offsetBit[6:0]:Offset value of 10-bit range23ROS80RW R channel ADBLC resultBit[7]:Offset adjustment sign0:Add offset1:Subtract offsetBit[6:0]:Offset value of 10-bit range24AEW78RW AGC/AEC - Stable Operating Region (Upper Limit) 25AEB68RW AGC/AEC - Stable Operating Region (Lower Limit)26VPT D4RW AGC/AEC Fast Mode Operating Region Bit[7:4]:Upper limit of 4 MSBBit[3:0]:Lower limit of 4 LSB27BBIAS80RW B Channel Signal Output Bias (effective only when COM6[0] = 1)Bit[7]:Bias adjustment sign0:Add bias1:Subtract biasBit[6:0]:Bias value of 10-bit range28GbBIAS80RW Gb Channel Signal Output Bias (effective only when COM6[0] = 1) Bit[7]:Bias adjustment sign0:Add bias1:Subtract biasBit[6:0]:Bias value of 10-bit range29Gr_COM00RW Analog BLC and Regulator Control Bit[7:6]:ReservedBit[5]:Bypass Analog BLCBit[4]:Bypass regulatorBit[3:0]:Reserved2A EXHCH00RW Dummy Pixel Insert MSBBit[7:4]: 4 MSB for dummy pixel insert in horizontal direction Bit[3:2]:HSYNC falling edge delay 2 MSBBit[1:0]:HSYNC rising edge delay 2 MSB2B EXHCL00RW Dummy Pixel Insert LSB8 LSB for dummy pixel insert in horizontal direction(Hex)Name(Hex)R/W Description2C RBIAS80RW R Channel Signal Output Bias (effective only when COM6[0] = 1) Bit[7]:Bias adjustment sign0:Add bias1:Subtract biasBit[6:0]:Bias value of 10-bit range2D ADVFL00RW LSB of insert dummy lines in vertical direction (1 bit equals 1 line) 2E ADVFH00RW MSB of insert dummy lines in vertical direction2F YAVE00RW Y/G Channel Average Value30HSYST08RW HSYNC Rising Edge Delay (low 8 bits)31HSYEN30RW HSYNC Falling Edge Delay (low 8 bits)32HREF A4RW HREF ControlBit[7:6]:HREF edge offset to data outputBit[5:3]:HREF end 3 LSB (high 8 MSB at register HSTOP) Bit[2:0]:HREF start 3 LSB (high 8 MSB at register HSTART)33CHLF00RW Bit[7:0]:Reserved 34ARBLM03RW Bit[7:0]:Reserved 35-36RSVD XX–Reserved37ADC04RW Bit[7:0]:Reserved 38ACOM12RW Bit[7:0]:Reserved39OFON00RW Bit[7:4]:ReservedBit[3]:Line buffer power down - must be set to "1" before chip power downBit[2:0]:Reserved3A TSLB0C RW Line Buffer Test OptionBit[7:6]:ReservedBit[5]:Bit-wise reverseBit[4]:UV output value0:Use normal UV output1:Use fixed UV value set in registers MANU and MANVas UV output instead of chip outputBit[3]:Output sequence is Y U Y V instead of U Y V YBit[2]:Output sequence is Y V Y U instead of Y U Y VBit[1]:ReservedBit[0]:Digital BLC(Hex)Name(Hex)R/W Description3B COM1100RW Common Control 11Bit[7]:Night mode0:Night mode disable1:Frame rate will adjust based on COM11[6:5] beforeAGC gain increases more than 2. Also,ADVFL andADVFL will be automatically updated.Bit[6:5]:Night mode insert frame option00:Normal frame rate01:1/2 frame rate10:1/4 frame rate11:1/8 frame rateBit[4:3]:Average calculation window option00:Use full frame01:Use half frame10:Use quarter frame11:Use lower two-thirdsBit[2:1]:ReservedBit[0]:Manual banding filter mode3C COM1240RW Common Control 12Bit[7]:HREF option0:No HREF when VREF is low1:Always has HREFBit[6:3]:ReservedBit[2]:Enable YUV averageBit[1:0]:Reserved3D COM1399RW Common Control 13Bit[7:6]:Gamma selection for signal00:No gamma function01:Gamma used for Y channel only10:Gamma used for Raw data before interpolation11:Not allowedBit[5]:ReservedBit[4]:Enable color matrix for RGB or YUVBit[3]:Enable Y channel delay option0:Delay UV channel1:Delay Y channelBit[2:0]:Output Y/UV delay3E COM140E RW Common Control 14Bit[7:2]:ReservedBit[1]:Enable edge enhancement for YUV output (effective only for YUV/RGB, no use for Raw data)Bit[0]:Edge enhancement option0:Edge enhancement factor = EDGE[3:0]1:Edge enhancement factor = 2 x EDGE[3:0](Hex)Name(Hex)R/W Description3F EDGE88RW Edge Enhancement AdjustmentBit[7:4]:Edge enhancement threshold[3:0](see register COM22[7:6} for Edge threshold[5:4]) Bit[3:0]:Edge enhancement factor40COM15C0RW Common Control 15Bit[7:6]:Data format - output full range enable0x:Output range: [10] to [F0]10:Output range: [01] to [FE]11:Output range: [00] to [FF]Bit[5:4]:RGB 555/565 option (must set COM7[2] high) x0:Normal RGB output01:RGB 56511:RGB 555Bit[3]:Swap R/B in RGB565/RGB555 formatBit[2:0]:Reserved41COM1610RW Common Control 16Bit[7:2]:ReservedBit[1]:Color matrix coefficient double option Bit[0]:Reserved42COM1708RW Common Control 17Bit[7:5]:ReservedBit[4]:Edge enhancement optionBit[3]:ReservedBit[2]:Select single frame outBit[1]:Tri-state outputBit[0]:Reserved43-4E RSVD XX–Reserved4F MTX158RW Matrix Coefficient 1 50MTX248RW Matrix Coefficient 2 51MTX310RW Matrix Coefficient 3 52MTX428RW Matrix Coefficient 4 53MTX548RW Matrix Coefficient 5 54MTX670RW Matrix Coefficient 6 55MTX740RW Matrix Coefficient 7 56MTX840RW Matrix Coefficient 8 57MTX940RW Matrix Coefficient 958MTXS0F RW Matrix Coefficient Sign for coefficient 9 to 2 0:Plus1:Minus59-61RSVD XX–Reserved(Hex)Name(Hex)R/W Description62LCC100RW Lens Correction Option 163LCC200RW Lens Correction Option 264LCC310RW Lens Correction Option 365LCC480RW Lens Correction Option 466LCC500RW Lens Correction Control67MANU80RW Manual U Value (effective only when register TSLB[4] is high) 68MANV80RW Manual V Value (effective only when register TSLB[4] is high)69HV00RW Manual Banding Filter MSBBit[7:1]:ReservedBit[0]:Matrix coefficient 1 sign6A MBD00RW LSB of Banding Filter Value (effective only when COM11[0] is high). 6B DBLV0A RW Bit[7:0]:Reserved6C-7B GSP XX RW Gamma curve7C-8A GST XX RW Gamma curve8B COM2104RW Common Control 21Bit[7:4]:ReservedBit[3]:VGA option - use VGA window modeBit[2]:ReservedBit[1]:Digital BLC optionBit[0]:UV channel uses sum or average of neighbor pixel in sub-sampling mode8C COM2200RW Common Control 22Bit[7:6]:Edge enhancement threshold[5:4](see register EDGE[7:4} for Edge threshold[3:0]) Bit[5]:De-noise enableBit[4:2]:ReservedBit[1]:White-pixel erase enableBit[0]:White-pixel erase option8D COM2300RW Common Control 23Bit[7:5]:ReservedBit[4]:Color bar test modeBit[3:2]:ReservedBit[1]:Digital AWB enableBit[0]:Reserved8E COM2400RW Common Control 24Bit[7:0]:Reserved(Hex)Name(Hex)R/W DescriptionRegister SetO8F DBLC10F RWDigital BLC Offset SignBit[7:4]:ReservedBit[3]:Digital BLC B offset sign Bit[2]:Digital BLC R offset sign Bit[1]:Digital BLC Gb offset sign Bit[0]:Digital BLC Gr offset sign90DBLC_B 00RWDigital BLC B Channel Offset ValueBit[7:0]:Digital BLC B channel offset value91DBLC_R 00RWDigital BLC R Channel Offset ValueBit[7:0]:Digital BLC R channel offset value92DM_LNL 00RWDummy Line low 8 bitsBit[7:0]:Control insert Dummy line[7:0]93DM_LNH 00RW Dummy Line high 8 bitsBit[7:0]:Control insert Dummy line[15:8]94-9C RSVD XX –Reserved9D LCCFB 00RW Lens Correction B Channel Control 9E LCCFR 00RW Lens Correction R Channel Control 9FDBLC_Gb00RWDigital BLC Gb Channel Offset ValueBit[7:0]:Digital BLC Gb channel offset value A0DBLC_Gr 00RWDigital BLC Gr Channel Offset ValueBit[7:0]:Digital BLC Gr channel offset valueA1AECHM40RWExposure Value - AEC MSB 5 bitsBit[7:6]:ReservedBit[5:0]:AEC[15:10] (see registers AECH for AEC[9:2] and COM1 for AEC[1:0])A2-A3RSVD XX –ReservedA4COM2500RWCommon Control 25Bit[7:0]:ReservedA5COM2600RWCommon Control 26Bit[7:0]:ReservedA6G_GAIN 80RWGreen Gain OptionBit[7:0]:Green gain when using digital AWBA7VGA_ST 14RW Vertical Start Point for VGABit[7:0]:Define vertical start point in VGA sub-windowing modeA8-AAACOMXX–ReservedNOTE: All other registers are factory-reserved. Please contact OmniVision Technologies for reference register settings.Table 7Device Control Register List (Continued)Address (Hex)Register NameDefault (Hex)R/WDescription8.008.00AA1.50s4.507.20s6.20SECTION A-ALensLens HolderKey for image orientationPCBImage PlaneImage Sensor6.606.607.8010.204.50Module shown installed in the socketPackage SpecificationsOMechanical SpecificationsConnector InformationThe OV9650S1G uses a 24-pin socket connector. Table 9 shows a listing of some recommended connectors.Optical SpecificationsTable 8Mechanical DimensionsParameterSpecification CommentsSensor 5.1 mm x 5.72 mm CMOS in housingLensGlass/Plastic Connection Type 10.2 x 10.2 x 4.5 mm SMK socket (consult OmniVision for details)Module Housing8 mm x 8 mm x 7.20 mmTable 9 Recommended ConnectorsManufacturerPart No.DescriptionSMKCLE9024-0201E CLE9024-0301F T-54-10499T-347379-JIGUSocket connector Shield case (optional)Socket without locking mechanism (for testing purposes)Module extraction jigTable 10Optical SpecificationsParameterSpecification CommentsLens Elements Glass/Plastic Hybrid1 glass, 3 plastic (aspheric) fixed focusViewing Angle 60° diagonal Focal Length 4.7 mm F Number 2.8Focus Range 30 cm → ∞FilterIR cut IncludedMount Description M7 x 0.35P TV Distortion 0.51%Focus AdjustmentFixed80 cmOV9650S1GColor CMOS SXGA (1.3 MegaPixel) OmniPixel™ Camera ModuleOHandling Precautions•DO NOT try to open the unit enclosure as there is no user-serviceable component inside.•To prevent damage to the camera module by electrostatic discharge, handle the camera module ONLY after discharging ALL static electricity from yourself and ensuring a static-free environment for the camera module.•DO NOT touch the top surface of the lens.•DO NOT press down on the lens.•DO NOT try to focus the lens.•DO NOT put the camera module in a dusty environment.•To reduce the risk of electrical shock and damage to the camera module, turn OFF the power before connect and disconnect the camera module.•DO NOT drop the camera module more than 60 cm onto any hard surface.•To prevent fire or shock hazard, DO NOT expose camera module to rain or moisture.•DO NOT expose camera module to direct sunlight.•DO NOT put camera module in a high temperature environment.•DO NOT use liquid or aerosol cleaners to clean the lens.•DO NOT make any changes or modifications to camera module.•DO NOT subject camera module to strong electromagnetic field.•DO NOT subject the camera module to excessive vibration or shock.WARNING: READ THIS FIRST!Prior to handling any OmniVision camera module, read the following precautions.Handling PrecautionsONote:•All information shown herein is current as of the revision and publication date. Please refer to the OmniVision web site ( ) to obtain the current versions of all documentation.•OmniVision Technologies, Inc. reserves the right to make changes to their products or todiscontinue any product or service without further notice (It is advisable to obtain current product documentation prior to placing orders).•Reproduction of information in OmniVision product documentation and specifications is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. In such cases, OmniVision is not responsible or liable for any information reproduced.•This document is provided with no warranties whatsoever, including any warranty of merchantability, non-infringement, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification or sample. Furthermore, OmniVision Technologies Inc. disclaims all liability, including liability for infringement of any proprietary rights, relating to use of information in this document. No license, expressed or implied, by estoppels or otherwise, to any intellectual property rights is granted herein.•‘OmniVision’, ‘CameraChip’, and ’OmniPixel’ are trademarks of OmniVision Technologies, Inc. All other trade, product or service names referenced in this release may be trademarks orregistered trademarks of their respective holders. Third-party brands, names, and trademarks are the property of their respective owners.For further information, please feel free to contact OmniVision at info@ .OmniVision Technologies, Inc.1341 Orleans Drive Sunnyvale, CA USA (408) 542-3000OV9650S1G Color CMOS SXGA (1.3 MegaPixel) OmniPixel™ Camera Module O。

GC65_硬件设计手册_V1.0(1)

e tia 3.3.3. 供电参考电路............................................................................................................... 20

上海移远通信技术有限公司

1 / 68

GC65 硬件设计手册

文档历史

修订记录

版本 1.0

日期

CQouneficdteenl tial 2013-09-16

作者 郝竹青

变更表述 初始版本

上海移远通信技术有限公司

2 / 68

GC65 硬件设计手册

目录

文档历史 ........................................................................................................................................................ 2 目录 ............................................................................................................................................................... 3 表格索引 ........................................................................................................................................................ 5 图片索引 ........................................................................................................................................................ 6

OV9650寄存器配置详解

OV9650寄存器配置之YUV Setting:******************************************************************************* VGA mode******************************************************************************* write_SCCB(0x12, 0x80); //CommonControl;Reset all registers to default valueswrite_SCCB(0x11, 0x81); //Data Format and Internal Clock;Enable double clock option,//meaning the maximum PCLK can be as high as input clock;//Internal clock pre-scalar=00001write_SCCB(0x6b, 0x0a); //DBLV,Reservedwrite_SCCB(0x6a, 0x3e); //Manual Banding Filter Value(effective only when COM11[0] is high)write_SCCB(0x3b, 0x09);write_SCCB(0x13, 0xe0);write_SCCB(0x01, 0x80);write_SCCB(0x02, 0x80);write_SCCB(0x00, 0x00);write_SCCB(0x10, 0x00);write_SCCB(0x13, 0xe5);//write_SCCB(0x39, 0x43);//50 for30fpswrite_SCCB(0x38, 0x12);//92 for30fpswrite_SCCB(0x37, 0x00);write_SCCB(0x35, 0x91);//81 for30fpswrite_SCCB(0x0e, 0x20);write_SCCB(0x1e, 0x04);//write_SCCB(0xa8, 0x80);write_SCCB(0x12, 0x40);write_SCCB(0x04, 0x00);write_SCCB(0x0c, 0x04);write_SCCB(0x0d, 0x80);write_SCCB(0x18, 0xc6);write_SCCB(0x17, 0x26);write_SCCB(0x32, 0xad);write_SCCB(0x03, 0x00);write_SCCB(0x1a, 0x3d);write_SCCB(0x19, 0x01);write_SCCB(0x3f, 0xa6);write_SCCB(0x14, 0x2e);write_SCCB(0x15, 0x02);write_SCCB(0x41, 0x02);//write_SCCB(0x1b, 0x00);write_SCCB(0x16, 0x06);write_SCCB(0x33, 0xe2);//c0 forinternalregulatorwrite_SCCB(0x34, 0xbf);write_SCCB(0x96, 0x04);write_SCCB(0x3a, 0x00);write_SCCB(0x8e, 0x00);//write_SCCB(0x3c, 0x77);write_SCCB(0x8b, 0x06);write_SCCB(0x94, 0x88);write_SCCB(0x95, 0x88);write_SCCB(0x40, 0xc1);write_SCCB(0x29, 0x3f);//2fforinternalregulatorwrite_SCCB(0x0f, 0x42);//write_SCCB(0x3d, 0x92);write_SCCB(0x69, 0x40);write_SCCB(0x5c, 0xb9);write_SCCB(0x5d, 0x96);write_SCCB(0x5e, 0x10);write_SCCB(0x59, 0xc0);write_SCCB(0x5a, 0xaf);write_SCCB(0x5b, 0x55);write_SCCB(0x43, 0xf0);write_SCCB(0x44, 0x10);write_SCCB(0x45, 0x68);write_SCCB(0x46, 0x96);write_SCCB(0x47, 0x60);write_SCCB(0x48, 0x80);write_SCCB(0x5f, 0xe0);write_SCCB(0x60, 0x8c);//0cforadvanced AWB(related to lens) write_SCCB(0x61, 0x20);write_SCCB(0xa5, 0xd9);write_SCCB(0xa4, 0x74);write_SCCB(0x8d, 0x02);write_SCCB(0x13, 0xe7);//write_SCCB(0x4f, 0x3a);write_SCCB(0x50, 0x3d);write_SCCB(0x51, 0x03);write_SCCB(0x52, 0x12);write_SCCB(0x54, 0x38);write_SCCB(0x55, 0x40);write_SCCB(0x56, 0x40);write_SCCB(0x57, 0x40);write_SCCB(0x58, 0x0d);//write_SCCB(0x8c, 0x23);write_SCCB(0x3e, 0x02);write_SCCB(0xa9, 0xb8);write_SCCB(0xaa, 0x92);write_SCCB(0xab, 0x0a);//write_SCCB(0x8f, 0xdf);write_SCCB(0x90, 0x00);write_SCCB(0x91, 0x00);write_SCCB(0x9f, 0x00);write_SCCB(0xa0, 0x00);write_SCCB(0x3a, 0x01);//write_SCCB(0x24, 0x70);write_SCCB(0x25, 0x64);write_SCCB(0x26, 0xc3);//write_SCCB(0x2a, 0x00);//10 for50Hz??? // Dummy Pixel Insert MSB// Bit[6:4]: 3 MSB for dummy pixel insert in horizontal direction//Bit[3:2]: HSYNC falling edge delay 2 MSB//Bit[1:0]: HSYNC rising edge delay 2 MSBwrite_SCCB(0x2b, 0x00);//40 for50Hz??? // Dummy Pixel Insert LSB//8 LSB for dummy pixel insert in horizontal direction////gammawrite_SCCB(0x6c, 0x40); //GSP; 6C-7B: Gamma curve(Gamma曲线)write_SCCB(0x6d, 0x30);write_SCCB(0x6e, 0x4b);write_SCCB(0x6f, 0x60);write_SCCB(0x70, 0x70);write_SCCB(0x71, 0x70);write_SCCB(0x72, 0x70);write_SCCB(0x73, 0x70);write_SCCB(0x74, 0x60);write_SCCB(0x75, 0x60);write_SCCB(0x76, 0x50);write_SCCB(0x77, 0x48);write_SCCB(0x79, 0x2e);write_SCCB(0x7a, 0x28);write_SCCB(0x7b, 0x22);write_SCCB(0x7c, 0x04);//GST; 7C-8A: Gamma curvewrite_SCCB(0x7d, 0x07);write_SCCB(0x7e, 0x10);write_SCCB(0x7f, 0x28);write_SCCB(0x80, 0x36);write_SCCB(0x81, 0x44);write_SCCB(0x82, 0x52);write_SCCB(0x83, 0x60);write_SCCB(0x84, 0x6c);write_SCCB(0x85, 0x78);write_SCCB(0x86, 0x8c);write_SCCB(0x87, 0x9e);write_SCCB(0x88, 0xbb);write_SCCB(0x89, 0xd2);write_SCCB(0x8a, 0xe6);******************************************************************************* SXGA mode******************************************************************************* write_SCCB(0x12, 0x80); //Reset all registers to default values;write_SCCB(0x11, 0x80); //Data Format and Internal Clock;Enable double clock option,//meaning the maximum PCLK can be as high as input clock;//Internal clock pre-scalar=00000write_SCCB(0x6b, 0x0a); //Reservedwrite_SCCB(0x6a, 0x41); //Manual Banding Filter Value(effective only when COM11[0]is high) write_SCCB(0x3b, 0x09); //light mode disable;//Average calculation window option: Use half frame//Manual banding filter mode[COM11]write_SCCB(0x13, 0xe0); //Enable fast AGC/AEC algorithm//Unlimited AEC step size//Banding filter ONwrite_SCCB(0x01, 0x80); //AWB-Blue channel gain setting:80write_SCCB(0x02, 0x80); //AWB-Red channel gain setting:80write_SCCB(0x00, 0x00); //AGC[7:0]-Gain control gain setting:00write_SCCB(0x10, 0x00); //Exposure Value AEC[9:2]:00write_SCCB(0x13, 0xe5); //AGC enable; AEC enable//write_SCCB(0x39, 0x43);//50 for15fps??// (Line buffer power down-must be set to ‘1’ before chip power down) write_SCCB(0x38, 0x12);//93 for15fps???//ACOM; Reservedwrite_SCCB(0x37, 0x00); //ADC; Reservedwrite_SCCB(0x35, 0x91);//81 for15fps???//RSVD; Reservedwrite_SCCB(0x0e, 0x20); //Master mode//Bit[7]: system clock selection. If the system clock is 48MHz, this bit//should be set to high to get 15fps for YUV or RGBwrite_SCCB(0x1e, 0x04); //Mirror/VFlipEnabe: Normal image, VFlip disable//write_SCCB(0xa8, 0x80); //ACOM; Reservedwrite_SCCB(0x12, 0x00); //COM7; SCCB Register no changewrite_SCCB(0x04, 0x00); //COM1; do nothing(HREF No Skip)write_SCCB(0x0c, 0x00);//COM3; do nothingwrite_SCCB(0x0d, 0x00); //COM4; Tri-state for output clock and data at power-down period write_SCCB(0x18, 0xbd);//HSTOP; Output format//Horizontal Frame(HREF column) end high 8-bit(low 3 bits are at HREF[5:3]) write_SCCB(0x17, 0x1d);//HSTART; Output format//Horizontal Frame(HREF column) end high 8-bit(low 3 bits are at HREF[2:0]) write_SCCB(0x32, 0xad); //HREF Control//Bit[7:6]: HREF edge offset to data output//Bit[5:3]: HREF end 3 LSB(high 8 MSB at register HSTOP)//Bit[2:0]: HREF start 3 LSB(high 8 MSB at register HSTART)write_SCCB(0x03, 0x12); //Vertical Frame Control//Bit[7:6]: AGC[9:8] (see register GAINfor AGC[7:0])//Bit[5:3]: VREF end low 3 bits (high 8 bits at VSTOP[7:0]//Bit[2:0]: VREF start low 3 bits (high 8 bits at VSTRT[7:0]write_SCCB(0x1a, 0x81);//VSTOP; Output Format//Vertical Frame (row) end high 8-bit (low 3 bits are at VREF[5:3]) write_SCCB(0x19, 0x01);//VSATRT; Output Format//Vertical Frame (row) start high 8-bit (low 3 bits are at VREF[2:0]) write_SCCB(0x14, 0x2e); //COM9; Automatic Gain Ceiling-maximum AGC value:8x//Exposure timing can be less than limit of banding filter when light is to strong//Data format-VSYNC will drop when frame data drops//Enable drop frame when AEC step is larger than the Exposure Gapwrite_SCCB(0x15, 0x00); //COM10; PCLK always outputwrite_SCCB(0x3f, 0xa6); //Edge Enhancement Adjustment//Bit[7:4]: Edge enhancement threshold[3:0]//(see register COM22[7:6} for Edge threshold[5:4])//Bit[3:0]: Edge enhancement factorwrite_SCCB(0x41, 0x02); //COM16; Color matrix coefficient double optionwrite_SCCB(0x42, 0x08); //COM17; do nothing//write_SCCB(0x1b, 0x00); //Data Format//Pixel Delay Select (delays timing of the D[9:0] data relative to HREF in pixel units)//•Range: [00] (no delay) to [FF] (256 pixel delay which accounts for whole array) write_SCCB(0x16, 0x06);//Reservedwrite_SCCB(0x33, 0xe2);//c0 forinternalregulator???//Reservedwrite_SCCB(0x34, 0xbf);//Reservedwrite_SCCB(0x96, 0x04);//Reservedwrite_SCCB(0x3a, 0x00); //Line Buffer Test Option//Use normal UV output//Output sequence is Y U Y V//Digital BLC disablewrite_SCCB(0x8e, 0x00);//Reserved//write_SCCB(0x3c, 0x77); //No HREF when VREF is low//Enable UV averagewrite_SCCB(0x8b, 0x06);//Reservedwrite_SCCB(0x94, 0x88);//Reservedwrite_SCCB(0x95, 0x88);//Reservedwrite_SCCB(0x40, 0xc1);//Data format-output full range enable:[00]to[FF]//RGB 555/565 option(must set COM7[2]high):Normal RGB output write_SCCB(0x29, 0x3f); //fforinternalregulator??? //Analog BLC and Regulator Control//Bypass Analog BLC//Bypass regulatorwrite_SCCB(0x0f, 0x42);//Disable HREF at optical black//Use 4-channel ADBLC//Reset all timing when format changes//write_SCCB(0x3d, 0x92); //Gamma used for Raw data before interpolation//Enable color matrix for RGB or YUV//Delay UV channel, output UV delay[2:0]=0x02write_SCCB(0x69, 0x40); //HV, Manual Banding Filter MSB , do nothingwrite_SCCB(0x5c, 0xb9);//Reservedwrite_SCCB(0x5d, 0x96); //Reservedwrite_SCCB(0x5e, 0x10);//Reservedwrite_SCCB(0x59, 0xc0); //Reservedwrite_SCCB(0x5a, 0xaf);//Reservedwrite_SCCB(0x5b, 0x55); //Reservedwrite_SCCB(0x43, 0xf0); //Reservedwrite_SCCB(0x44, 0x10); //Reservedwrite_SCCB(0x45, 0x68); //Reservedwrite_SCCB(0x46, 0x96); //Reservedwrite_SCCB(0x47, 0x60); //Reservedwrite_SCCB(0x48, 0x80); //Reservedwrite_SCCB(0x5f, 0xe0); //Reservedwrite_SCCB(0x60, 0x8c);//0cforadvanced AWB(Related to lens)??? //Reserved write_SCCB(0x61, 0x20); //Reservedwrite_SCCB(0xa5, 0xd9); //Reservedwrite_SCCB(0xa4, 0x74); //Reservedwrite_SCCB(0x8d, 0x02); //Color gain optin:Digitalwrite_SCCB(0x13, 0xe7); //Enable fast AGC/AEC algorithm//AEC-Step size limit: Unlimited step size//Banding filter ON//AGC enable; AWB enable; AEC enable//write_SCCB(0x4f, 0x3a); //Matrix Coefficient 1write_SCCB(0x50, 0x3d);//Matrix Coefficient 2write_SCCB(0x51, 0x03); //Matrix Coefficient 3write_SCCB(0x52, 0x12); //Matrix Coefficient 4write_SCCB(0x53, 0x26); //Matrix Coefficient 5write_SCCB(0x54, 0x38); //Matrix Coefficient 6write_SCCB(0x55, 0x40); //Matrix Coefficient 7write_SCCB(0x56, 0x40); //Matrix Coefficient 8write_SCCB(0x57, 0x40);//Matrix Coefficient 9write_SCCB(0x58, 0x0d); //Matrix Coefficient Sign for coefficient 9 to 2//write_SCCB(0x8c, 0x23); //Edge enhancement threshold[5:4]//(see register EDGE[7:4] for Edge threshold[3:0])//De-noise enable(去噪)//White-pixel erase enable//White-pixel erase option: bit[0]=1write_SCCB(0x3e, 0x02); //Enable edge enhancement for YUV output//(effective only for YUV/RGB, no use for Raw data)//Edge enhancement factor = EDGE[3:0]write_SCCB(0xa9, 0xb8);//Reservedwrite_SCCB(0xaa, 0x92);//Reservedwrite_SCCB(0xab, 0x0a);//No this register!!!//write_SCCB(0x8f, 0xdf); //Bit[3]: Digital BLC B offset sign// Bit[2]: Digital BLC R offset sign// Bit[1]: Digital BLC Gb offset sign// Bit[0]: Digital BLC Gr offset signwrite_SCCB(0x90, 0x00); //Digital BLC B Channel Offset Value[7:0]=0x00 write_SCCB(0x91, 0x00); //Digital BLC R channel offset value Bit[7:0]=0x00 write_SCCB(0x9f, 0x00); //Digital BLC Gb channel offset value Bit[7:0]=0x00 write_SCCB(0xa0, 0x00); //Digital BLC Gr channel offset value Bit[7:0]=0x00 write_SCCB(0x3a, 0x01); //Digital BLC enable//write_SCCB(0x24, 0x70); //AGC/AEC-Stable Operating Region(Upper Limit)write_SCCB(0x25, 0x64); //AGC/AEC-Stable Operating Region(Lower Limit)write_SCCB(0x26, 0xc3); //AGC/AEC Fast Mode Operating Region//Bit[7:4]: High nibble of upper limit//Bit[3:0]: High nibble of lower limit//write_SCCB(0x2a, 0x00);//10 for50Hz??? // Dummy Pixel Insert MSB//Bit[6:4]: 3 MSB for dummy pixel insert in horizontal direction//Bit[3:2]: HSYNC falling edge delay 2 MSB//Bit[1:0]: HSYNC rising edge delay 2 MSBwrite_SCCB(0x2b, 0x00);//34 for50Hz??? //Dummy Pixel Insert LSB//8 LSB for dummy pixel insert in horizontal direction////gammawrite_SCCB(0x6c, 0x40);//GSP; 6C-7B: Gamma curve(Gamma曲线)write_SCCB(0x6d, 0x30);write_SCCB(0x6e, 0x4b);write_SCCB(0x6f, 0x60);write_SCCB(0x70, 0x70);write_SCCB(0x71, 0x70);write_SCCB(0x72, 0x70);write_SCCB(0x73, 0x70);write_SCCB(0x74, 0x60);write_SCCB(0x75, 0x60);write_SCCB(0x76, 0x50);write_SCCB(0x77, 0x48);write_SCCB(0x78, 0x3a);write_SCCB(0x79, 0x2e);write_SCCB(0x7a, 0x28);write_SCCB(0x7b, 0x22);write_SCCB(0x7c, 0x04);//GST; 7C-8A: Gamma curvewrite_SCCB(0x7d, 0x07);write_SCCB(0x7e, 0x10);write_SCCB(0x7f, 0x28);write_SCCB(0x80, 0x36);write_SCCB(0x81, 0x44);write_SCCB(0x82, 0x52);write_SCCB(0x83, 0x60);write_SCCB(0x84, 0x6c);write_SCCB(0x85, 0x78);write_SCCB(0x86, 0x8c);write_SCCB(0x87, 0x9e);write_SCCB(0x88, 0xbb);write_SCCB(0x89, 0xd2);write_SCCB(0x8a, 0xe6);******************************************************************************* VGAchangeto SXGA******************************************************************************* write_SCCB(0x11, 0x80);write_SCCB(0x12, 0x00);write_SCCB(0x0c, 0x00);write_SCCB(0x0d, 0x00);write_SCCB(0x18, 0xbe);write_SCCB(0x17, 0x1e);write_SCCB(0x32, 0xbf);write_SCCB(0x03, 0x12);write_SCCB(0x1a, 0x81);write_SCCB(0x19, 0x01);write_SCCB(0x2a, 0x10);//24Mclockwrite_SCCB(0x2b, 0x34);//24Mclockwrite_SCCB(0x6a, 0x41);//24Mclock******************************************************************************* SXGA change to VGA******************************************************************************* write_SCCB(0x11, 0x81);write_SCCB(0x12, 0x40);write_SCCB(0x0c, 0x04);write_SCCB(0x0d, 0x80);write_SCCB(0x18, 0xc7);write_SCCB(0x17, 0x27);write_SCCB(0x32, 0xad);write_SCCB(0x03, 0x00);write_SCCB(0x1a, 0x3d);write_SCCB(0x19, 0x01);write_SCCB(0x6a, 0x3e);write_SCCB(0x11, 0x81);//for24Mclockwrite_SCCB(0x2a, 0x10);//for24Mclockwrite_SCCB(0x2b, 0x40);//for24Mclock。

OsiSense XUY PS1LCO965S 红外光传感器数据手册说明书

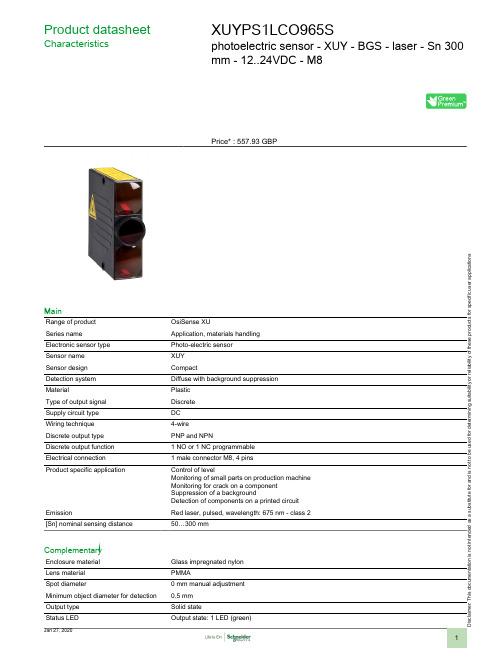

Product datasheetCharacteristicsXUYPS1LCO965Sphotoelectric sensor - XUY - BGS - laser - Sn 300mm - 12..24VDC - M8Price* : 557.93 GBPMainRange of product OsiSense XUSeries nameApplication, materials handling Electronic sensor type Photo-electric sensor Sensor name XUY Sensor design CompactDetection system Diffuse with background suppression MaterialPlastic Type of output signal Discrete Supply circuit type DC Wiring technique 4-wire Discrete output type PNP and NPNDiscrete output function 1 NO or 1 NC programmable Electrical connection 1 male connector M8, 4 pinsProduct specific applicationControl of levelMonitoring of small parts on production machine Monitoring for crack on a component Suppression of a backgroundDetection of components on a printed circuit EmissionRed laser, pulsed, wavelength: 675 nm - class 2[Sn] nominal sensing distance50…300 mmComplementaryEnclosure material Glass impregnated nylon Lens material PMMASpot diameter0 mm manual adjustment Minimum object diameter for detection 0.5 mm Output type Solid stateStatus LEDOutput state: 1 LED (green)i s c l a i m e r : T h i s d o c u m e n t a t i o n i s n o t i n t e n d e d a s a s u b s t i t u t e f o r a n d i s n o t t o b e u s e d f o r d e t e r m i n i n g s u i t a b i l i t y o r r e l i a b i l i t y o f t h e s e p r o d u c t s f o r s p e c i f i c u s e r a p p l i c a t i o n sNC function: 1 LED (none)NO function: 1 LED (red)Time delay active: 1 LED (red)[Us] rated supply voltage12...24 V DC with reverse polarity protectionSupply voltage limits10…30 V DCSwitching capacity in mA100 mA (overload and short-circuit protection)Switching frequency> 5 kHzMaximum voltage drop<2 V (closed state)Current consumption35 mAMaximum delay response40 ms for output circuit depending on wiringMaximum delay recovery150 µsSetting-up Manual adjustment of focusingProduct weight0.081 kgEnvironmentProduct certifications CULusCEAmbient air temperature for operation0…50 °CAmbient air temperature for storage-20…60 °CImmunity to ambient light10000 lux natural light500 lux incandescent bulbIP degree of protection IP65 conforming to IEC 60529Offer SustainabilitySustainable offer status Green Premium productEU RoHS Directive Pro-active compliance (Product out of EU RoHS legal scope)EU RoHS DeclarationMercury free YesRoHS exemption information YesEnvironmental Disclosure Product Environmental ProfileCircularity Profile End of Life InformationContractual warrantyWarranty18 months。

9651b安全性能综合测试仪用户手册

本仪器到达工作位置后,不要接任何测试线,接通测试仪电源进行自检。

1)自检通过后逐一设置测试项,启动测试,观察各测试项显示情况:

接地因开路而报警;绝缘显示设置电压,电阻大于1kMΩ;耐压显示设置电压,漏电流有较小零点;泄漏显示负载电压,有较小电流零点;功率、启动测试为零而报警。

2)若有异常现象,如不启动、无显示、无键响应、无继电器动作或无电压电流输出,请打开机壳,检查保险丝是否完好和各连接电缆连接是否良好。确认检查完好后再次开机启动。

2

1.测试迅速

本系列测试仪以Intel 16位微控制器为核心,测试通道实时捕获被测设备在测试过程中各参数变化情况,几秒钟内准确完成一项测试,最短在十秒内完成全部项目测试,能满足生产线对测试时间的要求。

2.输出方式先进

本系列测试仪摒弃了传统仪表自耦变压器调节输出信号的方法,采用正弦脉宽调制(SPWM)技术产生50Hz或60Hz标准正弦波,经大功率MOS管驱动输出,实现了高电压和大电流的无触点调节,大大提高了仪器的可靠性。

5)测试

设置完毕后,将被测负载电源插头插在接线盒上(注意根据负载选择接线盒上的插座),测试夹夹住被测负载金属外壳。确认接线无误后,按启动键启动测试。下一次测试若不改变测试项,只须按启动键即可。

6)关机

测试仪在关机前应先按停止键退出测试状态,去掉测试盒上的被测电器,断开后面板上的空气开关,然后关断测试仪前面板上的电源开关。

当光标移至每行行首或行尾时用左移键或右移键可以换行,光标自动转到上一行或下一行行首。每一测试组最多可以设置六项测试项,这六项可以完全相同,也可不同。如果只想测某一项或几项,将其它行设置为空行即可。各项具体设置方法请参照4.6~4.11节。

设置测试技术指标后,可通过按上移键或下移键选择“遇不合格项继续测试”或者“遇不合格项中止测试”,“50Hz”或者“60Hz”。

Vicor 输出功率能力和输入衰减模块(IAM)的数据手册说明书

10VU2U1OCOVVref 2Vref 1+OUT –OUT–IN +IN–IN+IN GATE INGATE OUTP ARALLEL Q1Q2D1D2C2VI-A11-xU 24 V (21 – 32 V)200 W VI-AWW-xU 24 V “W” (18 – 36 V)200 W VI-A33-xQ 48 V (42 – 60 V)400 W VI-ANN-xQ 48 V “N” (36 – 76 V)400 W VI-A66-xQ 300 V (200 – 400 V)400 W[a]MI-A22-xU 28 V (16 – 50 V)200 W MI-A66-xU270 V (125 – 400 V)200 W图14-1—输出功率能力图14-2—输出功率能力图14-2—输入衰减模块(IAM)的框图针对VI-200和VI-J00系列DC-DC转换器和可配置电源概述IAM是一个元件级、DC输入前端滤波器,在结合Vx-200和Vx-J00系列DC-DC转换器使用时,提供了一个输出电压范围1–95 Vdc和功率范围25 – 800 W 功率扩展的高效、高密度电源系统。

有五个输入衰减模块适用于商用市场,符合电信和工业控制EMC规范:适用标准请参阅的数据表。

EMC在允许的额定功率范围内,按照推荐的安装程序,IAM与推荐的Vicor转换器一起使用时,可以保证EMC性能(图14–3)。

所示的转换器输入两端的所示跨接的电容器,以及接地DC-DC转换器的–IN和+IN接地的所示旁路电容器是满足EMC规范所必需的。

这些电容器应具有Y额定值(干扰抑制)。

Y电容器具有高击穿电压额定值,可满足模块的输入到基板规范的隔离特性、自愈特性,以及安全机构安规认证。

输入反向极性保护当与IAM外部的适当额定值的熔断器一起使用时,EMC滤波器中的齐纳二极管可提供反向极性保护。

推荐的输入线熔断器的特性允许在反极性情况下通过熔断器的熔断来保护正常的满载运行(表4–3)。

中文9SX 5000 9SX 6000 9PX 5000 9PX 6000 9SX EBM 180V

9SX 50009SX 60009PX 50009PX 60009SX EBM 180V9PX EBM 180V安装和用户手册版权所有© 2012 EATON保留所有权利。

服务和支持:请致电您当地的服务代表5-6kVA EU_CN第 2 页5-6kVA EU_CN5-6kVA EU_CN 第 3 页中文安全说明保存这些说明。

本手册包含一些重要说明,在安装和维护 UPS 和电池过程中应加以遵循。

本手册中介绍的 9SX 和 9PX 型号适合安装在温度介于 0°C 到 40°C 之间且不存在导电污染物的环境中。

已对本设备进行测试,且结果符合 FCC 规则第 15部分中规定的关于 A 类数字设备的限制。

这些限制旨在提供合理的保护,以防止设备在商用环境中运行时遭到有害干扰。

此设备会产生、使用且能够辐射射频能量,如果未按照说明手册进行安装和使用,则可能对无线电通信造成有害干扰。

在住宅区域运行此设备可能导致有害干扰,此时用户需要自行支付纠正干扰产生的费用。

认证标准p 安全性: I EC/EN 62040-1/第 1 版:2008. UL 1778 第 4 版p EMC :IEC/EN 62040-2/第 2 版:2006. FCC 第 15部分 A 类。

p 性能: I EC/EN 62040-3/第 2.0版:2011. p IEC 61000-4-2 (ESD):3 级。

p IEC 61000-4-3(辐射场): 3 级。

p IEC 61000-4-4 (EFT):4 级。

p IEC 61000-4-5(快速瞬态): 4 级。

p IEC 61000-4-6(电磁场): 3 级。

p IEC 61000-4-8(导电磁场): 4 级。

特殊符号下面举例介绍了 UPS 或配件上使用的用于警告用户重要信息的符号:存在电击危险 -请遵守与电击危险符号关联的警告。

必须始终遵守的重要说明。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

TM

OV9650 Color CMOS SXGA (1.3 MegaPixel) CameraChip™ Implementation Guide

Last Modified: 7 December 2004 Document Version: 1.1

The information contained in this document is considered proprietary to OmniVision Technologies, Inc. This information may be distributed only to individuals or organizations authorized by OmniVision Technologies, Inc. to receive said information. Individuals and/or organizations are not allowed to re-distribute said information.

OV9650 Color CMOS SXGA (1.3 MegaPixel) CameraChip™

Omni

ision

00Table of Contents

Section 1, Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 1.1 Function Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

OmniVision Technologies, Inc. disclaims all liability, including liability for infringement of any proprietary rights, relating to the use of information in this document. No license, expressed or implied, by estoppel or otherwise, to any intellectual property rights is granted herein. * Third-party brands, names, and trademarks are the property of their respective owners. Note:

Section 3, Timing Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 3.1 3.2 3.3 Array Control and Frame Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 3.1.1 Frame Generation (SXGA, VGA, and lower resolutions) . . . . . . . . . 10 Sync Signal Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Frame Rate Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 3.3.1 3.3.2 3.3.3 3.4 3.5 3.6 3.4.1 Clock Prescalar (Timing Generator) . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Dummy Pixel Adjustment (Output Formatter) . . . . . . . . . . . . . . . . . . 12 Dummy Line Adjustment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Digital Exposure Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Section 4, Analog Processing Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 4.1 Gain Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 4.1.1 4.1.2 4.2 4.2.1 4.2.2 Manual Gain Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Automatic Gain Control (AGC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Automatic White Balance Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 Manual White Balance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Section 2, Image Sensor Array . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 2.1 Resolution Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Exposure Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Strobe Flash Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 RGB Raw Data Output Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

White Balance Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Section 5, Digital Signal Processor (DSP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 5.1 5.2 5.3 5.4 5.5 5.6 5.7

Revision Number

1.0 1.1

Date

11/29/04 12/07/04 Initial Release

Revision

In Table 4-1 on page 21, changed last six entries under column "Gain."

This document is provided "as is" with no warranties whatsoever, including any warranty of merchantability, non-infringement, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification, or sample.

2

Gamma Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 5.1.1 5.2.1 Gamma Slope Calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Color Matrix Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Color Matrix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Sharpness Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Noise-Canceling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 White Pixel Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Digital Black Level Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Lens Shading Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31