LM431数据手册(FAIRCHILD公司)

微小电子ZL40202精密LVPECL4 1输出缓冲器数据手册说明书

1FeaturesInputs/Outputs •Accepts differential or single-ended input •LVPECL, LVDS, CML, HCSL, LVCMOS •Four precision LVPECL outputs •Operating frequency up to 750 MHzPower •Option for 2.5 V or 3.3 V power supply •Core current consumption of 62 mA•On-chip Low Drop Out (LDO) Regulator for superior power supply noise rejectionPerformance •Ultra low additive jitter of 39 fs RMSApplications•General purpose clock distribution •Low jitter clock trees •Logic translation•Clock and data signal restoration•Wired communications: OTN, SONET/SDH, GE, 10 GE, FC and 10G FC•PCI Express generation 1/2/3 clock distribution •Wireless communications•High performance microprocessor clock distributionApril 2014Figure 1 - Functional Block DiagramZL40202Precision 1:4 LVPECL Fanout BufferData SheetOrdering InformationZL40202LDG1 16 Pin QFN TraysZL40202LDF116 Pin QFN Tape and ReelMatte TinPackage size: 3 x 3 mm-40o C to +85o CTable of ContentsFeatures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Change Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41.0 Package Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52.0 Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63.1 Clock Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63.2 Clock Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113.3 Device Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.4 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.1 Sensitivity to power supply noise. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.2 Power supply filtering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.3 PCB layout considerations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .164.0 AC and DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175.0 Performance Characterization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .206.0 Typical Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .217.0 Package Thermal Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .238.0 Mechanical Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24List of FiguresFigure 1 - Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - Pin Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Figure 3 - LVPECL Input DC Coupled Thevenin Equivalent . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Figure 4 - LVPECL Input DC Coupled Parallel Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 5 - LVPECL Input AC Coupled Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 6 - LVDS Input DC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 7 - LVDS Input AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 8 - CML Input AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 9 - HCSL Input AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 10 - CMOS Input DC Coupled Referenced to VDD/2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 11 - CMOS Input DC Coupled Referenced to Ground . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 12 - Simplified Output Driver. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 13 - LVPECL Basic Output Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 14 - LVPECL Parallel Output Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 15 - LVPECL Parallel Thevenin-Equivalent Output Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 16 - LVPECL AC Output Termination for Externally Terminated LVPECL Inputs . . . . . . . . . . . . . . . . . . . . 13 Figure 17 - LVPECL AC Output Termination for Internally Terminated LVPECL Inputs. . . . . . . . . . . . . . . . . . . . . 13 Figure 18 - LVPECL AC Output Termination for CML Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 19 - Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 20 - Decoupling Connections for Power Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 21 - Differential Voltage Parameter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 22 - Input To Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19Change SummaryPage ItemChange1Applications Added PCI Express clock distribution.5Pin Description Added exposed pad to Pin Description.6, 7Figure 3 and Figure 413Figure 16Corrected LVPECL interface circuit.18Figure 21Clarification of V ID and V OD .Below are the changes from the February 2013 to the April 2014 issue:Page Item Change7Figure 4Changed text to indicate the circuit is not recommended for VDD_driver=2.5V.7Figure 5Changed pull-up and pull-down resistors from 2kOhm to 100 Ohm.Below are the changes from the November 2012 issue to the February 2013 issue:Removed 22 Ohm series resistors from Figure 3 and 4.These resistors are not required; however there is no impact to performance if the resistors are included.The device is packaged in a 16 pin QFN1416642out3_nvddout3_pN Cc l k _pvddgndout0_no u t 2_no u t 2_po u t 1_n81210o u t 1_pc l k _nN Cout0_pgndFigure 2 - Pin Connections2.0 Pin DescriptionPin # Name Description1, 4clk_p, clk_n,Differential Input (Analog Input). Differential (or singled ended) input signals. For all input signal configuration see “Clock Inputs” on page 615,14, 12, 11, 10, 9, 7, 6out0_p, out0_n out1_p, out1_n out2_p, out2_n out3_p, out3_nDifferential Output (Analog Output). Differential outputs.8, 13vdd Positive Supply Voltage. 2.5 V DC or 3.3 V DC nominal.5, 16gnd Ground. 0 V.2, 3NCNo Connection. Leave unconnected.Exposed PadDevice GND .The ZL40202 is an LVPECL clock fanout buffer with four identical output clock drivers capable of operating at frequencies up to 750MHz.Inputs to the ZL40202 are externally terminated to allow use of precision termination components and to allow full flexibility of input termination. The ZL40202 can accept DC coupled LVPECL or LVDS and AC coupled LVPECL, LVDS, CML or HCSL input signals; single ended input signals can also be accepted. A pin compatible device with internal termination is also available.The ZL40202 is designed to fan out low-jitter reference clocks for wired or optical communications applications while adding minimal jitter to the clock signal. An internal linear power supply regulator and bulk capacitors minimize additive jitter due to power supply noise. The device operates from 2.5V+/-5% or 3.3V+/-5% supply. Its operation is guaranteed over the industrial temperature range -40°C to +85°C.The device block diagram is shown in Figure 1; its operation is described in the following sections.3.1 Clock InputsThe ZL40202 is adaptable to support different types of differential and singled-ended input signals depending on the passive components used in the input termination. The application diagrams in the following figures allow the ZL40202 to accept LVPECL, LVDS, CML, HCSL and single-ended inputs.Figure 3 - LVPECL Input DC Coupled Thevenin EquivalentFigure 4 - LVPECL Input DC Coupled Parallel TerminationFigure 5 - LVPECL Input AC Coupled TerminationFigure 6 - LVDS Input DC CoupledFigure 7 - LVDS Input AC CoupledFigure 8 - CML Input AC CoupledFigure 9 - HCSL Input AC CoupledFigure 11 - CMOS Input DC Coupled Referenced to GroundVDD_driver R1 (kΩ)R2 (kΩ)R3 (kΩ)RA (kΩ) C (pF) 1.5 1.25 3.075open10101.81 3.8open10102.50.33 4.2open10103.30.75open4.21010Table 1 - Component Values for Single Ended Input Reference to Ground* For frequencies below 100 MHz, increase C to avoid signal integrity issues.3.2 Clock OutputsLVPECL has a very low output impedance and a differential signal swing between 1V and 1.6 V. A simplified diagram for the output stage is shown in Figure 12.The LVPECL to LVDS output termination is not shown since there is a separate device that has the same input and LVDS outputs.out_pout_nFigure 12 - Simplified Output DriverThe methods to terminate the ZL40202 LVPECL drivers are shown in the following figures.Figure 15 - LVPECL Parallel Thevenin-Equivalent Output TerminationF igure 16 - LVPECL AC Output Termination for Externally Terminated LVPECL InputsFigure 17 - LVPECL AC Output Termination for Internally Terminated LVPECL InputsFigure 18 - LVPECL AC Output Termination for CML Inputs3.3 Device Additive JitterThe ZL40202 clock fan out buffer is not intended to filter clock jitter. The jitter performance of this type of device is characterized by its additive jitter. Additive jitter is the jitter the device would add to a hypothetical jitter-free clock as it passes through the device. The additive jitter of the ZL40202 is random and as such it is not correlated to the jitter of the input clock signal.The square of the resultant random RMS jitter at the output of the ZL40202 is equal to the sum of the squares of the various random RMS jitter sources including: input clock jitter; additive jitter of the buffer; and additive jitter due to power supply noise. There may be additional deterministic jitter sources that are not shown in Figure 19.Figure 19 - Additive Jitter3.4 Power SupplyThis device operates with either a 2.5V supply or 3.3V supply.3.4.1 Sensitivity to power supply noisePower supply noise from sources such as switching power supplies and high-power digital components such as FPGAs can induce additive jitter on clock buffer outputs. The ZL40202 is equipped with a low drop out (LDO) power regulator and on-chip bulk capacitors to minimize additive jitter due to power supply noise. The LDO regulator on the ZL40202 allows this device to have superior performance even in the presence of external noise sources. The on-chip regulation, recommended power supply filtering, and good PCB layout all work together to minimize the additive jitter from power supply noise.The performance of these clock buffers in the presence of power supply noise is detailed in ZLAN-403, “Power Supply Rejection in Clock Buffers” which is available from Applications Engineering.3.4.2 Power supply filteringFor optimal jitter performance, the device should be isolated from the power planes connected to its power supply pins as shown in Figure 20.•10 µF capacitors should be size 0603 or size 0805 X5R or X7R ceramic, 6.3 V minimum rating•0.1 µF capacitors should be size 0402 X5R ceramic, 6.3 V minimum rating•Capacitors should be placed next to the connected device power pins• a 0.3 ohm resistor is recommended for the filter shown in Figure 20Figure 20 - Decoupling Connections for Power Pins3.4.3 PCB layout considerationsThe power nets in Figure 20 can be implemented either as a plane island or routed power topology without changing the overall jitter performance of the device.Absolute Maximum Ratings*Parameter Sym.Min.Max.Units 1Supply voltage V DD_R-0.5 4.6V 2Voltage on any digital pin V PIN-0.5V DD V 3LVPECL output current I out30mA 4Soldering temperature T260 °C 5Storage temperature T ST-55125 °C 6Junction temperature T j125 °C 7Voltage on input pin V input V DD V 8Input capacitance each pin C p500fF 4.0 AC and DC Electrical Characteristics* Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.* Voltages are with respect to ground (GND) unless otherwise statedRecommended Operating Conditions*Characteristics Sym.Min.Typ.Max.Units1Supply voltage 2.5 V mode V DD25 2.375 2.5 2.625V2Supply voltage 3.3 V mode V DD33 3.135 3.3 3.465V3Operating temperature T A-402585°C* Voltages are with respect to ground (GND) unless otherwise statedDC Electrical Characteristics - Current ConsumptionCharacteristics Sym.Min.Typ.Max.Units Notes 1Supply current LVPECL drivers -unloadedI dd_unload62mA Unloaded2Supply current LVPECL drivers - loaded (all outputs are active)I dd_load140mA Including powerto R L = 50DC Electrical Characteristics - Inputs and Outputs - for 3.3 V SupplyCharacteristics Sym.Min.Typ.Max.Units Notes 1Differential input common modevoltageV CM 1.1 2.0V2Differential input voltage difference V ID0.251V3LVPECL output high voltage V OH V DD-1.40V* This parameter is measured from 125 MHz to 750 MHz* This parameter is measured from 125 MHz to 750 MHzFigure 21 - Differential Voltage Parameter* Supply voltage and operating temperature are as per Recommended Operating Conditions4LVPECL output low voltage V OL V DD -1.62V 5LVPECL output differential voltage*V OD0.50.9VDC Electrical Characteristics - Inputs and Outputs - for 2.5 V SupplyCharacteristicsSym.Min.Typ.Max.Units Notes1Differential input common mode voltageV CM 1.1 1.6V 2Differential input voltage difference V ID 0.251V 3LVPECL output high voltage V OH V DD -1.40V 4LVPECL output low voltage V OL V DD -1.62V 5LVPECL output differential voltage*V OD0.40.9VAC Electrical Characteristics* - Inputs and Outputs (see Figure 22) - for 2.5 and 3.3 V supplies.CharacteristicsSym.Min.Typ.Max.Units Notes1Maximum Operating Frequency 1/t p 750MHz 2Input to output clock propagation delay t pd 012ns 3Output to output skew t out2out 50100ps 4Part to part output skewt part2part 80300ps 5Output clock Duty Cycle degradation t PWH / t PWL-2%0%2%Duty Cycle 6LVPECL Output slew rater sl0.75 1.2V/nsDC Electrical Characteristics - Inputs and Outputs - for 3.3 V SupplyCharacteristicsSym.Min.Typ.Max.Units NotesInputt Pt PWL t pdt PWHOutputFigure 22 - Input To Output TimingAdditive Jitter at 2.5 V*Output Frequency (MHz)Jitter MeasurementFilterTypical RMS (fs)Notes112512 kHz - 20 MHz 1122212.512 kHz - 20 MHz 803311.0412 kHz - 20 MHz 70442512 kHz - 20 MHz 65550012 kHz - 20 MHz 566622.0812 kHz - 20 MHz 46775012 kHz - 20 MHz44Additive Jitter at 3.3 V*Output Frequency (MHz)Jitter MeasurementFilterTypical RMS (fs)Notes112512 kHz - 20 MHz 1122212.512 kHz - 20 MHz 823311.0412 kHz - 20 MHz 72442512 kHz - 20 MHz 63550012 kHz - 20 MHz 526622.0812 kHz - 20 MHz 43775012 kHz - 20 MHz395.0 Performance Characterization*The values in this table were taken with an approximate input slew rate of 0.8 V/ns*The values in this table were taken with an approximate input slew rate of 0.8 V/nsAdditive Jitter from a Power Supply Tone*Carrier frequencyParameterTypicalUnitsNotes125MHz 25 mV at 100 kHz 159fs RMS 750MHz25 mV at 100 kHz82fs RMS* The values in this table are the additive periodic jitter caused by an interfering tone typically caused by a switching power supply. For this test, measurements were taken over the full temperature and voltage range for V DD = 3.3 V. The magnitude of the interfering tone is measured at the DUT.6.0 Typical BehaviorTypical Phase Noise at 622.08 MHzTypical Waveform at 155.52 MHzInput Slew Rate versus Additive Jitter Propagation Delay versus TemperatureNote:This is for a single device. For more details see thecharacterization section.V ODversus FrequencyPower Supply Tone Magnitude versus PSRR (at 100 kHz) at 125 MHz Power Supply Tone Magnitude versus Additive Jitter (at 100 kHz) at 125 MHzPower Supply Tone Frequency (at 25 mV) versus PSRR at 125 MHz Power Supply Tone Frequency (at 25 mV) versus Additive Jitter at 125 MHz7.0 Package Thermal Characteristics*Proper thermal management must be practiced to ensure that T jmax is not exceeded.Thermal DataParameterSymbolTest ConditionValue UnitJunction to Ambient Thermal ResistanceΘJAStill Air 1 m/s 2 m/s 67.961.658.1oC/WJunction to Case Thermal Resistance ΘJC Still Air 44.1o C/W Junction to Board Thermal Resistance ΘJB Still Air23.2oC/WMaximum Junction Temperature*T jmax 125o C Maximum Ambient TemperatureT A85oC© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense and security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world’s standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 3,400 employees globally. Learn more at .Microsemi Corporate Headquarters One One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (800) 713-4113Outside the USA: +1 (949) 380-6100Sales: +1 (949) 380-6136Fax: +1 (949) 215-4996E-mail: ***************************Information relating to products and services furnished herein by Microsemi Corporation or its subsidiaries (collectively “Microsemi”) is believed to be reliable. However, Microsemi assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Microsemi or licensed from third parties by Microsemi, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Microsemi, or non-Microsemi furnished goods or services may infringe patents or other intellectual property rights owned by Microsemi.This publication is issued to provide information only and (unless agreed by Microsemi in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Microsemi without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user’s responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical and other products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Microsemi’s conditions of sale which are available on request.For more information about all Microsemi productsvisit our website at TECHNICAL DOCUMENTATION – NOT FOR RESALE。

FAIRCHILD FDT3N40 400V N-Channel MOSFET 数据手册

correction.Absolute Maximum RatingsThermal CharacteristicsSOT-223FDT SeriesGDSSymbolParameterFDT3N40UnitV DSS Drain-Source Voltage 400V I D Drain Current - Continuous (T C = 25︒C)- Continuous (T C = 100︒C) 2.0 *1.2 *A A I DM Drain Current - Pulsed(Note 1)8.0 *A V GSS Gate-Source voltage±30V E AS Single Pulsed Avalanche Energy (Note 2)46mJ I AR Avalanche Current(Note 1)2A E AR Repetitive Avalanche Energy (Note 1)0.2mJ dv/dt Peak Diode Recovery dv/dt (Note 3)4.5V/ns P D Power Dissipation(T C = 25︒C)- Derate above 25︒C20.02W W/︒C T J, T STG Operating and Storage Temperature Range -55 to +150︒C T LMaximum Lead Temperature for Soldering Purpose,1/8” from Case for 5 Seconds300︒CSymbolParameterTypMaxUnitR θJA *Thermal Resistance, Case-to-Sink Typ.--60︒C/W* Drain current limited by maximum junction temperature* Surface Mounted on JESD51-3 Board, T<0.1sec.NOTES:1. Repetitive Rating: Pulse width limited by maximum junction temperature2. L = 10mH, I AS = 2A, V DD = 50V, R G = 25Ω, Starting T J = 25︒C3. I SD ≤ 2A, di/dt ≤ 200A/μs, V DD ≤ BV DSS , Starting T J = 25︒C4. Pulse Test: Pulse width ≤ 300μs, Duty Cycle ≤ 2%5. Essentially Independent of Operating Temperature Typical CharacteristicsI GSSR Gate-Body Leakage Current, Reverse V GS = -30V, V DS = 0V -----100nA On CharacteristicsV GS(th)Gate Threshold Voltage V DS = V GS , I D = 250μA 3.0-- 5.0V R DS(on)Static Drain-Source On-ResistanceV GS = 10V, I D = 1A -- 2.8 3.4Ωg FS Forward Transconductance V DS = 40V, I D = 1A (Note 4)--2--S Dynamic CharacteristicsC iss Input Capacitance V DS = 25V, V GS = 0V,f = 1.0MHz--173225pF C oss Output Capacitance--3040pF C rss Reverse Transfer Capacitance --3.76pF Switching Characteristicst d(on)Turn-On Delay Time V DD = 200V, I D = 2A R G = 25Ω(Note 4, 5)--1030ns t r Turn-On Rise Time --3070ns t d(off)Turn-Off Delay Time --1030ns t f Turn-Off Fall Time --2560ns Q g Total Gate Charge V DS = 320V, I D = 2A V GS = 10V(Note 4, 5)-- 4.56nC Q gs Gate-Source Charge -- 1.2--nC Q gd Gate-Drain Charge--2--nCDrain-Source Diode Characteristics and Maximum RatingsI S Maximum Continuous Drain-Source Diode Forward Current ----2A I SM Maximum Pulsed Drain-Source Diode Forward Current ----8A V SD Drain-Source Diode Forward Voltage V GS = 0V, I S = 2A---- 1.4V t rr Reverse Recovery Time V GS = 0V, I S = 2AdI F /dt =100A/μs (Note 4)--210--ns Q rrReverse Recovery Charge--0.75--μCResistive Switching Test Circuit & WaveformsUnclamped Inductive Switching Test Circuit & WaveformsThe following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is notAuto-SPM™Build it Now™CorePLUS™CorePOWER™CROSSVOLT™CTL™Current Transfer Logic™ DEUXPEED®EcoSPARK®EfficientMax™ EZSWITCH™*™*®Fairchild®Fairchild Semiconductor®FACT Quiet Series™ FACT®FAST®FastvCore™FETBench™FPS™F-PFS™FRFET®Global Power Resource SMGreen FPS™Green FPS™ e-Series™G max™GTO™IntelliMAX™ISOPLANAR™MegaBuck™MICROCOUPLER™MicroFET™MicroPak™MillerDrive™MotionMax™Motion-SPM™OPTOLOGIC®OPTOPLANAR®®PDP SPM™PowerTrench®PowerXS™Programmable Active Droop™QFET®QS™Quiet Series™RapidConfigure™™Saving our world, 1mW/W/kW at a time™SignalWise™SmartMax™SMART START™SPM®STEALTH™SuperFET™SuperSOT™-3SuperSOT™-6SuperSOT™-8SupreMOS™SyncFET™Sync-Lock™®*The Power Franchise®TinyBoost™TinyBuck™TinyCalc™TinyLogic®TINYOPTO™TinyPower™TinyPWM™TinyWire™TriFault Detect™TRUECURRENT™*μSerDes™UHC®Ultra FRFET™UniFET™VCX™VisualMax™XS™* Trademarks of System General Corporation, used under license by Fairchild Semiconductor.DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1. Life support devices or systems are devices or systems which, (a) areintended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user. 2. A critical component in any component of a life support, device, orsystem whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.ANTI-COUNTERFEITING POLICYFairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, , under Sales Support.Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts.Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation ofcounterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information.Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage ourcustomers to do their part in stopping this practice by buying direct or from authorized distributors.© 2008 Fairchild Semiconductor Corporation 。

LM431LAN-XX-TR70中文资料

Shunt RegulatorShunt RegulatorGeneral Description• The LM431 Series ICs are low voltage three-terminalprogrammable shunt regulators with guaranteed thermal stability over a full operation range. These monolithic ICs voltage reference operate as a low temperature coefficientZener which is programmable from Vref to 18V with two external resistors. These devices exhibit a wide operating current rangeof 80µA to 50/100mA with a typical dynamic impedance of 0.05 to0.22Ω. The characteristics of these references make them excellent replacements for Zener diodes in many applications such asdigital voltmeters, power supplies and op amp circuitry• The LM431L precision reference is offered in three voltagetolerance for V REF =1.240V: 1.5%, 1.0% and 0.5%.• These ICs are available in 4 packages: TO-92, SOT-23, SOT-23-5 and SOT-89. . .Features Applications• Programmable Precise Output Voltage from 1.24V to 16/18V• High Stability under Capacitive Load• Low Temperature Deviation• Low Dynamic Output Impedance: 0.05 to 0.22Ω Typical • Operating Current from 80µA to 50/100mA. • Low Output Noise Voltage• RoHS ComplianceSOT-89SOT-23-5 SOT-23• Graphic Card• PC Motherboard • Voltage Adapter • Switching Power Supply • ChargerTO-92LM431L Ordering InformationPin ConfigurationOutline: ZTO-92Outline: NSOT-23Outline: N5SOT-23-5 Outline: KSOT-89LM431LBlock Diagram SymbolsAbsolute Maximum Ratings (Ta=25° C)(Full operating ambient temperature range applies unless otherwise noted.) SymbolDescription LM431L LM431LA LM431LBUnit V KA Cathode Voltage16 18 V I KA Cathode Current Range (Continuous) 50-100 ~ +100mAI REF Reference Input Current Range(Continuous)3 10 mAT J Operating Junction Temperature 150° C T OPR Operating Temperature Range -40 ~ 85-40 ~ 125 ° C T STGStorage Temperature Range-65 ~ 150° CZ:TO-92 700770 N:SOT-23 350 370N5:SOT-23-5550 370 P DPower DissipationK: SOT-89-770 mW Z:TO-92 180150 N:SOT-23 360 330N5:SOT-23-5230 250 Rth JAPackage Thermal ImpedanceK: SOT-89-50° C/WLM431L Electrical Characteristics(T A=25ºC, unless otherwise specified)LM431L LM431LALM431LBSymbol DescriptionMin.Typ. Max. Min.Typ.Max.Min.Typ.Max.UnitTestCircuitConditionsV REF Reference InputVoltage1.222 1.240 1.258 1.228 1.240 1.252 1.234 1.240 1.246 V Fig.1 V KA=V REF,I KA=10mA0-70° C - - - - 2 1- - 2 10-40-85° C- 7.0 20 - 3 10 - 3 10∆V REFReferenceInputVoltageDeviation -40-125° C- - - - 4 15 - 4 15mVFig.1(Note1)V KA=V REF,I KA=10mA ∆V REF/∆V KARatio of Change inReference InputVoltage to Change inCathode to AnodeVoltage- -0.6 -1.5 - -0.5 -1.5- -0.5 -1.5mV/V Fig.2IKA=10mA∆V KA=V KA(max)~V REFI REFReferenceInputCurrentTa=25°C- 0.15 0.3 - 0.150.4 - 0.150.4 µA Fig.2I KA=10mA, R1=10KΩ,R2=∞∆I REFReference InputCurrent DeviationOver TemperatureRange- 0.050.08 - 0.1 0.4 - 0.1 0.4 µA Fig.2I KA=10mA, R1=10KΩ,R2=∞I MIN Min. Cathode CurrentFor Regulation- 55 80 - 55 80 - 55 80 µA Fig.1 V KA=V REF- 2.6 1000 - 40 100- 40 100V KA= V KA(max),V REF=0VI OFF Off-State CathodeCurrent- - - - 10 50 - 10 50nA Fig.3V KA=6V, V REF=0V Z KA DynamicImpedance - 0.22 0.4 - 0.050.15- 0.050.15ΩFig.1(Note2)V KA=V REF,I KA=1.0mA~ I KA(max),f≤1.0KHz Fig.1- Test Circuit for V KA=V REF Fig.2- Test Circuit for V KA>V REFLM431LFig.3- Test Circuit for I OFFNote1: Note2:LM431LFig.4- V REF - T JJunction Temperature T J (° C)Fig.6- I K – V KA (1)Cathode Voltage V KA (V)Fig.5- I REF - T JJunction Temperature T J (° C)Typical Characteristics CurvesR e f e r e n c e I n p u t V o l t a g e V R E F (V )C a t h o d e C u r r e n t I K (m A )Fig.7- I K – V KA (2)Cathode Voltage V KA (V)R e f e r e n c e I n p u t C u r r e n t I R E F (n A )C a t h o d e C u r r e n t I K (µA )LM431LFig.8- G VO - fFrequency f (Hz)Fig.9- Pulse ResponseTime t (µs)V o l t a g e S w i n g (V )Fig.11- Z KA - fFrequency f (Hz)O p e n L o o p V o l t a g e G a i n G V O (d B )D y n a m i c I m p e d a n c e │Z K A │ (Ω)Fig.10- ∆V REF - T JJunction Temperature T J (° C)∆V R E F /∆V K A (m V /V )LM431L Typical ApplicationFig.12-Shunt RegulatorLM431L Typical Application (Continued)Fig.15- Precision 5V 1A RegulatorFig.16- PWM Converter with ReferenceLM431LDevice Marking CodeCircuit Tolerance SOT-23 (N) SOT-23-5 (N5)SOT-89 (K)Blank1.5%24A24A N/A A 1.0% EA7 E6A E41B LM431LB 0.5% EA6E5AE41ADimensions in inches (mm)TO-92LM431LSOT-23SOT-23-5LM431LSOT-89LM431L How to contact us:。

TS431 431A 431B 数据手册

Block Diagram

Operating Temp. (Ambient)

Package

TO-92 SOT-89 SOT-23 SOP-8

Pin Assignment

Pin No.

TS431/A/BCT 1 2 3 TS431/A/BCY 1 2 3 TS431/A/BCX 1 3 2 TS431/A/BCS 8 2,H

14.30(typ)

0.563(typ)

C

E

F

H

D

G

SOT-89 Mechanical Drawing

A B

SOT-89 DIMENSION

I

DIM A B C

MILLIMETERS MIN MAX 4.40 1.50 2.30 0.40 1.50 3.00 0.89 4.05 1.4 0.35 4.60 1.7 2.60 0.52 1.50 3.00 1.20 4.25 1.6 0.44

Pin Description Reference Anode Cathode Non connect 2003/12 rev. B

TS431/A/B

1-8

Absolute Maximum Rating

Cathode Voltage (Note 1) Continuous Cathode Current Range Reference Input Current Range Power Dissipation (Note 2, 3) TO-92 SOT-89 / SOP-8 SOT-23 Operating Junction Temperature Range Storage Temperature Range Note 2: Tj Max = 150 C Note 3: Rating apply to ambient temperature at 25 C

LM431AIM3中文资料

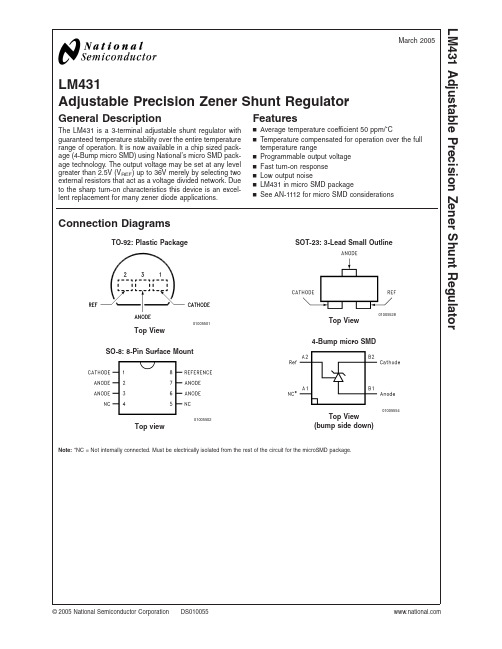

LM431Adjustable Precision Zener Shunt RegulatorGeneral DescriptionThe LM431is a 3-terminal adjustable shunt regulator with guaranteed temperature stability over the entire temperature range of operation.It is now available in a chip sized pack-age (4-Bump micro SMD)using National’s micro SMD pack-age technology.The output voltage may be set at any level greater than 2.5V (V REF )up to 36V merely by selecting two external resistors that act as a voltage divided network.Due to the sharp turn-on characteristics this device is an excel-lent replacement for many zener diode applications.Featuresn Average temperature coefficient 50ppm/˚Cn Temperature compensated for operation over the full temperature rangen Programmable output voltage n Fast turn-on response n Low output noisen LM431in micro SMD packagen See AN-1112for micro SMD considerationsConnection DiagramsNote:*NC =Not internally connected.Must be electrically isolated from therest of the circuit for the microSMD package.TO-92:Plastic PackageDS010055-1Top ViewSO-8:8-Pin Surface MountDS010055-2Top viewSOT-23:3-Lead Small OutlineDS010055-28Top View 4-Bump micro SMDDS010055-54Top View(bump side down)March 2002LM431Adjustable Precision Zener Shunt Regulator©2002National Semiconductor Corporation Ordering InformationPackage Typical Accuracy Order Number/Package MarkingTemperature Range Transport MediaNSC Drawing0.5%1%2%TO-92LM431CCZ/LM431CCZ LM431BCZ/LM431BCZ LM431ACZ/LM431ACZ 0˚C to +70˚CRailsZ03ALM431CIZ/LM431CIZLM431BIZ/LM431BIZ LM431AIZ/LM431AIZ −40˚C to +85˚C SO-8LM431CCM/431CCM LM431BCM/431BCM LM431ACM/LM431ACM 0˚C to +70˚CRails and Tape &ReelM08A LM431CIM/431CIMLM431BIM/431BIM LM431AIM/LM431AIM −40˚C to +85˚C SOT-23LM431CCM3/N1B LM431BCM3/N1D LM431ACM3/N1F 0˚C to +70˚CRails and Tape &ReelMF03A LM431CIM3N1ALM431BIM3N1CLM431AIM3N1E−40˚C to +85˚C micro SMD––LM431AIBPLM431AIBPX(Note 1)−40˚C to +85˚C250Units Tape and Reel3k Units Tape and ReelBPA04AFBNote 1:The micro SMD package marking is a 1digit manufacturing Date Code onlymicro SMD Top View Marking ExampleDS010055-56L M 431 2Symbol and Functional DiagramsDC Test CircuitsDS010055-99DS010055-55DS010055-4FIGURE 1.Test Circuit for V Z =V REFDS010055-5Note:V Z =V REF (1+R1/R2)+I REF •R1FIGURE 2.Test Circuit for V Z >V REFDS010055-6FIGURE 3.Test Circuit for Off-State CurrentLM4313Absolute Maximum Ratings (Note 2)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.Storage Temperature Range −65˚C to +150˚C Operating Temperature Range Industrial (LM431xI)−40˚C to +85˚C Commercial (LM431xC)0˚C to +70˚C Soldering InformationInfrared or Convection (20sec.)235˚CWave Soldering (10sec.)260˚C (lead temp.)Cathode Voltage37VContinuous Cathode Current−10mA to +150mAReference Voltage−0.5V Reference Input Current10mA Internal Power Dissipation (Notes 3,4)TO-92Package SO-8Package SOT-23Package 0.78W 0.81W 0.28W micro SMD Package0.30WOperating ConditionsMin Max Cathode Voltage V REF 37V Cathode Current1.0mA100mALM431Electrical CharacteristicsT A =25˚C unless otherwise specified Symbol ParameterConditionsMin Typ Max Units V REFReference VoltageV Z =V REF ,I I =10mA 2.4402.4952.550VLM431A (Figure 1)V Z =V REF ,I I =10mA 2.4702.4952.520VLM431B (Figure 1)V Z =V REF ,I I =10mA 2.4852.5002.510VLM431C (Figure 1)V DEVDeviation of Reference Input Voltage Over V Z =V REF ,I I =10mA,8.017mVTemperature (Note 5)T A =Full Range (Figure 1)Ratio of the Change in Reference Voltage I Z =10mAV Z from V REF to 10V −1.4−2.7mV/Vto the Change in Cathode Voltage(Figure 2)V Z from 10V to 36V−1.0−2.0I REF Reference Input CurrentR 1=10k Ω,R 2=∞, 2.04.0µA I I =10mA (Figure 2)∝I REFDeviation of Reference Input Current over R 1=10k Ω,R 2=∞,TemperatureI I =10mA,0.4 1.2µA T A =Full Range (Figure 2)I Z(MIN)Minimum Cathode Current for Regulation V Z =V REF (Figure 1)0.4 1.0mA I Z(OFF)Off-State CurrentV Z =36V,V REF =0V (Figure 3)0.31.0µA r ZDynamic Output Impedance (Note 6)V Z =V REF ,LM431A,0.75ΩFrequency =0Hz (Figure 1)V Z =V REF ,LM431B,LM431C 0.50ΩFrequency =0Hz (Figure 1)Note 2:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.Electrical specifications do not apply when operating the device beyond its rated operating conditions.Note 3:T J Max =150˚C.Note 4:Ratings apply to ambient temperature at 25˚C.Above this temperature,derate the TO-92at 6.2mW/˚C,the SO-8at 6.5mW/˚C,the SOT-23at 2.2mW/˚C and the micro SMD at 3mW/˚C.Note 5:Deviation of reference input voltage,V DEV ,is defined as the maximum variation of the reference input voltage over the full temperature range.L M 431 4LM431Electrical Characteristics(Continued)Where:T 2−T 1=full temperature change (0-70˚C).∝V REF can be positive or negative depending on whether the slope is positive or negative.Example:V DEV =8.0mV,V REF =2495mV,T 2−T 1=70˚C,slope is positive.Note 6:The dynamic output impedance,r Z ,is defined as:When the device is programmed with two external resistors,R1and R2,(see Figure 2),the dynamic output impedance of the overall circuit,r Z ,is defined as:Equivalent CircuitDS010055-7The average temperature coefficient of the reference input voltage,∝V REF ,is defined as:DS010055-3LM4315Typical Performance CharacteristicsInput Current vs V ZDS010055-29Thermal InformationDS010055-30Input Current vs V ZDS010055-31Dynamic Impedance vs FrequencyDS010055-9DS010055-10Stability Boundary ConditionsDS010055-11Note:The areas under the curves represent conditions that may cause the device to oscillate.For curves B,C,and D,R2and V +were adjusted to establish the initial V Z and I Z conditions with C L =0.V +and C L were then adjusted to determine the ranges of stability.Test Circuit for Curve A Above DS010055-12Test Circuit for Curves B,C and D AboveDS010055-13L M 431 6Typical ApplicationsShunt RegulatorDS010055-14Single Supply Comparator withTemperature Compensated ThresholdDS010055-15Series RegulatorDS010055-16Output Control of a ThreeTerminal Fixed RegulatorDS010055-17Higher Current Shunt RegulatorDS010055-18Crow BarDS010055-19LM4317Typical Applications(Continued)Over Voltage/Under VoltageProtection CircuitDS010055-20Voltage MonitorDS010055-21L M 431 8Typical Applications(Continued)Application Info1.0MountingTo ensure that the geometry of the micro SMD packagemaintains good physical contact with the printed circuitboard,pin A1(NC)must be soldered to the pcb.Please seeAN-1112for more detailed information regarding boardmounting techniques for the micro SMD package.2.0LM431micro SMD Light SensitivityWhen the LM431micro SMD package is exposed to brightsunlight,normal office fluorescent light,and other LED’s andlasers,it operates within the guaranteed limits specified inthe electrical characteristics table.Delay TimerDS010055-22Current Limiter or Current SourceDS010055-23Constant Current SinkDS010055-24LM4319Physical Dimensionsinches (millimeters)unless otherwise notedNS Package Number M08ASOT-23Molded Small Outline Transistor Package (M3)NS Package Number MF03AL M 431 10LM431 Physical Dimensions inches(millimeters)unless otherwise noted(Continued)11Physical Dimensions inches(millimeters)unless otherwise noted(Continued)LIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices orsystems which,(a)are intended for surgical implantinto the body,or(b)support or sustain life,andwhose failure to perform when properly used inaccordance with instructions for use provided in thelabeling,can be reasonably expected to result in asignificant injury to the user.2.A critical component is any component of a lifesupport device or system whose failure to performcan be reasonably expected to cause the failure ofthe life support device or system,or to affect itssafety or effectiveness.National SemiconductorCorporationAmericasEmail:support@National SemiconductorEuropeFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)6995086208English Tel:+44(0)8702402171Français Tel:+33(0)141918790National SemiconductorAsia Pacific CustomerResponse GroupTel:65-2544466Fax:65-2504466Email:ap.support@National SemiconductorJapan Ltd.Tel:81-3-5639-7560Fax:81-3-5639-7507 NOTES:UNLESS OTHERWISE SPECIFIED1.EPOXY COATING2.63Sn/37Pb EUTECTIC BUMP3.RECOMMEND NON-SOLDER MASK DEFINED LANDING PAD.4.PIN A1IS ESTABLISHED BY LOWER LEFT CORNER WITH RESPECT TO TEXT ORIENTATION.REMAINING PINS ARENUMBERED.5.XXX IN DRAWING NUMBER REPRESENTS PACKAGE SIZE VARIATION WHERE X1IS PACKAGE WIDTH,X2ISPACKAGE LENGTH AND X3IS PACKAGE HEIGHT.6.REFERENCE JEDEC REGISTRATION MO-211,VARIATION BA.4-Bump micro SMDX1=0.777X2=0.904X3=0.850NS Package Number BPA04AFBLM431AdjustablePrecisionZenerShuntRegulatorNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.。

LM431中文手册

LM431Adjustable Precision Zener Shunt RegulatorGeneral DescriptionThe LM431is a 3-terminal adjustable shunt regulator with guaranteed temperature stability over the entire temperature range of operation.It is now available in a chip sized pack-age (4-Bump micro SMD)using National’s micro SMD pack-age technology.The output voltage may be set at any level greater than 2.5V (V REF )up to 36V merely by selecting two external resistors that act as a voltage divided network.Due to the sharp turn-on characteristics this device is an excel-lent replacement for many zener diode applications.Featuresn Average temperature coefficient 50ppm/˚Cn Temperature compensated for operation over the full temperature rangen Programmable output voltage n Fast turn-on response n Low output noisen LM431in micro SMD packagen See AN-1112for micro SMD considerationsConnection DiagramsTO-92:Plastic Package01005501Top ViewSO-8:8-Pin Surface Mount01005502Top viewSOT-23:3-Lead Small Outline01005528Top View 4-Bump micro SMD01005554Top View(bump side down)Note:*NC =Not internally connected.Must be electrically isolated from the rest of the circuit for the microSMD package.March 2005LM431Adjustable Precision Zener Shunt Regulator©2005National Semiconductor Corporation Ordering InformationPackageTypical Accuracy Order Number/PackageMarking TemperatureRangeTransport MediaNSC Drawing0.5%1%2%TO-92LM431CCZ/LM431CCZ LM431BCZ/LM431BCZ LM431ACZ/LM431ACZ 0˚C to +70˚CRailsZ03ALM431CIZ/LM431CIZLM431BIZ/LM431BIZ LM431AIZ/LM431AIZ −40˚C to +85˚CSO-8LM431CCM/431CCM LM431BCM/431BCMLM431ACM/LM431ACM0˚C to +70˚CRailsM08ALM431CCMX/431CCM LM431BCMX/431BCM LM431ACMX/LM431ACM Tape &ReelLM431CIM/431CIM LM431BIM/431BIM LM431AIM/LM431AIM −40˚C to +85˚CRailsLM431CIMX/431CIMLM431BIMX/431BIMLM431AIMX/LM431AIMTape &ReelSOT-23LM431CCM3/N1BLM431BCM3/N1D LM431ACM3/N1F0˚C to +70˚CRailsMF03ALM431CCM3X/N1B LM431BCM3X/N1D LM431ACM3X/N1F Tape &ReelLM431CIM3N1ALM431BIM3N1CLM431AIM3N1E−40˚C to +85˚CRailsLM431CIM3XN1ALM431BIM3X N1C LM431AIM3XN1ETape &Reel micro SMD––LM431AIBPLM431AIBPX (Note 1)−40˚C to +85˚C 250Units Tape andReel3k Units Tape andReelBPA04AFBNote 1:The micro SMD package marking is a 1digit manufacturing Date Code onlymicro SMD Top View Marking Example01005556L M 431 2Symbol and Functional Diagrams0100559901005555DC Test Circuits01005506Test Circuit for Off-State Current01005504FIGURE 1.Test Circuit for V Z =V REF01005505Note:V Z =V REF (1+R1/R2)+I REF •R1FIGURE 2.Test Circuit for V Z >V REFLM4313Absolute Maximum Ratings (Note 2)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.Storage Temperature Range −65˚C to +150˚COperating Temperature Range Industrial (LM431xI)−40˚C to +85˚C Commercial (LM431xC)0˚C to +70˚C Soldering InformationInfrared or Convection (20sec.)235˚CWave Soldering (10sec.)260˚C (lead temp.)Cathode Voltage37VContinuous Cathode Current−10mA to +150mA Reference Voltage −0.5V Reference Input Current10mAInternal Power Dissipation (Notes 3,4)TO-92Package SO-8Package SOT-23Package 0.78W 0.81W 0.28W micro SMD Package0.30WOperating ConditionsMinMax Cathode Voltage V REF 37V Cathode Current1.0mA100mALM431Electrical CharacteristicsT A =25˚C unless otherwise specified Symbol ParameterConditionsMin Typ Max Units V REFReference VoltageV Z =V REF ,I I =10mA 2.4402.4952.550VLM431A (Figure 1)V Z =V REF ,I I =10mA 2.4702.4952.520VLM431B (Figure 1)V Z =V REF ,I I =10mA 2.4852.5002.510VLM431C (Figure 1)V DEVDeviation of Reference Input Voltage Over V Z =V REF ,I I =10mA,8.017mVTemperature (Note 5)T A =Full Range (Figure 1)Ratio of the Change in Reference Voltage I Z =10mA V Z from V REF to 10V −1.4−2.7mV/Vto the Change in Cathode Voltage(Figure 2)V Z from 10V to 36V−1.0−2.0I REF Reference Input CurrentR 1=10k Ω,R 2=∞, 2.04.0µA I I =10mA (Figure 2)∝I REFDeviation of Reference Input Current over R 1=10k Ω,R 2=∞,TemperatureI I =10mA,0.4 1.2µA T A =Full Range (Figure 2)I Z(MIN)Minimum Cathode Current for Regulation V Z =V REF (Figure 1)0.4 1.0mA I Z(OFF)Off-State CurrentV Z =36V,V REF =0V (Figure *NO TARGET FOR fi*)0.31.0µA r ZDynamic Output Impedance (Note 6)V Z =V REF ,LM431A,0.75ΩFrequency =0Hz (Figure 1)V Z =V REF ,LM431B,LM431C 0.50ΩFrequency =0Hz (Figure 1)Note 2:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.Electrical specifications do not apply when operating the device beyond its rated operating conditions.Note 3:T J Max =150˚C.Note 4:Ratings apply to ambient temperature at 25˚C.Above this temperature,derate the TO-92at 6.2mW/˚C,the SO-8at 6.5mW/˚C,the SOT-23at 2.2mW/˚C and the micro SMD at 3mW/˚C.Note 5:Deviation of reference input voltage,V DEV ,is defined as the maximum variation of the reference input voltage over the full temperature range.L M 431 4LM431Electrical Characteristics(Continued)01005507The average temperature coefficient of the reference input voltage,∝V REF ,is defined as:Where:T 2−T 1=full temperature change (0-70˚C).∝V REF can be positive or negative depending on whether the slope is positive or negative.Example:V DEV =8.0mV,V REF =2495mV,T 2−T 1=70˚C,slope is positive.Note 6:The dynamic output impedance,r Z ,is defined as:When the device is programmed with two external resistors,R1and R2,(see Figure 2),the dynamic output impedance of the overall circuit,r Z ,is defined as:LM4315Equivalent Circuit01005503Typical Performance CharacteristicsInput Current vs V ZThermal Information0100552901005530Input Current vs V ZDynamic Impedance vs Frequency0100553101005509L M 431 6Typical Performance Characteristics(Continued)Stability Boundary Conditions01005511Note:The areas under the curves represent conditions that may cause thedevice to oscillate.For curves B,C,and D,R2and V+were adjusted toestablish the initial V Z and I Z conditions with C L=0.V+and C L were thenadjusted to determine the ranges of stability.01005510Test Circuit for Curve A Above Test Circuit for Curves B,C and D Above0100551201005513Typical ApplicationsShunt Regulator01005514Single Supply Comparator withTemperature Compensated Threshold01005515LM4317Typical Applications(Continued)Series Regulator01005516Output Control of a ThreeTerminal Fixed Regulator01005517Higher Current Shunt Regulator01005518Crow Bar01005519 LM4318Typical Applications(Continued)Over Voltage/Under VoltageProtection Circuit01005520Voltage Monitor01005521LM4319Typical Applications(Continued)Delay Timer01005522Current Limiter or Current Source01005523Constant Current Sink01005524Application Info1.0MountingTo ensure that the geometry of the micro SMD packagemaintains good physical contact with the printed circuitboard,pin A1(NC)must be soldered to the pcb.Please seeAN-1112for more detailed information regarding boardmounting techniques for the micro SMD package.2.0LM431micro SMD Light SensitivityWhen the LM431micro SMD package is exposed to brightsunlight,normal office fluorescent light,and other LED’s andlasers,it operates within the guaranteed limits specified inthe electrical characteristics table.LM43110Physical Dimensionsinches (millimeters)unless otherwise noted8-Pin SOICNS Package Number M08ASOT-23Molded Small Outline Transistor Package (M3)NS Package Number MF03ALM43111Physical Dimensionsinches (millimeters)unless otherwise noted (Continued)NS Package Number Z03AL M 431 12Physical Dimensionsinches (millimeters)unless otherwise noted (Continued)NOTES:UNLESS OTHERWISE SPECIFIED 1.EPOXY COATING2.63Sn/37Pb EUTECTIC BUMP3.RECOMMEND NON-SOLDER MASK DEFINED LANDING PAD.4.PIN A1IS ESTABLISHED BY LOWER LEFT CORNER WITH RESPECT TO TEXT ORIENTATION.REMAINING PINS ARE NUMBERED.5.XXX IN DRAWING NUMBER REPRESENTS PACKAGE SIZE VARIATION WHERE X1IS PACKAGE WIDTH,X2IS PACKAGE LENGTH AND X3IS PACKAGE HEIGHT.6.REFERENCE JEDEC REGISTRATION MO-211,VARIATION BA.4-Bump micro SMDX1=0.777X2=0.904X3=0.850NS Package Number BPA04AFBNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.For the most current product information visit us at .LIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systems which,(a)are intended for surgical implant into the body,or (b)support or sustain life,and whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.BANNED SUBSTANCE COMPLIANCENational Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2)and the Banned Substances and Materials of Interest Specification (CSP-9-111S2)and contain no ‘‘Banned Substances’’as defined in CSP-9-111S2.National Semiconductor Americas Customer Support CenterEmail:new.feedback@ Tel:1-800-272-9959National SemiconductorEurope Customer Support CenterFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)6995086208English Tel:+44(0)8702402171Français Tel:+33(0)141918790National Semiconductor Asia Pacific Customer Support CenterEmail:ap.support@National SemiconductorJapan Customer Support Center Fax:81-3-5639-7507Email:jpn.feedback@ Tel:81-3-5639-7560LM431Adjustable Precision Zener Shunt Regulator。

FAIRCHILD PN4391 PN4392 PN4393 数据手册

GDSN-Channel SwitchThis device is designed for low level analog switching, sample TA = 25°C unless otherwise notedValue30- 3050-55 to +150G SDTO-92SOT-23Mark: 6J / 6K / 6GNOTE: Source & Drain are interchangeablePN4391 / 4392 / 4393 / MMBF4391 / 4392 / 4393PN4391 / 4392 / 4393 / MMBF4391 / 4392 / 4393ITEM DESCRIPTIONBase of Package to Lead Bend Component Height Lead Clinch Height Component Base HeightComponent Alignment ( side/side )Component Alignment ( front/back )Component Pitch Feed Hole Pitch Hole Center to First Lead Hole Center to Component Center Lead Spread Lead Thickness Cut Lead Length Taped Lead Length Taped Lead Thickness Carrier Tape ThicknessCarrier Tape Width Hold - down Tape Width Hold - down Tape position Feed Hole Position Sprocket Hole Diameter Lead Spring OutSYMBOL b Ha HO H1Pd Hd P PO P1P2F1/F2d L L1t t1W WO W1W2DO SDIMENSION 0.098 (max)0.928 (+/- 0.025)0.630 (+/- 0.020)0.748 (+/- 0.020)0.040 (max)0.031 (max)0.500 (+/- 0.020)0.500 (+/- 0.008)0.150 (+0.009, -0.010)0.247 (+/- 0.007)0.104 (+/- 0 .010)0.018 (+0.002, -0.003)0.429 (max)0.209 (+0.051, -0.052)0.032 (+/- 0.006)0.021 (+/- 0.006)0.708 (+0.020, -0.019)0.236 (+/- 0.012)0.035 (max)0.360 (+/- 0.025)0.157 (+0.008, -0.007)0.004 (max)Note : All dimensions are in inches.ITEM DESCRIPTIONSYSMBOL MINIMUM MAXIMUM Reel DiameterD113.97514.025Arbor Hole Diameter (Standard)D2 1.160 1.200 (Small Hole)D20.6500.700Core DiameterD3 3.100 3.300Hub Recess Inner Diameter D4 2.700 3.100Hub Recess DepthW10.3700.570Flange to Flange Inner WidthW2 1.6301.690Hub to Hub Center WidthW32.090Note: All dimensions are inchesTO-92 Tape and Reel TapingDimension Configuration: Figure 4.0HaH1HOPOP2P1F1DOPPdbd L1LSWOW2Wt t1HdW1TO-92 ReelConfiguration: Figure 5.0User Direction of FeedSEN SITIVE D EVICESELECT ROSTATIC D1D3Customized LabelW2W1W3F63TNR Label D4D2Human Readabl e Label sampleDimensions are in millimeterPkg type A0B0WD0D1E1E2FP1P0K0TWcTcSOT-23(8mm)3.15+/-0.102.77+/-0.108.0+/-0.31.55+/-0.051.125+/-0.1251.75+/-0.106.25min3.50+/-0.054.0+/-0.14.0+/-0.11.30+/-0.100.228+/-0.0135.2+/-0.30.06+/-0.02Dimensions are in inches and millimetersTape SizeReel OptionDim ADim BDim CDim DDim NDim W1Dim W2Dim W3 (LSL-USL)8mm7" Dia7.00177.80.0591.5512 +0.020/-0.00813 +0.5/-0.20.79520.2 2.165550.331 +0.059/-0.0008.4 +1.5/00.56714.40.311 – 0.4297.9 – 10.98mm 13" Dia13.003300.0591.5512 +0.020/-0.00813 +0.5/-0.20.79520.24.001000.331 +0.059/-0.0008.4 +1.5/00.56714.40.311 – 0.4297.9 – 10.9See detail AADim A max13" Diameter Option7" Diameter OptionDim A MaxSee detail AAW3W2 max Measured at HubW1 Measured at HubDim NDim D minDim CB Min DETAIL AANotes: A0, B0, and K0 dimensions are determined with respect to the EIA/Jedec RS-481rotational and lateral movement requirements (see sketches A, B, and C).20 deg maximum component rotation0.5mm maximum0.5mm maximumSketch C (Top View)Component lateral movementTypical component cavitycenter line20 deg maximumTypical component center lineB0A0Sketch B (Top View)Component RotationSketch A (Side or Front Sectional View)Component RotationUser Direction of FeedSOT-23 Embossed Carrier Tape Configuration: Figure 3.0SOT-23 Reel Configuration: Figure 4.0P1A0D1FW E1E2Tc WcK0TB0D0P0P2SOT-23 Tape and Reel Data, continuedTRADEMARKSThe following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORTDEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant intothe body, or (b) support or sustain life, or (c) whosefailure to perform when properly used in accordancewith instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.2. A critical component is any component of a lifesupport device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.PRODUCT STATUS DEFINITIONS Definition of Terms Datasheet Identification Product Status DefinitionAdvance InformationPreliminary No Identification Needed Obsolete This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.This datasheet contains preliminary data, andsupplementary data will be published at a later date.Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.This datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor.The datasheet is printed for reference information only.Formative or In DesignFirst ProductionFull ProductionNot In ProductionDISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY , FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.PowerTrench QFET™QS™QT Optoelectronics™Quiet Series™SILENT SWITCHER SMART START™SuperSOT™-3SuperSOT™-6SuperSOT™-8FASTr™GlobalOptoisolator™GTO™HiSeC™ISOPLANAR™MICROWIRE™OPTOLOGIC™OPTOPLANAR™PACMAN™POP™Rev. GACEx™Bottomless™CoolFET™CROSSVOLT ™DOME™E 2CMOS TM EnSigna TM FACT™FACT Quiet Series™FAST SyncFET™TinyLogic™UHC™VCX™。

431芯片原理,如何「自制」431芯片?

431芯片原理,如何「自制」431芯片?简介:根据431基准电压芯片内部结构电路,用三极管自制431基准电压芯片。

你将会看到8个板块内容:项目简介、设计方案、电路原理、原理图设计、PCB设计、焊接与调试、项目资料、设计图一、项目简介1.1 概述431电压基准芯片为3脚稳压集成电路,431基准电压源具有良好的热稳定性能,三端可调分流,也被称为电压调解器或三端取样集成电路。

凭借体积小、重量轻、精度高、稳定可靠、基准电压精密可调、输出电流大,且价格便宜等多种优良品质,深得工程师和爱好者的喜欢,广泛应用在各种电源电路中。

目前我们看到的例如TL431、KA431、μA431、LM431等不同名称的431芯片就是不同厂家所推出的431电压基准芯片,那么现在我们来根据431的内部结构一起来DIY一款自己的芯片,我把它命名为LC431。

图1-1 LC431_TO-92封装1.2 设计特点•用分立器件搭建,深入学习电路•使用直插器件,便于初学者焊接与调试•板载香蕉头与排针接口,便于调试与扩展•搭配测试底板,完成431常规实验的学习1.3 应用电路•精密基准电压源•可调稳压电路•恒流源电路•电压比较器•过电压保护电路二、总体设计方案2.1 内部结构根据厂商所提供的431数据手册中,找到如下图中的内部结构电路图。

如图可知431基准电压源由基准电压电路、误差放大器电路、达林顿输出电路和二极管保护电路所组成。

图2-1 431的内部结构电路图431的电路符号如图2-2所示,其使用方法与稳压管一样,阴极(K)接高电平,阳极(A)接低电平,R为参考基准端。

图2-2 431的电路符号图2-3为431的等效功能示意图,由运算放大器、保护二极管、NPN型三极管以及2.5V的精密基准电压源Vref所组成。

参考端(R)接运放的同相输入端,2.5V(Vref)基准电压源接运放的反相输入端。

运放相当于一个误差放大器,会把同相输入端与反相输入端的电压差放大很多倍。

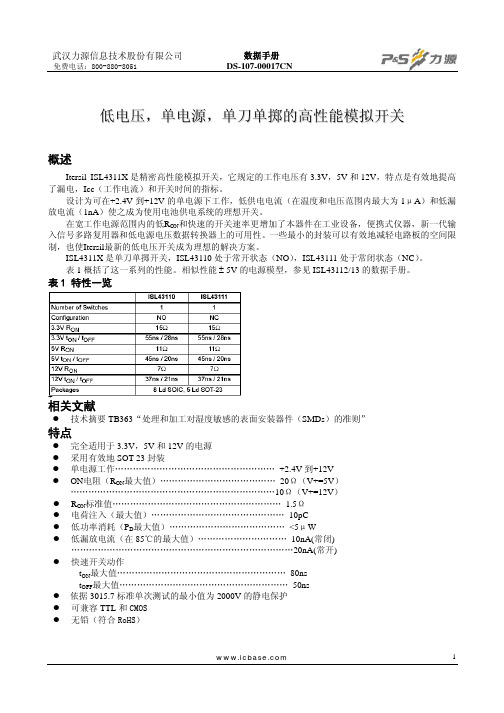

高精密高性能模拟开关ISL4311x中文资料

注:1. 所示开关为逻辑“0”输入

引脚描述

2

武汉力源信息技术股份有限公司

免费电话:800-880-8051

数据手册 DS-107-00017CN

真值表

注:逻辑“0” ≤ 0.8V,逻辑“1” ≥ 2.4V 订购信息

注:Intersil无铅产品采用特殊的无铅材料制成,模塑料/晶片的附属材料和100%无光泽锡盘引脚符合 RoHS标准,兼容SnPb和无铅低温焊接操作。Intersil无铅产品在无铅峰值回流温度中属于MSL级别分类, 完全满足和超过IPC/GEDEC JSTD-020的无铅要求。

免费电话:800-880-8051

数据手册 DS-107-00017CN

应用

电池供电,手提和便携式设备 ——蜂窝式/移动式电话,寻呼机 ——膝上型,笔记本,掌上型 PDAs 通信系统 ——无线电收音机 ——用户交换机,自动用户交换机 测试设备 ——逻辑和光谱分析器 ——便携式仪表,数字式电压表,数字万用表 医学设备 ——超声波,MRI,CAT 扫描 ——心电图仪,血液分析器 平视显示器 音频和视频转换 通用目的电路 ——+3V/+5V 数模转换器和模数转换器 ——抽样和保持电路 ——数字滤波器 ——运算放大器增益转换电路 ——高频模拟转换 ——高速多路复用 ——积分复位电路

最大引线温度(10s,低温焊接)…………………………………… 260℃

最大储存温度范围 ………………………………………… -65℃到 150℃

最大引脚温度范围(低温焊接 10s) ……………………… 300℃

注意:强度超出所列的极限参数可能导致器件的永久性损坏。这些仅仅是极限参数,并不意味着在极限条

典型性能曲线图

FAIRCHILD FQPF3N20 数据手册

现货库存、技术资料、百科信息、热点资讯,精彩尽在鼎好!1FEATURES•Advanced New Design •Avalanche Rugged Technology •Rugged Gate Oxide Technology •Very Low Intrinsic Capacitances •Excellent Switching Characteristics •Unrivalled Gate Charge: 6.0nC (Typ.)•Extended Safe Operating Area •Lower R DS(ON): 2.06Ω (Typ.)ABSOLUTE MAXIMUM RATINGSTHERMAL RESISTANCE SymbolCharacteristics Value Units V DSSDrain-to-Source Voltage −200V I DContinuous Drain Current (T C = 25°C)−2.2A Continuous Drain Current (T C = 100°C)−1.39I DMDrain Current-Pulsed −8.8A V GSGate-to-Source Voltage ±30V E AS Single Pulsed Avalanche Energy 150mJ I ARAvalanche Current −2.2A EARRepetitive Avalanche Energy 3.2mJ dv/dtPeak Diode Recovery dv/dt −5.5V/ns P DTotal Power Dissipation (T C = 25°C)Linear Derating Factor 320.26W W/°CT J , T STGOperating Junction and Storage Temperature Range −55 to +150°C T L Maximum Lead Temp. for Soldering Purposes, 1/8” from case for 5-seconds 300SymbolCharacteristics Typ.Max.Units R θJCJunction-to-Case − 3.9°C/WR θJA Junction-to-Ambient −62.5BV DSS = −200VR DS(ON) = 2.7ΩI D = −2.2A TO-220F1. Gate2. Drain3. Source321QFET P-CHANNEL FQPF3P20© 1999 Fairchild Semiconductor CorporationREV. B310-11001010100200300400C = C + C (C = shorted)C = C + CC = C ¡Ø Note ; 1. V = 0 V 2. f = 1 MHz C rssC oss C iss C a p a c i t a n c e s [p F ]-V DS , Drain-Source Voltage [V]Fig 1. Output CharacteristicsFig 2. Transfer CharacteristicsFig 6. Gate Charge vs. Gate-Source Voltage Fig 5. Capacitance vs. Drain-Source VoltageFig 4. Source-Drain Diode Forward VoltageFig 3. On-Resistance vs. Drain Current024680246810¡Ø Note : T = 25¡ÉV GS = - 20V V GS = - 10V R D S (o n ) , [Ω]D r a i n -S o u r c e O n -R e s i s t a n c e -I D , Drain Current [A]01234567024681012V DS = -100VV DS = -40VV DS = -160V ¡Ø Note : I = -2.8 A-V G S , G a t e -S o u r c e V o l t a g e [V ]Q G , Total Gate Charge [nC]10-110010110-1100 VTop : -15.0 V-10.0 V-8.0 V-7.0 V-6.5 V-6.0 VBottom : -5.5 V ¡Ø Note : 1. 250¥ìs Pulse Test 2. T = 25¡É-I D , D r a i n C u r r e n t [A ]-V DS , Drain-Source Voltage [V]24681010-1100¡Ø Note1. V = -40V2. 250¥ìs Pulse Test -55¡É150¡É25¡É-I D , D r a i n C u r r e n t [A ]-V GS , Gate-Source Voltage [V]0.40.8 1.2 1.6 2.0 2.4 2.810-110025¡É150¡É¡Ø Note : 1. V = 0V 2. 250¥ìs Pulse Test-I D R , R e v e r s e D r a i n C u r r e n t [A ]-V SD , Source-Drain Voltage [V]QFET P-CHANNEL FQPF3P20Fig 12. Gate Charge Test Circuit & Waveform Fig 13. Resistive Switching Test Circuit & WaveformsFig 14. Unclamped Inductive Switching Test Circuit & Waveforms--------------------E=LAS LI AS2----21BV DSS--V DDBV DSSV inV DS90%10%td(on)trtontofftd(off)tfChargeV GS-10VQ gQ gs Q gdV DDV DSBV DSSV DDI ASV DS (t)I D (t)tp TimeV DD( 0.5 rated V DS )-10VV DSR LDUTR G-3mAV GSDUTV DS300nF50K200nF12VSame Typeas DUT-10V DUTR GLI DQFET P-CHANNEL FQPF3P2057TO-220F Package Dimensions (7.00)(0.70)MAX1.47(3°)#13.30±.1015.8±.2015.87 ±0.206.68 ±0.209.75±.304.7±.210.16 ±0.20(1.00x45°) 2.54 ±0.200.80 ±0.109.40 ±0.20 2.76 ±0.200.35 ±0.10ø3.18 ±0.102.54TYP [2.54 ±0.20] 2.54TYP[2.54 ±0.20]0.50+0.10–0.05TO-220F (FS PKG CODE AQ)QFET P-CHANNEL FQPF3P20Dimensions in MillimetersSeptember 1999, Rev BTRADEMARKSThe following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY , FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBEDHEREIN; NEITHER DOES IT CONVER ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHOLD SEMICONDUCTOR CORPORATION.As used herein:PRODUCT STATUS DEFINITIONSDefinition of TermsDatasheet IdentificationProduct Status Definition Advance Information Formative orIn DesignThis datasheet contains the design specifications for product development. Specifications may change in any manner without notice.Preliminary First Production This datasheet contains preliminary data, and supplementarydata will be published at a later data.Fairchild Semiconductor reserves the right to make changesat any time without notice in order to improve design.No Identification Needed Full Production This datasheet contains final specifications. FairchildSemiconductor reserves the right to make changes at any timewithout notice in order to improve design.Obsolete Not In Production The datasheet contains specifications on a product that hasbeen discontinued by Fairchild Semiconductor.The datasheet is printed for reference information only.1. Life support devices or systems are devices orsystems which, (a) are intended for surgical implant intothe body, or (b) support or sustain life, or (c) whosefailure to perform when properly used in accordance withinstructions for use provided in the labeling, can bereasonably expected to result in significant injury to theuser.2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.ACEx TMCoolFET TMCROSSVOLT TME 2CMOS TMFACT TMFACT Quiet Seties TMFAST ®FASTr TMGTO TMHiSeC TM TinyLogic TM UHC TM VCX TMISOPLANAR TM MICROWIRE TM POP TM PowerTrench ®QFET TM QS TM Quiet Series TM SuperSOT TM -3SuperSOT TM -6SuperSOT TM -8。

LM431作大功率可调稳压电源

利用LM431作大功率可调稳压电源

作者:佚名来源:本站整理发布时间:2007-1-28 11:35:29 发布人:dunan

减小字体增大字体

精密电压基准IC LM431是TO-92封装如图1所示。

其性能是输出压连续可调达3 6V,

工作电流范围宽达0.1。

100mA,动态电阻典型值为0.22欧,输出杂波低。

图2是LM431的典型应用,其中③、②脚两端输出电压V=2.5(R2十R3)V/R3。

如果改变R2的阻值大小,就可以改变输出基准电压大小。

图3是利用它作电压基准和驱动外加场效应管K790作调整管构成的输出电流大(约6A)、电路简单、安全的稳压电源。

工作原理如图3所示,220v电压经变压器B降压、D1-D4整流、C1滤波。

此外D5、D6、C2、C3组成倍压电路(使得Vdc=60V),Rw、R3组成分压电路,LM431、R1组成取样放大电路,9013、R2组成限流保护电路,场效应管K790作调整管(可直接并联使用)以及C5是输出滤波器电路等。

稳压过程是:当输出电压降低时,f点电位降低,经LM431内部放大使e点电压增高,经K790调整后,b点电位升高;反之,当输出电压增高时,f点电位升高,e点电位降低,经K790调整后,b点电位降低。

从而使输出电压稳定。

当输出电流大于6A时,三极管9013处于截止,使输出电流被限制在6A以内,从而达到限流的目的。

本电路除电阻R1选用2W、R2选用5W外,其它元件无特殊要求,其元件参

数如图3所示。

LM431AIZ中文资料

Electrical Characteristics

(TA = +25°C, unless otherwise specified) Parameter

Reference Input Voltage Deviation of Reference Input Voltage OverTemperature Ratio of Change in Reference Input Voltage to the Change in Cathode Voltage Reference Input Current Deviation of Reference Input Current Over Full Temperature Range Minimum Cathode Current for Regulation Off - Stage Cathode Current Dynamic Impedance

Description

The LM431A/LM431B/LM431C are three terminal output adjustable regulators with thermal stability over operating temperature range. The output voltage can be set any value between VREF (approximately 2.5 volts) and 36 volts with two external resistors. These devices have a typical dynamic output impedance of 0.2Ω Active output circuit provides a sharp turn-on characteristic, making these devices excellent replacement for Zener Diodes in many applications.

ANALOG DEVICES UG-431 数据手册