多核 DSP(如TI C6678)基础软件开发平台

TMS320C6678硬件设计说明(中文版)

面向多相机接入的TMS320C6678(IISC-6678)图像处理系统硬件设计说明书目录1. 综述 (4)1.1 关键特性 (4)1.2 功能性综述 (5)1.3 基础操作 (5)1.4 引导模式和引导配置的开关设置 (6)1.5 电源供给 (6)2. IISC-6678板卡的介绍 (7)2.1 IISC-6678板卡的boot模式和boot配置的开关设置 (8)2.2 JTAG仿真概述 (8)2.3 时钟分配 (9)2.4 I2C Boot EEPROM/SPI NOR Flash (9)2.5 UART (10)2.6 FPGA (10)2.7 千兆以太网接口 (11)2.8 串行RapidIO接口 (11)2.9 DDR3外部存储器接口 (12)2.10 16bit异步外部存储器接口(EMIF-16) (13)2.11 HyperLink接口 (13)2.12 PCIe接口 (14)2.13 FMC接口 (14)3. IISC-6678板卡物理规格 (17)3.1 板卡布局 (17)3.2 连接器种类 (19)3.2.1 EMU1&DSP_JTAG,TI 60引脚& DSP_JTAG连接器 (20)3.2.2 JP2,风扇连接器 (21)3.2.3 J1,HyperLink连接器 (22)3.2.4 T1、T2,以太网连接器 (23)3.2.5 TAP_FPGA1,FPGA JTAG连接(仅限生产商使用) (24)3.2.6 J3,FMC连接器 (24)3.3 DIP和按钮开关 (31)3.3.1 RST_FULL1, Full Reset (32)3.3.2 RST_COLD1, Cold Reset (32)3.3.3 RST_WARM1, Warm Reset (32)3.3.4 SW2,SW3,SW4 和SW5,DSP Boot模式和配置 (32)3.3.5 SW6, DSP PCIESS使能和用户自定义开关配置 (33)3.4 系统LED (34)4. 系统电源供给 (35)4.1 各模块功耗 (35)4.2 电源分配 (36)4.3 电源上电时序 (37)5. IISC-6678板卡上FPGA 功能描述 (38)5.1 FPGA概述 (38)5.2 FPGA各信号描述 (39)5.3 操作顺序 (45)5.3.1 上电时序 (45)5.3.2 掉电时序 (46)5.4 复位详解 (46)5.4.1 复位操作 (46)5.4.2 复位开关触发 (47)6. 英文缩写注释 (49)1.综述本章讲述IISC-6678板卡的综述以及它所带有的关键特性和相关图解1.1 关键特性1.2 功能性综述1.3 基础操作1.4 可配置的开关设置1.5 电源供给1.1 关键特性IISC-6678是一块提供高性能、低成本、单机发展平台的板卡,此平台供用户评估和开发德州仪器的TMS320C6678 DSP的应用软件。

TMS320C6678多核DSP的HyperLink应用

设计了 H y p e r L i n k的映射 结构 , 并 分析 了性 能 , 对 多处 理器 间通信 具有 一定 的参考 价值 。

关键 词 : T M¥ 3 2 0 C 6 6 7 8 ; Hy p e r L i n k ; 处 理 器 问 通 信 中图分 类号 : T N 9 1 5 . 0 4 文 献标识 码 : A D O I :1 0 . 1 9 3 5 8 / j . i s s n . 1 6 7 4 — 7 7 2 0 . 2 0 1 7 . 0 3 . O 1 1

首先介绍 了 H y p e r L i n k的 原 理 与 机 制 , 然 后 分 析 芯 片 之 间 Hy p e r L i n k通 信 的 映射 原 理 , 给 出 了通 信 连 接 的实 现 方 法 , 并通过对 多种 映射关 系 进行 对 比, 得 出 优 缺 点 和 使 用 范 围, 为嵌 入 式 多处 理器 系统 的设 计 提 供 参考 。 1 Hy p e r L i n k机 制

摘 要 : 嵌 入 式应 用 中采 用 多处理 系统所 面临 的主要难 题是 多处理 器之 间 的数 据 通信 。通过 对 K e y — s t o n e架构 T MS 3 2 0 C 6 6 7 8处

理器的 H y p e r L i n k通 信 机 制 进 行 研 究 , 利 用其 高 速 、 低 延迟 、 引脚 少 的 特 性 实 现 处 理 器 间 的 高 速 数 据 交 换 。 从 实 际 应 用 的 角 度 ,

Ke y wor ds:TM S 3 20C6 6 78;Hy pe r L i n k;i n t e r — p r o c e s s o r c o mm u n i c a t i o n

多核dsptms320c6678高速信号处理板卡

新一代多核DSP TMS320C6678的通用信号处理板卡〔京齐天盛达电力科技〕C6678_4DSP_DDR3是基于TI 新一代多核DSP TMS320C6678的通用处理板卡。

板卡满足ANSI\VITA65平台标准,是一款适用于高速数据通讯、处理、存储的理想平台。

可为雷达、电子对抗、图像处理、声纳等高速实时信号处理任务提供可靠的硬件保障。

板上还预留高速扩展子卡接口,FPGA的充裕IO、DSP的SRIO/HyperLink/I2C/GPIO/SPI等信号都连入其中,方便用户自制子板扩展如Camera-link、高速AD/DA、光纤接口等。

性能指标处理才能1片V6SX315T FPGA4片TMS320C6678 DSP单板处理才能:1280 GMAC/s、640 GFLOPs存储才能单板DDR3存储才能:8/16/32GB可选互联才能板内互联:2个DSP间通过HyperLink总线互联,实现40Gbps的高速数据传输4片C6678之间及与FPGA之间通过SRIO Switch实现RapidIO互联,SRIO支持速率5Gbaud(SRIO 2.1)4片C6678之间及与FPGA之间通过PCIe Switch实现PCIe的互联,PCIE支持速率为5Gbaud(PCIe 2.0)板间互联:P0:满足VPX标准,电源、系统维护等;P1:满足VPX标准,板内SRIO Switch出4个4XRapidIO;P2:满足VPX标准,板内PCIe Switch出2个8XPCIe;P3:由板内FPGA出2个4XGTX;P4:满足VPX标准:2个千兆以太网;P5:由板内FPGA出自定义总线;P6:由板内FPGA出自定义总线;物理特性尺寸:标准6U 板卡,233X160X16(mm) 运行温度商业级运行温度:0°C ~ 100°C 扩展运行温度:- 40°C ~ 105°C 功耗:约70W散热:导冷散热和风冷散热系统框图C6678DDR3DDR3C6678DDR3DDR3P0P1P2P3P4P5P6SRIO SwitchC66781、X4 SRIO2、X2 PCIe3、EMAC 以太网4、 4 * X4 SRIO5、X4 PCIe6、 2 * X4 RoketIO7、2x 201Link8、HyperLink 10、FPDP 、同步定时总线9、板间以太网C6678PCIe Switch11 、X4 PCIe 12、 2 * X4SRIO FPGA电源CPLDIIC 隔离驱动器使能控制Power good使能控制温感EEPROMEEPROMEEPROMEEPROMIICIICIICIICIICIICIIC系统复位FPGA ResetPCIe ResetDSP0ResetDSP1ResetDSP2ResetDSP3Reset13、复位信号14、IIC 总线15、电源使能和监控板卡照片北京齐天盛达电力科技提供高速信号处理板及解决方案。

TMS320C6678开发板(DSP+Zynq)RTOS综合功能案例,嵌入式必看!

TMS320C6678开发板(DSP+Zynq)RTOS综合功能案例,嵌入式必看!前言减少在产品开发过程中对DSP外设接口程序进行整合的难度,我们提供对DSP主要外设接口实现底层初始化的RTOS综合功能测试IFD(Integrated Function Demo)案例程序,助力有需要的朋友基于此IFD案例程序模板进行开发,加快项目研发进度。

本次测试板卡为TMS320C6678开发板,它是一款基于TI KeyStone架构C6000系列TMS320C6678八核C66x定点/浮点DSP,以及Xilinx Zynq-7000系列XC7Z045/XC7Z100 SoC处理器设计的高端异构多核评估板,TMS320C6678开发板每核心主频可高达1.25GHz,XC7Z045/XC7Z100集成PS端双核ARM Cortex-A9 + PL 端Kintex-7架构28nm可编程逻辑资源,引出双路CameraLink、双路SFP+光口、四路千兆网口、双路SATA、双路PCIe、四路USB、双路CAN、双路CAMERA、HDMI IN/OUT、LVDS、LCD、RS485、RS232、Micro SD、HPC FMC等接口。

IFD案例主要功能为EEPROM、SPI FLASH和NAND FLASH等存储设备读写速率测试,以及PCIe、SRIO和Ethernet等外设接口测试,详细说明见下表。

表 1设备/接口测试内容读写速率write:0.02MB/sEEPROM 数据读写速率及正确性read:0.04MB/swrite:0.48MB/sNAND FLASH 数据读写速率及正确性read:0.80MB/swrite:0.29MB/sSPI FLASH 数据读写速率及正确性read:1.27MB/sDDR 数据写入速率及正确性write:33351Mbpswrite:690MBpsPCIe 作为PCIe EP设备进行通信read:639MBpswrite:12060MbpsSRIO(ZYNQ) 数据读写速率及正确性read:7616MbpsEthernet IP地址动态获取/UART 串口回显/KEY 按键检测/本文档案例程序默认使用DSP端主频为1GHz的核心板,通过TL-XDS200仿真器加载运行进行操作效果演示。

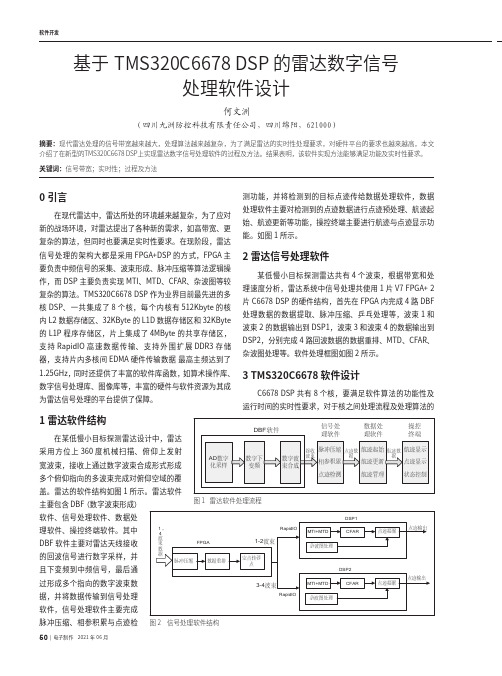

基于TMS320C6678 DSP的雷达数字信号处理软件设计

50 | 电子制作 2021年06月复杂的算法,但同时也要满足实时性要求。

在现阶段,雷达信号处理的架构大都是采用FPGA+DSP 的方式,FPGA 主要负责中频信号的采集、波束形成、脉冲压缩等算法逻辑操作,而DSP 主要负责实现MTI、MTD、CFAR、杂波图等较复杂的算法。

TMS320C6678 DSP 作为业界目前最先进的多核DSP、一共集成了8个核,每个内核有512Kbyte 的核内L2数据存储区、32KByte 的L1D 数据存储区和 32KByte 的L1P 程序存储区,片上集成了4MByte 的共享存储区,支持RapidIO 高速数据传输、支持外围扩展DDR3存储器,支持片内多核间EDMA 硬件传输数据 最高主频达到了1.25GHz,同时还提供了丰富的软件库函数,如算术操作库、数字信号处理库、图像库等,丰富的硬件与软件资源为其成为雷达信号处理的平台提供了保障。

1 雷达软件结构在某低慢小目标探测雷达设计中,雷达采用方位上360度机械扫描、俯仰上发射宽波束,接收上通过数字波束合成形式形成多个俯仰指向的多波束完成对俯仰空域的覆盖。

雷达的软件结构如图1所示。

雷达软件主要包含DBF (数字波束形成)软件、信号处理软件、数据处理软件、操控终端软件。

其中DBF 软件主要对雷达天线接收的回波信号进行数字采样,并且下变频到中频信号,最后通过形成多个指向的数字波束数据,并将数据传输到信号处理软件,信号处理软件主要完成脉冲压缩、相参积累与点迹检2 雷达信号处理软件某低慢小目标探测雷达共有4个波束,根据带宽和处理速度分析,雷达系统中信号处理共使用1片V7 FPGA+ 2片C6678 DSP 的硬件结构,首先在FPGA 内完成4路DBF 处理数据的数据提取、脉冲压缩、乒乓处理等,波束1和波束2的数据输出到DSP1,波束3和波束4的数据输出到DSP2,分别完成4路回波数据的数据重排、MTD、CFAR、杂波图处理等。

基于TMS320C6678的多核DSP并行处理应用技术研究共3篇

基于TMS320C6678的多核DSP并行处理应用技术研究共3篇基于TMS320C6678的多核DSP并行处理应用技术研究1随着信息技术的发展和科技应用的不断提升,现代社会对计算处理能力的需求也越来越高。

但传统的单核张量处理器受到性能瓶颈的限制,在处理大规模数据和高负载任务时面临着无法满足需求的问题。

为此,多核处理器正在被广泛应用和研究,并成为当前高性能计算领域的热点技术。

基于TMS320C6678的多核DSP并行处理就是其中一种应用技术,它利用DSP(Digital Signal Processor)的特殊结构和灵活性,在数据处理、信号处理、声音处理等方面表现出眼花缭乱的性能。

该技术在信息处理、通信、影像处理、控制及自动化等领域广泛应用,并在科技创新和社会进步中发挥着巨大的作用。

多核DSP并行处理技术的核心是通过利用多个处理核心的协作,将每个处理核心的任务进行分解并行执行。

TMS320C6678作为TI公司推出的多核DSP,通过采用基于C66x核心的对称多处理(SMP)和低延迟互联技术,在多处理器之间实现高效通信、高性能计算和低功耗运行,实现高性能计算需求的快速响应。

多核DSP并行处理技术在应用中还可以选用一些常用的并行编程模型来进行代码开发与优化。

其中,OpenMP模型适用于多线程程序,可以在多核心某一个处理器上执行,可以较容易地实现自动化并行计算; pthread模型为应用提供了多线程机制,可以用于多核DSP系统共享内存下的多线程并行计算; MPI模型则是适用于多节点通信和分布式计算,更适合大规模的并行计算,这种模型需要考虑数据分布等问题,对编程能力要求较高。

在多核DSP并行处理的应用实例中,通信领域是其中之一。

以TMS320C6678为核心的网关系统,将数据在两个不同的网络之间转发,通过在不同节点的DSP中使用OpenMP编程模型,提高数据处理并行性能。

此外,多核DSP并行处理技术还在无线通信、人工智能、视觉、图像分析、智能检测等领域有着广泛的应用,其应用广泛性和高并发性也确实满足了现代社会高速发展的需求。

C6678多核处理器开发板学习总结

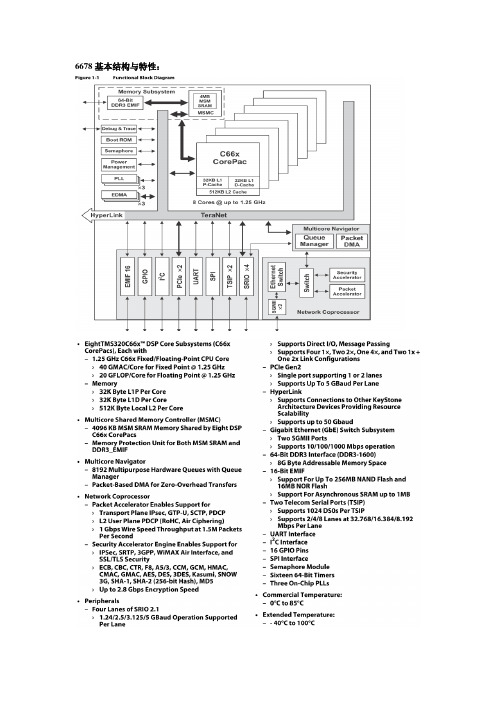

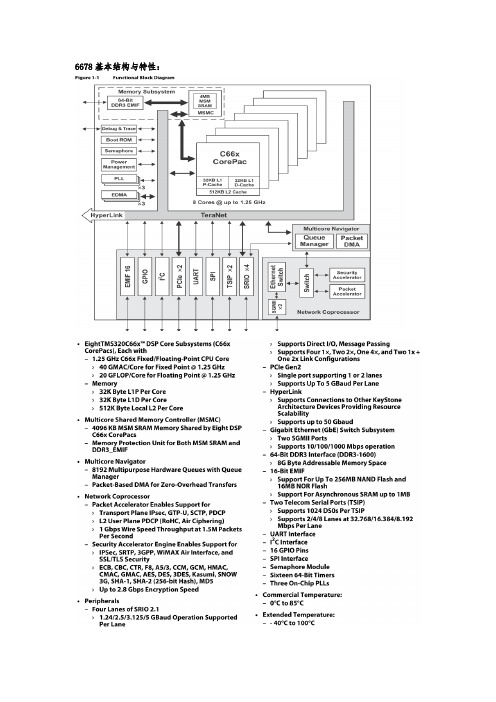

6678基本结构与特性:6678评估板功耗表:6678空间映射:6678加载过程BOOT配置引脚:8种加载方式:EIMF加载模式:8种PLL BOOT配置0x872E00-0x87FFFF保留给boot配置用,保存了BOOT外设的基本配置参数。

加载过程:上电后,6678读取BOOTMODE电平,数据存储在DEVSTAT寄存器中,改寄存器数值可编程,各个Core可不同的BOOT模式加载。

6678首先从Core0加载,Core1执行idle处于中断等待状态,当Core0加载完成后,首先Core0的BOOT_MAGIC_ADDRESS被写入加载程序的起始地址,Core0从BOOT_MAGIC_ADDRESS执行,Core0应该对次Core的BOOT_MAGIC_ADDRESS写入执行地址,同时写入IPCGRn寄存器触发次Core的中断,对6678而言BOOT_MAGIC_ADDRESS的映射地址是各Core本地L2的0x807FFF,在加载期间,所有的LP、LD被配置为Cache,L2被配置为可寻址Memory每个Core加载完成BOOTCOMPLETE寄存器被标志参看手册:sprugy56678基本外设:电源监控:EIMF :评估板连接512Mb NandFlash <NUMONYX_NAND512R3A2DZA6E>DDR3:评估板连接1Gb/1333MHZ DDR3 <SAMSUNG_K4B1G1646G_BCH9> ECC连接1Gb/1333MHZ DDR3(ECC) <SAMSUNG_K4B1G1646G_BCH9> 未连接512Mb/1333MHZ DDR3<SAMSUNG_K4B1G0846G_BCH9 >主要用到引脚如下:DDRA[0:15]/DDRD[0:63] 数据/地址DDR3_ECKE_0DDR3_ECS_0#DDR3_ECAS# DDRA为列地址DDR3_ERAS# DDRA为行地址DDR3_EWE# 写使能?DDR3_EBA_[0:2] BANK选通DDR3_EDM_[0:8] ?DDR3_EDQSP/N_[0:8]DDR3_ECC_[0:8] 0:7 连接SAMSUNG_K4B1G1646G_BCH9的DDRD[0:7] 纠错DDR3_EMRESETNDDR3_EODT_0 端接电阻DDRSLRATE_[0:1] 回转速率,00最快TSIP:评估板连接接口SPI:评估板连接128Mb SPI NorFlash <NUMONYX_N25Q128A21BSF40F> 评估板连接时钟发生器<TI_CDCE62005RGZT>PCIE:评估板连接接口MDIO:评估板连接PCA9306DCUT 电平转换至PHY芯片配置端<88E1111-B2>IIC:评估板连接1Mb <ST_M24M01_HRMN6TP>Hyperlink:评估板连接CONN接口<IPASS PLUS HD_36H>SRIO:评估板连接接口UART:评估板连接RS232 <TI_MAX3221ECPWR>评估板连接USB _CHB通道<FT2232HL>FT2232HL 配置芯片<ATMEL_AT93C46DN_SH_T IIC>EMAC:评估板连接PHY芯片<MARVELL_88E1111_B2_BAB1C000>评估板时钟DSP时钟:25MHZ输入,可级联使用<CDCE62005RGZT>,由FPGA配置,再使能DSP DSP_CORE_CLKP/N:100MHZDSP_DDR_CLKP/N:66.667MHZDSP_PA_SS_CLKP/N:100MHZDSP_SRIO_SGMII_CLKP/N:312.5MHZDSP_MCM_CLKP/N:312.5MHZDSP_PCIE_CLKP/N:100MHZFT2232HL时钟:12MHZ88E1111时钟:25MHZFPGA时钟:<CDCE62005>评估板电源电源组1:SmartReflex:UCD9222+UCD7242RSJT<获取CVDD、VCC1V0>电源组2:TI_TPS54620RGY Vsense=0.8V Vin=12V Pe=90% 级联TPS73701DRBT <获取VCC3V3_AUX VCC1V8_AUX VCC2V5 VCC1V8 VCC1V2>电源组3:TI_TPS54620RGY Vsense=0.8V Vin=12V Pe=90% 级联TPS51200DRCT <获取VCC1V5 VCC0V75 >电源组4:TPS54231D <获取VCC5 >评估板其他器件:可编程缓冲方向4路缓冲器TI_SN74A VC4T245PWR8位宽数据通道选择器TI_TS3L301DGG两路电平转换器件<VCCA转VCCB> TI_PCA9306DCUT八路电平转换器件<VCCA转VCCB> TI_TXS0108EPWRRJ45 RJ45_W/XFMR&LED时钟选择器IDT_ICS557GI-08LFTFPGA芯片XILINX_XC3S200AN_4FTG256C。

TMS320C6678多核DSP并行访问存储器性能的研究

TMS320C6678多核DSP并行访问存储器性能的研究摘要:为充分挖掘多核DSP能力,结合TI的TMS320C6678 DSP的存储器架构,分析了各个关键节点的理论数据传输带宽,展开了对多核DSP主设备(CPU内核、EDMA控制器)并行访问存储器(共享SL2、外部DDR3)的性能研究,并采用数据拷贝测试实验进行验证,最后讨论了影响带宽的因素,对多核软件设计具有一定的指导意义。

关键词:多核DSP;存储器性能;TMS320C6678嵌入式领域的处理器设计已向多核处理器迅速发展,TI最新的8核DSP处理器TMS320C6678(以下简称C6678),每个内核频率为1.25 GHz,提供高达40 GB/s MAC定点运算和20 GB/s FLOP浮点运算能力[1],在信号处理、图像处理等对定浮点运算能力及实时性要求较高的领域得到了广泛应用。

多核环境下并行访问存储器的性能是多核系统设计和应用开发的难点之一。

郝朋朋[2]研究了多核处理器的体系结构,但没有对带宽进行实验测试和结果分析;吴灏[3]分析了多核DSP的核间通信方法。

而本文基于TMS320C6678 DSP,详细阐述了多核DSP并行访问存储器的性能,分析了影响带宽的因素以及瓶颈所在,对多核软件设计具有一定的指导意义。

1 C6678多核DSP存储器架构存储器访问性能对于DSP的软件运行是至关重要的。

C6678 DSP所有的存储器都可以被DSP内核和多个DMA主设备访问。

图1显示了C6678的存储器系统架构框图,总线上的数字代表总线宽度,大部分模块运行在1/2或1/3 DSP内核频率[1]。

1.1 C66x内核C6678集成了8个C66x核,每个内核具有以下性能。

(1)32 KB L1D(Level 1 Data)SRAM,运行在DSP内核频率,可用于数据存储或缓存;(2)32 KB L1P(Level 1 Program)SRAM,运行在DSP内核频率,可用于程序存储或缓存;(3)512 KB LL2(Local Level2)SRAM,运行在1/2 DSP内核频率,可用于程序或数据的存储RAM或缓存[4]。

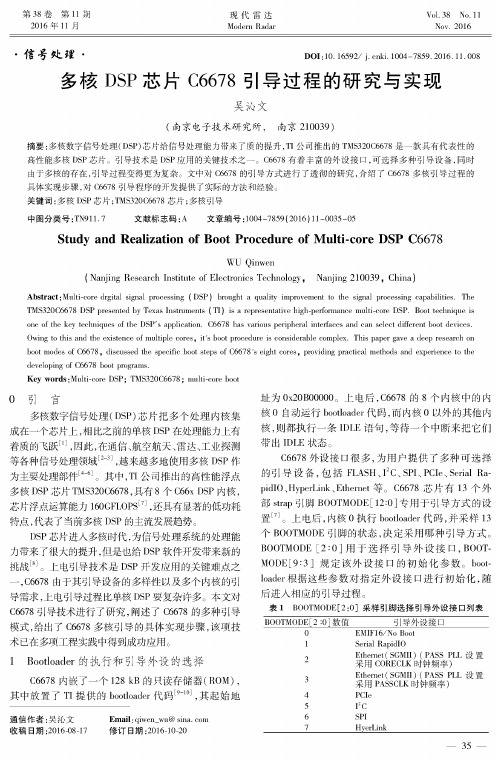

多核DSP芯片C6678引导过程的研究与实现

第38卷第11期现代雷达V d.38N o.l l 2016 年11 月M odem R adar N ov. 2016.信考处理.D O I:10.16592/ j.c n k i.1004-7859.2016.11.008多核DSP芯片C6678引导过程的研究与实现吴於文(南京电子技术研究所,南京210039)摘要:多核数字信号处理(D S P)芯片给信号处理能力带来了质的提升,T I公司推出的T M S320C6678是一款具有代表性的 高性能多核D S P芯片。

引导技术是D S P应用的关键技术之一。

C6678有着丰富的外设接口,可选择多种引导设备,同时 由于多核的存在,引导过程变得更为复杂。

文中对C6678的引导方式进行了透彻的研究,介绍了C6678多核引导过程的 具体实现步骤,对C6678引导程序的开发提供了实际的方法和经验。

关键词:多核D S P芯片;T M S320C6678芯片;多核引导中图分类号:T N911.7文献标志码:A文章编号= 1004-7859(2016)11-0035-05Study and Realization of Boot Procedure of Multi-core DSP C6678WU Qinwen(Nanjing Research Institute of Electronics Technology, Nanjing 210039 ,China) Abstract:M u lti-c o re d rg ita l signal processing (D S P) brought a q u a lity im provem ent to the signal processing ca p a b ilitie s. The TM S320C6678 DSP presented b y Texas Instrum ents (T I)is a representative high-perform ance m u lti-c o re DSP. Boot tech nique is one o f the key techniques o f the D S P^a p p lica tio n. C6678 has various p e rip h e ra l interfaces and can select d iffe re n t boot devices.Owing to th is and the existence o f m u ltip le co re s, it^s boot procedure is considerable com plex. T h is paper gave a deep research on boot modes o f C6678, discussed the spe cific boot steps o f C6678^s eigh t cores, p ro vid in g p ra ctica l methods and experience to the developing o f C6678 boot programs.Key words:M u lti-c o re D SP; TM S320C6678 ; m u lti-c o re boot〇引言多核数字信号处理(DSP)芯片把多个处理内核集 成在一个芯片上,相比之前的单核DSP在处理能力上有 着质的飞跃[1],因此,在通信、航空航天、雷达、工业探测 等各种信号处理领域[M],越来越多地使用多核DSP作 为主要处理部件[4_6]。

基于TMS320C6678的多核DSP上电加载技术

基于TMS320C6678的多核DSP上电加载技术作者:刘章文刘七华谢川林袁学文来源:《现代电子技术》2013年第18期摘要:对于多核DSP应用技术来说,BootLoad技术是一个关键点,也是应用难点之一。

针对8核高性能DSP——TMS320C6678的根配置问题进行了研究,包括上电加载过程,单核和多核的emif NOR⁃FLASH存储器的映像文件的产生,二级加载器的编写和FLASH编程器的构成等。

其中,关键是在多核映像文件中,将辅助核的入口地址作为特殊数据来处理,使其他核触发更容易,这也是其他文献未涉及的。

该项技术已经用在某图像处理系统中。

关键词:多核DSP; TMS320C6678; BootLoad;映像文件中图分类号: TN964⁃34 文献标识码: A 文章编号: 1004⁃373X(2013)18⁃0111⁃040 引言在视频检测、医疗影像及红外图像快速跟瞄系统应用中,越来越复杂的二维、三维甚至四维的图像处理,需要并行化的处理系统,并能够运行复杂的算法[1⁃8]。

要实现这些复杂的系统,高端FPGA+高性能DSP是目前普遍采用的方案[5⁃6,8],而单个DSP的性能已发展至极限,所以解决复杂的并行算法,多核DSP是现在发展的全新方向,其中多核DSP的根加载技术是其难点之一[7,9⁃10]。

TI公司推出的DSP芯片TMS320C6678(C6678)具有8个内核的高性能DSP,每个内核工作频率均达1 GHz。

其支持的Boot模式有SPI、I2C、EMAC、SRIO和并口Emif16NOR⁃FLASH。

其中Emif16 NOR⁃FLASH模式是不用上位机参与、比较简单、独立成系统的一种,大多独立DSP系统采用该方式。

关于多核的加载,也有相关的文献报道[9],而文献[9]是DSP+ARM的双核。

网上也能搜索到关于C6472和C6678零星一些加载资料,都是借助于第三方转换工具,太过于笼统。

下面是针对C6678的并口Emif16 NOR⁃FLASH的上电加载作详细的探讨。

ti6678应用

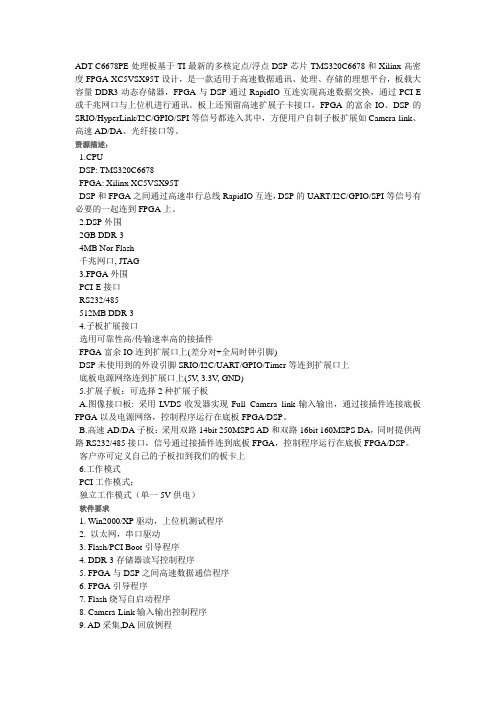

ADT-C6678PE处理板基于TI最新的多核定点/浮点DSP芯片-TMS320C6678和Xilinx高密度FPGA-XC5VSX95T设计,是一款适用于高速数据通讯、处理、存储的理想平台,板载大容量DDR3动态存储器,FPGA与DSP通过RapidIO互连实现高速数据交换,通过PCI-E 或千兆网口与上位机进行通讯。

板上还预留高速扩展子卡接口,FPGA的富余IO、DSP的SRIO/HyperLink/I2C/GPIO/SPI等信号都连入其中,方便用户自制子板扩展如Camera-link、高速AD/DA、光纤接口等。

资源描述:1.CPUDSP: TMS320C6678FPGA: Xilinx XC5VSX95TDSP和FPGA之间通过高速串行总线RapidIO互连,DSP的UART/I2C/GPIO/SPI等信号有必要的一起连到FPGA上。

2.DSP外围2GB DDR-34MB Nor Flash千兆网口, JTAG3.FPGA外围PCI-E接口RS232/485512MB DDR-34.子板扩展接口选用可靠性高/传输速率高的接插件FPGA富余IO连到扩展口上(差分对+全局时钟引脚)DSP未使用到的外设引脚SRIO/I2C/UART/GPIO/Timer等连到扩展口上底板电源网络连到扩展口上(5V, 3.3V, GND)5.扩展子板:可选择2种扩展子板A.图像接口板: 采用LVDS收发器实现Full Camera link输入输出,通过接插件连接底板FPGA以及电源网络,控制程序运行在底板FPGA/DSP。

B.高速AD/DA子板:采用双路14bit 250MSPS AD和双路16bit 160MSPS DA,同时提供两路RS232/485接口,信号通过接插件连到底板FPGA,控制程序运行在底板FPGA/DSP。

客户亦可定义自己的子板扣到我们的板卡上6.工作模式PCI工作模式;独立工作模式(单一5V供电)软件要求1. Win2000/XP驱动,上位机测试程序2. 以太网,串口驱动3. Flash/PCI Boot引导程序4. DDR-3存储器读写控制程序5. FPGA与DSP之间高速数据通信程序6. FPGA引导程序7. Flash烧写自启动程序8. Camera-Link输入输出控制程序9. AD采集,DA回放例程10. 其他接口测试例程1、板卡概述本板卡由我公司自主研发,基于CPCI架构,符合CPCI2.0标准,采用两片TI DSP TMS320C6678芯片和Xilinx公司V5系列FPGA XC5VLX110T-1FF1136芯片。

C6678多核处理器开发板学习总结

6678基本结构与特性:6678评估板功耗表:6678空间映射:6678加载过程BOOT配置引脚:8种加载方式:EIMF加载模式:8种PLL BOOT配置0x872E00-0x87FFFF保留给boot配置用,保存了BOOT外设的基本配置参数。

加载过程:上电后,6678读取BOOTMODE电平,数据存储在DEVSTAT寄存器中,改寄存器数值可编程,各个Core可不同的BOOT模式加载。

6678首先从Core0加载,Core1执行idle处于中断等待状态,当Core0加载完成后,首先Core0的BOOT_MAGIC_ADDRESS被写入加载程序的起始地址,Core0从BOOT_MAGIC_ADDRESS执行,Core0应该对次Core的BOOT_MAGIC_ADDRESS写入执行地址,同时写入IPCGRn寄存器触发次Core的中断,对6678而言BOOT_MAGIC_ADDRESS的映射地址是各Core本地L2的0x807FFF,在加载期间,所有的LP、LD被配置为Cache,L2被配置为可寻址Memory每个Core加载完成BOOTCOMPLETE寄存器被标志参看手册:sprugy56678基本外设:电源监控:EIMF :评估板连接512Mb NandFlash <NUMONYX_NAND512R3A2DZA6E>DDR3:评估板连接 1Gb/1333MHZ DDR3 <SAMSUNG_K4B1G1646G_BCH9> ECC连接1Gb/1333MHZ DDR3(ECC) <SAMSUNG_K4B1G1646G_BCH9>未连接 512Mb/1333MHZ DDR3<SAMSUNG_K4B1G0846G_BCH9 >主要用到引脚如下:DDRA[0:15]/DDRD[0:63] 数据/地址DDR3_ECKE_0DDR3_ECS_0#DDR3_ECAS# DDRA为列地址DDR3_ERAS# DDRA为行地址DDR3_EWE# 写使能?DDR3_EBA_[0:2] BANK选通DDR3_EDM_[0:8] ?DDR3_EDQSP/N_[0:8]DDR3_ECC_[0:8] 0:7 连接SAMSUNG_K4B1G1646G_BCH9的DDRD[0:7] 纠错DDR3_EMRESETNDDR3_EODT_0 端接电阻DDRSLRATE_[0:1] 回转速率,00最快TSIP:评估板连接接口SPI:评估板连接 128Mb SPI NorFlash <NUMONYX_N25Q128A21BSF40F> 评估板连接时钟发生器<TI_CDCE62005RGZT>PCIE:评估板连接接口MDIO:评估板连接PCA9306DCUT 电平转换至PHY芯片配置端<88E1111-B2>IIC:评估板连接 1Mb <ST_M24M01_HRMN6TP>Hyperlink:评估板连接CONN接口 <IPASS PLUS HD_36H>SRIO:评估板连接接口UART:评估板连接 RS232 <TI_MAX3221ECPWR>评估板连接USB _CHB通道<FT2232HL>FT2232HL 配置芯片<ATMEL_AT93C46DN_SH_T IIC>EMAC:评估板连接PHY芯片<MARVELL_88E1111_B2_BAB1C000>评估板时钟DSP时钟:25MHZ输入,可级联使用<CDCE62005RGZT>,由FPGA配置,再使能DSP DSP_CORE_CLKP/N:100MHZDSP_DDR_CLKP/N:66.667MHZDSP_PA_SS_CLKP/N:100MHZDSP_SRIO_SGMII_CLKP/N:312.5MHZDSP_MCM_CLKP/N:312.5MHZDSP_PCIE_CLKP/N:100MHZFT2232HL时钟:12MHZ88E1111时钟:25MHZFPGA时钟:<CDCE62005>评估板电源电源组1:SmartReflex:UCD9222+UCD7242RSJT<获取CVDD、VCC1V0>电源组2:TI_TPS54620RGY Vsense=0.8V Vin=12V Pe=90% 级联TPS73701DRBT <获取VCC3V3_AUX VCC1V8_AUX VCC2V5 VCC1V8 VCC1V2>电源组3:TI_TPS54620RGY Vsense=0.8V Vin=12V Pe=90% 级联TPS51200DRCT <获取VCC1V5 VCC0V75 >电源组4:TPS54231D <获取VCC5 >评估板其他器件:可编程缓冲方向4路缓冲器 TI_SN74AVC4T245PWR8位宽数据通道选择器 TI_TS3L301DGG两路电平转换器件<VCCA转VCCB> TI_PCA9306DCUT八路电平转换器件<VCCA转VCCB> TI_TXS0108EPWRRJ45 RJ45_W/XFMR&LED时钟选择器 IDT_ICS557GI-08LFTFPGA芯片 XILINX_XC3S200AN_4FTG256C。

基于创龙TMS320C6678 DSP+ Xilinx Kintex-7 FPGA工业核心板简介

2 典型运用领域

视频通信系统

电力采集 雷达声纳 光缆普查仪 医用仪器 机器视觉

3 软硬件参数

硬件框图

硬件参数

表 1 DSP 端硬件参数 CPU TMS320C6678,8 核 C66x,主频 1.0/1.25GHz

CPU 主频 1.0GHz/核 1.0GHz/核 1.0GHz/核 1.0GHz/核 1.25GHz/核 1.25GHz/核 1.25GHz/核 1.25GHz/核

表7 NAND FLASH

128MByte 128MByte 128MByte 128MByte 128MByte 128MByte 128MByte 128MByte

广州创龙结合 TI KeyStone 系列多核架构 TMS320C6678 及 Xilinx Kintex-7 系列 FPGA 设计的 SOM-TL6678F 核心板是一款 DSP+FPGA 高速大数据采集处理平台,采用沉金无铅 工艺的 14 层板设计,专业的 PCB Layout 保证信号完整性的同时,经过严格的质量控制, 满足多种环境应用。

表5 典型值电流

800mA

典型值功耗 7.47W

6 机械尺寸图

PCB 尺寸 安装孔数量 散热器安装孔数量

表6 112mm*75mm 4个 4个

7 产品订购型号

型号

SOM-TL6678F-1000/325T1GN-8/4GD-I

SOM-TL6678F-1000/325T1GN-8/8GD-I

SOM-TL6678F-1000/325T1GN-16/4GD-I

基于TI多核DSP TMS320C6678的BOOT方式研究

540 引言在当今数字化不断加快的背景下,各信号处理系统对嵌入式实时性要求在进一步提高。

TI推出的多核DSP TMS320C6678,具有8个运算核心,单核心主频最高可达1.25Ghz [1],无论是定点或浮点都具有较高的计算能力,并且TI为其配套了专用嵌入式实时操作系统SYS/BIOS,使该款芯片在软件设计上的难度大大降低。

在实际应用中,应用场景复杂多变,我们可根据其引导方式将其分成两类,一类需要主机将应用程序镜像下载到DSP内存并激活DSP运行用户程序。

另一类是将用户程序烧写在外部存储器中,上电后由DSP的引导程序完成自加载启动[2-3]。

C6678内置了一级引导程序RBL,RBL为用户提供了多种引导方式以满足其不同需求。

但同时RBL程序相对简单,无法满足一些较为复杂的引导需求,这时往往需要二级引导程序的辅助。

因此,C6678的启动引导过程常常是由一级和二级引导程序共同完成的。

1 C6678启动过程RBL是厂家固化在其Boot Rom内的一段程序,其主要功能是通过判断DEVSTAT寄存器后三位BOOTMODE[2:0]的状态来决定运行的Boot代码。

当C6678上电后,由内部的EDMA将Boot Rom中的代码搬运到Core0的内存中执行,完成一系列初始化工作。

C6678上电启动的大致过程可描述为:Core0运行RBL;RBL根据BootMode[2:0]运行相应一级引导程序;一级引导程序引导用户程序启动,如有二级引导,则先引导二级引导程序,由二级引导程序引导用户程序启动。

2 C6678常用引导方式2.1 PCIE BootPCIE [4]是一种高速串行总线的扩展标准,C6678集成了PCIE外设接口,PCIE启动过程可简单描述为:RBL检测到BootMode[2:0]的值并初始化PCIE模块;主机加载程序在PC与DSP间建立内存映射;主机通过PCIE总线将DDR初始化程序送入Core0 的L2内存并初始化DDR;主机将用户程序推送至DDR内存指定位置,并将入口地址写入magic地址[5],DSP跳转到magic内的入口地址执行,并通过IPC 中断通知从核工作。

基于TMS320C6678多核DSP的分布式通信系统

基于TMS320C6678多核DSP的分布式通信系统董渊文;张永军;高晓亮;滕晶【期刊名称】《微型机与应用》【年(卷),期】2014(000)013【摘要】According to the characteristics of TMS320C6678 and the requirement of the communication among cores, chips and boards, the paper proposes a transparent communication model over systems and the implementation, also provide the performance, and give the reference for the embedded software system design based on TMS320C6678.%根据TMS320C6678芯片的特点,针对核间、片间、板间的通信要求,提出了一种跨系统的透明传输模型及实现,并分析了传输性能,对基于 TMS320C6678的嵌入式软件系统设计提供了指导。

【总页数】3页(P74-76)【作者】董渊文;张永军;高晓亮;滕晶【作者单位】瑞典宜能嵌入式软件有限公司上海研发中心,上海 200021;瑞典宜能嵌入式软件有限公司上海研发中心,上海 200021;瑞典宜能嵌入式软件有限公司上海研发中心,上海 200021;瑞典宜能嵌入式软件有限公司上海研发中心,上海 200021【正文语种】中文【中图分类】TP3【相关文献】1.基于TMS320C6678的多核DSP加载模式研究 [J], 张乐年;关榆君2.基于TMS320C6678的多核DSP上电加载技术 [J], 刘章文;刘七华;谢川林;袁学文3.TMS320C6678多核DSP的加载配置和实现方法 [J], 邓豹4.基于TI多核DSP TMS320C6678的BOOT方式研究 [J], 杨磊;张莹5.基于TI多核DSP TMS320C6678的BOOT方式研究 [J], 杨磊[1];张莹[1]因版权原因,仅展示原文概要,查看原文内容请购买。

TMS320C6678平台函数接口要求

XXXXXX平台软件函数接口要求版本:1.2拟制_______________审核_______________批准_______________2015.11目录目录 (i)版本信息........................................................................................................................................................ i ii1.关于本文档 (1)2.概述 (1)3.函数接口定义 (2)3.1.中断资源 (2)3.2.定时器资源 (4)3.3.DMA资源 (5)3.3.1. 创建DMA函数 (5)3.3.2. 设置DMA参数函数 (6)3.3.3. 启动DMA函数 (6)3.3.4. 停止DMA函数 (7)3.3.5. 删除DMA函数 (7)3.3.6. 获取DMA概要信息函数 (7)3.3.7. 显示DMA信息函数 (8)3.3.8. 检验DMA传输结束信息函数 (8)3.4.串口操作 (8)3.4.1. 初始化串口模块函数 (9)3.4.2. 打开串口函数 (9)3.4.3. 关闭串口函数 (10)3.4.4. 串口发送函数 (10)3.4.5. 串口接收函数 (10)3.4.6. 串口设置函数 (11)3.5.I2C接口操作 (11)3.5.1. 初始化I2c接口函数 (12)3.5.2. 打开I2c接口函数 (12)3.5.3. 关闭I2c接口函数 (12)3.5.4. I2c接口操作函数 (13)3.5.5. I2c接口空闲操作函数 (13)3.6.SPI操作 (14)3.6.1. 初始化SPI接口函数 (14)3.6.2. 打开SPI接口函数 (14)3.6.3. 关闭SPI接口函数 (15)3.6.4. SPI接口设置函数 (15)3.6.5. SPI接口读操作函数 (16)3.6.6. SPI接口写操作函数 (16)3.7.GPIO接口操作 (17)3.7.1. 初始化GPIO接口函数 (17)3.7.2. 打开GPIO接口函数 (18)3.7.3. 关闭GPIO接口函数 (18)3.7.4. GPIO接口方向设置函数 (18)3.7.5. GPIO接口读操作函数 (19)3.7.6. GPIO接口写操作函数 (19)3.7.7. GPIO接口位设置操作函数 (19)3.7.8. GPIO接口位读操作函数 (20)3.7.9. GPIO接口位中断使能函数 (20)3.7.10. GPIO接口位中断禁止函数 (21)3.7.11. GPIO接口信息显示函数 (21)3.8.EMIF操作 (21)3.8.1. 初始化EMIF接口函数 (22)3.8.2. EMIF接口设置函数 (22)3.9.HyperLink操作 (23)3.9.1. 初始化HyperLink接口函数 (23)3.9.2. 打开HyperLink接口函数 (24)3.9.3. 关闭HyperLink接口函数 (24)3.9.4. HyperLink提醒操作函数 (24)3.9.5. HyperLink窗口映射函数 (25)3.9.6. HyperLink读操作函数 (25)3.9.7. HyperLink写操作函数 (25)3.10.多核间消息操作 (26)3.11.多核间互斥操作 (27)3.11.1. 创建核间互斥锁函数 (28)3.11.2. 删除核间互斥锁函数 (28)3.11.3. 核间加锁函数 (28)3.11.4. 核间解锁函数 (29)3.11.5. 查询核间锁状态函数 (29)3.12.Cache操作 (30)3.13.内存操作 (30)3.14.RIO操作 (31)版本信息1.关于本文档本文是XXXXXX平台软件函数接口需求规格书的说明文档。

基于TMS320C6678DSP多核编程的SPECAN成像处理算法实现

基于TMS320C6678DSP多核编程的SPECAN成像处理算法实现李佳洋【摘要】介绍了SPECAN(SPECtral analysis) SAR成像算法基于2片TMS320C6678的工程实现.文中对SPE-CAN SAR成像算法原理做了简单介绍,对算法工程化实现进行重点描述,着重对实现过程中DSP多核间同步、2片DSP间的同步、多核多通道EDMA传输以及大数据量存取及解决措施进行了介绍,并给出了工程实现结果.与其他几种成像算法工程化比较,通过结论可知对于成像精度要求不高,但要求快速实时处理时,SPE-CAN算法为最理想的工程化实现成像算法.【期刊名称】《弹箭与制导学报》【年(卷),期】2017(037)003【总页数】5页(P119-122,126)【关键词】SPECAN成像处理算法;TMS320C6678;多核编程【作者】李佳洋【作者单位】中国西南电子技术研究所,成都 610036【正文语种】中文【中图分类】TN958.3SAR在环境保护、灾害检测、资源勘察、地质测绘等方面有着广泛的应用[1]。

目前主要的SAR成像算法有距离多普勒(RD)算法、Chirp-Scaling(CS)算法、距离徙动算法(RMA)、反投影(BP)算法以及频谱分析(SPECAN)算法等。

相对于其他成像算法,SPECAN算法具有运算量小、所需内存较少的特点,更适合快速实时处理。

TI公司生产的8核高性能DSP芯片TMS320C6678具有运算资源丰富,高速总线接口类型多样化等特点。

文中着重介绍了基于2片TMS320C6678的SPECAN算法实现过程中的工程化处理,以达到算法精度以及实时性最优的目的。

SPECAN算法原理如图1所示。

1.1 距离向脉冲压缩及有效区域计算距离向脉冲压缩在频域进行,即将距离线回波在频域乘以参考函数,再变换到时域。

距离压缩完成后,还需进行轨迹相位粗补偿得到距离向脉压结果。

轨迹补偿的相位为:式中:RS为由惯导信息计算的平台真实轨迹的半径;Rideal为平台理想直线运动轨迹的半径。

TI携手4DSP公司打造最新FPGA整合型适配卡FMC667

TI携手4DSP公司打造最新FPGA整合型适配卡

FMC667

德州仪器与4DSP携手打造FPGA整合型适配卡,助力任务关键型开发商充分满足COTS系统的重要需求

日前,德州仪器(TI)与低功耗、轻量级、小型FPGA 信号影像处理系统的专业创新公司4DSP 宣布联合开发适用于任务关键型应用的最新整合型适配卡FMC667。

4DSP 的FMC667 整合型适配卡采用新兴FMC 外形,包含TI 基于KeyStone 的TMS320C6678 多核数字信号处理器(DSP)、DRAM 存储器及外设。

凭借TI 高性能C6678 多核DSP,FMC667 不但能够更高效、更快速地满足商业化成品(COTS)系统的重要需求,而且还可在任务关键型应用及工业应用中提高处理能力、准确性以及分辨率。

4DSP 嵌入式软件经理Arnaud Maye 表示:TI 多核软件开发套件帮助我们更便捷地为FMC667 卡开发支持库。

TI C6678 DSP 提供8 个 1.25 GHz 并行内核与内建功能以此作为PCIe 的根组件,是一款适用于需求最严谨的应用的控制及高端处理节点。