Ethernet_RTL8201BL_MII

中兴E300操作手册(基本操作)

V3.17R2 V3.18R2 V3.19R1 V3.19R2

20060317-R1.0 20070601-R1.0 20080418-R1.0 20090530-R1.0

资料编号 sjzl2003623

sjzl20041185

sjzl20041851

sjzl20050228

sjzl20051954 sjzl20060660 sjzl20070949 sjzl20081092 sjzl20090545

3. 鼠标操作约定

格式 单击 双击 右击 拖动

意义 快速按下并释放鼠标的左键 连续两次快速按下并释放鼠标的左键 快速按下并释放鼠标的右键 按住鼠标的左键不放,移动鼠标

4. 标志 本书采用四个醒目标志来表示在操作过程中应该特别注意的地方。

注意、 意的事项。

小心、

警告、

危险:提醒操作中应注

目录

第 1 章 基本操作指南................................................................................................................................1-1 1.1 ZXONM E300 的启动和登录 .........................................................................................................1-1 1.2 ZXONM E300 服务器端的退出 .....................................................................................................1-3 1.3 ZXONM E300 客户端的退出 .........................................................................................................1-4 1.4 登录窗口管理者信息输入功能 .....................................................................................................1-5 1.5 客户端操作窗口视图的切换 .........................................................................................................1-5 1.6 主菜单操作 .....................................................................................................................................1-6 1.7 主视图的主菜单/工具栏切换 ........................................................................................................1-7 1.8 导航树操作 .....................................................................................................................................1-8 1.9 拓扑图操作 .....................................................................................................................................1-9 1.9.1 锁定拓扑图 ...........................................................................................................................1-9 1.9.2 保存拓扑图 .........................................................................................................................1-10 1.9.3 恢复拓扑图 .........................................................................................................................1-10 1.9.4 缩放拓扑图 ......................................................................................................................... 1-11 1.9.5 修改拓扑图背景 ................................................................................................................. 1-11 1.10 设备类型统计 .............................................................................................................................1-13 1.11 选择网元(单板) .....................................................................................................................1-15 1.12 移动网元(单板) .....................................................................................................................1-17 1.13 查询网元/单板资源 ....................................................................................................................1-18 1.14 查找网元 .....................................................................................................................................1-19 1.15 ZXONM E300 帮助的使用 .........................................................................................................1-20 1.16 查询ZXONM E300 版本 ............................................................................................................1-21

交换机出现error-disable处理方法

pagp-flap Enable timer to recover from pagp-flap error disable state

err-disable的原因。

下面示例原因为bpduguard,在连接了交换机的端口配置了spanning-tree bpduguard enable。

sw1#show interfaces status err-disabled

Port Name Status Reason

Fa0/47 err-disabled bpduguard

unicast-flood Enabled

从列表中,我们可以看出常见的原因有udld,bpduguard,link-flap以及loopback等。

具体由什么原因导致当前接口err-disable可以由show interface status err-disable来查

看。

在接口模式下采用shutdown,no shutdown进行手动的激活。

在缺省配置下,一旦接口被置为err-disable,IOS将不会试图恢复接口。

这个可以由show errdisable recovery来查看,timer status下面所有的值都是disable。

下面的示例中,由于手工配置了bpduguard恢复,所以timer status的值变为Enable。

channel-misconfig Disabled

vmps Disabled

pagp-flap Disabled

dtp-flap Disabled

RTL8201数据手册

2. SYSTEM APPLICATIONS................................................................................................................1

3. FEATURES ..........................................................................................................................................2

5.1. LEAD (PB)-FREE PACKAGE AND VERSION IDENTIFICATION ...........................................................4

6. PIN DESCRIPTION............................................................................................................................5

ii

Track ID: JATR-1076-21 Rev. 1.3

RTL8201BL Datasheet

Table of Contents

1. INTRODUCTION ..........................................................1

Pin8: DVDD25-> PWFBIN

2. Add pull-high resistor for MDIO 3. Modify ResetB circuit to meet wake-on-LAN application Cosmetic layout changes

H3C登录方式配置

KIEN301和6M3024M 工业以太网交换机用户手册

2009 年 4 月第 2 版 2009 年 7 月第 3 版 资料编号:27030034-30

前言

KIEN3016M 和 KIEN3024M 是东土科技股份有限公司自主研发的两款光电汇合型 一体化管理型工业以太网交换机。该产品主要是针对工业领域内星型网络、树形 网络以及链形网络的应用而开发的。其高性能的交换引擎,坚固而封闭的机箱设 计,无风机但高效的单肋形机箱散热表面,电源输入端过流、过压及 EMC 防护, RJ45 端口优良的 EMC 防护性能,使得 KIEN3016M 和 KIEN3024M 能够适应严酷 而危险的工业环境。同时也非常适用于组建小区宽带网络。 《KIEN3016M/3024M 工业以太网交换机用户手册》主要介绍 KIEN3016M 和 KIEN3024M 工业以太网交换机的技术原理、性能指标、安装调试、Web 管理软件 介绍等方面的内容,供用户在系统开通、扩容和日常维护时参考,同样适用于用 户 培 训 以 及 相 关 技 术 人 员 的 学 习 , 是 广 大 用 户 认 识 和 了 解 KIEN3016M 和 KIEN3024M 工业以太网交换机的实用教材。 本手册主要包括以下内容: 第一章介绍了 KIEN3016M 和 KIEN3024M 的概况及系统特点; 第二章介绍了 KIEN3016M 和 KIEN3024M 的性能指标及业务功能; 第三章介绍了 KIEN3016M 的硬件结构; 第四章介绍了 KIEN3024M 的硬件结构; 第五章介绍了 KIEN3016M 和 KIEN3024M 的安装过程; 第六章介绍了 KIEN3016M 和 KIEN3024M 的现场测试方法; 第七章介绍了 KIEN3016M 和 KIEN3024M 的组网方式和系统配置; 第八章介绍了 KIEN3016M 和 KIEN3024M 的 WEB 管理软件功能介绍; 第九章介绍了 KIEN3016M 和 KIEN3024M 的串口控制台管理功能; 附录 A 介绍了 KIEN3016M 和 KIEN3024M 的双绞线和管脚分配的规则; 附录 B 介绍了 KIEN3016M 和 KIEN3024M 的线缆类型和规格; 附录 C 介绍了在本书中所用到的缩略语。

博达交换机配置

博达交换机测试补充配置说明上海博达数据通信有限公司2004年3月24日目录1、基本配置41.1Console口本地配置41.2基本配置命令41.3Console配置口密码设置51.4enable密码设置51.5Telnet用户&密码配置51.6限制Telnet到交换机上来的IP地址61.7Web管理61.8SNMP网管软件管理81.9中英文提示91.10TFTP软件升级、Zmodem协议升级91.11Syslog日志功能91.12DHCP Server功能91.13SNTP时间协议101.14Ping & Traceroute工具102、VLAN配置112.1 Cisco PVLAN概念及博达实现112.2华为PVLAN概念及博达实现142.3博达SuperVLAN配置162.4 Protected Port保护端口172.5 GVRP配置172.6生成树协议182.7安全端口183、路由协议183.1 RIP183.2 OSPF193.3 EIGRP193.4 BGP20四、网络安全204.1端口镜像204.2 802.1X认证214.3 ACL访问控制234.4 IP地址、MAC地址与端口的绑定244.5端口限定MAC地址数254.6 AAA & Radius、Tacacs+认证254.7 NAT功能25五、QoS265.1 CoS & 802.1P265.2 基于策略的QoS275.3拥塞控制275.4广播风暴抑制285.5带宽控制& 端口限速& 基于策略的限速28六、网络管理306.1 CLI命令行306.2 Telnet远程登录306.3 TFTP远程配置上传下载306.4 Web管理306.5 SNMP网络管理306.6集群管理30七、组播317.1 IGMP Snooping317.2组播路由协议31八、可靠性31端口汇聚功能311、基本配置1.1 Console口本地配置PC串口速率9600,数据位8,奇偶校验无,停止位1,数据流控无。

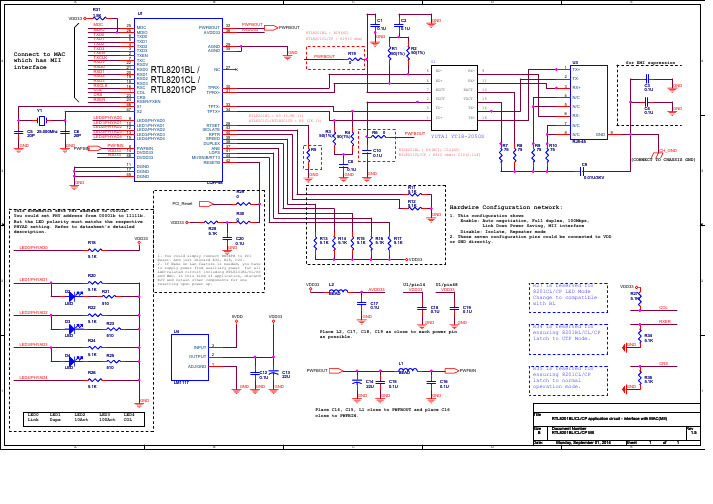

Ethernet_SCHRTL8201CLCp

Rev 1.5 1 of 1

A

B

C

D

4

Connect to MAC which has MII interface

PWFBOUT

RTL8201BL / RTL8201CL / RTL8201CP

for EMI supression

4

Y1 LED0/PHYAD0 LED1/PHYAD1 LED2/PHYAD2 LED3/PHYAD3 LED4/PHYAD4

8

PWFBIN 8 VDD33 14 VDD33 48 11 17 45

C10 0.1U

RTL8201BL : R6(NC); C10(NC) RTL8201CL/CP : R6(0 ohm); C10(0.1uF)

(CONNECT TO CHASSIS GND)

3

3

GND

This schematic sets PHY address to 00001b. You could set PHY address from 00001b to 11111b. But the LED polarity must matchs the respective PHYAD setting. Refer to datasheet's detailed description.

VDD33 R28 5.1K

R30 0

C20 0.1U GND

R13 5.1K

R14 5.1K

R15 5.1K

R16 5.1K

R17 5.1K

2

LED1/PHYAD1 D2 LED LED2/PHYAD2 D3 LED LED3/PHYAD3 D4 LED LED4/PHYAD4

迈普3000_端口操作命令

第 5 章 LLDP 功能命令 ................................................. 21

5.1 lldp enable ....................................................................................... 21 5.2 lldp enable(端口) ......................................................................... 21 5.3 lldp mode ......................................................................................... 21 5.4 lldp tx-interval.................................................................................. 22 5.5 lldp msgTxHold ............................................................................... 22 5.6 lldp transmit delay .......................................................................... 23 5.7 lldp notification interval.................................................................. 23 5.8 lldp trap............................................................................................ 23 5.9 lldp transmit optional tlv................................................................. 24 5.10 lldp neighbors max-num............................................................... 24 5.11 lldp tooManyNeighbors................................................................. 24 5.12 show lldp........................................................................................ 25 2

以太网PHY芯片之MIIMDIO接口详解

以太⽹PHY芯⽚之MIIMDIO接⼝详解本⽂主要分析MII/RMII/SMII,以及GMII/RGMII/SGMII接⼝的信号定义,及相关知识,同时本⽂也对RJ-45接⼝进⾏了总结,分析了在10/100模式下和1000M模式下的设计⽅法。

MII接⼝提供了MAC与PHY之间、PHY与STA(Station Management)之间的互联技术,该接⼝⽀持10Mb/s与100Mb/s的数据传输速率,数据传输的位宽为4位。

提到MII,就有可能涉及到RS,PLS,STA等名词术语,下⾯讲⼀下他们之间对应的关系。

所谓RS即Reconciliation sublayer,它的主要功能主要是提供⼀种MII和MAC/PLS之间的信号映射机制。

它们(RS与MII)之间的关系如下图:MII接⼝的Management Interface可同时控制多个PHY,802.3协议最多⽀持32个PHY,但有⼀定的限制:要符合协议要求的connector特性。

所谓Management Interface,即MDC信号和MDIO信号。

前⾯已经讲过RS与PLS的关系,以及MII接⼝连接的对象。

它们是通过MII接⼝进⾏连接的,⽰意图如下图。

由图可知,MII的Management Interface是与STA(Station Management)相连的。

接⼝⽀持10Mb/s以及100Mb/s,且在两种⼯作模式下所有的功能以及时序关系都是⼀致的,唯⼀不同的是时钟的频率问题。

802.3要求PHY 不⼀定⼀定要⽀持这两种速率,但⼀定要描述,通过Management Interface反馈给MAC。

下⾯将详细介绍MII接⼝的信号定义,时序特性等。

由于MII接⼝有MAC和PHY模式,因此,将会根据这两种不同的模式进⾏分析,同时还会对RMII/SMII进⾏介绍。

MII接⼝可分为MAC模式和PHY模式,⼀般说来MAC和PHY对接,但是MAC和MAC也是可以对接的。

物联网毕业论文

基于单片机的嵌入式以太网控制终端设计摘要:基于单片机技术的以太网终端广泛应用在各个领域,本文基于建荣AX2005+PHY的解决方案,实现ARP请求,以及ping命令。

同时,本文详细介绍以太网接口的硬件设计和通信电路的抗干扰设计。

覆盖单片机技术,通信技术,计算机网络技术等多个知识领域。

关键词:以太网协议;信道编码;TCP/IP协议;单片机;一,概述:随着单片机技术和嵌入式技术的广泛应用,以及通信技术的发展和计算机网络的普及,人们提出了对基于嵌入式系统的网络通信技术的应用需求。

嵌入式网络通信系统将过去单一独立的嵌入式系统组成一个网络系统,使得嵌入式系统不再是一个独立的个体,而是一个整体信息化网络的一个部分。

该技术广泛应用在智能设备,信息化家电,智能管理设备,安防监控设备等领域。

嵌入式网络系统具有以下特点:1,基于单片机系统。

2,系统之间存在数据通讯。

在嵌入式网络系统的实现方案中,有基于RS232/RS485总线协议,CAN总线协议,以太网协议,USB总线协议等多种方式。

其中基于以太网协议的实现方案中,具有成本低,安装方便,通讯距离远,兼容性好和平台移植方便等多种优势。

该技术广泛应用在以下领域。

1,实验室管理监控系统某生化实验室需要建立一个实时监控系统,检测实验室人员出入,实验结果数据,实验室温度湿度。

该实验室的仪器设备都有RS232接口输出打印,可以输出到单片机。

门禁和各种传感器也接入单片机系统。

这时候单片机可以通过以太网把数据提交到实验室的服务器上,服务器通过处理提交的数据,将控制命令通过以太网发给单片机,单片机再进行相应的操作。

2,智能家居系统现代家居系统中,由于需要宽带接入,基本上所有住户都有局域网接入。

在住户内部搭建局域网也很方便。

鉴于以上情况,利用以太网实现智能家居网络能够实现。

住房内的家电和各种设施,可以接入内部以太网实现相互通信,或者与上位机实现通信。

上位机可以被用户远程控制,对居室的家电和设施进行控制,达到对居室的温度,光亮的调节,同时可以利用下位机(单片机)将室内监控系统的状况传到上位机,上位机通过分析可以向主人或者相关部门报告火警或者匪警。

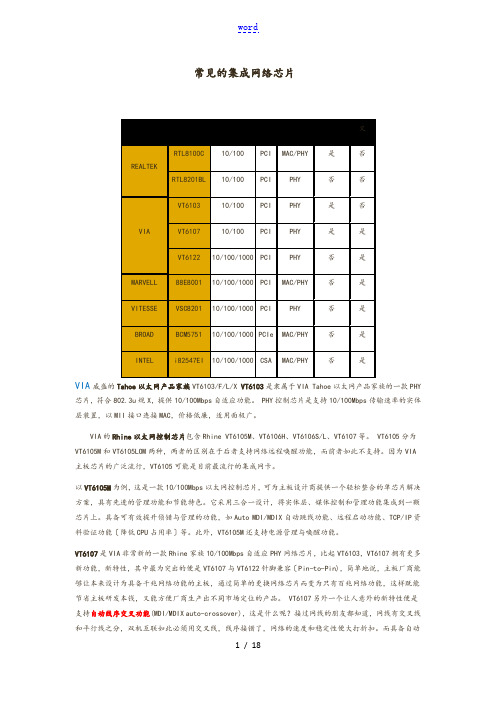

常见的地集成网络的芯片

常见的集成网络芯片VIA威盛的Tahoe以太网产品家族VT6103/F/L/X VT6103是隶属于VIA Tahoe以太网产品家族的一款PHY 芯片,符合802.3u规X,提供10/100Mbps自适应功能。

PHY控制芯片是支持10/100Mbps传输速率的实体层装置,以MII接口连接MAC,价格低廉,适用面极广。

VIA的Rhine以太网控制芯片包含Rhine VT6105M、VT6106H、VT6106S/L、VT6107等。

VT6105分为VT6105M和VT6105LOM两种,两者的区别在于后者支持网络远程唤醒功能,而前者如此不支持。

因为VIA 主板芯片的广泛流行,VT6105可能是目前最流行的集成网卡。

以VT6105M为例,这是一款10/100Mbps以太网控制芯片,可为主板设计商提供一个轻松整合的单芯片解决方案,具有先进的管理功能和节能特色。

它采用三合一设计,将实体层、媒体控制和管理功能集成到一颗芯片上。

具备可有效提升侦错与管理的功能,如Auto MDI/MDIX自动跳线功能、远程启动功能、TCP/IP资料验证功能〔降低CPU占用率〕等。

此外,VT6105M还支持电源管理与唤醒功能。

VT6107是VIA非常新的一款Rhine家族10/100Mbps自适应PHY网络芯片,比起VT6103,VT6107拥有更多新功能,新特性,其中最为突出的便是VT6107与VT6122针脚兼容〔Pin-to-Pin),简单地说,主板厂商能够让本来设计为具备千兆网络功能的主板,通过简单的更换网络芯片而变为只有百兆网络功能,这样既能节省主板研发本钱,又能方便厂商生产出不同市场定位的产品。

VT6107另外一个让人意外的新特性便是支持自动线序交叉功能(MDI/MDIX auto-crossover),这是什么呢?接过网线的朋友都知道,网线有交叉线和平行线之分,双机互联如此必须用交叉线,线序接错了,网络的速度和稳定性便大打折扣。

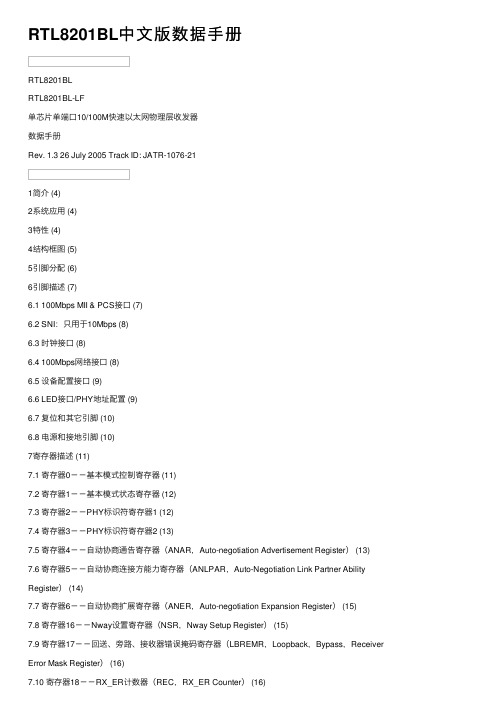

RTL8201BL数据手册(中文版)

RTL8201BLRTL8201BL-LF单芯片单端口10/100M快速以太网物理层收发器数据手册Rev. 1.3 26 July 2005 Track ID: JATR-1076-211简介 (4)2系统应用 (4)3特性 (4)4结构框图 (5)5引脚分配 (6)6引脚描述 (7)6.1 100Mbps MII & PCS接口 (7)6.2 SNI:只用于10Mbps (8)6.3 时钟接口 (8)6.4 100Mbps网络接口 (8)6.5 设备配置接口 (9)6.6 LED接口/PHY地址配置 (9)6.7 复位和其它引脚 (10)6.8 电源和接地引脚 (10)7寄存器描述 (11)7.1 寄存器0--基本模式控制寄存器 (11)7.2 寄存器1--基本模式状态寄存器 (12)7.3 寄存器2--PHY标识符寄存器1 (12)7.4 寄存器3--PHY标识符寄存器2 (13)7.5 寄存器4--自动协商通告寄存器(ANAR,Auto-negotiation Advertisement Register) (13)7.6 寄存器5--自动协商连接方能力寄存器(ANLPAR,Auto-Negotiation Link Partner AbilityRegister) (14)7.7 寄存器6--自动协商扩展寄存器(ANER,Auto-negotiation Expansion Register) (15)7.8 寄存器16--Nway设置寄存器(NSR,Nway Setup Register) (15)7.9 寄存器17--回送、旁路、接收器错误掩码寄存器(LBREMR,Loopback,Bypass,ReceiverError Mask Register) (16)7.10 寄存器18--RX_ER计数器(REC,RX_ER Counter) (16)7.11 寄存器19--10Mbps网络接口配置寄存器 (17)7.12 寄存器20--PHY1_1寄存器 (17)7.13 寄存器21--PHY1_2寄存器 (17)7.14 寄存器22--PHY 2寄存器 (17)7.15 寄存器23--Twister_1寄存器 (17)7.16 寄存器24--Twister_2寄存器 (18)7.17 寄存器25--测试寄存器 (18)8功能描述 (18)8.1MII和管理接口 (19)8.1.1数据传递 (19)8.1.2串行管理 (19)8.2 自动协商和平行检测 (20)8.3 流控支持 (21)8.4 硬件配置和自动协商 (21)8.5 LED和PHY地址配置 (22)8.6 串行网络接口 (22)8.7 掉电、掉线、省电和隔离模式 (22)8.8 媒介接口 (23)8.8.1100Base-TX (23)8.8.2100Base-FX光纤操作方式 (23)8.8.310Base-Tx/Rx (24)8.9 转发器模式 (24)8.10 复位和传输偏压(RTSET,Reset and Transmit Bias) (24)8.11 3.3V电源支持和电压转化电路 (24)8.12 远端故障指示 (25)9电气特性 (25)9.1 D.C.特性 (25)9.1.1绝对最大额定值 (25)9.1.2操作条件 (25)9.1.3功耗 (26)9.1.4供电电压:Vcc (26)9.2 A.C.特性 (27)9.2.1MII发送时序 (27)9.2.2MII接收时序 (28)9.2.3SNI发送时序 (29)9.2.4SNI接收时序 (29)9.2.5MDC/MDIO时序 (29)9.2.6无冲突发送 (30)9.2.7无冲突接收 (31)9.3 晶振和变压器规格 (31)9.3.1晶振规格 (31)9.3.2变压器规格 (31)10机械尺寸 (32)11订购信息 (33)1简介RTL8201BL是一个单端口的物理层收发器,它只有一个MII/SNI(媒体独立接口/串行网络接口)接口。

RTL8201BL中文版数据手册

RTL8201BL中⽂版数据⼿册RTL8201BLRTL8201BL-LF单芯⽚单端⼝10/100M快速以太⽹物理层收发器数据⼿册Rev. 1.3 26 July 2005 Track ID: JATR-1076-211简介 (4)2系统应⽤ (4)3特性 (4)4结构框图 (5)5引脚分配 (6)6引脚描述 (7)6.1 100Mbps MII & PCS接⼝ (7)6.2 SNI:只⽤于10Mbps (8)6.3 时钟接⼝ (8)6.4 100Mbps⽹络接⼝ (8)6.5 设备配置接⼝ (9)6.6 LED接⼝/PHY地址配置 (9)6.7 复位和其它引脚 (10)6.8 电源和接地引脚 (10)7寄存器描述 (11)7.1 寄存器0--基本模式控制寄存器 (11)7.2 寄存器1--基本模式状态寄存器 (12)7.3 寄存器2--PHY标识符寄存器1 (12)7.4 寄存器3--PHY标识符寄存器2 (13)7.5 寄存器4--⾃动协商通告寄存器(ANAR,Auto-negotiation Advertisement Register) (13) 7.6 寄存器5--⾃动协商连接⽅能⼒寄存器(ANLPAR,Auto-Negotiation Link Partner Ability Register) (14)7.7 寄存器6--⾃动协商扩展寄存器(ANER,Auto-negotiation Expansion Register) (15)7.8 寄存器16--Nway设置寄存器(NSR,Nway Setup Register) (15)7.9 寄存器17--回送、旁路、接收器错误掩码寄存器(LBREMR,Loopback,Bypass,Receiver Error Mask Register) (16)7.10 寄存器18--RX_ER计数器(REC,RX_ER Counter) (16)7.11 寄存器19--10Mbps⽹络接⼝配置寄存器 (17)7.12 寄存器20--PHY1_1寄存器 (17)7.13 寄存器21--PHY1_2寄存器 (17)7.14 寄存器22--PHY 2寄存器 (17)7.15 寄存器23--Twister_1寄存器 (17)7.16 寄存器24--Twister_2寄存器 (18)7.17 寄存器25--测试寄存器 (18)8功能描述 (18)8.1MII和管理接⼝ (19)8.1.1数据传递 (19)8.1.2串⾏管理 (19)8.2 ⾃动协商和平⾏检测 (20)8.3 流控⽀持 (21)8.4 硬件配置和⾃动协商 (21)8.5 LED和PHY地址配置 (22)8.6 串⾏⽹络接⼝ (22)8.7 掉电、掉线、省电和隔离模式 (22)8.8 媒介接⼝ (23)8.8.1100Base-TX (23)8.8.2100Base-FX光纤操作⽅式 (23)8.8.310Base-Tx/Rx (24)8.9 转发器模式 (24)8.10 复位和传输偏压(RTSET,Reset and Transmit Bias) (24) 8.11 3.3V电源⽀持和电压转化电路 (24)8.12 远端故障指⽰ (25)9电⽓特性 (25)9.1 D.C.特性 (25)9.1.1绝对最⼤额定值 (25)9.1.2操作条件 (25)9.1.3功耗 (26)9.1.4供电电压:Vcc (26)9.2 A.C.特性 (27)9.2.1MII发送时序 (27)9.2.2MII接收时序 (28)9.2.3SNI发送时序 (29)9.2.4SNI接收时序 (29)9.2.5MDC/MDIO时序 (29)9.2.6⽆冲突发送 (30)9.2.7⽆冲突接收 (31)9.3 晶振和变压器规格 (31)9.3.1晶振规格 (31)9.3.2变压器规格 (31)10机械尺⼨ (32)11订购信息 (33)1简介RTL8201BL是⼀个单端⼝的物理层收发器,它只有⼀个MII/SNI(媒体独⽴接⼝/串⾏⽹络接⼝)接⼝。

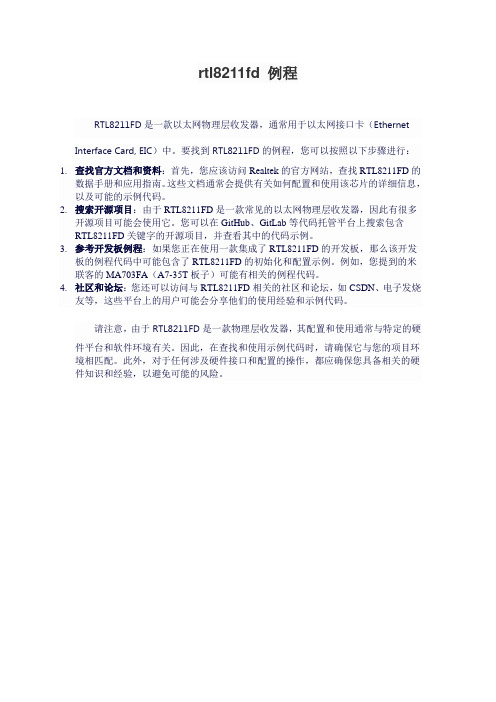

rtl8211fd 例程

rtl8211fd 例程

RTL8211FD是一款以太网物理层收发器,通常用于以太网接口卡(Ethernet Interface Card, EIC)中。

要找到RTL8211FD的例程,您可以按照以下步骤进行:

1.查找官方文档和资料:首先,您应该访问Realtek的官方网站,查找RTL8211FD的

数据手册和应用指南。

这些文档通常会提供有关如何配置和使用该芯片的详细信息,以及可能的示例代码。

2.搜索开源项目:由于RTL8211FD是一款常见的以太网物理层收发器,因此有很多

开源项目可能会使用它。

您可以在GitHub、GitLab等代码托管平台上搜索包含

RTL8211FD关键字的开源项目,并查看其中的代码示例。

3.参考开发板例程:如果您正在使用一款集成了RTL8211FD的开发板,那么该开发

板的例程代码中可能包含了RTL8211FD的初始化和配置示例。

例如,您提到的米联客的MA703FA(A7-35T板子)可能有相关的例程代码。

4.社区和论坛:您还可以访问与RTL8211FD相关的社区和论坛,如CSDN、电子发烧

友等,这些平台上的用户可能会分享他们的使用经验和示例代码。

请注意,由于RTL8211FD是一款物理层收发器,其配置和使用通常与特定的硬

件平台和软件环境有关。

因此,在查找和使用示例代码时,请确保它与您的项目环境相匹配。

此外,对于任何涉及硬件接口和配置的操作,都应确保您具备相关的硬件知识和经验,以避免可能的风险。

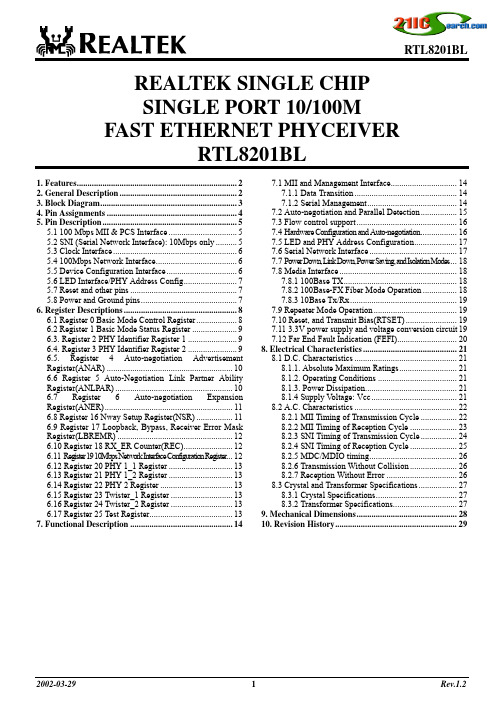

RTL8201

REALTEK SINGLE CHIPSINGLE PORT 10/100M FAST ETHERNET PHYCEIVERRTL8201BL1. Features (2)2. General Description (2)3. Block Diagram (3)4. Pin Assignments (4)5. Pin Description (5)5.1 100 Mbps MII & PCS Interface (5)5.2 SNI (Serial Network Interface): 10Mbps only (5)5.3 Clock Interface (6)5.4 100Mbps Network Interface (6)5.5 Device Configuration Interface (6)5.6 LED Interface/PHY Address Config (7)5.7 Reset and other pins (7)5.8 Power and Ground pins (7)6. Register Descriptions (8)6.1 Register 0 Basic Mode Control Register (8)6.2 Register 1 Basic Mode Status Register (9)6.3. Register 2 PHY Identifier Register 1 (9)6.4. Register 3 PHY Identifier Register 2 (9)6.5. Register 4 Auto-negotiation AdvertisementRegister(ANAR) (10)6.6 Register 5 Auto-Negotiation Link Partner AbilityRegister(ANLPAR) (10)6.7 Register 6 Auto-negotiation ExpansionRegister(ANER) (11)6.8 Register 16 Nway Setup Register(NSR) (11)6.9 Register 17 Loopback, Bypass, Receiver Error MaskRegister(LBREMR) (12)6.10 Register 18 RX_ER Counter(REC) (12)6.11 Register 19 10Mbps Network Interface Configuration Register (12)6.12 Register 20 PHY 1_1 Register (13)6.13 Register 21 PHY 1_2 Register (13)6.14 Register 22 PHY 2 Register (13)6.15 Register 23 Twister_1 Register (13)6.16 Register 24 Twister_2 Register (13)6.17 Register 25 Test Register (13)7. Functional Description (14)7.1 MII and Management Interface (14)7.1.1 Data Transition (14)7.1.2 Serial Management (14)7.2 Auto-negotiation and Parallel Detection (15)7.3 Flow control support (16)7.4 Hardware Configuration and Auto-negotiation (16)7.5 LED and PHY Address Configuration (17)7.6 Serial Network Interface (17)7.7 Power Down, Link Down, Power Saving, and Isolation Modes (18)7.8 Media Interface (18)7.8.1 100Base TX (18)7.8.2 100Base-FX Fiber Mode Operation (18)7.8.3 10Base Tx/Rx (19)7.9 Repeater Mode Operation (19)7.10 Reset, and Transmit Bias(RTSET) (19)7.11 3.3V power supply and voltage conversion circuit197.12 Far End Fault Indication (FEFI) (20)8. Electrical Characteristics (21)8.1 D.C. Characteristics (21)8.1.1. Absolute Maximum Ratings (21)8.1.2. Operating Conditions (21)8.1.3. Power Dissipation (21)8.1.4 Supply Voltage: Vcc (21)8.2 A.C. Characteristics (22)8.2.1 MII Timing of Transmission Cycle (22)8.2.2 MII Timing of Reception Cycle (23)8.2.3 SNI Timing of Transmission Cycle (24)8.2.4 SNI Timing of Reception Cycle (25)8.2.5 MDC/MDIO timing (26)8.2.6 Transmission Without Collision (26)8.2.7 Reception Without Error (26)8.3 Crystal and Transformer Specifications (27)8.3.1 Crystal Specifications (27)8.3.2 Transformer Specifications (27)9. Mechanical Dimensions (28)10. Revision History (29)1. FeaturesThe Realtek RTL8201BL is a Fast Ethernet Phyceiver with selectable MII or SNI interface to the MAC chip. It provides the following features:Supports MII/7-wire SNI (Serial Network Interface) interfaceSupports 10/100Mbps operationSupports half/full duplex operationSupport of twisted pair or Fiber mode outputIEEE 802.3/802.3u compliantSupports IEEE 802.3u clause 28 auto negotiation Supports power down modeSupports operation under Link Down Power Saving modeSupports Base Line Winder (BLW) compensationSupports repeater modeSpeed/duplex/auto negotiation adjustable3.3V operation with 5V IO signal toleranceLow operation power consumption and only need single supply 3.3VAdaptive Equalization25MHz crystal/oscillator as clock sourceMultiple network status LED supportFlow control ability support to co-work with MAC (by MDC/MDIO)48 pin LQFP package2. General DescriptionThe RTL8201BL is a single-port Phyceiver with an MII (Media Independent Interface)/SNI(Serial Network Interface). It implements all 10/100M Ethernet Physical-layer functions including the Physical Coding Sublayer (PCS), Physical Medium Attachment (PMA), Twisted Pair Physical Medium Dependent Sublayer (TP-PMD), 10Base-Tx Encoder/Decoder and Twisted Pair Media Access Unit (TPMAU). A PECL interface is supported to connect with an external 100Base-FX fiber optical transceiver. The chip is fabricated with an advanced CMOS process to meet low voltage and low power requirements.The RTL8201BL can be used as a Network Interface Adapter, MAU, CNR, ACR, Ethernet Hub, Ethernet Switch. Additionally, it can be used in any embedded system with an Ethernet MAC that needs a twisted pair physical connection or fiber PECL interface to external 100Base-FX optical transceiver module.3. Block DiagramRXIN+RXIN-TXO+TXO -RXC 25MTXC 25MTXDRXDMII SNI4. Pin Assignments5. Pin DescriptionLI: Latched Input in power up or reset I/O: Bi-directional input and outputI: Input O: OutputP: Power5.1 100 Mbps MII & PCS InterfaceSymbol Type Pin No. DescriptionTXC O 7 Transmit Clock: This pin provides a continuous clock as a timing referencefor TXD[3:0] and TXEN.TXEN I 2 Transmit Enable: The input signal indicates the presence of a valid nibbledata on TXD[3:0].TXD[3:0] I 3, 4, 5, 6 Transmit Data: MAC will source TXD[0..3] synchronous with TXC whenTXEN is asserted.RXC O 16 Receive Clock: This pin provides a continuous clock reference for RXDVand RXD[0..3] signals. RXC is 25MHz in the 100Mbps mode and 2.5Mhz inthe 10Mbps mode.COL O 1 Collision Detected: COL is asserted high when a collision is detected on the media. CRS O 23Carrier Sense: This pin’s signal is asserted high if the media is not in IDEL state. RXDV O 22 Receive Data Valid: This pin’s signal is asserted high when received data ispresent on the RXD[3:0] lines; the signal is deasserted at the end of thepacket. The signal is valid on the rising of the RXC.RXD[3:0] O 18, 19, 20, 21 Receive Data: These are the four parallel receive data lines aligned on thenibble boundaries driven synchronously to the RXC for reception by theexternal physical unit (PHY).RXER/ FXEN O/LI 24 Receive error: if any 5B decode error occurs, such as invalid J/K, T/R,invalid symbol, this pin will go high.Fiber/UTP Enable: During power on reset, this pin status is latched todetermine at which media mode to operate:1: Fiber mode0: UTP modeAn internal weak pull low resistor, sets this to the default of UTP mode. It ispossible to use an external 5.1KΩ pull high resistor to enable fiber mode.After power on, the pin operates as the Receive Error pin.MDC I 25 Management Data Clock: This pin provides a clock synchronous to MDIO,which may be asynchronous to the transmit TXC and receive RXC clocks.The clock rate can be up to 2.5MHz.MDIO I/O 26 Management Data Input/Output: This pin provides the bi-directionalsignal used to transfer management information.5.2 SNI (Serial Network Interface): 10Mbps onlySymbol Type Pin No. DescriptionCOL O 1 Collision DetectRXD0 O 21 Received Serial DataCRS O 23Carrier SenseRXC O 16 Receive Clock: Resolved from received dataTXD0 I 6 Transmit Serial DataTXC O 7 Transmit Clock: Generate by PHYTXEN I 2 Transmit Enable: For MAC to indicate transmit operation5.3 Clock InterfaceSymbol Type Pin No. DescriptionX2 O 4725MHz Crystal Output: This pin provides the 25MHz crystal output. Itmust be left open when X1 is driven with an external 25MHz oscillator.X1 I 4625MHz Crystal Input: This pin provides the 25MHz crystal input. If a25MHz oscillator is used, connect X1 to the oscillator’s output. Refer tosection 8.3 to obtain clock source specifications.5.4 100Mbps Network InterfaceSymbol Type Pin No. DescriptionTPTX+ TPTX- OO3433Transmit Output: Differential pair shared by 100Base-TX, 100Base-FX and10Base-T modes.When configured as 100Base-TX, output is an MLT-3encoded waveform. When configured as 100Base-FX, the output ispseudo-ECL level.RTSET I 28 Transmit Bias Resistor Connection: This pin should be pulled to GND bya 5.9KΩ (1%) resistor to define driving current for transmit DAC. Theresistance value may be changed, depending on experimental results of theRTL8201BL.TPRX+ TPRX- II3130Receive Input: Differential pair shared by 100Base-TX, 100Base-FX, and10Base-T modes.5.5 Device Configuration InterfaceSymbol Type Pin No. DescriptionISOLATE I 43 Set high to isolate the RTL8201BL from the MAC. This will also isolate theMDC/MDIO management interface. In this mode, the power consumption isminimum. This pin can be directly connected to GND or VCC.RPTR I 40 Set high to put the RTL8201BL into repeater mode. This pin can be directlyconnected to GND or VCC.SPEED LI 39 This pin is latched to input during a power on or reset condition. Set high toput the RTL8201BL into 100Mbps operation. This pin can be directly connectedto GND or VCC.DUPLEX LI 38 This pin is latched to input during a power on or reset condition. Set high toenable full duplex. This pin can be directly connected to GND or VCC.ANE LI 37 This pin is latched to input during a power on or reset condition. Set high toenable Auto-negotiation mode, set low to force mode. This pin can be directlyconnected to GND or VCC.LDPS I 41 Set high to put the RTL8201BL into LDPS mode. This pin can be directlyconnected to GND or VCC. Refer to Section 7.7 for more information.MII/SNIB/ RTT3(test) LI/O 44 This pin is latched to input during a power on or reset condition. Pull high toset the RTL8201BL into MII mode operation. Set low for SNI mode. This pincan be directly connected to GND or VCC. In test mode, this pin is an output pin andredefined as RTT35.6 LED Interface/PHY Address ConfigThese five pins are latched into the RTL8201BL during power up reset to configure PHY address [0:4] used for MII management register interface. And then, in normal operation after initial reset, they are used as driving pins for status indication LED. The driving polarity, active low or active high, is determined by each latched status of the PHY address [4:0] during power-up reset. If latched status is High then it will be active low, and if latched status is Low then it will be active high. Refer to Section 7.5 for more information.Symbol Type Pin No. DescriptionPHYAD0/ LED0 LI/O 9 PHY Address [0]Link LED: Active when linked.PAD1/ LED1 LI/O 10 PHY Address [1]Full Duplex LED: Active when in Full Duplex operation.PHYAD2/ LED2 LI/O 12 PHY Address [2]Link 10/ACT LED: Active when linked in 10Base-T mode, and blinkingwhen transmitting or receiving data.PHYAD3/ LED3 LI/O 13 PHY Address [3]Link 100/ACT LED: Active when linked in 100Base-TX and blinkingwhen transmitting or receiving data.PHYAD4/ LED4 LI/O 15 PHY Address [4]Collision LED: Active when collisions occur.5.7 Reset and other pinsSymbol Type Pin No. DescriptionRESETB I 42 RESETB: Set low to reset the chip. For a complete reset function, this pinmust be asserted low for at least 10ms.PWFBOUT O 32 Power Feedback Output: Be sure to connect a 22uF tantalum capacitor forfrequency compensation and a 0.1uF capacitor for noise de-coupling. Thenconnect this pin through a ferrite bead to PWFBIN(pin8). The connectionmethod is figured in section 7.11.PWFBIN I 8 Power Feedback Input: see the description of PWFBOUT.NC 27Not connection5.8 Power and Ground pinsSymbol Type Pin No. DescriptionA VDD33 P 36 3.3V Analog power input: 3.3V power supply for analog circuit; should bewell decoupled.AGND P 29,35 Analog Ground: Should be connected to a larger GND planeDVDD33 P 14,48 3.3V Digital Power input: 3.3V power supply for digital circuit.DGND P 11,17,45Digital Ground: Should be connected to a larger GND plane.6. Register DescriptionsThis section will describe definitions and usage for each of the registers available in the RTL8201BL.6.1 Register 0 Basic Mode Control RegisterAddressNameDescription/UsageDefault/Attribute0:<15>ResetThis bit sets the status and control registers of the PHY in a default state. This bit is self-clearing. 1 = software reset 0 = normal operation0, RW0:<14> Loopback This bit enables loopback of transmit data nibblesTXD<3:0> to the receive data path. 1 = enable loopback 0 = normal operation0, RW0:<13> Spd_Set This bit sets the network speed.1 = 100Mbps 0 = 10MbpsWhen 100Base-FX mode is enabled, this bit=1 and is read only.1, RW0:<12> Auto Negotiation Enable This bit enables/disables the Nway auto-negotiationfunction. 1 = enable auto-negotiation; bits 0:<13> and 0:<8>will be ignored.0 = disable auto-negotiation; bits 0:<13> and 0:<8> will determine the link speed and the data transfer mode, respectively.When 100Base-FX mode is enabled, this bit=0 and is read only.1, RW0:<11> Power Down This bit turns down the power of the PHY chipincluding internal crystal oscillator circuit. The MDC, MDIO is still alive for accessing the MAC. 1 = power down 0 = normal operation0, RW0:<10> Reserved 0:<9> Restart Auto Negotiation This bits allows the Nway auto-negotiation functionto be reset.1 = re-start auto-negotiation 0 = normal operation0, RW0:<8> Duplex Mode This bit sets the duplex mode if auto negotiation isdisabled (bit 0:<12>=0) 1 = full duplex 0 = half duplexAfter completing auto negotiation, this bit will reflect the duplex status.(1: Full duplex, 0: Half duplex)When 100Base-FX mode is enabled, this bit can be set through the MDC/MDIO SMI interface or DUPLEX pin.1, RW0:<7:0> Reserved6.2 Register 1 Basic Mode Status RegisterAddressName Description/UsageDefault/Attribute1:<15>100Base-T41 = enable 100Base-T4 support 0 = suppress 100Base-T4 support0, RO1:<14> 100Base_TX_ FD 1 = enable 100Base-TX full duplex support0 = suppress 100Base-TX full duplex support1, RO 1:<13> 100BASE_TX_HD 1 = enable 100Base-TX half duplex support0 = suppress 100Base-TX half duplex support1, RO 1:<12> 10Base_T_FD 1 = enable 10Base-T full duplex support0 = suppress 10Base-T full duplex support1, RO 1:<11> 10_Base_T_HD 1 = enable 10Base-T half duplex support0 = suppress 10Base-T half duplex support1, RO 1:<10:7> Reserved 1:<6> MF Preamble Suppression The RTL8201BL will accept management frameswith preamble suppressed. The RTL8201BL acceptsmanagement frames without preamble. A Minimum of 32 preamble bits are required for the first SMI read/write transaction after reset. One idle bit is required between any two management transactions as per IEEE802.3u specifications1, RO1:<5> Auto Negotiation Complete1 = auto-negotiation process completed0 = auto-negotiation process not completed 0, RO 1:<4> Remote Fault 1 = remote fault condition detected (cleared on read)0 = no remote fault condition detectedWhen in 100Base-FX mode, this bit means an in-band signal Far-End-Fault is detected. Refer to Section 7.11.0, RO1:<3> Auto Negotiation 1 = Link had not been experienced fail state0 = Link had been experienced fail state1, RO 1:<2> Link Status 1 = valid link established0 = no valid link established0, RO 1:<1> Jabber Detect 1 = jabber condition detected0 = no jabber condition detected0, RO 1:<0> Extended Capability 1 = extended register capability0 = basic register capability only 1, RO6.3. Register 2 PHY Identifier Register 1Address Name Description/UsageDefault/Attribute2:<15;0>PHYID1 PHY identifier ID for software recognizeRTL8201BL0000, RO6.4. Register 3 PHY Identifier Register 2Address Name Description/UsageDefault/Attribute3:<15;0>PHYID2PHY identifier ID for software recognize RTL82018201, RO6.5. Register 4 Auto-negotiation Advertisement Register(ANAR)This register contains the advertised abilities of this device as they will be transmitted to its link partner during Auto-negotiation.Address Name Description/UsageDefault/Attribute4:<15> NPNext Page bit.0 = transmitting the primary capability data page 1 = transmitting the protocol specific data page0, RO4:<14> ACK 1 = acknowledge reception of link partner capabilitydata word0 = do not acknowledge reception0, RO 4:<13> RF 1 = advertise remote fault detection capability0 = do not advertise remote fault detection capability0, RW 4:<12:11> Reserved 4:<10> Pause 1 = flow control is supported by local node0 = flow control is NOT supported by local node0, RW 4:<9> T4 1 = 100Base-T4 is supported by local node0 = 100Base-T4 not supported by local node0, RO 4:<8> TXFD 1 = 100Base-TX full duplex is supported by local node0 = 100Base-TX full duplex not supported by local node1, RW 4:<7> TX 1 = 100Base-TX is supported by local node0 = 100Base-TX not supported by local node1, RW 4:<6> 10FD 1 = 10Base-T full duplex supported by local node0 = 10Base-T full duplex not supported by local node1, RW 4:<5> 10 1 = 10Base-T is supported by local node0 = 10Base-T not supported by local node1, RW 4:<4:0> Selector Binary encoded selector supported by this node.Currently only CSMA/CD <00001> is specified. No other protocols are supported.<00001>, RW6.6 Register 5 Auto-Negotiation Link Partner Ability Register(ANLPAR)This register contains the advertised abilities of the Link Partner as received during Auto-negotiation. The content changes after the successful Auto-negotiation if Next-pages are supported.Address Name Description/UsageDefault/Attribute5:<15> NPNext Page bit.0 = transmitting the primary capability data page 1 = transmitting the protocol specific data page0, RO5:<14> ACK 1 = link partner acknowledges reception of localnode’s capability data word 0 = no acknowledgement0, RO 5:<13> RF 1 = link partner is indicating a remote fault0 = link partner does not indicate a remote fault0, RO 5:<12:11> Reserved 5:<10> Pause 1 = flow control is supported by Link partner0 = flow control is NOT supported by Link partner0, RO 5:<9> T4 1 = 100Base-T4 is supported by link partner0 = 100Base-T4 not supported by link partner0, RO 5:<8> TXFD 1 = 100Base-TX full duplex is supported by link partner0 = 100Base-TX full duplex not supported by link partner0, RO5:<7> 100BASE-TX 1 = 100Base-TX is supported by link partner0 = 100Base-TX not supported by link partnerThis bit will also be set after the link in 100Base is established by parallel detection.1, RO5:<6> 10FD 1 = 10Base-T full duplex is supported by link partner0 = 10Base-T full duplex not supported by link partner0, RO 5:<5> 10Base-T 1 = 10Base-T is supported by link partner0 = 10Base-T not supported by link partnerThis bit will also be set after the link in 10Base is established by parallel detection.0, RO5:<4:0> Selector Link Partner’s binary encoded node selectorCurrently only CSMA/CD <00001> is specified<00000>, RO6.7 Register 6 Auto-negotiation Expansion Register(ANER)This register contains additional status for NWay auto-negotiation.Address Name Description/UsageDefault/Attribute6:<15:5> Reserved This bit is always set to 0.6:<4> MLFStatus indicating if a multiple link fault has occurred. 1 = fault occurred 0 = no fault occurred0, RO6:<3>LP_NP_ABLE Status indicating if the link partner supports NextPage negotiation. 1 = supported 0 = not supported0, RO6:<2> NP_ABLE This bit indicates if the local node is able to sendadditional Next Pages.0, RO 6:<1>PAGE_RX This bit is set when a new Link Code Word Page hasbeen received. It is automatically cleared when the auto-negotiation link partner’s ability register (register 5) is read by management.0, RO6:<0>LP_NW_ABLE 1 = link partner supports Nway auto-negotiation.0, RO6.8 Register 16 Nway Setup Register(NSR)AddressName Description/Usage Default/Attribute16:<15:12> Reserved 16:<11> ENNWLE 1 = LED4 Pin indicates linkpulse 0, RW 16:<10> Testfun 1 = Auto-neg speeds up internal timer 0, RW 16:<9> NWLPBK 1 = set Nway to loopback mode. 0, RW 16:<8;3> Reserved 16:<2> FLAGABD 1 = Auto-neg experienced ability detect state 0, RO 16:<1> FLAGPDF 1 = Auto-neg experienced parallel detection fault state 0, RO 16:<0> FLAGLSC 1 = Auto-neg experienced link status check state0, RO6.9 Register 17 Loopback, Bypass, Receiver Error Mask Register(LBREMR)Address Name Description/UsageDefault/Attribute17:<15> RPTR Set to 1 to put the RTL8201BL into repeater mode 0, RW 17:<14>BP_4B5BAssertion of this bit allows bypassing of the 4B/5B & 5B/4B encoder.0, RW17:<13> BP_SCR Assertion of this bit allows bypassing of thescrambler/descrambler.0, RW 17:<12> LDPS Set to 1 to enable Link Down Power Saving mode 0, RW 17:<11> AnalogOFF Set to 1 to power down analog function of transmitterand receiver.0, RW 17:<10> DetectLength Detect length OK indication. Assert low to indicatedetect length OK.0, RO 17:<9:8> LB<1:0> LB<1:0> are register bits for loopback control asdefined below:1) 0 0 for normal mode; 2) 0 1 for PHY loopback; 3) 1 0 for twister loopback<0, 0>, RW17:<7> F_Link_100 Used to logic force good link in 100Mbps fordiagnostic purposes.1, RW 17:<6:5> Reserved 17:<4> CODE_err Assertion of this bit causes a code error detection tobe reported.0, RW 17:<3> PME_err Assertion of this bit causes a pre-mature end errordetection to be reported.0, RW 17:<2> LINK_err Assertion of this bit causes a link error detection to bereported.0, RW 17:<1> PKT_err Assertion of this bit causes a detection of packeterrors due to 722 ms time-out to be reported.0, RW 17:<0> RWPara Parameter access enable, set 1 to access register20~24 0, RW6.10 Register 18 RX_ER Counter(REC)Address Name Description/UsageDefault/Attribute18:<15:0>RXERCNTThis 16-bit counter increments by 1 for each valid packet received.H’[0000], RW6.11 Register 19 10Mbps Network Interface Configuration RegisterAddress Name Description/Usage Default/Attribute19:<15:6> Reserved 19:<5> LD This bit is the active low TPI link disable signal.When low TPIstilltransmit link pulses and TPI stays in good link state.1, RW19:<4:2> Reserved 19:<1> HBEN Heart beat enable 1, RW 19:<0> JBEN 1 = enable jabber function0 = disable jabber function1, RW6.12 Register 20 PHY 1_1 RegisterAddress Name Description/Usage Default/Attribute 20:<15:0> PHY1_1 PHY 1 register (functions as RTL8139C<78>) R/W6.13 Register 21 PHY 1_2 RegisterAddress Name Description/Usage Default/Attribute 21:<15:0> PHY1_2 PHY 1 register (functions as RTL8139C<78>) R/W6.14 Register 22 PHY 2 RegisterAddress Name Description/Usage Default/Attribute 22<15:8> PHY2_76 PHY2 register for cable length test (functions asRORTL8139C<76>)R/W22:<7:0> PHY2_80 PHY2 register for PLL select (functions asRTL8139C<80>)6.15 Register 23 Twister_1 RegisterAddress Name Description/Usage Default/Attribute 23:<15:0> TW_1 Twister register (functions as RTL8139C<7c>) R/W6.16 Register 24 Twister_2 RegisterAddress Name Description/Usage Default/Attribute 24:<15:0> TW_2 Twister register (functions as RTL8139C<7c>) R/W6.17 Register 25 Test RegisterAddress Name Description/Usage Default/ Attribute 25<15:14> Test Reserved for internal testing R/W 25<13> ReservedRO25:<12:8> PHYAD[4:0] Reflects the PHY address defined by external PHYaddress configuration pins25<7:2> Test Reserved for internal testing RORO 25<1> LINK10 1: Link established in 10Base OK0: No link established in 10BaseRO 25<0> LINK100 1: Link established in 100Base OK0: No link established in 100Base7. Functional DescriptionThe RTL8201BL Phyceiver is a physical layer device that integrates 10Base-T and 100Base-TX functions and some extra power manage features into a 48 pin single chip which is used in 10/100 Fast Ethernet applications. This device supports the following functions:MII interface with MDC/MDIO SMI management interface to communicate with MACIEEE 802.3u clause 28 Auto-Negotiation abilityFlow control ability support to cooperate with MACSpeed, duplex, auto-negotiation ability configurable by hard wire or MDC/MDIO.Flexible LED configuration.7-wire SNI(Serial Network Interface) support, works only on 10Mbps mode.Power Down mode support4B/5B transformScrambling/De-scramblingNRZ to NRZI, NRZI to MLT3Manchester Encode and Decode for 10 BaseT operationClock and Data recoveryAdaptive EqualizationFar End Fault Indication (FEFI) in fiber mode7.1 MII and Management Interface7.1.1 Data TransitionTo set the RTL8201BL for MII mode operation, pull MII/SNIB pin high and properly set the ANE, SPEED, and DUPLEX pins. The MII (Media Independent Interface) is an 18-signal interface which is described in IEEE 802.3u supplying a standard interface between PHY and MAC layer. This interface operates in two frequencies – 25Mhz and 2.5Mhz to support 100Mbps/10Mbps bandwidth for both the transmit and receive function. While transmitting packets, the MAC will first assert the TXEN signal and change byte data into 4 bits nibble and pass to the PHY by TXD[0..3]. PHY will sample TXD[0..] synchronously with TXC — the transmit clock signal supplied by PHY – during the interval TXEN is asserted. While receiving a packet, the PHY will assert the RXEN signal, pass the received nibble data RXD[0..3] clocked by RXC, which is recovered from the received data. CRS and COL signals are used for collision detection and handling.In 100Base-TX mode, when decoded signal in 5B is not IDLE, the CRS signal will assert and when 5B is recognized as IDLE it will be de-asserted. In 10Base-T mode, CRS will assert when the 10M preamble been confirmed and will be de-asserted when the IDLE pattern been confirmed.The RXDV signal will be asserted when decoded 5B are /J/K/and will be deasserted if the 5B are /T/R/or IDLE in 100Mbps mode. In 10Mbps mode, the RXDV signal is the same as the CRS signal.The RXER (Receive Error) signal will be asserted if any 5B decode errors occur such as invalid J/K, T/R, invalid symbol, this pin will go high for one or more clock period to indicate to the reconciliation sublayer that an error was detected somewhere in the frame.The RTL8201BL does not use the TXER signal and will not affect the transmit function.7.1.2 Serial ManagementThe MAC layer device can use the MDC/MDIO management interface to control a maximum of 31 RTL8201BL devices, configured with different PHY addresses (00001b to 11111b). During a hardware reset, the logic levels of pins 9,10,12,13,15 are latched into the RTL8201BL to be set as the PHY address for serial management interface communication. Setting the PHY address to 00000b will put the RTL8201BL into power down mode. The read and write frame structure for the。

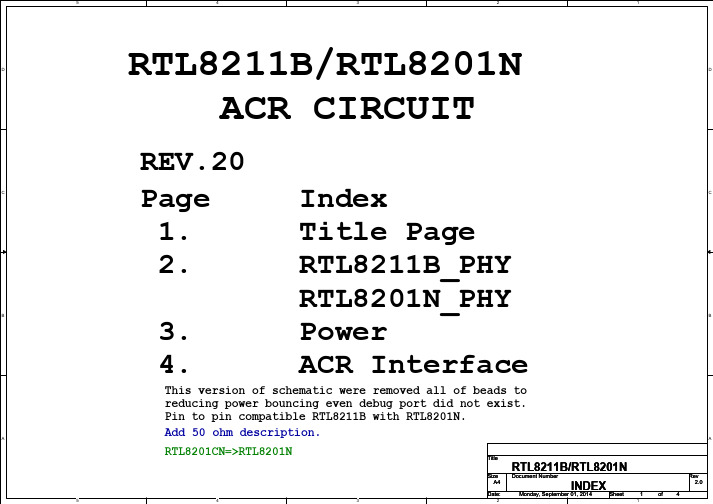

Ethernet_RTL8211B_RTL8201N_NVID

1 PHY_LINK_10 1 PHY_LINK_100 1 PHY_LINK_1000 1 PHY_FDUP 1 PHY_RX 1 PHY_TX

R2 510 R3 510 R4 R7 510 R8 510 R9 510

+ C3 GND

GND

C4

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49

U1

GND C6 .01uF + C7 GND PHY_AVDD18 MDI0+ MDI0PHY_AVDD18 MDI1+ MDI1PHY_AVDD33 CTRL18 PHY_AVDD18 MDI2+ MDI2PHY_AVDD18 MDI3+ MDI3RX_CTL

R10

C

R11 C5

CTRL15 AVDD15 CKXTAL2 CKXTAL1 AVDD33 DVDD15 Config[0] Config[1] Config[2] DVDD33 Config[3] Config[4] RXDLY TXDLY LED_10 DVDD33

D

PHY_AVDD33

C25 .1uF

C26 .1uF

GND VDD33

C

C

CTRL18

CTRL18

Q1 2SB1188 PHY_AVDD18 C28 + C27 10uF GND C32 .1uF .1uF GND GND .1uF .1uF .1uF C29 C30 C31

RTL8201N : Q1,C27,C32 ( NC ) RTL8211B : Q1,C27,C32 ( CONNECTED )

A

A

RTL8201N : Q2,C40,C41 ( NC ) RTL8211B : Q2,C40,C41 ( CONNECTED )

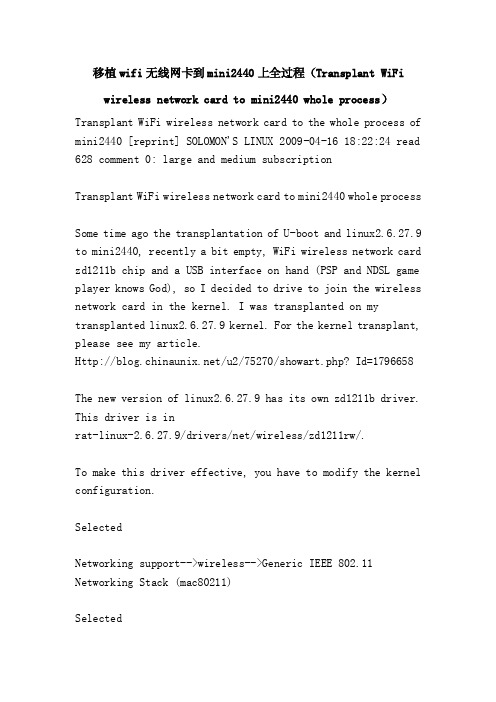

移植wifi无线网卡到mini2...

移植wifi无线网卡到mini2440上全过程(Transplant WiFiwireless network card to mini2440 whole process)Transplant WiFi wireless network card to the whole process of mini2440 [reprint] SOLOMON'S LINUX 2009-04-16 18:22:24 read 628 comment 0: large and medium subscriptionTransplant WiFi wireless network card to mini2440 whole processSome time ago the transplantation of U-boot and linux2.6.27.9 to mini2440, recently a bit empty, WiFi wireless network card zd1211b chip and a USB interface on hand (PSP and NDSL game player knows God), so I decided to drive to join the wireless network card in the kernel. I was transplanted on my transplanted linux2.6.27.9 kernel. For the kernel transplant, please see my article./u2/75270/showart.php? Id=1796658The new version of linux2.6.27.9 has its own zd1211b driver. This driver is inrat-linux-2.6.27.9/drivers/net/wireless/zd1211rw/.To make this driver effective, you have to modify the kernel configuration.SelectedNetworking support-->wireless-->Generic IEEE 802.11 Networking Stack (mac80211)SelectedDevice drivers-->netword device support-->wirelss lan-->ZyDAS ZD1211/ZD1211B USB-wireless supportRecompile kernel. Download to the board, restart. Add wireless network card. AppearUSB 1-1: USB disconnect, address 2USB 1-1: new full speed USB device using s3c2410-ohci and address 3USB 1-1: configuration #1 chosen from 1 choiceUSB 1-1: reset full speed USB device using s3c2410-ohci and address 3Zd1211rw 1-1:1.0: phy1Indicates that the wireless network card has been identified. Using the cat /proc/net/wireless command, you can see more than one wlan0 network card in the system. At this point, the network card is not working. Use lifeIfconfig wlan0 up appears firmware:requesting zd1211, and then it doesn't respond, because there's no reason for firmware, from here/zd1211/zd1211-firmware-1.4 .tar.bz2? Modtime=1191498990&big_mirror=0After downloading to zd1211 firmware 1.4, the zd1211*_* file is copied to the root file system /lib/firmware/zd1211 directory according to the instructions of firmware. thisThen execute the ifconfig wlan0 up command, then appearFirmware: requesting zd1211/zd1211b_ubFirmware: requesting zd1211/zd1211b_uphrZd1211rw 1-1:1.0: firmware version 4725Zd1211rw 1-1:1.0: zd1211b chip 0ace:1215 v4810 full 00-02-72 AL2230_RF PA0 g--NNIC hardware started to work properly. Among them, 0ace:1215 is the network card ID, can use the host Linux system command lsusb to see.But at this point, the network card has not been properly configured, can not be used properly.The normal use of wireless network card, but also the correct configuration. The configuration tool under Linux is wireless-tools, which can be downloaded to the latest version of it./personal/Jean_Tourrilhes/Linux/Tools. htmlAfter downloading, the source code is decompressed. And thenmodify the makefile file, which will beCC = GCCAR = arRANLIB = ranlibInsteadCC = arm-linux-gccAR = arm-linux-arRANLIB = arm-linux-ranlibAfter the make is executed, the generated iwconfig iwlist file is copied to the /bin directory in the root file system of rat-linux for mini2440Copy libiw.so.29 to /lib directory.Start the mini2440 development board, enter the Linux command line, execute the ifconfig wlan0 up, start the wireless network card. Execute iwlist scanning again, and this command can be searchedAvailable wireless network access point. My wireless access point is a wireless router, ESSID is "rat-linux", the implementation of the command will be the following outputWlan0 Scan completed:Cell 01 - Address: 00:19:C6:53:B9:CEESSID: "rat-linux""Mode:MasterChannel:2Frequency:2.417 GHz (Channel 2)Quality=11/100 Signal level:66/100Encryption key:onBit Rates:1 Mb/s; 2 Mb/s; 5.5 Mb/s; 11 Mb/s; 6 Mb/s9 Mb/s; 12 Mb/s; 18 Mb/s; 24 Mb/s; 36 Mb/s48 Mb/s; 54 Mb/sExtra:tsf=000000056306469fExtra: Last beacon: 1065ms agoYou can see that my wireless access point is password. Suppose the password is 123456. Use the following command to set the password.Iwconfig wlan0 key 123456To connect to the wireless network, use the following command to set up the ESSIDIwconfig wlan0 ESSID "rat-linux""Other parameters can be used without the default. You can use the following command to join the wireless network.Iwconfig wlan0 AP AutoAnd then iwconfig wlan0, you can see the following information.Wlan0 IEEE 802.11BG ESSID: "rat-linux""Mode:Managed Frequency:2.417 GHz Access Point:00:19:C6:53:B9:CEBit Rate=1 Mb/s Tx-Power=27 dBmRetry min limit:7 RTS thr:off Fragment thr=2352 BEncryption key:1234-56 Security mode:openPower Management:offLink Quality=100/100 Signal level:66/100Rx invalid nwid:0 Rx invalid crypt:0 Rx invalid frag:0Tx excessive retries:0 Invalid misc:0 Missed beacon:0This means that it has access to wireless networks.Finally, specify the IP address for the wireless network card. The following commandsIfconfig wlan0 192.168.1.30 netmask 255.255.255.0My development host and wireless network card are in the same network segment, so they can communicate with each other through PING. Therefore, you can use the IP address of the PING wireless network card on the host to ensure the networkDoes the card work properly?. The Ping 192.168.1.30 is executed on the host, and the normal PING pass.So far, the wireless network card installation is complete.Finally, in order to facilitate the configuration, the above configuration commands can be written into the Linux script file. After that, the configuration of the above steps can be completed as long as the script is executed. Script fileAs follows.# /bin/sh!Ifconfig wlan0 upIwconfig wlan0 key 123456Iwconfig wlan0 ESSID "rat-linux""Iwconfig wlan0 AP AutoIfconfig wlan0 192.168.1.30 netmask 255.255.255.0Note: the test using the HUAWEI hg522 wireless SAGEM XG-760N ZD1211B cat Sagem wireless card (Zydas)Telecomadmin password: nE7jA%5mSecurity settings WEPWEP certification: share 64bit / / if 128bit, the password is too long iwconfig password will return errorKey 12312Iwconfig wlan0 ESSID "ChinaNet-WS4P""Iwconfig wlan0 key s:12312iwconfig wlan0 ap carifconfig wlan0 192.168.1.30 netmask 255.255.255.0另有加密方式 wpa-psk 加密模式: tkip / aes / tkip aes +- 加密模式同上 wpa2 psk如果wep加密长度设为128bit, 则密码太长 iwconfig配置密码时会返回错误:error for wireless television "set encode" (8b2a):set options on device wlan0; invalid argument.无线模式如何设置无线网络的wpa - psk安全认证11 / 03 / 2010 | 08: 17分类: 未分类 |在笔记本电脑上安装slackware 10.1之后, 无线连接一直用wep认证.wep尽管比什么都不用要安全一点, 但是还是很容易被人破解, 而wpa认证在安全性上更有保障.wpa - psk更适合家庭用户使用, 相比企业级应用的wpa认证, 尽管安全性上稍逊, 但设置上简单得多, 不需要专门的认证服务器.下面是在slackware 10.1上设置wpa - psk的过程和配置文件, 主要软硬件环境是: slackware 10.1, 内核版本2.6.10, intel 2200b / g 无线网卡.首先是升级无线网卡的驱动程序.按下列顺序安装有关程序:1.从 http: / / 下载ieee80211-1.2.16.tgz 源码, 并编译安装 (make & make install).在其后运行的时候, 出现了 michael _ mic: tfm _ michael = = null 的错误提示, 说明模块安装时出现问题, 下载相关的补丁程序: http: / / / patches /ieee80211-1.2.16-crypt-fix2.patch 再度编译安装后, 错误消失.2.从 http: / / 下载ipw2200-1.2.1.tgz, 用 make & make install 编译安装.如果原来已经安装了ipw2200的驱动程序, 升级前用源码目录中的 remove old 脚本进行卸载.3.从 http: / / 下载 3.0版的firmware, 解压缩到 / lib / firmware / 目录.如果之前已经安装了旧版本的firmware, 直接删除有关文件即可.然后, 安装wpa _ supplicant从 http: / / hostap.epitest.fi / wpa wpa supplicant supplicant / 下载 _ _ - 0.4.9 的源码, 在源码目录建立.config 文件, 内容是:config _ driver _ ipw = y用 make & make install 编译安装.安装后, 运行 wpa passphrase your - your - _ ssid pre shared key 产生16进制表示的密码串, 其中 your - ssid 是无线网络的ssid, your - pre - shared - key就是wpa - psk认证所需的密码.产生的结果要放到 / etc / wpa _ supplicant.conf 文件中去, 内容是:network = {ssid = "your - ssid" # 这里是无线网络的ssidproto = wpakey _ mgmt = wpa-pskpairwise = tkippsk = xxxxxxxxxxxxxxxx # 这个就是用wpa _ passphrase命令生成的16进制串}最后, slackware 10.1及之前版本的用户, 到 http: / / / ~ alien / rc _ scripts / 下载 rc.inet1 和rc.wireless 脚本, 用来替换 / etc / rc.d 目录中的相应文件, 注意要赋予它们可执行属性 (chmod - x).然后建立 / etc / rc.d / rc.wireless.conf 内容如下:ipw2200″ info = ')# essid (extended 无线网络的ssid network name):essid = "your ssid.nwid = ""operation method: # ad-hoc managed master repeater, secondary, autostyle = "auto"# frequency or channel 1, 2, 3, 2.422g (channel), 2.46g (frequency)freq = ""channel = "6″ # 与无线ap / 路由器的设置一致# (cell size and the phase speed): 1, 2, 3; 70 (dbm) direction = ""# bit rate: car 11 feet.rate = ""# encryption key: development - 89ab - cd: passwordkey = "# 使用wpa - psk时, 这里保持空白# rts threshold: off, 500rts = ""a # fragmentation threshold: off"points"the iwconfig # parameters: power off, ap 01: 23 45 67, 89, ab iwconfig = ""# iwspy parameters: 01: 23 45 67, 89, abiwspy = ""# iwpriv parameters: set _ port 2, and _ conducted 50 60iwpriv = ""# wpa support, set key = "")"_ supplicant wpa wpa._ supplicant # wpa.wpadriver = "ipw" # 使用ipw2200驱动重新启动系统, 无线网络的wpa - psk认证就可以工作了.无线加密――wpa-psk加密的设置方法及特点 (五)一、wpa简介we 是改进wep所使用密钥的安全性的协议和算法.它改变了密钥生成方式, fi保护接入 (wpa) (wired equivalent privacy) 更频繁地变换密钥来获得安全.它还增加了消息完整性检查功能来防止数据包伪造. wpa的功能是替代现行的wep 协议.过去的无线lan之所以不太安全, 是因为在标准加密技术 "wep" 中存在一些缺点.wpa是继承了wep基本原理而又解决了wep缺点的一种新技术.由于加强了生成加密密钥的算法, 因此即便收集到分组信息并对其进行解析, 也几乎无法计算出通用密钥.wpa还追加了防止数据中途被篡改的功能和认证功能.由于具备这些功能, wep中此前倍受指责的缺点得以全部解决.二、wpa在家庭无线网络中的应用.完整的wpa实现是比较复杂的, 由于操作过程比较困难 (微软针对这些设置过程还专门开设了一门认证课程), 一般用户实现是不太现实.所以在家庭网络中采用的是wpa的简化版――wpa-psk (预共享密钥).这篇文档进行加密举例使用是我司无线宽带路由器tl - wr941n和无线网卡tl - wn821nwep加密方式可以分别和open system、shared key链路认证方式使用.1.采用open system authentication方式: 此时wep密钥只做加密, 即使密钥配的不一致, 用户也是可以上线, 但上线后传输的数据会因为密钥不一致被接收端丢弃.2.采用shared key authentication方式: 此时如果双方密钥不一致, 客户端就不能通过shared key认证, 无法上线.也就是说, 当wep和shared key认证方式配合使用时, wep也可以作为一种认证方法.无线网卡的master, managed, ad hoc monitor等模式无线网卡的工作模式Wireless network cards can work in a variety of modes. Common patterns are Master, Managed, ad-hoc, monitor, and so on.For Master mode, it is mainly used in wireless access point AP, providing wireless access service and routing function. We can imagine using a wireless router is in Master mode, but for ordinary PC, if there is a suitable hardware it can also turninto a wireless AP. In LINUX, the use of software HOSTAP can make a Linux PC has AP function, but the current HOSTAP support of wireless network card is limited, my INTEL Centrino PRO 4965 wireless card is not supported by hostap.For general wireless network cards, the most common patterns are managed, ad-hoc and monitor. Managed mode for wireless AP access connection, in this mode, we can wireless access, Internet access to the internet. The ad-hoc mode can be used when the two hosts need to be connected directly, so that the hosts are connected in a peer-to-peer way. The Monitor model is mainly used for monitoring the internal wireless network traffic, network is used to check and troubleshooting.The difference between Promiscuous and Monitor (RFMON)In the traditional finite network, we know that the network card can work in two modes, that is, ordinary and promiscuous modes. Under the Promiscuous mode, we can monitor the traffic inside the Ethernet directly. When this card does not distinguish between the data packets through the target address is not the machine, altogether will check for the upper layer of the protocol stack under section. This is also the basic basis for the existence of traditional sniffer software.There are differences and similarities between wireless networks and traditional wired ethernet. Wireless LAN signal transmission is completely broadcast by radio means, which means that each person can have a certain device to receive and crack the wireless signal. So wireless LAN is more insecure than wired network. According to the theory, when a network card isconnected to a known wireless network, it should be able to be configured as promiscuous mode to accept all packets as the traditional Ethernet network. Because in wireless environment, all wireless signals can be received by the network card, wireless AP can not play a switch to achieve point to point restriction forwarding. But the reality is that the current driver seems to have not yet developed enough to support such promiscuous patterns, at least for my IPW4965.But this does not mean that there is no way to monitor wireless traffic. The wireless network card has a special mode, that is, mode mode (monitor monitor, or RFMON, Radio Frequence). I have said all packets are transmitted by radio signals, so in this mode under network card can receive all it can receive the radio signal and trying to parse, but not limited to the wireless lan. This model has a fundamental role in the discovery mechanism of wireless LAN, but also provides an invisible tool to crack wireless lan. Some tools such as KISMET, NetStumbler and so on can use monitor mode to discover the SSID of WLAN and crack its password.It sounds like the monitor model is far more than the promiscuous model, but for the wireless LAN software development, there is no promicuous mode is a very troublesome thing. At least I'm still working on that. Although a little hope, such as in the monitor mode of packet injection, but the specific implementation remains to be explored.。

网络接口MII和PHY芯片

网络接口MII和PHYPHY指物理层,OSI的最底层。

一般指与外部信号接口的芯片。

以太网PHY芯片网络中最基础的部件是什么?不是交换机也不是路由器,而是小小的不起眼但又无处不在的网卡。

如果在5年前,或许网卡与您无关,但在如今这网络的时代,无论是上网冲浪还是联网玩游戏,都离不开网卡,更何况,就算您不食人间烟火,多数主板上也会为您集成一块板载网卡。

所以,对于想迈入网络之门的读者而言,先认识网卡,会让您在进行各种网络应用时更得心应手。

一、网卡的主要特点网卡(Network Interface Card,简称NIC),也称网络适配器,是电脑与局域网相互连接的设备。

无论是普通电脑还是高端服务器,只要连接到局域网,就都需要安装一块网卡。

如果有必要,一台电脑也可以同时安装两块或多块网卡。

电脑之间在进行相互通讯时,数据不是以流而是以帧的方式进行传输的。

我们可以把帧看做是一种数据包,在数据包中不仅包含有数据信息,而且还包含有数据的发送地、接收地信息和数据的校验信息。

一块网卡包括OSI模型的两个层——物理层和数据链路层。

物理层定义了数据传送与接收所需要的电与光信号、线路状态、时钟基准、数据编码和电路等,并向数据链路层设备提供标准接口。

数据链路层则提供寻址机构、数据帧的构建、数据差错检查、传送控制、向网络层提供标准的数据接口等功能。

网卡的功能主要有两个:一是将电脑的数据封装为帧,并通过网线(对无线网络来说就是电磁波)将数据发送到网络上去;二是接收网络上其它设备传过来的帧,并将帧重新组合成数据,发送到所在的电脑中。

网卡能接收所有在网络上传输的信号,但正常情况下只接受发送到该电脑的帧和广播帧,将其余的帧丢弃。

然后,传送到系统CPU做进一步处理。

当电脑发送数据时,网卡等待合适的时间将分组插入到数据流中。

接收系统通知电脑消息是否完整地到达,如果出现问题,将要求对方重新发送。

二、图解网卡以最常见的PCI接口的网卡为例,一块网卡主要由PCB线路板、主芯片、数据汞、金手指(总线插槽接口)、BOOTROM、EEPROM、晶振、RJ45接口、指示灯、固定片等等,以及一些二极管、电阻电容等组成。

BootMii完整安装图文教程变砖后可以修复

BootMii完整安装图⽂教程变砖后可以修复BootMii 完整安装图⽂教程变砖后可以修复含安装视频视频, BootMii, 教程本帖最后由 kavid 于 2010-1-8 19:59 编辑BootMii是⼀套安装在wii上你提供更多,更安全,更⽅便的软件。

作⽤:BootMii可以安装在启动进程⾥,也可以安装成⼀个IOS。

IOS的⽅式将让你更快捷地备份wii NAND记忆体,破解最新的wii。

启动进程⽅式为你提供⼀个“安全的区域”,你可以在3分钟之内备份整个Wii到SD卡上。

如果wii 不幸砖了,你可以通过BootMii 来还原在SD上的备份。

BootMii还可以跳过健康提⽰画⾯,直接运⾏SD卡上的HBC或者其他的后门程序。

下载:/doc/0f106c649b6648d7c1c746c5.html /thread-13145-1-1.html安装:1,准备⼀张SD卡,⽤此教程⾥⾯的程序格式化/doc/0f106c649b6648d7c1c746c5.html /thread-5943-1-1.html 2,下载hackmii_installer_beta1.zip压缩包后,把installer_beta1.elf改名成boot.dol,如下放置放到apps\hackmii\boot.dol3,然后通过HBC运⾏此程序,如果没有安装HBC参考此教程:/doc/0f106c649b6648d7c1c746c5.html /thread-12921-1-1.html4,运⾏后等⼏秒就能看到如下画⾯了,然后按“1”继续:5,看到如下画⾯,三个绿⾊提⽰,就说明你的机器可以安装成boot2模式。

boot2问题会在另外⼀篇教程说明。

6,还有些⼈也会看到如下画⾯,说明不能安装boot2模式,只能安装成IOS模式(⽬前没有程序对应):7,不管看到什么我们都按“A”继续安装了。

这⾥建议安装HBC,因为此处提供的是1.0.2版本,⽀持硬盘读取⾃制程序。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Hardwire Configuration network:

1. This configuration shows Enable: Auto negotiation, Full duplex, 100Mbps, Link Down Power Saving, MII interface Disable: Isolate, Repeater mode 2. These senven configuration pins could be connected to VDD or GND directly.

VDD33 R28 5.1K

R30 0

C20 0.1U GND

R13 5.1K

R14 5.1K

R15 5.1K

R16 5.1K

R17 5.1K

2

LED1/PHYAD1 D2 LED LED2/PHYAD2 D3 LED LED3/PHYAD3 D4 LED LED4/PHYAD4

R20 5.1K

R21 510

U1 MDC MDIO TXD0 TXD1 TXD2 TXD3 TXEN TXC RXDV RXD0 RXD1 RXD2 RXD3 RXC COL CRS RXER/FXEN X1 X2 PWFBOUT AVDD33 AGND AGND 32 36 29 35 PWFBOUT AVDD33 C1 PWFBOUT 0.1U GND GND R1 R2 50(1%) 50(1%) U2 NC 27 1 2 TPRX+ TPRXTPTXTPTX+ RTSET ISOLATE RPTR SPEED DUPLEX ANE LDPS MII/SNIB/RTT3 RESETB 31 30 33 34 28 43 40 39 38 37 41 44 42 3 15 14 16 RD+ RDCT TDCT TD+ RX+ CT RXTXCMT TX+ 7 5 6 11 12 10 1 2 3 4 5 6 7 8 R7 75 R8 75 R9 75 R10 75 U3 TX+ TXRX+ N/C N/C RXN/C N/C RJ8-45 CH_GND C9 0.01U/3KV R11 5.1K R12 5.1K GND GND 9 C4 0.1U GND C3 0.1U GND C2 0.1U GND

4

Connect to MAC which has MII interface

for EMI supression

4

RTL8201BL

Y1 LED0/PHYAD0 LED1/PHYAD1 LED2/PHYAD2 LED3/PHYAD3 LED4/PHYAD4

C5 25.000Mhz 20P GND

C6 20P GND PWFBIN

A

B

C

D

E

VDD33

R31 1.5K MDC MDIO TXD0 TXD1 TXD2 TXD3 TXEN TXCLK RXDV RXD0 RXD1 RXD2 RXD3 RXCLK COL CRS RXER 25 26 6 5 4 3 2 7 22 21 20 19 18 16 1 23 24 46 47 9 10 12 13 15

Place C14, C15, L1 close to PWFBOUT and place C16 close to PWFBIN.

1

1

GND

LED0 Link

LED1 Dupx

LED2 10Act

LED3 100Act

LED4 COL

Title Size B Date:

RTL8201BL application circuit - interface with MAC(MII) Document Number RTL8201BL MII Monday, September 01, 2014 Sheet

VDD33

2

R22 5.1K

5VDD R23 510 U4 3 2 1 C12 0.1U LM1117 GND GND

VDD33 VDD33 L2 BEAD

R24 5.1K

AVDD33 C17 0.1U GND

U1/pin14

VDD33

U1/pin48

VDD33 PWFBOUT C14 22U GND C15 0.1U GND

LED0/PHYAD0 LED1/PHYAD1 LED2/PHYAD2 LED3/PHYAD3 LED4/PHYAD4 PWFBIN DVDD33 DVDD33 DGND DGND DGND

PWFBIN 8 VDD33 14 VDD33 48 11 17 45

R5 5.9K (1%) GND

R3 50(1%)

R4 50(1%)

YUTAI YL18-2001S

3

C8 0.1U GND

(CONNECT TO CHASSIS GND)

3

GND

RTL8201BL LQFP48 R29 0 PCI_Reset

This schematic sets PHY address to 00001b. You could set PHY address from 00001b to 11111b. But the LED polarity must matchs the respective PHYAD setting. Refer to datasheet's detailed description.

E

Rev 1.2 1 of 1

A

B

C

D

L1 BEAD C16 0.1U GND PWFBIN

INPUT R25 510 OUTPUT ADJ/GND

C18 0.1U GND

C19 0.1U GND

R26 5.1K

C13 2218, C19 as close to each power pin as possible.

1. You could simply connect RESETB of RTL8201BL to PCI Reset. And just discard R30, R28, C20. 2. If Wake on Lan feature is needed, you have to supply power form auxiliary power for all LAN-related circuit including RTL8201BL and MAC. In this kind of application, discard R29 and retain other components for one resetting upon power up.