PCB印刷线路板阻抗控制

PCB电路板PCB阻抗计算

PCB电路板PCB阻抗计算在PCB电路板上,信号传输通过导线和平面层完成,信号的传输速度会受到导线和平面之间的阻抗匹配影响。

如果导线和平面之间的阻抗不匹配,信号反射和干扰可能会发生,导致信号品质下降甚至无法正常传输。

为了保证PCB电路板上的信号传输性能,我们需要计算和控制PCB电路板上的阻抗。

下面将介绍PCB阻抗计算的一般步骤和常见方法。

1.理论基础:PCB阻抗计算的理论基础是电磁场理论和电路分析。

其中,电磁场理论涉及导线和平面之间的电感、电容和电阻;而电路分析则涉及传输线和电源之间的线路电感、电容和电阻。

2.PCB结构:3.PCB阻抗计算的步骤:-确定所需阻抗数值:在设计PCB电路板之前,需要根据电路需求和信号特性确定所需的阻抗数值。

常见的阻抗数值有50欧姆和75欧姆。

-确定PCB结构:根据电路需求和阻抗数值,设计PCB的信号层、地层和电源层。

一般来说,信号层之间的间距较小,而信号层与地层或电源层之间的间距较大。

-计算阻抗:使用专业的PCB设计软件或在线计算工具,根据PCB结构和阻抗数值计算阻抗。

一些常见的计算方法包括物理建模方法、电路模型方法和数值模拟方法。

-优化PCB布局:根据计算结果,对PCB的布局进行优化。

可以根据需要调整信号层、地层和电源层之间的间距,或者增加层间引距、增加屏蔽层等。

-信号完整性分析:使用信号完整性分析工具对PCB布局进行验证,检查信号的传输性能是否满足要求。

如果存在问题,可以对PCB进行进一步优化。

4.常见的PCB阻抗计算方法:-物理建模方法:根据导线和平面的尺寸、距离和材料参数,使用物理公式计算阻抗。

这种方法适用于简单的PCB结构和导线几何形状。

-电路模型方法:根据传输线电路模型,将PCB导线抽象为等效电路元件,使用电路分析方法计算阻抗。

这种方法适用于复杂的PCB结构和高速信号传输。

-数值模拟方法:使用计算机仿真软件,对PCB结构进行数值模拟,计算阻抗。

这种方法适用于不规则的PCB结构和高频信号传输。

PCB阻抗设计准则

PCB阻抗设计准则PCB(Printed Circuit Board)阻抗设计是在高速电路设计中的一个关键环节,它直接影响到电路的性能和稳定性。

合理的阻抗设计可以减少信号的反射、串扰和损耗,提高信号的传输质量和稳定性。

在进行PCB阻抗设计时,有一些准则需要遵循。

下面将详细介绍这些准则。

1.根据电路需求确定PCB层次:根据电路的复杂程度,确定PCB的多层设计,其中内层可以用作阻抗控制层。

2.定位器研究和优化:通过研究信号的传输路径和布线,确定合适的定位器位置,使信号的功率尽量平均分布在整个PCB中。

3.地的设计:地是阻抗设计中非常重要的一部分,良好的地设计可以减少信号的反射和串扰。

要避免地回流,需使用地孔。

4.差分信号的布局:差分信号的布局能使得信号平等的分布在PCB上,减少串扰和不匹配引起的损耗。

5.控制合理的层间间距:层间间距会影响信号的传输速度,通常的层间距是4H,其中H为标准PCB高度。

6.保持合适的阻抗匹配:根据信号的频率和阻抗需求选择合适的线宽和距离,以确保阻抗的匹配。

7.特殊形状的布线:对于高速信号,可以采用宽度变化、走线方式变化等布线技巧来优化阻抗控制。

8.合理绘制地平面:在整个PCB中布满地平面,以减少信号的反射和串扰,提高信号的质量。

9.足够的缝隙:为了避免因成本考虑太小的缝隙导致信号失效,需要仔细考虑线宽和缝隙的选择。

10.验证和优化设计:在完成阻抗设计后,通过使用仿真工具和实际测试来验证设计的正确性,如果有必要,则进行优化。

以上是PCB阻抗设计的一些准则,实际设计过程中还需根据具体的电路需求和工艺条件来做出适当的调整。

通过合理的阻抗设计,可以提高电路的性能和稳定性,满足高速电路的要求。

PCB阻抗控制

PCB阻抗PCB阻抗控制,在PCB设计中经常遇到阻抗计算,但是我不明白阻抗计算是计算整板PCB的阻抗还是几个部分的阻抗PCB阻抗,在PCB设计中经常遇到阻抗计算,但是我不明白阻抗计算是计算整板PCB的阻抗还是几个部分的阻抗:如我有差分阻抗,单线阻抗。

那到底该采用哪些数值呢?可能几个部分的阻抗都不一样在同一PCB板上?这样的话该计算哪个阻抗来作为PCB的阻抗呢!完整性最佳。

是不是每个地方阻抗不一样,我得告诉PCB厂商,这个地方阻抗做多少,哪个地方阻抗做多少啊,比如:USB2.0差分做成90欧姆,DDR与DSP连接线做成多少欧姆,和时钟线做成多少欧姆等等啊?这样的话是不是要详细说明多处的阻抗要求。

关键布线部分是要给出详细的设计要求的,设计时的阻抗大小,是通过仿真软件,使信号完整性达到最好状态下,得到的。

根据仿真结果,可以得到该信号线的线长,线宽,线间距,在那层布线,串接多大的匹配电阻等要求,然后仿真设计人员将此仿真结果交给PCB LAUOUT设计人员,PCB LAUOUT设计人员会根据此要求进行PCB布线设计,设计完毕后的PCB文件生成为GERBER文件,送给PCB制造厂商即可制造出相应的PCB。

1.阻抗控制是控制信号线的阻抗,不是整板PCB的阻抗2.差分阻抗是两条差分信号的阻抗,单线阻抗是单一信号的阻抗。

如USB 2.0要做差分90欧姆,射频信号线一般做单线50欧姆等等。

哪些线要做阻抗控制,控制为多少,一般每个硬件平台都有自己的要求。

3.没有PCB阻抗这种说法,只有信号的阻抗。

电路设计中,差分信号的两条差分线能不能交换顺序?题目说的有些笼统,主要是想知道哪些是可以交换的,为什么,哪些是不可以交换的,又是为什么?还有差分线之间跨加100ohm或12 0ohm的电阻的作用是什么,是阻抗匹配还是将电流转换为电压?各位大牛,ths了会变小。

差分信号实际传输是电压还是电流,什么差分信号,说的通俗一点,差分信号时属于数字信号吗进一步看是以电压为的标准的能量信号,若内阻小,就可以带多个负载(电流大)。

PCB阻抗设计参考

PCB阻抗设计参考在PCB设计中,阻抗是一个非常重要的参数,尤其对于高频信号传输和数字信号传输。

正确设计PCB阻抗可以确保信号的稳定传输和减少信号衰减。

一般来说,要设计PCB的阻抗,需要考虑以下几个方面:1.材料特性:首先要了解所使用的PCB板材的介电常数和介磁常数。

这些参数会对阻抗产生影响,例如常用FR-4板材的介电常数在4.2~4.5之间。

2.PCB层结构:多层板的设计中,每一层的布线方式会影响阻抗。

通过选择合适的层次安排来控制阻抗。

两层板可以使用不同的宽度和间距的微带线或者分界线以控制阻抗,而对于多层板可以考虑使用阵列线、共面线、差分线等方式控制阻抗。

3. 线宽和间距的选择:根据所需的阻抗值和PCB的板厚,可以通过一些公式来选择合适的线宽和间距。

常用的公式有美国电气工程协会(IEEE)和Roger Ghirardi等提出的公式。

4.主要参数计算:对于常用的阻抗控制线如微带线、分界线和差分线,可以根据它们的几何特性和材料参数计算出所需的阻抗。

例如对于一条微带线,阻抗可以根据线宽、线距、介电常数等参数,使用公式计算得出。

5.仿真工具:使用仿真工具对阻抗进行验证也是一种常用的方法。

通过在仿真软件中建立PCB的模型,可以模拟信号在PCB中的传输情况,从而验证设计所得阻抗的准确性。

6.实际布局:在进行实际布局时,要确保实际线宽和间距与设计要求相符。

可以使用追踪宽度测量工具来检查PCB上的线宽,并使用追踪间距工具来检查线间距。

此外,还要注意信号线和地线的排列,以尽可能减小信号线的距离地线的距离。

通过合理的PCB阻抗设计,可以使得信号在PCB上得到稳定传输,减少信号衰减,提高系统的性能和可靠性。

(注:此回答基于2024年的知识,并不包括当前最新的技术和趋势,如有需要请参考最新资料和指导。

PCB电路板PCB阻抗计算

PCB电路板PCB阻抗计算在PCB电路板设计中,阻抗是一个非常重要的参数。

准确计算和控制PCB电路板的阻抗可以确保信号的传输质量,减少信号损耗和干扰,并提高电路的性能。

1.厚度模型法2.三维建模法三维建模法是一种精确计算PCB阻抗的方法。

在这种方法中,使用电磁场仿真软件对整个PCB电路板进行三维建模,根据所使用的材料参数和几何特征,计算出电磁场的分布和阻抗。

这种方法可以考虑到更多的因素,如接地和供电平面的存在对阻抗的影响。

3.公式计算法除了使用软件模拟的方法,还可以使用一些公式来粗略计算PCB电路板的阻抗。

例如,对于微带线,可以使用公式Z=87/(sqrt(εr+1.41)) * ln(5.98*h/w+1.41)来计算阻抗,其中εr是相对介电常数,h是线的高度,w是线的宽度。

4.经验法对于一些常见的线宽和线距组合,也可以使用经验法来估算PCB电路板的阻抗。

例如,根据常见的线宽和线距组合的经验值,可以制定一个阻抗表格,根据线宽和线距的值查找相应的阻抗。

在进行PCB阻抗计算时,还需要考虑信号频率的影响。

因为电路板的阻抗会随着频率的变化而变化,因此需要根据实际的工作频率来计算阻抗。

通常,在高频应用中,PCB的阻抗控制更为严格。

为了准确计算PCB电路板的阻抗,建议使用专业的PCB设计软件,该软件通常会提供阻抗计算工具和阻抗模拟分析。

在进行阻抗计算之前,还需要正确设置PCB的材料参数和几何特征。

总结起来,PCB阻抗的计算是一个非常重要的任务,对于保证电路的性能和传输质量至关重要。

通过合理选取计算方法和使用专业工具,可以准确计算和控制PCB电路板的阻抗,从而提高电路的可靠性和稳定性。

pcb阻抗设计要求

PCB阻抗设计要求介绍PCB(Printed Circuit Board)是电子产品中常见的一种电路板,用于连接和支持电子元件。

在PCB设计中,阻抗是一个重要的参数,它决定了电路板传输信号的质量和稳定性。

本文将探讨PCB阻抗设计的要求和技巧。

为什么需要阻抗设计阻抗是电路中的电阻和电感的综合体现,它与电流和电压的比例有关。

在PCB设计中,阻抗的控制对于信号的传输和抗干扰能力起着重要作用。

具体而言,以下是为什么需要阻抗设计的几个原因:1.信号完整性: 控制阻抗可以减少信号的反射和衰减,确保信号在传输过程中保持完整性,减少失真。

2.抗干扰能力: 正确的阻抗匹配可以提高电路板的抗干扰能力,减少外界电磁干扰对信号的影响。

3.功耗优化: 合理的阻抗设计可以降低功耗,提高电路的效率和稳定性。

PCB阻抗设计要求1. 阻抗规格在进行PCB阻抗设计之前,首先需要明确设计要求和规格。

根据设计的电路和信号要求,确定所需的阻抗数值。

常见的PCB阻抗规格包括50欧姆(Ω)和75欧姆(Ω),根据不同的应用选择合适的数值。

2. 材料选择PCB阻抗设计的首要任务是选择合适的材料。

常见的PCB材料包括FR-4和Rogers 等。

FR-4是一种常用的玻璃纤维层压板材料,适用于一般电路板设计。

Rogers材料具有更好的阻抗控制和高频特性,适用于高性能和高频率的应用。

3. 线宽和线间距线宽和线间距是影响PCB阻抗的重要参数。

根据所需的阻抗数值和材料特性,选择合适的线宽和线间距。

通常情况下,线宽越宽,阻抗越低;线间距越小,阻抗越高。

4. 地平面设计地平面是PCB阻抗设计中的关键因素之一。

在设计过程中,应尽量保持地平面的连续性和完整性。

通过增加地平面的面积,可以降低电感和电阻,提高阻抗的稳定性和一致性。

5. 信号层和电源层分离为了减少信号层和电源层之间的相互干扰,应尽量将它们分离开来。

通过在信号层和电源层之间设置地层,可以有效地减少电磁干扰和信号损耗。

印刷电路板(PCB)的特性阻抗与特性阻抗控制

印刷电路板(PCB)的特性阻抗与特性阻抗控制印刷电路板(PCB)的特性阻抗与特性阻抗控制1、电阻交流电流流过一个导体时,所受到的阻力称为阻抗(Impedance),符合为Z,单位还是Ω。

此时的阻力同直流电流所遇到的阻力有差别,除了电阻的阻力以外,还有感抗(XL)和容抗(XC)的阻力问题。

为区别直流电的电阻,将交流电所遇到之阻力称为阻抗(Z)。

Z=√ R2 +(XL -XC)22、阻抗(Z)近年来,IC集成度的提高和应用,其信号传输频率和速度越来越高,因而在印制板导线中,信号传输(发射)高到某一定值后,便会受到印制板导线本身的影响,从而导致传输信号的严重失真或完全丧失。

这表明,PCB导线所“流通”的“东西”并不是电流,而是方波讯号或脉冲在能量上的传输。

3、特性阻抗控制(Z0 )上述此种“讯号”传输时所受到的阻力,另称为“特性阻抗”,代表符号为Z0。

所以,PCB导线上单解决“通”、“断”和“短路”的问题还不够,还要控制导线的特性阻抗问题。

就是说,高速传输、高频讯号传输的传输线,在质量上要比传输导线严格得多。

不再是“开路/短路”测试过关,或者缺口、毛刺未超过线宽的20%,就能接收。

必须要求测定特性阻抗值,这个阻抗也要控制在公差以内,否则,只有报废,不得返工。

二、讯号传播与传输线1、信号传输线定义(1)根据电磁波的原理,波长(λ)越短,频率(f)越高。

两者的乘积为光速。

即C = λ.f =3×1010 cm/s(2)任何元器件,尽管具有很高的信号传输频率,但经过PCB导线传输后,原来很高的传输频率将降下来,或时间延迟了。

因此,导线长度越短越好。

(3)提高PCB布线密度或缩短导线尺寸是有利的。

但是,随着元件频率的加快,或脉冲周期的缩短,导线长度接近信号波长(速度)的某一范围,此时元件在PCB导线传输时,便会出现明显的“失真”。

(4)IPC-2141的3.4.4提出:当信号在导线中传输时,如果导线长度接近信号波长的1/7时,此时的导线被视为信号传输线。

PCB阻抗控制解决方案

PCB阻抗控制解决方案随着PCB 信号切换速度不断增长,当今的PCB 设计厂商需要理解和控制PCB 迹线的阻抗。

相应于现代数字电路较短的信号传输时间和较高的时钟速率,PCB 迹线不再是简单的连接,而是传输线。

在实际情况中,需要在数字边际速度高于1ns或模拟频率超过300Mhz时控制迹线阻抗。

PCB 迹线的关键参数之一是其特性阻抗(即波沿信号传输线路传送时电压与电流的比值)。

印制电路板上导线的特性阻抗是电路板设计的一个重要指标,特别是在高频电路的PCB设计中,必须考虑导线的特性阻抗和器件或信号所要求的特性阻抗是否一致,是否匹配。

这就涉及到两个概念:阻抗控制与阻抗匹配,本文重点讨论阻抗控制和叠层设计的问题。

阻抗控制阻抗控制(eImpedance Controling),线路板中的导体中会有各种信号的传递,为提高其传输速率而必须提高其频率,线路本身若因蚀刻,叠层厚度,导线宽度等不同因素,将会造成阻抗值得变化,使其信号失真。

故在高速线路板上的导体,其阻抗值应控制在某一范围之内,称为阻抗控制。

PCB 迹线的阻抗将由其感应和电容性电感、电阻和电导系数确定。

影响PCB走线的阻抗的因素主要有:铜线的宽度、铜线的厚度、介质的介电常数、介质的厚度、焊盘的厚度、地线的路径、走线周边的走线等。

PCB 阻抗的范围是25 至120 欧姆。

在实际情况下,PCB 传输线路通常由一个导线迹线、一个或多个参考层和绝缘材质组成。

迹线和板层构成了控制阻抗。

PCB 将常常采用多层结构,并且控制阻抗也可以采用各种方式来构建。

但是,无论使用什么方式,阻抗值都将由其物理结构和绝缘材料的电子特性决定:信号迹线的宽度和厚度迹线两侧的内核或预填材质的高度。

PCB线路板常用阻抗设计及叠层结构

PCB线路板常用阻抗设计及叠层结构PCB线路板的设计中,阻抗是一个重要的考虑因素。

阻抗设计是为了保证信号传输的质量和可靠性。

阻抗是指电流和电压之间的相对比例。

在PCB线路板设计中,要求电路中的高速和高频信号传输能够保持最佳的传输质量,所以需要对不同的信号进行不同的阻抗设计。

本文主要介绍PCB线路板常用的阻抗设计及叠层结构。

一、阻抗概述阻抗是电路中的一个重要参数,它描述了电路中电流和电压的关系。

在高速传输的PCB设计中,考虑阻抗的阻抗匹配特性,以尽量减少信号的反射和干扰,确保信号传输质量的稳定和可靠。

二、常用的阻抗设计1、单端阻抗设计单端阻抗设计是在单层PCB上完成的,适用于低频和中频的信号传输。

设计单端阻抗的目的是保持信号传输线的特性阻抗在设计范围内。

单端阻抗设计要考虑线宽、线距、板厚等因素,可通过常见的PCB设计软件实现。

2、差分阻抗设计差分阻抗设计是应用于高速传输的场合,旨在提高信号传输质量与带宽。

差分阻抗是指正负极性间的信号传输线阻抗,它相对于地线的阻抗相等。

差分阻抗的设计需要考虑线宽、线距、板层、板厚等因素,同时需要对信号输入端口的匹配进行优化。

三、常用的PCB线路板叠层开发结构1、4层板结构4层板结构是常见的PCB线路板设计中的最简单的叠层结构。

它包括两个内层地面层和两个信号层。

它通常被用于低频和中频电路设计,因为它具有较低的成本和更好的EMI性能。

2、6层板结构6层板结构是在4层的基础上增加信号层和地面层,同时也增加了堆叠方式的选择。

这使得6层板结构适用于更高频的应用程序,因为它具有更好的阻抗控制和EMI性能。

3、8层板结构8层板结构包括4层信号层和4层地面层。

在8层板结构中,可以通过两个内层地面层的特殊排布减少串扰,这使得它成为高速传输PCB线路板设计的理想选择。

此外,在PCB线路板设计中,8层板结构通常用于高密度板级设计,因为它提供更多的丰富选项和更好的EMI性能。

四、总结阻抗设计是PCB线路板设计中的一个重要环节,它要求传输线的特性阻抗能够稳定在设计范围内。

PCB生产工程阻抗制作规范

工程阻抗制作规范1.目的规范制作阻抗P C B的阻抗计算和阻抗图形设计方法,确保成品的阻抗符合规定。

2.适用范围适用于本厂客户要求阻抗控制的P C B的阻抗设计及之C A M制作的阻抗图形设计。

3.名词解释3.1特性阻抗(C h a r a c t e r i s t i c I m p e d a n c e):当一条导线与大地绝缘后,导线与大地彼此之间的阻抗。

3.2差分阻抗(D i f f e r e n t i a l I m p e d a n c e):二条平行导线与大地绝缘后的阻抗,两条导线与大地彼此之间的阻抗。

4.阻抗控制的制作规格范围一般地,对于成品产品来说,我司控制的阻抗值的规格范围为±10%,如客户又特别要求,可根据客户设计的产品结构或客户要求的阻抗规格制作。

4.1 与阻抗控制计算有关的各个材质的计算参数如下:⑴. 芯板:介电常数为4.5±0.2操作中,根据客户要求,以及产品的需要,可向板材供应商了解芯板的具体层压结构,然后依照该芯板的Prepreg配方的介电常数来计算。

⑵. 7628 PrepregA、介电常数为4.5±0.2B、压合后的介质厚度为(内层100%残铜理论值):RC%47 压合后的介质厚度为190±10UM,RC%43 压合后的介质厚度为180±15UM。

⑶. 2116 PrepregA、介电常数为4.3±0.2B、压合后的介质厚度为(内层100%残铜理论值):RC%54 压合后的介质厚度为118±10UM,RC%50 压合后的介质厚度为105±10UM。

⑷. 1080 PrepregA、介电常数为4.2±0.2B、压合后的介质厚度为(内层100%残铜理论值):RC68% 压合后的介质厚度为71±8UM,RC%62 压合后的介质厚度为65±8UM。

⑸. 当选用几种Prepreg同时压合时,则采用最高的介电常数与最低的介电常数的平均值进行计算。

PCB的阻抗控制要点

^谈PCB的阻抗控制随着电路设计日趋复杂和高速,如何保证各种信号(特别是高速信号)完整性,也就是保证信号质量,成为难题。

此时,需要借助传输线理论进行分析,控制信号线的特征阻抗匹配成为关键,不严格的阻抗控制,将引发相当大的信号反射和信号失真,导致设计失败。

常见的信号,如PCI总线、PCI-E总线、USB、以太网、DDR内存、LVDS信号等,均需要进行阻抗控制。

阻抗控制最终需要通过PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB 厂的沟通,并结合EDA软件的使用,我对这个问题有了一些粗浅的认识,愿和大家分享。

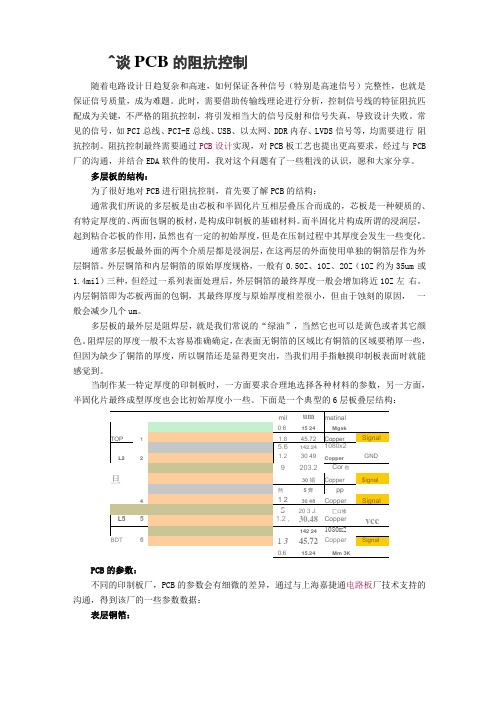

多层板的结构:为了很好地对PCB进行阻抗控制,首先要了解PCB的结构:通常我们所说的多层板是由芯板和半固化片互相层叠压合而成的,芯板是一种硬质的、有特定厚度的、两面包铜的板材,是构成印制板的基础材料。

而半固化片构成所谓的浸润层,起到粘合芯板的作用,虽然也有一定的初始厚度,但是在压制过程中其厚度会发生一些变化。

通常多层板最外面的两个介质层都是浸润层,在这两层的外面使用单独的铜箔层作为外层铜箔。

外层铜箔和内层铜箔的原始厚度规格,一般有0.5OZ、1OZ、2OZ(1OZ约为35um 或1.4mil)三种,但经过一系列表面处理后,外层铜箔的最终厚度一般会增加将近1OZ左右。

内层铜箔即为芯板两面的包铜,其最终厚度与原始厚度相差很小,但由于蚀刻的原因,一般会减少几个um。

多层板的最外层是阻焊层,就是我们常说的“绿油”,当然它也可以是黄色或者其它颜色。

阻焊层的厚度一般不太容易准确确定,在表面无铜箔的区域比有铜箔的区域要稍厚一些,但因为缺少了铜箔的厚度,所以铜箔还是显得更突出,当我们用手指触摸印制板表面时就能感觉到。

当制作某一特定厚度的印制板时,一方面要求合理地选择各种材料的参数,另一方面,半固化片最终成型厚度也会比初始厚度小一些。

下面是一个典型的6层板叠层结构:0.615.24Mm 3KPCB的参数:不同的印制板厂,PCB的参数会有细微的差异,通过与上海嘉捷通电路板厂技术支持的沟通,得到该厂的一些参数数据:表层铜箔:可以使用的表层铜箔材料厚度有三种:12um、18um和35um。

探讨PCB特性阻抗控制精度

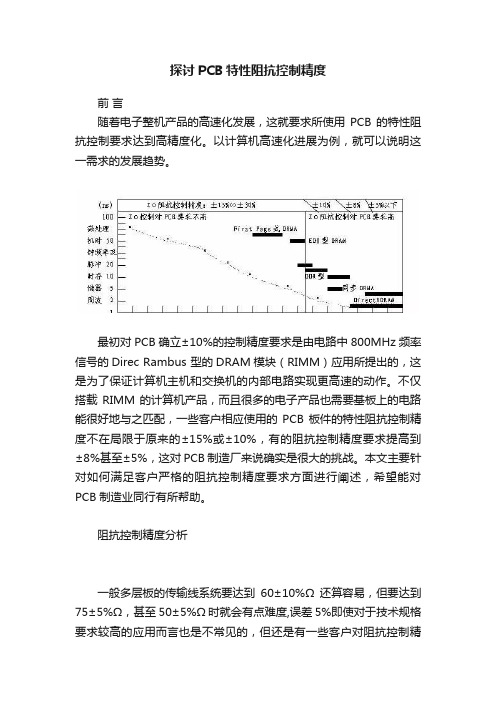

探讨PCB特性阻抗控制精度前言随着电子整机产品的高速化发展,这就要求所使用PCB的特性阻抗控制要求达到高精度化。

以计算机高速化进展为例,就可以说明这一需求的发展趋势。

最初对PCB确立±10%的控制精度要求是由电路中800MHz频率信号的Direc Rambus 型的DRAM模块(RIMM)应用所提出的,这是为了保证计算机主机和交换机的内部电路实现更高速的动作。

不仅搭载RIMM的计算机产品,而且很多的电子产品也需要基板上的电路能很好地与之匹配,一些客户相应使用的PCB板件的特性阻抗控制精度不在局限于原来的±15%或±10%,有的阻抗控制精度要求提高到±8%甚至±5%,这对PCB制造厂来说确实是很大的挑战。

本文主要针对如何满足客户严格的阻抗控制精度要求方面进行阐述,希望能对PCB制造业同行有所帮助。

阻抗控制精度分析一般多层板的传输线系统要达到60±10%Ω还算容易,但要达到75±5%Ω,甚至50±5%Ω时就会有点难度,误差5%即使对于技术规格要求较高的应用而言也是不常见的,但还是有一些客户对阻抗控制精度提出了±5%的要求,现举例来说明。

以下是我司生产的一种板件,该板的要求:4层板,完成板厚1.0±0.10mm,板材采用FR4,客户有指定的叠层结构,见下图其中TOP层有单线阻抗要求,参考层为第2层,其中单线阻抗线宽W1要求12.0MIL,阻抗要求50±5%Ω(50±2.5Ω),其结构如下:对于客户如此严格的阻抗控制精度要求,如何去满足?下面来谈谈我们公司是如何去进行控制的。

PCB特性阻抗的模拟计算对于有阻抗控制要求的板,目前,PCB工厂比较常见的做法就是在PCB的生产拼版板边适当位置设计一些阻抗试样,这些阻抗试样具有与PCB相同的分层和阻抗线构造。

在设计阻抗试样前会预先采用一些阻抗计算软件对阻抗进行模拟计算,以便对阻抗进行预测。

PCB FPC 电路板阻抗知识培训资料

H1

L4INT2 L5VCC

PP 2116 (4.1mil) INT2 FR4 1/1 0.15mm (6.0mil) VCC PP 2116HR (2.5mil)

L6

铜箔 0.5oz (0.7mil)

L6

电子表格应填入之数据: (L3线路量测层之理论奥姆值) Hinght (H): 35.4 (基材厚度-指量测层往上/往下最接近之地

Impedance Change

A

B

Incident

energy

Transmitted Energy

Reflected energy

阻抗之设计

四、阻抗之设计 印刷电路板对阻抗之要求,不外乎要求控制线路之宽度、厚度 及相关之绝缘层厚度。欲控制之层数越多,则难度越高;一般而 言,对阻抗之设计,不外乎下列三种结构,任何阻抗均可由此衍 生而来: (A)Microstrip 结构

1. 影响阻抗之主要因素: 印刷电路板对阻抗之要求,不外乎要求控制线路宽度,厚度及 相关之绝缘层厚度,欲控制之层数愈多,则难度愈高,主要影响 阻抗因素如下: A. 线宽:与阻抗值成反比,线宽↓,阻抗值↑,线宽↑,阻抗值 ↓ B. 迭构(压合厚度): 与阻抗值成正比,厚度↑,阻抗值↑,厚度 ↓,阻抗值↓ C. 介电介数(Er值): 与阻抗值成反比,介电↓,阻抗值↑,介电 ↑,阻抗值↓

(2)一旦多层板线路质量不良,等特性阻抗值超出公差时,所传讯 号的能量将出现反射(Reflection)、散失(dissipation)、衰减 (Attenuation)或延误(Delay)等劣化现象,严重时甚至出现讯号之 当机情形。 当A组件经由板面线路向B发出讯号,若该讯号线的线宽不均,造成 特性阻抗值上起伏变化时,则讯号的部份能量会反回A中去。

PCB阻抗值因素与计算方法

PCB阻抗值因素与计算方法PCB(Printed Circuit Board)阻抗是PCB设计中一个关键的参数,它对于保证板上信号传输的质量和稳定性非常重要。

PCB阻抗值通常是以Ohms(Ω)为单位来表示,是指电源或信号线上的电阻。

1. PCB材料:PCB的材料对阻抗有很大影响。

不同的材料具有不同的频率和温度相关的介电常数,这会直接影响到阻抗值的大小。

常见的PCB材料有FR4(玻璃纤维增强的环氧树脂)、Rogers(一种高频率材料)和PTFE(聚四氟乙烯,也是一种高频率材料)。

2.PCB层次和布线:PCB的阻抗也与板的层次和布线方式相关。

一般来说,多层板能提供更大的设计灵活性以及更好的阻抗控制。

当需要较低的阻抗值时,可以使用高阻抗的内层。

而布线方式则通过控制信号线的宽度、间距以及层数等参数来控制阻抗,常见的布线方式有微带线和同轴线。

3.信号的频率:信号的频率对于阻抗值也有很大的影响。

随着频率的增加,阻抗值也会增加。

这是因为随着频率的增加,信号更容易“逃逸”到PCB旁路上,从而增大了电流的路径长度。

根据以上因素,我们可以通过一些计算方法来估算或计算PCB的阻抗值:1.基于PCB材料的公式:根据不同的PCB材料,可以利用相关的公式来计算PCB阻抗。

例如,对于常用的FR4材料,可以使用Er=1+(εr-1)*(1-e^(-0.046*√(f)))来计算介电常数Er,从而进一步计算阻抗。

2. 基于PCB几何形状的公式:针对不同的布线方式,可以利用一些公式来计算PCB的阻抗。

例如,对于微带线布线方式,可以使用公式Zo= 87 / √(εr + 1.41) * (W/H + 0.67)来计算阻抗,其中Zo是阻抗,W是线宽,H是板的厚度,εr是介电常数。

而对于同轴线布线方式,可以使用公式Zo = 60 / √(εr) * ln(D/d)来计算阻抗,其中Zo是阻抗,D 是外层导体直径,d是内层导体直径。

3. 通过仿真软件:除了上述的方法,我们还可以使用一些仿真软件来快速计算PCB的阻抗。

印制电路板(PCB)的阻抗控制介绍

印制电路板(PCB)的阻抗控制介绍一:特性阻抗原理:传输线的定义,在国际标准IPC-2141 3.4.4说明其原则“当 信号在导线中传输时,若该导线长度大到信号波长的1/7,则该导线应被视做传输线。

如当某电磁波信号以时钟频率为900MHZ (GSM手机传输频率)在导线中传播时,则如果线路的长度大于:1/7波长=1C/7F=4.76CM 时,该线路就被定义为传输线。

众所周知,直流电路中电流传输时遇到的阻力叫电阻,交流电路中电流遇到的阻力叫阻抗而高频(》400MHZ )电路中传输信号所遇到的阻力叫特性阻抗,在高频情况下,印制板上的传输信号铜导线可以被视为由一串等效电阻及一并连电感所组合而成的传导线路,而此等效电阻在高频分析时小到可以忽略不记,因此我们在对一个印制板的信号传输进行高频分析时,则只需考虑杂散分布之串联电感及并联电容的效应,我们可以得到以下公式;Z0=R+√L/C √≈√L/C ( Z0为特性阻抗值)关于特性阻抗,有以下几原则:1、 在数字信号在板子上传输时,印制板线路的特性阻抗值必须与头尾元件的电子阻抗匹配,如果不匹配的话,所传送的信号能量将出现反射,散失,衰减,或延误,等现象,从而产生杂信,2、 由于电子元件的电子阻抗越高时,其传输速率才越快,因而电路板的特性阻抗值也要随之提高,才能与之匹配,3、射频通信用的PCB ,除强调 Z0外,有时更加强调板材本身具有低的 Er (介质常数)值及低的Df (介质损耗因子)值。

高频信号在介质中的传输速度为C/ Er,可知:Er 越小,传输速度越快,这也是为何高频要用低介质常数的高频材料。

Df 影响着信号在介质传输过程中的失真,Df 越小,失真越小。

二:特性阻抗的常见形式和计算方法:在线路板的设计中,传输信号最常见的有4种单线布线和2种差分布线方式方式:以上四种单线传输信号布线方式的阻抗计算公式见下;(差分略)1、 微带线:Z 。

=87ln 「5.98H/(0.8W+T )」Er+1.412、 埋入式微带线Z 。

PCB阻抗控制

PCB阻抗控制随着PCB 信号切换速度不断增长,当今的PCB 设计厂商需要理解和控制 PCB 迹线的阻抗。

相应于现代数字电路较短的信号传输时间和较高的时钟速率,PCB 迹线不再是简单的连接,而是传输线。

在实际情况中,需要在数字边际速度高于1ns或模拟频率超过300Mhz时控制迹线阻抗。

PCB 迹线的关键参数之一是其特性阻抗(即波沿信号传输线路传送时电压与电流的比值)。

印制电路板上导线的特性阻抗是电路板设计的一个重要指标,特别是在高频电路的PCB设计中,必须考虑导线的特性阻抗和器件或信号所要求的特性阻抗是否一致,是否匹配。

这就涉及到两个概念:阻抗控制与阻抗匹配,本文重点讨论阻抗控制和叠层设计的问题。

阻抗控制阻抗控制(eImpedance Controling),线路板中的导体中会有各种信号的传递,为提高其传输速率而必须提高其频率,线路本身若因蚀刻,叠层厚度,导线宽度等不同因素,将会造成阻抗值得变化,使其信号失真。

故在高速线路板上的导体,其阻抗值应控制在某一范围之内,称为“阻抗控制”。

PCB 迹线的阻抗将由其感应和电容性电感、电阻和电导系数确定。

影响PCB走线的阻抗的因素主要有: 铜线的宽度、铜线的厚度、介质的介电常数、介质的厚度、焊盘的厚度、地线的路径、走线周边的走线等。

PCB 阻抗的范围是 25 至120 欧姆。

在实际情况下,PCB 传输线路通常由一个导线迹线、一个或多个参考层和绝缘材质组成。

迹线和板层构成了控制阻抗。

PCB 将常常采用多层结构,并且控制阻抗也可以采用各种方式来构建。

但是,无论使用什么方式,阻抗值都将由其物理结构和绝缘材料的电子特性决定:•信号迹线的宽度和厚度•迹线两侧的内核或预填材质的高度•迹线和板层的配置•内核和预填材质的绝缘常数PCB传输线主要有两种形式:微带线(Microstrip)与带状线(Stripline)。

微带线(Microstrip):微带线是一根带状导线,指只有一边存在参考平面的传输线,顶部和侧边都曝置于空气中(也可上敷涂覆层),位于绝缘常数 Er 线路板的表面之上,以电源或接地层为参考。

PCB迹线的阻抗控制技术

随着通信科技的不断提升,必然对实现其功能的硬件载体—印刷电路板(Printed Circuit Board:简称为PCB)的要求也有了相应的提高,传统意义上PCB已受到严峻的挑战,以往PCB的最高要求open&short从目前来看已变成PCB的最基本要求,取而代之的是一些为保证客户设计意图而在PCB上所体现出的性能要求,如阻抗控制等。

在过去几年之中,阻抗控制的PCB已经开始从纯粹的专家应用转变为更加普及的应用,到目前为止有阻抗控制要求的PCB已广泛的应用于我司传输、视讯、电源、移动、交换、接入、网络、手机等产品中。

本文以PCB迹线的阻抗控制为中心,结合我所在PCB设计过程中的阻抗控制经验,从以下三个方面分别进行了讨论。

一、PCB迹线的阻抗控制简介二、传输线阻抗计算中的有关问题三、传输线阻抗控制典型应用总结一PCB迹线的阻抗控制简介1. PCB迹线的阻抗控制电信产品和计算机设备操作的速度和切换速率正在不断增长。

尽管在低频情况下,这是一个可以忽略的物理规律,但现在却需要严肃考虑了。

现代PCB上处理器时钟速度和组件切换速度的提高意味着组件间的互连路径(例如PCB迹线:PCB trace)不能再视为简单的导线。

实际应用中快速切换速度或高频(即数字边际速度超过1ns或者模拟频率大于300MHz)的PCB迹线必须视为传输线--其电子特性必须由 PCB 设计厂商来控制的信号线。

就是说,为了稳定和可预测的高速运行,PCB迹线和PCB绝缘物的电子特性必须得到控制。

PCB 迹线的关键参数之一就是其特性阻抗(即波沿信号传输线路传送时电压与电流的比值)。

这是一个有关迹线物理尺寸(例如迹线的宽度和厚度)和PCB底板材质的绝缘物厚度的函数。

实际情况中,PCB传输线路通常由一个导线迹线、一个或者多个参考层和绝缘材质组成。

传输线路,即迹线和板材共同实现控制阻抗。

PCB通常采用多层结构,并且控制阻抗也可以采用多层方式来构建。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

接地層 介質層

Home

1.阻抗匹配: 將訊號的傳輸看成軟管送水澆花

此時可將傳輸線(常見者有同軸電纜Coaxial Cable,與微帶線 Microstrip Line 或帶線 Strip Line 等)看成軟管,而握管處所施加的 壓力,就好比板面上“接受端”(Receiver)元件所並聯到 Gnd 的電 阻器一般,可用以調節其終點的特性阻抗(Characteristic Impedance),使匹配接受端元件內部的需求。

Home

1.阻抗匹配: 將訊號的傳輸看成軟管送水澆花 數位系統之多層板訊號線(Signal Line)中,當出現方 波訊號的傳輸時,可將之假想成為軟管(hose)送水澆 花。一端於手握處加壓使其射出水柱,另一端接在水龍 頭。當握管處所施壓的力道恰好,而讓水柱的射程正確 灑落在目標區.

Home

1.阻抗匹配: 將訊號的傳輸看成軟管送水澆花 然而一旦用力過度水注射程太遠,不但騰空越過目標浪費 水資源。也有可能因強力水壓無處宣洩,以致往來源反彈 造成軟管自龍頭上的掙脫! (阻抗太高)

Home

2.傳輸線之終端控管技術(Termination) 由上可知當“訊號”在傳輸線中飛馳旅行而到達終點, 欲進入接受元件(如 CPU 或 Memory 等大小不同的 IC )中工作時,則該訊號線本身所具備的“特性阻抗”, 必須要與終端元件內部的電子阻抗相互匹配才行,如此 才不致任務失敗白忙一場。用電腦術語說就是“正確執 行指令,減少雜訊干擾,避免錯誤動作”。一旦彼此未 能匹配時,則必將會有少許能量回頭朝向“發送端”反 彈,進而形成反射雜訊(Noise)的煩惱。

Home

166B6-102E-(0141)- ý ª

(1)¤ ¹ ¼ « « : ¶ q h p × h ¸ ¼¦ L1/2 L2/3 L3/4 L4/5 L5/6 (2)ª § ½ ¼ ¶ ´ : ý Ü u e q ú

q ú Â ¶ ´ I

Ü §

£ ¤

} ¨

À ¤

R ª

ø ³

i (¦ « ) § ¨ ~

0.100 ”

Drill Size <= 1.05mm PTH Holes

Dummy pad = Follow PCB HOUSE Dummy Pad Definition

(Dummy trace) x2

Line Width = 21mil (Outer layer) = 21mil (Internal layer) Line Space = 26mil (Outer layer) min = 21mil (Internal layer) min

Home

4.阻抗計算的邏輯 如左列結構, 計算阻抗時應先從外 層算起(Microstrip line), 外層阻抗 計算出來後可得到L1~L2及L9~L10 的介電層厚度, 然後再計算內層阻 抗, 因為內層結構為兩個Strip line 結構所組成, 算出L3及L4的阻抗結 構後, 一般的結構為對稱性設計, 故 可得到另一組L7及L8的阻抗結構, 至於L5~L6的介電層為介於兩層 GND之間, 所以這段厚度不會影響 阻抗, 可配合各介電層厚度總和, 自 由調整該處厚度.

ý Ü q ú ª § ¶ ´ ê Ú È ¹ »

Tek¶ ´ q ú ê Ú È ¹ »

u e ½¼ spec(line) É p » «

ê Ú q ú È ¹ » ¶ ´

L1

50.0~60.0£ [

56.82

56.39

L3

50.0~60.0£ [

60.33

60.4

L4

50.0~60.0£ [

6. 阻抗線路檢查事項 ( Imp. Trace Review Items )

正確的Coupon設計 (Correct Coupon Design)

GND Connection Dummy Pad

Imp. Traces

Dummy Traces

1. 正確的阻抗線路長度 ( 3 ~ 6 inch and up) 2. 足夠的 Dummy Trace 線距 (I/L: Min. 21 mil ; O/L : Min. 26 mil )

2001/10/13

SPEC 4.1 5.0 24.1 5.0 4.0 Ó 0.5 ¡ Ó 0.5 ¡ Ó 0.5 ¡ Ó 0.5 ¡ Ó 0.5 ¡ mil mil mil mil mil

ê Ú q ú È ¹ » ¶ ´ NO.1 4.17 4.92 23.24 4.96 4..05

ý Ü ª § spec

線路上鑽孔、不適當的Dummy pad、不適當的Anti-Pad

上下層線路重疊、量測點間距不符規定

6. 阻抗線路檢查事項 ( Imp. Trace Review Items )

Impedance coupon design rule

Single-end Impedance

0.100 ”

Impedance Trace = Simulated Line Width/Space Trace Length = 3”~6”

6. 阻抗線路檢查事項 ( Imp. Trace Review Items )

Impedance coupon design rule

Differential Impedance

0.100 ” 0.100 ”

Impedance Trace = Simulated Line width/Space Trace Length = 3”~6”

阻抗值與介電層厚度成正比.

Home

3.特性阻抗的定義(Characteristic Impedance) 阻抗值與線寬成反比 .

Home

3.特性阻抗的定義(Characteristic Impedance) 阻抗值與介電常數成反比.

¶qhp× ¤ ¹ ¼« « 2 3 4 5 6 7 8 10 12 14 15 16 Er 3.7 3.7 3.8 3.8 3.9 4.1 4.2 4.3 4.3 4.6 4.6 4.7 Er (HTg) 3.5 3.5 3.6 3.6 3.7 3.9 4 4.1 4.1 4.4 4.4 4.5

Home

3.特性阻抗的定義(Characteristic Impedance) 阻抗值與銅厚成反比

Home

3.特性阻抗的定義(Characteristic Impedance) 當上述微帶線中Z0的四種變數(w、t、h、 r)有任一項 發生異常,例如下圖的訊號線出現缺口時,將使得原來的 Z0突然上升(見上述公式中之Z0與W成反比的事實),而 無法繼續維持應有的穩定均勻(Continuous)時,則其 訊號的能量必然會發生部分前進,而部分卻反彈反射的缺 失。如此將無法避免雜訊及誤動作了。下圖中的軟管突然 被小朋友踩住,造成軟管兩端都出現異常,正好可說明上 述特性阻抗匹配不良的問題。

Home

1.阻抗匹配: 將訊號的傳輸看成軟管送水澆花 反之,當握處之擠壓不足以致射程太近者,則照樣得不到 想要的結果。(阻抗太低) 唯有拿捏恰到好處才能符合實際需求的距離。(阻抗匹配)

Home

1.阻抗匹配: 將訊號的傳輸看成軟管送水澆花 上述簡單的生活細節,正可用以說明方波(Square Wave )訊號(Signal)在多層板傳輸線(Transmission Line ,係由訊號線、介質層、及接地層三者所共同組成)中所 進行的快速傳送。 訊號線

Home

3.特性阻抗的定義(Characteristic Impedance)

阻抗設計簡單的說就是找一組參數(介電層厚度H , 線寬W , 介電常數 εr , 銅厚T) 的組合, 使參數代入公式中可以命中規格中值. 使用 APSIM RLGC模擬軟體計算阻抗, 相關作業程序, 請參考阻抗模擬作 業規範. 下圖為各參數與阻抗的關係.

4.29 5.23 2.16 4.09 4.60 1.37 4.37 5.15 1.45 3.93 5.08 2.52

5.材料成本的考量

1) 2) 3) 4) ISOLA材料最貴 單張材料一定比兩張材料便宜 以7628 ft2為基礎,其他為7628之倍數 NP180(FR 5)的比NP 170貴1.1倍

Home

2.傳輸線之終端控管技術(Termination) 當傳輸線本身的特性阻抗(Z0)被設計者訂定為28ohm 時,則終端控管的接地的電阻器(Zt)也必須是28ohm ,如此才能協助傳輸線對Z0的保持,使整體得以穩定在 28 ohm的設計數值。也唯有在此種 Z0=Zt 的匹配情形 下,訊號的傳輸才會最具效率,其“訊號完整性”( Signal Integrity,為訊號品質之專用術語)也才最好。

如何做好阻抗控制

如何做好阻抗控制

1.阻抗匹配 2.傳輸線之終端控管技術(Termination) 3.特性阻抗的定義(Characteristic Impedance) 4.阻抗計算的邏輯 5.材料成本的考量 6.阻抗線路檢查事項 ( Imp. Trace Review Items ) 7. 壓合結構設計重點

3. 正確的參考層接地點

4. 不可有其他造成干擾阻抗信號因素 (Drill on Trace、Thieving、 Anti-Pad、Near Traces、Insufficient pitch of holes)

58.5

59.14

L6

50.0~60.0£ [

58.37

59.25

W ¤ 5.0~5.5 ¤ U ª ° W ¤ 4.75~5.75 ¤ U ª ° W ¤ 4.75~5.75 ¤ U ª ° W ¤ 5.0~5.5 ¤ U ª °

T ´ T ´ × « T ´ T ´ × « T ´ T ´ × « T ´ T ´ × «

Home

3.特性阻抗的定義(Characteristic Impedance) 上述部分訊號能量的反彈,將造成原來良好ቤተ መጻሕፍቲ ባይዱ質的方波訊 號,立即出現異常的變形(即發生高準位向上的 Overshoot,與低準位向下的 Undershoot,以及二者後 續的 Ringing。此等高頻雜訊嚴重時還會引發誤動作,而 且當時脈速度愈快時雜訊愈多也愈容易出錯。