LM2465TANOPB;中文规格书,Datasheet资料

LMP92001SQENOPB;LMP92001SQXNOPB;LMP92001EVALNOPB;中文规格书,Datasheet资料

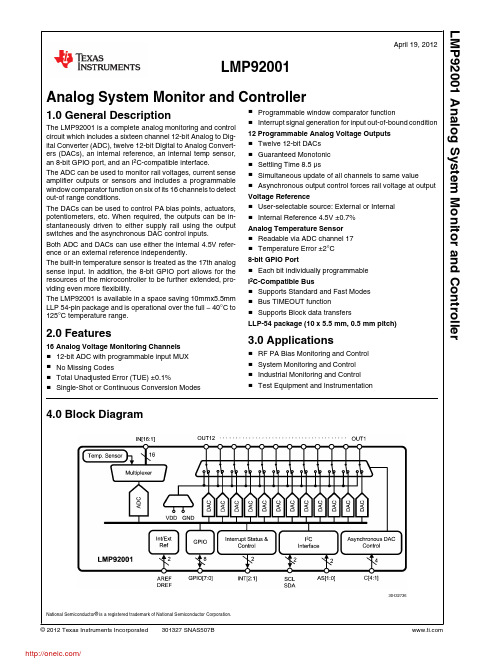

LMP92001April 19, 2012 Analog System Monitor and Controller1.0 General DescriptionThe LMP92001 is a complete analog monitoring and control circuit which includes a sixteen channel 12-bit Analog to Dig-ital Converter (ADC), twelve 12-bit Digital to Analog Convert-ers (DACs), an internal reference, an internal temp sensor, an 8-bit GPIO port, and an I2C-compatible interface.The ADC can be used to monitor rail voltages, current sense amplifier outputs or sensors and includes a programmable window comparator function on six of its 16 channels to detect out-of range conditions.The DACs can be used to control PA bias points, actuators, potentiometers, etc. When required, the outputs can be in-stantaneously driven to either supply rail using the output switches and the asynchronous DAC control inputs.Both ADC and DACs can use either the internal 4.5V refer-ence or an external reference independently.The built-in temperature sensor is treated as the 17th analog sense input. In addition, the 8-bit G PIO port allows for the resources of the microcontroller to be further extended, pro-viding even more flexibility.The LMP92001 is available in a space saving 10mmx5.5mm LLP 54-pin package and is operational over the full − 40°C to 125°C temperature range.2.0 Features16 Analog Voltage Monitoring Channels■12-bit ADC with programmable input MUX■No Missing Codes■Total Unadjusted Error (TUE) ±0.1%■Single-Shot or Continuous Conversion Modes ■Programmable window comparator function■Interrupt signal generation for input out-of-bound condition 12 Programmable Analog Voltage Outputs■Twelve 12-bit DACs■Guaranteed Monotonic■Settling Time 8.5 µs■Simultaneous update of all channels to same value■Asynchronous output control forces rail voltage at output Voltage Reference■User-selectable source: External or Internal■Internal Reference 4.5V ±0.7%Analog Temperature Sensor■Readable via ADC channel 17■Temperature Error ±2°C8-bit GPIO Port■Each bit individually programmableI2C-Compatible Bus■Supports Standard and Fast Modes■Bus TIMEOUT function■Supports Block data transfersLLP-54 package (10 x 5.5 mm, 0.5 mm pitch)3.0 Applications■RF PA Bias Monitoring and Control■System Monitoring and Control■Industrial Monitoring and Control■Test Equipment and Instrumentation4.0 Block Diagram30132736 National Semiconductor® is a registered trademark of National Semiconductor Corporation.© 2012 Texas Instruments Incorporated301327 SNAS507B LMP92001 Analog System Monitor and Controller5.0 Typical Application30132706 2L M P 920016.0 OverviewThe LMP92001 has a flexible, feature-rich functionality which makes it ideally suited for many analog monitoring and control applications, for example base-station PA subsystems. This device provides the analog interface between a pro-grammable supervisor, such as a microcontroller, and an analog system whose behavior is to be monitored and con-trolled by the supervisor.To facilitate analog monitoring functionality, the device con-tains a single 12-bit ADC fronted by a 17-input multiplexor. The 16 MUX inputs are available to the user via pins IN[16:1]. The last remaining MUX channel is reserved for the internal analog temperature sensor.The analog control functionality is served by twelve 12-bit voltage output DACs. Besides producing voltage correspond-ing to the digital input code, the DACs can be forced by the user to either rail instantaneously.Additional digital monitoring and control can be realized via the General Purpose I/O port GPIO[7:0].Two more blocks are present for added functionality: a local temperature sensor (already mentioned above) and an inter-nal reference voltage generator.6.1 17-CHANNEL ANALOG SENSE WITH 12-BIT ADC The user can monitor up to 16 external voltages with the 12-bit ADC and its 17-channel input MUX. Typically these volt-ages will be generated by the analog sensors, instrumenta-tion amplifiers, current sense amplifiers, or simply resistive dividers if high potentials need to be measured. Channel 17 of the input MUX is reserved for the internal temperature sen-sor, and is not available as an external input to the device. User can program which MUX channels to enable, and whether to convert these channel inputs in sequence contin-uously, or in a single-shot mode. Upon completion all con-version results are stored in the internal data registers, and can be read back by the user via the I2C-compatible interface. Analog input channels 1-3 and 9-11 have a built-in digital window comparator function with user programmable thresh-olds. This function can be used to alert the supervisor micro-controller of an out-of-bound condition. The comparator function result is stored in the internal status register which is user accessible. It can also be used as the interrupt signal generator where the out of bound conditions will be reported via the INT[2:1] output pins.Sequencing of the analog sense system is governed by the internal controller. Once enabled the MUX, the ADC, the win-dow comparator and the interrupts perform their function without further user intervention.6.2 PROGRAMMABLE ANALOG CONTROL VOLTAGE OUTPUTSTwelve identical individually programmable 12-bit DAC blocks are available to generate analog voltages, which canbe used to control bias conditions of external circuits, positionof servos, etc.In case simultaneous update of all outputs to the same levelis needed, a single internal register is provided that effectssimultaneous update of all DAC data registers.A DAC, by definition, produces an output in the range of GNDto DREF. In some systems, however, it may be desirable forthe OUT pins to produce either GND or VDD, i.e., beyondDREF. This is made possible via the asynchronous DAC con-trol inputs C[4:1]. When activated, these inputs will force theOUT pins to either rail. The choice of rail is made in the inter-nal control register.6.3 INTERNAL ANALOG TEMPERATURE SENSORAn on-board analog temperature sensor is available to mon-itor the device’s own temperature. Once enabled, the analogtemperature sensor output is sampled via the MUX channel17, and its conversion result is stored in the internal registerfor user read back.6.4 INTERNAL VOLTAGE REFERENCE SOURCEAnother resource available to the user is the internal, tem-perature-compensated reference voltage source. By defaultboth ADC and DACs expect reference potentials to be sup-plied externally. The user can choose to enable the internalreference and use it with the ADC and/or the DACs.The internal reference source cannot drive an external load.6.5 8-BIT GENERAL PURPOSE I/OThe GPIO port can be used to expand the microcontroller ca-pabilities. This port is memory mapped to the internal register,which in turn is accessible via the I2C-compatible interface.Since each bit is individually programmable as an Input orOutput, the port is ideally suited for external switch control andstatus flag monitoring, without further burdening of microcon-troller I/O resources.6.6 I2C-COMPATIBLE INTERFACEThe microcontroller supervisor communicates withLMP92001 via a popular I2C-compatible 2–wire interface.This interface provides the user full access to all Data, Statusand Control registers of the device.There are 2 address setting pins, AS[1:0], that allow the de-vice to occupy any one of 9 possible Interface Addresses onthe bus.Block Access commands are provided to minimize the trans-fer overhead of larger data sets.LMP920017.0 Connection Diagram30132708LLP-54 (SQA54AB)Top View 4L M P 920018.0 Pin DescriptionsNamePinESD StructuresFunctionVDD 14, 50Supply railGND 4, 13, 41, 45Device GroundIN15Analog Voltage Sense InputsIN26IN37IN48IN59IN610IN711IN812IN940IN1039IN1138IN1237IN1336IN1435IN1534IN1633OUT152Analog Control Voltage OutputsOUT253OUT354OUT41OUT52OUT63OUT748OUT847OUT946OUT1044OUT1143OUT1242SCL 23I 2C-compatible clock input SDA24Bidirectional I 2C-compatible data lineAS[0:1]31:32I 2C-compatible Interface Addressselection inputs.LMP92001Name Pin ESD Structures FunctionC[1:4]27:30Asynchronous DAC output controldigital inputs GPIO[0:7]15:22Digital I/O. CMOS Input or Open-DrainOutput INT[1:2]25:26Interrupt outputs. Open-Drain, activeLOWAREF49ADC referenceDREF 51DAC reference9.0 Ordering InformationOrder Number NS Package NumberTransport Media LMP92001SQE SQA54AB 250 piece reel LMP92001SQXSQA54AB2000 piece reel 6L M P 92001LMP92001Table of Contents1.0 General Description (1)2.0 Features (1)3.0 Applications (1)4.0 Block Diagram (1)5.0 Typical Application (2)6.0 Overview (3)6.1 17-CHANNEL ANALOG SENSE WITH 12-BIT ADC (3)6.2 PROGRAMMABLE ANALOG CONTROL VOLTAGE OUTPUTS (3)6.3 INTERNAL ANALOG TEMPERATURE SENSOR (3)6.4 INTERNAL VOLTAGE REFERENCE SOURCE (3)6.5 8-BIT GENERAL PURPOSE I/O (3)6.6 I2C-COMPATIBLE INTERFACE (3)7.0 Connection Diagram (4)8.0 Pin Descriptions (5)9.0 Ordering Information (6)10.0 Absolute Maximum Ratings (9)11.0 Operating Conditions (Note 1, Note 2) (9)12.0 Electrical Characteristics (9)13.0 I2C Interface Timing Diagram (12)14.0 Typical Performance Characteristics (13)15.0 Register Set (16)15.1 REGISTER MAP (16)15.2 TEST AND INFO REGISTERS (17)15.2.1 Test Register: TEST[7:0], default = 0x00 (17)15.2.2 Company ID Register: ID[7:0], default = 0x01 (17)15.2.3 Device Version Register: VER[7:0], default = 0x10 (17)15.3 STATUS REGISTERS (18)15.3.1 General Status Register: SGEN[7:0], default = 0x40 (18)15.3.2 GPIO Status Register: SGPI[7:0], default = 0x** (18)15.3.3 High-Limit Status Register: SHIL[7:0], default = 0x00 (18)15.3.4 Low-Limit Status Register: SLOL[7:0], default = 0x00 (18)15.4 CONTROL REGISTERS (19)15.4.1 General Configuration Register: CGEN[7:0], default = 0x00 (19)15.4.2 DAC Configuration Register: CDAC[7:0], default 0x03 (19)15.4.3 GPIO Output Control Register: CGPO[7:0], default = 0xFF (19)15.4.4 INT1, INT2 High-Limit Control Register: CINH[7:0], default = 0x00 (19)15.4.5 INT1, INT2 Low-Limit Control Register: CINL[7:0], default = 0x00 (19)15.4.6 ADC Conversion Enable Register 1: CAD1[7:0], default = 0x00 (19)15.4.7 ADC Conversion Enable Register 2: CAD2[7:0], default = 0x00 (19)15.4.8 ADC Conversion Enable Register 3: CAD3[7:0], default = 0x00 (19)15.4.9 ADC One-Shot Conversion Trigger Register : CTRIG[7:0], default = 0x00 (20)15.4.10 Reference Mode Register: CREF[7:0], default = 0x07 (20)15.5 DATA REGISTERS (20)15.5.1 ADC Output Data Register: ADCx[15:0], default 0x0000 (20)15.5.2 ADC High-Limit Register: LIHx[15:0], default 0x0FFF (20)15.5.3 ADC Low-Limit Register: LILx[15:0], default 0x0000 (20)15.5.4 DAC Data Register: DACx[15:0], default 0x0000 (20)15.5.5 Write all DAC's Data Register: DALL[15:0], default 0x0000 (20)15.6 BLOCK COMMANDS (21)16.0 Application Information (22)16.1 ANALOG SENSE SUBSYSTEM (22)16.1.1 Sampling and Conversion (22)16.1.2 Sampling Transient (22)16.1.3 Channel Selection (22)16.1.4 Single-Shot and Continuous Sequencing (22)16.1.5 Reference (24)16.1.6 Window Comparator Function (24)16.1.7 Interrupt Subsystem (25)16.2 PROGRAMMABLE ANALOG OUTPUT SUBSYSTEM (25)16.2.1 DAC Core (25)16.2.2 Reference (26)16.2.3 Asynchronous Output Control (26)16.3 TEMPERATURE SENSOR (27)16.4 ADC/DAC VOLTAGE REFERENCE (27)16.5 GENERAL PURPOSE I/O ..................................................................................................... 2816.6 SERIAL INTERFACE (28)16.6.1 I 2C-Compatible Protocol .............................................................................................. 2916.6.2 Device Address .......................................................................................................... 3016.6.3 Block Access ............................................................................................................. 3116.6.4 I 2C-Compatible Bus Reset . (31)17.0 Application Circuit Example ........................................................................................................... 3218.0 Physical Dimensions .. (33) 8L M P 9200110.0 Absolute Maximum Ratings (Note 1, Note 2)If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.VDD Relative to GND−0.3V to 6.0V Voltage between any 2 pins(Note 3) 6.0V Current in or out of any pin (Note 3)5mACurrent through VDD or GND78 mA, TA = 125°C120 mA, TA= 105°C Junction Temperature+150°C Storage Temperature Range−65°C to +150°C ESD Susceptibility(Note 4)Human Body Model Machine Model Charged Device Model 2500V250V1250VFor Soldering specifications:See product folder at and/ms/MS-SOLDERING.pdf.11.0 Operating Conditions (Note 1, Note2)Operating Ambient Temperature−40°C to 125°CVDD Voltage Range 4.5V to 5.5VDAC Output Load C0pF to 1500pFθJA24°C/WθJC2°C/W12.0 Electrical CharacteristicsUnless otherwise noted, these specifications apply for VDD=4.75V to 5.5V, AREF=DREF=VDD, TA=25°C. Boldface limits are over the temperature range of −40°C ≤ T A≤ 125°C unless otherwise noted. DAC input code range 48 to 4047. DAC output C L = 200 pF unless otherwise noted.Symbol Parameter Conditions Min Typ Max UnitsDAC CHARACTERISTICSResolution1212BitsMonotonicity12BitsDNL Differential Non-Linearity R L = 100k−0.60.6LSB INL Integral Non-Linearity R L = 100k−88ZE Zero Error R L = 100k15mVZEDRIFT Zero Error Temperature Drift R L = 100k 2.0µV/°CFSE Full-Scale Error R L = 100k0−0.75%FS GE Gain Error R L = 100k0−1GEDRIFT Gain Error Temperature Drift R L = 100k11.0ppm/° CZCO Zero Code Output IOUT= 200 µA7mV IOUT= 1mA31FSO Full Scale Output at code 4095VDD = DREF = 5V, I OUT = 1mA 4.988 4.995VDD VI OS Output Short Circuit Current(Source) (Note 5)VDD = 5V, OUT = 0V,Input Code = FFFhCDAC.OFF=0C[4:1]=HIGH−60mAI OS Output Short Circuit Current(Sink) (Note 5)VDD = 5V, OUT = DREF,Input Code = 000hCDAC.OFF=0C[4:1]=HIGH70I O Continuous Output Current perChannel (to prevent damage)TA= 105° C10TA= 125° C 6.5C L Load Capacitance RL= 2k or ∞1500pFDC Output Impedance8ΩOUT[1:12] Output Voltage whenAsynchronous Output Control isactivatedRL= 100k, C[1:4] = GND,CDAC.OLVL = 14.992VDD VC[1:4] = GND, CDAC.OLVL = 0GND0.6mVLMP92001Symbol ParameterConditionsMin Typ Max UnitsADC CHARACTERISTICSResolution with No Missing Codes11 Bits−40°C ≤ T A ≤ 105°C12 TUE Total Unadjusted Error−0.1 0.1%DNL Differential Non-Linearity −40°C ≤ T A ≤ 105°C−0.99 1LSB −1.2 1INL Integral Non-Linearity ±0.6 OE Offset Error−2.3 2.3OEDRIFT Offset Error Temperature Drift 0.005 LSB/°C OEMTCH Offset Error Match −1.5 1.5LSB GE Gain Error−2 2GEDRIFT Gain Error Temperature Drift −0.002 LSB/°C GEMTCH Gain Error Match −1.5 1.5LSB SNR Signal-to-Noise Ratio72 dB PSRR Power Supply Rejection Ratio Offset Error change with VDD 77 dB Gain Error change with VDD73 V IN FS Input RangeAREF I INA Input Current In Hold or inactive±1µA C INAInput CapacitanceIn Track 33 pF In Hold or inactive3 pF REFERENCE CHARACTERISTICSAREF Reference Input Range CREF.AEXT = 1 2.7 VDD V DREF Reference Input Range CREF.DEXT = 1 2.5 VDD V DREF Reference Input Resistance 10 k Ω DREF Input Current DREF = 5V,CREF.DEXT = 1 660µA AREF Peak Current AREF = 5V CREF.DEXT = 12.3 mA AREF and DREF Reference Current in Powerdown1µA Internally Generated Reference Voltage4.47 4.5 4.53VAREF, DREF Output Impedance when Internal Reference Active CREF.AEXT = 0CREF.DEXT = 05ΩTEMPERATURE SENSORSensor Gain−13.45 mV/°CTemperature Error−25°C to +85°C −2 2°C−45°C to +125°C−2.5 2.5DIGITAL INPUT CHARACTERISTICS (AS1:AS0)V IH Input HIGH Voltage 0.90x VDD V V IM Input MID Voltage 0.43 x VDD0.57 x VDD V IL Input LOW Voltage 0.1 x VDDV I IND Digital Input Current ±0.005±1µA C IND Input Capacitance 4 pF DIGITAL INPUT CHARACTERISTICS (GPIO0:GPIO7, C1:C4)V IH Input HIGH Voltage 0.7 x VDDV V IL Input LOW Voltage 0.3 x VDDVHysteresis0.47V 10L M P 92001分销商库存信息:NATIONAL-SEMICONDUCTORLMP92001SQE/NOPB LMP92001SQX/NOPB LMP92001EVAL/NOPB。

LF356NNOPB,LF356M,LF356H,LF156H,LF256H,LF356MX, 规格书,Datasheet 资料

capability

Applications

n Precision high speed integrators n Fast D/A and A/D converters n High impedance buffers n Wideband, low noise, low drift amplifiers

LF155/LF156/LF256/LF257/LF355/LF356/LF357 JFET Input Operational Amplifiers

December 2001

LF155/LF156/LF256/LF257/LF355/LF356/LF357

JFET Input Operational Amplifiers

1.5

12 5 12

LF257/ LF357 (AV=5)

1.5

50 20 12

Units µs

V/µs MHz

Simplified Schematic

*3pF in LF357 series.

BI-FET™, BI-FET II™ are trademarks of National Semiconductor Corporation.

300˚C

300˚C

Dual-In-Line Package

Soldering (10 sec.)

260˚C

260˚C

260˚C

Small Outline Package

Vapor Phase (60 sec.)

LM2452TBNOPB;中文规格书,Datasheet资料

LM2452LM2452 220V Monolithic Triple Channel 17 MHz DC Coupled CRT DTV DriverLiterature Number: SNOSAN8E20144501 FIGURE 1. Top ViewOrder Number LM2452TBSee NS Package Number TB15A20144502 FIGURE 2. Simplified Schematic Diagram(One Channel)© 2011 Texas Instruments 201445 Version 6 Revision 2Print Date/Time: 2011/11/02 10:28:56 2452 220V Monolithic Triple Channel 17 MHz DC Coupled CRT DTV Driver2201445 Version 6 Revision 2Print Date/Time: 2011/11/02 10:28:56L522014450310 pF load includes parasitic capacitance.FIGURE 3. Test Circuit (One Channel)Figure 3 shows a typical test circuit for evaluation of the LM2452. This circuit is designed to allow testing of the LM2452 in a environment without the use of an expensive FET probe. The two 4990Ω resistors form a 400:1 divider with the 50Ωand the oscilloscope. A test point is included for easy use of an oscilloscope probe. The compensation capacitor is used to com-pensate the network to achieve flat frequency response.201445 Version 6 Revision 2Print Date/Time: 2011/11/02 10:28:56C 20144504FIGURE 4. V OUT vs V IN20144505FIGURE 5. LM2452 Pulse Response 20144506FIGURE 6. Bandwidth 20144507FIGURE 7. Speed vs Load Capacitance20144508FIGURE 8. Speed vs Offset20144509FIGURE 9. Speed vs Case Temperature4201445 Version 6 Revision 2Print Date/Time: 2011/11/02 10:28:56LC20144510 FIGURE 10. Power Dissipation vs Frequency20144511 FIGURE 11. Safe Operating Area20144512FIGURE 12. LM2452 Cathode Response 201445 Version 6 Revision 2Print Date/Time: 2011/11/02 10:28:5652201445 FIGURE 13. One Channel of the LM2452 with the Recommended Application CircuitEFFECT OF LOAD CAPACITANCEFigure 7 shows the effect of increased load capacitance the speed of the device. This demonstrates the importance knowing the load capacitance in the application. Increasi the load capacitance from 10 pF to 20 pF adds about 9 ns the rise and fall times. It is very important to keep the boa capacitance as low as possible to maximize the speed of t driver.EFFECT OF OFFSETFigure 8 shows the variation in rise and fall times when tblack level of the device is varied from 180V to 200VDC . Trise time increases only about 2ns as the offset is increas6201445 Version 6 Revision 2Print Date/Time: 2011/11/02 10:28:56L52 This example assumes a capacitive load of 10 pF and no re-sistive load. If the maximum ambient temperature is 50°C,then the heat sink thermal resistance can increase to 3.3°C/W. The designer should note that if the load capacitance is201445 Version 6 Revision 2Print Date/Time: 2011/11/02 10:28:568201445 Version 6 Revision 2Print Date/Time: 2011/11/02 10:28:56L 201445 Version 6 Revision 2Print Date/Time: 2011/11/02 10:28:5652分销商库存信息: NATIONAL-SEMICONDUCTOR LM2452TB/NOPB。

LMK00101SQXNOPB;LMK00101SQNOPB;LMK00101SQENOPB;LMK00101BEVALNOPB;中文规格书,Datasheet资料

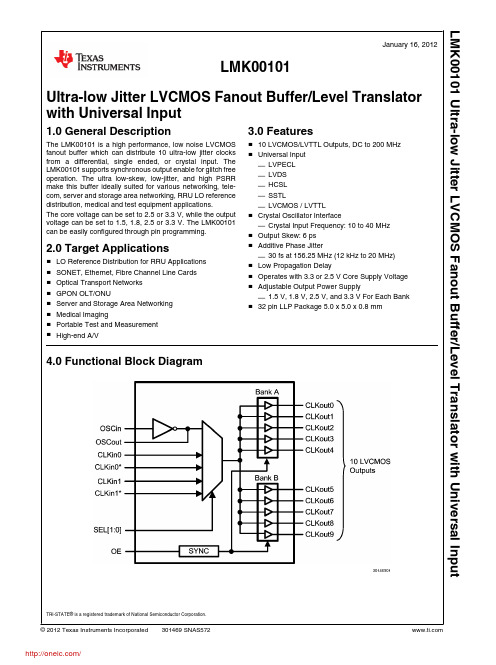

LMK00101January 16, 2012Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input1.0 General DescriptionThe LMK00101 is a high performance, low noise LVCMOS fanout buffer which can distribute 10 ultra-low jitter clocks from a differential, single ended, or crystal input. The LMK00101 supports synchronous output enable for glitch free operation. The ultra low-skew, low-jitter, and high PSRR make this buffer ideally suited for various networking, tele-com, server and storage area networking, RRU LO reference distribution, medical and test equipment applications.The core voltage can be set to 2.5 or 3.3 V, while the output voltage can be set to 1.5, 1.8, 2.5 or 3.3 V. The LMK00101 can be easily configured through pin programming.2.0 Target Applications■LO Reference Distribution for RRU Applications■SONET, Ethernet, Fibre Channel Line Cards■Optical Transport Networks■GPON OLT/ONU■Server and Storage Area Networking■Medical Imaging■Portable Test and Measurement■High-end A/V 3.0 Features■10 LVCMOS/LVTTL Outputs, DC to 200 MHz ■Universal Input—LVPECL—LVDS—HCSL—SSTL—LVCMOS / LVTTL■Crystal Oscillator Interface—Crystal Input Frequency: 10 to 40 MHz■Output Skew: 6 ps■Additive Phase Jitter—30 fs at 156.25 MHz (12 kHz to 20 MHz)■Low Propagation Delay■Operates with 3.3 or 2.5 V Core Supply Voltage ■Adjustable Output Power Supply—1.5 V, 1.8 V, 2.5 V, and 3.3 V For Each Bank ■32 pin LLP Package 5.0 x 5.0 x 0.8 mm4.0 Functional Block Diagram30146901TRI-STATE® is a registered trademark of National Semiconductor Corporation.© 2012 Texas Instruments Incorporated301469 LMK00101 Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input5.0 Connection Diagram32-Pin LLP Package301469026.0 Pin DescriptionsPin #Pin Name Type DescriptionDAP DAP -The DAP should be grounded1CLKout0Output LVCMOS Output2, 6Vddo Power Power Supply for Bank A (CLKout0 to CLKout4) CLKout pins.19,23Vddo Power Power Supply for Bank B (CLKout5 to CLKout9) CLKout pins.3CLKout1Output LVCMOS Output 4,9,15,16,21,25,26,32GND GND Ground5CLKout2Output LVCMOS Output 7CLKout3Output LVCMOS Output 8CLKout4Output LVCMOS Output10Vdd Power Supply for operating core and input buffer 11OSCin Input Input for Crystal 12OSCout Output Output for Crystal 13CLKin0Input Input Pin14CLKin0*Input Optional complimentary input pin 17CLKout5Output LVCMOS Output 18CLKout6Output LVCMOS Output 20CLKout7Output LVCMOS Output 22CLKout8Output LVCMOS Output 24CLKout9Output LVCMOS Output27CLKin1*Input Optional Complimentary Input Pin 28CLKin1Input Input Pin29SEL1Input MSB for Input Clock Selection. This pin has an internal pull-down resistor.30SEL0Input LSB for Input Clock Selection. This pin has an internal pull-down resistor.31OEInputOutput Enable. This pin has an internal pull-down resistor. 2L M K 00101 U l t r a -l o w J i t t e r L V C M O S F a n o u t B u f f e r /L e v e l T r a n s l a t o r w i t h U n i v e r s a l I n p u t7.0 Absolute Maximum Ratings (Note 1, Note 2)If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.Parameter Symbol Ratings Units Core Supply Voltage Vdd-0.3 to 3.6VOutput Supply Voltage Vddo-0.3 to 3.6V Input Voltage V IN-0.3 to Vdd + 0.3V Storage Temperature Range T STG-65 to 150°CLead Temperature (solder 4 s)T L+260°C Junction Temperature T J+125°C8.0 Recommended Operating ConditionsParameter Symbol Min Typ Max Units Ambient Temperature T A-402585°CCore Supply Voltage Vdd 2.375 3.3 3.45V Output Supply Voltage (Note 3)Vddo 1.425 3.3Vdd VNote 1:"Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions.Note 2:This device is a high performance integrated circuit with ESD handling precautions. Handling of this device should only be done at ESD protected work stations. The device is rated to a HBM-ESD of > 2.5 kV, a MM-ESD of > 250 V, and a CDM-ESD of > 1 kV.Note 3:Vddo should be less than or equal to Vdd(Vddo≤ Vdd)9.0 Package Thermal Resistance32-Lead LLPPackage Symbols Ratings UnitsThermal resistance from junction to ambienton 4-layer Jedec board (Note 4)θJA50° C/WThermal resistance from junction to case(Note 5)θJC (DAP)20° C/WNote 4:Specification assumes 5 thermal vias connect to die attach pad to the embedded copper plane on the 4-layer Jedec board. These vias play a key role in improving the thermal performance of the LLP. For best thermal dissipation it is recommended that the maximum number of vias be used on the board layout.Note 5:Case is defined as the DAP (die attach pad).LMK00101 Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input10.0 Electrical Characteristics(2.375 V ≤ Vdd ≤ 3.45 V, 1.425 ≤ Vddo ≤ Vdd, -40 °C ≤ T A ≤ 85 °C, Differential inputs. Typical values represent most likely parametric norms at Vdd = Vddo = 3.3 V, T A = 25 °C, at the Recommended Operation Conditions at the time of product charac-terization and are not guaranteed). Test conditions are: F test = 100 MHz, Load = 5 pF in parallel with 50 Ω unless otherwise stated.SymbolParameterTest ConditionsMinTypMaxUnitsTotal Device CharacteristicsVddCore Supply Voltage2.3752.5 or3.33.45VVddo Output Supply Voltage 1.425 1.5,1.8,2.5, or3.3Vdd VI VddCore CurrentNo CLKin1625mAV ddo = 3.3 V, F test = 100 MHz 24 V ddo = 2.5 V, F test = 100 MHz 20 I Vddo[n]Current for Each OutputV ddo = 2.5 V,OE = High, F test = 100 MHz5 mAV ddo = 3.3 V,OE = High, F test = 100 MHz7 OE = Low 0.1 I Vdd + I VddoTotal Device Current with Loads onall outputsOE = High @ 100 MHz95 mAOE = Low16Power Supply Ripple Rejection (PSRR)PSRRRipple Induced Phase Spur Level100 kHz, 100 mVpp Ripple Injected on V dd , V ddo = 2.5 V-44dBcOutputs (Note 6)Skew Output Skew Measured between outputs,referenced to CLKout06 ps f CLKoutOutput Frequency(Note 7)DC 200MHzt Rise Rise/Fall Time V dd = 3.3 V, V ddo = 1.8 V, C L = 10 pF500 psV dd = 2.5 V, V ddo = 2.5 V, C L = 10 pF 300 V dd = 3.3 V, V ddo = 3.3 V, C L = 10 pF200 V CLKout Low Output Low Voltage 0.1V V CLKout High Output High Voltage Vddo-0.1 R CLKoutOutput Resistance50 ohm t jRMS Additive Jitterf CLKout = 156.25 MHz,CMOS input slew rate ≥ 2 V/ns C L = 5 pF, BW = 12 kHz to 20 MHz30fs 4L M K 00101 U l t r a -l o w J i t t e r L V C M O S F a n o u t B u f f e r /L e v e l T r a n s l a t o r w i t h U n i v e r s a l I n p u tSymbol Parameter Test ConditionsMin Typ Max UnitsDigital Inputs (OE, SEL0, SEL1)V Low Input Low Voltage Vdd = 2.5 V 0.4VV High Input High Voltage Vdd = 2.5 V 1.3 Vdd = 3.3 V1.6 I IH High Level Input Current 50uAI IL Low Level Input Current -5 5CLKin0/0* and CLKin1/1* Input Clock Specifications, (Note 9, Note 10)I IH High Level Input Current V CLKin = Vdd 20uA I IL Low Level Input Current(Note 8)V CLKin = 0 V-20 uA V IH Input High Voltage Vdd VV ILInput Low VoltageGND V CMDifferential InputCommon Mode Input Voltage(Note 12)V ID = 150 mV0.5 Vdd-1.2VV ID = 350 mV 0.5 Vdd-1.1V ID = 800 mV0.5 Vdd-0.9V ID Differential Input Voltage Swing CLKin driven differentially 0.15 1.5V OSCin/OSCout Pinsf OSCinInput Frequency (Note 7)Single-Ended Input, OSCout floatingDC200MHzf XTALCrystal Frequency Input Range Fundamental Mode Crystal ESR < 200 Ω ( f Xtal ≤ 30 MHz )ESR < 120 Ω ( f Xtal > 30 MHz )(Note 11, Note 7)10 40MHzC OSCinShunt Capacitance1 pFNote 6:AC Parameters for CMOS are dependent upon output capacitive loading Note 7:Guaranteed by characterization.Note 8:V IL should not go below -0.3 volts.Note 9:See Section 12.1 Differential Voltage Measurement Terminology for definition of V ID and V OD .Note 10:Refer to application note AN-912 Common Data Transmission Parameters and their Definitions for more information.Note 11:The ESR requirements stated are what is necessary in order to ensure that the Oscillator circuitry has no start up issues. However, lower ESR values for the crystal might be necessary in order to stay below the maximum power dissipation requirements for that crystal.Note 12:When using differential signals with V CM outside of the acceptable range for the specified V ID , the clock must be AC coupled.LMK00101 Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input30146942Iddo per Output vs Frequency50100150200250051015C U R R E N T (m A )FREQUENCY (MHz)Cload = 10 pFVddo = 1.5 V Vddo = 1.8 V Vddo = 2.5 V Vddo = 3.3 V 30146976Note 13:Test conditions: LVCMOS Input, slew rate ≥ 2 V/ns, C L = 5 pF in parallel with 50 6L M K 00101 U l t r a -l o w J i t t e r L V C M O S F a n o u t B u f f e r /L e v e l T r a n s l a t o r w i t h U n i v e r s a l I n p u t12.0 Measurement Definitions12.1 Differential Voltage Measurement TerminologyThe differential voltage of a differential signal can be de-scribed by two different definitions causing confusion when reading datasheets or communicating with other engineers. This section will address the measurement and description of a differential signal so that the reader will be able to under-stand and discern between the two different definitions when used.The first definition used to describe a differential signal is the absolute value of the voltage potential between the inverting and non-inverting signal. The symbol for this first measure-ment is typically VID or VODdepending on if an input or outputvoltage is being described.The second definition used to describe a differential signal is to measure the potential of the non-inverting signal with re-spect to the inverting signal. The symbol for this second measurement is VSSand is a calculated parameter. Nowherein the IC does this signal exist with respect to ground, it onlyexists in reference to its differential pair. VSScan be measured directly by oscilloscopes with floating references, otherwisethis value can be calculated as twice the value of VODas de-scribed in the first sectionFigure 1 illustrates the two different definitions side-by-side for inputs and Figure 2 illustrates the two different definitionsside-by-side for outputs. The VIDand VODdefinitions showVAand VBDC levels that the non-inverting and inverting sig-nals toggle between with respect to ground. VSSinput and output definitions show that if the inverting signal is consid-ered the voltage potential reference, the non-inverting signal voltage potential is now increasing and decreasing above and below the non-inverting reference. Thus the peak-to-peak voltage of the differential signal can be measured.VIDand VODare often defined in volts (V) and VSSis oftendefined as volts peak-to-peak (VPP).30146912FIGURE 1. Two Different Definitions for Differential Input Signals30146913FIGURE 2. Two Different Definitions for Differential Output Signals LMK00101 Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input13.0 Functional DescriptionThe LMK00101 is a 10 output LVCMOS clock fanout buffer with low additive jitter that can operate up to 200 MHz. It fea-tures a 3:1 input multiplexer with a crystal oscillator input,single supply or dual supply (lower power) operation, and pin-programmable device configuration. The device is offered in a 32-pin LLP package.13.1 V dd and V ddo Power Supplies (Note 14, Note 15)Separate core and output supplies allow the output buffers to operate at the same supply as the Vdd core supply (3.3 V or 2.5 V) or from a lower supply voltage (3.3 V, 2.5 V, 1.8 V, or 1.5 V). Compared to single-supply operation, dual supply op-eration enables lower power consumption and output-level compatibility.Bank A (CLKout0 to CLKout4) and Bank B (CLKout5 to CLK-out9) may also be operated at different V ddo voltages, provid-ed neither V ddo voltage exceeds V dd .Note 14:Care should be taken to ensure the V ddo voltage does not exceed the Vdd voltage to prevent turning-on the internal ESD protection circuitry.Note 15:DO NOT DISCONNECT OR GROUND ANY OF THE V ddo PINS as the V ddo pins are internally connected within an output bank.13.2 CLOCK INPUTSThe LMK00101 has three different inputs, CLKin0/CLKin0*,CLKin1/CLKin1*, and OSCin that can be driven in different manners that are described in the following sections.13.2.1 SELECTION OF CLOCK INPUTClock input selection is controlled using the SEL0 and SEL1pins as shown in Table 1. Refer to Section 14.1 Driving the Clock Inputs for clock input requirements. When CLKin0 or CLKin1 is selected, the crystal circuit is powered down. When OSCin is selected, the crystal oscillator will start-up and its clock will be distributed to all outputs. Refer to Section 14.2Crystal Interface for more information. Alternatively, OSCin may be driven by a single ended clock, up to 200 MHz, instead of a crystal.TABLE 1. Input SelectionSEL1SEL0Input 00CLKin0, CLKin0*01CLKin1, CLKin1*1XOSCin (Crystal Mode)13.2.1.1 CLKin/CLKin* PinsThe LMK00101 has two differential inputs (CLKin0/CLKin0*and CLKin1/CLKin1*) that can be driven single-ended or dif-ferentially. They can accept AC or DC coupled 3.3V/2.5V LVPECL, LVDS, or other differential and singled ended sig-nals that meet the input requirements under the “CLKin0/0*and CLKin1/1* Input Clock Specifications” portion of the Sec-tion 10.0 El ectrical Characteristics and (Note 12). Refer to Section 14.1 Driving the Clock Inputs for more details on driv-ing the LMK00101 inputs.In the event that a Crystal mode is not selected and the CLKin pins do not have an AC signal applied to them, Table 2 fol-lowing will be the state of the outputs.TABLE 2. CLKinX Input vs. Output States CLKinX CLKinX*Output State Open Open Logic Low Logic Low Logic Low Logic Low Logic High Logic Low Logic High Logic LowLogic HighLogic Low13.3 CLOCK OUTPUTSThe LMK00101 has 10 LVCMOS outputs.13.3.1 Output Enable PinWhen the output enable pin is held High, the outputs are en-abled. When it is held Low, the outputs are held in a Low state as shown in Table 3.TABLE 3. Output Enable Pin StatesOE Outputs Low Disabled (Hi-Z)HighEnabledThe OE pin is synchronized to the input clock to ensure that there are no runt pulses. When OE is changed from Low to High, the outputs will initially have an impedance of about 400 Ω to ground until the second falling edge of the input clock. Starting with the second falling edge of the input clock,the outputs will buffer the input. If the OE pin is taken from Low to High when there is no input clock present, the outputs will either go High or Low and stay a that state; they will not oscillate. When the OE pin is taken from High to Low the out-puts will become Low after the second falling edge of the clock input and then will go to a Disabled (Hi-Z) state starting after the next rising edge.13.3.2 Using Less than Ten OutputsAlthough the LMK00101 has 10 outputs, not all applications will require all of these. In this case, the unused outputs should be left floating with a minimum copper length (Note 16) to minimize capacitance. In this way, this output will con-sume minimal output current because it has no load.Note 16:For best soldering practices, the minimum trace length should extend to include the pin solder mask. This way during reflow, the solder has the same copper area as connected pins. This allows for good, uniform fillet solder joints helping to keep the IC level during reflow. 8L M K 00101 U l t r a -l o w J i t t e r L V C M O S F a n o u t B u f f e r /L e v e l T r a n s l a t o r w i t h U n i v e r s a l I n p u t14.0 Application Information14.1 Driving the Clock InputsThe LMK00101 has two differential inputs (CLKin0/CLKin0*and CLKin1/CLKin1*) that can accept AC or DC coupled 3.3V/2.5V LVPECL, LVDS, and other differential and single ended signals that meet the input requirements specified in Sec-tion 10.0 Electrical Characteristics . The device can accept a wide range of signals due to its wide input common mode voltage range (V CM ) and input voltage swing (V ID )/dynamic range. AC coupling may also be employed to shift the input signal to within the V CM range.To achieve the best possible phase noise and jitter perfor-mance, it is mandatory for the input to have a high slew rate of 2 V/ns (differential) or higher. Driving the input with a lower slew rate will degrade the noise floor and jitter. For this rea-son, a differential input signal is recommended over single-ended because it typically provides higher slew rate and common-mode noise rejection.While it is recommended to drive CLKin0 and CLKin1 with a differential signal input, it is possible to drive them with a sin-gle ended clock. The single-ended input slew rate should be as high as possible to minimize performance degradation.The CLKinX input has an internal bias voltage of about 1.4 V,so the input can be AC coupled as shown in Figure 3, Figure 4, or Figure 5 depending upon the application.30146938FIGURE 3. Single-Ended LVCMOS Input, AC Coupling,Near and Far End Termination30146943FIGURE 4. Single-Ended LVCMOS Input, AC Coupling,Near End Termination30146944FIGURE 5. Single-Ended LVCMOS Input, AC Coupling,Far End Termination A single ended clock may also be DC coupled to CLKinX as shown in Figure 6. If the DC coupled input swing has a com-mon mode level near the devices internal bias of 1.4 V, then only a 0.1 µF bypass cap is required on CLKinX*. Otherwise,if the input swing is not optimally centered near the internal bias voltage, then CLKinX* should be externally biased to the midpoint voltage of the input swing. This can be achieved us-ing external biasing resistors, R B1 and R B2, or another low-noise voltage reference. The external bias voltage should be within the specified input common voltage (VCM) range. This will ensure the input swing crosses the threshold voltage at a point where the input slew rate is the highest.30146939FIGURE 6. Single-Ended LVCMOS Input, DC Couplingwith Common Mode Biasing If the crystal oscillator circuit is not used, it is possible to drive the OSCin input with an single-ended external clock as shown in Figure 7. Configurations similar to Figure 4 or Figure 5 could also be used as long as the OSCout pin is left floating. The input clock should be AC coupled to the OSCin pin, which has an internally generated input bias voltage, and the OSCout pin should be left floating. While OSCin provides an alterna-tive input to multiplex an external clock, it is recommended to use either differential input (CLKinX) since it offers higher op-erating frequency, better common mode, improved power supply noise rejection, and greater performance over supply voltage and temperature variations.LMK00101 Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input30146903FIGURE 7. Driving OSCin with a Single-Ended ExternalClock 14.2 Crystal InterfaceThe LMK00101 has an integrated crystal oscillator circuit that supports a fundamental mode, AT-cut crystal. The crystal in-terface is shown in Figure 8.30146904FIGURE 8. Crystal InterfaceThe load capacitance (C L ) is specific to the crystal, but usually on the order of 18 to 20 pF. While C L is specified for the crys-tal, the OSCin input capacitance (C IN = 1 pF typical) of the device and PCB stray capacitance (C STRAY ~ 1 to 3 pF) can affect the discrete load capacitor values, C 1 and C 2. For the parallel resonant circuit, the discrete capacitor values can be calculated as follows:C L = (C 1 * C 2) / (C 1 + C 2) + C IN + C STRAY(1)Typically, C 1 = C 2 for optimum symmetry, so Equation 1 can be rewritten in terms of C 1only:C L = C 12 / (2 * C 1 ) + C IN + C STRAY(2)Finally, solve for C 1:C 1 = (C L - C IN - C STRAY ) * 2(3)Section 10.0 Electrical Characteristics provides crystal inter-face specifications with conditions that ensure start-up of the crystal, but it does not specify crystal power dissipation. The designer will need to ensure the crystal power dissipation does not exceed the maximum drive level specified by the crystal manufacturer. Overdriving the crystal can cause pre-mature aging, frequency shift, and eventual failure. Drive level should be held at a sufficient level necessary to start-up and maintain steady-state operation.The power dissipated in the crystal, P XTAL , can be computed by:P XTAL = I RMS 2 * R ESR * (1 + C 0 / C L )2(4)Where:•I RMS is the RMS current through the crystal.•R ESR is the maximum equivalent series resistance specified for the crystal.•C L is the load capacitance specified for the crystal.•C 0 is the minimum shunt capacitance specified for the crystal.I RMS can be measured using a current probe (e.g. Tektronix CT-6 or equivalent) placed on the leg of the crystal connected to OSCout with the oscillation circuit active.As shown in Figure 8, an external resistor, R LIM , can be used to limit the crystal drive level if necessary. If the power dissi-pated in the selected crystal is higher than the drive level specified for the crystal with R LIM shorted, then a larger resis-tor value is mandatory to avoid overdriving the crystal. How-ever, if the power dissipated in the crystal is less than the drive level with R LIM shorted, then a zero value for R LIM can be used.As a starting point, a suggested value for R LIM is 1.5 k Ω14.3 Power Supply Ripple RejectionIn practical system applications, power supply noise (ripple)can be generated from switching power supplies, digital ASICs or FPGAs, etc. While power supply bypassing will help filter out some of this noise, it is important to understand the effect of power supply ripple on the device performance.When a single-tone sinusoidal signal is applied to the power supply of a clock distribution device, such as LMK00101, it can produce narrow-band phase modulation as well as am-plitude modulation on the clock output (carrier). In the single-side band phase noise spectrum, the ripple-induced phase modulation appears as a phase spur level relative to the car-rier (measured in dBc).For the LMK00101, power supply ripple rejection (PSRR),was measured as the single-sideband phase spur level (in dBc) modulated onto the clock output when a ripple signal was injected onto the V ddo supply. The PSRR test setup is shown in Figure 9.30146940FIGURE 9. PSRR Test SetupA signal generator was used to inject a sinusoidal signal onto the V ddo supply of the DUT board, and the peak-to-peak ripple amplitude was measured at the V ddo pins of the device. A lim-iting amplifier was used to remove amplitude modulation on the differential output clock and convert it to a single-ended signal for the phase noise analyzer. The phase spur level measurements were taken for clock frequencies of 100 MHz under the following power supply ripple conditions:•Ripple amplitude: 100 mVpp on V ddo = 2.5 V •Ripple frequency: 100 kHzAssuming no amplitude modulation effects and small index modulation, the peak-to-peak deterministic jitter (DJ) can be calculated using the measured single-sideband phase spur level (PSRR) as follows:10L M K 00101 U l t r a -l o w J i t t e r L V C M O S F a n o u t B u f f e r /L e v e l T r a n s l a t o r w i t h U n i v e r s a l I n p u t分销商库存信息:NATIONAL-SEMICONDUCTORLMK00101SQX/NOPB LMK00101SQ/NOPB LMK00101SQE/NOPB LMK00101BEVAL/NOPB。

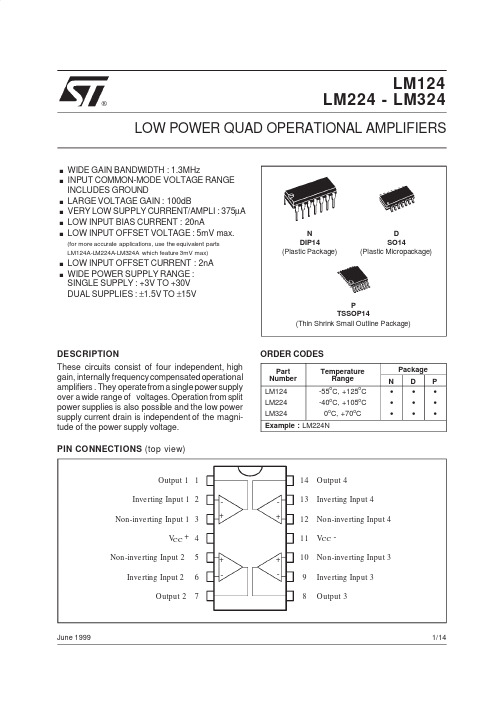

LM224中文资料_数据手册_参数

Parameter Supply Voltage

Input Voltage

Differential Input Voltage - (*)

Power Dissipation

N Suffix D Suffix

Output Short-circuit Duration - (note 1)

Supply Voltage Rejection (VCCT+am=b5=V+t2o53o0CV)

Ratio

(RS

≤

10kΩ)

Tmin. ≤ Tamb ≤ Tmax.

Supply Current, all Amp, no load

Tamb = +25oC

VCC = +5V

VCC = +30V

Tmin. ≤ Tamb ≤ Tmax.

(VCCTa=mb+5=V+,2R5LoC= 2kΩ)

Tmin. ≤ Tamb ≤ Tmax.

RL = 2kΩ RL = 10kΩ

Low Level Tamb =

Output +25oC

Voltage

(RL

=

10kΩ)

Tmin. ≤ Tamb ≤ Tmax.

Slew Rate VCC = 15V, VI = 0.5 to 3V, RL = 2kΩ, CL = 100pF, unity gain)

Input Offset Current Drift

Channel Separation (note 5) 1kHz ≤ f ≤ 20kHz

MHz

1.3 %

0.015

nV

40

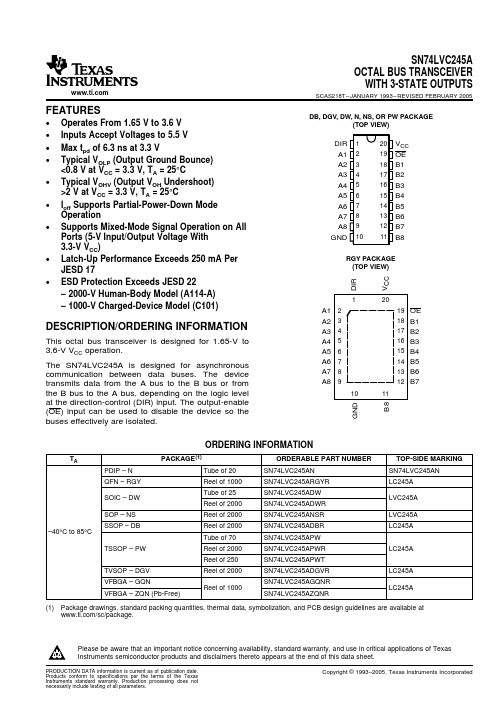

LC245A中文资料

GQN OR ZQN PACKAGE (TOP VIEW)

1234

A B C D E

TERMINAL ASSIGNMENTS

1

2

3

4

A

A1

DIR

VCC

OE

B

A3

B2

A2

B1

C

A5

A4

B4

B3

D

A7

B6

A6

B5

E

GND

A8

B8

B7

FUNCTION TABLE

INPUTS

OE DIR

L

L

L

H

H

X

OPERATION

QFN – RGY

Reel of 1000

SN74LVC245ARGYR

SOIC – DW

Tube of 25 Reel of 2000

SN74LVC245ADW SN74LVC245ADWR

SOP – NS

Reel of 2000

SN74LVC245ANSR

SSOP – DB

Reel of 2000

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

DIR 1 A1 2 A2 3 A3 4 A4 5 A5 6 A6 7 A7 8 A8 9 GND 10

LMX2354TMNOPB;LMX2354SLBXNOPB;LMX2354TMXNOPB;中文规格书,Datasheet资料

LMX2354LMX2354 PLLatinum Fractional N RF/ Integer N IF Dual Low Power Frequency Synthesizer LMX2354 2.5 GHz/550 MHzLiterature Number: SNAS118BLMX2354PLLatinum Fractional N RF/Integer N IF Dual Low Power Frequency Synthesizer LMX23542.5GHz/550MHzGeneral DescriptionThe LMX2354is part of a family of monolithic integrated fractional N/Integer N frequency synthesizers designed to be used in a local oscillator subsystem for a radio transceiver.It is fabricated using National’s 0.5µABiC V silicon BiCMOS process.The LMX2354contains quadruple modulus pres-calers along with modulo 15or 16fractional compensation circuitry in the RF divider.The LMX2354provides a continu-ous divide ratio of 80to 32767in 16/17/20/21(1.2GHz–2.5GHz)fractional mode and 40to 16383in 8/9/12/13(550MHz–1.2GHz)fractional mode.The IF cir-cuitry for the LMX2354contains an 8/9prescaler,and is fully ing a fractional N phase locked loop tech-nique,the LMX2354can generate very stable low noise control signals for UHF and VHF voltage controlled oscilla-tors (VCOs).For the RF PLL,a highly flexible 16level programmable charge pump supplies output current magnitudes from 100µA to 1.6mA.Two uncommitted CMOS outputs can be used to provide external control signals,or configured to FastLock mode.Serial data is transferred into the LMX2354via a three wire interface (Data,LE,Clock).Supply voltage can range from 2.7V to 5.5V.The LMX2354family features very low current consumption;typically LMX2354(2.5GHz)—7.0mA.The LMX2354are available in a 24-pin TSSOP surface mount plastic package and 24-pin CSP .Featuresn Pin compatible/functional equivalent to the LMX2350n Enhanced Low Noise Fractional Engine n 2.7V to 5.5V operation n Low current consumptionLMX2354:I CC =7mA typical at 3Vn Programmable or logical power down mode:I CC =5µA typical at 3Vn Modulo 15or 16fractional RF N divider supports ratios of 1,2,3,4,5,8,15,or 16nProgrammable charge pump current levels RF 100µA to 1.6mA in 100µA steps IF 100µA or 800µAn Digital filtered lock detectnAvailable in 24-pin TSSOP and 24-pin CSPApplicationsn Portable wireless communications (PCS/PCN,cordless)n Dual mode cellular telephone systems n Zero blind slot TDMA systemsn Spread spectrum communication systems (CDMA)nCable TV Tuners (CATV)Functional Block Diagram20004801©2001National Semiconductor Corporation 20004802Order Number LMX2354TM or LMX2355TMSee NS Package Number MTC2420004822Order Number LMX2354SLB or LMX2355SLBSee NS Package Number SLBL 2Pin No.for TSSOP Package Pin No.forCSPPackagePinName I/O Description124OUT0O Programmable CMOS output.Level of the output is controlled by IF_N[17]bit. 21V CCRF—RF PLL power supply voltage input.Must be equal to Vcc IF.May range from2.7V to5.5V.Bypass capacitors should be placed as close as possible to thispin and be connected directly to the ground plane.32V PRF —Power supply for RF charge pump.Must be≥V CCRFand V CCIF.43CP oRFO RF charge pump output.Connected to a loop filter for driving the control inputof an external VCO.54GND—Ground for RF PLL digital circuitry.65fin RF I RF prescaler input.Small signal input from the VCO.76fin RF I RF prescaler complimentary input.A bypass capacitor should be placed asclose as possible to this pin and be connected directly to the ground plane.87GND—Ground for RF PLL analog circuitry.98OSC RF I Dual mode oscillator output or RF R counter input.Has a V CC/2input thresholdwhen configured as an input and can be driven from an external CMOS or TTLlogic gate.109OSC IF I Oscillator input which can be configured to drive both the IF and RF R counterinputs or only the IF R counter depending on the state of the OSCprogramming bit.(See functional description1.1and programming description3.1.)1110Fo/LD O Multiplexed output of N or R divider and RF/IF lock detect.CMOS output.(Seeprogramming description3.1.5.)1211RF_EN I RF PLL Enable.Powers down RF N and R counters,prescaler,andTRI-STATE®charge pump output when LOW.Bringing RF_EN high powers upRF PLL depending on the state of RF_CTL_WORD.(See functional description1.9.)1312IF_EN I IF PLL Enable.Powers down IF N and R counters,prescaler,and TRI-STATEcharge pump output when LOW.Bringing IF_EN high powers up IF PLLdepending on the state of IF_CTL_WORD.(See functional description1.9.) 1413CLOCK I High impedance CMOS Clock input.Data for the various counters is clockedinto the24-bit shift register on the rising edge.1514DATA I Binary serial data input.Data entered MSB first.The last two bits are thecontrol bits.High impedance CMOS input.1615LE I Load Enable high impedance CMOS input.Data stored in the shift registers isloaded into one of the4internal latches when LE goes HIGH.(See functionaldescription1.7.)1716GND—Ground for IF analog circuitry.1817fin IF I IF prescaler complimentary input.A bypass capacitor should be placed asclose as possible to this pin and be connected directly to the ground plane. 1918fin IF I IF prescaler input.Small signal input from the VCO.2019GND—Ground for IF digital circuitry.2120CPo IF O IF charge pump output.For connection to a loop filter for driving the input of anexternal VCO.2221V PIF—Power supply for IF charge pump.Must be≥V CCRF and V CCIF.2322V CCIF —IF power supply voltage input.Must be equal to V CCRF.Input may range from2.7V to5.5V.Bypass capacitors should be placed as close as possible to thispin and be connected directly to the ground plane.2423OUT1O Programmable CMOS output.Level of the output is controlled by IF_N[18]bit.3Parameter SymbolValueU Min Typ MaxPower Supply Voltage V CCRF−0.3 6.5V CCIF−0.3 6.5Vp RF−0.3 6.5Vp IF−0.3 6.5 Voltage on any pin with GND=0V Vi−0.3V CC+0.3 Storage Temperature Range Ts−65+150 Lead Temperature(Solder4sec.)T L+260 Recommended Operating ConditionsParameter SymbolValueUn Min Typ MaxPower Supply Voltage V CCRF2.7 5.5V CCIF V CCRFV CCRFV pRF V CC 5.5V pIF V CC 5.5Operating Temperature T A−40+85˚Note1:“Absolute Maximum Ratings”indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the intended to be functional,but do not guarantee specific performance limits.For guaranteed specifications and test conditions,see the Electrical Characteris guaranteed specifications apply only for the test conditions listed.Note2:This Device is a high performance RF integrated circuit with an ESD rating<2kV and is ESD sensitive.Handling and assembly of this device sho be done at ESD-free workstations.Electrical Characteristics(Vcc RF =V ccIF=V PRF=V PIF=3.0V;−40˚C<T A<+85˚C except as specified)All min/max specifications are guaranteed by design,or test,or statistical methods.Symbol Parameter ConditionsValueMin Typ MaxGENERALI CC Power Supply Current RF and IF 6.08.5IF Only 1.1 2.0 I CC-PWDN Power Down Current RF_EN=IF_EN=LOW2050 f in RF RF Operating Frequency0.5 2.5 f in IF IF Operating Frequency10550 f OSC Oscillator Frequency No load on OSC RF250 fφPhase Detector Frequency RF and IF10 Pf in RF RF Input Sensitivity V CC=3.0V−150V CC=5.0V−100 Pf in IF IF Input Sensitivity 2.7V≤V CC≤5.5V−100 V OSC Oscillator Sensitivity OSC IF,OSC RF0.5V CC CHARGE PUMPICPo-source RF RF Charge Pump OutputCurrent(see ProgrammingDescription3.2.2)VCPo Vp/2,RF_CP_WORD=0000−100ICPo-sink RF VCPo=Vp/2,RF_CP_WORD=0000100 ICPo-source RF VCPo=Vp/2,RF_CP_WORD=1111−1.6ICPo-sink RF VCPo=Vp/2,RF_CP_WORD=11111.6L4Symbol Parameter ConditionsValueUnits Min Typ MaxICPo-source IF IF Charge Pump OutputCurrent(see ProgrammingDescription3.1.4)VCPo=Vp/2,CP_GAIN_8=0−100µAICPo-sink IF VCPo=Vp/2,CP_GAIN_8=0100µA ICPo-source IF VCPo=Vp/2,CP_GAIN_8=1−800µA ICPo-sink IF VCPo=Vp/2,CP_GAIN_8=1800µAICPo-Tri Charge Pump TRI-STATECurrent 0.5≤VCPo≤Vp−0.5−40˚C<T A<+85˚C−2.5 2.5nARF ICPo-sink vs.ICPo-source RF CP Sink vs.SourceMismatchVCPo=Vp/2T A=25˚CRF ICPo=900µA−1.6mA3.510%ICPo vs.VCPo CP Current vs.VoltageVariation 0.5≤VCPo≤Vp−0.5T A=25˚C RF ICPo510%ICPo vs.T CP Current vsTemperature VCPo=Vp/2−40˚C<T A<+85˚C RF ICPo8%V CP Charge Pump OutputVoltage(RF only)2.7V≤V CC≤3.3V,DoublerEnabled2*V CC−0.5VDIGITAL INTERFACE(DATA,CLK,LE,EN,FoLD)V IH High-level Input Voltage(Note3)0.8V CC V V IL Low-level Input Voltage(Note3)0.2V CC V I IL Low-level Input Current V IL=0,V CC=5.5V,(Note3)−1.0 1.0µA I IH High-level Input Current V IH=V CC=5.5V,(Note3)−1.0 1.0µA I IH Oscillator Input Current V IH=V CC=5.5V100µA I IL Oscillator Input Current V IL=0,V CC=5.5V−100µA V OH High-level Output Voltage I OH=−500µA V CC−0.4V V OL High-level Output Voltage I OL=500µA0.4V MICROWIRE TIMINGt CS Data to Clock Setup Time See Data Input Timing50ns t CH Data to Clock Hold Time See Data Input Timing10ns t CWH Clock Pulse Width High See Data Input Timing50ns t CWL Clock Pulse Width Low See Data Input Timing50nst ES Clock to Load Enable SetUp Time See Data Input Timing50nst EW Load Enable Pulse Width See Data Input Timing50nsNote3:except f IN,OSC IF and OSC RF520004823 I1=CP sink current at V Do=Vp−∆VI2=CP sink current at V Do=Vp/2I3=CP sink current at V Do=∆VI4=CP source current at V Do=Vp−∆VI5=CP source current at V Do=Vp/2I6=CP source current at V Do=∆V∆V=Voltage offset from positive and negative rails.Dependent on VCO tuning range relative to V CC and ground.Typical values are between0.5V and Note4:I Do vs V Do=Charge Pump Output Current magnitude variation vs Voltage=[1⁄2*{||1|−||3|}]/[1⁄2*{||1|+||3|}]*100%and[1⁄2*{||4|−||6|}]/[1⁄2 ||6|}]*100%Note5:I Do-sink vs I Do-source=Charge Pump Output Current Sink vs Source Mismatch=[||2|−||5|]/[1⁄2*{||2|+||5|}]*100%Note6:I Do vs T A=Charge Pump Output Current magnitude variation vs Temperature=[||2@temp|−||2@25˚C|]/||2@25˚C|*100%and[||5@temp 25˚C|]/||5@25˚C|*100%620004824Note:N =10,000R =50P =16Note:Sensitivity limit is reached when the error of the divided RF output,F o LD,is ≥1Hz.Typical Performance CharacteristicsI CC vs V CC LMX2354I CPO TRI-STATE vsCP O Voltage2000482520004827Charge Pump Current vs CP O Voltage RF_CP_WORD =0000and 0111IF CP_GAIN_8=0and 1Charge Pump Current vs CP O Voltage RF_CP_WORD =0011and 111120004828200048297Sink vs Source Mismatch(See (Note 6)under Charge Pump CurrentSpecification Definitions)RF Input ImpedanceV CC =2.7V to 5.5V,f IN =550MHz to 2.5GHz (f IN Capacitor =100pF)20004830IF Input ImpedanceV CC =2.7V to 5.5V,f IN =50MHz to 550MHz (f IN Capacitor =100pF)LMX2354RF Sensitivity vs Frequency20004832200L 8IF Input Sensitivity vs Frequency Oscillator Input Sensitivity vs Frequency20004836200048359分销商库存信息:NATIONAL-SEMICONDUCTORLMX2354TM/NOPB LMX2354SLBX/NOPB LMX2354TMX/NOPB。

LM3551SDNOPB;LM3552SDNOPB;LM3551SDXNOPB;LM3552SDXNOPB;中文规格书,Datasheet资料

Electrical Characteristics (Note 2, Note 9)

Limits in standard typeface are for TJ = +25° C. Limits in boldface type apply over the full operating junction temperature range

Typical Application Circuits

© 2011 National Semiconductor Corporation 201512

/

20151205

LM3551/L

Connection Diagram

14 Pin Dual LLP Package

VIN pin: Voltage to GND SW pin: Voltage to GND FB pin: Voltage to GND VC pin: Voltage to GND SD,T/F pins: Voltage to GND FET-T, FET-F: Voltage to GND Continuous Power Dissipation (Note 3) Junction Temperature (TJ-MAX ) Storage Temperature Range Maximum Lead Temperature (Soldering) ESD Rating(Note 5) Human Body Model

7.5V 21V

LMZ10501SEXNOPB;LMZ10501SENOPB;LMZ10501SEENOPB;LMZ10501EVALNOPB;中文规格书,Datasheet资料

LMZ10501 1A SIMPLE SWITCHER® Nano Module with 5.5V Maximum Input Voltage

Literature Number: SNVS677B

/

SIMPLE SWITCHER® Nano Module with 5.5V Maximum Input Voltage

Key Features

■ Integrated inductor ■ Miniature form factor (3.0 mm x 2.5 mm x 1.2 mm) ■ 8-pin LLP footprint ■ -40°C to 125°C junction temperature range ■ Adjustable output voltage ■ 2.0MHz fixed PWM switching frequency ■ Integrated compensation ■ Soft start function ■ Current limit protection ■ Thermal shutdown protection ■ Input voltage UVLO for power-up, power-down, and

Supplied As 250 units, Tape-and-Reel 1000 units, Tape-and-Reel 3000 units, Tape-and-Reel

Note: The actual physical placement of the package marking will vary from part to part. The package marking “X” designates the date code. “V” is a NSC inter code for die traceability. Both will vary in production. “S” designates device type as switcher and “SP” identifies the device (part number).

LMX2310USLDXNOPB;LMX2311USLDXNOPB;LMX2312USLDXNOPB;LMX2313USLDXNOPB;中文规格书,Datasheet资料

LMX2310U/LMX2311U/LMX2312U/LMX2313U PLLatinum Ultra Low Power Frequency Synthesizerfor RF Personal Communications LMX2310U - 2.5 GHz, LMX2311U 2.0 GHz,LMX2312U - 1.2 GHz, LMX2313U - 600 MHz

14 15

GND CE

— Digital ground. I High impedance CMOS Chip Enable input. Provides logical power-down control of the device. Pull-up to VµC if unused. The Chip Enable is internally referenced to VµC.

Features

■ ■ ■ ■ ■ ■ ■ ■ ■ ■ ■

RF operation up to 2.5 GHz 2.7V to 5.5V operation Ultra Low Current Consumption Low prescaler values LMX2310/1/2U 32/33 or 16/17 LMX2313U 16/17 or 8/9 Excellent Phase Noise Internal balanced, low leakage charge pump Selectable Charge Pump Current Levels Selectable Fastlock mode with Time-Out Counter Low Voltage MICROWIRE interface (1.72V to VCC) Digital and Analog Lock Detect Small 20-pad Thin Chip Scale Package

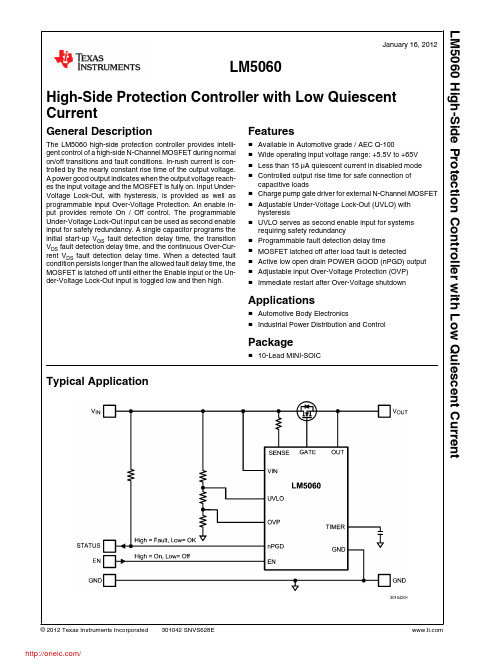

LM5060Q1MMNOPB;LM5060MMXNOPB;LM5060MMNOPB;LM5060Q1MMXNOPB;中文规格书,Datasheet资料

Features

■ Available in Automotive grade / AEC Q-100 ■ Wide operating input voltage range: +5.5V to +65V ■ Less than 15 µA quiescent current in disabled mode ■ Controlled output rise time for safe connection of

capacitor close to this pin is recommended to suppress noise.

Over-Voltage

An external resistor divider from the system input voltage sets the Over-Voltage turn-off threshold. The GATE pin is pulled low when OVP exceeds the typical 2.0V threshold, but the

The operating voltage range is 5.5V to 65V. The internal power-on-reset (POR) circuit typically 2 VIN Supply Voltage Input switches to the active state when the VIN pin is greater than 5.1V. A small ceramic bypass

The LM5060 high-side protection controller provides intelligent control of a high-side N-Channel MOSFET during normal on/off transitions and fault conditions. In-rush current is controlled by the nearly constant rise time of the output voltage. A power good output indicates when the output voltage reaches the input voltage and the MOSFET is fully on. Input UnderVoltage Lock-Out, with hysteresis, is provided as well as programmable input Over-Voltage Protection. An enable input provides remote On / Off control. The programmable Under-Voltage Lock-Out input can be used as second enable input for safety redundancy. A single capacitor programs the initial start-up VGS fault detection delay time, the transition VDS fault detection delay time, and the continuous Over-Current VDS fault detection delay time. When a detected fault condition persists longer than the allowed fault delay time, the MOSFET is latched off until either the Enable input or the Under-Voltage Lock-Out input is toggled low and then high.

LMV324中文资料

1 2 3 4

+

8 7

+

+Vs Out2 -In2 +In2

Out1 -In1 +In1 -Vs

1 2 3 4

+

8 7

+

+Vs Out2 -In2 +In2

6 5

6 5

LMV324

TSSOP-14 SOIC-14

Out1 -In1 +In1 +Vs +In2 -In2 Out2

1 2 3 4 5 6 7

DATA SHEET LMV321/LMV358/LMV324

Pin Assignments

LMV321

SOT23-5 SC70-5

+In -Vs -In

1

+

5

+Vs

+In -Vs

1+5 Nhomakorabea+Vs

2 3

–

2 3

–

4

Out

-In

4

Out

LMV358

SOIC-8 MSOP-8

Out1 -In1 +In1 -Vs

Vo = 1Vpp >50kHz 100kHz 100kHz

DC

50

120

LO HI

0 50

1.3

RL = 10kΩ to Vs/2; LO1 RL = 10kΩ to Vs/2; HI1

0.1

2.6

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters. Notes: 1. Guaranteed by testing or statistical analysis at +25°C. 2. +IN and -IN are gates to CMOS transistors with typical input bias current of <1nA. CMOS leakage is too small to practically measure.

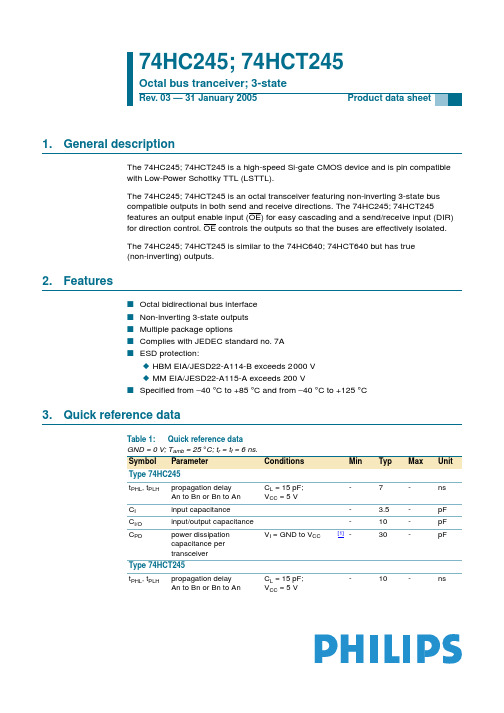

74HC245中文资料,74HC245N规格书,74HC245D技术文档,DATASHEET,NXP代理商

Table 1: Quick reference data GND = 0 V; Tamb = 25 °C; tr = tf = 6 ns.

Symbol Parameter

Conditions

Min Typ Max Unit

Type 74HC245

tPHL, tPLH propagation delay An to Bn or Bn to An

7#43;125 °C DIP20

plastic dual in-line package; 20 leads (300 mil)

SOT146-1

74HCT245D

−40 °C to +125 °C SO20

plastic small outline package; 20 leads; body width 7.5 mm

6. Pinning information

6.1 Pinning

1 DIR 20 VCC

DIR 1 A0 2 A1 3 A2 4 A3 5 A4 6 A5 7 A6 8 A7 9 GND 10

20 VCC 19 OE 18 B0 17 B1 16 B2 245 15 B3 14 B4 13 B5 12 B6 11 B7

SOT163-1

74HCT245PW

−40 °C to +125 °C TSSOP20 plastic thin shrink small outline package; 20 leads; SOT360-1 body width 4.4 mm

74HCT245DB

−40 °C to +125 °C SSOP20

74HC245DB

−40 °C to +125 °C SSOP20

APT24F50B;中文规格书,Datasheet资料

25 TJ = -55°C

TJ = 25°C 20

TJ = 125°C

15

10

5

0

0

5

10

15

20

25

ID, DRAIN CURRENT (A) Figure 5, Gain vs Drain Current

4 Co(cr) is defined as a fixed capacitance with the same stored charge as COSS with VDS = 67% of V(BR)DSS. 5 Co(er) is defined as a fixed capacitance with the same stored energy as COSS with VDS = 67% of V(BR)DSS. To calculate Co(er) for any value of

VGS = 0V, VDS = 0V to 333V

Qg Qgs Qgd td(on)

tr td(off)

tf

Total Gate Charge Gate-Source Charge Gate-Drain Charge Turn-On Delay Time Current Rise Time Turn-Off Delay Time Current Fall Time

nC ns

Source-Drain Diode Characteristics

Symbol Parameter

Test Conditions

Min Typ Max Unit

IS ISM VSD trr Qrr Irrm

dv/dt

Continuous Source Current (Body Diode) Pulsed Source Current (Body Diode) 1 Diode Forward Voltage Reverse Recovery Time

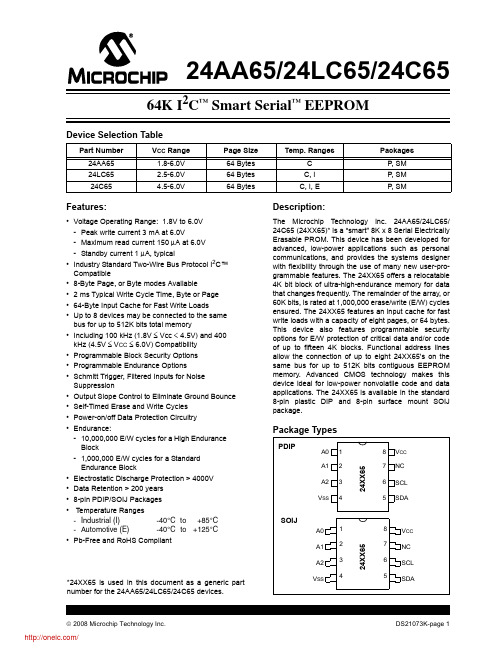

24LC65SM;24C65SM;24LC65-ISM;24LC65-IP;24C65P;中文规格书,Datasheet资料