core_cm3

CMSIS标准说明

( __TASKING__ ) __asm inline /*!< asm keyword for TASKING Compiler */ /*!< inline keyword for TASKING Compiler*/

这样 CPAL 中的功能函数就可以被定义成静态内联类型( static __INLINE) ,以实现编 译优化。

4.1 CMSIS 标准

ARM 公司于 2008 年 11 月 12 日发布了 ARM Cortex 微控制器软件接口标准 CMSIS 1.0。 CMSIS 是独立于供应商的 Cortex-M 处理器系列硬件抽象层, 为芯片厂商和中间件供应商提 供了简单的处理器软件接口,简化了软件复用工作,降低了 Cortex-M 上操作系统的移植难 度,并减少了新入门的微控制器开发者的学习曲线和新产品的上市时间。 根据近期的调查研究,软件开发已经被嵌入式行业公认为最主要的开发成本,图 4-1 为 近年来软件开发与硬件开发花费对比图。 因此, ARM 与 Atmel、 IAR、 KEIL、 Luminary Micro、 Micrium、NXP、SEGGER 和 ST 等诸多芯片和软件工具厂商合作,将所有 Cortex 芯片厂 商的产品的软件接口标准化,制定了 CMSIS 标准。此举意在降低软件开发成本,尤其针对 进行新设备项目开发或将已有的软件移植到其他芯片厂商提供的基于 Cortex 处理器的微控 制器的情况。 有了该标准, 芯片厂商就能够将他们的资源专注于对其产品的外设特性进行差 异化,并且能够消除对微控制器进行编程时需要维持的不同的、互相不兼容的标准的需求, 从而达到降低开发成本的目的。

4.1.1 基于 CMSIS 标准的软件架构

基于 CMSIS 2.0 标准的软件架构如图 4-2 所示。与 CMSIS 1.x 版本相比,CMSIS 2.0 去除了中间层,增加了一个可选的外设访问函数(Access Functions for Peripherals) 。

基于STM32F103单片机开发介绍

基于STM32F103单片机开发介绍目录一、IDE安装(MDK) (2)二、CMSIS架构简介 (3)三、标准外设库的外设库结构 (8)四、Startup文件的选择及文件拷贝 (10)五、创建工程 (14)六、配置工程 (24)七、下载及调试 (32)八、SourceInght添加技巧 (33)一、IDE安装(MDK)STM32使用的开发环境是MDK,目前我们使用的版本是MDK5.10。

安装步骤请参考《MDK5.10安装手册.pdf》。

二、CMSIS架构简介安装完ARM.CMSIS.3.20.4.pack和Keil.STM32F1xx_DFP.1.0.5.pack后,会在Keil的安装路径下生成对应的文件夹:Keil_v5\ARM\Pack\ARM\CMSIS\3.20.4Keil_v5\ARM\Pack\Keil\STM32F0xx_DFP\1.0.3Keil_v5\ARM\Pack\Keil\STM32F1xx_DFP\1.0.5PACK下的文件,将在我们开发和编译时都需要用上。

1.CMSISARM Cortex™微控制器软件接口标准(CMSIS:Cortex Microcontroller Software Interface Standard)是Cortex-M处理器系列的与供应商无关的硬件抽象层。

2.Core_cm3.h1、内对Lint进行了配置。

2、最重要的是调用了“stdint.h”文件,该文件由编译环境提供,对8位、16位、32位等整数类型的定义及其范围进行了规范,还定义了大数输出如:UINT_LEAST8_MAX。

主要用来屏蔽不同编译器之前的差异。

这种扩展整数类型的定义非常清晰,从类型名字上就可以看出它的长度,这有利于编写可移植的代码。

3、指示寄存器的访问权限。

CMSIS定义以下3种标识符来指定访问权限:_I(volatileconst)、_O(volatile)和_IO(volatile)。

STM32 3.5库文件中文说明

STM32库文件1.1.1 STM32标准外设库概述STM32标准外设库之前的版本也称固件函数库或简称固件库,是一个固件函数包,它由程序、数据结构和宏组成,包括了微控制器所有外设的性能特征。

该函数库还包括每一个外设的驱动描述和应用实例,为开发者访问底层硬件提供了一个中间API,通过使用固件函数库,无需深入掌握底层硬件细节,开发者就可以轻松应用每一个外设。

因此,使用固态函数库可以大大减少用户的程序编写时间,进而降低开发成本。

每个外设驱动都由一组函数组成,这组函数覆盖了该外设所有功能。

每个器件的开发都由一个通用API (application programming interface 应用编程界面)驱动,API对该驱动程序的结构,函数和参数名称都进行了标准化。

ST公司2007年10月发布了V1.0版本的固件库,MDK ARM3.22之前的版本均支持该库。

2008年6月发布了V2.0版的固件库,从2008年9月推出的MDK ARM3.23版本至今均使用V2.0版本的固件库。

V3.0以后的版本相对之前的版本改动较大,本书使用目前较新的V3.4版本。

1.1.2 使用标准外设库开发的优势简单的说,使用标准外设库进行开发最大的优势就在于可以使开发者不用深入了解底层硬件细节就可以灵活规范的使用每一个外设。

标准外设库覆盖了从GPIO到定时器,再到CAN、I2C、SPI、UART和ADC等等的所有标准外设。

对应的C源代码只是用了最基本的C编程的知识,所有代码经过严格测试,易于理解和使用,并且配有完整的文档,非常方便进行二次开发和应用。

1.1.3 STM32F10XXX标准外设库结构与文件描述1. 标准外设库的文件结构在上一小节中已经介绍了使用标准外设库的开发的优势,因此对标准外设库的熟悉程度直接影响到程序的编写,下面让我们来认识一下STM32F10XXX的标准外设库。

STM32F10XXX的标准外设库经历众多的更新目前已经更新到最新的3.5版本,开发环境中自带的标准外设库为2.0.3版本,本书中以比较稳定而且较新的V3.4版本为基础介绍标准外设库的结构。

core_cm3.c文件学习

1、core_cm3.c文件位于CoreSupport文件夹中,它是基于CMSIS标准的核内设备函数层的

CM3核通用的源文件。

它的作用是对于芯片商设计的芯片外设如果采用的是Cortex-M3核设计的话,它会为这些芯片外设提供一个进入CM3内核的接口。

2、core_cm3.c文件还有一些与编译器相关的条件编译语句,用于屏蔽不同编译器的差异。

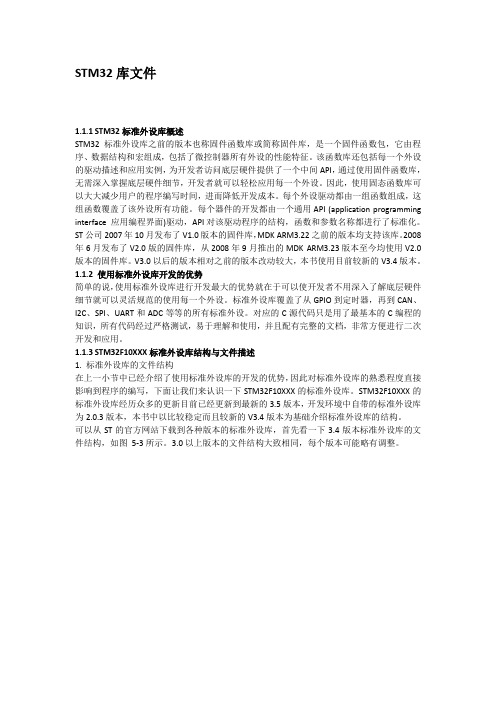

3、core_cm3.c文件中还包含了stdin.h这个头文件,这是一个ANSI C文件,该文件主要提

供一些新类型定义如

这些新类型定义屏蔽了在不同芯片平台是,出现的诸如int的大小是16位还是32位的差异,在以后的程序中,我们都将使用新类型如uint8_t uinit16_t等。

在稍旧版的程序中也会出现诸如u8 u16 u32这样的类型,分别表示无符号的8位、16位、32位整型,它们定义的位置在STM32f10x.h文件中,以后我们在新程序中还是尽量使用uint8_t uint16_t类型的定义。

4、core_cm3.c于启动文件一样都是底层文件,都是由ARM公司提供的,遵守CMSIS标准,即所有CM3芯片的库都带有这个文件,这样软件在不同的CM3芯片的移植工作上就得以简化。

CortexM3处理器异常事件相关寄存器

6

——

—— —— ——

5

——

—— —— ——

4

——

—— —— ——

3

USGFAULTACT

R

0 用法 fault 异常事件模块处于活动状态

2

——

—— —— ——

1

BUSFAULTACT

R

0 总线 fault 异常事件模块处于活动状态

0

MEMFAULTACT

R

0 存储器管理 fault 异常事件模块处于活动状态

CortexM3 处理器异常事件相关寄存器

CortexM3 处理器异常事件相关寄存器

一、概述

相对于传统单片机的中断系统,CM3 内核中断处理功能非常强大,但是带来的问题就是寄存器繁多, 不易理解、记忆,造成学习困难。本文对 CM3 内核处理器中断系统的相关寄存器进行分类,以方便学习。

二、控制开关类

2.1 总开关

1) 总标识:是内核提供的申请标识。 2) 子标识:是外设模块自己提供的具体中断申请标识(参见具体芯片手册)。

注 1:类似于 51 系列的各个中断的中断标识位。

注 2:可以人工写 1 来产生软件中断申请。

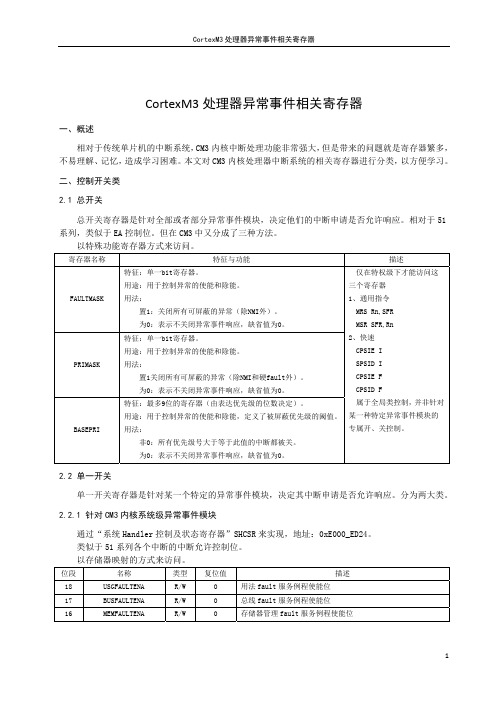

3.1 针对 CM3 内核系统级异常事件模块

1) 系统 Handler 控制及状态寄存器 SHCSR(地址:0xE000_ED24)。以存储器映射的方式来访问。

位段

名称

类型

复位值

描述

15 SVCALLPENDED R/W

0

SVC 悬起,当前有更高优先级的异常执行中。

14 BUSFAULTPENDED R/W

0

总线 fault 悬起,当前有更高优先级的异常执行中。

13 MEMFAULTPENDED R/W

STM32F103RC的工程模板创建

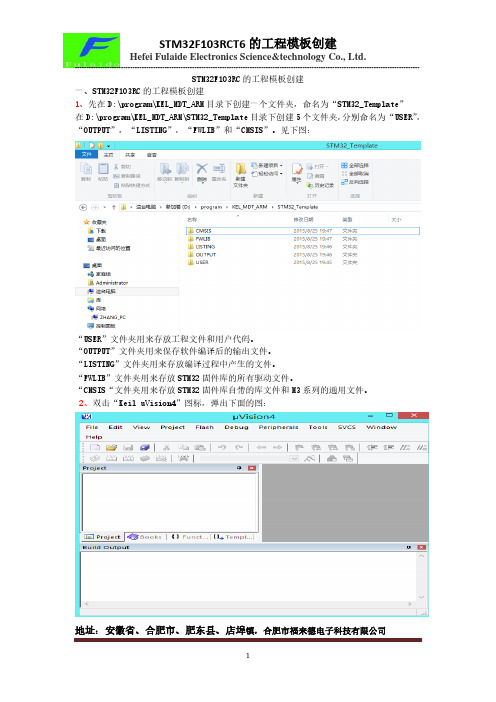

地址:安徽省、合肥市、肥东县、店埠镇,合肥市福来德电子科技有限公司STM32F103RC 的工程模板创建一、STM32F103RC 的工程模板创建1、先在D:\program\KEL_MDT_ARM 目录下创建一个文件夹,命名为“STM32_Template” 在D:\program\KEL_MDT_ARM\STM32_Template 目录下创建5个文件夹,分别命名为 “USER”, “OUTPUT ”,“LISTING”,“FWLIB ”和“CMSIS ”。

见下图:“USER”文件夹用来存放工程文件和用户代码。

“OUTPUT”文件夹用来保存软件编译后的输出文件。

“LISTING”文件夹用来存放编译过程中产生的文件。

“FWLIB ”文件夹用来存放STM32固件库的所有驱动文件。

“CMSIS“文件夹用来存放STM32固件库自带的库文件和M3系列的通用文件。

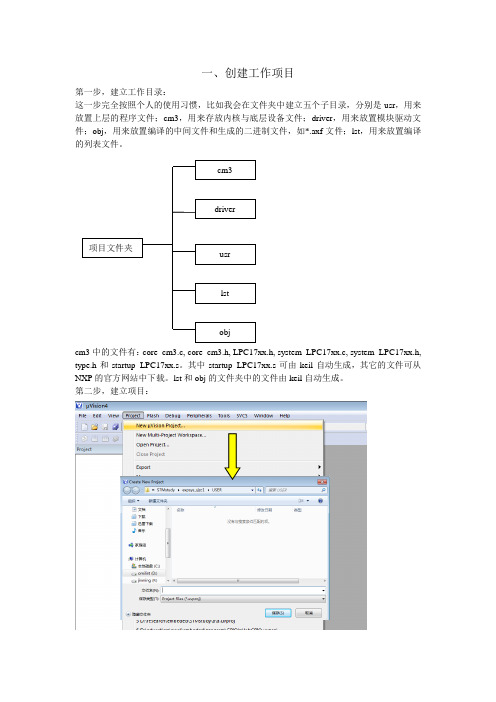

2、双击“Keil uVision4”图标,弹出下面的图:地址:安徽省、合肥市、肥东县、店埠镇,合肥市福来德电子科技有限公司3、点击“Project ”菜单下的“New uVision Project...”,见下图操作:4、找到D:\program\KEL_MDT_ARM\STM32_Template\USER 的目录,得到下面的对话框:地址:安徽省、合肥市、肥东县、店埠镇,合肥市福来德电子科技有限公司5、在上图的文件名栏目里输入“STM32-DEMO”,见下图:6、点击“保存”按钮,弹出下图对话框:地址:安徽省、合肥市、肥东县、店埠镇,合肥市福来德电子科技有限公司7、我们是用STM32F103RCT6,所以先找到芯片公司“STMicroelectronics ”,见下图:8、点击“STMicroelectronics”左边的“+”号,找到“STM32F103RC”,见下图:地址:安徽省、合肥市、肥东县、店埠镇,合肥市福来德电子科技有限公司9、点击“OK ”按钮,得到下面的对话框:10、点击“否(N )”按钮,得到下面的界面:地址:安徽省、合肥市、肥东县、店埠镇,合肥市福来德电子科技有限公司11、打开D:\program\开拓者3号\STM32F10x_StdPeriph_Lib_V3.5.0\Libraries\STM32F10x_StdPeriph_Driver 目录下,见下图:12、将上图中两个文件“inc”“src ”拷贝到D:\program\KEL_MDT_ARM\STM32_Template\FWLIB 目录下。

Cortex-M3 权威指南

Cortex-M3权威指南J oseph Yiu 著宋岩 译译序我接触ARM的历史约4年,早期是很欣赏这类处理器,到了后来切身使用它们的机会越来越多,慢慢地有了感觉,也更加喜欢了。

在偶然听说Cortex‐M3后,我就冥冥地感到它不寻常。

只是因为其它工作一直没有去了解它,直到今年初才进一步学习,很快就觉得相知恨晚。

当时只能看ARM官方的重量级资料,在看到这本书的英文原稿后,更感觉被电到了一样,于是突然有了把它翻译成中文的冲动。

经过累计约150个小时的奋战,终于有了此译稿。

在翻译过程中,我始终采用下列指导思想:1.尽量使用短句,并且把句子口语化。

我认为高深的道理不一定要用高级的语法句型才能表达。

想想看,即使是几位博士互相聊天讨论一个课题,也还是使用口语吧,而且火花往往就是在这种讨论中产生呢!2.多用修辞方法,并且常常引用表现力强的词汇——甚至包括网络用语和脍炙人口的歌词。

另外,有时会加工句子,使得风格像是对话。

这样做的目的是整个文风更鲜活——有点像为写出高分作文而努力的样子。

这点可能与很多学术著作的“严肃、平实”文风不同,也是一次大胆的尝试。

还希望读者不吝给予反馈。

3.在“宏观”上直译,在“微观”上意译。

英语不仅单一句子的语法和汉语不同,并且句子的连贯方式也与汉语不同。

因此在十几个到几十个单词的范围内,我先把它们翻译成脑子里的“中间语言”,再把中间语言翻译成汉语。

这样,就最大地避免了贻笑大方的“英式汉语”。

4.有些术语名词不方便翻译成汉语,或者目前的翻译方式不统一,或者与其它术语翻译的结果很接近,如error和fault,就只能用英语意会。

此时我就保留英文单词,相信这样比硬生生地翻译成汉语还好。

这些词汇主要是:retarget, fault, region等。

另外,英文中有一个很能精练表达“两者都”意思的单词及其用法:”both”,我也常常保留之。

5.图表对颜色的使用比较丰满,尤其是比较大型的插图,相信这样能帮助读者分析和理解。

在keil下开发lpc176x

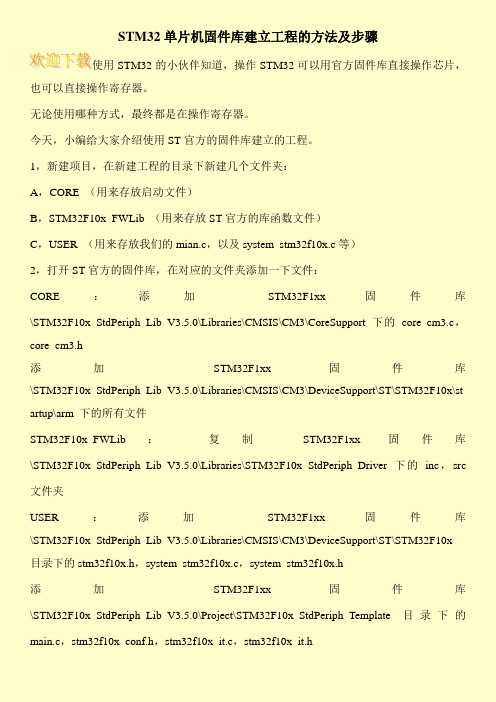

一、创建工作项目第一步,建立工作目录:这一步完全按照个人的使用习惯,比如我会在文件夹中建立五个子目录,分别是usr ,用来放置上层的程序文件;cm3,用来存放内核与底层设备文件;driver ,用来放置模块驱动文件;obj ,用来放置编译的中间文件和生成的二进制文件,如*.axf 文件;lst ,用来放置编译的列表文件。

cm3中的文件有:core_cm3.c, core_cm3.h, LPC17xx.h, system_LPC17xx.c, system_LPC17xx.h, type.h 和startup_LPC17xx.s 。

其中startup_LPC17xx.s 可由keil 自动生成,其它的文件可从NXP 的官方网站中下载。

lst 和obj 的文件夹中的文件由keil 自动生成。

第二步,建立项目:将项目文件放到项目文件夹中就可以了,接着会让你选择CPU的型号:接下来会出现是否生成启动文件,选是,会生成startup_LPC17xx.s,我将其放入了cm3文件夹中。

接下来就是建立项目虚拟文件夹,并将内核文件等已有的文件加入项目中最后我们的目录是:然后我们建立主函数入口程序:建立一个最简单的主函数,然后另存到真实目录usr中,然后加载到虚拟目录usr中完成后为:第三步,设定各项参数:其中在Output和Listing中,分别把目录设为Obj和lst,具体可见教程中,我们主要说C/C++、Debug和Utilities的选项。

其中,Define中可以填写需要预定义的宏,Optimization中的Level 0(-O0)表示优化参数,Level后面的数字越大,表示优化程度越高,但是优化程度的提高可能导致Debug的失败,因此我们一般选择0,等到程序全部测试成功后再用高优化参数进行编译。

Simulator表示使用虚拟仿真技术,也就是Keil自带的ARM虚拟机来进行仿真,一般我们使用时会选中下面的Limit Speed to Real-Time,使虚拟机的时钟和实际的时间保持一致。

STM32单片机固件库建立工程的方法及步骤

STM32单片机固件库建立工程的方法及步骤使用STM32的小伙伴知道,操作STM32可以用官方固件库直接操作芯片,也可以直接操作寄存器。

无论使用哪种方式,最终都是在操作寄存器。

今天,小编给大家介绍使用ST官方的固件库建立的工程。

1,新建项目,在新建工程的目录下新建几个文件夹:A,CORE (用来存放启动文件)B,STM32F10x_FWLib (用来存放ST官方的库函数文件)C,USER (用来存放我们的mian.c,以及system_stm32f10x.c等)2,打开ST官方的固件库,在对应的文件夹添加一下文件:CORE:添加STM32F1xx固件库\STM32F10x_StdPeriph_Lib_V3.5.0\Libraries\CMSIS\CM3\CoreSupport 下的core_cm3.c,core_cm3.h添加STM32F1xx固件库\STM32F10x_StdPeriph_Lib_V3.5.0\Libraries\CMSIS\CM3\DeviceSupport\ST\STM32F10x\st artup\arm 下的所有文件STM32F10x_FWLib:复制STM32F1xx固件库\STM32F10x_StdPeriph_Lib_V3.5.0\Libraries\STM32F10x_StdPeriph_Driver 下的inc,src 文件夹USER:添加STM32F1xx固件库\STM32F10x_StdPeriph_Lib_V3.5.0\Libraries\CMSIS\CM3\DeviceSupport\ST\STM32F10x 目录下的stm32f10x.h,system_stm32f10x.c,system_stm32f10x.h添加STM32F1xx固件库\STM32F10x_StdPeriph_Lib_V3.5.0\Project\STM32F10x_StdPeriph_Template 目录下的main.c,stm32f10x_conf.h,stm32f10x_it.c,stm32f10x_it.h。

STM32学习笔记——新建工程模板步骤(向原子哥学习)

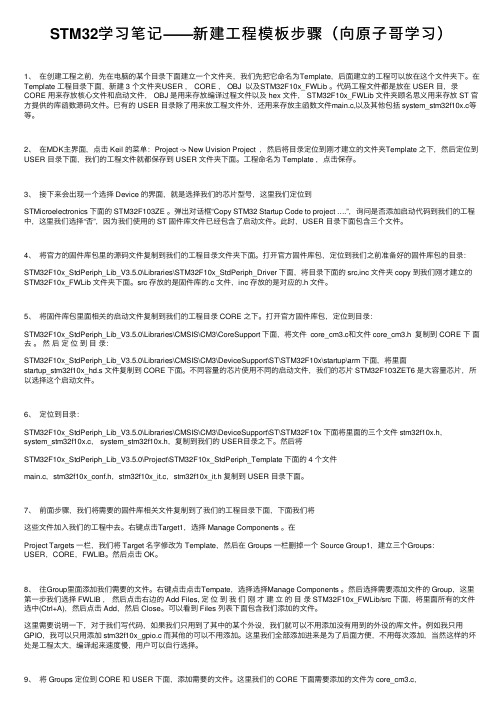

STM32学习笔记——新建⼯程模板步骤(向原⼦哥学习)1、在创建⼯程之前,先在电脑的某个⽬录下⾯建⽴⼀个⽂件夹,我们先把它命名为Template,后⾯建⽴的⼯程可以放在这个⽂件夹下。

在Template ⼯程⽬录下⾯,新建 3 个⽂件夹USER , CORE , OBJ 以及STM32F10x_FWLib 。

代码⼯程⽂件都是放在 USER ⽬,录CORE ⽤来存放核⼼⽂件和启动⽂件, OBJ 是⽤来存放编译过程⽂件以及 hex ⽂件, STM32F10x_FWLib ⽂件夹顾名思义⽤来存放 ST 官⽅提供的库函数源码⽂件。

已有的 USER ⽬录除了⽤来放⼯程⽂件外,还⽤来存放主函数⽂件main.c,以及其他包括 system_stm32f10x.c等等。

2、在MDK主界⾯,点击 Keil 的菜单:Project -> New Uvision Project ,然后将⽬录定位到刚才建⽴的⽂件夹Template 之下,然后定位到USER ⽬录下⾯,我们的⼯程⽂件就都保存到 USER ⽂件夹下⾯。

⼯程命名为 Template ,点击保存。

3、接下来会出现⼀个选择 Device 的界⾯,就是选择我们的芯⽚型号,这⾥我们定位到STMicroelectronics 下⾯的 STM32F103ZE 。

弹出对话框“Copy STM32 Startup Code to project ….”,询问是否添加启动代码到我们的⼯程中,这⾥我们选择“否”,因为我们使⽤的 ST 固件库⽂件已经包含了启动⽂件。

此时,USER ⽬录下⾯包含三个⽂件。

4、将官⽅的固件库包⾥的源码⽂件复制到我们的⼯程⽬录⽂件夹下⾯。

打开官⽅固件库包,定位到我们之前准备好的固件库包的⽬录:STM32F10x_StdPeriph_Lib_V3.5.0\Libraries\STM32F10x_StdPeriph_Driver 下⾯,将⽬录下⾯的 src,inc ⽂件夹 copy 到我们刚才建⽴的STM32F10x_FWLib ⽂件夹下⾯。

关于ARM的内核架构介绍

张凌001关于ARM的内核架构很多时候我们都会对M0,M0+,M3,M4,M7,arm7,arm9,CORTEX-A系列,或者说AVR,51,PIC等,一头雾水,只知道是架构,不知道具体是什么,有哪些不同?今天查了些资料,来解解惑,不是很详细,但对此有个大体了解。

咱先来当下最火的ARM吧1.ARMARM即以英国ARM(Advanced RISC Machines)公司的内核芯片作为CPU,同时附加其他外围功能的嵌入式开发板,用以评估内核芯片的功能和研发各科技类企业的产品.ARM 微处理器目前包括下面几个系列,以及其它厂商基于 ARM 体系结构的处理器,除了具有ARM 体系结构的共同特点以外,每一个系列的 ARM 微处理器都有各自的特点和应用领域。

- ARM7 系列- ARM9 系列- ARM9E 系列- ARM10E 系列- ARM11系列- Cortex 系列- SecurCore 系列- OptimoDE Data Engines- Intel的Xscale- Intel的StrongARM ARM11系列2. Cortex 系列32位RISCCPU开发领域中不断取得突破,其设计的微处理器结构已经从v3发展到现在的v7。

Cortex 系列处理器是基于ARMv7架构的,分为Cortex-M、Cortex-R和Cortex-A三类。

由于应用领域的不同,基于v7架构的Cortex处理器系列所采用的技术也不相同。

基于v7A的称为“Cortex-A系列。

高性能的Cortex-A15、可伸缩的Cortex-A9、经过市场验证的Cortex-A8处理器以及高效的Cortex-A7和Cortex-A5处理器均共享同一体系结构,因此具有完整的应用兼容性,支持传统的ARM、Thumb指令集和新增的高性能紧凑型Thumb-2指令集。

1Cortex-M系列Cortex-M系列又可分为Cortex-M0、Cortex-M0+、Cortex-M3、Cortex-M4;2Cortex-R系列Cortex-R系列分为Cortex-R4、Cortex-R5、Cortex-R7;3Cortex-A 系列Cortex-A系列分为Cortex-A5、Cortex-A7、Cortex-A8、Cortex-A9、Cortex-A15、Cortex-A50等 ,同样也就有了对应内核的Cortex-M0开发板、Cortex-A5开发板、Cortex-A8开发板、Cortex-A9开发板、Cortex-R4开发板等等。

嵌入式技术与应用开发项目教程(STM32版)习题答案

嵌入式技术与应用开发项目教程(STM32版)习题答案项目一LED控制设计与实现1-1 嵌入式系统是如何定义的?嵌入式系统(Embedded system),是一种“完全嵌入受控器件内部,为特定应用而设计的专用计算机系统”,根据IEEE(国际电气和电子工程师协会)的定义:嵌入式系统是控制、监视或辅助设备、机器或用于工厂运作的设备。

目前,国内普遍认同的嵌入式系统定义是:以应用为中心,以计算机技术为基础,软硬件可裁剪,适应应用系统对功能、可靠性、成本、体积、功耗等严格要求的专用计算机系统。

1-2 嵌入式系统具有哪些特点?嵌入式系统具有以下几个显著特点:(1)嵌入式系统是面向特定应用;(2)软件要求固态化存储;(3)嵌入式系统的硬件和软件都必须具备高度可定制性;(4)嵌入式系统的生命周期较长;(5)嵌入式系统开发需要开发工具和环境。

1-3 ARM Cortex-M3处理器是哪几个部分组成?嵌入式系统一般是由嵌入式处理器、存储器、输入输出和软件(嵌入式设备的应用软件和操作系统是紧密结合的)等4部分组成。

1-4 简述STM32F103系列产品的命名规则。

STM32F103系列产品的命名规则,是按照“STM32F103XXYY”格式来命名的,具体含义如下:(1)产品系列:STM32是基于ARM Cortex-M3内核设计的32位微控制器;(2)产品类型:F是通用类型;(3)产品子系列:101是基本型、102是USB基本型(USB全速设备)、103是增强型、105或107是互联型;(4)引脚数目(第一个X):T是36脚、C是48脚、R是64脚、V是100脚、Z是144脚;(5)闪存存储器容量(第二个X):4是16K、6是32K、8是64K、B是128K、C是256K、D是384K、E是512K;(6)封装(第一个Y):H是BGA、T是LQFP、U是VFQFPN、Y是WLCSP64;(7)温度范围(第二个Y):6是工业级温度范围-400C~850C、7是工业级温度范围-400C~1050C。

嵌入式技术与应用开发项目教程(STM32版)习题答案

嵌入式技术与应用开发项目教程(STM32版)习题答案项目一LED控制设计与实现1-1 嵌入式系统是如何定义的?嵌入式系统(Embedded system),是一种“完全嵌入受控器件内部,为特定应用而设计的专用计算机系统”,根据IEEE(国际电气和电子工程师协会)的定义:嵌入式系统是控制、监视或辅助设备、机器或用于工厂运作的设备。

目前,国内普遍认同的嵌入式系统定义是:以应用为中心,以计算机技术为基础,软硬件可裁剪,适应应用系统对功能、可靠性、成本、体积、功耗等严格要求的专用计算机系统。

1-2 嵌入式系统具有哪些特点?嵌入式系统具有以下几个显著特点:(1)嵌入式系统是面向特定应用;(2)软件要求固态化存储;(3)嵌入式系统的硬件和软件都必须具备高度可定制性;(4)嵌入式系统的生命周期较长;(5)嵌入式系统开发需要开发工具和环境。

1-3 ARM Cortex-M3处理器是哪几个部分组成?嵌入式系统一般是由嵌入式处理器、存储器、输入输出和软件(嵌入式设备的应用软件和操作系统是紧密结合的)等4部分组成。

1-4 简述STM32F103系列产品的命名规则。

STM32F103系列产品的命名规则,是按照“STM32F103XXYY”格式来命名的,具体含义如下:(1)产品系列:STM32是基于ARM Cortex-M3内核设计的32位微控制器;(2)产品类型:F是通用类型;(3)产品子系列:101是基本型、102是USB基本型(USB全速设备)、103是增强型、105或107是互联型;(4)引脚数目(第一个X):T是36脚、C是48脚、R是64脚、V是100脚、Z是144脚;(5)闪存存储器容量(第二个X):4是16K、6是32K、8是64K、B是128K、C是256K、D是384K、E是512K;(6)封装(第一个Y):H是BGA、T是LQFP、U是VFQFPN、Y是WLCSP64;(7)温度范围(第二个Y):6是工业级温度范围-400C~850C、7是工业级温度范围-400C~1050C。

固件库文件夹介绍

文件夹介绍1.Libraries 文件夹:●Libraries 文件夹里面的文件在我们建立工程的时候都会使用到;●下面有CMSIS 和STM32F10x_StdPeriph_Driver 两个目录;●这两个目录包含固件库核心的所有子文件夹和文件。

其中:⏹CMSIS 目录:启动文件;⏹STM32F10x_StdPeriph_Driver :STM32 固件库源码文件:◆inc目录存放的是stm32f10x_xxx.h 头文件,无需改动;◆src目录下面放的是stm32f10x_xxx.c 格式的固件库源码文件。

◆每一个.c 文件和一个相应的.h 文件对应。

这里的文件也是固件库的核心文件,每个外设对应一组文件。

2.Project 文件夹:●STM32F10x_StdPeriph_Examples 文件夹:⏹存放的的ST 官方提供的固件实例源码:◆在以后的开发过程中,可以参考修改这个官方提供的实例来快速驱动自己的外设;◆很多开发板的实例都参考了官方提供的例程源码。

●STM32F10x_StdPeriph_Template 文件夹:⏹存放的是工程模板;3.Utilities文件夹:●是官方评估板的一些对应源码,这个可以忽略不看。

4.stm32f10x_stdperiph_lib_um.chm文件:●这是一个固件库的帮助文档,这个文档非常有用;●在开发过程中,这个文档会经常被使用到。

关键文件介绍1.Libraries 目录下面几个重要的文件:●core_cm3.c 和core_cm3.h 文件:⏹位于\Libraries\CMSIS\CM3\CoreSupport 目录下面的;⏹是CMSIS 核心文件,提供进入M3 内核接口;⏹ARM 公司提供,对所有CM3 内核的芯片都一样;⏹你永远都不需要修改这个文件。

●\DeviceSupport\ST\STM32F10xt 文件夹:⏹主要存放一些启动文件、比较基础的寄存器定义文件、中断向量定义的文件;2.stm32f10x_rcc.c,stm32f10x_usart.c 以及misc.c 在每个实验基本都需要添加;。

在KeilMDK环境下使用STM32固件库

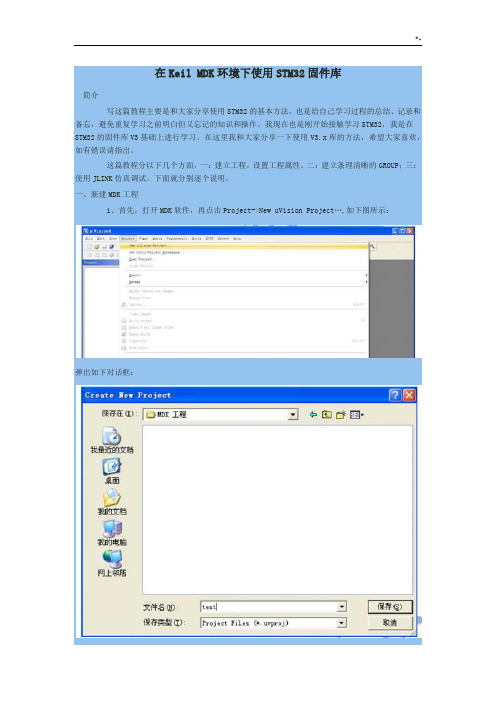

在Keil MDK环境下使用STM32固件库简介写这篇教程主要是和大家分享使用STM32的基本方法,也是给自己学习过程的总结、记录和备忘,避免重复学习之前明白但又忘记的知识和操作。

我现在也是刚开始接触学习STM32,我是在STM32的固件库V3基础上进行学习。

在这里我和大家分享一下使用V3.x库的方法,希望大家喜欢,如有错误请指出。

这篇教程分以下几个方面,一:建立工程,设置工程属性。

二:建立条理清晰的GROUP;三:使用JLINK仿真调试。

下面就分别逐个说明。

一、新建MDK工程1、首先,打开MDK软件,再点击Project->New uVision Project…,如下图所示:弹出如下对话框:新建一个文件夹MDK工程,然后把工程名字设为test,点击保存。

弹出选择器件的对话框,我们使用的是stm32单片机,所以选择STMicroelectronics下面的器件,如STM32F107VCT6,如图所示:点击OK,MDK会弹出一个对话框,如图所示:问是否加载启动代码到当前工程下面,如果选择是,则这个启动代码是旧版本库的启动代码,新版本的启动代码和这个不同,需要自己添加。

在这里我们使用的是新版本的库,所以点击否,自己添加启动代码。

启动代码是一段和硬件相关的汇编代码,是必不可少的!这个代码具体如何工作,感兴趣可以研究一下,现在可以不必关心它。

2、接下来我们需要对工程进行一些设置。

在工程区,右键点击Target1,选择Options for Target‘Target1’ 如图所示:弹出如下窗口,选择Output标签,设置目标文件的生成路径及其他相关参数。

如图点击Select Folder for Objects 在弹出的窗口中点空白处新建“Obj”文件夹,然后双击“Obj”文件夹,如图中所示的Path后,点击OK.点击Listing标签,新建“list”文件夹,设置链接文件的生成路径,及相关参数。

cm3的权限分级和操作模式

cm3的权限分级和操作模式

CM3是Cortex-M3的简称,它支持两种操作模式(处理器模式):Handler模式和线程模式,两种特权等级:特权级和用户级。

在CM3运行主程序(即线程模式)时,可以使用特权级别和用户级别;但是异常服务例程(即Handler模式)只能使用特权级别。

特权级访问特权级下,程序可以访问所有范围的存储器(除MPU),并且可以执行所有命令;用户级访问受限,一些访问权限将被禁止。

将代码区分成用户级和特权级,有利于程序架构的稳定,如某一个用户代码出问题,不会使其成为害群之狗,因为用户级别的代码是禁止对一些要害寄存器操作的。

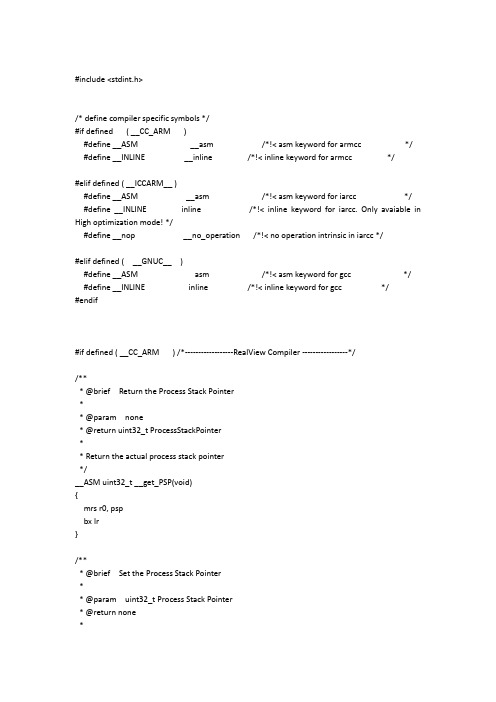

core_cm3

#include <stdint.h>/* define compiler specific symbols */#if defined ( __CC_ARM )#define __ASM __asm /*!< asm keyword for armcc */ #define __INLINE __inline /*!< inline keyword for armcc */#elif defined ( __ICCARM__ )#define __ASM __asm /*!< asm keyword for iarcc */ #define __INLINE inline /*!< inline keyword for iarcc. Only avaiable in High optimization mode! */#define __nop __no_operation /*!< no operation intrinsic in iarcc */#elif defined ( __GNUC__ )#define __ASM asm /*!< asm keyword for gcc */ #define __INLINE inline /*!< inline keyword for gcc */#endif#if defined ( __CC_ARM ) /*------------------RealView Compiler -----------------*//*** @brief Return the Process Stack Pointer** @param none* @return uint32_t ProcessStackPointer** Return the actual process stack pointer*/__ASM uint32_t __get_PSP(void){mrs r0, pspbx lr}/*** @brief Set the Process Stack Pointer** @param uint32_t Process Stack Pointer* @return none** Assign the value ProcessStackPointer to the MSP* (process stack pointer) Cortex processor register*/__ASM void __set_PSP(uint32_t topOfProcStack){msr psp, r0bx lr}/*** @brief Return the Main Stack Pointer** @param none* @return uint32_t Main Stack Pointer** Return the current value of the MSP (main stack pointer) * Cortex processor register*/__ASM uint32_t __get_MSP(void){mrs r0, mspbx lr}/*** @brief Set the Main Stack Pointer** @param uint32_t Main Stack Pointer* @return none** Assign the value mainStackPointer to the MSP* (main stack pointer) Cortex processor register*/__ASM void __set_MSP(uint32_t mainStackPointer){msr msp, r0bx lr}/*** @brief Reverse byte order in unsigned short value** @param uint16_t value to reverse* @return uint32_t reversed value* Reverse byte order in unsigned short value*/__ASM uint32_t __REV16(uint16_t value){rev16 r0, r0bx lr}/*** @brief Reverse byte order in signed short value with sign extension to integer ** @param int16_t value to reverse* @return int32_t reversed value** Reverse byte order in signed short value with sign extension to integer*/__ASM int32_t __REVSH(int16_t value){revsh r0, r0bx lr}#if (__ARMCC_VERSION < 400000)/*** @brief Remove the exclusive lock created by ldrex** @param none* @return none** Removes the exclusive lock which is created by ldrex.*/__ASM void __CLREX(void){clrex}/*** @brief Return the Base Priority value** @param none* @return uint32_t BasePriority* Return the content of the base priority register*/__ASM uint32_t __get_BASEPRI(void){mrs r0, basepribx lr}/*** @brief Set the Base Priority value** @param uint32_t BasePriority* @return none** Set the base priority register*/__ASM void __set_BASEPRI(uint32_t basePri){msr basepri, r0bx lr}/*** @brief Return the Priority Mask value** @param none* @return uint32_t PriMask** Return the state of the priority mask bit from the priority mask * register*/__ASM uint32_t __get_PRIMASK(void){mrs r0, primaskbx lr}/*** @brief Set the Priority Mask value** @param uint32_t PriMask* @return none** Set the priority mask bit in the priority mask register */__ASM void __set_PRIMASK(uint32_t priMask){msr primask, r0bx lr}/*** @brief Return the Fault Mask value** @param none* @return uint32_t FaultMask** Return the content of the fault mask register*/__ASM uint32_t __get_FAULTMASK(void){mrs r0, faultmaskbx lr}/*** @brief Set the Fault Mask value** @param uint32_t faultMask value* @return none** Set the fault mask register*/__ASM void __set_FAULTMASK(uint32_t faultMask) {msr faultmask, r0bx lr}/*** @brief Return the Control Register value** @param none* @return uint32_t Control value** Return the content of the control register*/__ASM uint32_t __get_CONTROL(void){mrs r0, controlbx lr}/*** @brief Set the Control Register value** @param uint32_t Control value* @return none** Set the control register*/__ASM void __set_CONTROL(uint32_t control){msr control, r0bx lr}#endif /* __ARMCC_VERSION */#elif (defined (__ICCARM__)) /*------------------ ICC Compiler -------------------*/ #pragma diag_suppress=Pe940/*** @brief Return the Process Stack Pointer** @param none* @return uint32_t ProcessStackPointer** Return the actual process stack pointer*/uint32_t __get_PSP(void){__ASM("mrs r0, psp");__ASM("bx lr");}/*** @brief Set the Process Stack Pointer** @param uint32_t Process Stack Pointer* @return none** Assign the value ProcessStackPointer to the MSP* (process stack pointer) Cortex processor register*/void __set_PSP(uint32_t topOfProcStack){__ASM("msr psp, r0");__ASM("bx lr");}/*** @brief Return the Main Stack Pointer** @param none* @return uint32_t Main Stack Pointer** Return the current value of the MSP (main stack pointer) * Cortex processor register*/uint32_t __get_MSP(void){__ASM("mrs r0, msp");__ASM("bx lr");}/*** @brief Set the Main Stack Pointer** @param uint32_t Main Stack Pointer* @return none** Assign the value mainStackPointer to the MSP* (main stack pointer) Cortex processor register*/void __set_MSP(uint32_t topOfMainStack){__ASM("msr msp, r0");__ASM("bx lr");}/*** @brief Reverse byte order in unsigned short value** @param uint16_t value to reverse* @return uint32_t reversed value** Reverse byte order in unsigned short value */uint32_t __REV16(uint16_t value){__ASM("rev16 r0, r0");__ASM("bx lr");}/*** @brief Reverse bit order of value** @param uint32_t value to reverse* @return uint32_t reversed value** Reverse bit order of value*/uint32_t __RBIT(uint32_t value){__ASM("rbit r0, r0");__ASM("bx lr");}/*** @brief LDR Exclusive** @param uint8_t* address* @return uint8_t value of (*address)** Exclusive LDR command*/uint8_t __LDREXB(uint8_t *addr){__ASM("ldrexb r0, [r0]");__ASM("bx lr");}/*** @brief LDR Exclusive** @param uint16_t* address* @return uint16_t value of (*address)* Exclusive LDR command*/uint16_t __LDREXH(uint16_t *addr){__ASM("ldrexh r0, [r0]");__ASM("bx lr");}/*** @brief LDR Exclusive** @param uint32_t* address* @return uint32_t value of (*address)** Exclusive LDR command*/uint32_t __LDREXW(uint32_t *addr){__ASM("ldrex r0, [r0]");__ASM("bx lr");}/*** @brief STR Exclusive** @param uint8_t *address* @param uint8_t value to store* @return uint32_t successful / failed** Exclusive STR command*/uint32_t __STREXB(uint8_t value, uint8_t *addr) {__ASM("strexb r0, r0, [r1]");__ASM("bx lr");}/*** @brief STR Exclusive** @param uint16_t *address* @param uint16_t value to store* @return uint32_t successful / failed* Exclusive STR command*/uint32_t __STREXH(uint16_t value, uint16_t *addr){__ASM("strexh r0, r0, [r1]");__ASM("bx lr");}/*** @brief STR Exclusive** @param uint32_t *address* @param uint32_t value to store* @return uint32_t successful / failed** Exclusive STR command*/uint32_t __STREXW(uint32_t value, uint32_t *addr){__ASM("strex r0, r0, [r1]");__ASM("bx lr");}#pragma diag_default=Pe940#elif (defined (__GNUC__)) /*------------------ GNU Compiler ---------------------*//*** @brief Return the Process Stack Pointer** @param none* @return uint32_t ProcessStackPointer** Return the actual process stack pointer*/uint32_t __get_PSP(void){uint32_t result=0;__ASM volatile ("MRS %0, psp" : "=r" (result) );return(result);}/*** @brief Set the Process Stack Pointer** @param uint32_t Process Stack Pointer* @return none** Assign the value ProcessStackPointer to the MSP* (process stack pointer) Cortex processor register*/void __set_PSP(uint32_t topOfProcStack){__ASM volatile ("MSR psp, %0" : : "r" (topOfProcStack) ); }/*** @brief Return the Main Stack Pointer** @param none* @return uint32_t Main Stack Pointer** Return the current value of the MSP (main stack pointer) * Cortex processor register*/uint32_t __get_MSP(void){uint32_t result=0;__ASM volatile ("MRS %0, msp" : "=r" (result) );return(result);}/*** @brief Set the Main Stack Pointer** @param uint32_t Main Stack Pointer* @return none** Assign the value mainStackPointer to the MSP* (main stack pointer) Cortex processor register*/void __set_MSP(uint32_t topOfMainStack){__ASM volatile ("MSR msp, %0" : : "r" (topOfMainStack) );/*** @brief Return the Base Priority value** @param none* @return uint32_t BasePriority** Return the content of the base priority register*/uint32_t __get_BASEPRI(void){uint32_t result=0;__ASM volatile ("MRS %0, basepri_max" : "=r" (result) ); return(result);}/*** @brief Set the Base Priority value** @param uint32_t BasePriority* @return none** Set the base priority register*/void __set_BASEPRI(uint32_t value){__ASM volatile ("MSR basepri, %0" : : "r" (value) );}/*** @brief Return the Priority Mask value** @param none* @return uint32_t PriMask** Return the state of the priority mask bit from the priority mask * register*/uint32_t __get_PRIMASK(void){uint32_t result=0;__ASM volatile ("MRS %0, primask" : "=r" (result) ); return(result);}/*** @brief Set the Priority Mask value** @param uint32_t PriMask* @return none** Set the priority mask bit in the priority mask register*/void __set_PRIMASK(uint32_t priMask){__ASM volatile ("MSR primask, %0" : : "r" (priMask) );}/*** @brief Return the Fault Mask value** @param none* @return uint32_t FaultMask** Return the content of the fault mask register*/uint32_t __get_FAULTMASK(void){uint32_t result=0;__ASM volatile ("MRS %0, faultmask" : "=r" (result) ); return(result);}/*** @brief Set the Fault Mask value** @param uint32_t faultMask value* @return none** Set the fault mask register*/void __set_FAULTMASK(uint32_t faultMask){__ASM volatile ("MSR faultmask, %0" : : "r" (faultMask) );}/*** @brief Reverse byte order in integer value** @param uint32_t value to reverse* @return uint32_t reversed value** Reverse byte order in integer value*/uint32_t __REV(uint32_t value){uint32_t result=0;__ASM volatile ("rev %0, %1" : "=r" (result) : "r" (value) );return(result);}/*** @brief Reverse byte order in unsigned short value** @param uint16_t value to reverse* @return uint32_t reversed value** Reverse byte order in unsigned short value*/uint32_t __REV16(uint16_t value){uint32_t result=0;__ASM volatile ("rev16 %0, %1" : "=r" (result) : "r" (value) );return(result);}/*** @brief Reverse byte order in signed short value with sign extension to integer ** @param int32_t value to reverse* @return int32_t reversed value** Reverse byte order in signed short value with sign extension to integer*/int32_t __REVSH(int16_t value){uint32_t result=0;__ASM volatile ("revsh %0, %1" : "=r" (result) : "r" (value) ); return(result);}/*** @brief Reverse bit order of value** @param uint32_t value to reverse* @return uint32_t reversed value** Reverse bit order of value*/uint32_t __RBIT(uint32_t value){uint32_t result=0;__ASM volatile ("rbit %0, %1" : "=r" (result) : "r" (value) );return(result);}/*** @brief LDR Exclusive** @param uint8_t* address* @return uint8_t value of (*address)** Exclusive LDR command*/uint8_t __LDREXB(uint8_t *addr){uint8_t result=0;__ASM volatile ("ldrexb %0, [%1]" : "=r" (result) : "r" (addr) );return(result);}/*** @brief LDR Exclusive** @param uint16_t* address* @return uint16_t value of (*address)**/uint16_t __LDREXH(uint16_t *addr){uint16_t result=0;__ASM volatile ("ldrexh %0, [%1]" : "=r" (result) : "r" (addr) );return(result);}/*** @brief LDR Exclusive** @param uint32_t* address* @return uint32_t value of (*address)** Exclusive LDR command*/uint32_t __LDREXW(uint32_t *addr){uint32_t result=0;__ASM volatile ("ldrex %0, [%1]" : "=r" (result) : "r" (addr) );return(result);}/*** @brief STR Exclusive** @param uint8_t *address* @param uint8_t value to store* @return uint32_t successful / failed** Exclusive STR command*/uint32_t __STREXB(uint8_t value, uint8_t *addr){uint32_t result=0;__ASM volatile ("strexb %0, %2, [%1]" : "=r" (result) : "r" (addr), "r" (value) );return(result);}/**** @param uint16_t *address* @param uint16_t value to store* @return uint32_t successful / failed** Exclusive STR command*/uint32_t __STREXH(uint16_t value, uint16_t *addr){uint32_t result=0;__ASM volatile ("strexh %0, %2, [%1]" : "=r" (result) : "r" (addr), "r" (value) );return(result);}/*** @brief STR Exclusive** @param uint32_t *address* @param uint32_t value to store* @return uint32_t successful / failed** Exclusive STR command*/uint32_t __STREXW(uint32_t value, uint32_t *addr){uint32_t result=0;__ASM volatile ("strex %0, %2, [%1]" : "=r" (result) : "r" (addr), "r" (value) );return(result);}/*** @brief Return the Control Register value** @param none* @return uint32_t Control value** Return the content of the control register*/uint32_t __get_CONTROL(void){uint32_t result=0;__ASM volatile ("MRS %0, control" : "=r" (result) ); return(result);}/*** @brief Set the Control Register value** @param uint32_t Control value* @return none** Set the control register*/void __set_CONTROL(uint32_t control){__ASM volatile ("MSR control, %0" : : "r" (control) ); }#endif。

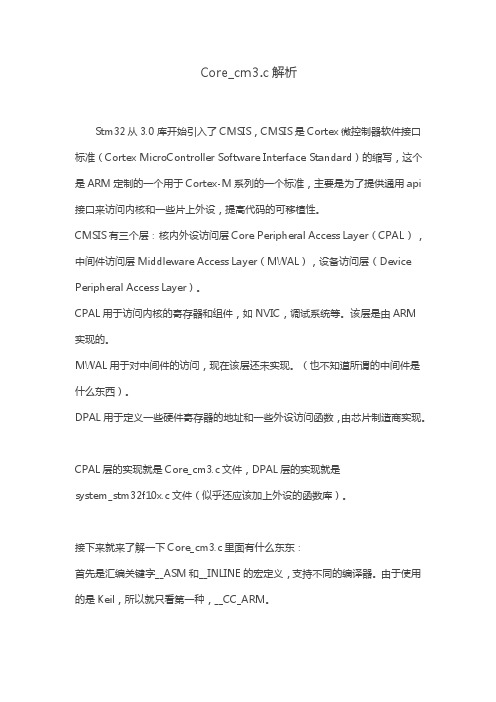

Core_cm3c解析

Core_cm3.c解析Stm32从3.0库开始引入了CMSIS,CMSIS是Cortex微控制器软件接口标准(Cortex MicroController Software Interface Standard)的缩写,这个是ARM定制的一个用于Cortex-M系列的一个标准,主要是为了提供通用api 接口来访问内核和一些片上外设,提高代码的可移植性。

CMSIS有三个层:核内外设访问层Core Peripheral Access Layer(CPAL),中间件访问层Middleware Access Layer(MWAL),设备访问层(Device Peripheral Access Layer)。

CPAL用于访问内核的寄存器和组件,如NVIC,调试系统等。

该层是由ARM实现的。

MWAL用于对中间件的访问,现在该层还未实现。

(也不知道所谓的中间件是什么东西)。

DPAL用于定义一些硬件寄存器的地址和一些外设访问函数,由芯片制造商实现。

CPAL层的实现就是Core_cm3.c文件,DPAL层的实现就是system_stm32f10x.c文件(似乎还应该加上外设的函数库)。

接下来就来了解一下Core_cm3.c里面有什么东东:首先是汇编关键字__ASM和__INLINE的宏定义,支持不同的编译器。

由于使用的是Keil,所以就只看第一种,__CC_ARM。

这里面的函数调用都只符合ARM过程调用标准的,如R0到R3用作参数和返回值传递,这也是这里面唯一用到的。

此外,在Keil中使用了__asm关键字后,编译器不会为函数增加返回指令,所以需要自己编写返回命令,也就是每个函数后面的bx lr。

1. __ASM uint32_t __get_PSP(void):获取进程堆栈指针PSP。

2. __ASM void __set_PSP(uint32_t topOfProcStack):设置PSP。

3. __ASM uint32_t __get_MSP(void):获取主堆栈指针MSP。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

#include <stdint.h>/* define compiler specific symbols */#if defined ( __CC_ARM )#define __ASM __asm /*!< asm keyword for armcc */ #define __INLINE __inline /*!< inline keyword for armcc */#elif defined ( __ICCARM__ )#define __ASM __asm /*!< asm keyword for iarcc */ #define __INLINE inline /*!< inline keyword for iarcc. Only avaiable in High optimization mode! */#define __nop __no_operation /*!< no operation intrinsic in iarcc */#elif defined ( __GNUC__ )#define __ASM asm /*!< asm keyword for gcc */ #define __INLINE inline /*!< inline keyword for gcc */#endif#if defined ( __CC_ARM ) /*------------------RealView Compiler -----------------*//*** @brief Return the Process Stack Pointer** @param none* @return uint32_t ProcessStackPointer** Return the actual process stack pointer*/__ASM uint32_t __get_PSP(void){mrs r0, pspbx lr}/*** @brief Set the Process Stack Pointer** @param uint32_t Process Stack Pointer* @return none** Assign the value ProcessStackPointer to the MSP* (process stack pointer) Cortex processor register*/__ASM void __set_PSP(uint32_t topOfProcStack){msr psp, r0bx lr}/*** @brief Return the Main Stack Pointer** @param none* @return uint32_t Main Stack Pointer** Return the current value of the MSP (main stack pointer) * Cortex processor register*/__ASM uint32_t __get_MSP(void){mrs r0, mspbx lr}/*** @brief Set the Main Stack Pointer** @param uint32_t Main Stack Pointer* @return none** Assign the value mainStackPointer to the MSP* (main stack pointer) Cortex processor register*/__ASM void __set_MSP(uint32_t mainStackPointer){msr msp, r0bx lr}/*** @brief Reverse byte order in unsigned short value** @param uint16_t value to reverse* @return uint32_t reversed value* Reverse byte order in unsigned short value*/__ASM uint32_t __REV16(uint16_t value){rev16 r0, r0bx lr}/*** @brief Reverse byte order in signed short value with sign extension to integer ** @param int16_t value to reverse* @return int32_t reversed value** Reverse byte order in signed short value with sign extension to integer*/__ASM int32_t __REVSH(int16_t value){revsh r0, r0bx lr}#if (__ARMCC_VERSION < 400000)/*** @brief Remove the exclusive lock created by ldrex** @param none* @return none** Removes the exclusive lock which is created by ldrex.*/__ASM void __CLREX(void){clrex}/*** @brief Return the Base Priority value** @param none* @return uint32_t BasePriority* Return the content of the base priority register*/__ASM uint32_t __get_BASEPRI(void){mrs r0, basepribx lr}/*** @brief Set the Base Priority value** @param uint32_t BasePriority* @return none** Set the base priority register*/__ASM void __set_BASEPRI(uint32_t basePri){msr basepri, r0bx lr}/*** @brief Return the Priority Mask value** @param none* @return uint32_t PriMask** Return the state of the priority mask bit from the priority mask * register*/__ASM uint32_t __get_PRIMASK(void){mrs r0, primaskbx lr}/*** @brief Set the Priority Mask value** @param uint32_t PriMask* @return none** Set the priority mask bit in the priority mask register */__ASM void __set_PRIMASK(uint32_t priMask){msr primask, r0bx lr}/*** @brief Return the Fault Mask value** @param none* @return uint32_t FaultMask** Return the content of the fault mask register*/__ASM uint32_t __get_FAULTMASK(void){mrs r0, faultmaskbx lr}/*** @brief Set the Fault Mask value** @param uint32_t faultMask value* @return none** Set the fault mask register*/__ASM void __set_FAULTMASK(uint32_t faultMask) {msr faultmask, r0bx lr}/*** @brief Return the Control Register value** @param none* @return uint32_t Control value** Return the content of the control register*/__ASM uint32_t __get_CONTROL(void){mrs r0, controlbx lr}/*** @brief Set the Control Register value** @param uint32_t Control value* @return none** Set the control register*/__ASM void __set_CONTROL(uint32_t control){msr control, r0bx lr}#endif /* __ARMCC_VERSION */#elif (defined (__ICCARM__)) /*------------------ ICC Compiler -------------------*/ #pragma diag_suppress=Pe940/*** @brief Return the Process Stack Pointer** @param none* @return uint32_t ProcessStackPointer** Return the actual process stack pointer*/uint32_t __get_PSP(void){__ASM("mrs r0, psp");__ASM("bx lr");}/*** @brief Set the Process Stack Pointer** @param uint32_t Process Stack Pointer* @return none** Assign the value ProcessStackPointer to the MSP* (process stack pointer) Cortex processor register*/void __set_PSP(uint32_t topOfProcStack){__ASM("msr psp, r0");__ASM("bx lr");}/*** @brief Return the Main Stack Pointer** @param none* @return uint32_t Main Stack Pointer** Return the current value of the MSP (main stack pointer) * Cortex processor register*/uint32_t __get_MSP(void){__ASM("mrs r0, msp");__ASM("bx lr");}/*** @brief Set the Main Stack Pointer** @param uint32_t Main Stack Pointer* @return none** Assign the value mainStackPointer to the MSP* (main stack pointer) Cortex processor register*/void __set_MSP(uint32_t topOfMainStack){__ASM("msr msp, r0");__ASM("bx lr");}/*** @brief Reverse byte order in unsigned short value** @param uint16_t value to reverse* @return uint32_t reversed value** Reverse byte order in unsigned short value */uint32_t __REV16(uint16_t value){__ASM("rev16 r0, r0");__ASM("bx lr");}/*** @brief Reverse bit order of value** @param uint32_t value to reverse* @return uint32_t reversed value** Reverse bit order of value*/uint32_t __RBIT(uint32_t value){__ASM("rbit r0, r0");__ASM("bx lr");}/*** @brief LDR Exclusive** @param uint8_t* address* @return uint8_t value of (*address)** Exclusive LDR command*/uint8_t __LDREXB(uint8_t *addr){__ASM("ldrexb r0, [r0]");__ASM("bx lr");}/*** @brief LDR Exclusive** @param uint16_t* address* @return uint16_t value of (*address)* Exclusive LDR command*/uint16_t __LDREXH(uint16_t *addr){__ASM("ldrexh r0, [r0]");__ASM("bx lr");}/*** @brief LDR Exclusive** @param uint32_t* address* @return uint32_t value of (*address)** Exclusive LDR command*/uint32_t __LDREXW(uint32_t *addr){__ASM("ldrex r0, [r0]");__ASM("bx lr");}/*** @brief STR Exclusive** @param uint8_t *address* @param uint8_t value to store* @return uint32_t successful / failed** Exclusive STR command*/uint32_t __STREXB(uint8_t value, uint8_t *addr) {__ASM("strexb r0, r0, [r1]");__ASM("bx lr");}/*** @brief STR Exclusive** @param uint16_t *address* @param uint16_t value to store* @return uint32_t successful / failed* Exclusive STR command*/uint32_t __STREXH(uint16_t value, uint16_t *addr){__ASM("strexh r0, r0, [r1]");__ASM("bx lr");}/*** @brief STR Exclusive** @param uint32_t *address* @param uint32_t value to store* @return uint32_t successful / failed** Exclusive STR command*/uint32_t __STREXW(uint32_t value, uint32_t *addr){__ASM("strex r0, r0, [r1]");__ASM("bx lr");}#pragma diag_default=Pe940#elif (defined (__GNUC__)) /*------------------ GNU Compiler ---------------------*//*** @brief Return the Process Stack Pointer** @param none* @return uint32_t ProcessStackPointer** Return the actual process stack pointer*/uint32_t __get_PSP(void){uint32_t result=0;__ASM volatile ("MRS %0, psp" : "=r" (result) );return(result);}/*** @brief Set the Process Stack Pointer** @param uint32_t Process Stack Pointer* @return none** Assign the value ProcessStackPointer to the MSP* (process stack pointer) Cortex processor register*/void __set_PSP(uint32_t topOfProcStack){__ASM volatile ("MSR psp, %0" : : "r" (topOfProcStack) ); }/*** @brief Return the Main Stack Pointer** @param none* @return uint32_t Main Stack Pointer** Return the current value of the MSP (main stack pointer) * Cortex processor register*/uint32_t __get_MSP(void){uint32_t result=0;__ASM volatile ("MRS %0, msp" : "=r" (result) );return(result);}/*** @brief Set the Main Stack Pointer** @param uint32_t Main Stack Pointer* @return none** Assign the value mainStackPointer to the MSP* (main stack pointer) Cortex processor register*/void __set_MSP(uint32_t topOfMainStack){__ASM volatile ("MSR msp, %0" : : "r" (topOfMainStack) );/*** @brief Return the Base Priority value** @param none* @return uint32_t BasePriority** Return the content of the base priority register*/uint32_t __get_BASEPRI(void){uint32_t result=0;__ASM volatile ("MRS %0, basepri_max" : "=r" (result) ); return(result);}/*** @brief Set the Base Priority value** @param uint32_t BasePriority* @return none** Set the base priority register*/void __set_BASEPRI(uint32_t value){__ASM volatile ("MSR basepri, %0" : : "r" (value) );}/*** @brief Return the Priority Mask value** @param none* @return uint32_t PriMask** Return the state of the priority mask bit from the priority mask * register*/uint32_t __get_PRIMASK(void){uint32_t result=0;__ASM volatile ("MRS %0, primask" : "=r" (result) ); return(result);}/*** @brief Set the Priority Mask value** @param uint32_t PriMask* @return none** Set the priority mask bit in the priority mask register*/void __set_PRIMASK(uint32_t priMask){__ASM volatile ("MSR primask, %0" : : "r" (priMask) );}/*** @brief Return the Fault Mask value** @param none* @return uint32_t FaultMask** Return the content of the fault mask register*/uint32_t __get_FAULTMASK(void){uint32_t result=0;__ASM volatile ("MRS %0, faultmask" : "=r" (result) ); return(result);}/*** @brief Set the Fault Mask value** @param uint32_t faultMask value* @return none** Set the fault mask register*/void __set_FAULTMASK(uint32_t faultMask){__ASM volatile ("MSR faultmask, %0" : : "r" (faultMask) );}/*** @brief Reverse byte order in integer value** @param uint32_t value to reverse* @return uint32_t reversed value** Reverse byte order in integer value*/uint32_t __REV(uint32_t value){uint32_t result=0;__ASM volatile ("rev %0, %1" : "=r" (result) : "r" (value) );return(result);}/*** @brief Reverse byte order in unsigned short value** @param uint16_t value to reverse* @return uint32_t reversed value** Reverse byte order in unsigned short value*/uint32_t __REV16(uint16_t value){uint32_t result=0;__ASM volatile ("rev16 %0, %1" : "=r" (result) : "r" (value) );return(result);}/*** @brief Reverse byte order in signed short value with sign extension to integer ** @param int32_t value to reverse* @return int32_t reversed value** Reverse byte order in signed short value with sign extension to integer*/int32_t __REVSH(int16_t value){uint32_t result=0;__ASM volatile ("revsh %0, %1" : "=r" (result) : "r" (value) ); return(result);}/*** @brief Reverse bit order of value** @param uint32_t value to reverse* @return uint32_t reversed value** Reverse bit order of value*/uint32_t __RBIT(uint32_t value){uint32_t result=0;__ASM volatile ("rbit %0, %1" : "=r" (result) : "r" (value) );return(result);}/*** @brief LDR Exclusive** @param uint8_t* address* @return uint8_t value of (*address)** Exclusive LDR command*/uint8_t __LDREXB(uint8_t *addr){uint8_t result=0;__ASM volatile ("ldrexb %0, [%1]" : "=r" (result) : "r" (addr) );return(result);}/*** @brief LDR Exclusive** @param uint16_t* address* @return uint16_t value of (*address)**/uint16_t __LDREXH(uint16_t *addr){uint16_t result=0;__ASM volatile ("ldrexh %0, [%1]" : "=r" (result) : "r" (addr) );return(result);}/*** @brief LDR Exclusive** @param uint32_t* address* @return uint32_t value of (*address)** Exclusive LDR command*/uint32_t __LDREXW(uint32_t *addr){uint32_t result=0;__ASM volatile ("ldrex %0, [%1]" : "=r" (result) : "r" (addr) );return(result);}/*** @brief STR Exclusive** @param uint8_t *address* @param uint8_t value to store* @return uint32_t successful / failed** Exclusive STR command*/uint32_t __STREXB(uint8_t value, uint8_t *addr){uint32_t result=0;__ASM volatile ("strexb %0, %2, [%1]" : "=r" (result) : "r" (addr), "r" (value) );return(result);}/**** @param uint16_t *address* @param uint16_t value to store* @return uint32_t successful / failed** Exclusive STR command*/uint32_t __STREXH(uint16_t value, uint16_t *addr){uint32_t result=0;__ASM volatile ("strexh %0, %2, [%1]" : "=r" (result) : "r" (addr), "r" (value) );return(result);}/*** @brief STR Exclusive** @param uint32_t *address* @param uint32_t value to store* @return uint32_t successful / failed** Exclusive STR command*/uint32_t __STREXW(uint32_t value, uint32_t *addr){uint32_t result=0;__ASM volatile ("strex %0, %2, [%1]" : "=r" (result) : "r" (addr), "r" (value) );return(result);}/*** @brief Return the Control Register value** @param none* @return uint32_t Control value** Return the content of the control register*/uint32_t __get_CONTROL(void){uint32_t result=0;__ASM volatile ("MRS %0, control" : "=r" (result) ); return(result);}/*** @brief Set the Control Register value** @param uint32_t Control value* @return none** Set the control register*/void __set_CONTROL(uint32_t control){__ASM volatile ("MSR control, %0" : : "r" (control) ); }#endif。