最新 1553B总线接口模块测试设备的设计系统开发-精品

1553B总线接口板的设计与实现

图 3 接口板总体设计框图

3 1553B 总线接口板的关键技术实现 3.1 DSP 模块设计 高速数字信号处理器是当前信息产业的热点技术之一。 与传统的 普通单片机相比, DSP 芯片放弃了冯·诺依曼结构, 代之以程序和数据 分开的哈佛结构。 从而大大提高了处理速度, 指令周期多为 ns 级, 比 普通单片机(多为 ms 级)快了 3 个数量级。 同时, DSP 芯片广泛采用流 水线操作, 这使得处理速度大为提高。 文中采用 TI 的 DSP 芯片 TMS320F206 用来实现 1553B 总线协议 的主体部分, 实现字和消息的处理等功能, DSP 模块工作流程如图 4 所 示, 主要包括: 1) 对总线接口板的初始化 (包括初始化 DSP 本身内部电路和寄存 器、 FPGA 和与上位机通讯寄存器); 2) 实现 RT 地址识别。 由于是多 RT 总线接口板, 所以收到数据 后, 应该判别该 RT 地址是否属于该接口板; 3) 与上位机消息传输控制功能。 消息传输控制程序完成总线传输 的数据在总线接口板和上位机之间的数据交换。 包括数据的读写过程和 自检测过程, 所要完成的操作如下: A、 向 FPGA 写入发送数据(到总线); B、 从 FPGA 内读出数据(该数据由 DSP 处理); C、 向双口 RAM 写入数据(到上位机); D、 自检测过程。 自检测过程是在收到上位机的自检命令后, 实现 接口板的数据发送和接收性能测试。 4) 中断控制程序。 在设计中, 使用了 3 个硬件中断, INT1, INT2 由 FPGA 来产生, INT3 则由上位机来产生。 INT3 是上位机和接口板 数据传输控制的一种手段, 通过 INT3 中断, 上位机告诉接口板(也就是 DSP)进行数据接收还是数据发送操作, 发送多少数据, 采用的消息格 式以及总线控制等等信息。 DSP 模块的软件采用 C 语言和汇编语言混合编程, 关键路径如中 断服务程序, 数据发送和接收程序都采用汇编语言以达到最大的执行效 率, 主程序采用 C 语言编写。

1553B总线接口检测仪设计与实现

导 系统 的 维修 能 力 。 关键 词: 1 5 5 3 B 总线 故 障检 测 终 端模拟 接 口 检 码: A

文章 编号 : 1 0 0 7 . 9 4 1 6 ( 2 0 1 5 ) 0 3 — 0 1 4 2 . 0 2

设计开发

I E i 目 啦 术

1 5 5 3 B总线接 口检测仪设计与实现

王战军 李雷 。

( 1 . 9 1 3 2 9 部队 山东威海 2 6 4 2 0 0 ; 2 . 北海舰队装备部 山东青 岛 2 6 6 0 0 0 )

摘要 : 针 对综导 系统 采用MI L — s T D一 1 5 5 3 B 总线进 行信息传输 而没有相应故 障检 测手段 的问题 提 出和设计 实现 了综导 总线接 口检测仅 阐述 了 系 统的主 要功 能 、 系统 架构、 软件 设计 和 工作 流程 。 该检 测仪 的 实现 , 为完成 综导 系统 日常维 护检测 、 分设备 调 试提 供 了技 术手段 和 工具, 有效提 高综

1553B总线控制器设计与调试

1553B总线控制器设计与调试丁明亮庄喜盈王虎锋(中国空空导弹研究院,河南洛阳471009)摘要本文分析了1553B的工作原理,提出了总线控制器控制方法的设计和总线控制器控制软件的设计,给出了部分中断代码,并结合笔者经验分析了1553B系统连接与调试应注意的一些问题。

关键词1553B总线;总线控制器;调试1引言1553B总线是美国军用标准MIL-STD-1553B定义的一种串行总线的传输形式。

由美国于20世纪70年代提出,总线的组成包插一个总线控制器(BC),若干个(最多31个)远程终端(RT),如果需要的话还可以加上负责监视总线信息的总线监视器(BM), 1553B总线通讯之所以得到如此广泛的应用,就是其具有以下特点:(1)强调实时性,1553B的传送速率为IMb/s,传输速率快。

(2)1553B总线按指令/响应的方式异步操作,即总线上所有的消息传输都由总线控制器发出的指令来控制,相关终端对指令应给予回答并执行操作。

这种方式非常适合集中控制的分布式处理系统。

(3)1553B总线是双冗余的传输线,总线都是双备份的,如果总线通讯不通,系统将会根据BC初始化时候的设定自动选择通讯重试,增强了系统的可靠性。

总线控制器是总线信息通讯的发起者和组织者,因此对BC控制的好坏将直接影响到总线通讯的质量。

2 总线的控制方法设计总线控制器是总线信息通讯的发起者,同时总线上所有信息的传输又均由BC来控制和激励,其简单的通讯过程为:BC向RT(或多个RT)发送一个发送或者接收指令,如果为接收指令,指令后会携带需要RT接收的数据字,RT接收到命令字后,在给定的相应时间范围内返回一个状态字,并执行相应动作。

如果为发送指令,RT只需接收BC 发送的数据字,然后返回状态即可。

在1553B总线上通讯的信息多种多样,所以针对不同的背景要有不同的总线设计方法,对于结构单一、数据量较少系统,总线上数据的活动不是很频繁,可以采取比较简单的方法:对周期性传输的消息采用固定周期来定时传输,对一次性消息采用命令插入的方式,要求RT返回数据的采用查询方式向RT的子地址下达命令字来获取数据。

1553总线接口模拟器设计

四、宿主CPU与BIU接口关系

图3

80C196与BU一6】580接口图

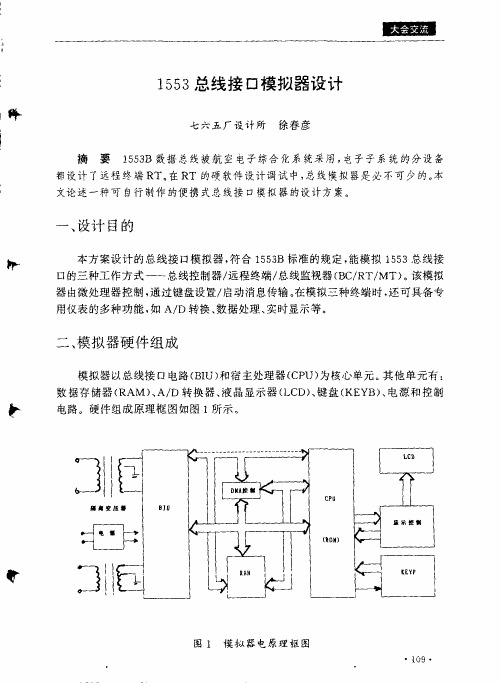

图3给出模拟器硬件设计的关键部分——CPu和BIU的接口连接方法。本方

・1¨・

案选用的1553终端电路BU61 580具有灵活的处理器/存储器接VI,可外接成多种 形式,在这里连接成16一BitDMA方式。单片计算机80C196KC同样具有灵活的接 口和应答I/O引脚。本方案CPU与BIU接口大都采用直接相连,基本上不用附加 组合逻辑或延时电路。图3中所列的译码器,根据实际情况均可简化为直接连接或 反相连接,若为保密目的,当然也可以采用一些PLD器件。

≮r]厂一

BIU

岩};# {{尚.1{ 吲}刽

圈1

i{精

模拟器电原理框图

CPU

《RO*)

三、各组成单元的作用及器件选用

1、键盘——选用164-8键的组合键盘、设定为1 6个数字键和8个功能键。键 盘是模拟器的输入设备,用来设置总线传输的消息桢集合和每一个桢消息的指令 和数据。使用者借助键盘控制、干予模拟器的工作过程,调动LCD的显示内容。 CPU响应键盘中断,执行键盘扫描程序,实现人机对话。 2、显示器——为兼顾便携和丰富显示幅面,显示屏选用SEDl330控制逻辑和 DMF50081液晶屏。SEDI 330最大驱动为640x256点阵,有较强的I/O缓冲器,和 DMF50081组合,可满足每个消息桢32字数据的整幅屏,还可以模拟波形和动态 表头的屏显。 3、共享RAM——根据动态数据量可选用不同容量的随机存储器,16位或8 位均可。本方案选用的DPS3232为64Kxl6位RAM,以DMA方式与BIU和CPU 连接,主要用作数据堆栈和消息桢的连续存储。 4、总线接口电路(BIU)——BIU是实现1553数据传输的器件。选用DIN;公 司的BU61580。该电路是DDC公司的第5代1553协议电路,集成度高,它的总线 收发器、编/译码器、1553协议逻辑、CPU接口及4Kxl6共享RAM混合于一个封 装之内,由70个引脚给出数据/地址、控制和接口线,由宿主CPU编程使用。 BU6】58的组成如下:

1553B总线接口模块测试设备的设计与实现

1553B总线接口模块测试设备的设计与实现摘要:1553B多路传输数据总线接口模块作为一种通用模块在我国自行研制的机载设备上大量使用,在研究1553B 总线接口模块测试技术的理论基础上,主要研究多块1553B总线接口模块的测试设备的设计与实现,为1553B总线接口模块的测试提供技术基础。

关键词:1553B总线接口;LBE总线;测试技术;80486CPU中图分类号:TN915.04?34 文献标识码:A 文章编号:1004?373X(2015)15?0022?03Design and realization of test equipment for 1553B bus interface moduleFAN Jiangfeng,HUANG Yi,YAO Lijuan(AVIC Xi’an Aeronautics Computing Technique Research Institute,Xi’an 710119,China)Abstract:As a general module,1553B multiplex transmission data bus interface module has been extensively used in airborne equipments made in China. On studying theoretical basis of 1553B bus interface modules testing technology,test equipment design and implementation ofmulti?block1553B bus interface module are researched. It provides a technical foundation for 1553B bus interface module testing.Keywords:1553B bus interface;LBE bus;testing technology;80486CPU0 引言MIL?STD?1553B总线是美军为其航空应用定义的串行多路数据总线标准,其数据传输率为1 Mb/s,具有实时性好、抗干扰能力强、冗余备份、易于扩展等优点,是一种确定的、可靠的、命令/响应式数据通信标准。

1553B总线多RT接口板的研究设计

西北工业大学硕士学位论文1553B总线多RT接口板的研究设计姓名:李海宁申请学位级别:硕士专业:系统工程指导教师:吴勇20030301西北I:业大学硕士学位论文摘要本文结合目前国内外航空电子通讯系统的发展状况,讨论了航空电子通讯网络的拓扑结构,总线通讯的传输协议,以及航空电子通讯软件的设计规则。

重点提出了一种新的“1553B总线多RT接口板”设计方案。

数字信号处理的理论与实现手段获得了快速的发展,已成为当代发展最快的学科之一。

由于其高速的处理速度和强大而又灵活的接口与通讯能力,在很多领域已经得到了广泛的应用。

随着工艺和技术的进步,集成电路技术的发展已经使得在一个芯片上集成一个可编程系统(即SOPC,ProgrammableSystemOnaChiP)成为可能。

其中,“现场可编程门阵列”(即FPGA,FieldProgrammableGateArray)由于其设计灵活、速度快,在数字专用集成电路的设计中得到更为广泛的应用。

本次设计以DSP(HN数字信号处理,DigitalSignalProcessing)和FPGA为核心,介绍了实现“1553B总线多RT接口板”原理,以及硬件的设计和软件的编制和仿真,重点介绍了FPGA内部的1553B总线数据发送和接收等处理单元的设计,并通过软件的仿真给予了论证。

关键词航空电子通讯系统1553B总线接口数据传输系统仿真DSPFPGA曲』B工业大学硕士学位论文AbstractThispaperintroducethetopologiesofavionicscommunicationsystem,transferprotocolofthedatabusandthekernelofdesigningtheavionicssystemthroughthestudyofthedevelopmentofavionicscommunicationsytemintheworldEmphasizingontheintroductionofanewdesignschemeof‘‘1553BBUSMulti—RTInterfaceBoard”.ThetheoryandimplementingmethodofDigitalSignalProcessing(DSP)hasgainedaverymuchrapidrise,andhasbecomeoneofthemostgrowingtechnologyinthisworld.Forit’SrapidSignalProcessingandpowerfullandflexibleinterfaceandcommunicationability,ithasbeenusedinalotofarea.Withtheadvancementoftechnologyandcraffwork,thedevolpmentofthetechniqueofIntegratedCircuit(IC)hasmadeitposibbletointegrateaProgrammableSystemOnaChip(SOPC).Amongallofthese,becauseit’Sflexibledesignmethodandhighspeed,“FieldProgrammableGateArray’’(FPGA)hasbeenwidelyusedinmanydigitaldesignofApplicationSpecificIntegratedCircuit.ThecoreofthispaperisDSPandFPGA.Thispaperintroducetheprincipleofthe“1553BBusMulti-RTInterfaceBoard”,thedesignofhardwareandsoftware,emphasizing011theinnerpartofFPGAwhichfulfillthefunctionofthetransmisionandreceptionof1553BBUSdataandotherfunctionpart.Throughsoftwaresimulation,thispaperalsogiveademonstrationtothedesign.Keyword:Avionicscommunicationsystem;1553BBUSinterface;BUStransfer;Simulationsystem;DSPFPGA西北工业人学硕十学位论文第一章概述随着时代的发展,对于增加飞机推力、改善气动性能等技术的成熟,航空系统设计任务的重点,逐渐集中在飞机内部的电子设计上。

1553B总线测试分析系统

MIL-STD-1553总线测试分析设备技术方案闵登学,TEL:,一、概述MIL-STD-1553总线测试分析设备主要用于对MIL-STD-1553总线形式的在线仿真测试、数据分析、数据存盘、数据回放、图形化显示等功能,满足了设备检测和故障定位的需要,为总线测试提供了强大的分析工具。

应用于飞机综合航电系统、装甲车辆综合电子系统、舰船综合电子系统、导弹等武器系统中。

二、主要功能MIL-STD-1553总线测试分析设备具备互为冗余的A、B两个总线通道,可用在MIL-STD-1553A/B 总线的测试、仿真和分析领域。

除去支持完整的MIL-STD-1553A/B总线协议外,还提供了差错注入功能。

高精度示波器,可监测总线信号波形,并实时显示出来。

三、技术方案3.1设备框图3.1.1对输出信号的测量将示波器和总线输出端口相连接,观测总线输出信号的幅值,判断输出信号是否满足总线规范的要求。

测试平台如下图:3.1.2连接器冗余通道A/B 通道测量由于板卡提供了双冗余通道A/B 总线,用户可以分别搭建A 或者B 总线平台,测量A 或者B 总线通信是否满足1553B 总线协议。

MIL-STD-1553总线测试分析设备主要由两大部分组成,第一部分是软件部分。

第二部分是硬件板卡和通用检测仪器,硬件组成主要由的PXI 、CPCI 系统主机;1553b 总线板卡和安捷伦公司的通用检测仪器产品;下面对上面软硬件功能做以详述。

3.2、硬件产品概述被测系统总线支线测试口1553测试板卡耦合器总线波形检测产品机箱采用具有高密度、坚固外壳及高性能连接器的特性的PXI便携式机箱,选用PXI高主频系统以适应高速采集的需要,硬件板卡所要完成航空MIL-STD-1553总线数据采集功能。

下面对硬件板卡的特性和功能做如下详述:3.2.1 便携式机箱PXIS-2558T功能及特性·CPCI/PXI总线更好的机械特性·兼容P X I规范R ev. 2.1·8个PXI槽(1个系统槽,7个PXI/CPCI外围槽)·带8.4英寸触摸LCD显示屏,支持分辨率800*600·带350W ATX, 220 AC电源·电源,温度和风扇监视灯3.2.2 PXI系统控制器功能及特性·PentiumM2.0G, 2G DDR内存,80G HDD·最新的3U P X I控制器·兼容P X I规范R ev. 2.1·前面板VGA输出,支持分辨率2048 *1536·热插拔C om p actFlash卡·U S B 2.0接口和10/100/1000以太网3.2.3M IL-STD-1553总线卡功能及特性·单通道,4个独立的双冗余MIL-STD-1553通道·同时具备BC/RT/MT三种功能·每个通道1M字节QDRMemory·完全适应MIL-STD-1553B Notice II/IV, MIL-STD-1760, 1553A 和 Link-163.2.4数字示波器DSO5012A功能及特性:·带宽100M,2通道,英文手册,运输箱·高达12位的垂直分辨率·MegaZoom III 存储与显示技术·USB (3 个端口),LAN,GPIB,XGA 显示输出·符合 LXI C类仪器标准·11种可选语言的用户手册和示波器在线帮助·安全环境选项3.3软件产品概述3.3.1模拟仿真软件主要特征1:1553B网络电气测试2:干扰状态下的测试3:干扰错误信息的注入4:软件可运行在自动控制、半自动控制、手动三种模式 5:测试完毕打印测试曲线及测试PV值,生成测试报告3.3.2扩展开发系统平台3.3.2.1 RTX实时系统平台概述由于很多商业和技术原因,Windows 2000、Windows XP、Windows vista和Windows XP Embedded操作系统越来越多被考虑作为实时系统平台,应用在军事、航空航天、交通、医疗、工业自动化等行业领域。

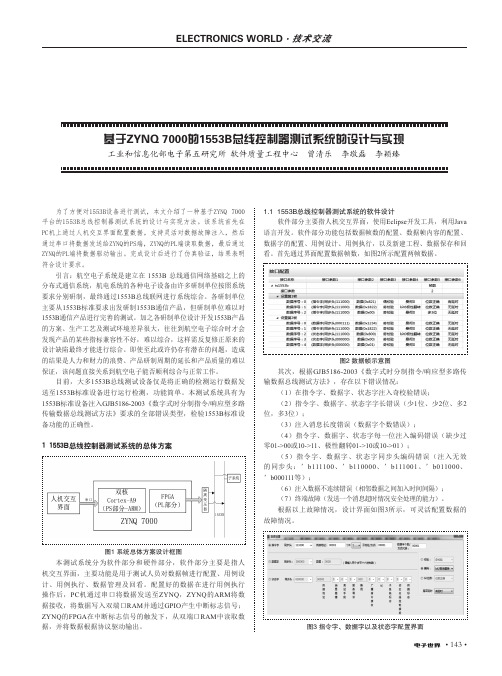

基于zynq 7000的1553b总线控制器测试系统的设计与实现

• 143•为了方便对1553B设备进行测试,本文介绍了一种基于ZYNQ 7000平台的1553B总线控制器测试系统的设计与实现方法。

该系统首先在PC机上通过人机交互界面配置数据,支持灵活对数据故障注入,然后通过串口将数据发送给ZYNQ的PS端,ZYNQ的PL端读取数据,最后通过ZYNQ的PL端将数据驱动输出。

完成设计后进行了仿真验证,结果表明符合设计要求。

引言:航空电子系统是建立在 1553B 总线通信网络基础之上的分布式通信系统,航电系统的各种电子设备由许多研制单位按照系统要求分别研制,最终通过1553B 总线联网进行系统综合。

各研制单位主要从1553B 标准要求出发研制1553B 通信产品,但研制单位难以对1553B 通信产品进行完善的测试。

加之各研制单位设计开发1553B 产品的方案、生产工艺及测试环境差异很大,往往到航空电子综合时才会发现产品的某些指标兼容性不好,难以综合,这样需反复修正原来的设计缺陷最终才能进行综合。

即使至此或许仍存有潜在的问题,造成的结果是人力和财力的浪费、产品研制周期的延长和产品质量的难以保证,该问题直接关系到航空电子能否顺利综合与正常工作。

目前,大多1553B 总线测试设备仅是将正确的检测运行数据发送至1553B 标准设备进行运行检测,功能简单。

本测试系统具有为1553B 标准设备注入GJB5186-2003《数字式时分制指令/响应型多路传输数据总线测试方法》要求的全部错误类型,检验1553B 标准设备功能的正确性。

1 1553B总线控制器测试系统的总体方案图1 系统总体方案设计框图本测试系统分为软件部分和硬件部分,软件部分主要是指人机交互界面,主要功能是用于测试人员对数据帧进行配置、用例设计、用例执行、数据管理及回看。

配置好的数据在进行用例执行操作后,PC 机通过串口将数据发送至ZYNQ ,ZYNQ 的ARM 将数据接收,将数据写入双端口RAM 并通过GPIO 产生中断标志信号;ZYNQ 的FPGA 在中断标志信号的触发下,从双端口RAM 中读取数据,并将数据根据协议驱动输出。

1553B总线测试分析系统

1553B总线测试分析系统

简介

1553B是一种数字化总线标准,主要运用于航空、军事、舰船等领域,采用双绞线或同轴电缆进行数据通信。

1553B总线测试分析系统是一款用于检测1553B 总线协议的设备,它可以通过模拟1553B数据流来测试和分析总线接口和设备的工作情况,进而帮助用户优化总线系统的性能。

功能特点

1.支持1553B协议的数据分析和解码

2.可以模拟1553B总线数据流进行测试

3.支持多种不同的总线速率和带宽

4.可以实时监控总线的状态和传输状态

5.支持数据传输的截获和注入

应用领域

1.航空航天领域:测试飞机上的1553B设备的可靠性和性能,优化总

线系统的稳定性、可靠性以及数据传输速率等。

2.军事领域:测试和维护1553B总线的设备,以确保各种战争情况下

的数据传输的稳定性和安全性。

3.船舶领域:测试和检测1553B总线的设备是否按照船舶的情况进行

优化,以保证船舶数据传输的速率和安全性。

实际操作

1553B总线测试分析系统经过简单的设置和调整,就可以使用。

以下是测试流程的示例:

•首先,将系统连接到1553B总线的接口上;

•然后,配置测试软件,包括总线速率、带宽、存储位置等;

•接下来,进入测试模式,模拟测试;

•最后,测试完毕后,分析测试结果,查看1553B总线的性能是否优化。

1553B总线测试分析系统的出现,对1553B总线协议的测试和优化带来了极大的便利,它可以帮助用户更快速、更准确地检测总线设备的工作情况,并通过数

据的捕获、注入和分析等手段进行有效的优化。

在航空、军事、舰船等领域,使用1553B总线测试分析系统是必不可少的。

1553B总线电缆网络自动测试系统设计及研究

随着航机电一体程度的日益提高,作为当前宇航电子设备首选的数据总线,MIL-STD-1553B总线(以下简称1553B总线)的地位日益突出,已广泛运用于航空航天、海上武器、地面武器等领域。

作为星载/箭载/机载/舰载/车载等控制系统中的数据总线,1553B总线电缆网络的可靠性直接影响到整个系统的正常运行,总线故障甚至会造成难以估计的损失。

有关1553B总线电缆网络的生产加工、系统组装前等各环节的检测,显得至关重要。

因此,如何对1553B总线电缆网络进行全面有效的检测是长期以来的一个重要课题。

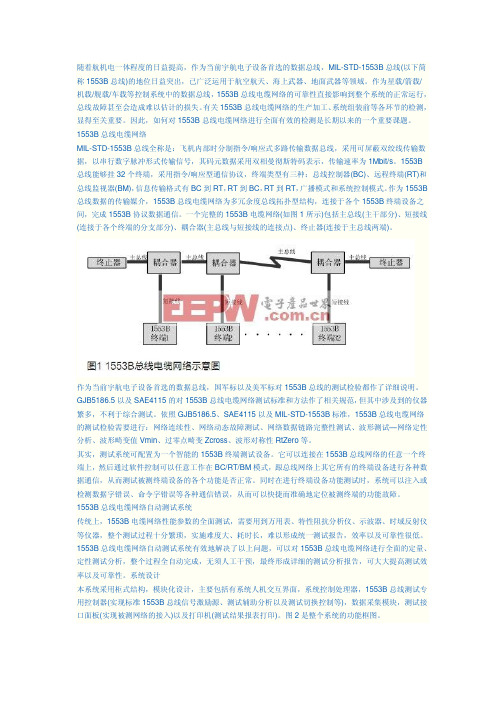

1553B总线电缆网络MIL-STD-1553B总线全称是:飞机内部时分制指令/响应式多路传输数据总线,采用可屏蔽双绞线传输数据,以串行数字脉冲形式传输信号,其码元数据采用双相曼彻斯特码表示,传输速率为1Mbit/s。

1553B 总线能够挂32个终端,采用指令/响应型通信协议,终端类型有三种:总线控制器(BC)、远程终端(RT)和总线监视器(BM),信息传输格式有BC到RT,RT到BC,RT到RT,广播模式和系统控制模式。

作为1553B 总线数据的传输媒介,1553B总线电缆网络为多冗余度总线拓扑型结构,连接于各个1553B终端设备之间,完成1553B协议数据通信。

一个完整的1553B电缆网络(如图1所示)包括主总线(主干部分)、短接线(连接于各个终端的分支部分)、耦合器(主总线与短接线的连接点)、终止器(连接于主总线两端)。

作为当前宇航电子设备首选的数据总线,国军标以及美军标对1553B总线的测试检验都作了详细说明。

GJB5186.5以及SAE4115的对1553B总线电缆网络测试标准和方法作了相关规范,但其中涉及到的仪器繁多,不利于综合测试。

依照GJB5186.5、SAE4115以及MIL-STD-1553B标准,1553B总线电缆网络的测试检验需要进行:网络连续性、网络动态故障测试、网络数据链路完整性测试、波形测试—网络定性分析、波形畸变值Vmin、过零点畸变Zcross、波形对称性RtZero等。

1553B接口BC功能设计

1553B总线BC功能设计本设计要求测试台实现1553B总线BC→RT的信息传输。

总线控制器会发出一个接收指令,后面是需要发送的特定数目的数据字。

当远程终端接收到并验证消息后,会反馈一个状态字给总线控制器[10][11]。

总线控制器为了确定RT 是否收到消息,可以用相关探询的方式指令得到状态信息。

BC→RT的传输过程如图3.1。

控制字接受命令字数据字1#数据字2#…最后一个数据状态字图3.1 BC→RT的传输过程1.11553B总线BC功能硬件设计1.1.1EP-H31580芯片周围电路设计(1)数据总线D0~D15是一个双向数据总线。

在大多数情况下是三态的,处于高阻态[14]。

EP-H31580的数据总线与FPGA的I/O引脚连接,实现两者之间的通信。

图3.2 数据总线的连接图(2)地址总线A0~A15是一个双向的地址总线,当CPU访问EP-H31580内部的寄存器和4K的存储器用A11-A0,CPU访问寄存器时用A4-A0选择寄存器,因此A11-A0与FPGA的地址线连接。

图3.3 地址总线的连接图(3)芯片设计手册规定CLK工作时钟为24MHz时钟,故接24MHz晶振。

图3.4 时钟引脚的连接图(4)本设计采用变压器耦合方式,电路图如下:图3.5 变压器耦合电路图图中电阻R57,R58,R59和R60采用了设计手册中推荐的55Ω/1W阻值,由于EP-H31580是双冗余总线,故有BUSA和BUSB。

PM-DB2725EX为隔离变压器,负责电压的转化。

1.21553B总线BC功能软件设计参照EP-H31580设计手册中给出的BC模式软件初始化序列,本设计的芯片初始化步骤如下:图3.6 初始化步骤。

基于FPGA的1553B总线接口技术研究与实现

基于FPGA的1553B总线接口技术研究与实现1553B总线是一种利用同轴电缆进行数据传输的串行数据总线,在军事航空领域有着广泛的应用。

为了更好地与1553B总线进行通讯,需要使用1553B总线接口技术。

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,可以通过编程实现不同的电路功能。

基于FPGA的1553B总线接口技术,可以使得1553B总线与其他系统更加灵活、高效地进行通讯。

1. 设计思路基于FPGA的1553B总线接口技术的设计主要包括两个部分:硬件设计和软件设计。

其中硬件设计主要使用FPGA实现1553B总线的接口电路,涉及到FPGA芯片的选择、1553B总线接口电路的设计等;软件设计则主要负责控制FPGA芯片接收和发送数据,并且进行相应的数据处理。

2. 硬件设计在FPGA芯片的选择过程中,需要根据1553B总线接口的需求,选择一个具有高速时钟频率,大容量存储器,丰富的I/O控制器等特点的FPGA芯片。

同时,在设计1553B总线接口电路时,需考虑到总线拓扑结构和接口标准等因素,确保设计的电路可以与1553B总线进行正常的通讯。

基于FPGA的1553B总线接口技术的软件设计主要包括四个方面:驱动程序、FPGA配置文件、通讯控制程序和数据处理程序。

驱动程序主要是将1553B总线接口电路控制所需的信号传递给FPGA芯片,从而实现与1553B总线的有效通讯。

FPGA配置文件主要包括FPGA芯片的配置信息,如时钟频率、芯片类型等,这些信息对于FPGA芯片的工作十分重要,需要进行正确的配置。

通讯控制程序主要是FPGA芯片接收、发送数据的控制程序,可以通过特定的通讯协议与1553B总线进行通讯。

数据处理程序主要是对接收到的数据进行解码、解析和存储,可以对1553B总线数据进行有效的处理和管理,方便后续使用。

4. 实现结果基于FPGA的1553B总线接口技术的实现结果表明,这种技术具有接口速度快、适应性强、功能丰富、易于维护等特点,可以更好地满足1553B总线在军事航空领域的应用需求。

MIL-STD-1553B总线测试、仿真解决方案(HI6130)

MIL-STD-1553B 总线通讯/测试/仿真解决方案天津优蓝科技有限公司⏹概述美国军用标准MIL-STD-1553B(飞机内部时分制指令/响应式多路传输总线)是美国军方专为飞机上的设备制定的一种信息传输总线标准,世界上有许多国家(GJB289A-97是依据MIL-STD-1553B制定的)引用了这个标准,其优越性、可靠性、合理性已被广泛的应用所证实。

天津优蓝1553B总线卡是一种具有智能化、通用化和标准化特征的1553B 多路传输总线通信接口卡。

该卡为33MHz 32 位PCI 总线插卡。

提供CPCI、PCI 多种结构形式。

可作为MIL-STD-1553B标准的通讯或总线仿真、测试卡使用,单功能(BC、RT和BM同时仅一种模式可用)、多功能(BC、2个RT和BM 多种模式同时可用)。

-40℃~+85℃工业级工作温度。

功能丰富,方便二次开发。

3U CPCI 板卡可提商用型和全加固型两种产品形式。

全加固型可供高可靠性应用和恶劣环境下使用。

⏹应用场合基于MIL-STD-1553B数据通讯,新产品的开发、调试,机载设备的测试,以及构建1553B仿真模拟测试平台⏹应用领域航空机载电子系统、飞机综合航电系统、装甲车辆综合电子系统、舰船综合电子系统、导弹武器系统。

基于MIL-STD-1553B数据通讯,新产品的开发、调试,机载设备的测试,以及构建1553B仿真模拟测试平台。

⏹主要性能●支持多种计算机总线平台:PCI、CPCI、PC104/Plus、ISA●遵循MIL-STD-1553B/GJB289A-97《飞机里面时分制指令/响应型多路传输数据总线要求》协议规范;●单功能、多功能选择;1、2路选择;每路为A、B双冗余通道(2通道)●多功能可支持1个BC、2个RT和1个BM同时工作模式;●使用1553B总线分析软件,可快速完成设备测试、现场调试和数据记录、查询等功能;●BM模式可设置多种过滤条件,降低主机负载;●RT模式支持数据长度和方式代码过滤;●BC可编程配置信息发送条件和发送时间间隔●总线传输速率1Mbps,●支持直接耦合或变压器耦合方式●提供灵活时标模式,BM可提供48位分辨率100ns时标;BC/RT可提供分辨率2us时标●板卡具有64M x 16bit的数据缓存空间,降低主机负载、防止丢数据;●支持中断操作操作模式;●3U CPCI 板卡可提供商用型和全加固型产品;●驱动支持:Windows XP、Win7、Win8、VxWorks、Linux 等等⏹1553B总线分析软件DATABUS-1553主要功能DATABUS-1553总线分析软件是一款基于Windows 平台,针对MIL-STD-1553B 总线进行测试和分析的应用软件。

1553B总线接口通用测试系统设计与实现

图 1 典型 1 5 B总线 系统 53

终 端 负 载

终 端 负

1 15 B总线系统 介绍 53

MI广 T)15B总线 全 称是 : 机 内部 时 分 制 指令 / LS 1 53 - 飞 响应 式 多 路 传输 数 据 总线 , 用 可 屏蔽 双绞 线 传输 数 据 , 采

载

以串行数字脉冲形式传输信号 , 其码元数据采用双相曼彻 斯特码进行表示 , 传输速率为 1Mbs 53 / 。15B数据总线可 连接 有 3 类 型 的 系统 :1总 线 控 制器 (C — —控 制 总 种 () B) 线上的数据传输 ; 2 远程终端控制器 ( T) () R ——响应 B C

Ab ta t a e n a ay ig teGJ 2 9 ( L S sr c :B sd o n l zn h B 8 A MI - TD- 5 3 1 5 B)d t u h r u h y h e in a di lme t t n o aab st o o g l ,t d sg n mpe na i f e o

( p o h e to i n ce c ,Th ce c n tt t ,Ai re En ie rn nv riy De . fte Elcr nca d S in e eS in eI siu e rFo c gn eig U iest ,Xi n71 0 ) ’ 0 51 a

c n r l r t s i a d,i p e n a i n ma h n s ,P e t g s fwa e r a ia i n p o e s s a ea s ic s e n o t o l e t e g o n b r t i lme t t c a im C t s i o t r e l t r c s e r lo d s u s d i sm o n z o ti pp r hs a e.

基于VxWorks的1553B总线测试系统设计与实现的开题报告

基于VxWorks的1553B总线测试系统设计与实现的开题报告一、研究背景及意义1553B总线是一种串行双绞线数据总线,广泛应用于军事、航空航天、船舶等领域。

由于应用广泛,需要对1553B总线进行测试验证,以保证数据传输的准确性和稳定性。

而基于VxWorks操作系统的1553B总线测试系统,能够在实际应用中快速进行测试和诊断,是现代化测试技术的主要手段之一。

本项目旨在设计并实现基于VxWorks的1553B总线测试系统,包括硬件设计与软件实现两个部分。

通过构建测试平台,实现1553B总线的性能测试、稳定性测试、兼容性测试等多项测试,并对测试结果进行分析和处理,提高测试效率和数据可靠性。

二、研究内容本项目的研究内容主要包括以下几个方面:1.硬件设计:设计1553B总线测试板卡,包括硬件接口设计、信号隔离设计、电源管理设计等。

2.软件设计:基于VxWorks操作系统,设计1553B总线测试系统软件,实现测试任务的下发和结果的上传,提高测试效率和数据可靠性。

3.测试方案设计:根据测试需求,设计多项测试方案,包括性能测试、稳定性测试、兼容性测试等,保证测试结果的全面性和准确性。

4.测试结果分析:对测试结果进行处理和分析,提取有价值的信息,为测试优化和下一步研发提供参考。

三、研究方法与技术路线本项目采用“硬件设计-软件设计-测试方案设计-测试结果分析”的研究方法,具体技术路线如下:1.硬件设计:根据1553B总线测试板卡的需求,完成电路设计、PCB设计、线束设计等,保证测试板卡的可靠性和稳定性。

2.软件设计:基于VxWorks操作系统,设计测试系统软件,包括通信协议设计、任务调度设计、数据处理设计等,提高测试效率和数据可靠性。

3.测试方案设计:根据测试需求,设计多项测试方案,包括性能测试、稳定性测试、兼容性测试等,保证测试结果的全面性和准确性。

4.测试结果分析:对测试结果进行处理和分析,提取有价值的信息,为测试优化和下一步研发提供参考。

基于FPGA的1553B总线接口技术研究与实现

基于FPGA的1553B总线接口技术研究与实现1553B总线是指一种数字式数据总线,它是一种用于军用航空电子设备中进行数据传输的标准,其具有性能稳定、数据传输可靠性高等特点。

FPGA是可编程逻辑门阵列的缩写,是一种可编程集成电路,可以用于实现各种数字电路,广泛应用于数字系统设计和通信领域。

一、1553B总线协议1553B总线协议是指在1553B总线上进行通信时的数据传输规则,其具体内容包括帧格式、数据时间序列、状态机等内容,是1553B总线的核心部分。

在1553B总线上,通信双方可以将数据分成两个方向进行传输,即从总线控制单元(BC)到远端设备(RT)的数据传输和从远端设备到总线控制单元的数据传输。

两个方向的数据传输的帧格式是不同的,具体如下:1、从BC到RT的数据传输帧格式首先是同步码,包括一个全1的码字和一个全0的码字,以便接收方进行时钟同步。

然后是各种命令字,包括广播命令字、直接寻址命令字、随机寻址命令字等,以便控制和选择特定的从设备。

接下来是数据和校验码,用于传输和校验数据的可靠性。

同样是首先发送同步码,然后发送标准响应、不正常响应等响应字,以回复BC端发来的数据请求。

最后是数据和校验码,用于传输和校验数据的可靠性。

基于FPGA的1553B总线接口技术主要是利用FPGA芯片实现1553B总线控制单元(BCU)和远端设备(RT)的数字电路,主要涉及到以下两个方面。

1、1553B总线控制单元(BCU)数字电路设计1553B总线控制单元(BCU)是负责发起数据传输请求,选择远端设备、传递控制信息和数据等任务的总线控制单元。

对于基于FPGA的1553B总线接口系统而言,BCU模块是整个系统的核心模块。

其主要功能是完成总线控制命令的解析、总线控制信息的生成、收发数据的控制等任务。

2、远端设备(RT)数字电路设计远端设备(RT)是总线上的被控设备,主要的任务是接受来自总线控制单元的控制指令,并按照指令返回相应的数据。

基于DSP的1553B总线系统设计与实现

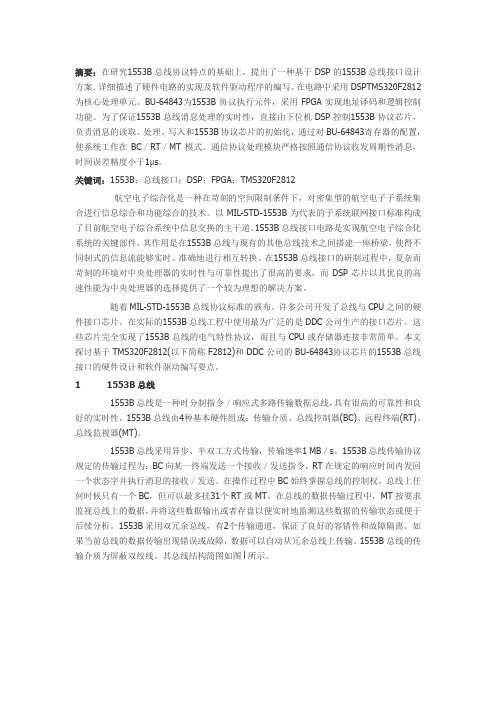

摘要:在研究1553B总线协议特点的基础上,提出了一种基于DSP的1553B总线接口设计方案.详细描述了硬件电路的实现及软件驱动程序的编写。

在电路中采用DSPTMS320F2812为核心处理单元。

BU-64843为1553B协议执行元件,采用FPGA实现地址译码和逻辑控制功能。

为了保证1553B总线消息处理的实时性,直接由下位机DSP控制1553B协议芯片,负责消息的读取、处理、写入和1553B协议芯片的初始化,通过对BU-64843寄存器的配置,使系统工作在BC/RT/MT模式。

通信协议处理模块严格按照通信协议收发周期性消息,时间误差精度小于1μs。

关键词:1553B;总线接口;DSP;FPGA;TMS320F2812航空电子综合化是一种在苛刻的空间限制条件下,对密集型的航空电子子系统集合进行信息综合和功能综合的技术。

以MIL-STD-1553B为代表的子系统联网接口标准构成了目前航空电子综合系统中信息交换的主干道。

1553B总线接口电路是实现航空电子综合化系统的关键部件,其作用是在1553B总线与现有的其他总线技术之间搭建一座桥梁,使得不同制式的信息流能够实时、准确地进行相互转换。

在1553B总线接口的研制过程中,复杂而苛刻的环境对中央处理器的实时性与可靠性提出了很高的要求,而DSP芯片以其优良的高速性能为中央处理器的选择提供了一个较为理想的解决方案。

随着MIL-STD-1553B总线协议标准的颁布。

许多公司开发了总线与CPU之间的硬件接口芯片。

在实际的1553B总线工程中使用最为广泛的是DDC公司生产的接口芯片。

这些芯片完全实现了1553B总线的电气特性协议,而且与CPU或存储器连接非常简单。

本文探讨基于TMS320F2812(以下简称F2812)和DDC公司的BU-64843协议芯片的1553B总线接口的硬件设计和软件驱动编写要点。

1 1553B总线1553B总线是一种时分制指令/响应式多路传输数据总线,具有很高的可靠性和良好的实时性。

基于USB接口1553B总线设备检测系统设计

基于USB接口1553B总线设备检测系统设计1 引言MIL-STD-1553B 军用总线标准,在军事装备,特别是飞机系统中得到了广泛的应用,舰载系统中也正在逐步推广。

对于1553B 总线传输信息的飞机系统,特别是由该总线网络构成的综合航火控系统、通信系统而言,系统时实监测与在线故障诊断均建立在信息录取的前提下。

为了方便录取1553B 总线上传输的信息就需要应用1553B 总线到计算机标准接口转换器,目前常用转换器有1553B- PCI、1553B-VXI 等,但在工程实践过程中,它们存在体积大、价格高、使用不方便等缺陷。

相比而言,USB 接口具有体积小、携带方便、热插拔等特征,具有不可替代的优势。

本文介绍的1553B 设备检测系统就是基于USB 接口的。

设计包含两大部分:硬件设计和软件设计。

硬件设计主要实现1553B 接口到USB 接口的转换;软件设计主要是USB 芯片固件开发、USB 接口驱动、开发计算机测试1553B 设备软件。

2 硬件系统设计本系统的硬件设计工作主要集中在1553B 与USB 总线接口的转换设计。

硬件系统分成三部分:1553B 接口转换电路、FPGA 译码电路和USB 接口电路。

如 2.1 1553B 接口转换电路目前,1553B 接口芯片种类繁多,根据工程应用场合和实际需要,我们选用DDC 公司BU-61580 芯片。

BU-61580 芯片除了具有远程终端(RT)功能外,还可以用作总线控制器(BC)、总线监控器(MT)。

其内部功能极强,接口灵活、便于控制,有各种封装形式和供电电压供用户选择。

2.2 FPGA 译码电路。

基于FPGA的1553B总线接口技术研究与实现

基于FPGA的1553B总线接口技术研究与实现

本文基于现场可编程逻辑门阵列(FPGA)技术,对1553B总线接口进行了研究与实现。

FPGA是一种可编程的硬件设备,具有灵活性强、速度快等优点,非常适合于数字通信接口的设计和实现。

在本研究中,我们首先研究了1553B总线接口的工作原理和相关协议。

然后,设计了基于FPGA的1553B总线接口电路,并进行了硬件电路设计和信号调试。

我们通过实验验证了基于FPGA的1553B总线接口的可行性和性能。

实验结果表明,基于FPGA的1553B总线接口具有良好的性能和稳定性。

相对于传统的硬件电路实现,基于FPGA的接口具有以下优点:

FPGA具有非常高的灵活性和可扩展性。

通过编程,可以实现不同的功能和协议,并根据具体应用需求进行定制化设计。

这使得基于FPGA的1553B总线接口能够适应不同的应用场景和需求。

基于FPGA的1553B总线接口速度快。

FPGA可以实现并行处理和高速数据传输,保证了数据传输的实时性和可靠性。

这在航空航天领域的高速通信中非常重要。

基于FPGA的1553B总线接口易于更新和维护。

通过重新编程,可以灵活地修改和升级功能,而无需更换硬件设备。

这降低了维护成本,并延长了使用寿命。

基于FPGA的1553B总线接口技术在航空航天领域具有广阔的应用前景。

通过进一步的研究和开发,可以不断提高性能和功能,为航空航天通信提供更加先进和可靠的解决方案。

基于1553B总线的测试系统的设计与实现

O 引 言

总 线控 制器 B C只 能 有 一 个 , 1 5 5 3 B总线 上 的 操 作

复的功能。1 5 5 3 B总线采用双冗余 的通道 , 能够提 高整个系统的可靠性。弹上测试系统对数据传输的

可靠 性 , 准 确性 , 传输速度要求高, 所 以对 于弹 上 测 试 系统采 用 1 5 5 3 B总线 进行 数据 通信 。 1 1 5 5 3 B总线 的特 点 1 5 5 3 B总线 包括 总线 控制 器 B C 、 远程 终 端 RT 、

Ap r. 2 01 5

基于 1 5 5 3 B总线 的测试 系统的设 计与实现

刘金 梅 许 振 忠 张 明 明。

( 1 .北华航天工业学院 电子与控制工程学院 ,河北 廊坊 0 6 5 0 0 0 ;2 .廊 坊职业技术学院,河北 廊 坊 0 6 5 0 0 0 )

摘

要 :本文基于弹上 系统进行 测试 的研 究 ,详细叙述 1 5 5 3 B总线 的特点 以及 1 5 5 3 B总线 的协议 在弹上测 试系

息流 , MT首先要对消息流进行解码 , 对 于协议规定 的所有传输形式 , MT都要将接收到的命令字 、 状态

字、 数据 字按 照一定 格 式存储 在存 储器 中 , 并 生成 状

图1 1 5 5 3 B总 线 系统 结构 图

态字来表征消息流的状态 , 对于不符合协议要求的 错误 消息流 , MT如实存储接 收到的命令字 、 状态

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1553B总线接口模块测试设备的设计系

统开发

摘要: 1553B多路传输数据总线接口模块作为一种通用模块在我国自行研制的机载设备上大量使用,在研究1553B 总线接口模块测试技术的理论基础上,主要研究多块1553B总线接口模块的测试设备的设计与实现,为1553B总线接口模块的测试提供技术基础。

关键词: 1553B总线接口; LBE总线;测试技术; 80486CPU

中图分类号: TN915.04?34 文献标识码: A 文章编号: 1004?373X (2019)15?0022?03

Design and realization of test equipment for 1553B bus interface module

FAN Jiangfeng, HUANG Yi, YAO Lijuan

(AVIC Xi’an Aeronautics puting Technique Research Institute,Xi’an 710119, China)

Abstract: As a general module, 1553B multiplex transmission data bus interface module has been extensively used in airborne equipments made in China. On studying theoretical basis of 1553B bus interface modules testing technology, test equipment design and implementation of multi?block1553B bus interface module are researched. It provides a technical foundation for 1553B bus interface module testing.

Keywords: 1553B bus interface; LBE bus; testing technology;80486CPU

0 引言

MIL?STD?1553B总线是美军为其航空应用定义的串行多路数据总线标准,其数据传输率为1 Mbs,具有实时性好、抗干扰能力强、冗余备份、易于扩展等优点,是一种确定的、可靠的、命令响应式数据通信标准。

我国于20世纪90年代引进和使用该标准。

GJB289A?97 飞机内部时分制指令响应型多路传输数据总线,简称GJB289A,是我国制定的与美国1553B相对应的军用航空总线标准,目前该标准已广泛应用在国内机载航空电子系统通信网络中,1553B总线接口模块(也称MBI模块)作为一种通用模块在我国自行研制的机载设备上大量使用。

本文在研究1553B总线接口模块测试技术的理论基础上,主要研究多块1553B总线接口模块的测试设备的设计与实现。

1 1553B总线测试设备的设计与实现

1.1 1553B总线概述

1553B总线系统主要包括终端模块、耦合器、电缆、电缆连接器、终端匹配器等,它们通过两根余度电缆连接,最多可挂接32个终端。

在总线通信过程中一条总线(A总线)工作,另一条总线(B总线)处于热备份状态;总线耦合有直接耦合与变压器耦合两种方式。

1553B总线通信系统联接的终端按其作用分为总线控制器(BC)、远程终端(RT)和总线监控器(BM或MT)。

BC是在总线上惟一建立和启动数据传输。