布局布线---SoC Encouter

Encounter数字实现系统的先进

Encounter 数字实现系统的先进Cadence 公司最新推出的Encounter Digital ImplementaTIon System 采用领先的多CPU 基础架构与高级存储器结构,实现了端到端并行处理流程,实现了极高的从RTL-to-GDSII 的可调整性,在RSH、sun grid 和LSF 平台上的性能可提高10 到15 倍。

该系统还带来了一个新的超高效的核存储架构,使单CPU 性能/容量>40%,可提供单CPU 操作的更高性能、更高容量的设计收敛,使IC 设计的周转时间大大缩短。

使用Encounter 数字实现系统,设计师能够从它统一和自动化的实现环境中,在高性能、高容量的设计收敛,低功耗、混合信号与先进节点设计,以及signoff 分析等各方面获得的可预测性、可生产性、可调整性,以及灵活性。

除了改进的性能和容量,Encounter 数字实现系统还提供了硅虚拟原型、硅片面积估算及RTL 和物理综合的新技术,实现了对设计流程早期可预测性及性能优化方面的改进。

Encounter 数字实现系统可提供多种IC 实现方案,让设计师在时序收敛、布局面积和功耗之间做权衡。

另外,它还引入了多项新的、改进的实现与设计收敛技术,包括硅片面积探索与自动化布局综合、端到端mulTI-mode mulTI-corner 优化、variaTIon-tolerant 和低功耗时钟树及时钟网综合、高容量布局和优化、32nm 布线和基于制造考量的优化、signoff-driven 的实现以及flip chip 设计等特性,以及实现由简至难、层级式的设计的Active-logic 降低技术(ART)。

Encounter 数字实现系统的先进节点技术,包括光刻、CMP、统计漏电功。

SoC-Encounter设计流程ppt

SMIC 65nm process

2024/8/14

2011-10-24

主要内容

1. Initial_design 2. Floorplan 3. Pre_place 4. Place_opt 5. Clock_syn 6. Clock_opt 7. Nano_route

命令:

loadCPF $cpf_file

commitCPF

2024/8/14

1.Initial_design

MMMC:

MMMC=multi-mode and multi-corner 即多角多模分析法

一般情况下有以下几种分析方法:

Full MMMC(完全方法)

分析所有工作模式下的最好最坏角点。

#### scan trace and generate original scan def

:输出扫描链

另外还有specifyScanCell(指定扫描单元)和specifyScanChain(指定名称和输入输出端 口)命令等。

2024/8/14

1.Initial_design

Load CPF file:

normal_setup2_max_dcw_view normal_setup1_max_dcw_view} \

-hold { normal_func2_min_dcb_view }

#### set analysis mode

:设置时序分析模式

setAnalysisMode -analysisType onChipVariation \

根据上面产生的模式组合和角点组合,结合时间的情况及方法,生成能够切实代表时序分析情况的 view组合。一般情况下,每次进行时序分析和优化时,只激活部分的view进行操作,使用的命令为: set_analysis_view。下次再进行分析和优化时再激活别的部分view进行操作。

cadence工具介绍

标签:cadence工具介绍主要是cadence的常用工具:(一)System&LogicDesign&Verification1、SPW:系统仿真工具,与matlab相似,但是比其专业,用于系统建模,常用于通信系统2、Incisive:就是大家最常用的nc_verilog,nc_sim,nc_lauch,以及ABV,TBV的集合,仿真和验证功能很强大(二)Synthesis&Place&Route1、BuildGates:与DC同期推出的综合工具,但是在国内基本上没有什么市场,偶尔有几家公司用2、RTLCompliler:继BuildGates之后的一个综合工具,号称时序,面积和功耗都优于DC,但是仍然无法取代人们耳熟能详的DC3、SiliconEnsemble&PKS:硅谷早期做物理设计的工程师,几乎都用它。

是第一个布局布线工具4、FirstEncounter&SoCEncounter:继SE以后的很好的P&R工具,但是盗版太少,所以也只有大公司能用且都用,但是目前astro在国内有赶超之意5、Cetlic:噪声分析工具,权威6、Fire&Ice:分布参数提取工具,国内很多人用synopsys的StarRC7、VoltageStrom:静态功耗和动态功耗分析的很不错的工具,与s的PowerComplier相同。

8、SingnalStrom:时序分析工具,唯一一个能建库的工具9、nanoroute:很强大的布线器喔,但是不是一般人能用的到的。

我也是在cadence实习的时候爽过的,比astro快十倍不止。

(三)customICDesign1、Virtoso:版图编辑工具,没有人不知道吧,太常用了,现在还有一个公司的laker2、diva,dracula,assura:物理验证工具,用的比较普遍,但是calibre是标准,很多公司都是用其中的一个和calibre同时验证,我好可怜,现在只能用herculus(四)数模混合信号设计这部分太多了,但是一个ADE的环境基本上都能包括,不细说了,打字都打累了(五)PCBAllego最为典型了,很多大公司都用的。

Cadence工具简介

Cadence工具简介1,逻辑设计与验证工具* 逻辑仿真工具: Cadence NC-Verilog, Verilog-XL, NCSim,Simvision Waveform Viewer* 综合工具: Cadence BuildGates* 形式验证工具: VerplexLEC2.综合布局布线工具SoC Encounter—可应用于如90nm及其以下的SOC设计;△ SE-PKS—可应用于如复杂时序收敛的IC设计;△ Fire & Ice QX and SignalStorm—可应用于3维电阻电容参数提取及延时计算;△ VoltageStorm—可应用于功耗分析;△ CeltIC—可应用于信号完整性分析。

3 system level design工具综合(Hardware Design System 2000)算法验证(SPW)△ 结构设计工具(SystemC-based simulators, CoWare, etc)△ 硬件/软件混合设计工具(Verification Platform, Seamless, etc)△ 模拟/混合信号工具(AMS, Agilent ADS, etc)4,CIC(layout & custom layout) 全定制集成电路布局设计工具△ Virtuoso Layout Editor△ Assura (Layout verification)5,AMS (analog mixed signal, RF analysis and design)模拟集成电路设计工具。

AnalogDesignEnvironment。

MixedSignal Design Environment。

Analog Modeling with Verilog-A。

Spectre Circuit Simulator6,HS-PSD(high speed PCB system design) 高速系统和板极设计工具o Concept HDL Front-to-Back Design Flow –原理图输入工具o PCB Librarian –器件建库工具o Allegro PCB Layout System – PCB板布局布线工具o Specctra AutoRoute Basics –基本自动布线器o Advanced Specctra Autorouting Techniques –高级自动布线器o SpecctraQuest Foundations –信号完整性仿真工具o Advanced SpecctraQuest Techniques –高级信号仿真工具*VerilogHDL 仿真工具 Verilog-XL*电路设计工具 Composer电路模拟工具 Analog Artist*版图设计工具 Virtuoso Layout Editor版图验证工具 Dracula 和 Diva*自动布局布线工具 Preview 和 Silicon Ensembleform:Mr Bond coms-chip expert设计任务 EDA工具功能仿真和测试 a. Cadence, NC_simb. Mentor ModelSim (调试性能比较突出)c. Synopsys VCS/VSSd. Novas Debussy (仅用于调试)逻辑综合 a. Synopsys, DCb. Cadence, BuildGatesc. Mentor, LeonardoDFT a. Mentor, DFTAdvisorb. Mentor, Fastscanc. Mentor, TestKompressd. Mentor, DFTInsighte. Mentor, MBISTArchitectf. Mentor, LBISTArchitectg. Mentor, BSDArchitecth. Mentor, Flextesti. Synopsys, DFT Complierj. Synopsys, Tetra MAXk. Synopsys, BSD Complier布局,时钟树综合和自动布线a. Cadence, Design Plannerb. Cadence, CT-Genc. Cadence, PKSd. Cadence, Silicon Ensemblee. Synopsys, Chip Architectf. Synopsys, Floorplan Managerg. Synopsys, Physical Complier & Apolloh. Synopsys, FlexRoute网表提取及RC参数提取物理验证a. Mentor, xCalibreb. Cadence, Assure RCXc. Synopsys, Star-RCXTd. Mentor, Calibree. Synopsys, Herculef. Cadence, Assure延时计算与静态时序分析a. Synopsys, Prime Timeb. Cadence, Pearlc. Mentor, SST Velocity形式验证 a. Mentor, FormalProb. Synopsys, Formalityc. Cadence, FormalCheck功能优化与分析 a. Synopsys, Power Compilerb. Synopsys, PowerMill-ACEHDLQA a. TransEDA, Verification Navigatorb. Synopsys, LEDAFPGA开发 a. Mentor, FPGAdvantageb. XILINX, ISEc. Altera, QuartusIISoC开发 a. Mentor, Seamless CVEb. Cadence, SPWc. Synopsys, Co-Centric版图设计工具 a. Cadence, Virtuosob. Mentor, IC-Stationc. 思源科技, Laker电路级仿真 a. Mentor, ELDOb. Mentor, ADMSc. Cadence, Spectre, Spectre RFd. Cadence, AMSe. Synopsys, Star-Hspice以下只是个人和本公司的评价,不一定十分全面,仅供参考。

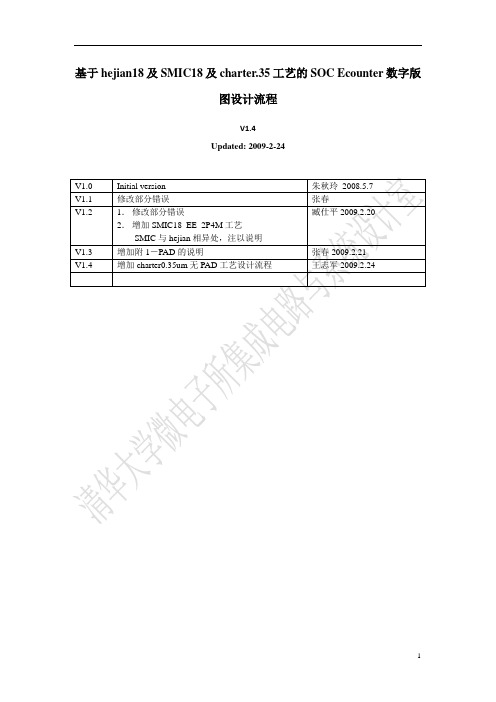

改进版-Soc Encounter数字版图V1.4

基于hejian18及SMIC18及charter.35工艺的SOC Ecounter数字版图设计流程V1.4Updated: 2009-2-24目录1 文件准备(异) (4)1.1 库文件的准备 (4)1.2 根据设计自己准备的文件 (5)2 运行软件 (8)3 Design_import(异) (9)4Load DEF文件和IO file 文件 (12)5 Global Net Connection (13)6 FloorPlan (14)7 Add Power Rings (16)8 Add Stripes (可选) (17)9 Placement Blockage (可选) (18)10 Placement (19)11 Special Route (SRoute) (20)12 Creat clock tree spec (21)14 Post–CTS Optimization (24)15 Trail Routing (25)16 Nano Routing (26)17 IO Filling (27)18 Add Filling (28)19 Post–Route Optimization (29)20 生成SDF时序文件 (30)21 Verify connectivity (31)22 Verify Geometry (32)23 Export Files(异) (33)24 版图验证——导入ICFB(异) (38)1 HEJIAN18 (38)2 SMIC18 (40)3 charter0.35 (40)25 DRC(异) (41)1 HEJIAN18 (41)2 SMIC18 (42)3 charter0.35 (42)26 LVS (43)1 HEJIAN18 (43)2 SMIC (45)3 charter0.35 (45)27 后仿真 (47)28 版图体会 (48)附一关于umc18工艺库IO PAD的使用 (49)附二charter0.35进行图层转换(24步:版图验证—导入ICFB)时的Hercules文件及map文件 (50)1 文件准备(异)1.1 库文件的准备对于 SOC Encounter而言后端设计所需的数据主要有是Foundry厂提供的标准单元和I/O Pad的库文件,它包括物理库、时序库,分别以.lef、.tlf(或者.lib,更好)的形式给出,其中I/O Pad 的相关库文件只有在做有Pad的版图时才需要,否则不需要。

VLSI EDA布局布线总结报告

VLSI EDA布局布线总结报告指导教师:xxxxxxxxxx组员:xxxxxxxxxxxxxxxxxxxxxx设计内容:CFI Flash Controller一.物理设计流程物理设计的输入是电路的元件说明和网表,其输出是设计好的版图。

物理设计主要包括布图规划(floorlan)、电源规划(powerplan)、布局(Placement )、时钟树综合(clock tree)、布线(routing)、验证仿真到流片。

如图:二.存储器控制器的物理设计1.数据准备该阶段为物理设计作准备,包括时序约束文件(.sdc)、布图要求文件(.conf)、I/O文件(.io)和相应的物理库文件(.lef)、时序库文件(.lib),并输入到布图规划的工具环境中来,为其后的布局和布线做好准备。

2.写出CFI_CTRL.v文件,通过dc综合文件(综合文件如下图),生成CFI_CTRL.sdc文件:综合文件增加如下改动:# compilecompile -map_effort medium > $log_path/compile.logset current design CFI_CTRL# report timingsource $scr_path/report.tcl# insert testing# source $scr_path/dft.tclsetverilogout_no_tri trueset_fix_multiple_port_nets -buffer_constants -allchange_names -hier -rule verilogwrite -f db -hier -o $db_path/$current_design.dbwrite -f verilog -hier -o $netlist_path/$current_design.vwrite_sdc $netlist_path/$current_design.sdcwrite_sdf $netlist_path/$current_design.sdfsetmodulename CFI_CTRLread_file -f verilog "$src_path/CFI_CTRL.v $netlist_path/cfi_ctrl.v"setcurrent_design CFI_CTRLuniquifylinkcheck_design> $log_path/check_design.log#write unmapped designwrite -f db -hier -o $db_path/$modulename-no-map.dbwrite -f db -hier -o $db_path/$current_design.dbwrite -f verilog -hier -o $netlist_path/$current_design.vwrite_sdc $netlist_path/$current_design.sdcwrite_sdf $netlist_path/$current_design.sdf将生成的.sdc文件中做如下改动:3.布局规划(floorplan):(1)I/O PAD :I/O PAD 可以分为功能I/O PAD 和电源I/O PAD 两种。

Encounter使用入门教程

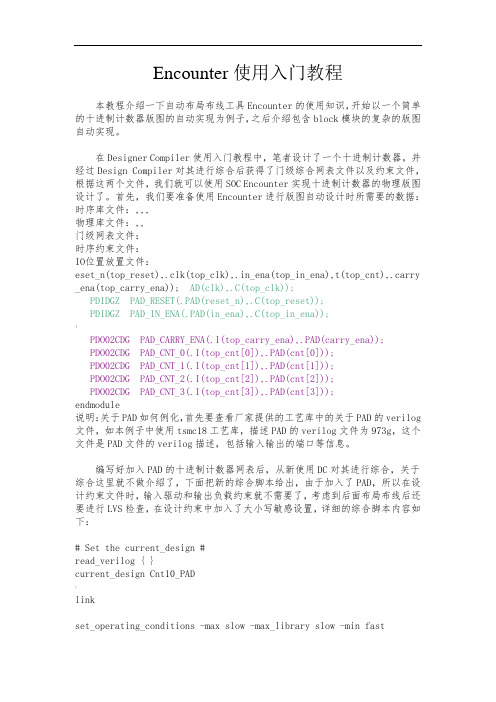

Encounter使用入门教程本教程介绍一下自动布局布线工具Encounter的使用知识,开始以一个简单的十进制计数器版图的自动实现为例子,之后介绍包含block模块的复杂的版图自动实现。

在Designer Compiler使用入门教程中,笔者设计了一个十进制计数器,并经过Design Compiler对其进行综合后获得了门级综合网表文件counter.sv 以及约束文件counter.sdc,根据这两个文件,我们就可以使用SOC Encounter 实现十进制计数器的物理版图设计了。

首先,我们要准备使用Encounter进行版图自动设计时所需要的数据:时序库文件:fast.lib,slow.lib,tpz973gwc.lib,tpz973gbc.lib物理库文件:tsmc18_6lm_cic.lef,tpz973g_5lm_cic.lef,tsmc18_6lm_antenna_cic.lef 门级网表文件:pad_counter.sv时序约束文件:pad_counter.sdcIO位置放置文件:pad_counter.io //在设计导入Encounter中指定PAD的放置位置文件,不是必须文件还有其它一些文件在后面用到时进行介绍。

一、网表中添加PAD、编写IO Assignment File这里,pad_counter.sv是加入PAD后综合得到的门级网表。

工程项目中设计制作完成后的芯片要进行封装,PAD就是芯片在封装时连接封装引线的地方。

一般信号输入/输出PAD即I/O PAD要在综合前添加进入网表中,电源电压PAD可以在综合时添加也可以在综合后添加。

接下来就先介绍一下如何在网表中加入PAD,其实给网表加入PAD就是一般的module例化,和Verilog中一般的module 模块例化是一样的。

这里介绍在综合时给设计中加入I/O PAD。

十进制计数器的Verilog源程序如下:module Cnt10(reset_n,clk,in_ena,cnt,carry_ena);input clk;input reset_n;input in_ena;output [3:0] cnt;output carry_ena;reg [3:0] cnt;reg carry_ena;always @(posedge clk or negedge reset_n)beginif(!reset_n)cnt<=4'b0;else if(in_ena && cnt==4'd10)cnt<=4'b0;else if(in_ena && cnt<4'd10)cnt<=cnt+1'b1;endalways @(posedge clk or negedge reset_n)beginif(!reset_n)carry_ena<=1'b0;else if(in_ena && cnt==4'd10)carry_ena<=1'b1;elsecarry_ena<=1'b0;endendmodule加入PAD后的十进制计数器Verilog网表如下:module Cnt10_PAD(reset_n,clk,in_ena,cnt,carry_ena); //顶层模块input reset_n;input clk;input in_ena;output [3:0] cnt;output carry_ena;wire top_clk,top_reset,top_in_ena;wire top_carry_ena;wire [3:0] top_cnt;Cnt10CNT10(.reset_n(top_reset),.clk(top_clk),.in_ena(top_in_ena),.cnt(top_cnt),.carry_ena (top_carry_ena)); //这里是对Cnt10 module的例化//下面是I/O PAD module的例化PDIDGZ PAD_CLK(.PAD(clk),.C(top_clk));PDIDGZ PAD_RESET(.PAD(reset_n),.C(top_reset));PDIDGZ PAD_IN_ENA(.PAD(in_ena),.C(top_in_ena));PDO02CDG PAD_CARRY_ENA(.I(top_carry_ena),.PAD(carry_ena));PDO02CDG PAD_CNT_0(.I(top_cnt[0]),.PAD(cnt[0]));PDO02CDG PAD_CNT_1(.I(top_cnt[1]),.PAD(cnt[1]));PDO02CDG PAD_CNT_2(.I(top_cnt[2]),.PAD(cnt[2]));PDO02CDG PAD_CNT_3(.I(top_cnt[3]),.PAD(cnt[3]));endmodule说明:关于PAD如何例化,首先要查看厂家提供的工艺库中的关于PAD的verilog 文件,如本例子中使用tsmc18工艺库,描述PAD的verilog文件为tpz973g.v,这个文件是PAD文件的verilog描述,包括输入输出的端口等信息。

Encounter使用方法

Encounter使用入门教程本教程介绍一下自动布局布线工具Encounter的使用知识,开始以一个简单的十进制计数器版图的自动实现为例子,之后介绍包含block模块的复杂的版图自动实现。

在Designer Compiler使用入门教程中,笔者设计了一个十进制计数器,并经过Design Compiler对其进行综合后获得了门级综合网表文件counter.sv以及约束文件counter.sdc,根据这两个文件,我们就可以使用SOC Encounter实现十进制计数器的物理版图设计了。

首先,我们要准备使用Encounter进行版图自动设计时所需要的数据:时序库文件:fast.lib,slow.lib,tpz973gwc.lib,tpz973gbc.lib物理库文件:tsmc18_6lm_cic.lef,tpz973g_5lm_cic.lef,tsmc18_6lm_antenna_cic.lef 门级网表文件:pad_counter.sv时序约束文件:pad_counter.sdcIO位置放置文件:pad_counter.io //在设计导入Encounter中指定PAD的放置位置文件,不是必须文件还有其它一些文件在后面用到时进行介绍。

一、网表中添加PAD、编写IO Assignment File这里,pad_counter.sv是加入PAD后综合得到的门级网表。

工程项目中设计制作完成后的芯片要进行封装,PAD就是芯片在封装时连接封装引线的地方。

一般信号输入/输出PAD即I/O PAD要在综合前添加进入网表中,电源电压PAD 可以在综合时添加也可以在综合后添加。

接下来就先介绍一下如何在网表中加入PAD,其实给网表加入PAD就是一般的module例化,和Verilog中一般的module 模块例化是一样的。

这里介绍在综合时给设计中加入I/O PAD。

十进制计数器的Verilog源程序如下:module Cnt10(reset_n,clk,in_ena,cnt,carry_ena);input clk;input reset_n;input in_ena;output [3:0] cnt;output carry_ena;reg [3:0] cnt;reg carry_ena;always @(posedge clk or negedge reset_n)beginif(!reset_n)cnt<=4'b0;else if(in_ena && cnt==4'd10)cnt<=4'b0;else if(in_ena && cnt<4'd10)cnt<=cnt+1'b1;endalways @(posedge clk or negedge reset_n)beginif(!reset_n)carry_ena<=1'b0;else if(in_ena && cnt==4'd10)carry_ena<=1'b1;elsecarry_ena<=1'b0;endendmodule加入PAD后的十进制计数器Verilog网表如下:module Cnt10_PAD(reset_n,clk,in_ena,cnt,carry_ena); //顶层模块input reset_n;input clk;input in_ena;output [3:0] cnt;output carry_ena;wire top_clk,top_reset,top_in_ena;wire top_carry_ena;wire [3:0] top_cnt;Cnt10CNT10(.reset_n(top_reset),.clk(top_clk),.in_ena(top_in_ena),.cnt(top_cnt),.carry_ena (top_carry_ena)); //这里是对Cnt10 module的例化//下面是I/O PAD module的例化PDIDGZ PAD_CLK(.PAD(clk),.C(top_clk));PDIDGZ PAD_RESET(.PAD(reset_n),.C(top_reset));PDIDGZ PAD_IN_ENA(.PAD(in_ena),.C(top_in_ena));PDO02CDG PAD_CARRY_ENA(.I(top_carry_ena),.PAD(carry_ena));PDO02CDG PAD_CNT_0(.I(top_cnt[0]),.PAD(cnt[0]));PDO02CDG PAD_CNT_1(.I(top_cnt[1]),.PAD(cnt[1]));PDO02CDG PAD_CNT_2(.I(top_cnt[2]),.PAD(cnt[2]));PDO02CDG PAD_CNT_3(.I(top_cnt[3]),.PAD(cnt[3]));endmodule说明:关于PAD如何例化,首先要查看厂家提供的工艺库中的关于PAD的verilog 文件,如本例子中使用tsmc18工艺库,描述PAD的verilog文件为tpz973g.v,这个文件是PAD文件的verilog描述,包括输入输出的端口等信息。

第十一讲 数字后端电路实现-布局布线与验证

以上命令在dc_shell-t>的状态下执行

逻辑综合——补充

• 编写脚本文件后,可以直接执行

– dc_shell-t>source 脚本文件名

• 除了tcl方式,还可以采用其他方式使用DC • 对于综合后的网表和时序,应当进行仿真 • 使用man、help、sold获取dc使用的帮助

布局布线——流程综述

后端设计

布局布线 Soc Encounter

DRC和LVS

RC参数提取

dracula

N

Timing Ok?

Tape out

Cell-based ASIC

怎样实现自动布局布线?对标准单元有什么要求?

?

综合出来的网表对应于哪个部分? 还缺少什么?

Cell-based ASIC

简单的布局布线流程

时序驱动的布局布线流程

逻辑综合——tcl脚本文件

(接上页) write -output top.db -hier write_script -full_path_lib_name -output top.constr write_constraints -format sdf-v2.1 -max_path_timing -max_paths 1000 -output top_constr.sdf set verilogout_single_bit "true" write top -format verilog -output top_post.v -hier write_sdf -context verilog top.sdf

布局布线——启动

• 在工作目录命令行输 入:

encounter

• 图形界面从菜单 design 选择 菜单项 design import • 在design import对话 框中填入相应文件

基于Encounter软件的布局布线_

导出GDSⅡ

共44页 44

谢谢大家!

共44页

45

共44页

7

Design Import对话框中Design栏

共44页 8

Core Spec Defaults栏

在Core Spec Defaults栏目中: Spect Ratio为芯片的高度和宽度之比; Core Utilization是芯片的利用率; Core to left:芯片到左边I/O边缘的距离; Core to right:芯片到右边I/O边缘的距离; Core to top:芯片到上边边I/O边缘的距离; Core to bottom:芯片到下边I/O边缘的距离; 设置Core到I/O边缘的距离大于零是为了给后面布电源和地线留出空间来。

共44页 10

Power栏

Power/Ground Nets/Power Nets中填入设计需要的电源名称; Power/Ground Nets/Ground Nets中填入设计需要的地线名称; 在后面布电源线和地线的时候会用到;如果设计中有多组电源和地, 比如电源有VDDC、 VDDO、VDDH和地VSSC,、VSSO、VSSH,就分别都填上去,中 间用一个空格隔开。

共44页 18

添加了横竖STRIPES后的版图

共44页 19

SROUTE

布好CORE 的电源和地 线后,就可 以给标准单 元布电源和 地线,通过 Route / SRoute设置

共44页 20

Basic / Net (s) 中填入给标准 单元供电的电 源地线。 Route一栏选 择要连接该组 电源地线的选 项。 Layer Change Control中Top layer和Bottom layer分别填入 用到的库的最 高金属层次和 最低金属层次。 Sroute对话框

Cadence后端实验系列15布局布线SoCEncouter

5、creat power ring

在power里选择power planing→add rings会弹出add ring对话框

将值设为1

选上选项,将number of bits设 为3

6、placement

• place→standard cells

里面的参数我们用默认值,1

然后place→place Flip I/O

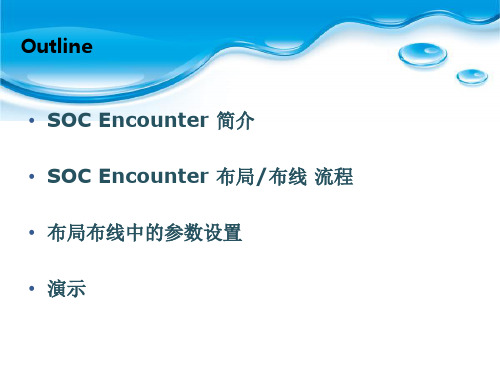

Outline

• SOC Encounter 简介 • SOC Encounter 布局/布线 流程 • 布局布线中的参数设置 • 演示

SOC Encounter 简介

SOC Encounter是cadence数字集成电路设计平台的 一个集成的后端工具,功能相当强大,可以从综合,一 直做到生成GDSII文件!当然里面集成了很多的工具,如 RC,Nanoroute,FIRE&ICE QXC等。支持超过5000万门 180纳米以下工艺的层次化设计。

7、Route route→nanoroute

选上timing driven和 SI driven

选择attribute,修改参数

选上ture,意思是 route as short as possible

Weight, spacing都 设为1

得到最后的布线图

参考文献

➢ SOC encounter user guide ➢ 台湾经典培训教材-SOC Encounter

SOC Encounter 布局/布线 流程

IO,电源和地的布置

指定平面布置图 平面布置图

电源的规划

电源布线

布线

输入文件

• 逻辑和时序库:TLF或.lib • 物理库:库交换格式(.LEF) • 门级网表:*.v • 时序约束:*.sdc • IO assignment file:*.io

第讲CellbasedIC设计方法(自动图设计)剖析

通过该标志选择 Bottom_Core_Boundary

点击 应用

2020/11/11

15

Floorplan: Relative Floorplan

先好RAM256块,点击 get selected

选择

点击 应用

2020/11/11

16

Floorplan: Relative Floorplan

先好RAM128块, 点击get

selected

点击 应用

选好RAM256块, 点击get

selected

2020/11/11

17

Floorplan: Relative Floorplan

点击 应用

先选好PLL块, 点击get selected

选择

2020/11/11

18

Floorplan: Edit Halos

2020/11/11

在弹出的对话 框中点Load,

选择 dtmfLef.conf。

9

SOC的使用: Floorplan

设计建立 Design Setup 布局规划 Floorplan 电源规划 Power plan 布置 Placement 时钟树综合 CTS 布线 Routing

2020/11/11

2020/11/11

5

启动SOC Encounter

2020/11/11

进入工作目 录,打入启

动命令 encounter

6

2020/11/11

7

Design Improt

Design-> Design Import 把一些库文件等导 入设计。

2020/11/11

VLSI设计课件七自动布局布线及SOC简介

Soc基本特征: SOC是VLSI技术的最新产物。 SOC是实现现代电子系统的重要途径。 SOC技术涉及: 集成电路制造技术; 设计技术; 电子系统设计理论; 软件工程等。 SOC芯片采用超深亚微米(VDSM)或纳米IC制造技术。 SOC的复杂性!绝大多数设计厂商不可能覆盖全部技术领域,不可 能也没有必要在设计上完全采用自主设计方法。 大量采用IP核来完成设计已成为一种趋势。

③

时钟树综合

在芯片版图设计中,时钟树的设计是非常重要的,数字系统中一切的电路行 为都是在时钟的严格同步下进行的。 系统中的时钟负载很大,而且遍布整个芯片。这样就造成了较大的本地时钟 间的相对延时,也叫时钟偏斜 (Clock Skew) ,时钟偏斜严重影响电路的同步, 会造成时序紊乱。

延时

延时最大

④

布线

布线是根据电路连接的关系,在满足工艺规则和电学性能 的要求下,在指定的区域内完成所需的全部互连,同时尽 可能地对连线长度和通孔数目进行优化。 完成预布线以后,一些特定网络的布线,如时钟、总线等 一些关键路径需要严格保证其时序要求;在布线中,这些 关键路径的布线被赋予较高的优先级,有时甚至进行手工 布线。 全局布线 布线工具首先把版图区域划分为不同的布线单元,同 时建立布线通道; 对连线的网络连接方向和占用的布线资源(布线通道和 过孔)、连线的最短路径等进行确定; 对布线的拥塞程度进行估计,调整连线网络过度拥塞 的部分。

a)

设计规则检查(DRC, Design Rule Check)

设计规则是以器件的特征尺寸为基准,根据制造工艺水平及其它考虑, 制定出的一整套关于各掩膜相关层上图形自身尺寸及图形间相对尺寸的 允许范围。 设计规则检查则是检查版图中各掩膜相关层上图形的各种尺寸,保证无 一违反规定的设计规则。 设计规则的范围很宽,项目繁多,但其中多数规则是关于图形边与边之 间的距离规范,包括宽度检查、面积检查、内间距检查和外间距检查。

SOC_encounter使用说明

Power Planning and Routing

点击菜单栏Power 图:

Power Planning

Add Rings, 如下

• ’Ring Configuration‘ 选项设置电源地环所用的金属层及其宽度、间距信

息。如上图,本例中环的上下左右部分分别采用Metal6, Metal6, Metal5, Metal5。因为考虑到高层金属的电阻较小,电源环通常采用较高层金属,以尽量 减小电压降。 金属宽度Width: 都设为10um; 间距Spacing;点 击 ’update‘以更新; offset: 设电源金属环位于pad和core的中间,即 选’Center in channel‘项,如下图:

Import design

1. 运行“encounter”命令启动软件SOC Encounter。

如图:

2. 菜单栏Design

Import Design, 打开后如下:

3. 点‘load’键选中之前保存的设置文件V1_X.conf,各项按上次保存

的路径加入相应的文件,加完后如下图:

4. 不同于3,或者直接给各项加入文件,具体如下:

(4)给’Advanced’中RC Extraction选项填入如下文件:

(5)给’Advanced‘中SI Analysis项填入如下噪声库.cdB文件:

上述各项填好后,点’save’将此次的设置保存成.conf文件,然

后点击’OK‘键即可导入设计,如下图:

Floorplan

点击菜单栏Floorplan

电源环的 具体参数 需根据设 计特点设 定。

• “Advanced” 选项中’Wire Group‘选择:’Use wire group‘, ‘Interleaving’, Number of bits: 本例中设为2, 即将电源地环分为 互相交叉的2条,具体形式可根据需要调节。如下图:

复旦大学-集成电路设计-设计流程

–集成电路设计流程与EDA软件•半定制设计流程•全定制设计流程–选择EDA设计工具的原则–主要的EDA Vendor工具特色–集成电路设计流程与EDA软件•半定制设计流程•全定制设计流程–选择EDA设计工具的原则–主要的EDA Vendor工具特色迭代性2与3可互换LVS/DRC1. 设计输入硬件描述语言设计输入,任何文本编辑工具–如:Ultraedit (IDM Computer Solutions 公司); vi (Linux 文本编辑工具)–仿真器自带编辑器…计规范检查:LEDA (Synopsys )-增强了设计人员检查HDL 代码的能力,包括可综合性,可仿真性、可测试性和可重用性Logic Design Flow2、逻辑综合–Synopsys:Design Compiler;380到500个综合库198890 %ASIC设计师选用1年的license 83万RMBLogic Design Flowdesign entryPhysical Design FlowDesign & timing SetupFloor Planning布图规划:包括裸片大小的规划、I/O规划、电源规划、大量硬核或模块(hard core、block)的规划等,是对芯片内部结构的完整规划和设计。

布图规划的合理与否直接关系到芯片的时序收敛、布线通畅。

CTSCTS步骤中,需要对设计的时钟分布有大体的了解,buffer tree的级数,时钟的skew等分为全局布线(global routing )、详细布线(detailrouting )和布线修正(search and repair )。

RoutingDesign For Manufacturability(DFM)保证芯片能被foundry正确制造:1.天线效应修补:如果某一层的一个信号线过长,在制造过程中可能会吸收大量的电荷,从而造成栅氧化层击穿。

一般工具软件会使信号跳层或者插入反偏二极管来消除;2.单孔变多孔:布线完成后不同层的金属在连接处都只用了单一孔来进行连接,这样接触电阻大,而且如果制造出问题时容易断路。

Encounter数字版图设计流程-2010-4-24_730405883

基于umc18工艺的SOC Encounter数字版图设计流程 ——组合逻辑电路数字版图设计V1.12010.4.23一、文件的准备 (2)1.1库文件的准备 (2)1.2根据设计准备所需文件 (2)二、运行软件 (3)三、版图设计流程 (3)3.1Design_import (3)3.2Global Net Connection (5)3.3 FloorPlan (6)3.4 Add Power Rings (8)3.5Add Stripes (9)3.6Placement Blockage (9)3.7 Placement (9)3.8 Special Route (SRoute) (10)3.9 Trail Routing (12)3.10 Nano Routing (13)3.11 Add Filling (14)3.12 Verify connectivity (14)3.13 Verify Geometry (15)3.14 Export Files (17)四、源文件 (18)五、修改记录 (18)一、文件的准备1.1库文件的准备对于SOC Encounter而言,后端设计所需的主要有由Foundry厂所提供的标准单元和I/O Pad 的库文件,它包括物理库、时序库,分别以.lef、.tlf(或者.lib)的形式给出,其中I/O Pad 的相关库文件只有在做有Pad的版图时才需要。

本次实验设计的32位乘法器是组合逻辑电路,不需要时序约束文件。

本次设计中不包括Pad,因此不需要I/O库。

对于umc18的工艺,版图设计所需要的库文件在服务器上的路径如下:/software/course_lib_umc18/umc18_6lm.lef (标准单元)1.2根据设计准备所需文件完整的时序电路数字版图设计所包括的文件有:Verilog网单,sdc时序文件,def电源pad 声明文件,io位置说明文件。

IC后端流程(初学必看)

校外IC后端实践报告本教程通过对synopsys公司给的lab进行培训,从verilog代码到版图的整个流程(当然只是基本流程,因为真正一个大型的设计不是那么简单就完成的),此教程的目的就是为了让大家尽快了解数字IC设计的大概流程,为以后学习建立一个基础。

此教程只是本人探索实验的结果,并不代表内容都是正确的,只是为了说明大概的流程,里面一定还有很多未完善并且有错误的地方,我在今后的学习当中会对其逐一完善和修正。

此后端流程大致包括一下内容:1.逻辑综合(工具DC 逻辑综合是干吗的就不用解释了把?)2.设计的形式验证(工具formality)形式验证就是功能验证,主要验证流程中的各个阶段的代码功能是否一致,包括综合前RTL 代码和综合后网表的验证,因为如今IC设计的规模越来越大,如果对门级网表进行动态仿真的话,会花费较长的时间(规模大的话甚至要数星期),这对于一个对时间要求严格(设计周期短)的asic设计来说是不可容忍的,而形式验证只用几小时即可完成一个大型的验证。

另外,因为版图后做了时钟树综合,时钟树的插入意味着进入布图工具的原来的网表已经被修改了,所以有必要验证与原来的网表是逻辑等价的。

3.静态时序分析(STA),某种程度上来说,STA是ASIC设计中最重要的步骤,使用primetime对整个设计布图前的静态时序分析,没有时序违规,则进入下一步,否则重新进行综合。

(PR后也需作signoff的时序分析)4.使用cadence公司的SOCencounter对综合后的网表进行自动布局布线(APR)5.自动布局以后得到具体的延时信息(sdf文件,由寄生RC和互联RC所组成)反标注到网表,再做静态时序分析,与综合类似,静态时序分析是一个迭代的过程,它与芯片布局布线的联系非常紧密,这个操作通常是需要执行许多次才能满足时序需求,如果没违规,则进入下一步。

6.APR后的门级功能仿真(如果需要)7.进行DRC和LVS,如果通过,则进入下一步。

Encounter使用入门教程

Encounter使用入门教程本教程介绍一下自动布局布线工具Encounter的使用知识,开始以一个简单的十进制计数器版图的自动实现为例子,之后介绍包含block模块的复杂的版图自动实现。

在Designer Compiler使用入门教程中,笔者设计了一个十进制计数器,并经过Design Compiler对其进行综合后获得了门级综合网表文件以及约束文件,根据这两个文件,我们就可以使用SOC Encounter实现十进制计数器的物理版图设计了。

首先,我们要准备使用Encounter进行版图自动设计时所需要的数据:时序库文件:,,,物理库文件:,,门级网表文件:时序约束文件:IO位置放置文件:eset_n(top_reset),.clk(top_clk),.in_ena(top_in_ena),t(top_cnt),.carry _ena(top_carry_ena)); AD(clk),.C(top_clk));PDIDGZ PAD_RESET(.PAD(reset_n),.C(top_reset));PDIDGZ PAD_IN_ENA(.PAD(in_ena),.C(top_in_ena));(PDO02CDG PAD_CARRY_ENA(.I(top_carry_ena),.PAD(carry_ena));PDO02CDG PAD_CNT_0(.I(top_cnt[0]),.PAD(cnt[0]));PDO02CDG PAD_CNT_1(.I(top_cnt[1]),.PAD(cnt[1]));PDO02CDG PAD_CNT_2(.I(top_cnt[2]),.PAD(cnt[2]));PDO02CDG PAD_CNT_3(.I(top_cnt[3]),.PAD(cnt[3]));endmodule说明:关于PAD如何例化,首先要查看厂家提供的工艺库中的关于PAD的verilog 文件,如本例子中使用tsmc18工艺库,描述PAD的verilog文件为973g,这个文件是PAD文件的verilog描述,包括输入输出的端口等信息。

使用Encounter进行电路布局布线

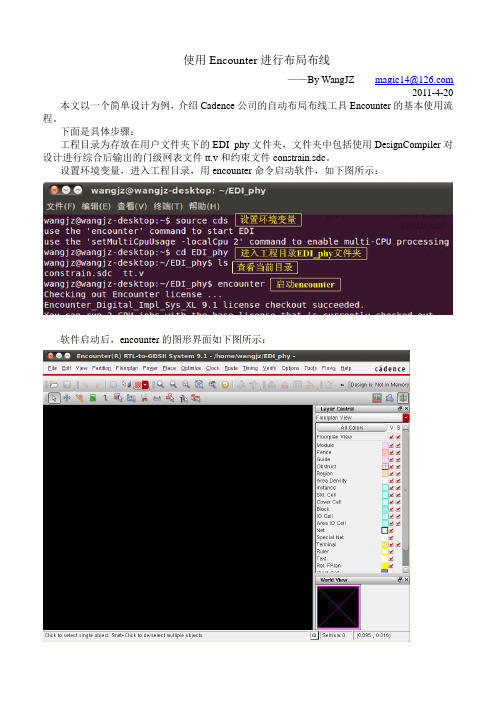

使用Encounter进行布局布线——By WangJZ magic14@2011-4-20 本文以一个简单设计为例,介绍Cadence公司的自动布局布线工具Encounter的基本使用流程。

下面是具体步骤:工程目录为存放在用户文件夹下的EDI_phy文件夹,文件夹中包括使用DesignCompiler对设计进行综合后输出的门级网表文件tt.v和约束文件constrain.sdc。

设置环境变量,进入工程目录,用encounter命令启动软件,如下图所示:软件启动后,encounter的图形界面如下图所示:导入设计文件,如下所示。

其他选项可暂时不填,保持默认设置,点击确认按钮。

成功导入设计文件后,Encounter视图如下所示:定义设计的尺寸、长宽比等信息,如下所示:完成后如下图所示,Core区和IO边缘有10um的距离。

添加全局连线,此处主要是电源和地的全局连线,分别把VDD的pin、net和高电平连接到全局连线VDD,把VSS的pin、net和低电平连接到全局连线VSS,如下所示:添加电源环,如下所示:填入电源环的宽度、距离、使用的金属层等信息,点击确认后,电源环添加到Core区和IO 边缘之间的空间,如下所示:添加core区中标准单元的电源连线,如下所示:添加电源连线后,视图如下所示:放置标准单元,然后切换到版图视图,可看到标准单元放置后的效果,如下所示:接着进行时钟树综合,可使用手动编写的时钟树配置文件或者用软件自动生配置文件进行时钟树综合。

此处采用软件自动生成配置文件的方式,如下所示:时钟树综合的同时会进行版图的初始布线。

完成时钟树综合后,进行版图的详细布线,如下所示:详细布线采用默认设置即可,完成详细布线后效果图如下:如果只是进行Encounter的学习,到此处即可保存并输出结果。

如果是要进行实际的流片生产,还需对各层进行填充,包括标准单元填充和各个金属层的填充,以保证满足生产所需的密度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

• place→standard cells →

里面的参数我们用默认值,1

然后place→place Flip I/O → 然后

7、Route 、 route→nanoroute →

选上timing driven和 SI driven

选择attribute,修改参数 , 选择

选上ture,意思是 route as short as possible

SOC Encounter 布局 布线 流程 布局/布线

IO,电源和地的布置

指定平面布置图

平面布置图

电源的规划

电源布线

布线

输入文件

• 逻辑和时序库:TLF或.lib • 物理库:库交换格式(.LEF) • 门级网表:*.v • 时序约束:*.sdc • IO assignment file:*.io

Weight, spacing都 设为1 得到最后的布线图参考文献

SOC encounter user guide 台湾经典培训教材-SOC Encounter 台湾经典培训教材 ——Cell-Based IC Physical Design and Verification-SOC Encounter

Import design

添加所有的输入文 件

3、在advanced的power里添加 VDD advanced的power里添加

GND

4、布图规划floorplan 、布图规划 一开始有默认值, 一开始有默认值,但我们需要对自动布局的结果进来 手工调整。 手工调整。 Floorplan→specify Floorplan → 我们需要芯片具体的尺寸要求改变里面的数值。 我们需要芯片具体的尺寸要求改变里面的数值。 改为1 将Ratio(H/W) 改为 改为0.5 将core utilization改为 改为 改为10 将core to left /right/top/bottom 改为

SOC Encouter布局布线 布局布线

2011.01.10

Outline

• SOC Encounter 简介 • SOC Encounter 布局 布线 流程 布局/布线 • 布局布线中的参数设置 • 演示

SOC Encounter 简介

SOC Encounter是cadence数字集成电路设计平台的 一个集成的后端工具,功能相当强大,可以从综合,一 直做到生成GDSII文件!当然里面集成了很多的工具,如 RC,Nanoroute,FIRE&ICE QXC等。支持超过5000万门 180纳米以下工艺的层次化设计。

Thank you! !

I/O assignment file I/O assignment file 是可选的输入文件,它可以 用来指示工具放置IO引脚(在一个块级设计)或IO单元 (在芯片级设计),指示芯片pad的分布。如果希望工具 来自动确定这些位置,您可以将该字段留空。它需要输入 一个.def或.io格式的文件,如果没有这个文件,布局工具 将根据实例网表的自动的决定设计的尺寸,而IO的引脚也 将随机的分布。

SOC Encounter同Silicon Ensemble一样,也 是Cadence的自动布线工具。对Silicon Ensemble 而言,最多可以做到0.18的工艺,到0.18工艺以 下,必须使用SOC Encounter。其实,对于0.25以 上工艺,使用SOC Encounter将会大大方便整个后 端设计。

5、creat power ring 、 rings会弹出 会弹出add 在power里选择power planing→add rings会弹出add power里选择power 里选择 ring对话框 ring对话框

将值设为1

选上选项,将number of bits设 为3

6、placement 、

SOC Encounter采用层次化设计功能将芯片分割成 多个小块,以便单独进行设计,再重新进行组装。SOC Encounter首先读入RTL或门级网表,并快速构建可准确代 表最终芯片(包括时序、布线、芯片大小,功耗和信号完整 性)的芯片“虚拟原型”。通过使用物理虚拟原型功能,设 计师可以快速验证物理可行性并在逻辑上进行必要更改。

布局布线设计流程

1、登录服务器,进入终端,输入:encounter ,进入soc encounter

这里输入命令: encounter,就可以启 用soc encounter软件

用户界面

2、调入门级网表和库 、 网表文件: 网表文件:bin/accu_synth.v 约束文件: 约束文件:bin/accu.sdc 时序库: 时序库: hjtc18_ff.lib hjtc18_ss.lib hjtc18_tt.lib IO约束文件:bin/accu.io 约束文件: 约束文件