495040中文资料

4550N;中文规格书,Datasheet资料

/

ห้องสมุดไป่ตู้

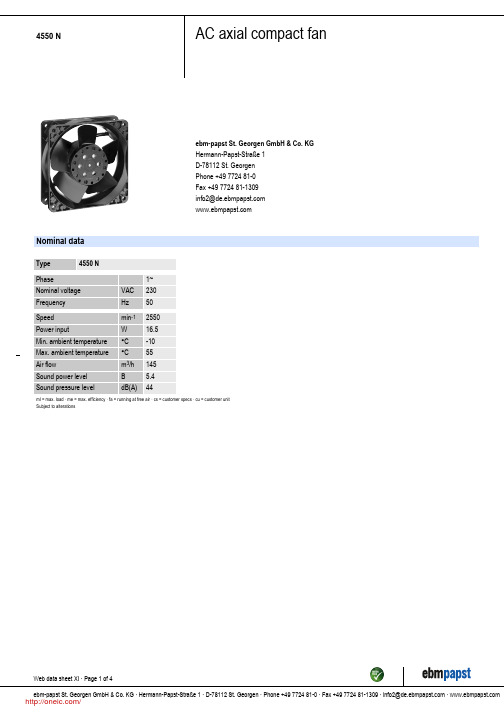

4550 N

AC axial compact fan

Charts: Air flow

(in H ² O) 0,05 0,10 0,15 0,20

∆ pf ä

Pa

60

45

30

15

0

20

40

60

80

CFM m³/h

Vä

•

25

50

75

100

125

Web data sheet XI · Page 4 of 4 ebm-papst St. Georgen GmbH & Co. KG · Hermann-Papst-Straße 1 · D-78112 St. Georgen · Phone +49 7724 81-0 · Fax +49 7724 81-1309 · info2@ ·

/

4550 N

AC axial compact fan

Technical features

General description AC voltage fan with external rotor shaded-pole motor. Protected from overload by impedance protection. Fan housing and fan impeller made of metal. Inlet over bars. Rotational direction clockwise looking at rotor. Types 4890 N and 4840 N air exhaust over bars. Electrical connection to 2 flat plugs 3.0 x 0.5 mm. Impeller with 3 or 5 blades, see note for fan type. Optionally available: variants with reinforced mounting flanges and single strands that are brought out. Fan housing with grounding lugs with M4 and UNC thread. Mass 550 g. Please note our new ACmaxx series. With identical fastening dimensions and voltages, this series achieves higher energy efficiency. 0.550 kg 119 x 119 x 38 mm Metal Metal Inlet over bars Right, looking at rotor Sintec sleeve bearing system 42500 h 30000 h 2 flat plugs 3.0 x 0.5 mm. Housing with grounding lugs for screw M4 and UNC. Protected from overload using impedance protection VDE, CSA, UL, CE

5404中文资料

TL F 64945404 DM5404 DM7404 Hex Inverting GatesJune1989 5404 DM5404 DM7404Hex Inverting GatesGeneral DescriptionThis device contains six independent gates each of whichperforms the logic INVERT functionFeaturesY Alternate Military Aerospace device(5404)is availableContact a National Semiconductor Sales Office Distrib-utor for specificationsConnection DiagramDual-In-Line PackageTL F 6494–1Order Number5404DMQB 5404FMQB DM5404J DM5404W DM7404M or DM7404NSee NS Package Number J14A M14A N14A or W14BFunction TableY e AInputs OutputA YL HH LH e High Logic LevelL e Low Logic LevelC1995National Semiconductor Corporation RRD-B30M105 Printed in U S AAbsolute Maximum Ratings(Note)If Military Aerospace specified devices are required please contact the National Semiconductor Sales Office Distributors for availability and specifications Supply Voltage7V Input Voltage5 5V Operating Free Air Temperature RangeDM54and54b55 C to a125 C DM740 C to a70 C Storage Temperature Range b65 C to a150 C Note The‘‘Absolute Maximum Ratings’’are those values beyond which the safety of the device cannot be guaran-teed The device should not be operated at these limits The parametric values defined in the‘‘Electrical Characteristics’’table are not guaranteed at the absolute maximum ratings The‘‘Recommended Operating Conditions’’table will define the conditions for actual device operationRecommended Operating ConditionsSymbol ParameterDM5404DM7404Units Min Nom Max Min Nom MaxV CC Supply Voltage4 555 54 7555 25V V IH High Level Input Voltage22V V IL Low Level Input Voltage0 80 8V I OH High Level Output Current b0 4b0 4mA I OL Low Level Output Current1616mA T A Free Air Operating Temperature b55125070 C Electrical Characteristicsover recommended operating free air temperature range(unless otherwise noted)Symbol Parameter Conditions MinTypMax Units (Note1)V I Input Clamp Voltage V CC e Min I I e b12mA b1 5VV OH High Level Output V CC e Min I OH e Max2 43 4VVoltage V IL e MaxV OL Low Level Output V CC e Min I OL e Max0 20 4VVoltage V IH e MinI I Input Current Max V CC e Max V I e5 5V1mA Input VoltageI IH High Level Input Current V CC e Max V I e2 4V40m AI IL Low Level Input Current V CC e Max V I e0 4V b1 6mAI OS Short Circuit V CC e Max DM54b20b55mA Output Current(Note2)DM74b18b55I CCH Supply Current with V CC e Max612mA Outputs HighI CCL Supply Current with V CC e Max1833mA Outputs LowSwitching Characteristics at V CC e5V and T A e25 C(See Section1for Test Waveforms and Output Load) Symbol Parameter Conditions Min Max Unitst PLH Propagation Delay Time C L e15pF22ns Low to High Level Output R L e400Xt PHL Propagation Delay Time15ns High to Low Level OutputNote1 All typicals are at V CC e5V T A e25 CNote2 Not more than one output should be shorted at a time23Physical Dimensions inches(millimeters)14-Lead Ceramic Dual-In-Line Package(J)Order Number5404DMQB or DM5404JNS Package Number J14A4Physical Dimensions inches(millimeters)(Continued)14-Lead Small Outline Molded Package(M)Order Number DM7404MNS Package Number M14A14-Lead Molded Dual-In-Line Package(N)Order Number DM7404NNS Package Number N14A55404 D M 5404 D M 7404H e x I n v e r t i n g G a t e sPhysical Dimensions inches (millimeters)(Continued)14-Lead Ceramic Flat Package (W)Order Number 5404FMQB or DM5404WNS Package Number W14BLIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION As used herein 1 Life support devices or systems are devices or 2 A critical component is any component of a life systems which (a)are intended for surgical implant support device or system whose failure to perform can into the body or (b)support or sustain life and whose be reasonably expected to cause the failure of the life failure to perform when properly used in accordance support device or system or to affect its safety or with instructions for use provided in the labeling can effectivenessbe reasonably expected to result in a significant injury to the userNational Semiconductor National Semiconductor National Semiconductor National Semiconductor CorporationEuropeHong Kong LtdJapan Ltd1111West Bardin RoadFax (a 49)0-180-530858613th Floor Straight Block Tel 81-043-299-2309。

LCK4950资料

Data Sheet November 2001LCK4950Low-Voltage PLL Clock DriverFeaturess Fully integrated phase-locked loop (PLL)s Oscillator or crystal reference input s Output frequency up to 180 MHz s Outputs disable in high impedancesCompatible with PowerPC ®, Intel ®, and high-performance RISC microprocessors s TQFP packagings Output frequency configurable s ±35ps typical cycle-to-cycle jittersPin compatible with the Motorola ® MPC950 clock driverDescriptionThe LCK4950 is a PLL-based clock driver device intended for high-performance clock tree designs. The LCK4950 is 3.3V compatible with outputfrequencies of up to 180MHz and output skews of 200ps. The LCK4950 can accommodate the most demanding tree designs by employing a fullydifferential PLL design. This minimizes cycle-to-cycle jitter, which is critical when the device is acting as the reference clock for PLLs in today ’s microprocessors and ASICs. The device has nine low-skewconfigurable outputs for support of the clocking needs of the various high-performance microprocessors.To provide input reference clock flexibility, two selectable division ratios are available on theLCK4950. The internal V CO runs at either 2x or 4x the high-speed output. The FBSEL pin is used to select between a divide by 8 or a divide by 16 of the V CO frequency to be compared with the inputreference. These selections allow the input reference to be either one-half, one-fourth, or one-eighth of the high-speed output.The LCK4950 is capable of scan clock distribution or system diagnostics due to an external test clock input. The REF_SEL pin allows the selectionbetween a crystal input to an on-chip oscillator for the reference or selection of a TTL level oscillator input directly. Only a parallel resonant crystal is required for the onboard crystal oscillator external components.The LCK4950 is fully 3.3V compatible and requires no external loop filter components. All inputs accept LVCMOS or LVTTL compatible levels while theoutputs provide LVCMOS levels with the capability to drive terminated 50 Ω transmission lines. TheLCK4950 can drive two traces, giving the device an effective fan out of 1:18 for series-terminated 50 Ω lines. For optimum performance and board density, the device is packaged in a 7 mm x 7 mm 32-lead TQFP package.2Agere Systems Inc.Data Sheet November 2001Low-Voltage PLL Clock Driver LCK4950Description (continued)5-9698 (F)Figure 1. Logic Diagramfsela PLL_En Tclk Ref_Selxtal1xtal2FBsel (PULL-DOWN)fselbfselc MR/OEfseldPOWER-ON RESET÷4/÷8÷4/÷8÷4/÷8÷2/÷4QaQbQc0Qc1Qd0Qd1Qd2Qd3Qd4(V CO )200 MHz —480 MHzPHASE DETECTORLPF ÷8/÷16xtal OSCAgere Systems Inc.3Data SheetNovember 2001Low-Voltage PLL Clock DriverLCK4950Pin Information5-9699 (F)Figure 2. Pin DiagramFunctional DescriptionTable 1. Function TablesRef_SelFunction 1TCLK 0XTAL_OSC PLL_EnFunction 1PLL Enabled 0PLL Bypass FBsel Function 1÷80÷16MR/OE Function 1Outputs Disabled 0Outputs Enabled fseln Function1Qa =÷4; Qb:d = ÷80Qa =÷2; Qb:d = ÷4LCK49502526272829303132161514131211109876543211718192021222324V SS Qb V DD QaV SS TCLK PLL_En Ref_SelV S S Q d 1V D DQ d 0V S SQ c 1V D DQ c 0Qd2V DD Qd3V SSQd4V DD MR/OE xtal2x t a l 1V S Sf s e l df s e l cf s e l bf s e l aF B s e lV D D A4Agere Systems Inc.Data Sheet November 2001Low-Voltage PLL Clock Driver LCK4950Functional Description (continued)Table 2. Function TableNote: x =fVCO/4; 200MHz <fVCO <480MHz.Table 3. PLL Input Reference Characteristics*Maximum and minimum input reference is limited by the V CO lock range and the feedback divider for the TCLK or xtal1 inputs.†See the Applications section for more crystal information.InputsOutputs Totals fsela fselb fselc fseld Qa(1)Qb(1)Qc(2)Qd(5)Total 2xTotal x Total x/200002x x x x 18000012x x x x/213500102x x x/2x 16200112x x x/2x/211701002x x/2x x 17101012x x/2x x/212601102x x/2x/2x 13501112x x/2x/2x/21081000x x x x 0901001x x x x/20451010x x x/2x 0721011x x x/2x/20271100x x/2x x 0811101x x/2x x/20361110x x/2x/2x 0631111xx/2x/2x/218CharacteristicSymbol Min Max Unit TCLK Input Rise/Fallst r , t f — 3.0ns Reference Input Frequency f ref —*—*MHz Crystal Oscillator Frequency †f Xtal 12.525MHz Reference Input Duty Cyclef refdc2575%Agere Systems Inc.5Data SheetNovember 2001Low-Voltage PLL Clock DriverLCK4950ApplicationsProgramming the LCK4950SSeveral frequency relationships are configurable by the LCK4950. Frequency ratios of 1:1, 2:1, 4:1, and 4:2:1 are possible from configuring the output dividers for the four output groups. To ensure that the output duty cycle is always 50%, the LCK4950 uses even dividers. Table 4 illustrates output configurations of the LCK4950, describing the outputs using the V CO frequency as a reference. For example, setting the Qa outputs to V CO /2, the Qb and Qc to V CO /4, and the Qd to V CO /8 would provide the output frequency relationship of 4:2:1.Table 4. Programmable Output Frequency RelationshipsThe division settings establish the output relationship, but one must still ensure that the V CO will be stable given the frequency of the outputs desired. The feedback frequency should be used to situate the V CO into a frequency range in which the PLL will be stable. The design of the PLL is such that for output frequencies between 25 MHz and 180 MHz, the LCK4950 can generally be configured into a stable region.InputsOutputsFSELA FSELB FSELC FSELD Qa Qb Qc Qd 0000V CO /2V CO /4V CO /4V CO /40001V CO /2V CO /4V CO /4V CO /80010V CO /2V CO /4V CO /8V CO /40011V CO /2V CO /4V CO /8V CO /80100V CO /2V CO /8V CO /4V CO /40101V CO /2V CO /8V CO /4V CO /80110V CO /2V CO /8V CO /8V CO /40111V CO /2V CO /8V CO /8V CO /81000V CO /4V CO /4V CO /4V CO /41001V CO /4V CO /4V CO /4V CO /81010V CO /4V CO /4V CO /8V CO /41011V CO /4V CO /4V CO /8V CO /81100V CO /4V CO /8V CO /4V CO /41101V CO /4V CO /8V CO /4V CO /81110V CO /4V CO /8V CO /8V CO /41111V CO /4V CO /8V CO /8V CO /86Agere Systems Inc.Data Sheet November 2001Low-Voltage PLL Clock Driver LCK4950Applications (continued)Table 5. Input Reference vs. Output Frequency Relationships The relationship between the input reference and the output frequency is very flexible. Table 5 shows themultiplication factors between the inputs and outputs for the LCK4950. Figure 3 through Figure 6 illustrate several programming possibilities.Note:The variations of the configurations shown are not complete, but do represent potential applications.Config fsela fselb fselc fseldFB_Sel = 1FB_Sel = 0QaQb Qc Qd Qa Qb Qc Qd 100004x 2x 2x 2x 8x 4x 4x 4x 200014x 2x 2x x 8x 4x 4x 2x 300104x 2x x 2x 8x 4x 2x 4x 400114x 2x x x 8x 4x 2x 2x 501004x x 2x 2x 8x 2x 4x 4x 601014x x 2x x 8x 2x 4x 2x 701104x x x 2x 8x 2x 2x 4x 801114x x x x 8x 2x 2x 2x 910002x 2x 2x 2x 4x 4x 4x 4x 1010012x 2x 2x x 4x 4x 4x 2x 1110102x 2x x 2x 4x 4x 2x 4x 1210112x 2x x x 4x 4x 2x 2x 1311002x x 2x 2x 4x 2x 4x 4x 1411012x x 2x x 4x 2x 4x 2x 1511102x x x 2x 4x 2x 2x 4x 1611112xxxx4x2x2x2xAgere Systems Inc.7Data SheetNovember 2001Low-Voltage PLL Clock DriverLCK4950Applications (continued)5-9700 (F)Figure 3. Dual-Frequency Configuration 5-9701 (F)Figure 4. Dual-Frequency Configuration66.66 MHz33.33 MHz33.33 MHz66.66 MHzfsela fselb fselc fseld FBselQdQcQbQaINPUT REF16.66 MHz 00111112533.33 MHz66.66 MHz66.66 MHz66.66 MHzfsela fselb fselc fseld FBselQdQcQbQaINPUT REF33.33 MHz 1110011255-9702 (F)Figure 5. Dual-Frequency Configuration5-9703 (F)Figure 6. Triple-Frequency Configuration33.33 MHz33.33 MHz33.33 MHz66.66 MHzfsela fselb fselc fseld FBselQdQcQbQaINPUT REF16.66 MHz 0111112540 MHz40 MHz80 MHz160 MHzfsela fselb fselc fseld FBselQdQcQbQaINPUT REF20 MHz 010011125Absolute Maximum RatingsStresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.Table 6. Absolute Maximum RatingsParameterSymbol Min Max Unit Supply Voltage V DD , V DDA–0.3 4.6V Input Voltage V I –0.3V DD + 0.3V Input CurrentI IN —±20mA Storage Temperature RangeT Stor–40125°C8Agere Systems Inc.Data Sheet November 2001Low-Voltage PLL Clock Driver LCK4950Electrical CharacteristicsTable 7. dc CharacteristicsT A = 0 °C to 70 °C, V CC = 3.3V ± 5%.Table 8. ac CharacteristicsT A = 0 °C to 70 °C, V CC = 3.3V ± 5%.CharacteristicSymbol Min Typ Max Unit Condition Input High Voltage (LVCMOS inputs)V IH 2.0— 3.6V —Input Low Voltage (LVCMOS inputs)V IL ——0.8V —Output High Voltage V OH 2.4——V I OH = –40 mA 11.The LCK4950 outputs can drive series or parallel-terminated 50 Ω (or 50 Ω to V CC /2) transmission lines on the incident edge.Output Low Voltage V OL ——0.5V I OL = 40mA 1Input CurrentI IN ——±120µA —Input CapacitanceC IN ——4pF —Power Dissipation CapacitanceC pd —25—pF Per Output Maximum Quiescent Supply Current Non-PLLI DDQ ——1mA AllV DD Pins Except V DDA 22.Total power = (I DDPLL + I DDQ ) x V + (fQaCQa + fQbCQb + fQc0CQc0 + fQc1CQc1 + fQd0CQd0 + fQd1CQd1 + fQd2CQd2 + fQd3CQd3 +fQd4CQd4) x V 2; where V = V DD, CQa = load capacitance on Qa, CQb = load capacitance on Qb, etc.Maximum PLL Supply CurrentI DDPLL——55mAV DDA Pin OnlyCharacteristicSymbol Min Typ Max Unit Condition Output Rise/Fall Time t r , t f 0.10— 1.0ns 0.8V to 2.0VOutput Duty Cycle t pw 48.5—52.5%—Same FrequenciesOutput-to-Output Skews t sk(0)—150300ps —Different Frequencies:Qa fmax < 150MHz Qa fmax > 150MHz——200—400400ps ps ——PLL V CO (feedback = V CO /4)Lock (feedback = V CO /8)Range (feedback = V CO /16)f VCO200200200———480480480MHz MHz MHz ———Maximum Output Frequency:Qa(÷2)Qa/Qb (÷4)Qb (÷8)f max——————18012060MHz MHz MHz ———Output Disable Time t PLZ,HZ ——7ns —Output Enable Timet PZL ——6ns —Cycle-to-Cycle Jitter (peak-to-peak)t jitter —±35±50ps —11.See Applications section for more information.Maximum PLL Clock Timet lock——10ms—LCK4950 Data SheetNovember 2001Low-Voltage PLL Clock Driver Electrical Characteristics (continued)Jitter Performance of the LCK4950SMore focus is given to clock distribution design and management today because of the continuing increase of today’s digital system’s clock rates. System-clock jitter and its effect on overall system timing budget is at the center of this focus. The LCK4950 is designed to utilize a differential CMOS PLL and incorporate multiple power and ground pins in the design to minimize clock jitter. The following text provides details on the jitter performance, illustrates measurement limitations, and provides guidelines to minimize the jitter of the LCK4950.The most commonly specified jitter parameter is cycle-to-cycle jitter. With today’s high-performance measurement equipment, there is no way to measure this parameter for jitter performance in the class demonstrated by the LCK4950. As a result, different methods are used which approximate cycle-to-cycle jitter. The typical method of measuring the jitter is to accumulate a large number of cycles, create a histogram of the edge placements, and record peak-to-peak as well as standard deviations of the jitter. It is of great importance to measure the edge immediately following the trigger edge. If this is not the case, the measurement inaccuracy will add significantly to the measured jitter. The oscilloscope cannot collect adjacent pulses. It is safe to assume that collecting pulse information in this mode will produce jitter values somewhat larger than if consecutive cycles were measured; therefore, this measurement will represent an upper bound of cycle-to-cycle jitter. Most likely, this is a conservative estimate of the cycle-to-cycle jitter.There are two common sources of jitter for a PLL-based clock driver. The most common source of jitter is random jitter. Less commonly known is the jitter produced by different frequency outputs switching synchronously. If all of the outputs are switching at the same frequency, the PLL jitter is equal to the total jitter of the device. In theLCK4950, where a number of the outputs can be switching synchronously but at different frequencies, a multimodal jitter distribution can be seen on the highest frequency outputs. It is important to consider what is happening on the other outputs because the output being monitored is affected by the activity on the other outputs. From Figure7, one can see that for each rising edge on the higher-frequency signal, the activity on the lower-frequency signal is not consistent.The placement of the edge that is being monitored is displaced in time due to the activity on the other outputs altering the internal thresholds of the device. The relationship is periodic because the signals are synchronous. The resulting jitter is a superposition of the PLL jitter on the displaced edges. The multimodal distribution will appear to be a fat Gaussian distribution, or a truly multimodal distribution depending on the size of the PLL jitter and displacement of the edges. When all the outputs are switching at the same frequency, there is no edge displacement and the jitter is that of the PLL.Agere Systems Inc.910Agere Systems Inc.Data Sheet November 2001Low-Voltage PLL Clock Driver LCK4950Electrical Characteristics (continued)5-9704 (F)Figure 7. PLL Jitter and Edge DisplacementAgere Systems Inc.11Data SheetNovember 2001Low-Voltage PLL Clock DriverLCK4950Electrical Characteristics (continued)5-9707 (F)Figure 8. Power Supply FilterPLL jitter can be measured for configurations where the outputs are switching at different frequencies by triggering the lowest-frequency output. PLL jitter is dependent on internal V CO frequency more so than output configuration.There are some general guidelines that will minimize the output jitter of the device. First, always configure the device so the V CO runs as fast as possible. This is the most important aspect in minimizing jitter of the LCK4950. Second, maintain the reference frequency at the highest possible frequency. These more frequent phase detector updates help to reduce jitter. There is a trade-off between higher reference frequencies and higher V CO frequency; always choose a higher V CO frequency to reduce jitter. Third, and the most difficult to follow, minimize the number of different frequencies sourced from a single chip. The fixed edgedisplacement associated with the switching noise, in most cases, nearly doubles the effective jitter of a high-speed output.Power Supply FilteringThe LCK4950 exhibits some sensitivities that would not be seen on a fully digital product because the LCK4950 is a mixed analog/digital product. Analog circuitry is naturally sensitive to random noise, most noticeably when the noise is in the power supply pins. The LCK4950 provides a separate output buffer power supply (V DD ) and phase-locked loop (V DDA ) power supply pins. This design isolates the highswitching noise digital outputs from the sensitive internal analog phase-locked loop. In a controlled setup (i.e., an evaluation board), this amount of isolation will suffice. In a digital system, where it is much more difficult to minimize noise on the power supplies, an additional level of isolation may berequired. The easiest means of accomplishing this is by applying a power supply filter on the V DDA pin for the LCK4950.Figure 8 illustrates a typical power supply filter scheme for the LCK4950. The device is most greatly affected by spectral content in the 1 kHz to 1 MHz range, and therefore needs a filter to target this range. The most important aspect of this final filter design is the dc voltage drop between the V DD supply and V DDA pin. The I DDPLL current (current forced through the V DDA pin) is normally 45mA (55mA maximum), assuming that a minimum of 3.0V must be maintained on the V DDA pin. Very little voltage drop can be tolerated when a 3.3V V DD supply is used. The resistor shown inFigure 10 must have a resistance of 5 Ω—10Ω to meet the voltage drop criteria. The RC filter shown provides a broadband filter with about 100:1 attenuation for noise, with a spectral content above 20kHz. As the noise frequency crosses the series resonant point of an individual capacitor, its overall impedance begins to look inductive and therefore increases with increasing frequency. The parallel capacitor circuit shown in Figure 11 guarantees that a low- impedance path to ground exists for frequencies exceeding the bandwidth of the PLL. It is recommended that the user start with an 8 Ω—10Ω resistor to avoid potential V DD drop problems and only use higher-value resistors when a higher level of attenuation is needed.The LCK4950 has several design features to minimize the susceptibility to power supply noise (isolated power and grounds and fully differential PLL). Still, there may be applications in which overall performance is being degraded due to system power supply noise. The power supply filter schemes discussed in this section should be adequate to eliminate power supply noise-related problems in most designs.0.01 µF22 µFR S =5 Ω—10 ΩV CCPLL_V CCLCK49500.01 µF3.3 V12Agere Systems Inc.Data Sheet November 2001Low-Voltage PLL Clock Driver LCK4950Electrical Characteristics (continued)Using the On-Chip Crystal OscillatorThe LCK4950 features an on-chip crystal oscillator buffer to allow for seed clock generation as well as final distribution. The only external component required is the crystal since the on-chip oscillator buffer is completely self-contained. The user is advised to mount the crystal as close to the LCK4950 as possible to avoid board-level parasitics since the oscillator is, to a degree, sensitive to loading at the inputs. To facilitate collocation, surface-mount crystals are recommended, but not required.The oscillator circuit is a parallel resonant circuit with on-chip shunt capacitors. A parallel resonant crystal is simply a crystal that has been characterized in its parallel resonant mode. Therefore, in the majority of cases, a parallel specified crystal or a series resonant crystal can be used with the LCK4950 with just a minor frequency error.Typically, a series crystal used in a parallel resonant mode will exhibit an oscillatory frequency a few hundred ppm different than the specified value. For most processor implementations, a few hundred ppm translates into kHz inaccuracies, a small enough level not to represent a major issue.The LCK4950 is a clock driver that was designed to generate outputs with programmable frequency relationships. As a result, the crystal input frequency is a function of the desired output frequency. To determine the crystal required to produce the desired output frequency for an application that utilizes internal feedback, the PLL block diagram (Figure 9) should be used. The P and the M values for the LCK4950 are also included in Figure 9. The M values can be found in Table 1 on page 3.Table 9. Crystal SpecificationsParameterValueCrystal Cut Fundamental AT Cut ResonanceParallel Resonance Frequency Tolerance±75ppm at 25 °CFrequency/Temperature Stability ±150ppm at 0 °C to 70 °C Operating Range 0 °C to 70 °C Shunt Capacitors10pF —40pF Equivalent Series Resistance (ESR)50Ω to 80Ω Max Correction Drive Level 100µWAging5ppm/yr (first three years)Agere Systems Inc.13Data SheetNovember 2001Low-Voltage PLL Clock DriverLCK4950Electrical Characteristics (continued)5-9708 (F)Figure 9. PLL Block DiagramNote:For computations refer to the following equations:m = 8 (FBsel = 1), 16(FBsel = 0), P = 1For the LCK4950 clock driver, the following will provide an example of how to determine the crystal frequency required for a given design.Given:Qa = 160MHz Qb = 80MHz Qc = 40MHz Qd = 40MHz FBSel = 0(eq. 1)From Figure 3:fQd = V CO /8 then N = 8 or fQa = V CO /2 then N = 2From Figure 9:m = 16 and P = 1orPHASE DETECTORLPFV CO ÷P ÷N ÷mQnf reff f VCO m-------------f vco fQ =,=f ref fQn N P••m-----------------------------=∴f ref fQn N P ••m -----------------------------=t ref 4081••16------------------------20 MHz ==t ref 16021••16---------------------------20 MHz==14Agere Systems Inc.Data Sheet November 2001Low-Voltage PLL Clock Driver LCK4950Agere Systems Inc.15Data SheetNovember 2001Low-Voltage PLL Clock DriverLCK4950Outline DiagramDimensions are in millimeters.12-3076(F)18 1.60 MAXSEATING PLANEDETAIL A0.101.40 ± 0.050.80 TYP0.05/0.15DETAIL BDETAIL B0.30/0.450.20M0.09/0.200DETAIL APowerPC is a registered trademark of International Business Machines Corporation.Intel is a registered trademark of Intel Corporation.Motorola is a registerd trademark of Motorola, Inc.Copyright © 2001 Agere Systems Inc.All Rights ReservedNovember 2001DS02-033HSI (Replaces DS01-118ANET)Agere Systems Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application.For additional information, contact your Agere Systems Account Manager or the following:INTERNET: E-MAIL:docmaster@N. AMERICA:Agere Systems Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18109-32861-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106)ASIA:Agere Systems Hong Kong Ltd., Suites 3201 & 3210-12, 32/F, Tower 2, The Gateway, Harbour City, KowloonTel. (852) 3129-2000, FAX (852) 3129-2020CHINA: (86) 21-5047-1212 (Shanghai), (86) 10-6522-5566 (Beijing), (86) 755-695-7224 (Shenzhen)JAPAN: (81) 3-5421-1600 (Tokyo), KOREA: (82) 2-767-1850 (Seoul), SINGAPORE: (65) 778-8833, TAIWAN: (886) 2-2725-5858 (Taipei)EUROPE:Tel. (44) 7000 624624, FAX (44) 1344 488 045。

A4950ELJTR-T;APEK4950ELJ-01-T-DK;中文规格书,Datasheet资料

DescriptionDesigned for pulse width modulated (PWM) control of DC motors, the A4950 is capable of peak output currents to ±3.5 A and operating voltages to 40 V .Input terminals are provided for use in controlling the speed and direction of a DC motor with externally applied PWM control signals. Internal synchronous rectification control circuitry is provided to lower power dissipation during PWM operation. Internal circuit protection includes overcurrent protection, motor lead short to ground or supply, thermal shutdown with hysteresis, undervoltage monitoring of V BB , and crossover-current protection.For high ambient operating temperature applications, an automotive grade device is offered (A4950K). The K grade device is tested across extended temperature and voltage ranges to ensure compliance in automotive or industrial applications.The A4950 is provided in a low-profile 8-pin SOICN package with exposed thermal pad (suffix LJ) that is lead (Pb) free, with 100% matte tin leadframe plating.Features and Benefits• Low R DS(on) outputs• Overcurrent protection (OCP)▫ Motor short protection▫ Motor lead short to ground protection ▫ Motor lead short to battery protection • Low Power Standby mode • Adjustable PWM current limit • Synchronous rectification• Internal undervoltage lockout (UVLO) • Crossover-current protection• A4950K is AEC-Q100 Grade 1 qualified• Commercial temperature grade (A4950E: –40°C to 85°C )• Automotive temperature grade (A4950K: –40°C to 125°C)Full-Bridge DMOS PWM Motor DriverPackage: 8-pin SOICN with exposed thermal pad (suffix LJ)Functional Block DiagramNot to scaleA4950Terminal List TableNumberName Function1GND Ground 2IN2Logic input 23IN1Logic input 14VREF Analog input 5VBB Load supply voltage 6OUT1DMOS full bridge output 17LSS Power return – sense resistor connection 8OUT2DMOS full bridge output 2–PADExposed pad for enhanced thermal dissipationPin-out DiagramAbsolute Maximum RatingsCharacteristicSymbol NotesRating Unit Load Supply Voltage V BB 40V Logic Input Voltage Range V IN –0.3 to 6V V REF Input Voltage Range V REF –0.3 to 6V Sense Voltage (LSS pin)V S –0.5 to 0.5V Motor Outputs Voltage V OUT –2 to 42V Output CurrentI OUT Duty cycle = 100% 3.5A Transient Output Current i OUT T W < 500 ns6A Operating Temperature Range T A Temperature Range E –40 to 85°C Temperature Range K–40 to 125°C Maximum Junction Temperature T J (max)150°C Storage Temperature RangeT stg–55 to 150°CSelection GuidePart NumberPackingAmbient Operating Temperature, T AA4950ELJTR-T 3000 pieces per 13-in. reel –40°C to 85°C A4950KLJTR-T3000 pieces per 13-in. reel–40°C to 125°CThermal Characteristics may require derating at maximum conditions, see application informationCharacteristicSymbolTest Conditions*ValueUnitPackage Thermal ResistanceR θJAOn 2-layer PCB with 0.8 in 2. exposed 2-oz. copper each side 62ºC/W On 4-layer PCB based on JEDEC standard35ºC/W*Additional thermal information available on the Allegro website.OUT2LSS OUT1VBBGND IN2IN1VREFELECTRICAL CHARACTERISTICS Valid for Temperature Range E version at T J = 25°C and for Temperature Range Kversion at T J = –40°C to 150°C, V BB = 8 to 40 V, unless otherwise specifiedCharacteristic Symbol Test Conditions Min.Typ.Max.Unit GeneralLoad Supply Voltage Range V BB8–40VR DS(on) Sink + Source Total R DS(on)I OUT = |2.5 A|, T J = 25°C–0.60.8ΩI OUT = |2.5 A|, T J = 150°C– 1.1 1.5ΩLoad Supply Current I BB f PWM < 30 kHz –1020mA Low Power Standby mode––10μABody Diode Forward Voltage V f Source diode, I f = –2.5 A–– 1.5V Sink diode, I f = 2.5 A–– 1.5VLogic InputsLogic Input Voltage RangeV IN(1) 2.0––V V IN(0)––0.8V V IN(STANDBY)Low Power Standby mode––0.4VLogic Input Current I IN(1)V IN = 2.0 V–40100μA I IN(0)V IN = 0.8 V–1640μALogic Input Pull-Down Resistance R LOGIC(PD)V IN = 0 V = IN1 = IN2–50–kΩInput Hysteresis V HYS–250550mV TimingCrossover Delay t COD50–500ns V REF Input Voltage Range V REF0–5VCurrent Gain A V V REF / I SS , V REF = 5 V9.5–10.5V/V V REF / I SS , V REF = 2.5 V9.0–10.0V/V V REF / I SS , V REF = 1 V8.0–10.0V/VBlank Time t BLANK234μs Constant Off-time t off162534μs Standby Timer t st IN1 = IN2 < V IN(STANDBY)–1 1.5ms Power-Up Delay t pu––30μs Protection CircuitsUVLO Enable Threshold V BBUVLO V BB increasing77.57.95V UVLO Hysteresis V BBUVLOhys–500–mV Thermal Shutdown Temperature T JTSD Temperature increasing–160–°C Thermal Shutdown Hysteresis T TSDhys Recovery = T JTSD – T TSDhys–15–°CCharacteristic PerformancePWM Control Timing DiagramPWM Control Truth TableIN1IN210×V S > V REFOUT1OUT2Function01False L H Reverse 10False H L Forward01True H/L L Chop (mixed decay), reverse 10True L H/L Chop (mixed decay), forward 11False L L Brake (slow decay)FalseZZCoast, enters Low Power Standby mode after 1 msNote: Z indicates high impedance.GND GND+I REG0 A-I REGIN1IN2I OUT(x)V IN(1)V IN(1)Functional DescriptionDevice OperationThe A4950 is designed to operate DC motors. The output drivers are all low-R DS(on), N-channel DMOS drivers that feature inter-nal synchronous rectification to reduce power dissipation. The current in the output full bridge is regulated with fixed off-time pulse width modulated (PWM) control circuitry. The IN1 and IN2 inputs allow two-wire control for the bridge.Protection circuitry includes internal thermal shutdown, and pro-tection against shorted loads, or against output shorts to ground or supply. Undervoltage lockout prevents damage by keeping the outputs off until the driver has enough voltage to operate nor-mally.Standby ModeLow Power Standby mode is activated when both input (INx) pins are low for longer than 1 ms. Low Power Standby mode disables most of the internal circuitry, including the charge pump and the regulator. When the A4950 is coming out of standby mode, the charge pump should be allowed to reach its regulated voltage (a maximum delay of 200 μs) before any PWM com-mands are issued to the device.Internal PWM Current ControlInitially, a diagonal pair of source and sink FET outputs are enabled and current flows through the motor winding and the optional external current sense resistor, R S . When the voltage across R S equals the comparator trip value, then the current sense comparator resets the PWM latch. The latch then turns off the sink and source FETs (Mixed Decay mode).V REFThe maximum value of current limiting is set by the selection of R Sx and the voltage at the VREF pin. The transconductance func-tion is approximated by the maximum value of current limiting, I TripMAX (A), which is set by:I TripMAX=10RSVREFwhere V REF is the input voltage on the VREF pin (V) and R S is the resistance of the sense resistor (Ω) on the LSS terminal. Overcurrent ProtectionA current monitor will protect the IC from damage due to output shorts. If a short is detected, the IC will latch the fault and disable the outputs. The fault latch can only be cleared by coming out of Low Power Standby mode or by cycling the power to VBB. Dur-ing OCP events, Absolute Maximum Ratings may be exceeded for a short period of time before the device latches.ShutdownIf the die temperature increases to approximately 160°C, the full bridge outputs will be disabled until the internal temperature falls below a hysteresis, T TSDhys, of 15°C. Internal UVLO is present on VBB to prevent the output drivers from turning-on below the UVLO threshold.BrakingThe braking function is implemented by driving the device in Slow Decay mode, which is done by applying a logic high to both inputs, after a bridge-enable Chop command (see PWM Control Truth Table). Because it is possible to drive current in both direc-tions through the DMOS switches, this configuration effectively shorts-out the motor-generated BEMF, as long as the Chop com-mand is asserted. The maximum current can be approximated by V BEMF / R L. Care should be taken to ensure that the maximum ratings of the device are not exceeded in worse case braking situ-ations: high speed and high-inertia loads.Synchronous RectificationWhen a PWM off-cycle is triggered by an internal fixed off-time cycle, load current will recirculate. The A4950 synchronous rec-tification feature turns-on the appropriate DMOSFETs during the current decay, and effectively shorts out the body diodes with the low R DS(on) driver. This significantly lowers power dissipation. When a zero current level is detected, synchronous rectification is turned off to prevent reversal of the load current.Mixed Decay OperationThe bridges operate in Mixed Decay mode. Referring to the lower panel of the figure below, as the trip point is reached, the device goes into fast decay mode for 50% of the fixed off-time period. After this fast decay portion the device switches to slow decay mode for the remainder of the off-time. During transitions from fast decay to slow decay, the drivers are forced off for the Crossover Delay, t COD. This feature is added to prevent shoot-through in the bridge. During this “dead time” portion, synchro-nous rectification is not active, and the device operates in fast decay and slow decay only.Mixed Decay Mode OperationV PHASE IIApplication InformationSense Pin (LSS)In order to use PWM current control, a low-value resistor is placed between the LSS pin and ground for current sensing pur-poses. To minimize ground-trace IR drops in sensing the output current level, the current sensing resistor should have an indepen-dent ground return to the star ground point. This trace should be as short as possible. For low-value sense resistors, the IR drops in the PCB can be significant, and should be taken into account. When selecting a value for the sense resistor be sure not to exceed the maximum voltage on the LSS pin of ±500 mV at maximum load. During overcurrent events, this rating may be exceeded for short durations.GroundA star ground should be located as close to the A4950 as possible. The copper ground plane directly under the exposed thermal pad of the device makes a good location for the star ground point. The exposed pad can be connected to ground for this purpose. LayoutThe PCB should have a thick ground plane. For optimum electrical and thermal performance, the A4950 must be soldered directly onto the board. On the underside of the A4950 package is an exposed pad, which provides a path for enhanced thermal dis-sipation. The thermal pad must be soldered directly to an exposed surface on the PCB in order to achieve optimal thermal conduc-tion. Thermal vias are used to transfer heat to other layers of the PCB.The load supply pin, VBB, should be decoupled with an electro-lytic capacitor (typically 100 μF) in parallel with a lower valued ceramic capacitor placed as close as practicable to the device.Bill of MaterialsItem Reference Value Units Description1RS0.25(for V REF = 5 V, I OUT = 2 A)Ω2512, 1 W, 1% or better,carbon film chip resistor2C10.22μF X5R minimum, 50 V or greater 3C2100μF Electrolytic, 50 V or greaterPackage LJ, 8-Pin SOICN with exposed thermal padReference land pattern layout (reference IPC7351SOIC127P600X175-9AM); all pads a minimum of 0.20 mm from all adjacent pads; adjust as necessary to meet application processrequirements and PCB layout tolerances; when mounting on a multilayer PCB, thermal vias at the exposed thermal pad land can improve thermal dissipation (reference EIA/JEDEC Standard JESD51-5)PCB Layout Reference ViewCA Terminal #1 mark areaB CFor Reference Only; not for tooling use (reference MS-012BA)Dimensions in millimetersDimensions exclusive of mold flash, gate burrs, and dambar protrusions Exact case and lead configuration at supplier discretion within limits shown Exposed thermal pad (bottom surface); dimensions may vary with deviceRevision HistoryRevision Revision Date Description of RevisionRev. 4August 6, 2012Add AEC qualification; update PWM tableCopyright ©2011-2012, Allegro MicroSystems, Inc.Allegro MicroSystems, Inc. reserves the right to make, from time to time, such de p ar t ures from the detail spec i f i c a t ions as may be required to per-mit improvements in the per f or m ance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.Allegro’s products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.The in f or m a t ion in c lud e d herein is believed to be ac c u r ate and reliable. How e v e r, Allegro MicroSystems, Inc. assumes no re s pon s i b il i t y for its use; nor for any in f ringe m ent of patents or other rights of third parties which may result from its use.For the latest version of this document, visit our website:分销商库存信息:ALLEGROA4950ELJTR-T APEK4950ELJ-01-T-DK。

FCX495TA;FCX495TC;中文规格书,Datasheet资料

FCX495SOT89 NPN silicon planar high voltage transistorFeatures•150 Volt V CEO•1 Amp continuous currentDevice markingN95Absolute maximum ratingsElectrical characteristics (at T amb = 25°C)Parameter Symbol Value Unit Collector-base voltage V CBO 170 V Collector-emitter voltage V CEO 150 V Emitter-base voltage V EBO 5 VContinuous collector current I C1 A Peak pulse current I CM2 A Base current I B 200 mAPower dissipation at T amb = 25°CP tot 1 WOperating and storage temperature range T j :T stg-65 to +150 °C Parameter Symbol Min. Max. Unit Conditions Breakdown voltages V(BR)CBO 170V I C =100µA V CEO(sus) 150 V I C =10mA (*)NOTES:(*)Measured under pulsed conditions. Pulse width = 300s. Duty cycle Յ2%V (BR)EBO 5 V I E =100µACollector cut-off currentsI CBO , I CES 100nA V CB =150V, V CE =150V Emitter cut-off currentI EBO 100nA V EB =4V Emitter saturation voltagesV CE(sat) 0.2V I C =250mA, I B =25mA (*) 0.3VI C =500mA, I B =50mA (*) V BE(sat)1.0 V I C =500mA, I B =50mA (*) Base-emitter turn on voltageV BE(on) 1.0 V I C =500mA, V CE =10V (*)Static forward current transfer ratio h FE100300I C =1mA, V CE =10V 100I C =250mA, V CE =10V (*)50I C =500mA, V CE =10V (*)10I C =1A, V CE =10V (*)Transition frequency f T 100M H z I C =50mA, V CE =10V f=100MHzCollector-base breakdown voltage C obo 10 pF V CB =10V, f=1MHzTypical characteristicsTypical characteristicsIntentionally left blankPackage outline - SOT89DIM Millimeters Inches DIM Millimeters Inches Min Max Min Max Min Max Min MaxA 1.40 1.600.5500.630E 2.29 2.600.0900.102B0.440.560.0170.022E1 2.13 2.290.0840.090 B10.360.480.0140.019e 1.50 BSC0.059 BSC C0.350.440.0140.017e1 3.00 BSC0.118 BSCD 4.40 4.600.1730.181H 3.94 4.250.1550.167D1 1.52 1.830.0640.072L0.89 1.200.0350.047 Note: Controlling dimensions are in millimeters. Approximate dimensions are provided in inchesZetex sales offices EuropeZetex GmbHKustermann-park Balanstraße 59D-81541 München GermanyTelefon: (49) 89 45 49 49 0Fax: (49) 89 45 49 49 49europe.sales@AmericasZetex Inc700 Veterans Memorial Highway Hauppauge, NY 11788USATelephone: (1) 631 360 2222Fax: (1) 631 360 8222usa.sales@Asia PacificZetex (Asia Ltd)3701-04 Metroplaza Tower 1Hing Fong Road, Kwai Fong Hong KongTelephone: (852) 26100 611Fax: (852) 24250 494asia.sales@Corporate HeadquartersZetex Semiconductors plcZetex Technology Park, Chadderton Oldham, OL9 9LL United KingdomTelephone: (44) 161 622 4444Fax: (44) 161 622 4446hq@© 2007 Published by Zetex Semiconductors plcDefinitionsProduct changeZetex Semiconductors reserves the right to alter, without notice, specifications, design, price or conditions of supply of any product or service. Customers are solely responsible for obtaining the latest relevant information before placing orders.Applications disclaimerThe circuits in this design/application note are offered as design ideas. It is the responsibility of the user to ensure that the circuit is fit for the user’s application and meets with the user’s requirements. No representation or warranty is given and no liability whatsoever is assumed by Zetex with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Zetex does not assume any legal responsibility or will not be held legally liable (whether in contract,tort (including negligence), breach of statutory duty, restriction or otherwise) for any damages, loss of profit, business, contract,opportunity or consequential loss in the use of these circuit applications, under any circumstances.Life supportZetex products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Zetex Semiconductors plc. As used herein:A. Life support devices or systems are devices or systems which:1.are intended to implant into the body or2.support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected tocause the failure of the life support device or to affect its safety or effectiveness.ReproductionThe product specifications contained in this publication are issued to provide outline information only which (unless agreed by the company in writing) may not be used, applied or reproduced for any purpose or form part of any order or contract or be regarded as a representation relating to the products or services concerned. Terms and ConditionsAll products are sold subjects to Zetex’ terms and conditions of sale, and this disclaimer (save in the event of a conflict between the two when the terms of the contract shall prevail) according to region, supplied at the time of order acknowledgement.For the latest information on technology, delivery terms and conditions and prices, please contact your nearest Zetex sales office.Quality of productZetex is an ISO 9001 and TS16949 certified semiconductor manufacturer.To ensure quality of service and products we strongly advise the purchase of parts directly from Zetex Semiconductors or one of our regionally authorized distributors. For a complete listing of authorized distributors please visit: /salesnetworkZetex Semiconductors does not warrant or accept any liability whatsoever in respect of any parts purchased through unauthorized sales channels.ESD (Electrostatic discharge)Semiconductor devices are susceptible to damage by ESD. Suitable precautions should be taken when handling and transporting devices.The possible damage to devices depends on the circumstances of the handling and transporting, and the nature of the device. The extent of damage can vary from immediate functional or parametric malfunction to degradation of function or performance in use over time.Devices suspected of being affected should be replaced.Green complianceZetex Semiconductors is committed to environmental excellence in all aspects of its operations which includes meeting or exceeding reg-ulatory requirements with respect to the use of hazardous substances. Numerous successful programs have been implemented to reduce the use of hazardous substances and/or emissions.All Zetex components are compliant with the RoHS directive, and through this it is supporting its customers in their compliance with WEEE and ELV directives.Product status key:“Preview”Future device intended for production at some point. Samples may be available “Active”Product status recommended for new designs “Last time buy (LTB)”Device will be discontinued and last time buy period and delivery is in effect “Not recommended for new designs”Device is still in production to support existing designs and production “Obsolete”Production has been discontinued Datasheet status key:“Draft version”This term denotes a very early datasheet version and contains highly provisional information, whichmay change in any manner without notice.“Provisional version”This term denotes a pre-release datasheet. It provides a clear indication of anticipated performance.However, changes to the test conditions and specifications may occur, at any time and without notice.“Issue”This term denotes an issued datasheet containing finalized specifications. H owever, changes tospecifications may occur, at any time and without notice.分销商库存信息:DIODESFCX495TA FCX495TC。

SD4590中文资料

SD4590RF POWER TRANSISTORS800-960MHz CELLULAR BASE STATIONνGOLD METALLIZATIONνDIFFUSED EMITTER BALLASTING νINTERNAL INPUT/OUTPUT MATCHING νCOMMON EMITTER CONFIGURATIONνDESIGNED FOR LINEAR OPERATION HIGH SATURATED POWER CAPABILITY 26VOLT,900MHz PERFORMANCE νP OUT =150W MIN.GAIN =8.5dB MIN.IMD 3=-28dB MAX.@P OUT =150W PEP νINHERENT RUGGEDNESS:LOAD MISMATCH TOLERANCE OF 5:1MIN.VSWR3dB OVERDRIVE CAPABILITYνESD SENSITIVITY,CLASS 3(MIL STD-883D METHOD 3015)DESCRIPTIONThe SD4590is designed for both analog and digital cellular base stations over the 800to 960MHz frequency range,specifically those systems requiring the high linearity and efficiency afforded by class AB operation.Integrated input/output pre-matching simplifies amplifier design.Ruggedness,MTTF,and linearity are enhanced using diffused emitter resistors and refractory/gold metallization.PIN CONNECTIONMarch 2000ABSOLUTE MAXIMUM RATINGS (T case =25o C)Symbol ParameterValue Unit V CBO Collector-Base Voltage 65V V CEO Collector-Emitter Voltage 28V V EBO Emitter-Base Voltage 3.5V I C Device Current 25A P DISS Power Dissipation300WT j Max.Operating Junction Temperature 200o C T STGStorage Temperature-65to 150oCTHERMAL DATAR th (j-c)Junction-Case Thermal Resistance0.60oC/WM208epoxy sealed®ORDER CODE BRANDING SD4590SD45901.Collector 3.Base2.Emitter1/8ELECTRICAL SPECIFICATION(T case=25o C)STATICSymbol Parameter Min.Typ.Max.Unit BV CBO I C=100mA V BE=0V6580V BV CEO I C=100mA I B=0mA2830V BV CER IC=100mA R BE=80 Ω3340V BV EBO I C=50mA I C=0mA 3.5 4.0VI CEO V CE=26V V BE=0V10mAI CEO V CE=10V V BE=0V0.5mAI EBO V BE=1V V CE=0V0.1mAI EBO V BE=2.5V V CE=0V3mAh FE V CE=5V I C=6A2545120DYNAMICSymbol Parameter Min.Typ.Max.UnitC OB f=1MHz V CB=26Vfor information only-this part is collector matched75pF DYNAMIC(CW)Symbol Parameter Min.Typ.Max.Unit P I N f=900MHz V CE=26V I CQ=2x200mA P OUT=150W21W P OUT f=900MHz V CE=26V I CQ=2x200mA P IN=21W150175WG P f=900MHz V CE=26V I CQ=2x200mA P OUT=150W8.59.5dBηC f=900MHz V CE=26V I CQ=2x200mA P OUT=150W5055% P1dB f=900MHz V CE=26V I CQ=2x200mA150160WOVD f=900MHz V CE=26V I CQ=2x200mA Set P OUT=150W PEP;Increase P IN3dB No Degratation in Device PerformanceDYNAMIC(Two-Tone)Symbol Parameter Min.Typ.Max.Unit *G P V CE=26V I CQ=2x200mA P OUT=150W PEP8.59.5dB *ηC V CE=26V I CQ=2x200mA P OUT=150W PEP3035% *IMD3V CE=26V I CQ=2x200mA P OUT=150W PEP-32-28dBT*Load Mismatch V CE=26V I CQ=2x200mA P OUT=150W PEPVSWR=5:1MIN@All Phase AnglesNo Degratation in DevicePerformance*OVD V CE=26V I CQ=2x200mASet P OUT=150W PEP;Increase P IN3dB No Degratation in Device PerformanceNote:f1=900.00MHzf2=900.10MHz REF1016365ETESTED PER SIDE SD45902/8Output Power vs Input PowerOutput Power vs Supply VoltagePower Gain vs Output PowerOutput Power vs FrequencyIntermodulation Distortion vs Output PowerBroadband PerformanceP O W E R G A I N (d B )TYPICAL PERFORMANCE 860MHz960MHz900MHzVCE =26V I CQ =400mAP IN =36W 36W 30W24W 18W 12W 16W6WP IN =ORDER24W3RD 5TH7TH9TH8WF 1=900.00MHz F 2=900.10MHz V CE =26V I CQ =400mAP GR L ηCFREQ =900MHz I CQ =400mAFREQ =900MHz V CE =26mAIMDI CQ =1200mA900mA 600mA400mA300mAP OUT =150WPEP V CE =26V I CQ =400mAV CE =26V I CQ =400mASD45903/8SERIES EQUIVALENT INPUT/OUTPUT IMPEDANCESFREQ.Z IN (Ω)Z CL (Ω)800MHz 4.25+j 12.25 5.75−j 4.25820MHz 4.75+j 13.25 5.00−j 2.75840MHz 5.25+j 12.50 5.50−j 2.50860MHz 4.75+j 10.25 5.00−j 3.00880MHz 6.25+j 9.00 4.60−j 2.90900MHz 7.75+j 10.25 4.25−j 2.90920MHz 6.50+j 11.50 3.95−j 2.90940MHz 6.50+j 10.25 3.80−j 2.80960MHz 8.50+j 9.50 3.40−j 2.85980MHz 9.25+j 11.50 3.10−j 3.001000MHz8.50+j 13.25 2.75−j 3.15CONDITIONS:V CE =26VI CQ =2X 200mA POUT =150W PEP IMD 3≤-28dBT (∆f1f2=100KHz)NOTE:A =800MHzB =1000MHz(Measured in 10MHz increments)A B BZ IN AZ CLSD45904/8TEST CIRCUIT SCHEMATICPCBROGERS ,εr =2.55,Height =31.25mil 1oz.Cu.Balun 1,250ΩCoaxial Cable Lenght 2.2”attached to 2x 50Ωprinted microstrip transmission lines (see photomaster)C1,C2,C23,C2575pF Ceramic Chip ATC B C3,C4,C21,C222x 47pF Ceramic Chip,ATC B C5,C160.8-8pF Variable,JOHANSON Giga -Trim C6,C9750pF Ceramic Chip,ATC B C7,C1039nF Ceramic Chip,ATCB C8,C11,C24,C2647µF,50V Electrolytic C13,C17100µF,50V Electrolytic C129.1pF,Ceramic Chip,ATC A C14,C1839nF Ceramic Chip (OPTIONAL)C15,C19750pF Ceramic Chip (OPTIONAL)C20 1.3pF Ceramic Chip,ATC B L1,L4,L5,L812Turns,#200AWG,0.15”I.D.(Tight)L2,L3,L6,L74Turns,#20AWG,0.13”I.D.(1:1)R1,R2,R3,R45X 50ΩChip ResistorTEST CIRCUIT COMPONENT PART LIST SD45905/8SD4590TEST CIRCUIT PHOTOMASTER 6/8SD45907/8SD4590Information furnished is believed to be accurate and reliable.However,STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use.No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics.Specification mentioned in this publication are subject to change without notice.This publication supersedes and replaces all information previously supplied.STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is a trademark of STMicroelectronics©2000STMicroelectronics–Printed in Italy–All Rights Reserve dSTMicroelectronics GROUP OF COMPANIESAustralia-Brazil-China-Finland-France-Germany-Hong Kong-India-Italy-Japan-Malaysia-Malta-Morocco-Singapore-Spain-Sweden-Switzerland-United Kingdom-U.S.A.8/8。

A4950KLJTR-T;中文规格书,Datasheet资料

DescriptionDesigned for pulse width modulated (PWM) control of DC motors, the A4950 is capable of peak output currents to ±3.5 A and operating voltages to 40 V .Input terminals are provided for use in controlling the speed and direction of a DC motor with externally applied PWM control signals. Internal synchronous rectification control circuitry is provided to lower power dissipation during PWM operation. Internal circuit protection includes overcurrent protection, motor lead short to ground or supply, thermal shutdown with hysteresis, undervoltage monitoring of V BB , and crossover-current protection.For high ambient operating temperature applications, an automotive grade device is offered (A4950K). The K grade device is tested across extended temperature and voltage ranges to ensure compliance in automotive or industrial applications.The A4950 is provided in a low-profile 8-pin SOICN package with exposed thermal pad (suffix LJ) that is lead (Pb) free, with 100% matte tin leadframe plating.Features and Benefits• Low R DS(on) outputs• Overcurrent protection (OCP)▫ Motor short protection▫ Motor lead short to ground protection ▫ Motor lead short to battery protection • Low Power Standby mode • Adjustable PWM current limit • Synchronous rectification• Internal undervoltage lockout (UVLO) • Crossover-current protection• A4950K is AEC-Q100 Grade 1 qualified• Commercial temperature grade (A4950E: –40°C to 85°C )• Automotive temperature grade (A4950K: –40°C to 125°C)Full-Bridge DMOS PWM Motor DriverPackage: 8-pin SOICN with exposed thermal pad (suffix LJ)Functional Block DiagramNot to scaleA4950Terminal List TableNumberName Function1GND Ground 2IN2Logic input 23IN1Logic input 14VREF Analog input 5VBB Load supply voltage 6OUT1DMOS full bridge output 17LSS Power return – sense resistor connection 8OUT2DMOS full bridge output 2–PADExposed pad for enhanced thermal dissipationPin-out DiagramAbsolute Maximum RatingsCharacteristicSymbol NotesRating Unit Load Supply Voltage V BB 40V Logic Input Voltage Range V IN –0.3 to 6V V REF Input Voltage Range V REF –0.3 to 6V Sense Voltage (LSS pin)V S –0.5 to 0.5V Motor Outputs Voltage V OUT –2 to 42V Output CurrentI OUT Duty cycle = 100% 3.5A Transient Output Current i OUT T W < 500 ns6A Operating Temperature Range T A Temperature Range E –40 to 85°C Temperature Range K–40 to 125°C Maximum Junction Temperature T J (max)150°C Storage Temperature RangeT stg–55 to 150°CSelection GuidePart NumberPackingAmbient Operating Temperature, T AA4950ELJTR-T 3000 pieces per 13-in. reel –40°C to 85°C A4950KLJTR-T3000 pieces per 13-in. reel–40°C to 125°CThermal Characteristics may require derating at maximum conditions, see application informationCharacteristicSymbolTest Conditions*ValueUnitPackage Thermal ResistanceR θJAOn 2-layer PCB with 0.8 in 2. exposed 2-oz. copper each side 62ºC/W On 4-layer PCB based on JEDEC standard35ºC/W*Additional thermal information available on the Allegro website.OUT2LSS OUT1VBBGND IN2IN1VREFELECTRICAL CHARACTERISTICS Valid for Temperature Range E version at T J = 25°C and for Temperature Range Kversion at T J = –40°C to 150°C, V BB = 8 to 40 V, unless otherwise specifiedCharacteristic Symbol Test Conditions Min.Typ.Max.Unit GeneralLoad Supply Voltage Range V BB8–40VR DS(on) Sink + Source Total R DS(on)I OUT = |2.5 A|, T J = 25°C–0.60.8ΩI OUT = |2.5 A|, T J = 150°C– 1.1 1.5ΩLoad Supply Current I BB f PWM < 30 kHz –1020mA Low Power Standby mode––10μABody Diode Forward Voltage V f Source diode, I f = –2.5 A–– 1.5V Sink diode, I f = 2.5 A–– 1.5VLogic InputsLogic Input Voltage RangeV IN(1) 2.0––V V IN(0)––0.8V V IN(STANDBY)Low Power Standby mode––0.4VLogic Input Current I IN(1)V IN = 2.0 V–40100μA I IN(0)V IN = 0.8 V–1640μALogic Input Pull-Down Resistance R LOGIC(PD)V IN = 0 V = IN1 = IN2–50–kΩInput Hysteresis V HYS–250550mV TimingCrossover Delay t COD50–500ns V REF Input Voltage Range V REF0–5VCurrent Gain A V V REF / I SS , V REF = 5 V9.5–10.5V/V V REF / I SS , V REF = 2.5 V9.0–10.0V/V V REF / I SS , V REF = 1 V8.0–10.0V/VBlank Time t BLANK234μs Constant Off-time t off162534μs Standby Timer t st IN1 = IN2 < V IN(STANDBY)–1 1.5ms Power-Up Delay t pu––30μs Protection CircuitsUVLO Enable Threshold V BBUVLO V BB increasing77.57.95V UVLO Hysteresis V BBUVLOhys–500–mV Thermal Shutdown Temperature T JTSD Temperature increasing–160–°C Thermal Shutdown Hysteresis T TSDhys Recovery = T JTSD – T TSDhys–15–°CCharacteristic PerformancePWM Control Timing DiagramPWM Control Truth TableIN1IN210×V S > V REFOUT1OUT2Function01False L H Reverse 10False H L Forward01True H/L L Chop (mixed decay), reverse 10True L H/L Chop (mixed decay), forward 11False L L Brake (slow decay)FalseZZCoast, enters Low Power Standby mode after 1 msNote: Z indicates high impedance.GND GND+I REG0 A-I REGIN1IN2I OUT(x)V IN(1)V IN(1)Functional DescriptionDevice OperationThe A4950 is designed to operate DC motors. The output drivers are all low-R DS(on), N-channel DMOS drivers that feature inter-nal synchronous rectification to reduce power dissipation. The current in the output full bridge is regulated with fixed off-time pulse width modulated (PWM) control circuitry. The IN1 and IN2 inputs allow two-wire control for the bridge.Protection circuitry includes internal thermal shutdown, and pro-tection against shorted loads, or against output shorts to ground or supply. Undervoltage lockout prevents damage by keeping the outputs off until the driver has enough voltage to operate nor-mally.Standby ModeLow Power Standby mode is activated when both input (INx) pins are low for longer than 1 ms. Low Power Standby mode disables most of the internal circuitry, including the charge pump and the regulator. When the A4950 is coming out of standby mode, the charge pump should be allowed to reach its regulated voltage (a maximum delay of 200 μs) before any PWM com-mands are issued to the device.Internal PWM Current ControlInitially, a diagonal pair of source and sink FET outputs are enabled and current flows through the motor winding and the optional external current sense resistor, R S . When the voltage across R S equals the comparator trip value, then the current sense comparator resets the PWM latch. The latch then turns off the sink and source FETs (Mixed Decay mode).V REFThe maximum value of current limiting is set by the selection of R Sx and the voltage at the VREF pin. The transconductance func-tion is approximated by the maximum value of current limiting, I TripMAX (A), which is set by:I TripMAX=10RSVREFwhere V REF is the input voltage on the VREF pin (V) and R S is the resistance of the sense resistor (Ω) on the LSS terminal. Overcurrent ProtectionA current monitor will protect the IC from damage due to output shorts. If a short is detected, the IC will latch the fault and disable the outputs. The fault latch can only be cleared by coming out of Low Power Standby mode or by cycling the power to VBB. Dur-ing OCP events, Absolute Maximum Ratings may be exceeded for a short period of time before the device latches.ShutdownIf the die temperature increases to approximately 160°C, the full bridge outputs will be disabled until the internal temperature falls below a hysteresis, T TSDhys, of 15°C. Internal UVLO is present on VBB to prevent the output drivers from turning-on below the UVLO threshold.BrakingThe braking function is implemented by driving the device in Slow Decay mode, which is done by applying a logic high to both inputs, after a bridge-enable Chop command (see PWM Control Truth Table). Because it is possible to drive current in both direc-tions through the DMOS switches, this configuration effectively shorts-out the motor-generated BEMF, as long as the Chop com-mand is asserted. The maximum current can be approximated by V BEMF / R L. Care should be taken to ensure that the maximum ratings of the device are not exceeded in worse case braking situ-ations: high speed and high-inertia loads.Synchronous RectificationWhen a PWM off-cycle is triggered by an internal fixed off-time cycle, load current will recirculate. The A4950 synchronous rec-tification feature turns-on the appropriate DMOSFETs during the current decay, and effectively shorts out the body diodes with the low R DS(on) driver. This significantly lowers power dissipation. When a zero current level is detected, synchronous rectification is turned off to prevent reversal of the load current.Mixed Decay OperationThe bridges operate in Mixed Decay mode. Referring to the lower panel of the figure below, as the trip point is reached, the device goes into fast decay mode for 50% of the fixed off-time period. After this fast decay portion the device switches to slow decay mode for the remainder of the off-time. During transitions from fast decay to slow decay, the drivers are forced off for the Crossover Delay, t COD. This feature is added to prevent shoot-through in the bridge. During this “dead time” portion, synchro-nous rectification is not active, and the device operates in fast decay and slow decay only.Mixed Decay Mode OperationV PHASE IIApplication InformationSense Pin (LSS)In order to use PWM current control, a low-value resistor is placed between the LSS pin and ground for current sensing pur-poses. To minimize ground-trace IR drops in sensing the output current level, the current sensing resistor should have an indepen-dent ground return to the star ground point. This trace should be as short as possible. For low-value sense resistors, the IR drops in the PCB can be significant, and should be taken into account. When selecting a value for the sense resistor be sure not to exceed the maximum voltage on the LSS pin of ±500 mV at maximum load. During overcurrent events, this rating may be exceeded for short durations.GroundA star ground should be located as close to the A4950 as possible. The copper ground plane directly under the exposed thermal pad of the device makes a good location for the star ground point. The exposed pad can be connected to ground for this purpose. LayoutThe PCB should have a thick ground plane. For optimum electrical and thermal performance, the A4950 must be soldered directly onto the board. On the underside of the A4950 package is an exposed pad, which provides a path for enhanced thermal dis-sipation. The thermal pad must be soldered directly to an exposed surface on the PCB in order to achieve optimal thermal conduc-tion. Thermal vias are used to transfer heat to other layers of the PCB.The load supply pin, VBB, should be decoupled with an electro-lytic capacitor (typically 100 μF) in parallel with a lower valued ceramic capacitor placed as close as practicable to the device.Bill of MaterialsItem Reference Value Units Description1RS0.25(for V REF = 5 V, I OUT = 2 A)Ω2512, 1 W, 1% or better,carbon film chip resistor2C10.22μF X5R minimum, 50 V or greater 3C2100μF Electrolytic, 50 V or greaterPackage LJ, 8-Pin SOICN with exposed thermal padReference land pattern layout (reference IPC7351SOIC127P600X175-9AM); all pads a minimum of 0.20 mm from all adjacent pads; adjust as necessary to meet application processrequirements and PCB layout tolerances; when mounting on a multilayer PCB, thermal vias at the exposed thermal pad land can improve thermal dissipation (reference EIA/JEDEC Standard JESD51-5)PCB Layout Reference ViewCA Terminal #1 mark areaB CFor Reference Only; not for tooling use (reference MS-012BA)Dimensions in millimetersDimensions exclusive of mold flash, gate burrs, and dambar protrusions Exact case and lead configuration at supplier discretion within limits shown Exposed thermal pad (bottom surface); dimensions may vary with deviceRevision HistoryRevision Revision Date Description of RevisionRev. 4August 6, 2012Add AEC qualification; update PWM tableCopyright ©2011-2012, Allegro MicroSystems, Inc.Allegro MicroSystems, Inc. reserves the right to make, from time to time, such de p ar t ures from the detail spec i f i c a t ions as may be required to per-mit improvements in the per f or m ance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.Allegro’s products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.The in f or m a t ion in c lud e d herein is believed to be ac c u r ate and reliable. How e v e r, Allegro MicroSystems, Inc. assumes no re s pon s i b il i t y for its use; nor for any in f ringe m ent of patents or other rights of third parties which may result from its use.For the latest version of this document, visit our website:分销商库存信息: ALLEGROA4950KLJTR-T。

AO4459中文资料

AO4459中⽂资料SymbolTyp Max 33406275R θJL 1824Maximum Junction-to-Lead CSteady-State°C/WThermal Characteristics ParameterUnits Maximum Junction-to-AmbientAt ≤ 10s R θJA °C/W Maximum Junction-to-Ambient ASteady-State °C/W AO4459AO4459SymbolMin TypMaxUnits BV DSS -30V -1T J =55°C-5I GSS ±100nA V GS(th)-1.5-1.85-2.5V I D(ON)-30A 3846T J =125°C53685872m ?g FS 11S V SD -0.78-1V I S-3.5A C iss 668830pF C oss 126pF C rss 92pF R g69?Q g (10V)12.716nC Q g (4.5V) 6.4nC Q gs 2nC Q gd 4nC t D(on)7.7ns t r 6.8ns t D(off)20ns t f 10ns t rr 2230ns Q rr15nCTHIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT NOTICE.DYNAMIC PARAMETERS Maximum Body-Diode Continuous CurrentGate resistanceV GS =0V, V DS =0V, f=1MHzV GS =0V, V DS =-15V, f=1MHz Input Capacitance Output Capacitance Turn-On Rise Time Turn-Off DelayTime V GS =-10V, V DS =-15V, R L =2.5?, R GEN =3?Turn-Off Fall TimeTurn-On DelayTime SWITCHING PARAMETERSTotal Gate Charge (4.5V)Gate Source Charge Gate Drain Charge Total Gate Charge (10V)V GS =-10V, V DS =-15V, I D =-6.5Am ?V GS =-4.5V, I D =-5AI S =-1A,V GS =0V V DS =-5V, I D =-6.5AR DS(ON)Static Drain-Source On-ResistanceForward TransconductanceDiode Forward VoltageI DSS µA Gate Threshold Voltage V DS =V GS I D =-250µA V DS =-24V, V GS =0VV DS =0V, V GS =±20V Zero Gate Voltage Drain Current Gate-Body leakage current Electrical Characteristics (T J =25°C unless otherwise noted)STATIC PARAMETERS ParameterConditions Body Diode Reverse Recovery Time Body Diode Reverse Recovery ChargeI F =-6.5A, dI/dt=100A/µsDrain-Source Breakdown Voltage On state drain currentI D =-250µA, V GS =0V V GS =-10V, V DS =-5V V GS =-10V, I D =-6.5AReverse Transfer Capacitance I F =-6.5A, dI/dt=100A/µs A: The value of R θJA is measured with the device mounted on 1in 2FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The value in any a given application depends on the user's specific board design. The current rating is based on the t ≤ 10s thermal resistance rating.B: Repetitive rating, pulse width limited by junction temperature.C. The R θJA is the sum of the thermal impedence from junction to lead R θJL and lead to ambient.D. The static characteristics in Figures 1 to 6 are obtained using < 300µs pulses, duty cycle 0.5% max.E. These tests are performed with the device mounted on 1 in 2FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The SOA curve provides a single pulse rating. Rev0 Sept 2006AO4459AO4459。

电子元器件zr4040-5中文资料_数据手册_IC数据表

PRECISION 5.0 VOLT MICROPOWER VOLTAGE REFERENCEISSUE 2 - MARCH 1998DEVICE DESCRIPTIONThe ZR4040-5.0 uses a bandgap circuit design to achieve a precision micropower voltage reference of 5.0 volts. The device is available in small outline surface mount packages, ideal for applications where space saving is important, as well as packages for through hole requirements. The ZR4040-5.0 design provides a stable voltage without an external capacitor and is stable with capacitive loads. The ZR4040-5.0 is recommended for operation between 60µA and 15mA and so is ideally suited to low power and battery powered applications.Excellent performance is maintained to an absolute maximum of 25mA, however the rugged design and 20 volt processing allows the reference to withstand transient effects and currents up to 200mA. Superior switching capability allows the device to reach stable operating conditions in only a few microseconds.FEATURES•Small outline SO8 and SOT23packages•TO92 style package•No stabilising capacitor required•Typical T C 20ppm/°C•Typical slope resistance 0.33Ω•2% and 1% tolerance•Industrial temperature range•Operating current 60µA to 15mA•T ransient response,stable in less than10µsAPPLICATIONS•Battery powered and portableequipment.•Metering and measurement systems.•Instrumentation.•T est equipment.•Data acquisition systems.•Precision power supplies.VRGndSCHEMETIC DIAGRAM https://https://https://https:// httpshttps://https:// https://wwwhttps:// :// https://www.ichunhttps://www.ichun :// https://https://www https:// https://https https://https://ELECTRICAL CHARACTERISTICSReverse Current 25mAForward Current25mAOperating Temperature -40 to 85°C Storage Temperature-55 to 125°CPower Dissipation (T amb =25°C)SOT23330mW SO8625mW E-Line, 3 pin (TO92)500mWhttps://httpshttps://www:// https://www.ichunhttps://www.ichunhttps://https://wwwhttps://httpshttps https:// https://www:// https://www.ichunhttps://www.ichun https://https://www https://httpsORDERING INFORMATION* E-Line, 3 pin ReversedCONNECTION DIAGRAMShttps://httpshttps://https://wwwhttps://:// https://www.ichunhttps://www.ichunhttps://https://wwwhttps://httpshttps://。

FMBT3904中文资料

FMBT3904中⽂资料Formosa MSIssued Date : 2002/12/25Revised Date :Page No. :1/3FMBT3904NPN EPITAXIAL PLANAR TRANSISTORDescriptionThe FMBT3904 is designed for general purpose switching amplifier applications.Absolute Maximum RatingsMaximum TemperaturesStorage Temperature.......................................................................................................-65~+150?C Junction Temperature................................................................................................................+150?C ?Maximu m Power DissipationTotal Power Dissipation (Ta=25?C).........................................................................................225 mW ?Maximum Voltages and Currents (Ta=25?C)VCBO Collector to Base Voltage....................................................................................................60 V VCEO Collector to Emitter Voltage................................................................................................40 V VEBO Emitter to Base Voltage .........................................................................................................6 V IC Collector Current....................................................................................................................200 mACharacteristics (Ta=25?C)Symbol Min.Typ.Max.Unit Test ConditionsBVCBO 60--V IC=10uA BVCEO 40--V IC=1mA BVEBO 6--VIC=10uAICEX --50nA VCE=30V, VBE=-3V *VCE(sat)1--200mV IC=10mA, IB=1mA *VCE(sat)2--300mV IC=50mA, IB=5mA*VBE(sat)1650-850mV IC=10mA, IB=1mA *VBE(sat)2--950mVIC=50mA, IB=5mA *hFE140--VCE=1V, IC=0.1mA *hFE270--VCE=1V, IC=1mA *hFE3100-300VCE=1V, IC=10mA *hFE460--VCE=1V, IC=50mA *hFE530--VCE=1V, IC=100mAfT 300--MHz VCE=20V, IC=10mA, f=100MHz Cob--4pFVCB=5V, f=1MHz*Pulse Test: Pulse Width ?380us, Duty Cycle ?2%Formosa MS Issued Date : 2002/12/25 Revised Date :Page No. :2/3Characteristics CurveFormosa MSIssued Date : 2002/12/25Revised Date :Page No. :3/3SOT-23 Dimension*:TypicalInches MillimetersInches Millimeters DIM Min.Max.Min.Max.DIM Min.Max.Min.Max.A 0.11020.1204 2.80 3.04J0.00340.00700.0850.177B 0.04720.0630 1.20 1.60K 0.01280.02660.320.67C 0.03350.05120.89 1.30L 0.03350.04530.851.15D 0.01180.01970.300.50S 0.08300.10832.10 2.75G 0.06690.0910 1.70 2.30V0.00980.02560.250.65H0.00050.00400.0130.10Notes:1.Dimension and tolerance based on our Spec. dated Sep. 07,1997.2.Controlling dimension: millimeters.3.Maximum lead thickness includes lead finish thickness, and minimum lead thickness is the minimum thickness of base material.4.If there is any question with packing specification or packing method, please contact your local HSMC sales office. Material:Lead: 42 Alloy; solderplatingMold Compound: Epoxy resin family, flammability solid burning class:UL94V-0Important Notice:All rights are reserved. Reproduction in whole or in part is prohibited without the prior written approval of HSMC. FORMOSA MS reserves the right to make changes to its products without notice.FORMOSA MS semiconductor products are not warranted to be suitable for use in Life-Support Applications, or systems. FORMOSA MS assumes no liability for any consequence of customer product design, infringement of patents, or application assistance.Head Office And Factory:Head Office & Factory (TAIPEI):4F.,No.21,Lane 126,Sec.3, Chung-Yang. Rd.Tu-Cheng,Taipei County,Taiwan R.O.C.Tel: 886-2-2269-6661Fax: 886-2-2269-6141。

0440670402;中文规格书,Datasheet资料

This document was generated on 08/20/2012PLEASE CHECK FOR LATEST PART INFORMATIONPart Number:44067-0402Status:ActiveOverview:Micro-Fit 3.0™ ConnectorsDescription:3.00mm Pitch Micro-Fit 3.0™ Wire-to-Board Header, Dual Row, Vertical for up to 3.56mm Thick PCB, 4 Circuits, 0.38µm Gold (Au) Selective PlatingDocuments:3D ModelTest Summary TS-43045-002 (PDF)Drawing (PDF)RoHS Certificate of Compliance (PDF)Product Specification PS-43045 (PDF)GeneralProduct Family PCB Headers Series44067Application Power, Wire-to-BoardComments High Temperature, Polarization Key to PCB OverviewMicro-Fit 3.0™ Connectors Product Name Micro-Fit 3.0™UPC800754773225PhysicalBreakawayNo Circuits (Loaded)4Circuits (maximum)4Color - ResinBlack Durability (mating cycles max)30First Mate / Last Break No Glow-Wire Compliant No Guide to Mating Part No Keying to Mating Part None Lock to Mating PartYes Material - Plating MatingGold Material - Plating Termination TinMaterial - Resin High Temperature Thermoplastic Net Weight0.741/g Number of Rows 2Orientation Vertical PC Tail Length 4.01mm PCB Locator Yes PCB RetentionYes PCB Thickness - Recommended 3.60mm Packaging TypeTray Pitch - Mating Interface3.00mm Pitch - Termination Interface 3.00mm Plating min - Mating0.381µm Plating min - Termination 2.540µm Polarized to PCB Yes Shrouded Fully StackableNo Surface Mount Compatible (SMC)YesTemperature Range - Operating -40°C to +105°CTermination Interface: StyleThrough Hole - Kinked Pin ElectricalCurrent - Maximum per Contact 5A Voltage - Maximum250VSeriesimage - Reference onlyEU RoHSChina RoHSELV and RoHS Compliant REACH SVHCContains SVHC: No Low-Halogen Status Low-HalogenNeed more information on product environmental compliance?Email productcompliance@For a multiple part number RoHS Certificate of Compliance, click herePlease visit the Contact Us section for any non-product compliance questions.Search Parts in this Series 44067SeriesMates With43025 Micro-Fit™ HeaderSolder Process DataDuration at Max. Process Temperature (seconds)30Lead-free Process Capability SMC & Wave Capable (TH only)Max. Cycles at Max. Process Temperature3Process Temperature max. C260Material InfoReference - Drawing NumbersProduct Specification PS-43045Sales Drawing SD-44067-001Test Summary TS-43045-002This document was generated on 08/20/2012PLEASE CHECK FOR LATEST PART INFORMATION分销商库存信息: MOLEX 0440670402。