AEC_Q200-003B

Panasonic AEC-Q200 合规性解决方案指南说明书

Capacitors • Electromechanical • Wireless Connectivity • Resistors • Inductors • Relays • Connectors • Storage Media • Sensors • Semiconductors • Circuit Protection • Thermal Management Copyright © 2018 Panasonic Corporation of North America. | All Rights Reserved. | AEC-Q200 Compliance Solutions Guide Rev 5, FY15-081-xxxx

ERJ - U

All Case Sizes except 0201, Ag Pb Based

EXB - U24 / U28 / U2H 2/4/8 Elements Array, 0402 Base

EXB - U34 / U38

2/4 Elements Array, 0603 Base

CHIP RESISTOR ARRAYS

ERJ - 1TR

2512, Low Ohmic Value

CURRENT SENSING CHIP RESISTORS, METAL PLATE TYPE

ERJ - MS

2512, 2526

ERJ - MB

1020

HIGH POWER CURRENT SENSING CHIP RESISTORS

ERJ - A1

EEV - F

105°C, Surface Mount, Low Impedance

AEC_Q100-003_rev_E

Component Technical CommitteeATTACHMENT 3AEC - Q100-003 REV-EMACHINE MODEL ELECTROSTATIC DISCHARGE TESTComponent Technical CommitteeAcknowledgmentAny document involving a complex technology brings together experience and skills from many sources. The Automotive Electronics Counsel would especially like to recognize the following significant contributors to the development of this document:Mark A. Kelly Delphi Delco Electronics SystemsComponent Technical CommitteeChange NotificationThe following summary details the changes incorporated into AEC-Q100-003 Rev-E:• Section 5, Acceptance Criteria: Added wording to reflect device classification, rather than meeting a 200 volt level.• Table 3, Integrated Circuit MM ESD Classification Levels: Added new table listing classification levels for MM ESD.Component Technical CommitteeMETHOD - 003MACHINE MODEL (MM)ELECTROSTATIC DISCHARGE (ESD) TESTText enhancements and differences made since the last revision of this document are shown as underlined areas.1. SCOPE1.1 DescriptionThe purpose of this specification is to establish a reliable and repeatable procedure for determiningthe MM ESD sensitivity for electronic devices.1.2 Reference DocumentsEOS/ESD Association Specification S5.2JEDEC Specification EIA/JESD22-A1151.3 Terms and DefinitionsThe terms used in this specification are defined as follows.1.3.1 Device FailureA condition in which a device does not meet all the requirements of the acceptance criteria, asspecified in section 5, following the ESD test.1.3.2 DUTAn electronic device being evaluated for its sensitivity to ESD.1.3.3 Electrostatic Discharge (ESD)The transfer of electrostatic charge between bodies at different electrostatic potentials.1.3.4 Electrostatic Discharge SensitivityAn ESD voltage level resulting in device failure.DaimlerChrysler Date Delphi Delco Electronics Systems Date Visteon Corporation DateMajdi Mortazavi Detlef Griessman Robert V. Knoell Copyright © 2003 by DaimlerChrysler, Delphi Delco Electronics Systems, and Visteon Corporation. This document may be freely reprinted with this copyright notice. This document cannot be changed without approval by the AEC Component Technical Committee.Component Technical Committee1.3.5 ESD SimulatorAn instrument that simulates the machine model ESD pulse as defined in this specification.1.3.6 Machine Model (MM) ESDAn ESD pulse meeting the waveform criteria specified in this test method, approximating an ESDpulse from a machine or mechanical equipment.1.3.7 Major Pulse Period (t pm)The time (t pm) measured between first and third zero crossing points.1.3.8 Non-Supply PinsAll pins including, but not limited to, input, output, bi-directional, Vref, Vpp, clock, and “no-connect”pins. These pins do not supply voltage and/or current to the device under test.1.3.9 Power PinsAll power supply, external voltage source and ground pins. All power pins that are metallicallyconnected together on the chip or in the package shall be treated as one (1) power pin.1.3.10 PUTThe pin under test.1.3.11 Withstanding VoltageThe ESD voltage level at which, and below, the device is determined to pass the failure criteriarequirements specified in section 4.1.3.12 Worst-Case Pin Pair (WCP)WCP is the pin pair representing the worst-case waveform that is within the limits and closest to the minimum or maximum parameter values as specified in Table 1. The WCP shall be identified foreach socket. It is permissible to use the worst-case pin pair that has been previously identified by the HBM ESD method (AEC-Q100-002) when performing the Simulator Waveform Verification asdefined in section 2.4.2. EQUIPMENT2.1 Test ApparatusThe apparatus for this test consists of an ESD pulse simulator and DUT socket. Figure 1shows a typical equivalent MM ESD circuit. Other equivalent circuits may be used, but the actual simulator must be capable of supplying pulses which meet the waveform requirements of Table 1,Figure 2, and Figure 3.Component Technical CommitteeR 2200 pFC1Terminal ATerminal B500s h o r tS1S2High Voltage SourceΩDUTsocketR110k to 10MohmFigure 1: Typical Equivalent MM ESD CircuitNotes:1. Figure 1 is shown for guidance only; it does not attempt to represent all associated circuit components, parasitics, etc..2. The performance of any simulator is influenced by its parasitic capacitance and inductance.3. Resistor R1, in series with switch S2, ensures a slow discharge of the device.4. Precautions must be taken in simulator design to avoid recharge transients and multiple pulses.5. R2, used for Equipment Qualification as specified in section 2.3, shall be a low inductance, 1000 volt, 500 ohm resistor with ±1% tolerance.6.Piggybacking of DUT sockets (the insertion of secondary sockets into the main DUT socket) is allowed only if the combined piggyback set (main DUT socket with the secondary DUT socket inserted) waveform meets the requirements of Table 1, Figure 2, and Figure 3. 7. Reversal of terminals A and B to achieve dual polarity is not permitted 8.S2 should be closed 10 to 100 milliseconds after the pulse delivery period to ensure the DUT socket is not left in a charged state. S2 should be opened at least 10 milliseconds prior to the delivery of the next pulse.2.2 Measurement EquipmentEquipment shall include an oscilloscope and current probe to verify conformance of the simulator output pulse to the requirements of this document as specified in Table 1, Figure 2, and Figure 3.2.2.1 Current ProbeThe current probe shall have a minimum bandwidth of 350 MHz and maximum cable length of 1 meter (Tektronix CT-1, CT-2, or equivalent). A CT-2 probe or equivalent should be used with voltages greater than 800 volts.Component Technical Committee2.2.2 Evaluation LoadsThe two evaluation loads shall be: 1) a low inductance, 1000 volt, 500 ohm sputtered film resistorwith + 1% tolerance, and 2) an 18 AWG tinned copper shorting wire. The lead length of both theshorting wire and the 500 ohm resistor shall be as short as possible and shall span the maximumdistance between the worst-case pin pair (WCP) while passing through the current probe as defined in section 2.2.1.2.2.3 OscilloscopeThe oscilloscope and amplifier combination shall have a minimum bandwidth of 350 MHz, aminimum sensitivity of 100 milliamperes per large division and a minimum visual writing speed of 4cm per nanosecond.2.3 Equipment QualificationEquipment qualification must be performed during initial acceptance testing or after repairs are made to the equipment that may affect the waveform. The simulator must meet the requirements of Table1 and Figure2 for five (5) consecutive waveforms at all voltage levels using the worst-case pin pair(WCP) on the highest pin count, positive clamp test socket DUT board with the shorting wire perFigure 1. The simulator must also meet the requirements of Table 1 and Figure 3 for five (5)consecutive waveforms at the 400 volt level using the worst-case pin pair (WCP) on the highest pincount, positive clamp test socket DUT board with the 500 ohm load per Figure 1. Thereafter, the test equipment shall be periodically qualified as described above; a period of one (1) year is the maximum permissible time between full qualification tests.2.4 Simulator Waveform VerificationThe performance of the simulator can be dramatically degraded by parasitics in the discharge path.Therefore, to ensure proper simulation and repeatable ESD results, it is recommended thatwaveform performance be verified on the worst-case pin pair (WCP) using the shorting wire persection 2.4.1. The worst-case pin pair (WCP) for each socket and DUT board shall be identified and documented. The waveform verification shall be performed when a socket/mother board is changed or on a weekly basis (if the equipment is used for at least 20 hours). If at any time the waveformsdo not meet the requirements of Table 1 and Figure 2 at the 400 volt level, the testing shall behalted until waveforms are in compliance.2.4.1 Waveform Verification Procedurea. With the required DUT socket installed and with no device in the socket, attach a shortingwire in the DUT socket such that the worst-case pin pair (WCP) is connected betweenterminal A and terminal B as shown in Figure 1. Place the current probe around theshorting wire.b. Set the horizontal time scale of the oscilloscope at 20 nanoseconds per division or greater.c. Initiate a positive pulse at the 400 volt level per Table 1. The simulator shall generate onlyone (1) waveform per pulse applied.Component Technical Committeed. Measure and record the first peak current, second peak current, and major pulse period.All parameters must meet the limits specified in Table 1 and Figure 2.e. Initiate a negative pulse at the 400 volt level per Table 1. The simulator shall generate onlyone (1) waveform per pulse applied.f. Measure and record the first peak current, second peak current, and major pulse period.All parameters must meet the limits specified in Table 1 and Figure 2.Table 1: MM Waveform SpecificationVoltage Level (V)PositiveFirst PeakCurrentfor Short,I ps1(A)PositiveSecond PeakCurrentfor Short,I ps2(A)Major PulsePeriod forShort,t pm(ns)PositiveFirst PeakCurrent for500 Ohm*,I pr(A)Current at100 ns for500 Ohm*,I I00(A)100 1.5 - 2.0 67% to 90%of I ps1 66 - 90 NotApplicableNotApplicable200 3.0 - 4.0 67% to 90%of I ps1 66 - 90 NotApplicableNotApplicable400 6.0 - 8.1 67% to 90%of I ps166 - 90 0.85 to 1.2 0.29 ± 10%800 11.9 - 16.1 67% to 90%of I ps1 66 - 90 NotApplicableNotApplicable* The 500 ohm load is used only during Equipment Qualification as specified in section 2.3.2.5 Automated ESD Test Equipment Relay VerificationIf using automated ESD test equipment, the system diagnostics test shall be performed on all high voltage relays per the equipment manufacturer's instructions. This test normally measurescontinuity and will identify any open or shorted relays in the test equipment. Relay verification must be performed during initial equipment qualification and on a weekly basis. If the diagnostics testdetects relays as failing, all sockets boards using those failed relays shall not be used until thefailing relays have been replaced. The test equipment shall be repaired and requalified per section2.3.Component Technical CommitteeFigure 2: MM current waveform through a shorting wire, 400 volt dischargeTime in nanosecondsI prC u r r e n t i n A m p e r e sFigure 3: MM Current waveform through a 500 ohm res istor *, 400 volt discharge* The 500 ohm load is used only during Equipment Qualification as specified in section 2.3.Component Technical Committee3. PROCEDURE3.1 Sample SizeEach sample group shall be composed of three (3) units. Each sample group shall be stressed at one (1) voltage level using all pin combinations specified in Table 2. The use of a new sample group for each pin combination specified in Table 2 is also acceptable. Voltage level skipping is notallowed. It is permitted to use the same sample group for the next pin combination or stressvoltage level if all devices in a sample group meet the acceptance criteria requirements specified in section 5 after exposure to a specified voltage level. Therefore the minimum number of devicesrequired for ESD qualification is 3 devices, while the maximum number of devices depends on the number of pin combinations and the number of voltage steps required to achieve the maximumwithstanding voltage. For example, a device (1 VCC pin, 1 GND pin, and 2 IO pins) with amaximum withstanding voltage of 200 volts requires 4 voltage steps of 50 volts each, 3 pincombinations, and 3 devices per pin combination per voltage level for a maximum total of 36devices.Maximum # of devices = (# of pin combinations) X (# of voltage steps required) X 3 devices3.2 Pin CombinationsThe pin combinations to be used are given in Table 2. The actual number of pin combinationsdepends on the number of power pin groups. Power pins of the same name (VCC1, VCC2, VSS1, VSS2, etc.) may be tied together and considered one (1) power pin group if they are connected in the package or on the chip via a metal line. Same name power pins that are resistively connected via the chip substrate or wells, or are electrically isolated from each other, must be treated as aseparate power pin group. All pins configured as "no connect" pins shallbe considered non-supply pins and included in the pin groups stressed during ESD testing.Integrated Circuits with six (6) pins or less shall be tested using all possible pin pair combinations (one pin connected to terminal A, another pin connected to terminal B) regardless of pin name orfunction.Table 2: Pin Combinations for Integrated CircuitsPin CombinationConnectIndividually toTerminal A (Stress)ConnectIndividually toTerminal B (Ground)Floating Pins(unconnected)1All pins one at a time,except the pin(s)connected to Terminal BFirst powerpin(s)All pins except PUTand first powerpin(s)2All pins one at a time,except the pin(s)connected to Terminal BSecond powerpin(s)All pins except PUTand second powerpin(s)3All pins one at a time,except the pin(s)connected to Terminal BNth powerpin(s)All pins except PUTand Nth powerpin(s)4 Each Non-supply pinAll otherNon-supply pinsexcept PUTAll power pinsComponent Technical Committee3.3 Test TemperatureEach device shall be subjected to ESD pulses at room temperature.3.4 MeasurementsPrior to ESD testing, complete initial DC parametric and functional testing (initial ATE verification) shall be performed on all sample groups and all devices in each sample group per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in thedevice specification.3.5 Detailed ProcedureThe ESD testing procedure shall be per the test flow diagram of Figure 4 and as follows:a. Set the pulse voltage at 50 volts. Voltage level skipping is not allowed.b. Connect a power pin group to terminal B. Leave all other power pins unconnected (seeTable 2 / pin combination 1).c. Connect an individual pin to terminal A. Leave all other pins unconnected.d. Apply one (1) positive pulse at the specified voltage to the PUT. Wait a minimum of one (1)second before applying the next test pulse. The use of three (3) pulses at each stressvoltage polarity is required.e. Apply one (1) negative pulse at the specified voltage to the PUT. Wait a minimum of one(1) second before applying the next test pulse. The use of three (3) pulses at each stressvoltage polarity is required.f. Disconnect the PUT from testing and connect the next individual pin to terminal A. Leaveall other pins unconnected.g. Repeat steps (d) through (f) until every pin not connected to terminal B is pulsed at thespecified voltage.h. Repeat steps (b) through (g) until all power pin groups have been stressed (see Table 2 /pin combinations 2 and 3). The use of a new sample group for each pin combinationspecified in Table 2 is also acceptable.i. Connect one non-supply pin to terminal A and tie all other non-supply pins to terminal B.Leave all power pins unconnected (see Table 2 / pin combination 4). The use of a newsample group for each pin combination specified in Table 2 is also acceptable.j. Apply one (1) positive pulse at the specified voltage to the PUT. Wait a minimum of one (1) second before applying the next test pulse. The use of three (3) pulses at each stressvoltage polarity is required.k. Apply one (1) negative pulse at the specified voltage to the PUT. Wait a minimum of one(1) second before applying the next test pulse. The use of three (3) pulses at each stressvoltage polarity is required.Component Technical Committeel. Disconnect the PUT from testing and connect the next non-supply pin to terminal A. Tie all non-supply pins not under test to terminal B. Leave all other pins unconnected (see Table2 / pin combination 4).m. Repeat steps (j) through (l) until all non-supply pins have been tested.n. Test the next device in the sample group and repeat steps (b) through (m) until all devices in the sample group have been tested at the specified voltage level.o. Submit the device for complete DC parametric and functional testing (final ATE verification) per the device specification at room temperature followed by hot temperature, unless specifiedotherwise in the device specification, and determine whether the devices pass the failurecriteria requirements specified in section 4. The functionality of "E2PROM" type devices shallbe verified by programming random patterns. If a different sample group is tested for each pincombination or stress voltage level, it is permitted to perform the DC parametric and functionaltesting (final ATE verification) per device specification after all sample groups have been tested.p. Using the next sample group, increase the pulse voltage by 50 volts and repeat steps (b) through (o). Voltage level skipping is not allowed. It is permitted to use the same samplegroup for the next pin combination or stress voltage level if all devices in a sample group passthe failure criteria requirements specified in section 4 after exposure to a specified voltage level.q. Repeat steps (b) through (p) until failure occurs or the device fails to meet the 50V stress voltage level.4. FAILURE CRITERIAA device will be defined as a failure if, after exposure to ESD pulses, the device no longer meets thedevice specification requirements. Complete DC parametric and functional testing (initial and final ATE verification) shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.5. ACCEPTANCE CRITERIAA device passes a voltage level if all devices in the sample group stressed at that voltage level andbelow pass. All the devices and sample groups used must pass the measurement requirementsspecified in section 3 and the failure criteria requirements specified in section 4. Using theclassification levels specified in Table 3, the supplier shall classify the device according to themaximum withstanding voltage level.Table 3: Integrated Circuit MM ESD Classification LevelsComponent Classification Maximum Withstand VoltageM0 ≤ 50 VM1 > 50 V to ≤ 100 VM2 > 100 V to ≤ 200 VM3 > 200 V to ≤ 400 VM4 > 400 VComponent Technical CommitteeFigure 4: Integrated Circuit MM ESD Test Flow DiagramComponent Technical CommitteeRevision HistoryRev #-A B C D E Date of changeJune 9, 1994May 15, 1995Sept. 6, 1996Oct. 8, 1998Aug. 25, 2000July 18, 2003Brief summary listing affected sectionsInitial ReleaseAdded Copyright statement. Revised the following: Foreword; Sections 2.3,2.4,3.1, 3.2, 3.4, 3.5 (g, h, I, o, and p), and4.0; Tables 1 and 2; Figures 2,3, and 4.Revised the following: Sections 1.3.1, 1.3.7, 1.3.8, 2.1, 2.4.1 (d and f), 3.1,3.2, 3.3, 3.4, 3.5 (o, p, and q),4.0, and5.0; Table 1; Figures 1 and 4.Revised the following: Sections 1.2, 2.1, 3.1, 3.5 (a and p); Tables 1 and 2;Figures 1 and 4. Revision to section 3.5 (a and p) and Figure 4 reflects achange from 100 volt increments to 50 volt increments. Revision to Table 1reflects the addition of a 100 volt level and a ±15% tolerance applied to allIps1 (positive first peak current for short) parameter v alues.Added note to page 1 concerning optional use of Q100-011 Field InducedCharged Device Model (FCDM) instead of Q100-003 Machine Model.Revision to section 5 reflects addition of classification levels for ESD testing.New Table 3 added listing MM ESD classification levels.。

AECQ200电阻精密低温漂电阻

Automotive Grade Thin Film Precision Chip Resistor■ Features-AEC-Q200 Compliance-Advanced thin film technology -RoHS compliant- Special materials, design, and processing for high sulfur applications - Test proven immunity to humidity, moisture, and sulfur■Applications-Automotive-Medical Equipment-Testing / Measurement Equipment -Printer Equipment-Automatic Equipment Controller -Converters-Communication Device, Cell Phone, GPS, PDA■Construction■Dimensions Unit: mm■Part Numbering1Alumina Substrate 4Edge Electrode (NiCr) 7 Resistor Layer (NiCr)2Bottom Electrode (Ag)5Barrier Layer (Ni) 8 Overcoat (Epoxy) 3Top Electrode ( Cu) 6External Electrode (Sn) 9 MarkingType Size (Inch) LWTD1D2Weight (g) (1000pcs)AR02 0402 1.00±0.05 0.50±0.05 0.30±0.05 0.20±0.10 0.20±0.10 0.54 AR03 0603 1.55±0.10 0.80±0.10 0.45±0.10 0.30±0.20 0.30±0.20 1.83 AR05 0805 2.00±0.15 1.25±0.15 0.55±0.10 0.30±0.20 0.40±0.20 4.71 AR06 1206 3.05±0.15 1.55±0.15 0.55±0.10 0.42±0.20 0.35±0.25 9.02 AR13 1210 3.10±0.15 2.40±0.15 0.55±0.10 0.40±0.20 0.55±0.25 10 AR10 2010 4.90±0.15 2.40±0.15 0.55±0.10 0.60±0.30 0.50±0.25 23.61 AR1225126.30±0.15 3.10±0.15 0.55±0.10 0.60±0.30 0.50±0.25 38.06■Derating Curve■Standard Electrical Specifications■High Power Rating Electrical SpecificationsOperating Voltage=√(P*R) or Max. operating voltage listed above, whichever is lower. Overload Voltage=2.5*√(P*R) or Max. overload voltage listed above, whichever is lower. Viking is capable of manufacturing the optional spec based on customer’s requirement.■Environmental CharacteristicsItemRequirementTest Method Tol. ≦0.05% Tol. > 0.05%Temperature Coefficient of Resistance (T.C.R.) As Spec.JIS-C-5201-1 4.8IEC-60115-1 4.8-55°C~+125°C, 25°C is the reference temperatureShort Time Overload ΔR±0.05% ΔR±0.2% JIS-C-5201-1 4.13IEC-60115-1 4.13RCWV*2.5 or Max. overload voltage whichever islower for 5 secondsΔR±0.2% for high power ratingInsulation Resistance >1000 MΩJIS-C-5201-1 4.6IEC-60115-1 4.6Apply 100V DC for 1 minuteEndurance ΔR±0.05% ΔR±0.2% JIS-C-5201-1 4.25IEC-60115-1 4.25.170±2°C, RCWV for 1000 hrs with 1.5 hrs “ON” and 0.5hrs “OFF”>7kΩΔR±0.5%ΔR±0.5% for high power ratingBiased Humidity ΔR±0.05% ΔR±0.2%MIL-STD-202 Method 1031000 hrs 85°C/85%RH 10% of operating power. >7kΩΔR±0.5%ΔR±0.5% for high power ratingHigh Temperature Exposure ΔR±0.05%MIL-STD-202 Method 108 at +155°C for 1000 hrsTemperature Cycling ΔR±0.05% ΔR±0.2%JESD22 Method JA-104-55°C to +125°C, 1000 cyclesBending Strength (Board Flex) ΔR±0.05% ΔR±0.2% IEC-60115-1 4.33JIS-C-5201-1 6.1.4Bending amplitude 3 mm for 10 secondsSolderability 95% min. coverageJIS-C-5201-1 4.17 IEC-60115-1 4.17 245±5°C for 3 secondsResistance to Soldering Heat ΔR±0.05% ΔR±0.2%JIS-C-5201-1 4.18 IEC-60115-1 4.18260±5°C for 10 secondsTerminal strength No broken AEC-Q200-006Force of 1.8kg for 60 seconds.Mechanical Shock ΔR±0.25% ΔR±0.5% MIL-STD-202 Method 213Wave Form: Tolerance for half sine shock pulse. Peak value is 100g’s. Normal duration (D) is 6.Vibration ΔR±0.25% ΔR±0.5% MIL-STD-202 Method 2045 g’s for 20 min., 12 cycles each of 3 orientations, 10-2000 HzESD ΔR±0.1% AEC-Q200-002 Human body, 2KVFlame RetardanceNot flame AEC-Q200-001Temperature sensing at 500℃, voltage power subjected to 32VDC current clamped up to 500ADC and decreased in 1.0VDC/hour.Resistance to solvents Marking Unsmeared MIL-STD-202Method 215Add Aqueous wash chemical - OKEM Clean or equivalent. Do not use banned solvents.Sulfur Test± 0.5%ASTM-B-809-953~5ppm H2S, 50±2°C, 91~93% R.H., no power rating for 1000 hrsRCWV(Rated continuous working voltage)= √(P*R) or Max. Operating voltage whichever is lower Storage Temperature: 25±3°C; Humidity < 80%RH▓Reflow▓Marking0603 3digit marking3digit marking for Example: 14C=13K7Ω 13C=13K3Ω 68B=4K99Ω 68X=49.9Ω0603 3digit marking for E24 Example: 101=100Ω 102=1K Ω E24 10 11 12 13 15 1618 20 22 242730333639434751 56 62 687582910805~2512 4digit marking ExampleResistance 100Ω 2.2K Ω 10K Ω 49.9K Ω 100K Ωmarking1000 2201 1002 4992 100314C89BMarking TableCode E96Code E96Code E96Code E9601 100 25 178 49 316 73 56202 102 26 182 50 324 74 57603 105 27 187 51 332 75 59004 107 28 191 52 340 76 60405 110 29 196 53 348 77 61906 113 30 200 54 357 78 63407 115 31 205 55 365 79 64908 118 32 210 56 374 80 66509 121 33 215 57 383 81 68110 124 34 221 58 392 82 69811 127 35 226 59 402 83 71512 130 36 232 60 412 84 73213 133 37 237 61 422 85 75014 137 38 243 62 432 86 76815 140 39 249 63 442 87 78716 143 40 255 64 453 88 80617 147 41 261 65 464 89 82518 150 42 267 66 475 90 84519 154 43 274 67 487 91 86620 158 44 280 68 499 92 88721 162 45 287 69 511 93 90922 165 46 294 70 523 94 93123 169 47 301 71 536 95 95324 174 48 309 72 549 96 976Code A B C D E F G H X Y Z Multiplier 100 101 102 103 104 105 106 107 10-1 10-2 10-3■PackagingP a c k i n g Q u a n t i t y & R e e l S p e c i f i c a t i o n s Unit :mmPaper Tape SpecificationsUnit: mm TypeABWEF P 0 P 1 P 2ΦD 0TAR02 0.70±0.05 1.16±0.05 8.00±0.10 1.75±0.05 3.5±0.05 4.00±0.10 2.00±0.05 2.00±0.05 1.55±0.05 0.40±0.03AR03 1.10±0.05 1.90±0.05 8.00±0.10 1.75±0.05 3.5±0.05 4.00±0.10 4.00±0.10 2.00±0.05 1.55±0.05 0.60±0.03AR05 1.60±0.05 2.37±0.05 8.00±0.10 1.75±0.05 3.5±0.05 4.00±0.10 4.00±0.10 2.00±0.05 1.55±0.05 0.75±0.05AR06 2.00±0.05 3.55±0.05 8.00±0.10 1.75±0.05 3.5±0.05 4.00±0.10 4.00±0.10 2.00±0.05 1.55±0.05 0.75±0.05AR13 2.75±0.05 3.40±0.05 8.00±0.10 1.75±0.05 3.5±0.054.00±0.054.00±0.102.00±0.05 1.60±0.10 0.75±0.05Peel force of top cover tapeThe peel speed shall be about 300mm/min±5%The peel force of top cover tape shall be between 8g to 40gTop Cover TapeTypeØAØBØCWTPaperTape (EA)Emboss Plastic Tape (EA)AR02 178.0±1.0 60.0+1.0 13.5±0.79.5±1.0 11.5±1.010,000 - AR03 178.0±1.0 60.0+1.0 13.5±0.79.5±1.0 11.5±1.05,000 - AR05 178.0±1.0 60.0+1.0 13.5±0.79.5±1.0 11.5±1.05,000 - AR06 178.0±1.0 60.0+1.0 13.5±0.79.5±1.0 11.5±1.05,000 - AR13 178.0±1.0 60.0±1.0 13.5±0.79.5±1.0 11.5±1.05,000 - AR10 178.0±1.0 60.0+1.0 13.5±0.713.5±1.0 15.5±1.0- 4,000 AR12 178.0±1.0 60.0+1.0 13.5±0.713.5±1.0 15.5±1.0-4,000Top TapeBottom TapeEmboss Plastic Tape SpecificationsTop Tape1 1.4Min.Unit: mmType A B W E F P 0P 1 P 2 ØD 0 TAR10 2.85±0.10 5.45±0.10 12.0±0.10 1.75±0.10 5.5±0.05 4.00±0.05 4.00±0.10 2.00±0.05 1.50+0.10 1.00±0.20AR12 3.40±0.10 6.65±0.10 12.0±0.10 1.75±0.105.5±0.054.00±0.054.00±0.102.00±0.05 1.50+0.101.00±0.20Peel force of top cover tapeThe peel speed shall be about 300mm/min±5%The peel force of top cover tape shall be between 20g to 80g■Recommend Land Pattern Unit: mmTypeABCAR02 0.50 0.500.60±0.2 AR03 0.80 1.00 0.90±0.2 AR05 1.00 1.00 1.35±0.2 AR06 2.00 1.15 1.70±0.2 AR13 2.00 1.15 2.50±0.2 AR10 3.60 1.40 2.50±0.2AR12 4.90 1.60 3.10±0.2REVISION HISTORYREVISION DATE CHANGE NOTIFICATION DESCRIPTION Version A5May 07.2013 --Correct the scheme.Version A6Aug 20.2013 --Delete Thermal Shock & MoistureResistance Tests (Follow AEC-Q200Rev.D)Version A7Oct 24.2013 -- Update product features descriptionand add a reliability test item.。

车规级贴片电阻AC系列风华原厂规格书

High Temperature Exposure (Storage)

0.5% 1% R (1.0%R 0.05 ) 2% 5% 10% R (2.0%R 0.05 )

Temperature Cycling

No mechanical damage No mechanical damage 0.5% 1% R 50 m (J ) R (0.5%R 0.05 ) R 20 m (G ) 2% 5% 10% R 10 m (F ) R (1.0%R 0.05 )

;

Biased Humidity

No mechanical damage R (3.0%R 0.05 )

No mechanical 85 85% 10% ( ) damage 1000 R 50 m (J ) 85 /85%RH. 1000 hours, Apply 10% of operating power R 20 m (G ) R 10 m (F ) (current) or limiting element voltage whichever is lower.

2% 5% 10% 10m

C

Tape & Reel

Chip No Marking Jumper

F

1/4W

06

1206

103 =10K (E-24) 1003=100K (E-96) 1R0 =1.0 (E-24) 000=0

20m 50m

Case

J

58

【南京南山—领先的片式无源器件整合供应商】

Ratings

70

Type

70 Rated Power at 70 (W)

1/16

1/10 1/8 1/ 4

AEC-Q200厚膜电阻器

精品推介I Product Express能够快速唤醒以捕捉完整的关键字,当与Vesper 的零 功耗监听(ZeroPower Listening tm )技术结合使用时, 其关键字捕捉精度提高了 2倍。

并且,超快速启动还 意味着麦克风无需保持待机模式,从而进一步节省了 电能。

VM3000将使压电MEMS 麦克风能够服务于更广 泛的应用,并且可以与几乎所有音频芯片匹配使用。

对于大型阵列、大型系统和有很多射频干扰的情况, VM3000的优势尤其突出,这证明Vesper 能够开发复 杂的高性能专用集成电路(ASIC )。

VM3000的典型信噪比(SNR )为63dB (1kHz 信号),并提供122dB 声压级(SPL )的声学过载点 (AOP )。

VM3000麦克风具有防水、防尘、防颗粒和防震 性能,因此,它无惧水浸、灰尘,暴露于粉尘颗粒物 中或是跌落,它都能保持正常运行。

无论是作为一个 独立的麦克风或是麦克风阵列,VM3000都是一款能 够应对恶劣环境并提供丰富声学性能的麦克风。

VM3000 具有行业标准的 3.5mmx2.65mmxl.3mm 封装尺寸,兼容回流焊工艺,不影响器件灵敏度。

VM3000目前提供底部进声,超快速启动时间低于200 微秒,休眠模式功耗仅为2piA 。

VM3000现己开始批 量送样,计划将于2019年第四季度开始大规模量产。

可快速响应温度变化,还满足智能手表和医疗贴等小 尺寸、电池供电应用对功耗及尺寸的严苛要求,有效 简化了可穿戴医疗产品中的电池供电和测温设计。

与 竞争产品相比,器件非常容易使用,可通过设备顶部 测温,无需受到自身散热干扰。

支持多达4个I :C 地址, 允许在同一 1C 总线上挂接多个传感器,可安装到PCB 或柔性印刷电路板(FPC ).Bourns 推出新系列的抗硫化AEC-Q200厚膜电阻 器。

Bourns* CRxxxxA-AS 系列芯片电阻器提供8种不 同的封装尺寸,从小型0201 (0603公制)至2512 (6432 公制),额定功率从0.05W-1W.新型表面贴装芯片 电阻还具有1欧姆至20百万欧姆的宽电阻范围,非常 适合各种应用。

AECQ相关

标签:AECQAECQ信息汇总最近在整理元器件方面的资料,涉及ROSH与AECQ的信息,下面整理了AE CQ的信息。

克莱斯勒、福特和通用汽车为建立一套通用的零件资质及质量系统标准而设立了汽车电子委员会(AEC),AEC 是“Automotive Electronics Council:汽车电子协会”之略,是主要汽车制造商与美国的主要部件制造商汇聚一起成立的、以车载电子部件的可靠性以及认定标准的规格化为目的的团体,AEC建立了质量控制的标准。

同时,由于符合AEC规范的零部件均可被上述三家车厂同时采用,促进了零部件制造商交换其产品特性数据的意愿,并推动了汽车零件通用性的实施,为汽车零部件市场的快速成长打下基础。

主要的汽车电子成员有:Autoliv, Co ntinental, Delphi, Johnson Controls 和Visteon。

AEC-Q100:主要用于预防产品可能发生各种状况或潜在的故障状态,引导零部件供货商在开发的过程中就能采用符合该规范的芯片。

AEC-Q100对每一个芯片个案进行严格的质量与可靠度确认,确认制造商所提出的产品数据表、使用目的、功能说明等是否符合最初需求的功能,以及在连续使用后个功能与性能是否能始终如一。

A EC-Q100标准的目标是提高产品的良品率,这对芯片供货商来说,不论是在产品的尺寸、合格率及成本控制上都面临很大的挑战。

AEC-Q100又分为不同的产品等级,其中第1级标准的工作温度范围在-40℃-1 25℃之间,最严格的第0级标准工作温度范围可达到-40℃-150℃。

0 等级:环境工作温度范围-40℃-150℃1 等级:环境工作温度范围-40℃-125℃2 等级:环境工作温度范围-40℃-105℃3 等级:环境工作温度范围-40℃-85℃4 等级:环境工作温度范围0℃-70℃AEC - Q100 Rev - G base: 集成电路的应力测试标准(不包含测试方法)AEC-Q100-001 邦线切应力测试AEC-Q100-002 人体模式静电放电测试AEC-Q100-003 机械模式静电放电测试AEC-Q100-004 集成电路闩锁效应测试AEC-Q100-005 可写可擦除的永久性记忆的耐久性、数据保持及工作寿命的测试AEC-Q100-006 热电效应引起的寄生闸极漏电流测试AEC-Q100-007 故障仿真和测试等级AEC-Q100-008 早期寿命失效率(ELFR)AEC-Q100-009 电分配的评估AEC-Q100-010 锡球剪切测试AEC-Q100-011 带电器件模式的静电放电测试AEC-Q100-012 12V 系统灵敏功率设备的短路可靠性描述AEC - Q101 Rev - C: 分立半导体元件的应力测试标准(包含测试方法)* AEC - Q101-001 - Rev-A: 人体模式静电放电测试* AEC - Q101-002 - Rev-A: 机械模式静电放电测试* AEC - Q101-003 - Rev-A: 邦线切应力测试* AEC - Q101-004 - Rev-: 同步性测试方法* AEC - Q101-005 - Rev-A: 带电器件模式的静电放电测试* AEC - Q101-006 - Rev-: 12V 系统灵敏功率设备的短路可靠性描述AEC - Q200 Rev - C: 半导体被动元件的应力测试标准(包含测试方法)* AEC - Q200-001 - Rev-A: 阻燃性能测试* AEC - Q200-002 - Rev-A: 人体模式静电放电测试* AEC - Q200-003 - Rev-A: 断裂强度测试* AEC - Q200-004 - Rev-: 自恢复保险丝测量程序* AEC - Q200-005 - Rev-: PCB板弯曲/端子邦线应力测试* AEC - Q200-006 - Rev-: 端子应力(贴片元件)/切应力测试* AEC - Q200-007 - Rev-: 电压浪涌测试AEC-Q001 零件平均测试指导原则提出了所谓的参数零件平均测试(PPAT)方法。

AEC Q200D-2010 汽车

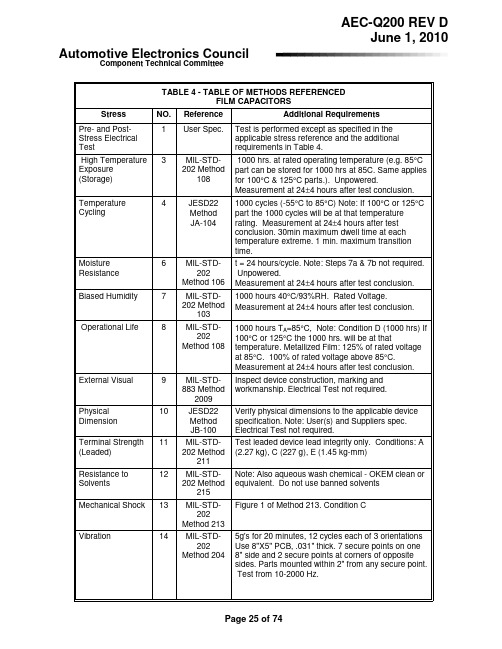

Automotive Electronics Council

Component Technical Committee

TABLE 4 - TABLE OF METHODS REFERENCED FILM CAPACITORS Stress Pre- and PostStress Electrical Test High Temperature Exposure (Storage) Temperature Cycling NO. 1 Reference User Spec. Additional Requirements Test is performed except as specified in the applicable stress reference and the additional requirements in Table 4. 1000 hrs. at rated operating temperature (e.g. 85°C part can be stored for 1000 hrs at 85C. Same applies for 100°C & 125°C parts.). Unpowered. Measurement at 24±4 hours after test conclusion. 1000 cycles (-55°C to 85°C) Note: If 100°C or 125°C part the 1000 cycles will be at that temperature rating. Measurement at 24±4 hours after test conclusion. 30min maximum dwell time at each temperature extreme. 1 min. maximum transition time. t = 24 hours/cycle. Note: Steps 7a & 7b not required. Unpowered. Measurement at 24±4 hours after test conclusion. 1000 hours 40°C/93%RH. Rated Voltage. Measurement at 24±4 hours after test conclusion. 1000 hours TA=85°C, Note: Condition D (1000 hrs) If 100°C or 125°C the 1000 hrs. will be at that temperature. Metallized Film: 125% of rated voltage at 85°C. 100% of rated voltage above 85°C. Measurement at 24±4 hours after test conclusion. Inspect device construction, marking and workmanship. Electrical Test not required. Verify physical dimensions to the applicable device specification. Note: User(s) and Suppliers spec. Electrical Test not required. Test leaded device lead integrity only. Conditions: A (2.27 kg), C (227 g), E (1.45 kg-mm) Note: Also aqueous wash chemical - OKEM clean or equivalent. Do not use banned solvents Figure 1 of Method 213. Condition C

AEC-Q200试验项目以及要求中文

77pcs

1 0

湿度存储

7

77pcs

1 0

工作寿命

8

MIL-PRF-27

77pcs

1 0

外观

9

MIL-STD-883 2009

所有提交认 证的产品

0

尺寸

10

JESD22 Method JB-100 按器件详细规格验证物理尺寸。 不要求电气测试。 MIL-STD-202 211 MIL-STD-202 215 MIL-STD-202 213 Method 条件:A(910g), C(1.13kg),E(1.45kg-mm)

Method 5g , 20min , 频率 10~20000Hz , DG XYZ三方向每方向12个循环。 器 件 焊 接 在 203mm*127mm*0.8mm 的 PCB 上,一侧长边安置 7 个固定点,另 外 2 个固定点位于对角位置,器件 距离固定点50mm以内; Method 条件 B,样品不进行预热。注意: DG 单一波峰焊-表贴元件按照程序2; 插针产品按照程序 1 进行焊接,浸 入器件本体1.5mm的深度。 或 D

0 1 0

高温存储

3

MIL-STD-202 Method108

77pcs

温度循环

4

JESD22 Method JA-104 1000个循环(-40~125℃) DG 每个温度的驻留时间 30min ,转换 时间不超过1min。 试验结束后 24+-4 小时内进行电气 测试 MIL-STD-202 Method103 在温度85℃,湿度85%的条件下放 DG 置1000小时,不通电。试验结束后 24+-4小时进行电气测试。 DG 125℃,1000小时; 器件需通电工作; 125 ℃包括器件 本体因通电产生的温度; 试验结束后 24+-4 小时进行电气测 试。 Method 检查器件结构,标识和工艺质量; NG 不要求电气测试;

OARS中文资料

* Dependent on ohmic value

T

2.36

±0.25

D

4.83

±0.76

4.7

±0.76

4.83

±0.76

W a nom. b nom. c nom. d nom.

3.18

±0.38

3.56

±0.38

6.35

±0.38

4.07

4.45 7.24

9.37 9.58

3.07 3.18

Meets JIS-C-6429 Meets MIL-STD-002 Method 215

Meets J-STD-002 Method B

>R015

>R007 40 0.75 1 0.75 1 0.5 1 1

Pulse Energy Rating

120 100

80 60 40 20

0 0 25 50 75 100 125 150 175 Am bient Tem perature (Deg C)

OARS-XP

Note: This graph relates to single pulses of short duration (≤ 100ms). Higher energy limits apply for longer pulses and overloads

% of Rated Power

Dimensions (mm) and recommended solder pads

Type

L

H

OARS1 >R003, OARS-1Z 11.18

3.05 ±0.76

OARS1-R003

±0.38

3.51

AEC-Q200 中文(单一元件)

耐溶解力

机械冲击

振动

耐焊接热

ESD

MIL-STD12 202 Method 215 MIL-STD13 202 Method 213 MIL-STD14 202 Method 204 MIL-STD15 202 Method 210 AEC-Q200002 or 17 ISO/DIS 10605

Байду номын сангаас

水系化学清洗。OKEM清洗或等同。

可焊性 电性能描述 线路板弯曲 引线强度 (SMD)

引脚产品和SMD都适用。不用电性能测试。50倍放大,条件: 引脚产品Method A@235℃,category 3. 18 J-STD-002 SMD 产品:a)Method B,4小时@155℃干热@235 ℃ b)Method B @215℃ category3 c)Method D category3 @260℃ 19 User Spec 每批和规定数量的样品进行参数测试。室温下和工作温度下最小,最大平均,标准值。 AEC-Q200最少保留60秒 21 005 AEC-Q20022 006

注:受压前电性能测试也作电性能参数。1000小时测试时250小时和 500小时作间隙测试。

见213方法图1,C条 5g的力20分钟,用8*5*0.031英寸的PCB在3个方向各做12各循环。在8英寸边上有7个支撑点,在对面的角 上两个支撑点。器件安装在任意一个支撑点的2英寸范围内。测试从10HZ-2000HZ. 未预热的样品Condition B. 备注:单波焊接-Porcedure 1 引脚产品焊料少于1.5mm,除了230℃外其他 Procedure 1,SMD产品浸到覆盖SMD引脚。

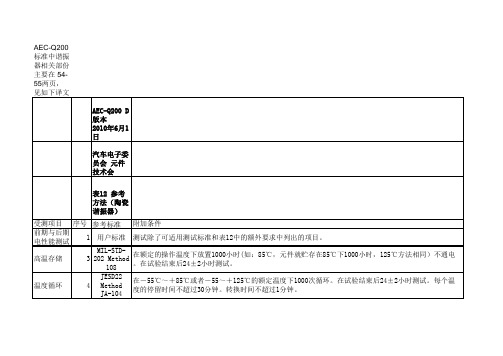

aecq200标准中谐振器相关部份主要在5455两页见如下译文aecq200d版本2010年6月1日汽车电子委员会元件技术会表12参考方法陶瓷谐振器受测项目序号参考标准附加条件前期与后期电性能测试1用户标准测试除了可适用测试标准和表12中的额外要求中列出的项目

如何实现零缺陷的汽车元件设计生产

如何实现零缺陷的汽车元件设计生产汽车与其他普通消费类产品的重要差别之一就是更高的安全性要求。

在汽车产业中,往往系统的功能与质量相比只能处于次要地位。

汽车操控的安全性与组成整个汽车的零件都有密切关系。

每个零部件都被要求能达到最高的质量与可靠性,甚至实现零缺陷(Zero Defect)的理想状态。

汽车零部件及相关产品的最大推动力往往不是先进的技术,而更多的是质量的水平;而质量的提升需要严格管控程序来实现。

目前汽车产业的重要质量管理系统与相关规范包括由汽车电子设备委员会(Automotive Electronics Council, AEC)所提出的各项规范以及QS-9000和TS 16949等。

另外零件提供商也会提出自己的规范,如ST的汽车等级认证(Automotive Grade Qualification)等。

AEC系列规范克莱斯勒、福特和通用汽车/Delco Electronics为建立一套通用的零件资质及质量系统标准而设立了汽车电子委员会(AEC)。

AEC建立了质量控制的标准,同时,由于符合AEC规范的零部件均可被上述三家车厂同时采用,促进了零部件制造商交换其产品特性数据的意愿,并推动了汽车零件通用性的实施,为汽车零件市场的快速成长打下基础。

专门用于芯片应力测试(Stress Test)的认证规范AEC-Q100是AEC的第一个标准。

AEC-Q100于1994年6月首次发表,经过十多年的发展,AEC-Q100已经成为汽车电子系统的通用标准。

在此文件的开发过程中,重要的芯片供应商都有机会提出他们的意见。

该规范能使汽车元件更快速地满足汽车市场的采购需求。

汽车电子元件只要被认定为符合此规范要求即被认为具有高质量与可靠性,并可适合于汽车应用的复杂恶劣的环境中,而不再需要进行反复的循环认证测试。

AEC在AEC-Q100之后又陆续制定了针对离散组件的AEC-Q101和针对被动组件的AEC-Q200等规范,以及AEC-Q001/Q002/Q003/Q004等指导性原则(Guideline)。

AEC-Q200培训教材

测试频率从10-2000赫兹,5g/s的力20分钟, 初始限制 三个方向每个方向12个循环。 260±5℃,时间10±1s,浸入深度1.27mm / C 水蒸*h, (助焊剂:松香+异丙醇) 255±5 º ,深度为0.10mm,停留时间5s+0.5s/-0

15 17 18

MIL-STD-202Method210 AEC-Q200-002 Or ISO/DIS10605 J-STD-002

二、条款简要内容

1.1 描述 AECQ 定义了无源电子器件的低应力测试认证要求和参考测试条件。使用本标准并不是要解除供应商自己内部认证项目的责 任性。在本文中,其中的用户被定义为所有按照规格书使用其认证器件的用户,用户有责任去证实确认所有的认证数据与本 文件相一致。 1.1.1 应力认证测试的定义:应力认证测试定义为成功地完成本标准中定义的测试。每一种无源电子器件要求的低温度范围 (大能力)以及各等级的典型运用案例(指定应用)列于下表: 如果成功完成备注中的器件类型达到的低温度等级的资格认证,那么将允许供应商声称他们的零件通过了该等级或更低等级 的“AEC认证”。对于低于上述低温度的资格鉴定,将仅允许供应商声称他们的零件通过了较低等级的“AEC认证”。

Change<=+/-x% 初始限制 初始限制 初始限制

初始限制 初始限制

耐焊接热 ESD 可焊性

根据AEC-Q200–不需要电气测试

Electrical Characterization 电气特性

19

UserSpec.用户规格

按批次和样品数量要求进行参数试验,总结 列出室温下及低,高工作温度下器件的小值, 初始限制 初始限制 大值,平均值和标准偏差。至少要测量低温 Change<=+/-x% 无要求 度/室温/高温度下的参数CP,DF,IR。见参数 表格中的建议。 只适用于MLCC,至少60秒的支撑时间

AEC_Q004_DRAFT_2

DRAFTAEC - Q004August 31, 2006Automotive Electronics CouncilComponent Technical CommitteeComponent Technical CommitteeAcknowledgmentAny document involving a complex technology brings together experience and skills from many sources. The Automotive Electronics Council would especially like to recognize the following significant contributors to the revision of this document:Sustaining Members:Mark A. Kelly Delphi CorporationJean Clarac Siemens VDOBrian Jendro Siemens VDORobert V. Knoell Visteon CorporationAssociate Members: Guest Members:Tim Haifley Altera David Locker AMRDECDaniel Vanderstraeten AMI Semiconductor Jeff Jarvis AMRDECEarl Fischer AutolivMike Klucher Cirrus LogicXin Miao Zhao Cirrus LogicJohn Timms Continental Automotive SystemsRoy Ozark Continental Automotive SystemsNick Lycoudes FreescaleWerner Kanert Infineon TechnologiesElfriede Geyer Infineon TechnologiesJohn Bertaux International RectifierGary Fisher Johnson ControlsTom Lawler Lattice SemiconductorMike Buzinski MicrochipRob Horton MicrochipAnnette Nettles NEC ElectronicsRaj Radjassamy NEC ElectronicsZhongning Liang NXP SemiconductorsMark Gabrielle ON SemiconductorKen Berry Renesas TechnologyBruce Townsend SpansionAdam Fogle SpansionBrian Mielewski STMicroelectronicsJames Williams Texas InstrumentsDiana Siddall Texas InstrumentsDon Pecko XilinxOther Contributors:Masachi Murase NEC ElectronicsMichael Wieberneit NEC ElectronicsDavid Lehtonen SpansionComponent Technical CommitteeNOTICEAEC documents contain material that has been prepared, reviewed, and approved through the AEC Technical Committee.AEC documents are designed to serve the automotive electronics industry through eliminating misunderstandings between manufacturers and purchasers, facilitating interchangeability and improvement of products, and assisting the purchaser in selecting and obtaining with minimum delay the proper product for use by those other than AEC members, whether the standard is to be used either domestically or internationally.AEC documents are adopted without regard to whether or not their adoption may involve patents or articles, materials, or processes. By such action AEC does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the AEC documents. The information included in AEC documents represents a sound approach to product specification and application, principally from the automotive electronics system manufacturer viewpoint. No claims to be in Conformance with this document shall be made unless all requirements stated in the document are met.Inquiries, comments, and suggestions relative to the content of this AEC document should be addressed to the AEC Technical Committee on the link .Published by the Automotive Electronics Council.This document may be downloaded free of charge, however AEC retains the copyright on this material. By downloading this file, the individual agrees not to charge for or resell the resulting material.Printed in the U.S.A.All rights reservedCopyright © 2006 by Delphi, Siemens VDO, and Visteon Corporation. This document may be freely reprinted with this copyright notice. This document cannot be changed without approval from the AEC Component Technical Committee.Component Technical CommitteeZERO DEFECTS GUIDELINEThe proposed DRAFT of AEC-Q004 is made available for a 6-month industry review period, scheduled to expire on April 1, 2007. All comments and suggested edits should be made by contacting the AEC Technical Committee (/AECRequest.html). After the 6-month review period has expired, all received comments and suggestions will be reviewed by the Technical Committee and incorporated (where applicable) into a final version of the Q004 document.1. SCOPEThis document describes and organizes a set of tools and processes which suppliers and users of integrated circuits can use to approach or achieve the goal of zero defects during a product's lifetime.This guideline makes suggestions for when each of these tools and methods should be used depending on the application or business case.This is not to be construed as a requirements document, but is a tool box of methods that have been used to reduce defects. This is not an exhaustive list. There are suppliers that are using internally developed and proprietary methods to reduce defects. As the part and/or process is optimized and matures over time, less tools are needed to improve or maintain quality and reliability.1.1 PurposeThe flowchart below describes the sequence of steps involved in component design, manufacture, test and use and where each of the zero defect tool or method fits in with this component flow. Each tool or method is described along with how it addresses zero defects, when it would or wouldn't be used, the estimated cost versus benefit, the components and technologies it applies to, the defect type addressed and the metric used to measure performance.Component Technical CommitteeComponent Technical Committee1.2 Reference Documents• AEC-Q100: Stress Test Qualification for Integrated Circuits• AEC-Q101: Stress Test Qualification for Discrete Semiconductors• AEC-Q100-009: Electrical Distribution Assessment• AEC-Q001: Guidelines for Part Average Testing• AEC-Q002: Guidelines for Statistical Yield Analysis• APQP-2: Advanced Product Quality Planning & Control Plan• EIA 659: Failure Mechanism Driven Reliability Monitoring• EIA-557-A: Statistical Process Control Systems• FMEA-3: Potential Failure Modes & Effects Analysis, AIAG• JESD50A: Special Requirements for Maverick Product Elimination• JEP13A: Guideline for Constant Temperature Aging to Characterize Aluminum Interconnect Method for Stress Migration Induced Voiding• JEP119A: A Procedure For Executing SWEAT• JEP122B: Failure Mechanisms and Models for Silicon Semiconductor Devices• JEP131A: Process Failure Modes & Effects Analysis• JEP148: Reliability Qualification of Semiconductor Devices Based Upon Physics of Failure Risks and Applications Assessments• JEP150: Stress Test Drive Qualification of and Failure Mechanisms Associated With Assembled Solid State Surface Mount Components• JESD16-a: Assessment of Average Outgoing Quality Levels in Parts Per Million (PPM)• JESD35: Procedure for Wafer Level Testing of Thin Dielectrics• JESD671: Component Quality Problem Analysis and Corrective Action Requirements• JESD74: Early Life Failure Rate Calculation Procedure for Electronic Components• JESD94: Application Specific Qualification Using Knowledge Based Test Methodology• JESD659: Failure Mechanism Driven Reliability Monitoring• SPC-3: Statistical Process Control, AIAG• JEDEC JESD-46 Customer Notification of Product/Process Changes by Semiconductor SuppliersComponent Technical CommitteeLIST OF REFERENCESSect# Tool AEC JEDEC AIAG SAE IEC Other3.14.1 Failure Mode and EffectAnalysis (FMEA)FMEA-3JEP1313.2 Redundancy3.35.2Built-in Self Test3.45.1Design for Test3.58.1Design for Analysis3.6 Design for Manufacture3.7 Design for Reliability JEP1483.8 Simulation JEP122JEP1483.9 Characterization AEC-Q003AEC-Q100-0094.2 Statistical Analysis ofVariance4.3 Control Plan APQP-24.4 Statistical Process Control EIA557 SPC-35.3 Process/Part Average Testing AEC-Q0015.4 Statistical Bin Yield Analysis AEC-Q0025.5 Data Collection, Storage andRetrieval5.6 Screens JESD50JESD16JESD74 MIL-PRF-19500 MIL-STD-8835.7 Lot Acceptance Gates JESD50JESD16JESD74 6.1 Stress-Strength Analysis6.2 Data Analysis6.3 Industry Standards6.4 Environmental Stress Testing AEC-Q100AEC-Q101AEC-Q200 JESD22 JESD94 JEP1506.5 Part Derating7.1 Wafer Level FailureMechanism Monitoring7.2 Process/ProductImprovementsAEC-Q100 JESD467.3 Production Part Monitoring EIA/JESD6598.2 Problem Solving Techniques JESD6718.3 Failure Analysis Process JESD6718.4 Fault Tree Analysis9.1 System Engineering9.2 Quality Function Deployment1.3 DefinitionsData mining – automating the process of searching for patterns in a data set.Ongoing defect – typically a common cause or intrinsic failure that follows a trend Spike defect – typically a special cause or extrinsic failure that occurs infrequently NTF – No trouble foundTNI – Trouble not identifiedComponent Technical Committee2. RECOMMENDATIONSP recommended/needed O may be used O not recommended/neededSect Tool All newparts atthe designstageHighcomplexitypartLowcomplexitypartFully matureor nearobsolescentcomponentCostsensitivepart orapplicationDesignorprocesschangeIssueorfailureoccursLowreliabilityapplicationHigh reliabilityor safetycriticalapplication3.14.1 Failure Mode and EffectAnalysis FMEAP O O O O P P O P3.2 Redundancy O P O O O O O O P 3.35.2Built-in Self Test O P O O O O P O P3.45.1Design for Test P P O O O P P O P3.58.1Design for Analysis O P O O O O P O P 3.6 Design for Manufacture O O O O O P P O P 3.7 Design for Reliability O O O O O O P O P 3.8 Simulation P P O O P O P O P3.9 Characterization P P O O O P O O P4.2 Statistical Analysis ofVarianceO O O O O O P O O 4.3 Control Plan O O O O O P O O P 4.4 Statistical ProcessControlP P P P P P P P P5.3 Process/Part AverageTestingP O O O O O O O P5.4 Statistical Bin YieldAnalysisP O O O O O O O P5.5 Data Collection, Storageand RetrievalO O O P O P P O O 5.6 Screens P P P P P P P P P5.7 Lot Acceptance Gates O P O P P O O P O6.1 Stress-Strength Analysis O P O O O O O O P 6.2 Data Analysis P P P P P P P P P 6.3 Industry Standards P P P P P P P P P 6.4 Environmental StressTestingP P O O O P O O P6.5 Part Derating P O P P O O O P O7.1 Wafer Level FailMechanism MonitoringP O O O O O O O P7.2 Process/ProductImprovementsO O O O O P P O P7.3 Production PartMonitoringO O O O O O O O P8.2 Problem SolvingTechniquesO O O O O P P O O8.3 Failure Analysis Process O O O O O P P O O8.4 Fault Tree Analysis O O O O O P P O O9.1 System Engineering P O O O O O O O O 9.2 Quality FunctionDeploymentP O O O O O O O OComponent Technical Committee3. DESIGN3.1 Failure Mode and Effect Analysis (FMEA)3.1.1 DescriptionA process performed by subject experts that identifies potential failure modes and their effects on thesystem and customer, determines their severity, occurrence and detection, and identifies possible causes and controls. The FMEA document identifies the risks associated with something potentially going wrong (creating a defect - out of specification) in the production of the product. The FMEA identifies what controls are placed in the production process to catch any defects at various stages on the processing. This applies both to process and design (product) FMEAs. The FMEA is essentially a collection of lessons learned from other related processes and products.3.1.2 Where this fits in the material flowDFMEAs are performed on all new components and systems before design of component or arrangement of process flow. DFMEAs are also updated for all design changes. This is a living document that can change upon new lessons learned and should be periodically reviewed for accuracy or relevance.3.1.3 Components and technologies this applies to and how it addresses zero defectsDFMEAs identify all potential modes of failure in design, their risks and how to control them.3.1.4 LimitationsNot intended for use with a product that is fully mature or is entering obsoletion.3.1.5 Estimated cost versus benefitCost includes man-hours to generate the expert knowledge document and uncertainty to new unknown failure mechanisms/modes. Benefit includes prioritizing the circuit or process step most susceptible to part failure in order to improve it and communicating learning throughout the organization.3.1.6 Defect type addressed (ongoing or spike)Ongoing (controllable) and spike (extrinsic) defects based on lessons learned.3.1.7 Metrics used and meaning of valuesRisk priority number (product of severity, occurrence and detection) used to pareto which failure mode or mechanism is most influential to product failure.3.1.8 ReferencesFMEA-3: Potential Failure Modes & Effects Analysis, AIAG3.1.9 ExamplesExample of a FMEA is shown in figure 4.1aComponent Technical Committee3.2 Redundancy3.2.1 DescriptionA parallel system of duplicate cells or components that can replace faulty ones seamlessly during thefinal test or actual use of a part. Redundancy can greatly increase the part’s mean time to failure.Another form of redundancy is error correction code to avoid latent data retention errors.3.2.2 Where this fits in the material flowUsed during design and test of logic, memory (e.g., flash, OTP), etc.3.2.3 Components and technologies this applies to and how it addresses zero defectsGreatly reduces failure rates via robust design (transparent cell replacement), and may reduce both 0 km (time zero) and field failure rates. Use for critical memory and application functions or when die size percentage increase is small or low cost vs. benefit.3.2.4 LimitationsDesign or performance restrictions may inhibit the use of redundancy. Not intended for use with low complexity or mature devices. Not to be used for low lifetime applications or where cost per die size is critical.3.2.5 Estimated cost versus benefitCost includes added circuitry, overhead support, and software. Benefit includes much improved reliability.3.2.6 Defect type addressed (ongoing or spike)Both ongoing and spike defects.3.2.7 Metrics used and meaning of valuesYield and number of customer returns.3.2.8 References3.2.9 ExamplesExample of redundancy in a memory array:Component Technical Committee3.3 Built-in Self Test3.3.1 DescriptionThe practice of designing the circuitry such that inputting a logic solution will allow the part to test itself.3.3.2 Where this fits in the material flowIntended for use with high complexity components and is designed into the product.3.3.3 Components and technologies this applies to and how it addresses zero defectsProvides the device with the capability of diagnosing itself for process or design errors which otherwise might go undetected through the development stage. This includes functions or parametrics internal to the device that are not accessible from the outside.3.3.4 LimitationsNot intended for use with low complexity parts. May be possible to switch off and not use as the part and process matures. May increase die size and software code.3.3.5 Estimated cost versus benefitCost includes added circuitry and software. Benefit includes improved fault coverage over the die. 3.3.6 Defect type addressed (ongoing or spike)Ongoing (controllable) and spike (extrinsic) defects.3.3.7 Metrics used and meaning of valuesDefect detectability and test coverage3.3.8 References3.3.9 ExamplesExample of a BIST circuit block and test program is shown in figure 3.3aComponent Technical Committee3.4 Design for Test3.4.1 DescriptionThe practice of designing the circuitry such that as many nodes as possible can be tested in a reasonable amount of time.3.4.2 Where this fits in the material flowIntended for use with high complexity components and is designed into the product.3.4.3 Components and technologies this applies to and how it addresses zero defectsProvides the capability for testing as many nodes as possible and, thus, providing maximum fault coverage during test.3.4.4 LimitationsNot intended for use with low complexity parts.3.4.5 Estimated cost versus benefitCost includes layout complexity, potential design time increase, and test software development.Benefit includes more efficient defect screening.3.4.6 Defect type addressed (ongoing or spike)Ongoing (controllable) and spike (extrinsic) defects.3.4.7 Metrics used and meaning of valuesTest coverage, reduced incidence of NPF/TNI, and improved cycle time.3.4.8 References3.4.9 ExamplesExample of a test program with percent fault coverage and test time is shown in figure 3.4aComponent Technical Committee3.5 Design for Analysis3.5.1 DescriptionThe practice of designing the circuitry such that failure analysis can be performed as efficiently as possible for elimination of no defect found.3.5.2 Where this fits in the material flowIntended for use with all components having a large number of metal layers or unique interconnection schemes (e.g., chip-on-chip). Designed into the product.3.5.3 Components and technologies this applies to and how it addresses zero defectsProvides the capability of a more accurate and accessible analysis of failures which otherwise could be masked by the proliferation of materials and features over the failed site.3.5.4 LimitationsNot intended for use with low complexity parts (few metal levels).3.5.5 Estimated cost versus benefitCost includes layout complexity and potential design time increase. Benefit includes easier and more efficient failure analysis.3.5.6 Defect type addressed (ongoing or spike)Ongoing (controllable) and spike (extrinsic) defects.3.5.7 Metrics used and meaning of valuesReduced cycle time for FA and reduced incidence of NPF/TNI.3.5.8 References3.5.9 ExamplesExample of chip designs allowing for DFA is shown in figure 3.5aComponent Technical Committee3.6 Design for Manufacture3.6.1 DescriptionThe practice of designing the circuitry so that the part can be more easily manufactured via larger design margins. These designs are intended to reduce the effects of extrinsic defects on the device, such as particulates and process margins (e.g., lithography definition).3.6.2 Where this fits in the material flowIntended for use in new processes or sub-processes, new technology, new material sets or subsets and new fab or assembly sites.3.6.3 Components and technologies this applies to and how it addresses zero defectsExamples include doubling (redundant) vias in areas that are process sensitive (e.g., sparse areas of vias), widen spacing between interconnect lines, reduce the number of critical timing paths using synthesis tools.3.6.4 LimitationsNot intended for use in standard parts or processes and mature processes and technologies.3.6.5 Estimated cost versus benefitCost includes increased die area to accommodate design margin techniques (e.g., redundant vias).Benefit includes reduced manufacturing defects (increased yield).3.6.6 Defect type addressed (ongoing or spike)Ongoing (controllable) and spike (extrinsic) defects.3.6.7 Metrics used and meaning of valuesManufacturing yield, process control improvement3.6.8 References3.6.9 ExamplesExample of design margin for DFM is shown in figure 3.6aFigure 3.6a - Redundant vias in place of isolated onesComponent Technical Committee3.7 Design for Reliability3.7.1 DescriptionRelaxation of design rules without sacrificing performance. The use of physics of failure to determine design and material limitations. Use of computer-aided engineering (CAE) analysis and simulation tools at an early stage in the design can improve product reliability more inexpensively and in a shorter time than building and testing physical prototypes. Tools such as finite element analysis, fluid flow, thermal analysis, integrated reliability prediction models, etc., are becoming more widely used, more user friendly and less expensive. Design of Experiments techniques can provide a structured, proactive approach to improving reliability and robustness as compared to unstructured, reactive design/build/test approaches. Further, these techniques consider the effect of both product and process parameters on the reliability of the product and address the effect of interactions between parameters. Finally, the company should begin establishing a mechanism to accumulate and apply "lessons learned" from the past related to reliability problems as well as other producibility and maintainability issues. These lessons learned can be very useful in avoiding making the same mistakes twice.3.7.2 Where this fits in the material flowIntended for use in new part designs or processes, parts designed for new applications, applications requiring high reliability.3.7.3 Components and technologies this applies to and how it addresses zero defectsProvides the capability of more rapid evaluation of reliability risks and the opportunity to mitigate them early in the design process instead of after pre-development. Eliminating or minimizing the opportunity for mistakes to occur in manufacturing can be done early in the design process.3.7.4 LimitationsNot intended for use in standard designs or processes.3.7.5 Estimated cost versus benefitCost includes risk of lower reliability if the models and simulations are wrong, computer and software overhead, time and cost needed to perform design of experiments, expertise in failure mechanisms.Benefits include a reduction in material needed for validation, faster cycle time, higher reliability if the models and simulation are right.3.7.6 Defect type addressed (ongoing or spike)Ongoing (controllable) and spike (extrinsic) defects.3.7.7 Metrics used and meaning of valuesMean time to failure, warranty returns.3.7.8 ReferencesJEP13A: Guideline for Constant Temperature Aging to Characterize Aluminum Interconnect Method for Stress Migration Induced VoidingJEP119A: A Procedure For Executing SWEATJEP148: Reliability Qualification of Semiconductor Devices Based Upon Physics of Failure Risks and Applications AssessmentsJESD35: Procedure for Wafer Level Testing of Thin Dielectrics/lifecycle.html3.7.9 Examples• Design based on the expected range of the operating environment.• Design to minimize or balance stresses and thermal loads and/or reduce sensitivity to these stresses or loads.Component Technical Committee• De-rate components for added margin.• Provide subsystem redundancy.• Use proven component parts & materials with well-characterized reliability.• Reduce parts count & interconnections (and their failure opportunities).• Improve process capabilities to deliver more reliable components and assemblies.Component Technical Committee3.8 Simulation3.8.1 DescriptionRecreating the functioning of the component through computer modeling using established engineering and physics-based relationships to functionality, construction and reliability.3.8.2 Where this fits in the material flowPerformed on all components during the design phase and possibly during the evaluation phase.May be used during production to aid in debug or failure analysis (FA). Simulation should ALWAYS be used for every significant silicon pass.3.8.3 Components and technologies this applies to and how it addresses zero defectsVerifies functional operation of the device in addition to highlighting process, voltage and temperature sensitivities related directly to the design and process parametrics.3.8.4 LimitationsNot intended for use after the component has been ramped up to full production (i.e., after initial release of the product). It may not always be needed in determining production yield issues or FA.3.8.5 Estimated cost versus benefitIrrelevant during the design phase as it is impossible to design without simulation. May be slightly different if trying to use simulation as means to identify process or modeling issues. Cost includes running and analyzing data, and Q&R simulation program development/purchase. Benefit includes mitigating defects in design that otherwise would promulgate to manufacturing.3.8.6 Defect type addressed (ongoing or spike)Both ongoing and spike defects.3.8.7 Metrics used and meaning of valuesDirect simulation of specified parameters and functions. Parameter fit to empirical data, confidence bound.3.8.8 ReferencesJEP122B: Failure Mechanisms and Models for Silicon Semiconductor DevicesJEP148: Reliability Qualification of Semiconductor Devices Based Upon Physics of Failure Risks and Applications Assessments3.8.9 ExamplesExample of a simulation is shown in figure 3.8aComponent Technical Committee3.9 Characterization3.9.1 DescriptionThe process of collecting and analyzing data in order to understand the attributes, behavior and limitations of a process, product design and the package. The characterization is performed to generate the specification or datasheet for the product, process or package. Intent is to look at parametric performance of the device with temperature, voltage, frequency, etc. Characterized parts, generated either via corner lot processing or sorted as extreme parametric values, can then be applied to the application to determine sensitive process corners that the supplier can either shift or tighten the process away from or sort out at test.3.9.2 Where this fits in the material flowTypically performed on all new and changed components involving new designs or processes, at wafer probe or final test.3.9.3 Components and technologies this applies to and how it addresses zero defectsEstablishes the functional and parametric performance of the device by determining the electrical and process parametric and performance limits. The "sweet spot" of the process is then fed back into manufacturing where it can be controlled.3.9.4 LimitationsNot intended for use after the component has been ramped up to full production (i.e., after initial release of the product).3.9.5 Estimated cost versus benefitCost includes added testing for various parameters such as temperature, voltage, frequency, etc., and manufacturing corner lots varying parameters such as Vtn, Vtp, CD, Rs, etc.. Benefit includes centering of the process, test versus the intended application, and establishing more accurate process and test limits.3.9.6 Defect type addressed (ongoing or spike)Ongoing.3.9.7 Metrics used and meaning of valuesMean, minimum, maximum standard deviation, sample size, Cp, Cpk vs. datasheet or test limits, temperature, voltage, frequency, and process corner variables (e.g., Vt, Leff, Rs, CD). Determines capability.3.9.8 ReferencesAEC-Q003AEC-Q100-009: Electrical Distribution Assessment3.9.9 ExamplesExample of a characterization is shown in figure 3.9a-dComponent Technical Committee Schmoo plotComponent Technical Committee4. MANUFACTURING4.1 Failure Mode and Effect Analysis (FMEA)4.1.1 DescriptionA process performed by subject experts that identifies potential failure modes and their effects on thesystem and customer, determines their severity, occurrence and detection, and identifies possible causes and controls. The FMEA document identifies the risks associated with something potentially going wrong (creating a defect - out of specification) in the production of the product. The FMEA identifies what controls are placed in the production process to catch any defects at various stages on the processing. This applies both to process and design (product) FMEAs.4.1.2 Where this fits in the material flowPerformed on all new components and systems before design of component or arrangement of process flow. This is a living document that can change upon new lessons learned and should be periodically reviewed for accuracy or relevance.4.1.3 Components and technologies this applies to and how it addresses zero defectsIdentifies all potential modes of failure in design and process, their risks and how to control them.4.1.4 LimitationsNot intended for use with a product that is fully mature or is entering obsoletion.4.1.5 Estimated cost versus benefitCost includes man-hours to generate the expert knowledge document and uncertainty to new unknown failure mechanisms/modes. Benefit includes prioritizing the circuit or process step most susceptible to part failure in order to improve it, and communicating learning throughout the organization.4.1.6 Defect type addressed (ongoing or spike)Ongoing (controllable) and spike (extrinsic) defects.4.1.7 Metrics used and meaning of valuesRisk priority number (product of severity, occurrence and detection) used to pareto which failure mode or mechanism is most influential to product failure.4.1.8 ReferencesFMEA-3: Potential Failure Modes & Effects Analysis, AIAGJEP131A: Process Failure Modes & Effects Analysis4.1.9 ExamplesExample of a FMEA is shown in figure 4.1a。

AEC Q200试验条件

AEC Q200试验条件aec-q200试验条件Aec-q200试验条件:注:Aec-q200的环境试验条件主要根据mil-std-202和jedec22a-104规范制定。

除了不同部件的不同测试温度外,所用电源(电压、电流和负载)的要求也会不同。

高温贮存不施加偏压和载荷,但在高温工作寿命中是必要的,温度循环和温度n吹的试验目的和方法不同。

在温度循环中,需要控制高低温变化的温度变化率,但不需要控制n-blow温度。

高湿度通常被称为高温高湿试验,耐湿性则是湿冻结试验试验条件注意事项:1000h试验过程需在250h、500h进行间隔量测高温储存(mil-std-202-108):[适用设备:ths]薄膜电容、网路低通滤波器、网路电阻、热敏电阻、可变电容、可变电阻、陶瓷共鸣器、emi干扰抑制器、emi干扰过滤器:85℃/1000h电感、变压器、电阻:125℃/1000h变阻器:150℃/1000h钽电容器、陶瓷电容器、铝电解电容器:最高额定温度/1000h高温工作寿命(mil-std-202-108):[适用设备:ths]网路低通滤波器、网路电阻:85℃/1000hEMI干扰抑制器、EMI干扰滤波器:85℃/1000h/外加额定IL钽电容器、陶瓷电容器:最高额定温度/1000h/(2/3)负载/额定电压铝电解电容器、电感、变压器:105℃/1000h薄膜电容:1000h/(85℃/125%额定电压、105℃&125℃/100%额定电压)自恢复保险丝:125℃/1000h电阻、热敏电阻和可变电容:125℃/1000h/额定电压可变电阻:125℃/1000h/额定功率变阻器:125℃/1000h/额定电压85%+ma电流陶瓷谐振器:85℃/1000h/额定VDD+1mΩ,并联逆变器在每个晶体引脚和接地之间有2倍晶体CL电容石英震u器:125℃/1000h/额定vdd+1mω,并联逆变器,在每个晶体脚和地之间有2x的晶体cl电容温度循环(jedec22a-104):[适用设备:TSR、ESS]薄膜电容器、可变电容器、可变电阻、陶瓷谐振器、EMI干扰抑制器、EMI干扰滤波器:-55℃(30分钟)←→ 85℃(30分钟)/缓变(15℃/min)/1000次循环钽电容、陶瓷电容、电阻、热敏电阻:-55℃(30min)←→125℃(30min)/ramp(15℃/min)/1000cycles铝电解电容器:-40℃(30分钟)←→ 105℃(30分钟)/斜坡(15℃/min)/1000周电感、变压器、变阻器、石英振子、自恢复保险丝:-40℃(30分钟)←→ 125℃(30min)/缓变(15℃/min)/1000次循环网路低通滤波器、网路电阻:-55℃(30min)←→125℃(30min)/ramp(15℃/min)/1000cycles温度N-Strike(mil-std-202-107):[适用设备:TC、TSK]自恢复保险丝:-40℃(15min)←→125℃(15min)/300cycles偏高湿度(mil-std-202-103):[适用设备:ths]钽电容器和陶瓷电容器:85℃/85%R.H./1000h/电压1.3~1.5V电感和变压器:85℃/85%R.H./1000h/非通电铝电解电容器:85℃/85%R.H./1000h/额定电压emi干扰抑制器、emi干扰过滤器:85℃/85%r.h./1000h/额定电压&电流电阻、热敏电阻:85℃/85%r.h./1000h/工作电源10%自恢复保险丝:85℃/85%r.h./1000h/额定电流10%可变电容和可变电阻:85℃/85%R.H./1000h/10%额定功率网路低通滤波器&网路电阻:85℃/85%r.h./1000h/电压[网路电容(额定电压)、网路电阻(10%额定功率)]变阻器:85℃/85%R.H./1000h/额定电压85%+ma电流石英震u器、陶瓷共鸣器:85℃/85%r.h./1000h/额定vdd+1mω,并联逆变器,在每个晶体脚和地之间有2x的晶体cl电容薄膜电容:40℃/93%R.H./1000h/额定电压耐湿性(mil-std-202-106):[适用设备:ths]薄膜电容:(25℃←→65℃/90%r.h.*2cycle)/18h→-10℃/3h,每一cycle共24h,step7a&7b不通电。

AEC_Q003A