M48Z32V-35MT1中文资料

MEMORY存储芯片MT48LC32M16A2P-75IT中文规格书

DDR2 SDRAMMT47H512M4 – 64 Meg x 4 x 8 banks MT47H256M8 – 32 Meg x 8 x 8 banks MT47H128M16 – 16 Meg x 16 x 8 banksFeatures•V DD = 1.8V ±0.1V, V DDQ = 1.8V ±0.1V•JEDEC-standard 1.8V I/O (SSTL_18-compatible)•Differential data strobe (DQS, DQS#) option•4n-bit prefetch architecture•Duplicate output strobe (RDQS) option for x8•DLL to align DQ and DQS transitions with CK •8 internal banks for concurrent operation •Programmable CAS latency (CL)•Posted CAS additive latency (AL)•WRITE latency = READ latency - 1 t CK •Programmable burst lengths: 4 or 8•Adjustable data-output drive strength•64ms, 8192-cycle refresh•On-die termination (ODT)•Industrial temperature (IT) option•RoHS-compliant•Supports JEDEC clock jitter specification Options1Marking •Configuration–512 Meg x 4 (64 Meg x 4 x 8 banks)512M4–256 Meg x 8 (32 Meg x 8 x 8 banks)256M8–128 Meg x 16 (16 Meg x 16 x 8 banks)128M16•FBGA package (Pb-free) – x16–84-ball FBGA (11.5mm x 14mm) Rev. A HG •FBGA package (Pb-free) – x4, x8–60-ball FBGA (11.5mm x 14mm) Rev. A HG •FBGA package (Pb-free) – x16–84-ball FBGA (9mm x 12.5mm) Rev. C RT •FBGA package (Pb-free) – x4, x8–60-ball FBGA (9mm x 11.5mm) Rev. C EB •FBGA package (Lead solder) – x16–84-ball FBGA (9mm x 12.5mm) Rev. C PK •Timing – cycle time– 1.875ns @ CL = 7 (DDR2-1066)-187E– 2.5ns @ CL = 5 (DDR2-800)-25E– 2.5ns @ CL = 6 (DDR2-800)-25– 3.0ns @ CL = 5 (DDR2-667)-3•Self refresh–Standard None •Operating temperature–Commercial (0°C ื T C ื +85°C)None–Industrial (–40°C ื T C ื +95°C;–40°C ื T A ื +85°C)IT •Revision:A/:CNote: 1.Not all options listed can be combined todefine an offered product. Use the PartCatalog Search on forproduct offerings and availability.2Gb: x4, x8, x16 DDR2 SDRAMFeaturesFunctional DescriptionThe DDR2 SDRAM uses a double data rate architecture to achieve high-speed opera-tion. The double data rate architecture is essentially a 4n -prefetch architecture, with an interface designed to transfer two data words per clock cycle at the I/O balls. A single READ or WRITE operation for the DDR2 SDRAM effectively consists of a single 4n -bit-wide, two-clock-cycle data transfer at the internal DRAM core and four corresponding n -bit-wide, one-half-clock-cycle data transfers at the I/O balls.A bidirectional data strobe (DQS, DQS#) is transmitted externally, along with data, for use in data capture at the receiver. DQS is a strobe transmitted by the DDR2 SDRAM during READs and by the memory controller during WRITEs. DQS is edge-aligned with data for READs and center-aligned with data for WRITEs. The x16 offering has two data strobes, one for the lower byte (LDQS, LDQS#) and one for the upper byte (UDQS,UDQS#).The DDR2 SDRAM operates from a differential clock (CK and CK#); the crossing of CK going HIGH and CK# going LOW will be referred to as the positive edge of CK. Com-mands (address and control signals) are registered at every positive edge of CK. Input data is registered on both edges of DQS, and output data is referenced to both edges of DQS as well as to both edges of CK.Read and write accesses to the DDR2 SDRAM are burst-oriented; accesses start at a se-lected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an ACTIVATE command, which is then followed by a READ or WRITE command. The address bits registered coincident with the ACTIVATE command are used to select the bank and row to be accessed. The ad-dress bits registered coincident with the READ or WRITE command are used to select the bank and the starting column location for the burst access.The DDR2 SDRAM provides for programmable read or write burst lengths of four or eight locations. DDR2 SDRAM supports interrupting a burst read of eight with another read or a burst write of eight with another write. An auto precharge function may be en-abled to provide a self-timed row precharge that is initiated at the end of the burst ac-cess.As with standard DDR SDRAM, the pipelined, multibank architecture of DDR2 SDRAM enables concurrent operation, thereby providing high, effective bandwidth by hiding row precharge and activation time.A self refresh mode is provided, along with a power-saving, power-down mode.All inputs are compatible with the JEDEC standard for SSTL_18. All full drive-strength outputs are SSTL_18-compatible.Industrial TemperatureThe industrial temperature (IT) option, if offered, has two simultaneous requirements:ambient temperature surrounding the device cannot be less than –40°C or greater than 85°C, and the case temperature cannot be less than –40°C or greater than 95°C. JEDEC specifications require the refresh rate to double when T C exceeds 85°C; this also requires use of the high-temperature self refresh option. Additionally, ODT resistance, input/output impedance and I DD values must be derated when T C is < 0°C or > 85°C.2Gb: x4, x8, x16 DDR2 SDRAM Functional Description。

MEMORY存储芯片MT48LC32M16A2TG-75C中文规格书

Figure 33: WRITE Burst Followed by PRECHARGE – WL = 1, BL = 4Transitioning dataAuto PrechargeBefore a new row can be opened in an active bank, the active bank must be precharged using either the PRECHARGE command or the auto precharge function. When a READ or WRITE command is issued to the device, the auto precharge bit (AP) can be set to enable the active bank to automatically begin precharge at the earliest possible mo-ment during the burst READ or WRITE cycle.If AP is LOW when the READ or WRITE command is issued, then normal READ or WRITE burst operation is executed and the bank remains active at the completion of the burst.If AP is HIGH when the READ or WRITE command is issued, the auto precharge func-tion is engaged. This feature enables the PRECHARGE operation to be partially or com-pletely hidden during burst READ cycles (dependent upon READ or WRITE latency),thus improving system performance for random data access.READ Burst with Auto PrechargeIf AP (CA0f) is HIGH when a READ command is issued, the READ with auto precharge function is engaged.These devices start an auto precharge on the rising edge of the clock BL/2 or BL/2 - 2 +RU(t RTP/t CK) clock cycles later than the READ with auto precharge command, which-ever is greater. For auto precharge calculations, see the PRECHARGE and Auto Pre-charge Clarification table.I DD SpecificationsTable 4: 64 Meg x 16 I DD Specifications1Gb: x16, x32 Automotive Mobile LPDDR2 SDRAM I DD Specifications。

ZFM32F030 系列 32 位微控制器数据手册说明书

ZFM32F030系列32位微控制器数据手册V1.02版本记录版本日期更改者描述V1.002021.11.01第一版V1.012022.03.18第二版V1.022022.05.25第三版目录1简介 (1)1.1概述 (1)1.2主要特点 (1)2管脚描述 (3)2.1TSSOP20封装管脚排布图 (3)2.2QFN32封装管脚排布图 (3)2.3管脚定义表 (4)2.4管脚对应外设表 (7)3系统框图 (9)4系统描述 (10)4.1ARM Cortex®-M0内核 (10)4.2内存映射 (11)4.3嵌套向量中断控制器(NVIC) (13)4.4系统复位 (14)4.5时钟控制 (14)4.6I/O复用配置 (15)5外设描述 (16)5.1GPIO(通用输入/输出接口) (16)5.2UART(通用异步收发器) (16)5.3I2C总线 (16)5.4SPI(串行外设接口) (16)5.5TIM(定时/计数器) (17)5.6PWM(脉冲宽度调制)模块 (17)5.7WDT(看门狗定时器) (17)5.8ADC(模拟/数字转换器) (17)5.9存储器 (18)5.10电源管理 (18)5.10.1睡眠模式 (18)5.10.2停止模式 (18)5.11SWD调试口 (19)6电气规范 (20)6.1绝对最大额定值 (20)6.2电特性表 (20)6.2.1MCU参数 (20)6.2.2BOD参数 (21)6.2.3ADC参数 (21)6.2.4Flash参数 (22)6.2.5SPI参数 (22)6.2.6I2C参数 (24)7封装尺寸 (25)7.1TSSOP20封装 (25)7.2QFN32封装 (26)1简介1.1概述ZFM32F030系列是内嵌ARM Cortex®-M0核的32位低成本通用微控制器。

最高频率可达48MHz,片内集成32KB Flash存储器,4KB SRAM存储器。

MT35中文资料

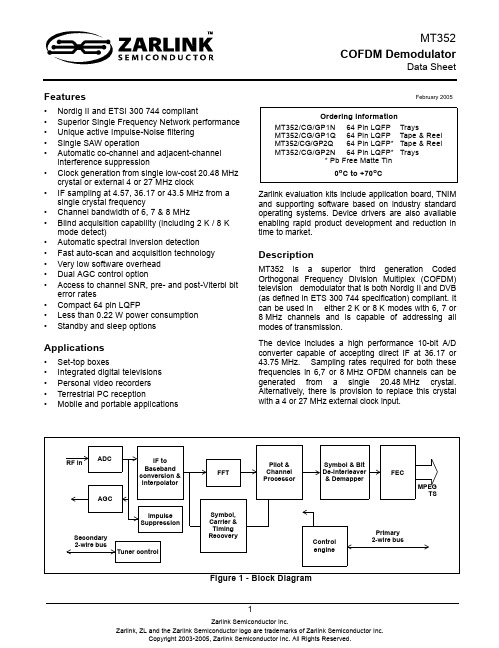

Ordering InformationMT352/CG/GP1N 64 Pin LQFP TraysMT352/CG/GP1Q 64 Pin LQFP Tape & Reel MT352/CG/GP2Q 64 Pin LQFP*Tape & Reel MT352/CG/GP2N 64 Pin LQFP*Trays* Pb Free Matte Tin0o C to +70o CMT352COFDM DemodulatorData SheetFigure 1 - Block DiagramRF inADCAGCSecondary Tuner controlImpulse SuppressionIF to Baseband conversion &InterpolatorFFTSymbol,Carrier &Timing RecoveryPilot &Channel Processor Control engineSymbol & Bit De-interleaver & DemapperFECMPEGTS2-wire busPrimary 2-wire busMT352Data SheetUnique algorithms that actively filter out impulse noise, without affecting normal performance, have been implemented. This reduces the interference effect from vehicles and electrical appliances, which is known to have significant detrimental effect on the quality of digital TV reception.Programming is simplified utilizing a high level command driven interface. A sophisticated engine controls all acquisition and tracking operations as well as controlling the tuner via a 2-wire bus. Any frequency range can be automatically scanned for digital TV channels. This mechanism ensures minimal interaction, maximum flexibility,fastest acquisition and the fastest auto scan capability of any chip in the market.Blind acquisition mode enables automatic detection of all OFDM signal parameters, including mode, guard and spectral inversion. The frequency capture range is sufficient to compensate for the combined offset introduced by the tuner and broadcaster.The device is packaged in a 64 pin LQFP and consumes less than 220mW of power.Figure 2 - Package OutlineMT352 CG YYWW *W ∆•Pin 1 CornerMT352Data Sheet Pin DescriptionPin Description TablePin No Name Description I/O Type V mA MPEG pins47MOSTRT MPEG packet start OCMOS Tristate 3·3148MOVAL MPEG data valid O3·31 49-53, 56-58MDO(0:7)MPEG data bus O3·31 61MOCLK MPEG clock out O3·31 62BKERR Block error O3·31 63MICLK MPEG clock in I CMOS 3·311STATUS Status output O3·31 6IRQ Interrupt output O Open drain56 Control pins4CLK1Serial clock I CMOS55DATA1Serial data I/O Open drain 56 23XTI Low phase noiseoscillatorICMOS24XTO O10SLEEP Device power down I3·3 12, 15-18SADD(4:0)Serial address set I3·344SMTEST Scan mode enable I3·335CLK2/GPP0Serial clock tuner I/OOpen drain 5636DATA2/GPP1Serial data tuner I/O56 42AGC1Primary AGC O56 41AGC2/GPP2Secondary AGC I/O56 43GPP(3)General purpose I/O I/O56 9RESET Device reset I CMOS527OSCMODE Crystal oscillator mode I CMOS3·326PLLTEST PLL analogue test OAnalog inputs30VIN positive input I31VIN negative input ISupply pinsMT352Data Sheet21PLLVDD PLL supplyS 1·822PLLGND S 07, 19, 37, 39, 59, 64CVDD Core logic power S 1·82, 13, 45, 54, VDD I/O ring power S 3·31, 3, 8, 14, 20, 25, 38, 40, 46, 55, 60GND Core and I/O ground S 028AVDD ADC analog supplyS 1·829, 32AGND S 033DVDD ADC digital supply S 1·834DGNDSPin Description Table (continued)Pin NoName Description I/O TypeV mATable of ContentsFeatures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 1.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81.1 Analogue-to-Digital Converter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .91.2 Automatic Gain Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .91.3 IF to Baseband Conversion. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .91.4 Adjacent Channel Filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101.5 Interpolation and Clock Synchronisation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101.6 Carrier Frequency Synchronisation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101.7 Symbol Timing Synchronisation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101.8 Fast Fourier Transform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101.9 Common Phase Error Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101.10 Channel Equalisation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101.11 Impulse Filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101.12 Transmission Parameter Signalling (TPS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111.13 De-Mapper. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111.14 Symbol and Bit De-Interleaving. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111.15 Viterbi Decoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111.16 MPEG Frame Aligner . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111.17 De-interleaver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111.18 Reed-Solomon Decoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111.19 De-scrambler. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121.20 MPEG Transport Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122.0 Software control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123.0 Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123.1 2-Wire Bus. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133.2 Host. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133.2.1 Tuner . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133.2.2 Examples of 2-Wire Bus Messages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143.2.3 Primary 2-Wire Bus Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143.3 MPEG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.3.1 Data Output Header Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.3.2 MPEG data output signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.3.3 MPEG Output Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.3.3.1 MOCLKINV = 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173.3.3.2 MOCLKINV = 0. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .174.0 Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .194.1 Recommended Operating Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .194.2 Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .194.3 DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .204.4 Crystal Specification and External Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215.0 Application Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22Figure 1 - Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - Package Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 Figure 3 - OFDM Demodulator Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 4 - FEC Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 5 - Primary Interfaces. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 6 - Primary 2-Wire Bus Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 7 - DVB Transport Packet Header Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 8 - MPEG Output Data Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 9 - MPEG Timing - MOCLKINV = 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Figure 10 - MPEG Timing - MOCLKINV = 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 11 - Crystal Oscillator Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Figure 12 - Typical Application Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22Table 1 - Programmable Address Details for 2-Wire Bus in TNIM Evaluation Application. . . . . . . . . . . . . . . . . . . 13 Table 2 - Timing of 2-Wire Bus. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Table 3 - MOCLKINV = 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Table 4 - MDOSWAP = 0. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Table 5 - MDOSWAP = 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181.0 Functional DescriptionA functional block diagram of the MT352 OFDM demodulator is shown in Figure 3. This accepts an IF analogue signal and delivers a stream of demodulated soft decision data to the on-chip Viterbi decoder. Clock, timing and frequency synchronization operations are all digital and there are no analogue control loops except the AGC. The frequency capture range is large enough for all practical applications. This demodulator has novel algorithms to combat impulse noise as well as co-channel and adjacent channel interference. If the modulation is hierarchical, the OFDM outputs both high and low priority data streams. Only one of these streams is FEC-decoded, but the FEC can be switched from one stream to another with minimal interruption to the transport stream.Figure 3 - OFDM Demodulator DiagramThe FEC module shown in Figure 4 consists of a concatenated convolutional (Viterbi) and Reed-Solomon decoder separated by a depth-12 convolutional de-interleaver. The Viterbi decoder operates on 5-bit soft decisions to provide the best performance over a wide range of channel conditions. The trace-back depth of 128 ensures minimum loss of performance due to inevitable survivor truncation, especially at high code rates. Both the Viterbi and Reed-Solomon decoders are equipped with bit-error monitors. The former provides the bit error rate (BER) at the OFDM output. The latter is the more useful measure as it gives the Viterbi output BER. The error collecting intervals of these are programmable over a very wide range.Figure 4 - FEC Block DiagramThe FSM controller shown in Figure 3 above controls both the demodulator and the FEC. It also drives the 2-wire bus to the tuner. The controller facilitates the automated search of all parameters or any sub-set of parameters of the received signal. It can also be used to scan any defined frequency range searching for OFDM channels. Thismechanism provides the fast channel scan and acquisition performance, whilst requiring minimal software overhead in the host driver.The algorithms and architectures used in the MT352 have been heavily optimized to minimize hardware and chip area. This is proven by its 220mW (typical) power consumption, which is the lowest of any OFDM device in the market today.1.1 Analogue-to-Digital ConverterThe MT352 has a high performance 10-bit analogue-to-digital converter (ADC) which can sample a 6, 7 or 8MHz bandwidth OFDM signal, with its spectrum centred at:• 4.57MHz near-zero IF•36.17MHz IF•43.75MHz IFThe ADC can be clocked using:•Crystal oscillator with a 20.48MHz crystal• 4 MHz or 27MHz clock inputAn on-chip programmable phase locked loop (PLL) is used to generate the ADC sampling clock. The crystal frequency of 20.48MHz is used for 36.17MHz IF sampling and 19.6267MHz is used for 43.75MHz IF sampling. Note that this 19.6267MHz sampling clock can be generated from the 20.48MHz crystal by appropriately programming the PLL. Hence the same 20.48MHz crystal can support 6, 7 and 8MHz OFDM as well as 36.17 and 43.75MHz IF.1.2 Automatic Gain ControlAn AGC module compares the absolute value of the digitized signal with a programmable reference. The error signal is filtered and is used to control the gain of the amplifier. A sigma-delta modulated output is provided, which has to be RC low-pass filtered to obtain the voltage to control the amplifier. Upper and lower limits can be set to the AGC control voltage using registers.The programmable AGC reference has been optimized. A large value for the reference leads to excessive ADC clipping and a small value results in excessive quantization noise. Hence the optimum value has been determined assuming the input signal amplitude to be Gaussian distributed. The latter is justified by applying the central limit theorem in statistics to the OFDM signal, which consists of a large number of randomly modulated carriers. This reference or target value may have to be lowered slightly for some applications. Slope control bits have been provided for the AGCs and these have to be set correctly depending on the Gain-versus-Voltage slope of the gain control amplifiers.The bandwidth of the AGC is set to a large value for quick acquisition then reduced to a small value for tracking. The AGC is free running during OFDM channel changes and locks to the new channel while the tuner lock is being established. This is one of the features of MT352 used to minimize acquisition time. A robust AGC lock mechanism is provided and the other parts of the MT352 begin to acquire only after the AGC has locked. Two AGC control outputs are available, one to drive an RF amplifier and the other to control an IF amplifier. The parameters for both loops are programmable. In the default mode, only the IF AGC loop is activated.1.3 IF to Baseband ConversionSampling a 36.17MHz IF signal at 20.48MHz results in a spectrally inverted OFDM signal centred at 4.79MHz. Sampling a 43.75MHz IF signal at 19.6267MHz gives a non-inverted signal at 4.5MHz. The first step of the demodulation process is to convert this signal to a complex (in-phase and quadrature) signal in baseband. A correction for spectral inversion is implemented during this conversion process. Note also that the MT352 has control mechanisms to search automatically for an unknown spectral inversion status.1.4 Adjacent Channel FilteringAdjacent channels, in particular the Nicam digital sound signal associated with analogue channels, are filtered prior to the FFT.1.5 Interpolation and Clock SynchronisationMT352 uses digital timing recovery and this eliminates the need for an external VCXO. The ADC samples the signal at a fixed rate, for example, 20.48MHz. Conversion of the 20.48MHz signal to the OFDM sample rate is achieved using the time-varying interpolator. The OFDM sample rate is 64/7MHz for 8 MHz and this is scaled by factors 6/8 and 7/8 for 6 and 7MHz channel bandwidths. The nominal ratio of the ADC to OFDM sample rate is programmed in a MT352 register (defaults are for 20.48MHz sampling and 8MHz OFDM). The clock recovery phase locked loop in the MT352 compensates for inaccuracies in this ratio due to uncertainties of the frequency of the sampling clock.1.6 Carrier Frequency SynchronisationThere can be frequency offsets in the signal at the input to OFDM, partly due to tuner step size and partly due to broadcast frequency shifts, typically 1/6MHz. These are tracked out digitally, without the need for an analogue frequency control (AFC) loop.The default frequency capture range has been set to ±285kHz in the 2K mode and ±142kHz in the 8K mode. However, these values can be doubled, if necessary, by programming an on-chip register. It is recommended that this larger capture range be used for channel scan in order to find channels with broadcast frequency shifts, without having to adjust the tuner.After the OFDM module has locked, the frequency offset can be read from an on-chip register.1.7 Symbol Timing SynchronisationThis module computes the optimum sample position to trigger the FFT in order to eliminate or minimize inter-symbol interference in the presence of multi-path distortion. Furthermore, this trigger point is continuously updated to dynamically adapt to time-variations in the transmission channel.1.8 Fast Fourier TransformThe FFT module uses the trigger information from the timing synchronization module to set the start point for an FFT. It then uses either a 2K or 8K FFT to transform the data from the time domain to the frequency domain. An extremely hardware-efficient and highly accurate algorithm has been used for this purpose.1.9 Common Phase Error CorrectionThis module subtracts the common phase offset from all the carriers of the OFDM signal to minimize the effect of the tuner phase noise on system performance.1.10 Channel EqualisationThis consists of two parts. The first part involves estimating the channel frequency response from pilot information. Efficient algorithms have been used to track time-varying channels with a minimum of hardware. The second part involves applying a correction to the data carriers based on the estimated frequency response of the channel. This module also generates dynamic channel state information (CSI) for every carrier in every symbol.1.11 Impulse FilteringMT352 contains several mechanisms to reduce the impact of impulse noise on system performance.1.12 Transmission Parameter Signalling (TPS)An OFDM frame consists of 68 symbols and a superframe is made up of four such frames. There is a set of TPS carriers in every symbol and all these carry one bit of TPS. These bits, when combined, include information about the transmission mode, guard ratio, constellation, hierarchy and code rate, as defined in ETS 300 744. In addition, the first eight bits of the cell identifier are contained in even frames and the second eight bits of the cell identifier are in odd frames. The TPS module extracts all the TPS data, and presents these to the host processor in a structured manner.1.13 De-MapperThis module generates soft decisions for demodulated bits using the channel-equalized in-phase and quadrature components of the data carriers as well as per-carrier channel state information (CSI). The de-mapping algorithm depends on the constellation (QPSK, 16QAM or 64QAM) and the hierarchy α = 0, 1, 2 or 3). Soft decisions for both low- and high-priority data streams are generated.1.14 Symbol and Bit De-InterleavingThe OFDM transmitter interleaves the bits within each carrier and also the carriers within each symbol. The de-interleaver modules consist largely of memory to invert these interleaving functions and present the soft decisions to the FEC in the original order.1.15 Viterbi DecoderThe Viterbi decoder accepts the 5-bit soft decision data from the OFDM demodulator and outputs a decoded bit-stream. The decoder does the de-puncturing of the input data for all code rates other than 1/2. It then evaluates the branch metrics and passes these to a 64-state path-metric updating unit, which in turn outputs a 64-bit word to the survivor memory. The Viterbi decoded bits are obtained by tracing back the survivor paths in this memory. A trace-back depth of 128 is used to minimize any loss in performance, especially at high code rates.The decoder re-encodes the decoded bits and compares these with received data (delayed) to compute bit errors at its input, on the assumption that the Viterbi output BER is significantly lower than its input BER.1.16 MPEG Frame AlignerThe Viterbi decoded bit stream is aligned into 204-byte frames. A robust synchronization algorithm is used to ensure correct lock and to prevent loss of lock due to noise impulses.1.17 De-interleaverErrors at the Viterbi output occur in bursts and the function of the de-interleaver is to spread these errors over a number of 204-byte frames to give the Reed-Solomon decoder a better chance of correcting these. The de-interleaver is a memory unit which implements the inverse of the convolutional interleaving function introduced by the transmitter.1.18 Reed-Solomon DecoderEvery 188-byte transport packet is encoded by the transmitter into a 204-byte frame, using a truncated version of a systematic (255,239) Reed-Solomon code. The corresponding (204,188) Reed-Solomon decoder is capable of correcting up to eight byte errors in a 204-byte frame. It may also detect frames with more than eight byte errors. In addition to efficiently performing this decoding function, the Reed-Solomon decoder in MT352 keeps a count of the number of bit errors corrected over a programmable period and the number of uncorrectable blocks. This information can be used to compute the post-Viterbi BER.1.19 De-scramblerThe de-scrambler de-randomizes the Reed-Solomon decoded data by generating the exclusive-OR of this with a pseudo-random bit sequence (PRBS). This outputs 188-byte MPEG transports packets. The TEI bit of the packet header is set to indicate uncorrectable packets.1.20 MPEG Transport InterfaceMPEG data can be output in parallel or serial mode. The output clock frequency is automatically chosen to present the MPEG data as uniformly spaced as possible to the transport processor. This frequency depends on the guard ratio, constellation, hierarchy and code rate. There is also an option for the data to be extracted from the MT352 with a clock provided by the user.2.0 Software controlAcquisition of an OFDM channel and frequency scan for OFDM channels are controlled by an on-chip state machine, which minimizes the software requirement in the host processor. To acquire a channel, the host programs the channel frequency in the MT352. The on-chip state machine then writes the frequency information to the tuner, awaits tuner lock and acquires the OFDM channel to generate the transport stream. The controller can be made to automatically search for every parameter in the OFDM signal, including spectral inversion status. Furthermore, this controller will re-acquire the channel in the event of an interruption to the incoming signal.To scan a frequency range, the host programs the start and end frequencies for the search as well as the step size, which defaults to 8 MHz. The MT352 then automatically scans the frequency range by appropriately programming the tuner and searching for OFDM signals. Once a channel has been located, the host is interrupted to read the channel information from the MT352. Then MT352 continues the search. By default, only the channels which can generate a reliable transport stream are reported, but there is also provision for locating very weak channels. The frequency capture range of MT352 can be maximized to capture channels with frequency offsets without re-programming the tuner, in both 2K and 8K modes.The above approach to channel acquisition and scan has resulted in very fast acquisition and scan times whilst minimizing software overhead in the host processor. Furthermore, all this functionality has very efficiently been mapped into hardware to result in a device consuming less than 220mW of power.3.0 InterfacesFigure 5 - Primary InterfacesThe MT352 interfaces to other parts of a terrestrial receiver system can be partitioned into three groups: the host controller, the tuner and the MPEG decoder. One other pin, the Status output, is multi-functional and can directlydrive a LED to show the status of a range of different internal lock flags. Alternatively, it can drive an audio transducer to give an audio frequency that is dependent upon the error rate of the received signal.This feature can be used for faster installation of a system where the aerial may need to be adjusted, as signal strength is not the best guide for the optimum aerial position for COFDM reception.3.1 2-Wire Bus3.2 HostThe primary 2-wire bus serial interface uses pins:•DATA1 (pin 5) serial data, the most significant bit is sent first.•CLK1 (pin 4) serial clock.The 2-wire bus address is determined by applying VDD or VSS to the SADD[4:0] pins.In the current TNIM evaluation application, the 2-wire bus address is 0001 111 R/ W with the pins connected as follows:ADDR[7] ADDR[6] ADDR[5] ADDR[4] ADDR[3] ADDR[2] ADDR[1]Not programmable SADD[4] SADD[3] SADD[2] SADD[1] SADD[0]VSS VSS VSS VDD VDD VDD VDD Table 1 - Programmable Address Details for 2-Wire Bus in TNIM Evaluation ApplicationWhen the MT352 is powered up, the RESET pin 28 should be held low for at least 50ms after VDD has reached normal operation levels. As the RESET pin goes high, the logic levels on SADD[4:0] are latched as the 2-wire bus address. ADDR[0] is the R/ W bit.The circuit works as a slave transmitter with the lsb set high or as a slave receiver with the lsb set low. In receive mode, the first data byte is written to the RADD virtual register, which forms the register sub-address. The RADD register takes an 8-bit value that determines which of 256 possible register addresses is written to by the following byte. Not all addresses are valid and many are reserved registers that must not be changed from their default values. Multiple byte reads or writes will auto-increment the value in RADD, but care should be taken not to access the reserved registers accidentally.Following a valid chip address, the 2-wire bus STOP command resets the RADD register to 00. If the chip address is not recognized, the MT352 will ignore all activity until a valid chip address is received. The 2-wire bus START command does NOT reset the RADD register to 00. This allows a combined 2-wire bus message, to point to a particular read register with a write command, followed immediately with a read data command. If required, this could next be followed with a write command to continue from the latest address. RADD would not be sent in this case. Finally, a STOP command should be sent to free the bus.When the 2-wire bus is addressed (after a recognized STOP command) with the read bit set, the first byte read out is the contents of register 00.3.2.1 TunerThe MT352 has a General Purpose Port that can be configured to provide a secondary 2-wire bus. Master control mode is selected by a single register control bit.The allocation of the pins is: GPP0 pin 35 = CLK2, GPP1 pin 36 = DATA2.。

黑金 AN3845 RS232 485 422 通信模块用户手册说明书

第一部分RS232/485/422通信模块说明黑金AN3845模块专门为工业现场应用设计的RS232/485/422通信模块。

它包含一路RS232接口,2路RS485和2路RS422通信接口。

配合开发板实现RS232、485和422的数据远程传输和通信。

RS232、485和422接口分别采用MAX3232、MAX3485和MAX3490芯片作为电平转换芯片。

模块留有一个40针的排母用于连接开发板,RS232接口为一个标准的DB9串口公座,通过串口线直接连接电脑或者其他设备;RS485和RS422接口采用接线端子跟外部连接,超远距离传输可达上千米,另外RS485和RS422接口部分带有正负15KV的ESD 防护功能。

AN3845模块实物照片如下:AN3845通信模块正面图1.1 AN3485模块的参数说明以下为AN3485通信模块的详细参数:RS232接口●一路标准的DB9公座串行接口;●使用MAX3232作为RS232和TTL电平的转换;●传输率高达120Kbps数据通讯速率RS485接口●两路RS485接口,采用3线的接线端子;●使用MAX3485作为RS485和TTL的电平转换;●工业级设计,抗干扰能力超强,同时采用有效的防雷设计;●具有120欧匹配电阻,插上跳线帽即可使能匹配电阻,长距离传输时建议短接。

●支持多机通讯,允许接在最多128个设备的总线上●传输率高达500Kbps数据通讯速率。

RS422接口●两路RS422接口,采用5线的接线端子;●使用MAX3490作为RS422和TTL的电平转换;●工业级设计,抗干扰能力超强,同时采用有效的防雷设计;●具有120欧匹配电阻,插上跳线帽即可使能匹配电阻,长距离传输时建议短接。

●支持多机通讯,允许接在最多128个设备的总线上●传输率高达500Kbps数据通讯速率。

1.2 AN3485模块尺寸AN3485通信模块尺寸图第二部分模块功能说明2.1 RS232电路设计AN3485模块的RS232接口采用MAX3232芯片实现RS232和+3.3V TTL 电平的转换。

Z35摇臂钻床

目录说明┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈3第一章绪论┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈4【一】目的和意义┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈4 【二】本设计的主要内容┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈4第二章 Z 35摇臂钻床简介和电路设计┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈5【一】Z35摇臂钻床简介┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈5 【二】电路设计┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈6 【三】设计过程的感受┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈8第三章电动机的选择和电气元件的选择┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈8【一】电动机类型的选择┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈81、电动机选择的基本原则┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈82、电动机额定电压的选择┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈93、电动机转速的选择┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈94、电动机功率的选择┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈9 【二】电气元件的选择┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈101、熔断器的选择┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈10(1)、熔断器类型的选择┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈10(2)、熔断器额定电压的选择┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈11(3)、熔体额定电流的选择┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈11(4)、熔断器(熔管)额定电流的确定┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈11(5)、校核熔断器的保护特性┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈112、热继电器的选择┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈12(1)、热继电器机构形式的选择┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈12(2)、热继电器时间的选择┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈12(3)、热元件额定电流的选取┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈12(4)、热继电器保护┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈123、接触器的选择┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈12(1)、根据使用类别选用相应产品系列┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈12(2)、根据电动机等负载的功率和操作情况确定接触器的容量等级┈┈┈┈┈┈┈┈┈13(3)、根据控制回路电压决定接触器线圈电压┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈13(4)、额定电流的选择┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈13(5)、根据使用环境来选择接触器的系列或规格┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈144、控制变压器的选择┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈145、导线的选择┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈14(1)、截面积┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈14(2)、材质┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈14(3)、绝缘和外护层┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈146、接线端子的选择┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈167、按钮、开关的选择┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈17(1)、按钮┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈17(2)、组合开关┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈17(3)、行程开关┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈17(4)、断路器(自动开关)┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈18(5)、照明灯所选开关┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈188、变压器的选择┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈189、指示灯的选择┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈18【三】电气元件目录表┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈18 【四】个人体会┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈20第四章元器件的检测┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈21【一】控制元器件的检测┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈21【二】操作元器件的检测┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈22 【三】显示元器件的检测┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈22 【四】电动机的检测┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈23 【五】小结┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈23第五章工艺设计┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈23【一】电气原理图┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈23 【一】元件布置图┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈24 【三】单件端子编号图┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈24 【四】电气安装接线图┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈24 【五】总结┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈25第六章元件的安装与布线┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈25【一】元件的安装┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈251、元件上元件的安装前的准备工作┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈252、安装过程中应该注意的问题┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈253、元件的固定安装工艺┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈264、装配后的清理检查工作┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈26 【二】布线┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈261、布线前的准备工作┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈262、布线的基本要求┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈263、布线方法┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈274、布线┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈27 【三】毕业设计心得┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈27第七章电路检测┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈28【一】控制电路检测┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈28 【二】通电检测┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈29 【三】常见故障及检测方法┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈31 【四】个人体会总结┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈36参考文献┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈┈37说明此次毕业设计由要晓伟、马建刚、杨丽伟、吴云、陶海峰、周晓芳合作完成。

Z系列二极管参数

Z系列⼆极管参数Z系列⼆极管参数型号PDF资料⼚商特性⽤途极限⼯作电压Vrwm(V)极限⼯作电流Im(A)耗散功率Pw(w)最⾼⼯作频率fm(Hz)代换型号ZMM55-C3V6 BILIN 3.6V稳压⼆极管 3.6 0.5 ZMM55-C3V9 BILIN 3.9V稳压⼆极管 3.9 0.5 ZMM55-C43 BILIN 43V稳压⼆极管43 0.5 ZMM55-C47 BILIN 47V稳压⼆极管47 0.5 ZMM55-C4V3 BILIN 4.3V稳压⼆极管 4.3 0.5 ZMM55-C4V7 BILIN 4.7V稳压⼆极管 4.7 0.5 ZMM55-C5V1 BILIN 5.1V稳压⼆极管 5.1 0.5 ZMM55-C5V6 BILIN 5.6V稳压⼆极管 5.6 0.5 ZMM55-C6V2 BILIN 6.2V稳压⼆极管 6.2 0.5 ZMM55-C6V8 BILIN 6.8V稳压⼆极管 6.8 0.5 ZMM55-C7V5 BILIN 7.5V稳压⼆极管7.5 0.5 ZMM55-C8V2 BILIN 8.2V稳压⼆极管8.2 0.5 ZMM55-C9V1 BILIN 9.1V稳压⼆极管9.1 0.5 ZP10整流⼆极管3000 10ZP100整流⼆极管3000 100ZP100/100整流⼆极管100 100ZP100/1000整流⼆极管1000 100ZP100/1200整流⼆极管1200 100ZP100/1400整流⼆极管1400 100ZP100/1600整流⼆极管1600 100ZP100/200整流⼆极管200 100ZP100/300整流⼆极管300 100ZP100/400整流⼆极管400 100ZP100/500整流⼆极管500 100ZP100/600整流⼆极管600 100ZP100/700整流⼆极管700 100ZP100/800整流⼆极管800 100ZP100/900整流⼆极管900 100ZP1000整流⼆极管3000 1000ZP1000/100整流⼆极管100 1000型号PDF资料⼚商特性⽤途极限⼯作电压Vrwm(V)极限⼯作电流Im(A)耗散功率Pw(w)最⾼⼯作频率fm(Hz)代换型号ZP1000/1000整流⼆极管1000 1000 ZP1000/1200整流⼆极管1200 1000 ZP1000/1400整流⼆极管1400 1000 ZP1000/1600整流⼆极管1600 1000 ZP1000/1800整流⼆极管1800 1000 ZP1000/200整流⼆极管200 1000 ZP1000/2000整流⼆极管2000 1000 ZP1000/300整流⼆极管300 1000 ZP1000/400整流⼆极管400 1000 ZP1000/500整流⼆极管500 1000 ZP1000/600整流⼆极管600 1000 ZP1000/700整流⼆极管700 1000 ZP1000/800整流⼆极管800 1000ZP1000/900整流⼆极管900 1000 ZP10A整流⼆极管25 10 ZP10B整流⼆极管50 10 ZP10C整流⼆极管100 10 ZP10D整流⼆极管200 10 ZP10E整流⼆极管300 10 ZP10F整流⼆极管400 10 ZP10G整流⼆极管500 10 ZP10H整流⼆极管600 10 ZP10J整流⼆极管700 10 ZP10K整流⼆极管800 10 ZP10L整流⼆极管900 10 ZP10N整流⼆极管1200 10 ZP10P整流⼆极管1400 10 ZP10Q整流⼆极管1600 10 ZP10R整流⼆极管1800 10 ZP10S整流⼆极管2000 10型号PDF资料⼚商特性⽤途极限⼯作电压Vrwm(V)极限⼯作电流Im(A)耗散功率Pw(w)最⾼⼯作频率fm(Hz)代换型号ZP1500整流⼆极管3000 1500ZP20整流⼆极管3000 20ZP200整流⼆极管3000 200 R50210010RSWA,10SM200 ZP200/100整流⼆极管100 200ZP200/1000整流⼆极管1000 200ZP200/1200整流⼆极管1200 200ZP200/1400整流⼆极管1400 200ZP200/1600整流⼆极管1600 200ZP200/1800整流⼆极管1800 200ZP200/200整流⼆极管200 200ZP200/300整流⼆极管300 200ZP200/400整流⼆极管400 200ZP200/500整流⼆极管500 200ZP200/600整流⼆极管600 200ZP200/700整流⼆极管700 200ZP200/800整流⼆极管800 200ZP200/900整流⼆极管900 200ZP2000整流⼆极管3000 2000ZP20A整流⼆极管25 20ZP20B整流⼆极管50 20ZP20C整流⼆极管100 20ZP20D整流⼆极管200 20ZP20E整流⼆极管300 20ZP20F整流⼆极管400 20ZP20G整流⼆极管500 20ZP20H整流⼆极管600 20ZP20J整流⼆极管700 20ZP20K整流⼆极管800 20ZP20L整流⼆极管900 20ZP20M整流⼆极管1000 20型号PDF资料⼚商特性⽤途极限⼯作电压Vrwm(V)极限⼯作电流Im(A)耗散功率Pw(w)最⾼⼯作频率fm(Hz)代换型号ZP20P整流⼆极管1400 20 ZP20Q整流⼆极管1600 20 ZP20R整流⼆极管1800 20 ZP20S整流⼆极管2000 20 ZP30整流⼆极管3000 30 ZP300整流⼆极管3000 300 ZP300/100整流⼆极管100 300 ZP300/1000整流⼆极管1000 300 ZP300/1200整流⼆极管1200 300 ZP300/1400整流⼆极管1400 300 ZP300/1600整流⼆极管1600 300 ZP300/1800整流⼆极管1800 300 ZP300/200整流⼆极管200 300 ZP300/2000整流⼆极管2000 300 ZP300/300整流⼆极管300 300 ZP300/400整流⼆极管400 300 ZP300/500整流⼆极管500 300 ZP300/600整流⼆极管600 300 ZP300/700整流⼆极管700 300 ZP300/800整流⼆极管800 300 ZP300/900整流⼆极管900 300 ZP400整流⼆极管3000 400 ZP5整流⼆极管3000 5 ZP50整流⼆极管3000 50 ZP500整流⼆极管3000 500 ZP500/100整流⼆极管100 500 ZP500/1000整流⼆极管1000 500 ZP500/1200整流⼆极管1200 500 ZP500/1400整流⼆极管1400 500型号PDF资料⼚商特性⽤途极限⼯作电压Vrwm(V)极限⼯作电流Im(A)耗散功率Pw(w)最⾼⼯作频率fm(Hz)代换型号ZP500/1600整流⼆极管1600 500 ZP500/1800整流⼆极管1800 500 ZP500/200整流⼆极管200 500 ZP500/2000整流⼆极管2000 500 ZP500/300整流⼆极管300 500 ZP500/400整流⼆极管400 500 ZP500/500整流⼆极管500 500 ZP500/600整流⼆极管600 500 ZP500/700整流⼆极管700 500 ZP500/800整流⼆极管800 500 ZP500/900整流⼆极管900 500 ZP50A整流⼆极管25 50 ZP50B整流⼆极管50 50 ZP50C整流⼆极管100 50 ZP50D整流⼆极管200 50 ZP50E整流⼆极管300 50 ZP50F整流⼆极管400 50 ZP50G整流⼆极管500 50 ZP50H整流⼆极管600 50ZP50N整流⼆极管1200 50 ZP50P整流⼆极管1400 50 ZP50Q整流⼆极管1600 50 ZP50R整流⼆极管1800 50 ZP50S整流⼆极管2000 50 ZP55A整流⼆极管25 1 ZP55B整流⼆极管50 1型号PDF资料⼚商特性⽤途极限⼯作电压Vrwm(V)极限⼯作电流Im(A)耗散功率Pw(w)最⾼⼯作频率fm(Hz)代换型号ZP55C整流⼆极管100 1 ZP55D整流⼆极管200 1 ZP55E整流⼆极管300 1 ZP55F整流⼆极管400 1 ZP55G整流⼆极管500 1 ZP55H整流⼆极管600 1 ZP55J整流⼆极管700 1 ZP55K整流⼆极管800 1 ZP55L整流⼆极管900 1 ZP55M整流⼆极管1000 1 ZP55N整流⼆极管1200 1 ZP57A整流⼆极管25 25 ZP57B整流⼆极管50 25 ZP57C整流⼆极管100 25 ZP57D整流⼆极管200 25 ZP57E整流⼆极管300 25 ZP57F整流⼆极管400 25 ZP57G整流⼆极管500 25 ZP57H整流⼆极管600 25 ZP57K整流⼆极管800 25 ZP57L整流⼆极管900 25 ZP57M整流⼆极管1000 25 ZP59A整流⼆极管25 20 ZP59B整流⼆极管50 20 ZP59C整流⼆极管100 20 ZP59D整流⼆极管200 20 ZP59E整流⼆极管300 20 ZP59F整流⼆极管400 20 ZP59G整流⼆极管500 20 ZP59H整流⼆极管600 20型号PDF资料⼚商特性⽤途极限⼯作电压Vrwm(V)极限⼯作电流Im(A)耗散功率Pw(w)最⾼⼯作频率fm(Hz)代换型号ZP59J整流⼆极管700 20 ZP59K整流⼆极管800 20 ZP59L整流⼆极管900 20 ZP59M整流⼆极管1000 20 ZP59S整流⼆极管2000 20 ZP5A整流⼆极管25 5ZP5G整流⼆极管500 5 ZP5H整流⼆极管600 5 ZP5J整流⼆极管700 5 ZP5K整流⼆极管800 5 ZP5L整流⼆极管900 5 ZP5M整流⼆极管1000 5 ZP5N整流⼆极管1200 5 ZP5P整流⼆极管1400 5 ZP5Q整流⼆极管1600 5 ZP5R整流⼆极管1800 5 ZP5S整流⼆极管2000 5 ZP600整流⼆极管3000 600 ZP800整流⼆极管3000 800 ZP800/100整流⼆极管100 800 ZP800/1000整流⼆极管1000 800 ZP800/1200整流⼆极管1200 800 ZP800/1400整流⼆极管1400 800 ZP800/1600整流⼆极管1600 800 ZP800/1800整流⼆极管1800 800 ZP800/200整流⼆极管200 800型号PDF资料⼚商特性⽤途极限⼯作电压Vrwm(V)极限⼯作电流Im(A)耗散功率Pw(w)最⾼⼯作频率fm(Hz)代换型号ZP800/2000整流⼆极管2000 800 ZP800/300整流⼆极管300 800 ZP800/400整流⼆极管400 800 ZP800/500整流⼆极管500 800 ZP800/600整流⼆极管600 800 ZP800/700整流⼆极管700 800 ZP800/800整流⼆极管800 800 ZP800/900整流⼆极管900 800。

ATmega8中文资料

ATmega8中文资料ATmega8 是ATMEL公司在2002年第一季度推出的一款新型AVR高档单片机。

在AVR家族中,ATmega8是一种非常特殊的单片机,它的芯片内部集成了较大容量的存储器和丰富强大的硬件接口电路,具备AVR高档单片机MEGE 系列的全部性能和特点。

但由于采用了小引脚封装(为DIP 28和TQFP/MLF3 2),所以其价格仅与低档单片机相当,再加上AVR单片机的系统内可编程特性,使得无需购买昂贵的仿真器和编程器也可进行单片机嵌入式系统的设计和开发,同时也为单片机的初学者提供了非常方便和简捷的学习开发环境。

ATmega8的这些特点,使其成为一款具有极高性能价格比的单片机,深受广大单片机用户的喜爱,在产品应用市场上极具竞争力,被很多家用电器厂商和仪器仪表行业看中,从而使ATmega8迅速进入大批量的应用领域.ATmega系列单片机属于AVR中的高档产品,它承袭了AT90所具有的特点,并在AT90(如AT9058515、AT9058535)的基础上,增加了更多的接口功能,而且在省电性能。

稳定性、抗干扰性以及灵活性方面考虑得更加周全和完善。

ATmega8 是一款采用低功耗CMOS工艺生产的基于AVR RISC结构的8位单片机。

AVR单片机的核心是将32个工作寄存器和丰富的指令集联结在一起,所有的工作寄存器都与ALU(算术逻辑单元)直接相连,实现了在一个时钟周期内执行的一条指令同时访问(读写)两个独立寄存器的操作。

这种结构提高了代码效率,使得大部分指令的执行时间仅为一个时钟周期.因此, ATmega8可以达到接近1MIPS/MHz的性能,运行速度比普通CISC单片机高出10倍。

ATmega8的主要性能如下:*高性能、低功耗的8位AVR微控制器,先进的RISC精简指令集结构130条功能强大的指令,大多数为单时钟周期指令32个8位通用工作寄存器工作在16MHz时,具有16MIPS的性能片内集成硬件乘法器(执行速度为2个时钟周期)*片内集成了较大容量的非易失性程序和数据存储器以及工作存储器8K字节的Flash程序存储器,擦写次数:>10000次支持可在线编程(ISP)、可在应用自编程(IAP)带有独立加密位的可选BOOT区,可通过BOOT区内的引导程序区(用户自己写入)来实现IAP编程.512个字节的E2PROM,擦写次数:100000次1K字节内部SRAM可编程的程序加密位*丰富强大的外部接口(Peripheral)性能2个具有比较模式的带预分频器(Separate Prescale)的8位定时/计数器1个带预分频器(SeParat Prescale),具有比较和捕获模式的16位定时/计数器1个具有独立振荡器的异步实时时钟(RTC)3个PWM通道,可实现任意<16位、相位和频率可调的PWM脉宽调制输出8通道A/D转换( TQFP、MLF封装),6路10位A/D+2路8位A/D6通道A/D转换( PDIP封装),4路10位A/D+2路8位A/D1个I2C的串行接口,支持主/从、收/发四种工作方式,支持自动总线仲裁1个可编程的串行USART接口,支持同步、异步以及多机通信自动地址识别1个支持主/从(Master/Slave)、收/发的SPI同步串行接口带片内RC振荡器的可编程看门狗定时器片内模拟比较器*特殊的微控制器性能可控制的上电复位延时电路和可编程的欠电压检测电路内部集成了可选择频率(l/2/4/8MHZ)、可校准的RC振荡器外部和内部的中断源18个五种睡眠模式:空闲模式(Idle)、ADC噪声抑制模式(ADC Noise Reduction)。

ZMM8V2 ST LL34 ZMM稳压系列

Symbol RthA VF

Max. 0.3 1) 1

Unit K/mW V

Valid provided that electrodes are kept at ambient temperature

Characteristics at Ta = 25 OC

Zener Voltage 1) Type Min. (V) ZMM2V2HC ZMM2V2HCA ZMM2V2HCB ZMM2V4HC ZMM2V4HCA ZMM2V4HCB ZMM2V7HC ZMM2V7HCA ZMM2V7HCB ZMM3V0HC ZMM3V0HCA ZMM3V0HCB ZMM3V3HC ZMM3V3HCA ZMM3V3HCB 2.09 2.12 2.22 2.3 2.33 2.43 2.5 2.54 2.69 2.8 2.85 3.01 3.1 3.16 3.32 VZ Max. (V) 2.41 2.3 2.41 2.64 2.52 2.63 2.9 2.75 2.91 3.2 3.07 3.22 3.5 3.38 3.53 at lZT (mA) 20 20 20 20 20 20 20 20 20 20 20 20 20 20 20 Dynamic Resistance ZZT Max. (Ω) 120 120 120 120 120 120 100 100 100 80 80 80 70 70 70 at lZT (mA) 20 20 20 20 20 20 20 20 20 20 20 20 20 20 20 Reverse Leakage Current IR Max. (µA) 120 120 120 120 120 120 100 100 100 50 50 50 20 20 20 at VR (V) 0.7 0.7 0.7 1 1 1 1 1 1 1 1 1 1 1 1

双串口单片机(51单片机)

15. 串行口 ...............................................................................................................................55 15.1 模式 0....................................................................................................................56 15.2 模式 1....................................................................................................................56 15.3 模式 2....................................................................................................................58 15.4 模式3.....................................................................................................................59 15.5 贞错误检测............................................................................................................59 15.6 多机通信 ...............................................................................................................60

中移物联网有限公司CM32M4xxR芯片数据手册说明书

2 功能简介 ............................................................................................................................................................................. 16bit 基础定时计数器

― 1x 24bit SysTick

― 1x 7bit 窗口看门狗(WWDG)

― 1x 12bit 独立看门狗( IWDG)

编程方式

― 支持 2-wire/4-wire JTAG 在线调试接口

― 支持 UART Bootloader

安全特性

― 内置密码算法硬件加速引擎

CM32M4xxR芯片数据手册

中移物联网有限公司

CM32M4xxR系列芯片采用 32 bit RISC-V N308内核,最高工作主频144MHz,支持浮点运算和DSP指 令,集成多达512KB Flash、144KB SRAM、4x12bit 5Msps ADC、4xOPAMP、7xCOMP、2x1Msps 12bit DAC,支持多达24通道电容式触摸按键,集成多路U(S)ART、I2C、SPI、QSPI、CAN通信接口,内置密 码算法硬件加速引擎

M48Z35AV-10PC1中文资料

M48Z35M48Z35Y256Kbit(32Kbit x8)ZEROPOWER®SRAMFEATURES SUMMARYs INTEGRATED,ULTRA LOW POWER SRAM,POWER-FAIL CONTROL CIRCUIT,andBATTERYs READ CYCLE TIME EQUALS WRITE CYCLE TIMEs AUTOMATIC POWER-FAIL CHIP DESELECT and WRITE PROTECTIONs WRITE PROTECT VOLTAGES:(V PFD=Power-fail Deselect Voltage)–M48Z35:V CC=4.75to5.5V4.5V≤V PFD≤4.75V–M48Z35Y:4.5to5.5V4.2V≤V PFD≤4.5Vs SELF-CONTAINED BATTERY IN THE CAPHAT™DIP PACKAGEs PACKAGING INCLUDES A28-LEAD SOIC and SNAPHAT®TOP(to be Ordered Separately)s PIN and FUNCTION COMPATIBLE WITH JEDEC STANDARD32K x8SRAMss SOIC PACKAGE PROVIDES DIRECT CONNECTION FOR A SNAPHAT TOP WHICH CONTAINS THE BATTERY and CRYSTAL1/20May2002M48Z35,M48Z35YTABLE OF CONTENTS DESCRIPTION (3)Logic Diagram(Figure3.) (3)Signal Names(Table1.) (3)DIP Connections(Figure4.) (4)SOIC Connections(Figure5.) (4)Block Diagram(Figure6.) (4)MAXIMUM RATING (5)Absolute Maximum Ratings(Table2.) (5)DC AND AC PARAMETERS (6)Operating and AC Measurement Conditions(Table3.) (6)AC Measurement Load Circuit(Figure7.) (6)Capacitance(Table4.) (6)DC Characteristics(Table5.) (7)OPERATING MODES (7)Operating Modes(Table6.) (7)READ Mode (8)READ Mode AC Waveforms(Figure8.) (8)READ Mode AC Characteristics(Table7.) (9)WRITE Mode (10)WRITE Enable Controlled,WRITE AC Waveforms(Figure9.) (10)Chip Enable Controlled,WRITE AC Waveforms(Figure10.) (10)WRITE Mode AC Characteristics(Table8.) (11)Data Retention Mode (12)Power Down/Up Mode AC Waveforms(Figure11.) (12)Power Down/Up AC Characteristics(Table9.) (12)Power Down/Up Trip Points DC Characteristics(Table10.) (13)V CC Noise And Negative Going Transients (13)Supply Voltage Protection(Figure12.) (13)PART NUMBERING (14)SNAPHAT Battery Table(Table12.) (14)PACKAGE MECHANICAL INFORMATION (15)REVISION HISTORY (19)2/20M48Z35,M48Z35Y DESCRIPTIONThe M48Z35/Y ZEROPOWER®RAM is a32Kbit x8,non-volatile static RAM that integrates power-fail deselect circuitry and battery control logic on a single die.The monolithic chip is available in two special packages to provide a highly integrated battery backed-up memory solution.The M48Z35/Y is a non-volatile pin and function equivalent to any JEDEC standard32K x8SRAM. It also easily fits into many ROM,EPROM,and EEPROM sockets,providing the non-volatility of PROMs without any requirement for special WRITE timing or limitations on the number of WRITEs that can be performed.The28pin600mil DIP CAPHAT™houses the M48Z35/Y silicon with a long life lithium button cell in a single package.The28pin330mil SOIC provides sockets with gold plated contacts at both ends for direct con-nection to a separate SNAPHAT housing contain-ing the battery.The unique design allows the SNAPHAT battery package to be mounted on top of the SOIC package after the completion of the surface mount process.Insertion of the SNAPHAT housing after reflow prevents potential battery damage due to the high temperatures required for device surface-mounting.The SNAPHAT housing is keyed to prevent reverse insertion.The SOIC and battery packages are shipped sep-arately in plastic anti-static tubes or in Tape&Reel form.For the28lead SOIC,the battery package(i.e. SNAPHAT)part number is“M4Z28-BR00SH1.”Table1.Signal NamesA0-A14Address InputsDQ0-DQ7Data Inputs/OutputsE Chip Enable InputG Output Enable InputW WRITE Enable InputV CC Supply VoltageV SS Ground3/20M48Z35,M48Z35Y4/205/20M48Z35,M48Z35YMAXIMUM RATINGStressing the device above the rating listed in the “Absolute Maximum Ratings”table may cause permanent damage to the device.These are stress ratings only and operation of the device at these or any other conditions above those indicat-ed in the Operating sections of this specification is not implied.Exposure to Absolute Maximum Rat-ing conditions for extended periods may affect de-vice reliability.Refer also to the STMicroelectronics SURE Program and other rel-evant quality documents.Table 2.Absolute Maximum RatingsNote: 1.For DIP package:Soldering temperature not to exceed 260°C for 10seconds (total thermal budget not to exceed 150°C for longerthan 30seconds).2.For SO package:Reflow at peak temperature of 215°C to 225°C for <60seconds (total thermal budget not to exceed 180°C for between 90to 120seconds).CAUTION:Negative undershoots below –0.3V are not allowed on any pin while in the Battery Back-up mode.Do NOT wave solder SOIC to avoid damaging SNAPHAT sockets.Symbol ParameterValue Unit T AAmbient Operating TemperatureGrade 10to 70°C Grade 6–40to 85°C T STG Storage Temperature (V CC Off,Oscillator Off)SNAPHAT ®–40to 85°C SOIC–55to 125°C T SLD (1,2)Lead Solder Temperature for 10seconds 260°C V IO Input or Output Voltages –0.3to 7.0V V CC Supply Voltage –0.3to 7.0V I O Output Current 20mA P DPower Dissipation1WM48Z35,M48Z35Y6/20DC AND AC PARAMETERSThis section summarizes the operating and mea-surement conditions,as well as the DC and AC characteristics of the device.The parameters in the following DC and AC Characteristic tables are derived from tests performed under the Measure-ment Conditions listed in the relevant tables.De-signers should check that the operating conditions in their projects match the measurement condi-tions when using the quoted parameters.Table 3.Operating and AC Measurement ConditionsNote:Output Hi-Z is defined as the point where data is no longer driven.Table 4.CapacitanceNote: 1.Effective capacitance measured with power supply at 5V.Sampled only,not 100%tested.2.Outputs deselected.3.At 25°C.ParameterM48Z35M48Z35Y Unit Supply Voltage (V CC )4.75to5.5V4.5to5.5V Ambient Operating Temperature (T A )Grade 10to 700to 70°C Grade 6–40to 85–40to 85°C Load Capacitance (C L )100100pF Input Rise and Fall Times ≤5≤5ns Input Pulse Voltages0to 30to 3V Input and Output Timing Ref.Voltages1.51.5VSymbol Parameter (1,2)MinMax Unit C IN Input Capacitance 10pF C IO (3)Input /Output Capacitance10pF7/20M48Z35,M48Z35YTable 5.DC CharacteristicsNote: 1.Valid for Ambient Operating Temperature:T A =0to 70°C or –40to 85°C;V CC =4.75to 5.5V or 4.5to 5.5V (except where noted).2.Outputs deselected.3.Negative spikes of –1V allowed for up to 10ns once per cycle.OPERATING MODESThe M48Z35/Y also has its own Power-fail Detect circuit.The control circuitry constantly monitors the single 5V supply for an out of tolerance condi-tion.When V CC is out of tolerance,the circuit write protects the SRAM,providing a high degree of data security in the midst of unpredictable system operation brought on by low V CC .As V CC falls be-low approximately 3V,the control circuitry con-nects the battery which maintains data until valid power returns.Table 6.Operating ModesNote:X =V IH or V IL ;V SO =Battery Back-up Switchover Voltage.1.See Table 10,page 13for details.Symbol ParameterTest Condition (1)MinMax Unit I LI (2)Input Leakage Current 0V ≤V IN ≤V CC ±1µA I LO (2)Output Leakage Current 0V ≤V OUT ≤V CC ±5µA I CC Supply CurrentOutputs open 50mA I CC1Supply Current (Standby)TTL E =V IH 3mA I CC2Supply Current (Standby)CMOS E =V CC –0.2V3mA V IL (3)Input Low Voltage –0.30.8V V IH Input High Voltage 2.2V CC +0.3V V OL Output Low Voltage I OL =2.1mA 0.4V V OHOutput High VoltageI OH =–1mA2.4VMode V CCE G W DQ0-DQ7Power Deselect 4.75to 5.5Vor4.5to5.5VV IH X X High Z Standby WRITE V IL X V IL D IN Active READ V IL V IL V IH D OUT Active READ V IL V IH V IH High Z Active Deselect V SO to V PFD (min)(1)X X X High Z CMOS Standby Deselect≤V SO (1)XXXHigh ZBattery Back-up ModeM48Z35,M48Z35Y8/20READ ModeThe M48Z35/Y is in the READ Mode whenever W (WRITE Enable)is high,E (Chip Enable)is low.The device architecture allows ripple-through ac-cess of data from eight of 264,144locations in the static storage array.Thus,the unique address specified by the 15Address Inputs defines which one of the 32,768bytes of data is to be accessed.Valid data will be available at the Data I/O pins within Address Access time (t AVQV )after the last address input signal is stable,providing that the E and G access times are also satisfied.If the E and G access times are not met,valid data will be available after the latter of the Chip Enable Access time (t ELQV )or Output Enable Access time (t GLQV ).The state of the eight three-state Data I/O signals is controlled by E and G.If the outputs are activat-ed before t AVQV ,the data lines will be driven to an indeterminate state until t AVQV .If the Address In-puts are changed while E and G remain active,output data will remain valid for Output Data Hold time (t AXQX )but will go indeterminate until the next Address Access.9/20M48Z35,M48Z35YTable 7.READ Mode AC CharacteristicsNote: 1.Valid for Ambient Operating Temperature:T A =0to 70°C or –40to 85°C;V CC =4.75to 5.5V or 4.5to 5.5V (except where noted).2.C L =100pF.3.C L =5pF.SymbolParameter (1)M48Z35/YUnit–70MinMaxt AVAV READ Cycle Time70ns t AVQV (2)Address Valid to Output Valid 70ns t ELQV (2)Chip Enable Low to Output Valid 70ns t GLQV (2)Output Enable Low to Output Valid 35ns t ELQX (3)Chip Enable Low to Output Transition 5ns t GLQX (3)Output Enable Low to Output Transition 5ns t EHQZ (3)Chip Enable High to Output Hi-Z 25ns t GHQZ (3)Output Enable High to Output Hi-Z 25ns t AXQX (2)Address Transition to Output Transition10nsM48Z35,M48Z35Y10/20WRITE ModeThe M48Z35/Y is in the WRITE Mode whenever W and E are low.The start of a WRITE is referenced from the latter occurring falling edge of W or E.A WRITE is terminated by the earlier rising edge of or The addresses must be held valid through-out the cycle.E or W must return high for a mini-mum of t EHAX from Chip Enable or t WHAX from WRITE Enable prior to the initiation of anotherREAD or WRITE cycle.Data-in must be valid t D-VWH prior to the end of WRITE and remain valid for t WHDX afterward.G should be kept high during WRITE cycles to avoid bus contention;although,if the output bus has been activated by a low on and G,a low on W will disable the outputs t WLQZ after W falls.11/20Table 8.WRITE Mode AC CharacteristicsNote: 1.Valid for Ambient Operating Temperature:T A =0to 70°C or –40to 85°C;V CC =4.75to 5.5V or 4.5to 5.5V (except where noted).2.C L =5pF (see Figure 7,page 6).3.If goes low simultaneously with going low,the outputs remain in the high impedance state.SymbolParameter (1)M48Z35/YUnit–70MinMaxt AVAV WRITE Cycle Time70ns t AVWL Address Valid to WRITE Enable Low 0ns t AVEL Address Valid to Chip Enable Low 0ns t WLWH WRITE Enable Pulse Width50ns t ELEH Chip Enable Low to Chip Enable High 55ns t WHAX WRITE Enable High to Address Transition 0ns t EHAX Chip Enable High to Address Transition 0ns t DVWH Input Valid to WRITE Enable High 30ns t DVEH Input Valid to Chip Enable High 30ns t WHDX WRITE Enable High to Input Transition 5ns t EHDX Chip Enable High to Input Transition 5ns t WLQZ (2,3)WRITE Enable Low to Output Hi-Z 25ns t AVWH Address Valid to WRITE Enable High 60ns t AVEH Address Valid to Chip Enable High 60ns t WHQX (2,3)WRITE Enable High to Output Transition5ns12/20Data Retention ModeWith valid V CC applied,the M48Z35/Y operates as a conventional BYTEWIDE™static RAM.Should the supply voltage decay,the RAM will automati-cally power-fail deselect,write protecting itself when V CC falls within the V PFD (max),V PFD (min)window.All outputs become high impedance,and all inputs are treated as “don't care.”Note:A power failure during a WRITE cycle may corrupt data at the currently addressed location,but does not jeopardize the rest of the RAM's con-tent.At voltages below V PFD (min),the user can be assured the memory will be in a write protected state,provided the V CC fall time is not less than t F .The M48Z35/Y may respond to transient noise spikes on V CC that reach into the deselect window during the time the device is sampling V CC .There-fore,decoupling of the power supply lines is rec-ommended.When V CC drops below V SO ,the control circuit switches power to the internal battery which pre-serves data.The internal button cell will maintain data in the M48Z35/Y for an accumulated period of at least 10years (at 25°C)when V CC is less than V SO .As system power returns and V CC rises above V SO ,the battery is disconnected,and the power supply is switched to external V CC .Write protec-tion continues until V CC reaches V PFD (min)plus t REC (min).Normal RAM operation can resume t REC after V CC exceeds V PFD (max).For more information on Battery Storage Life refer to the Application Note AN1012.Table 9.Power Down/Up AC CharacteristicsNote: 1.Valid for Ambient Operating Temperature:T A =0to 70°C or –40to 85°C;V CC =4.75to 5.5V or 4.5to 5.5V (except where noted).2.V PFD (max)to V PFD (min)fall time of less than t F may result in deselection/write protection not occurring until 200µs after V CC pass-es V PFD (min).3.V PFD (min)to V SS fall time of less than t FB may cause corruption of RAM data.4.t REC (min)=20ms for industrial temperature Grade (6)device.Symbol Parameter (1)Min MaxUnit t PD E or W at V IH before Power Down 0µs t F (2)V PFD (max)to V PFD (min)V CC Fall Time 300µs t FB (3)V PFD (min)to V SS V CC Fall Time 10µs t R V PFD (min)to V PFD (max)V CC Rise Time 10µs t RB V SS to V PFD (min)V CC Rise Time 1µs t REC (4)V PFD (max)to Inputs Recognized40200ms13/20Table 10.Power Down/Up Trip Points DC CharacteristicsNote:All voltages referenced to V SS .1.Valid for Ambient Operating Temperature:T A =0to 70°C or –40to 85°C;V CC =4.75to 5.5V or 4.5to 5.5V (except where noted).2.At 25°C.V CC Noise And Negative Going Transients I CC transients,including those produced by output switching,can produce voltage fluctuations,re-sulting in spikes on the V CC bus.These transients can be reduced if capacitors are used to store en-ergy which stabilizes the V CC bus.The energy stored in the bypass capacitors will be released as low going spikes are generated or energy will be absorbed when overshoots occur.A ceramic by-pass capacitor value of 0.1µF (see Figure 12)is recommended in order to provide the needed fil-tering.In addition to transients that are caused by normal SRAM operation,power cycling can generate neg-ative voltage spikes on V CC that drive it to values below V SS by as much as one volt.These negative spikes can cause data corruption in the SRAM while in battery backup mode.To protect from these voltage spikes,ST recommends connecting a schottky diode from V CC to V SS (cathode con-nected to V CC ,anode to V SS ).(Schottky diode 1N5817is recommended for through hole and MBRS120T3is recommended for surface mount).Symbol Parameter (1)Min Typ Max Unit V PFD Power-fail Deselect Voltage M48Z35 4.5 4.6 4.75V M48Z35Y 4.24.35 4.5V V SO Battery Back-up Switchover Voltage M48Z35/Y3.0V t DR (2)Expected Data Retention Time10YEARSPART NUMBERINGTable11.Ordering Information SchemeExample:M48Z35Y–70MH1TRDevice TypeM48ZSupply Voltage and Write Protect Voltage35(1)=V CC=4.75to5.5V;V PFD=4.5to4.75V35Y=V CC=4.5to5.5V;V PFD=4.2to4.5VSpeed–70=70nsPackagePC=PCDIP28MH(2)=SOH28Temperature Range1=0to70°C6(3)=–40to85°CShipping Method for SOICblank=TubesTR=Tape&ReelNote: 1.The M48Z35part is offered with the PCDIP28(CAPHAT)package only.2.The SOIC package(SOH28)requires the battery package(SNAPHAT®)which is ordered separately under the part number“M4Zxx-BR00SH”in plastic tube or“M4Zxx-BR00SHTR”in Tape&Reel form.3.Industrial temperature grade available in SOIC package(SOH28)only.Caution:Do not place the SNAPHAT battery package“M4Zxx-BR00SH”in conductive foam as it will drain the lithium button-cell bat-tery.For a list of available options(e.g.,Speed,Package)or for further information on any aspect of this device, please contact the ST Sales Office nearest to you.Table12.SNAPHAT Battery TablePart Number Description PackageM4Z28-BR00SH Lithium Battery(48mAh)SNAPHAT SHM4Z32-BR00SH Lithium Battery(120mAh)SNAPHAT SH14/20PACKAGE MECHANICAL INFORMATIONNote:Drawing is not to scale.Table13.PMDIP28–28-pin Plastic DIP,battery CAPHAT™,Package Mechanical DataSymbmm inchesTyp Min Max Typ Min MaxA8.899.650.3500.380A10.380.760.0150.030A28.388.890.3300.350B0.380.530.0150.021B1 1.14 1.780.0450.070C0.200.310.0080.012D39.3739.88 1.550 1.570E17.8318.340.7020.722e1 2.29 2.790.0900.110e329.7236.32 1.170 1.430eA15.2416.000.6000.630L 3.05 3.810.1200.150N282815/20Table14.SOH28–28-lead Plastic Small Outline,battery SNAPHAT,Package Mechanical DataSymbolmm inchTyp Min Max Typ Min MaxA 3.050.120A10.050.360.0020.014 A2 2.34 2.690.0920.106 B0.360.510.0140.020 C0.150.320.0060.012 D17.7118.490.6970.728 E8.238.890.3240.350e 1.27––0.050––eB 3.20 3.610.1260.142 H11.5112.700.4530.500 L0.41 1.270.0160.050α0°8°0°8°N2828CP0.100.00416/20Table15.SH–4-pin SNAPHAT Housing for48mAh Battery,Package Mechanical DataSymbmm inchesTyp Min Max Typ Min MaxA9.780.385A1 6.737.240.2650.285A2 6.48 6.990.2550.275A30.380.015B0.460.560.0180.022D21.2121.840.8350.860E14.2214.990.5600.590eA15.5515.950.6120.628eB 3.20 3.610.1260.142L 2.03 2.290.0800.09017/20Table16.SH–4-pin SNAPHAT Housing for120mAh Battery,Package Mechanical DataSymbmm inchesTyp Min Max Typ Min MaxA10.540.415 A18.008.510.3150.335 A27.248.000.2850.315 A30.380.015 B0.460.560.0180.022 D21.2121.840.8350.860 E17.2718.030.6800.710 eA15.5515.950.6120.628 eB 3.20 3.610.1260.142 L 2.03 2.290.0800.09018/20REVISION HISTORYTable17.Revision HistoryDate Revision DetailsAugust1999First Issue04/21/00SH and SH28packages for2-pin and2-socket removed05/10/01Reformatted;added temperature information(Table4,5,7,8,9,10)05/29/02Modified reflow time and temperature footnotes(Table2)19/20Information furnished is believed to be accurate and reliable.However,STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use.No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics.Specifications mentioned in this publication are subject to change without notice.This publication supersedes and replaces all information previously supplied.STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is registered trademark of STMicroelectronicsAll other names are the property of their respective owners.©2002STMicroelectronics-All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia-Brazil-Canada-China-Finland-France-Germany-Hong Kong-India-Israel-Italy-Japan-Malaysia-Malta-Morocco-Singapore-Spain-Sweden-Switzerland-United Kingdom-U.S.A.20/20。

英士达机电——闭环步进 步进电机产品手册

80

750

2.4

24.48

7.2

72.43

3000

2.4

0.8

44

2.88

6.4

2.22

全封闭, 通风 IP65(不 括轴 分和连 处) 工作温 :0~400C,存储温 :-20~800C

于90%( 凝露)

阳光 ,

蚀气体、易燃气体、油污或 尘

2.86

14

08 -0.36

1.在 /拆卸 合 件 电机轴 时,不要用力

1.3

13

1.在 /拆卸 合 件 电机轴 时,不要用力

打轴 , 止电机轴另一 的编码

坏。

2. 力使轴 对其 佳状态, 止 动和轴承

损坏。

80.5±0.5

Φ 90

63.64±0.5

Φ5.5

40±0.5

3

12

25±0.5

162±0.5

41.1±0.5

12.5

0 -0.1

伺服电机型 伺服驱动 型

兰规格 额功 额

英士达机电

Instar Electromechanical

深圳市英士达机电技术开发有限公司

CN2

CN1

CN3

英士达机电

Instar Electromechanical

POWER

我们拥有九大系列共计数百款产品供市场选择; 自主研发、自主开模、自主生产于一体;

我们为客户提供高品质、高性能、低售后的产品。

110±0.5

56±0.5

15

16

/19-20

/21-22

/23-24

810

/25-26

/27-28

420

/29-30

720

AT32F415系列微控制器数据手册说明书

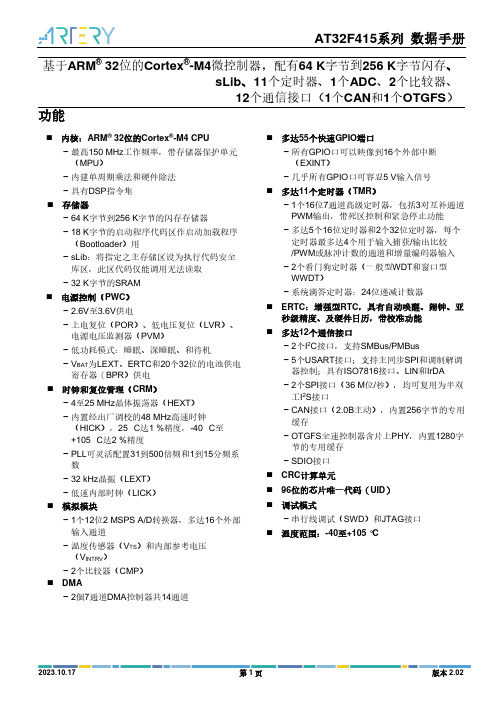

基于ARM® 32位的Cortex®-M4微控制器,配有64 K字节到256 K字节闪存、sLib、11个定时器、1个ADC、2个比较器、12个通信接口(1个CAN和1个OTGFS)功能⏹内核:ARM® 32位的Cortex®-M4 CPU−最高150 MHz工作频率,带存储器保护单元(MPU)−内建单周期乘法和硬件除法−具有DSP指令集⏹存储器− 64 K字节到256 K字节的闪存存储器− 18 K字节的启动程序代码区作启动加载程序(Bootloader)用− sLib:将指定之主存储区设为执行代码安全库区,此区代码仅能调用无法读取− 32 K字节的SRAM⏹电源控制(PWC)− 2.6V至3.6V供电−上电复位(POR)、低电压复位(LVR)、电源电压监测器(PVM)−低功耗模式:睡眠、深睡眠、和待机− V BAT为LEXT、ERTC和20个32位的电池供电寄存器(BPR)供电⏹时钟和复位管理(CRM)− 4至25 MHz晶体振荡器(HEXT)−内置经出厂调校的48 MHz高速时钟(HICK),25 °C达1 %精度,-40 °C至+105 °C达2 %精度− PLL可灵活配置31到500倍频和1到15分频系数− 32 kHz晶振(LEXT)−低速内部时钟(LICK)⏹模拟模块− 1个12位2 MSPS A/D转换器,多达16个外部输入通道−温度传感器(V TS)和内部参考电压(V INTRV)− 2个比较器(CMP)⏹DMA− 2個7通道DMA控制器共14通道⏹多达55个快速GPIO端口−所有GPIO口可以映像到16个外部中断(EXINT)−几乎所有GPIO口可容忍5 V输入信号⏹多达11个定时器(TMR)− 1个16位7通道高级定时器,包括3对互补通道PWM输出,带死区控制和紧急停止功能−多达5个16位定时器和2个32位定时器,每个定时器最多达4个用于输入捕获/输出比较/PWM或脉冲计数的通道和增量编码器输入− 2个看门狗定时器(一般型WDT和窗口型WWDT)−系统滴答定时器:24位递减计数器⏹ERTC:增强型RTC,具有自动唤醒、闹钟、亚秒级精度、及硬件日历,带校准功能⏹多达12个通信接口− 2个I2C接口,支持SMBus/PMBus− 5个USART接口;支持主同步SPI和调制解调器控制;具有ISO7816接口、LIN和IrDA− 2个SPI接口(36 M位/秒),均可复用为半双工I2S接口− CAN接口(2.0B主动),内置256字节的专用缓存− OTGFS全速控制器含片上PHY,内置1280字节的专用缓存− SDIO接口⏹CRC计算单元⏹96位的芯片唯一代码(UID)⏹调试模式−串行线调试(SWD)和JTAG接口⏹温度范围:-40至+105 °C封装Array− LQFP64 10 x 10 mm− LQFP64 7 x 7 mm− LQFP48 7 x 7 mm− QFN48 6 x 6 mm− QFN32 4 x 4 mm目录1规格说明 (11)2功能简介 (13)2.1ARM®Cortex®-M4 (13)2.2存储器 (14)2.2.1闪存存储器(Flash) (14)2.2.2存储器保护单元(MPU) (14)2.2.3内置随机存取存储器(SRAM) (14)2.3中断 (14)2.3.1嵌套的向量式中断控制器(NVIC) (14)2.3.2外部中断(EXINT) (14)2.4电源控制(PWC) (14)2.4.1供电方案 (14)2.4.2复位和电源电压监测器(POR / LVR / PVM) (15)2.4.3电压调节器(LDO) (15)2.4.4低功耗模式 (15)2.5启动模式 (15)2.6时钟 (16)2.7通用输入输出口(GPIO) (16)2.8重映射功能 (16)2.9直接存储器访问控制器(DMA) (16)2.10定时器(TMR) (17)2.10.1高级定时器(TMR1) (17)2.10.2通用定时器(TMR2~5和TMR9~11) (17)2.10.3系统滴答定时器(SysTick) (18)2.11看门狗(WDT) (18)2.12窗口型看门狗(WWDT) (18)2.13增强型实时时钟(ERTC)和电池供电寄存器(BPR) (18)2.14通信接口 (19)2.14.1串行外设接口(SPI) (19)2.14.2内部集成音频接口(I2S) (19)2.14.3通用同步/异步收发器(USART) (19)2.14.4内部集成电路总线(I2C) (19)2.14.5安全数字输入/输出接口(SDIO) (19)2.14.6控制器区域网络(CAN) (20)2.14.7通用串行总线On-The-Go全速(OTGFS) (20)2.15循环冗余校验(CRC)计算单元 (20)2.16模拟/数字转换器(ADC) (20)2.16.1温度传感器(V TS) (20)2.16.2内部参考电压(V INTRV) (21)2.17比较器(CMP) (21)2.18调试:串行线(SWD)/ JTAG调试接口 (21)3引脚定义 (22)4存储器映像 (28)5电气特性 (29)5.1测试条件 (29)5.1.1最小和最大数值 (29)5.1.2典型数值 (29)5.1.3典型曲线 (29)5.1.4供电方案 (29)5.2绝对最大值 (30)5.2.1额定值 (30)5.2.2电气敏感性 (31)5.3规格 (32)5.3.1通用工作条件 (32)5.3.2上电和掉电时的工作条件 (32)5.3.3内嵌复位和电源控制模块特性 (32)5.3.4存储器特性 (34)5.3.5供电电流特性 (34)5.3.6外部时钟源特性 (42)5.3.7内部时钟源特性 (46)5.3.8PLL特性 (47)5.3.9低功耗模式唤醒时间 (47)5.3.10EMC特性 (47)5.3.11GPIO端口特性 (48)5.3.12NRST引脚特性 (50)5.3.13TMR定时器特性 (50)5.3.14SPI接口特性 (51)5.3.15I2S接口特性 (53)5.3.16I2C接口特性 (54)5.3.17SDIO接口特性 (55)5.3.18OTGFS接口特性 (56)5.3.1912位ADC特性 (57)5.3.20内部参照电压(V INTRV)特性 (59)5.3.21温度传感器(V TS)特性 (60)5.3.22比较器(CMP)特性 (61)6封装特性 (62)6.1LQFP64 – 10 x 10 mm封装数据 (62)6.2LQFP64 – 7 x 7 mm封装数据 (64)6.3LQFP48 – 7 x 7 mm封装数据 (66)6.4QFN48 – 6 x 6 mm封装数据 (68)6.5QFN32 – 4 x 4 mm封装数据 (70)6.6封装丝印 (71)6.7热特性 (72)7型号说明 (73)8版本历史 (74)表目录表1. 选型列表 (2)表2. AT32F415系列器件功能和配置 (12)表3. 启动加载程序(Bootloader)的管脚配置 (16)表4. 定时器功能比较 (17)表5. AT32F415系列引脚定义 (25)表6. 电压特性 (30)表7. 电流特性 (30)表8. 温度特性 (30)表9. ESD值 (31)表10. Latch-up值 (31)表11. 通用工作条件 (32)表12. 上电和掉电时的工作条件 (32)表13. 内嵌复位和电源管理模块特性 (32)表14. 可编程电压检测器特性 (33)表15. 内部闪存存储器特性 (34)表16. 内部闪存存储器寿命和数据保存期限 (34)表17. 运行模式下的典型电流消耗 (35)表18. 睡眠模式下的典型电流消耗 (36)表19. 运行模式下的最大电流消耗 (37)表20. 睡眠模式下的最大电流消耗 (37)表21. 深睡眠和待机模式下的典型和最大电流消耗 (38)表22. V BAT的典型和最大电流消耗(LEXT和ERTC开启) (40)表23. 内置外设的电流消耗 (41)表24. HEXT 4 ~ 25 MHz晶振特性 (42)表25. 高速外部用户时钟特性 (43)表26. LEXT 32.768 kHz晶振特性 (44)表27. 低速外部用户时钟特性 (45)表28. HICK振荡器特性 (46)表29. LICK振荡器特性 (46)表30. PLL特性 (47)表31. 低功耗模式的唤醒时间 (47)表32. EMS特性 (47)表33. GPIO静态特性 (48)表34. 输出电压特性 (49)表35. 输入交流特性 (49)表36. NRST引脚特性 (50)表37. TMR定时器特性 (50)表38. SPI特性 (51)表39. I2S特性 (53)表40. SD/MMC接口特性 (55)表41. OTGFS启动时间 (56)表42. OTGFS直流特性 (56)表43. OTGFS电气特性 (56)表44. ADC特性 (57)表45. f ADC = 14MHz时的最大R AIN (58)表46. f ADC = 28MHz时的最大R AIN (58)表47. ADC精度 (58)表48. 内置参照电压特性 (59)表49. 温度传感器特性 (60)表50. 比较器特性 (61)表51. LQFP64 – 10 x 10 mm 64引脚薄型正方扁平封装机械数据 (63)表52. LQFP64 – 7 x 7 mm 64引脚薄型正方扁平封装机械数据 (65)表53. LQFP48 – 7 x 7 mm 48引脚薄型正方扁平封装机械数据 (67)表54. QFN48 – 6 x 6 mm 48引脚正方扁平无引线封装机械数据 (69)表55. QFN32 – 4 x 4 mm 32引脚正方扁平无引线封装机械数据 (71)表56. 封装的热特性 (72)表57. AT32F415系列型号说明 (73)表58. 文档版本历史 (74)图目录图1. AT32F415系列功能框图 (13)图2. AT32F415系列LQFP64引脚分布 (22)图3. AT32F415系列LQFP48引脚分布 (23)图4. AT32F415系列QFN48引脚分布 (23)图5. AT32F415系列QFN32引脚分布 (24)图6. 存储器图 (28)图7. 供电方案 (29)图8. 上电复位和掉电复位波形图 (33)图9. LDO在运行模式时,深睡眠模式下的典型电流消耗在不同的V DD时与温度的对比 (38)图10. LDO在低功耗模式时,深睡眠模式下的典型电流消耗在不同的V DD时与温度的对比 (39)图11. 待机模式下的典型电流消耗在不同的V DD时与温度的对比 (39)图12.V BAT的典型电流消耗(LEXT和RTC开启)在不同的V BAT电压时与温度的对比 (40)图13. 使用8 MHz晶体的典型应用 (42)图14. 外部高速时钟源的交流时序图 (43)图15. 使用32.768 kHz晶体的典型应用 (44)图16. 外部低速时钟源的交流时序图 (45)图17. HICK时钟精度与温度的对比 (46)图18. 建议的NRST引脚保护 (50)图19. SPI时序图– 从模式和CPHA = 0 (52)图20. SPI时序图– 从模式和CPHA = 1 (52)图21. SPI时序图–主模式 (52)图22. I2S从模式时序图(Philips协议) (53)图23. I2S主模式时序图(Philips协议) (54)图24. SDIO高速模式 (55)图25. SD默认模式 (55)图26. OTGFS时序:数据信号上升和下降时间定义 (56)图27. ADC精度特性 (59)图28. 使用ADC典型的连接图 (59)图29. V TS对温度理想曲线图 (60)图30. 比较器迟滞图 (61)图31. LQFP64 – 10 x 10 mm 64引脚薄型正方扁平封装图 (62)图32. LQFP64 – 7 x 7 mm 64引脚薄型正方扁平封装图 (64)图33. LQFP48 – 7 x 7 mm 48引脚薄型正方扁平封装图 (66)图34. QFN48 – 6 x 6 mm 48引脚正方扁平无引线封装图 (68)图35. QFN32 – 4 x 4 mm 32引脚正方扁平无引线封装图 (70)图36. 丝印示意图 (71)1 规格说明AT32F415系列微控制器基于高性能的ARM®Cortex®-M4 32位的RISC内核,最高工作频率达到150MHz,Cortex®-M4内核具有一组DSP指令和提高应用安全性的一个存储器保护单元(MPU)。

威力铭408MT技术描述和配置

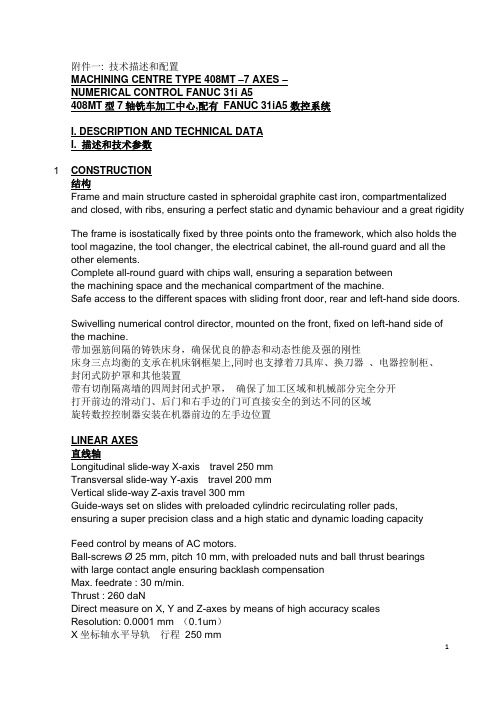

附件一: 技术描述和配置MACHINING CENTRE TYPE 408MT –7 AXES –NUMERICAL CONTROL FANUC 31i A5408MT型7轴铣车加工中心,配有FANUC 31iA5数控系统I. DESCRIPTION AND TECHNICAL DATAI. 描述和技术参数1 CONSTRUCTION结构Frame and main structure casted in spheroidal graphite cast iron, compartmentalized and closed, with ribs, ensuring a perfect static and dynamic behaviour and a great rigidity The frame is isostatically fixed by three points onto the framework, which also holds the tool magazine, the tool changer, the electrical cabinet, the all-round guard and all the other elements.Complete all-round guard with chips wall, ensuring a separation betweenthe machining space and the mechanical compartment of the machine.Safe access to the different spaces with sliding front door, rear and left-hand side doors.Swivelling numerical control director, mounted on the front, fixed on left-hand side of the machine.带加强筋间隔的铸铁床身,确保优良的静态和动态性能及强的刚性床身三点均衡的支承在机床钢框架上,同时也支撑着刀具库、换刀器、电器控制柜、封闭式防护罩和其他装置带有切削隔离墙的四周封闭式护罩,确保了加工区域和机械部分完全分开打开前边的滑动门、后门和右手边的门可直接安全的到达不同的区域旋转数控控制器安装在机器前边的左手边位置LINEAR AXES直线轴Longitudinal slide-way X-axis travel 250 mmTransversal slide-way Y-axis travel 200 mmVertical slide-way Z-axis travel 300 mmGuide-ways set on slides with preloaded cylindric recirculating roller pads,ensuring a super precision class and a high static and dynamic loading capacityFeed control by means of AC motors.Ball-screws Ø 25 mm, pitch 10 mm, with preloaded nuts and ball thrust bearingswith large contact angle ensuring backlash compensationMax. feedrate : 30 m/min.Thrust : 260 daNDirect measure on X, Y and Z-axes by means of high accuracy scalesResolution: 0.0001 mm (0.1um)X坐标轴水平导轨行程250 mmY坐标轴纵向导轨行程200 mmZ坐标轴垂直导轨行程300 mm在导轨上装有超精密级预紧的循环滚柱滑枕,确保了高精密度的高静态和动态的承载能力。

数控车刀型号说明之欧阳术创编

外圆车刀型号说明内孔车刀型号说明可转位精密车刀简介可转位精密车刀是车削工具系统中主要部件,规格、品种较多的产品之一,精密级产品,车刀的主要尺寸公差控制在±0.08mm以内。

螺钉夹紧式外圆车刀螺钉夹紧式外圆车刀SDJCR/L、SDPCN、SDPCR/L、SSDPN、STACR/L、SCGCR/L、SCFCR/L、SCLCR/L、SRDCN、SRGCR/L、SVJBR/L、SVVBN、SVHBR/L0808H09STACR/L10 10 10 101010H09STACR/L12 12 12 121212H09STAPR/L16 16 16 16 131616H11STAPR/LTCMT11020420 20 20 25 18 1252020K11STAPR/L25 25 25 32 25 1502525M11型号b h h1f l2l1刀尖半径配用刀片螺钉扳手0.4 CCMT060204 M2.5x5 T8 SCGCR/L 1212H0612 12 12 16 12100SCGCR/L 1616H0916 16 16 20 16SCGCR/L 2020K0920 20 20 25 25 1250.8 CCMT09T308 M4x9 T15 SCGCR/L 2525M0925 25 25 32 25 150螺钉夹紧式外圆车刀刀尖半型号b h h1f l2l1配用刀片螺钉扳手径SCFCR/L0.4 CCMT0602 M2.5x5 T812 12 12 161212H0616 100SCFCR/L16 16 16 201616H09SCFCR/L0.8 CCMT09T308 M4x9 T1520 20 20 25 25 1252020K09SCFCR/L25 25 25 32 25 1502525M09刀尖半型号b h h1f l2l1配用刀片螺钉扳手径SCLCR/L0.4 CCMT060204 M2.5x5 T812 12 12 16 121212H06100SCLCR/L16 16 16 20 161616H090.8 CCMT09T308 M4x9 T15 SCLCR/L20 20 20 25 25 1252020K09螺钉夹紧式外圆车刀螺钉夹紧式内孔车刀螺钉夹紧式内孔车刀S-STFPR/L、S-STUPR/L、S-STLPR/L、S-SSKPR/L、S-SCLCR/L、S-SDUCR/LSCLCR/L0932 25 17 250 40 23 22.5 6°型号最小加工直径Dd f l1l2H Bα°a刀尖半径配用刀片螺钉扳手S12M-SDUCR/L0716 12 9 150 25 11 11.5 8°7.0 0.4 DCMT070204 M2.5x5 T8 S16Q-SDUCR/L0720 16 11 180 30 14 15 6°S20R-SDUCR/L1125 20 13 200 35 18 18.5 8° 10.5 0.8 DCMT11T308 M4x9 T15复合上压式车刀型号b h.h1l1f l2a刀尖半径配用刀片复合上压式车刀型号 b h.h1 l1 f l2 a 配用刀片MSSNR/L20 20 125 252020K1234 8 SNMG120408 MSSNR/L25 25 150 322525M12MSSNR/L25 32 170 32 38 10 SNMG150612 3225P15型号f h1l2b h l1A配用刀片MRGNR/L25 2020 20 1252020K1228MRGNR/L?12 RNMG120432 25 25 25 1502525M12MRGNR/L32 32 32 25 32 1703225P12刀尖半型号f h1l2b h l1a配用刀片径MDPNN 10 20 45 20 20 125 12 0.8 DNMG150608复合上压式车刀MSBNR/L、MSDNN、MSKNR/L、MSSNR/L、MRGNR/L、MDPNN、MTGNR/L、MCLNR/L、MTFNR/L、MWLNR/L、MDJNR/L、MDHNR/L复合上压式车刀杠杆式车刀PSBNR/L、PSDNN、PSSNR/L、PCFNR/L、PSKNR/L、PCBNR/L、PTGNR/L、PCLNR/L、PTFNR/L、PDPNN、PDJNR/L、PDHNR/L、PRGNR/LPSSNR/L3225P1232 32 170 161.71.2SNMG150608 PSSNR/L4040R1950 32.5 40 40 40 40 200 187.5 12 SNMG190612杠杆式车刀型号f f1h1l2b h l1a刀尖半径配用刀片PCFNR/L2020K122518202820 20 12512 0.8 CNMG120408PCFNR/L2525M1232252525 150PCFNR/L3225P1232 32 170型号f f1h1l2b h l1l0a刀尖半径配用刀片PSKNR/L1616H0920 15 16 17 16 16 100 102 80.8SNMG090308 PSKNR/L 25 17 20 22 20 20 125 128 11 SNMG120408PSKNR/L2525M1232 25 25 25 150 153PSKNR/L3232P1540 22 32 30 32 32 170 174 13.51.2SNMG150612 PSKNR/L4040R1950 27 40 40 40 40 200 205 16.5 SNMG190612型号f h1l2b h l1a刀尖半径配用刀片PCBNR/L2020K1217 2028 20 20 12511 0.8 CNMG120408PCBNR/L2525M1222 252525 150PCBNR/L3225P1632 31 32 170 14.5 1.2 CNMG160612杠杆式车刀型号f f1h1l2b h l1a刀尖半径配用刀片PTGNR/L 20 16 16 22 16 16 100 14.5 0.8 TNMG160408杠杆式车刀切断(槽)刀型号说明QZQ1616RL、QZQ2020RL、QZQ2525RL、QZQ3225RL切断(槽)刀螺纹车刀型号说明外螺纹车刀型号hh1bLf配用刀片螺 钉 扳 手SE R/L 1616H16 16 16 16 100 20 16ER/L M3.5x14 T15SE R/L 2020K16 20 20 20 125 25SE R/L 2525M16 25 25 25 15032SE R/L 3225P16 32 32 25 170 SE R/L 3232P16 32 32 32 170 40 SE R/L 2525M22 25 25 25 150 32 22ER/L M4x15T20SE R/L 3225P22 32 32 25 170 32 SE R/L 3232P2232323217040内螺纹车刀SER/L,SNR/L。

MEMORY存储芯片MT48LC32M16A2TG-75IT中文规格书