半导体 第十三讲 金属化与平坦化

金属化与平坦化

34

Salicide: 它的生成比较复杂,先是完成栅刻蚀及 源漏注入以后,以溅射的方式在POLY上淀积一层金 属层(一般为 Ti,Co或Ni),然后进行第一次快速 升温退火处理(RTA),使多晶硅表面和淀积的金属 发生反应,形成金属硅化物。

根据退火温度设定,使得其他绝缘层( Nitride 或 Oxide)上的淀积金属不能跟绝缘层反应产生不希望 的硅化物,因此是一种自对准的过程(does not require lithographic patterning processes)。

然后再用一种选择性强的湿法刻蚀(NH4OH/H2O2/H20或 H2SO4/H2O2的混合液)清除不需要的金属淀积层,留下 栅极及其他需要做硅化物的salicide。

35

自对准硅化物工艺 Salicide

Self-aligned silicide (“salicide”) process

多晶硅 有源硅区

触电阻很小;

肖特基接触:相当于理想的二极管;

10

11

形成欧姆接触的方式

低势垒欧姆接触 一般金属Al和/pP-S型0i.势4半e垒V导高度体 的接触势垒较低

高复合欧姆接触半导体表面的晶体缺陷和高复合中心杂质

在半导体表面耗尽区中起复合中心作用

高掺杂欧姆接触

Al/N-Si势垒高度

0.7eV

需高掺杂欧姆接触

侧墙氧化层 场氧化层

Silicon substrate

1. 有源硅区

钛硅反应区

2. 钛淀积

T成iSi2 形

3. 快速热退火处理

4. 去除钛

36

The term salicide refers to a technology used in the microelectronics industry used to form electrical contacts between the semiconductor device and the supporting interconnect structure. The salicide process involves the reaction of a thin metal film with silicon in the active regions of the device, ultimately forming a metal silicide contact through a series of annealing and/or etch processes.

半导体CMP工艺介绍

半导体CMP工艺介绍半导体CMP工艺的基本原理是将硅片或其他基底材料放置在旋转的抛光盘上,其中涂有一层精细研磨颗粒的抛光材料。

通过施加垂直于硅片表面的压力和旋转抛光盘,在化学溶液的作用下,研磨颗粒将不均匀的材料移除,从而使表面平整化。

此外,化学溶液中添加的缓冲剂和表面活性剂等物质还可以起到控制反应速率和表面质量的作用。

CMP工艺的应用主要包括以下几个方面:1.平坦化:在半导体制造的各个步骤中,不可避免地会产生不均匀的层厚度和表面高度差。

通过CMP工艺,可以将这些不均匀物质去除,实现表面的平整化。

平坦化可以提高电子器件的性能,减少漏电流和损耗,并且提高芯片的可靠性。

2.边缘控制:在制造微小结构的芯片中,边缘效应是一个很重要的因素。

通过CMP工艺,在边缘处可以实现材料的去除,从而改善边缘效应,并提高芯片的性能。

3.材料移除:在半导体器件的制造过程中,常常会有需要移除的材料层,例如氧化物、金属等。

通过选择合适的抛光材料和化学溶液,可以对这些材料进行高效、精确的去除。

4.纳米级平整化:随着科技的发展,芯片的制造尺寸不断减小,对表面平整度和光洁度的要求也越来越高。

CMP工艺可以实现纳米级别的平整化,使得芯片表面具有非常高的质量。

除了以上的应用之外,半导体CMP工艺还被广泛应用于高深度微细加工、背隙法制备硅为基的太阳能电池、数据存储器件等领域。

虽然CMP工艺在半导体制造过程中起到了重要作用,但是在实际应用中也存在一些挑战。

例如,选择合适的抛光材料和化学溶液,控制好抛光时间和压力等参数都需要精确的掌握。

此外,还需要解决杂质污染和热效应等问题,以确保芯片的质量和稳定性。

总之,半导体CMP工艺是一种重要的半导体后期加工技术,能够在半导体制造过程中实现表面的平整化和材料的去除。

它在半导体行业中的应用已经非常广泛,并且随着芯片制造尺寸的不断缩小和技术的不断进步,CMP工艺的发展和应用还具有很大的潜力。

半导体制造工艺第章金属化

半导体制造工艺第章:金属化在半导体制造过程中,金属化是一个至关重要的步骤。

在这个过程中,金属被用来建立电路中的连线,使芯片能够进行电气连接。

本文将介绍半导体制造工艺中的金属化过程,包括种类、步骤、材料和要点。

金属化种类半导体制造中的金属化可以分为两种类型:全金属化和部分金属化。

全金属化是指整个芯片表面都被金属覆盖。

这种方法会消耗大量金属,但能够提高芯片的电性能,例如在高频和高速应用中使用。

部分金属化是指仅在需要的位置上涂覆金属,这种方法会减少金属的使用量,但这也会导致电性能不如全金属化。

因此,部分金属化常常被用在较低的频率和速度应用中。

金属化步骤金属化的步骤大致可以分为以下几个:1.陶瓷氧化物底片准备:第一步是将金属蒸发到陶瓷氧化物底片上。

在这之前,必须将底片表面彻底清洁,以确保金属与底片能够连接。

2.准备光刻胶:将光刻胶涂在底片表面上,这种胶质稳定且可以保护底片表面。

3.照相排版:使用照相版,将图案转移到底片表面上。

这个过程可以用来确定哪些区域需要涂金属。

4.以金属充电:将金属塔蒸发到底片表面上,确保金属已经完全充电。

5.除去光刻胶:将光刻胶除去,只剩下金属图案。

6.沉积门电极:将金属导线或电路图案分别与门电极一起沉积在甲烷基硅酸锑膜上,然后就可以使用了。

金属化要点1.放热吸附一定要彻底:在金属化过程中,要确保金属与陶瓷氧化物底片的相互作用足够强大,这样才能达到良好的连接。

因此,放热吸附这个步骤必须要彻底,以确保任何潜在污染的消除,其目的是创造一个适合在其上沉积电极材料的表面。

2.光刻过程:光刻过程需要立即消除不需要的区域。

如果光刻胶不符合或者在时间不够的情况下被卸载,则会予以保护,以避免在接下来的沉积过程中产生污染。

3.导线线宽和间距:导线线宽和间距不仅影响芯片的电性能,而且还会影响制造成本。

因此,在金属化步骤中,必须仔细控制导线线宽和间距。

4.金属选择:不同的金属具有不同的电学和物理特性,它们的选择会直接影响芯片的电性能。

欧姆接触

25

铜在硅和二氧化硅中都有很高的扩散率,这种高 扩散率将破坏器件的性能。可淀积一层阻挡层金属, 作用是阻止层上下的材料互相混合(见下图)。其厚 度对 0.25µm 工艺来说为 100nm ;对 0.35µm 工艺来说为 400~600nm。

阻挡层金属 铜

铜需要由一层薄膜阻挡层完全封闭起来,这层封闭 薄膜的作用是加固附着并有效地阻止扩散。

熔点(C)

1412 1412 660 1083 3417 1670 2996 2620 1772

电阻率 (-cm)

109 500 – 525 2.65 1.678 8 60 13 – 16 5 10

21

铝铜合金

由于铝的低电阻率及其与硅片制造工艺的兼容性,因 此被选择为IC的主要互连材料。然而铝有众所周知的 电迁徒引起的可靠性问题。由于电迁徒,在金属表面 金属原子堆起来形成小丘(如图所示)如果大量的小 丘形成,毗邻的连线或两层之间的连线有可能短接在 一起。 当少量百分比的铜与铝形成合金,铝的电迁移现象会 被显著的改善。 Al-Si-Cu (0.5%)合金是最常使用的连线金属

由于在优化超大规模集成电路的性能方面,需要进一步 按比列缩小器件的尺寸,因此在源 / 漏和第一金属层之 间电接触的面积是很小的。这个小的接触面积将导致接 触电阻增加。一个可提供稳定接触结构、减小源 / 漏区 接触电阻的工艺被称为自对准硅化物技术。它能很好地 与露出的源、漏以及多晶硅栅的硅对准。许多芯片的性 能问题取决于自对准硅化物的形成(见下图)。

常用扩散阻挡层:TiN, TiW

较好的方法是采用阻挡层, Ti 或 TiSi2有好的接触和黏附 性,TiN 可作为阻挡层

16

2.铝的电迁移

平坦化

P 是所加压力

V是硅片和抛光垫的相对速度

K与设备和工艺有关的参数,包括氧化硅的硬度、抛光液 和抛光垫等参数

2021/4/15

• 磨料中的水与氧化硅反应生成氢氧键, 这种反应称为表面水合反应,氧化硅的表 面水合降低了氧化硅的硬度、机械强度和 化学耐久性,

• 在抛光过程中,在硅片表面会由于摩擦 而产生热量,这也降低了氧化硅的硬度, 这层含水的软表层氧化硅被磨料中的颗粒 机械地去掉。

能和速度上同时满足硅片图形加工的要求,是目

前唯一可以实现全局平坦化的技术。

2021/4/15

3.化学机械平坦化(CMP)

3.1 CMP机理 3.2 CMP设备 3.3 CMP后清洗 3.4 CMP应用

2021/4/15

化学机械平坦化 (Chemical Mechanical Planarization)

2021/4/15

反刻平坦化

process: After Oxide Deposited

2021/4/15

Photoresist Coating and Baking

2021/4/15

Photoresist Etchback

2021/4/15

2.2 玻璃回流

• 玻璃回流是在升高温度的情况下给掺杂氧化硅加 热,使它发生流动。例如,硼磷硅玻璃(BPSG) 在850°,氮气环境的高温炉中退火30分钟发生流 动,使BPSG在台阶覆盖出的流动角度大约在20 度左右, BPSG的这种流动性能用来获得台阶覆 盖处的平坦化或用来填充缝隙。

平坦化

(Planarization) —— 何立娟

2021/4/15

• 1.平坦化基础理论 • 2.传统平坦化技术 • 3.CMP技术

化学机械平坦化

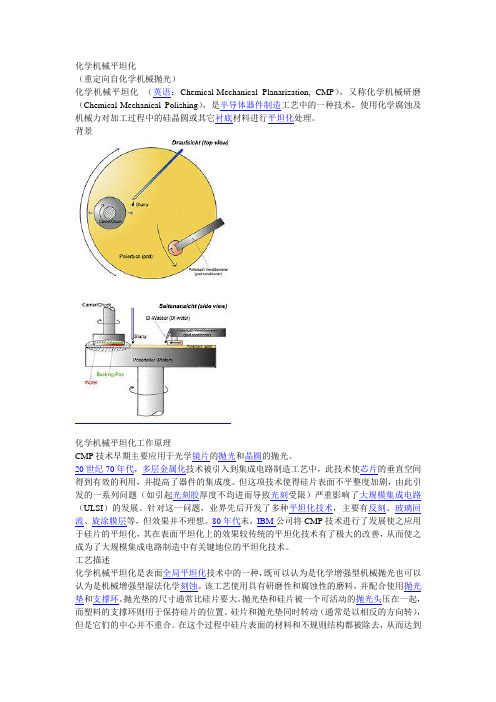

化学机械平坦化工作原理

CMP技术早期主要应用于光学镜片的抛光和晶圆的抛光。

20世纪70年代,多层金属化技术被引入到集成电路制造工艺中,此技术使芯片的垂直空间得到有效的利用,并提高了器件的集成度。但这项技术使得硅片表面不平整度加剧,由此引发的一系列问题(如引起光刻胶厚度不均进而导致光刻受限)严重影响了大规模集成电路(ULSI)的发展。针对这一问题,业界先后开发了多种平坦化技术,主要有反刻、玻璃回流、旋涂膜层等,但效果并不理想。80年代末,IBM公司将CMP技术进行了发展使之应用于硅片的平坦化,其在表面平坦化上的效果较传统的平坦化技术有了极大的改善,从而使之成为了大规模集成电路制造中有关键地位的平坦化技术。

应用

化学机械抛光主要用于以下几个方面

深槽填充的平面化

接触孔和过孔中的金属接头的平面化

生产中间步骤中氧化层和金属间电介层的平面化

金属抛光

金属抛光与氧化硅抛光机理有一定的区别,采用氧化的方法使金属氧化物在机械研磨中被去除。

物料选用

研磨液

磨料是平坦化工艺中研磨材料和化学添加剂的混合物,研磨材料主要是石英,二氧化铝和氧化铈,其中的化学添加剂则要根据实际情况加以选择,这些化学添加剂和要被除去的材料进行反应,弱化其和硅分子联结,这样使得机械抛光更加容易。在应用中的通常有氧化物磨料、金属钨磨料、金属铜磨料以及一些特殊应用磨料。台湾主要的厂商有长兴科技公司。

设备

CMP设备与晶圆生产中的抛光设备有相似之处(见上图),但集成电路硅片中很多材料的加入以及金属层的增加使得CMP设备不能如同抛光设备那样简单,而需要加入特别的过程获得平坦化的效果。这主要体现在对抛光厚度、抛光速率的检测上,被称作终点检测,通常有电机电流终点检测、光学终点检测。

平坦化工艺

CMP通过比去除低处图形块的速度去除高出图形来获 得均匀的硅片表面,由于它能精确并均匀地把硅片抛光 为需要的厚度和平坦度,已称为一种最广泛的技术。

BPSG在图形处平坦化

1.3旋涂膜层

旋涂膜层是在硅片上旋涂不同的液体材料以获得平坦化 的一种技术,主要是层间介质。这种技术在0.35um及 以上器件的制造中得到普遍应用。

旋涂利用离心力来填充图形低处,获得表面形貌的平滑 效果。这种旋涂法的平坦化能力与许多因素有关,如溶 液的化学组份、分子重量以及粘滞度。旋涂后烘烤蒸发 掉溶剂,留下氧化硅填充低处的间隙。为了进一步填充 表面的间隙,用CVD在淀积一层氧化硅。

三 CMP的机理

有两种机理可以解释是如何来进行硅片表面平坦化的: 1、表面材料与磨料发生化学反应生成一层相对容易去除的 表面层, 2、这一反应生成的硅片表面层通过磨料中研磨剂和研磨压 力与抛光垫的相对运动被机械地磨去。

CMP的微观作用是化学和机械作用的结合,不能使用一个 完全的机械过程,如用砂纸来磨一块板子,因为这样一个研 磨过程会损坏硅片的表面,带来沟槽和擦伤。

2.2CMP的开始

常见的传统平面化技术很多, 如热流法、旋 转式玻璃法、回蚀法电子环绕共振法、淀积一 腐蚀一淀积等, 这些技术在IC工艺中都曾得 到应用, 但是它们都是属于局部平面化技术, 不能做到全局平面化。l965年Walsh和 Herzog首次提出了化学机械抛光技术(CMP) 之后逐渐被应用起来。

半导体制造工艺第章平坦化

半导体制造工艺第章:平坦化半导体制造工艺中的平坦化是指将芯片表面变平坦的过程,这个过程在制造过程中的重要性日益增加。

随着芯片尺寸的不断缩小,芯片表面的平坦度要求越来越高。

本章将介绍芯片平坦化的方法和工艺。

什么是芯片表面平坦化?在制造芯片的过程中,芯片表面会因为工艺原因或者是晶片本身的结构因素,形成一些凸起和凹陷。

这些凸起和凹陷会对芯片的电学和机械特性产生影响。

因此,为了保证芯片的性能和可靠性,需要对芯片表面进行平坦化处理。

在芯片制造过程中,平坦化通常在化学机械抛光(CMP)的过程中进行。

通过化学机械抛光,可以将芯片表面的凸起磨平,提高芯片表面的平坦度,从而降低芯片表面的光散射和反射,提高芯片效率。

高速旋转平坦化技术除了化学机械抛光,还有一种叫做高速旋转平坦化技术(SPC)的平坦化方法。

它是利用高速旋转的压制杆在芯片表面来回压制,使表面呈现类似于球形的地形细节,由此消除芯片表面的凸起和凹陷。

与CMP相比,SPC具有以下优点:1.SPC具有更高的处理速度,能在几秒钟内快速平坦化芯片表面。

2.SPC使用的化学物质比CMP少,可以减少对环境的影响。

3.SPC可以处理具有较高粘性的微纹路材料,而CMP则不能做到。

然而,SPC技术也存在着一些局限性,对于一些特殊结构的芯片,例如3D芯片或者Memristor,SPC可能不太适用。

平坦度的评价指标芯片表面平坦度的评价指标主要有两个:Ra和RMS。

Ra是指表面粗糙度的平均值,是表征表面平整度的基本评价指标之一,单位为微米。

RMS是表面粗糙度的均方根值,不仅包含了表面的长波高度信息,也考虑了表面的短波波动,是更全面、更准确地反映表面粗糙度的指标,单位同样为微米。

芯片表面平坦化是芯片制造过程中非常重要的一个环节,不仅直接影响到芯片性能,同时也是现代半导体制造领域中的一个热门研究课题。

本章介绍了芯片表面平坦化的方法和工艺,还介绍了一个比CMP更快速和环保的平坦化技术,并介绍了两种常见的评价指标Ra和RMS。

半导体制造工艺教案金属化

授课主要内容或板书设计课堂教学安排教学过程主要教学内容及步骤6.1引言6.1.1金属化的概念在硅片上制造芯片可以分为两部分:第一,在硅片上利用各种工艺(如氧化、CVD、掺杂、光刻等)在硅片表面制造出各种有源器件和无源元件。

第二,利用金属互连线将这些元器件连接起来形成完整电路系统。

金属化工艺(Metallization)就是在制备好的元器件表面淀积金属薄膜,并进行微细加工,利用光刻和刻蚀工艺刻出金属互连线,然后把硅片上的各个元器件连接起来形成一个完整的电路系统,并提供与外电路连接接点的工艺过程。

6.1.2金属化的作用金属化在集成电路中主要有两种应用:一种是制备金属互连线,另一种是形成接触。

1.金属互连线2.接触1)扩散法是在半导体中先扩散形成重掺杂区以获得N+N或P+P的结构,然后使金属与重掺杂的半导体区接触,形成欧姆接触。

2)合金法是利用合金工艺对金属互连线进行热处理,使金属与半导体界面形成一层合金层或化合物层,并通过这一层与表面重掺杂的半导体形成良好的欧姆接触。

金属化技术在中、小规模集成电路制造中并不是十分关键。

但是随着芯片集成度越来越高,金属化技术也越来越重要,甚至一度成为制约集成电路发展的瓶颈。

早期的铝互连技术已不能满足高性能和超高集成度对金属材料的要求,直到铜互连技术被应用才解决了这个问题。

硅和各种金属材料的熔点和电阻率见表6 1。

为了提高IC性能,一种好的金属材料必须满足以下要求:1)具有高的导电率和纯度。

2)与下层衬底(通常是二氧化硅或氮化硅)具有良好的粘附性。

3)与半导体材料连接时接触电阻低。

4)能够淀积出均匀而且没有“空洞”的薄膜,易于填充通孔。

5)易于光刻和刻蚀,容易制备出精细图形。

6)很好的耐腐蚀性。

7)在处理和应用过程中具有长期的稳定性。

表6-1硅和各种金属材料的熔点和电阻率(20° C)6.2.2铝与硅和二氧化硅一样,铝一直是半导体制造技术中最主要的材料之一。

从集成电路制造早期开始就选择铝作为金属互连的材料,以薄膜的形式在硅片中连接不同器件。

半导体工艺(第10章) 平坦化

➢ CMP是目前能提供超大规模集成电路制造 过程中全面平坦化的一种新技术;

➢ 对介电层的抛光的目的是去除光刻胶,并 使整个晶片表面均匀平坦,被去除的厚度 约为0.5~1μm;

平坦化

原因:多层布线

➢ 随着金属层表面而产生高低不平的介电层 沉积,因为沉积层不平坦,将使得接下来 的第二层金属层的光刻工艺在曝光聚焦上 有困难;

➢ 集成电路的多层布线势在必行,于是平坦 化也就成了新出现的一种工艺技术;

➢旋涂玻璃法(SOG)

➢化学机械抛光(CMP)

SOG是目前普遍采用的一种局部平坦化技 术,其原理类似于光刻胶旋涂,即把一种 溶于溶剂的介电材料以旋涂的方式涂布在 晶片上;

后果:

➢ 导致金属在靠近正极一端堆积,形成小丘 或晶须,而靠近负极一端则产生空洞。金 属的堆积会引起布线金属间的短路、空洞 则会引起布线金属开路;

金属化要求:

➢台阶覆盖(蒸发源射向晶片表面的金属会 在台阶的阴面和阳面产生很大的沉积速率 差,要求晶片阳面或阴面所得到的薄膜厚 度要一致,利用多源蒸发和旋转晶片)

பைடு நூலகம்要求:

➢ 满足电学性能,形成欧姆接触;

平坦化

➢ 把晶片表面起伏的电介质层加以平坦的一 种工艺技术;

➢ 经过平坦化处理的介电层,无悬殊的高低 落差,在制作第二层金属内连线时,很容 易进行;

欧姆接触

➢ 金属与半导体间的电压与电流关系具有线 性关系,接触电阻小,不产生明显的附加 阻抗;

布线技术

对布线互连线的要求

➢ 热处理使金属与半导体界面形成一层合金 层或化合物层,并通过这一层与表面重掺 杂的半导体形成良好的欧姆接触;

金属化 半导体工艺87页PPT

43、重复别人所说的话,只需要教育; 而要挑战别人所说的话,则需要头脑。—— 玛丽·佩蒂博恩·普尔

44、卓越的人一大优点是:在不利与艰 难的遭遇里百折不饶。——贝多芬

45、自己的饭量自己知道。——苏联

金属化 半导体工艺

41、实际上,我们想要的不是针对犯 罪的法 律,而 是针对 疯狂的 法律。 ——马 克·吐温 42、法律的力量应当跟随着公民,就 像影子 跟随着 身体一 样。— —贝卡 利亚 43、法律和制度必须跟上人类思想进 步。— —杰弗 逊 44、人类受制于法律,法律受制于情 理。— —托·富 勒

45、法律的制定是为了保证每一个人 自由发 挥自己 的才能 ,而不 是为了பைடு நூலகம்束缚他 的才能 。—— 罗伯斯 庇尔

41、学问是异常珍贵的东西,从任何源泉吸 收都不可耻。——阿卜·日·法拉兹

金半接触ppt课件

呈现施主型

q0 以上的表面态被电子填充时,表面带负电,

呈现受主型

18

Ws

qns

q0

qVD EC EF

EV

存在受主表面态时 n 型半导体的能带图

19

若表面态密度很大,只要 EF 比 q0 高一点,

表面上就会积累很多负电荷,能带上弯

42

J sT

A*T 2

exp

qns

kT

热电子发射理论得到的伏-安特性与扩散理论 的一致。

Ge, Si, GaAs的迁移率高,自由程大,它们的 肖特基势垒中的电流输运机构,主要是多子 的热电子发射。

43

3. 镜象力和隧道效应的影响

锗检波器的反向特性

44

(1)镜象力的影响

在金属–真空系统中,一个在金属外面的电子, 要在金属表面感应出正电荷,同时电子要受到 正电荷的吸引。

Jms JSm V 0

A*T 2 exp( qns )

kT

40

有效理查逊常数

A*

4qmn*k 2

h3

热电子向真空发射的有效理查逊常数

A 120 A /(cm2 K 2 )

41

由上式得到总电流密度为:

J JSm Jms

A*T

2

exp(

qns

)exp(

qV

)

1

k T k T

JsT exp(qkVT ) 1

34

{ d 2V

dx 2

– qND

r0

0

(0 x xd )

(x xd )

E(x) dV (x) qND

dx r0

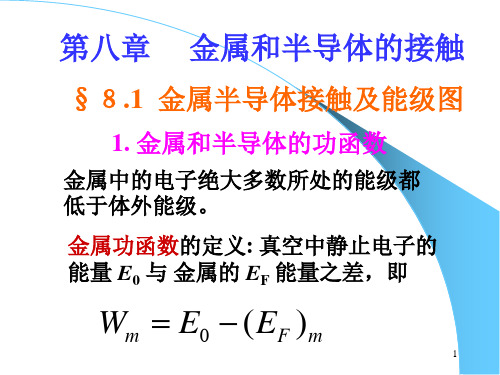

第八章金属化与平坦化

1

金属化ห้องสมุดไป่ตู้

集成电路的各个组件制作完成后,需要按照设计要 求将这些组件进行相应的连接以形成一个完整的电路 系统,并提供与外电路相连接的接点,完成此项任务 的就是金属布线。

金属化就是在组件制作完成的器件表面淀积金属薄 膜,金属线在IC中传导信号,介质层则保证信号不受 临近金属线的影响。

对于多层电极系统,由于铜具有更低的电阻率,已在 逐步取代铝成为主要的互连金属材料。

16

金属填充塞

多层金属布线使得金属化系统中出现很多通孔,为了 保证两层金属间形成电通路,这些通孔需要用金属塞来 填充。用于制作栓塞的材料有很多种,但实用性较高, 且已被集成电路制造广泛应用的是钨塞和铝塞。

17

18

化学机械平坦化

2

金属化工艺的作用

3

金属铝互连

4

金属铝互连

5

金属铝互连

6

金属铝互连系统中的失效与改进

7

8

9

10

金属铜互连

11

金属铜互连

12

金属铜互连

13

铜大马士革

14

15

铝互连&铜互连

最早用于集成电路制造的金属就是铝,室温下,铝的 电阻率比铜、金、银的电阻率稍高,但是由于铜和银比较 容易腐蚀,在硅和二氧化硅中的扩散率太高,这些都不利 于它们用于集成电路的制造;另外,金和银的成本比铝高, 而且与二氧化硅的粘附性不好,所以,也不常用。铝则能 很容易的淀积在wafer上,而且刻蚀时分辨率较高,所以, 铝作为首选金属用于金属化。

24

旋涂膜层平坦化

25

化学机械平坦化(CMP)

传统的平坦化方法都只是局部化的平坦,如果是整 个平面的介电层平坦则通常采用化学机械抛光法来完成。

半导体平坦化制造工艺技术概述

3 化学机械平坦化

② 研磨液供给与输送系统实现的目标:通过恰当设计和管理研磨液 供给与输送系统来保证CMP工艺的一致性。研磨液的混合、过滤、 滴定以及系统的清洗等程序会减轻很多与研磨液相关的问题。那么 就要设计一个合适的研磨液的供给与输送系统,完成研磨液的管理, 控制研磨液的混合、过滤、浓度、滴定及系统的清洗,减少研磨液 在供给、输送过程中可能出现的问题和缺陷,保证CMP的平坦化效 果。 ③ 研磨液混合和输送设备的设计特点: 搅动:一般来讲,研磨液中的固体颗粒经过一段时间后会逐渐淀积, 为了满足特定的工艺要求,必须保持桶中和储蓄罐中的液体均一, 专业的研磨液系统制造商可以为每种研磨液设置特定的淀积率和分

3 化学机械平坦化

图10-16 CMP设备组成

(1)抛光机运动组件(常叫抛光机)包括抛光头、研磨盘,是实现CM P的关键机械装置。 1)抛光头组件。

3 化学机械平坦化

图10-17 抛光头

3 化学机械平坦化

图10-18 CMP非均匀边沿区域

3 化学机械平坦化

图 10-19 更新的抛光头设计

2)研磨盘是CMP研磨的支撑平台,其作用是承载抛光垫并带动其 转动。

在研磨盘上,抛光时,旋转的抛光头以一定的压力压在旋转的抛光 垫上,由亚微米或纳米磨粒和化学溶液组成的研磨液在硅片表面和 抛光垫之间流动,然后研磨液在抛光垫的传输和离心力的作用下, 均匀分布其上,在硅片和抛光垫之间形成一层研磨液液体薄膜。研 磨液中的化学成分与硅片表面材料产生化学反应,将不溶的物质转 化为易溶物质,或者将硬度高的物质进行软化,然后通过磨粒的微 机械摩擦作用将这些化学反应物从硅片表面去除,溶入流动的液体 中带走,即在化学去膜和机械去膜的交替过程中实现平坦化的目的, 如图10⁃8所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

坦的工艺。经过平坦化处理的介电层,没有高低落差,在制

作金属线时很容易进行,而且光刻出的连线图形比较精确。

2

欧姆接触

加工成型的金属互连线与半导体之间由于功函数的差异

会形成一个势垒区。若只是简单的将金属和半导体连接在一 起,接触区就会出现整流效应,这种附加的单向导电性,使 得晶体管或集成电路不能正常工作。要使接触区不存在整流 效应,就是要形成欧姆接触,良好的欧姆接触应满足以下的

采用各种退火方法进行热退火,包括传统的烧结退火和 快速热退火,以便反应生产金属硅化物;

25

3.栓塞

多层金属布线使得金属

化系统中出现很多通孔,为

了保证两层金属间形成电通 路,这些通孔需要用金属塞 来填充。用于制作栓塞的材 料有很多种,但实用性较高,且已被集成电路制造广泛应用

的是钨塞和铝塞。

26

钨塞的制备有毯覆式金属钨淀积和选择性金属钨两种。 毯覆式金属钨淀积也叫反刻钨塞工艺,采用化学气相淀积法 生长钨薄膜后,将wafer上多余的钨刻蚀掉,是最广泛的制

方会出现空洞,金属连线变薄,极易引起断路,器件可靠性

较低。而在其它区域,由于原子的堆积会造成金属薄膜上出

现小丘,小丘短接会导致相邻的两条连线发生短路。器件工 作时,随着温度的增加,这两种缺陷会使铝的电迁移更加严 重,继而形成恶性循环 。 向铝中加入少量的铜(0.5%~4%),电迁移被有效

的抑制。但由于铜的抗腐蚀性较差,所以,金属反刻

接触区的整流特性严重退化,电压-电流的正反向特性趋于

一致,即由整流接触转化为欧姆接触。 势垒越窄,遂穿效应越明显,而势垒的宽度取决于半导 体的掺杂浓度,掺杂浓度越高,势垒越窄。因此,只要控制 好半导体的掺杂浓度,就可以得到良好的欧姆接触。

4

5

2.欧姆接触的制备

需要制备欧姆接触的地方并非都是重掺杂区,因次,必

备技术。选择性金属钨工艺中,钨只在接触窗底部成核生

长,直至长满整个孔洞,介质层表面不会生长钨膜,所以,

不需附加粘着层,也不需进行钨反刻,工艺简单。但互连可

靠性较低,而且钨要同时填满接触窗也很困难。因此,集成 电路制造不采用此法。

27

PVD法制备的铝膜台阶覆盖能力较差,接触窗或通孔 开口的水平方向有较厚的铝淀积,孔洞内壁的铝膜较薄, 易产生孔隙,影响可靠性。CVD法制备的铝膜电阻率低, 台阶覆盖能力强。因此,通常选择铝作为互连材料,钨作 为栓塞填充材料。

性仍然很高;抗侵蚀和氧化性要好。

20

通常用于阻挡层的金属是钛、钨、钽等难熔金属。铜在 硅和二氧化硅中的扩散率都很高,传统的阻挡层远不能满足 阻挡铜扩散的需要,需要有一层薄膜阻挡层将铜完全包装起

来。作为铜的阻挡层金属材料需满足以下要求:阻止铜扩

散;薄膜电阻低;与介质材料和铜的粘附性都很好;台阶覆

盖性好等。钽、氮化钽和钽硅氮都是铜阻挡层的备选材料。

条件:电压与电流之间具有线性的对称关系;接触电阻尽可

能低,不产生明显的附加阻抗;有一定的机械强度,能承受

冲击、震动等外力的作用。

3

1.欧姆接触的形成条件 金属铝与轻掺杂浓度( N D 1017 / cm3)的N型硅接触时, 形成整流接触;当提高N型硅的掺杂浓度( N D 1019 / cm3)后,

金属化与平坦化

一、欧姆接触 二、金属布线

三、金属膜的制备

四、平坦化 五、铜金属化

1

集成电路的各个组件制作完成后,需要按照设计要求将 这些组件进行相应的连接以形成一个完整的电路系统,并提 供与外电路相连接的接点,完成此项任务的就是金属布线。 金属化就是在组件制作完成的器件表面淀积金属薄膜,

金属线在IC中传导信号,介质层则保证信号不受临近金属线

24

填充生产金属硅化物的步骤如下: 依次用有机溶液、稀释过的氢氟酸和去离子水除去 wafer表面的杂质,再用氮气干燥wafer。 快速将清洗干燥后的wafer金属淀积腔内,有的 wafer需要采用氩离子溅射法清洁表面; 在wafer上淀积厚约20~200nm的金属薄膜,衬底

温度保持室温,也可在较高或较低的温度下进行淀积;

28

金属膜的制备

金属薄膜的制备方法有蒸发、溅射、金属CVD以及电

镀等。

1.金属CVD

CVD有很强的台

阶覆盖能力,具有良 好的高深宽比接触和 无间隙式的填充,在 金属淀积方面应用非

常广泛。

29

(1)氮化钛CVD

金属化系统中氮化钛主要作为Al、Cu以及W的金属阻

挡层,可以阻止上下层材料间的交互扩散,增强稳定性和可 靠性。 PVD法制备的氮化钛膜会在接触窗或介质窗顶部产生 悬突,继而导致孔洞的产生。所以,氮化钛通常采用金属化

硅化物是把难熔金属淀积在wafer上,进行高温退火处

理形成的。钛/硅是最普遍的接触硅化物,它用作晶体管有 源区和钨栓塞之间的接触。因为颗粒尺寸比钛/硅的尺寸小 了约十倍,钴硅化物的接触电阻很低。颗粒尺寸小也使得它 的接触电阻比较容易形成。因此,对于小尺寸器件,钴硅化

物是很有希望的硅化物。

23

在一些硅化物中发现,硅迅速的扩散穿过硅化物。扩散 发生在金属-硅化物-硅系统的热处理过程中,硅扩散穿过硅 化物进入到金属中,降低了系统的完整性。所以需要在硅化 物和金属层之间淀积一层金属阻挡层,氮化钛用于钨和铝的 金属阻挡层,钽用于铜的金属阻挡层。

裂、空洞以及应力等造成的材料失效。

15

(2)互连金属

最早用于集成电路制造的金属就是铝,它也是最普遍的

互连金属,以薄膜的形式在wafer中连接不同的器件。 室温下,铝的电阻率比铜、金、银的电阻率稍高,但是 由于铜和银比较容易腐蚀,在硅和二氧化硅中的扩散率太 高,这些都不利于它们用于集成电路的制造;另外,金和银

18

后若有剩余的铜就会促使侵蚀的发生。

钨可应用于小范围的局部金属互连。钨的抗电迁移性 好,可靠性比铝铜合金高。作为局部连线,钨的电阻率较 低,但对于长距离的连线,还是选择铝铜合金较好。

19

(3)阻挡层金属

阻挡层金属是淀积金属或金

属塞,其作用是阻止上下层材料

互相混合,对于0.18μm工艺,

阻挡层金属厚约20nm。 阻挡层金属应具有以下基本特性:能很好的阻挡材料的 扩散;电导率高,且有很低的欧姆接触电阻;与半导体以及 金属间的粘附性很好;抗电迁移能力强;阻挡层很薄时稳定

短路,在层间

淀积了介电层

起到隔离作用。

9

(2)多层电极 在一般的IC制造中通常采用铝作为电极,但对于高频

大功率器件、微波器件等会由于采用铝电极而导致器件失

效。要找到一种能完全代替铝的金属材料非常困难,金的导

电性很好但与二氧化硅之间的粘附性却很差,而且在高温下

会与硅形成金-硅合金;钼、铂等金属虽然熔点很高,但又 难以键合。因而只有采用多层金属电极。利用几种金属各自 的优点,取长补短,制作出符合要求的电极。

随着IC尺寸的减小,对金属布线的要求也越来越高:电

阻率要低、稳定性要高;可被精细的刻蚀,具有抗环境侵蚀

的能力;易于淀积成膜,粘附性要好,台阶覆盖能力强;互

连线应具有很强的抗电迁移能力,可焊性好。

8

1.多层金属布线 (1)多层金属布线结构 为了提高电路速度、集成度、缩短互连线,大规模集成 电路的金属层都是多层金属布线层。为了防止金属层之间的

为了不影响深宽比较高的栓塞的电阻率,阻挡层必须很薄。

21

(4)硅化物

难熔金属与硅反

应形成硅化物,硅化 物的热稳定性较高, 并且硅-难熔金属界面 的电阻率较低。为了

提高芯片性能,需要减小硅接触电阻,所以,硅化物是非常

重要的。

22

若参加反应的是多晶硅,形成的是多晶硅化物,多晶硅 栅的电阻率较高,导致RC信号的延迟。多晶硅化物对减小 连接多晶硅的电阻有益,而且与氧化硅的界面特性也很好。

10

多层金属电极大致可分为两类:用于微波晶体管、超高 频低噪声管等器件的铝基系统和用于高频大功率管的金基系 统。按器件经受的环境和使用的条件不同,采用不同的多层

金属结构。但按照作用,大体可分为四层(由硅片表面向外

依次为):欧姆接触层、粘附层、阻挡层以及导电层。

欧姆接触层的作用是与半导体层形成良好的欧姆接触,

WF6 与氢气反应生成钨

WF6 3H 2 W 6HF

33

为了阻止钨的扩散、保证它能很好的粘附在下层材料 上,需要在淀积钨之前淀积一层氮化钛膜。而为了得到低的 接触电阻,又需要在淀积氮化钛之前淀积钛。所以,垫膜 CVD的第一步是采用物理气相淀积法制备钛膜,接着淀积 一层氮化钛膜,最后再进行钨的淀积与平坦化.

学气相淀积法制备。

30

氮化钛CVD根据参加反应的气体分为有机和无机两

种,无机的氮化钛CVD气体源主要是四氯化钛,有机的则

主要是是TDMAT和TDEAT两种。无机气体淀积由于淀积

温度过高以及残留氯原子影响器件的可靠性等问题,不常采

用。而有机淀积的温度较低,所以氮化钛的淀积通常采用金 属有机化学气相淀积(MOCVD)。 MOCVD可分为TDMAT/TDEAT和TDMAT+ NH 3 /TDEAT+ NH 3 两大类,反应气体中不含氨气时,淀积膜的

须对要制作接触区的半导体进行重掺杂,以实现欧姆接触。

常用的方法有扩散法和合金法。合金法又叫烧结法,这

种方法不仅可以形成欧姆接触,而且也可制备PN结。合金 时,将金属放在wafer上,装进模具,压紧后,在真空中加 热到熔点以上,合金溶解与wafer凝固而结合在一起,形成 欧姆接触,合金完成。整个过程分为升温、恒温、降温三个

的成本比铝高,而且与二氧化硅的粘附性不好,所以,也不

常用。铝则能很容易的淀积在wafer上,而且刻蚀时分辨率

较高,所以,作为首选金属用于金属化。