8PA42;中文规格书,Datasheet资料

IR958-8P, 规格书,Datasheet 资料

Technical Data Sheet 1.6mm Side Looking Infrared Emitting DiodeIR958-8P█ Features․Low forward voltage ․Peak wavelength λp=950nm ․High reliability ․Pb free ․The product itself will remain within RoHS compliant version.█ DescriptionsThe IR958-8P is a GaAs infrared emitting diode. The miniature side-facing device is a chip that emits radiation from the side of the pink clear package.█ Applications․VCR ․Floppy disk drive ․Automatic stroboscope ․Cassette type recorder ․Optoelectronic switch ․Photo interrupter█ Device Selection GuidePart No. IR Chip Material GaAs Lens Color PinkEverlight Electronics Co., Ltd.http:\\Rev2Page:1 of 6芯天下--/Device No:DIR-958-142IR958-8P█ Package DimensionsNotes: 1.All dimensions are in millimeters 2.Tolerances unless dimensions ±0.2mmDevice No:DIR-958-142Everlight Electronics Co., Ltd.http:\\Rev2Page:2 of 6芯天下--/IR958-8P█ Absolute Maximum Ratings (Ta=25℃)Item Power Dissipation Reverse Voltage Forward Current Peak Forward Current (*1) Operating Temperature Storage Temperature Soldering Temperature (1/16 inch from body for 5 seconds) Notes: (*1) tw=100µ secs. T=10 m secs. Symbol PD VR IF IFP Topr Tstg Tsol Rating 75 6 50 1 -25~+85 -40~+85 260 Unit mW V mA A ℃ ℃ ℃█ Electro-Optical Characteristics (Ta=25℃)Parameter Collector Current Peak Wavelength Spectral Bandwidth View Angle Forward Voltage Reverse Current Symbol Ic(on) λp △λ 2θ1/2 VF IR Min 300 Typ 950 80 ±11 1.2 Max 2000 1.5 10 Unit μA nm nm Deg V μA Condition IF=4mA,VCE=3.5V IF =20mA IF =20mA IF =20mA IF =20mA VR=6VDevice No:DIR-958-142Everlight Electronics Co., Ltd.http:\\Rev2Page:3 of 6芯天下--/IR958-8PTypical Electro-Optical Characteristics CurvesFig.1 Forward Current vs. Ambient Temperature Fig.2 Spectral Distribution70 60 50 40 30 20 10 0 -25 0 25 50 75 85 100100 80 60 40 20 0IF=20mA Ta=25°CFig.3Peak Emission Wavelength Ambient TemperatureFig.4 Forward Current vs. Forward Voltage980104960109403109202900 -251 100 25 50 75 10001234Everlight Electronics Co., Ltd.http:\\Rev2Page:4 of 6芯天下--/IR958-8PTypical Electro-Optical Characteristics CurvesFig.5 Relative Intensity vs. Forward Current Fig.6 Relative Radiant Intensity vs Angular Displacement1000Ie-Radiant Intensity(mW/sr)-20-1001020 301001.01040 50 60 70 800.9 0.8 0.7100110110210310 4IF-Forward Current (mA)Everlight Electronics Co., Ltd.http:\\Rev2Page:5 of 6芯天下--/IR958-8P█ Test Method█ To Distinguish Intensity:Ranks Color Code No paint No paint No paint No paint No paint Parameter 7-2 7-1 6-2 6-1 5-2 Symbol Ic(on) Ic(on) Ic(on) Ic(on) Ic(on) Min 300 330 450 630 1000 Max 450 565 770 1300 2000 Unit μA μA μA μA μA Test Condition IF=4mA,VCE=3.5V IF=4mA,VCE=3.5V IF=4mA,VCE=3.5V IF=4mA,VCE=3.5V IF=4mA,VCE=3.5VDevice No:DIR-958-142Everlight Electronics Co., Ltd.http:\\Rev2Page:6 of 6芯天下--/IR958-8P█ Reliability Test Item And ConditionThe reliability of products shall be satisfied with items listed below. Confidence level:90% LTPD:10% NO. Item Test Conditions TEMP.:260℃±5℃ 30mins 5mins 30mins 5mins 10secs 5mins 1000 hrs 1000 hrs 1000 hrs 1000 hrs 22pcs 22pcs 22pcs 22pcs 50 Cycles 22pcs U:Upper Specification Limit L:Lower Specification Limit 0/1 0/1 0/1 0/1 Test Hours/ Cycles 10 secs 50 Cycles Sample Sizes 22pcs 22pcs IR≧U×2 Ic(ON)≦L×0.8 VF≧U×1.2 Failure Judgment Criteria Ac/Re 0/1 0/11 Solder Heat2 Temperature Cycle H : +85℃ L : -55℃ 3 Thermal Shock H :+100℃ L :-10℃ 4 High Temperature Storage 5 Low Temperature Storage0/1TEMP.:+100℃ TEMP.:-55℃6 DC Operating Life IF=20mA 7 High Temperature/ 85℃ / 85% R.H High HumidityEVERLIGHT ELECTRONICS CO., LTD. Office: No 25, Lane 76, Sec 3, Chung Yang Rd, Tucheng, Taipei 236, Taiwan, R.O.CTel: 886-2-2267-2000, 2267-9936 Fax: 886-2267-6244, 2267-6189, 2267-6306 http:\\Device No:DIR-958-142Everlight Electronics Co., Ltd.http:\\Rev2Page:7 of 6芯天下--/。

2SD882;中文规格书,Datasheet资料

October 2007Rev 31/82SD882NPN medium power transistorFeatures■High current■Low saturation voltage ■Complement to 2SB772Applications■Voltage regulation ■Relay driver ■Generic switch ■Audio power amplifier ■DC-DC converterDescriptionThe device is a NPN transistor manufactured by using planar technology resulting in rugged high performance devices. The complementary PNP type is 2SB772.Table 1.Device summaryOrder code Marking Package Packing 2SD882D882SOT -32T ubeAbsolute maximum ratings2SD882 1 Absolute maximum ratingsTable 2.Absolute maximum ratingSymbol Parameter Value UnitV CBO Collector-base voltage (I E = 0) 60VV CEO Collector-emitter voltage (I B = 0) 30VV EBO Collector-base voltage (I C = 0) 5VI C Collector current3AI CM Collector peak current (t P < 5ms)6AI B Base current1AI BM Base peak current (t P < 5ms)2AP TOT T otal dissipation at T c = 25°C12.5WT STG Storage temperature-65 to 150°CT J Max. operating junction temperature150°CTable 3.Thermal dataSymbol Parameter Value UnitR thJ-case Thermal resistance junction-case max10°C/W 2/83/82 Electrical characteristics(T CASE = 25°C; unless otherwise specified)Table 4.Electrical characteristicsSymbol ParameterTest conditions Min.Typ.Max.Unit I CES Collector cut-off current(V BE = 0)V CE = 60 V 10µA I CEO Collector cut-off current (I B = 0)V CE = 30 V 100µA I EBOEmitter cut-off current (I C = 0)V EB = 5 V10µAV (BR)CEO(1)Collector-emitter breakdownvoltage (I B = 0 )I C = 10 mA 30VV (BR)CBO Collector-base breakdownvoltage(I E = 0 )I C = 100 µA60VV (BR)EBO Emitter-base breakdownvoltage(I C = 0 )I E = 100 µA5V V CE(sat)(1)Collector-emitter saturationvoltageI C = 1 A I B = 50 mAI C = 2 A I B = 100 mAI C = 3 A I B = 150 mA 0.40.71.1V V V V BE(sat)(1)1.Pulsed duration = 300 ms, duty cycle ≤1.5%.Base-emitter saturation voltage I C = 2 A I B = 100 mA 1.2Vh FE DC current gain I C = 100 mA V CE = 2 V I C = 1 A V CE = 2 V I C = 3 A V CE = 2 V 1008030300f TTransition frequencyI C = 0.1 A V CE = 10 V100MHzcharacteristics (curves) 2.1 Typical4/82SD882Package mechanical data 3 Package mechanical dataIn order to meet environmental requirements, ST offers these devices in ECOPACK®packages. These packages have a Lead-free second level interconnect . The category ofsecond level interconnect is marked on the package and on the inner box label, incompliance with JEDEC Standard JESD97. The maximum ratings related to solderingconditions are also marked on the inner box label. ECOPACK is an ST trademark.ECOPACK specifications are available at: 5/8Package mechanical data2SD8826/82SD882Revision history7/84 Revision historyTable 5.Document revision historyDate RevisionChanges09-Sep-20052Final datasheet. New template 02-Oct-20073Updated mechanical data2SD8828/8Please Read Carefully:Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.All ST products are sold pursuant to ST’s terms and conditions of sale.Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.UNLESS O THERWISE SET FO RTH IN ST’S TERMS AND CO NDITIO NS O F SALE ST DISCLAIMS ANY EXPRESS O R IMPLIED WARRANTY WITH RESPECT TO THE USE AND/O R SALE O F ST PRO DUCTS INCLUDING WITHO UT LIMITATIO N IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS EXPRESSLY APPRO VED IN WRITING BY AN AUTHO RIZED ST REPRESENTATIVE, ST PRO DUCTS ARE NO T RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.ST and the ST logo are trademarks or registered trademarks of ST in various countries.Information in this document supersedes and replaces all information previously supplied.The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.© 2007 STMicroelectronics - All rights reservedSTMicroelectronics group of companiesAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America分销商库存信息: STM2SD882。

8312;中文规格书,Datasheet资料

Nominal data

Type 8312 VDC VDC min-1 W °C °C m3/h B dB(A) 12 6 .. 15 3300 2.6 -20 75 54 5.2 36

Nominal voltage Nominal voltage range Speed Power input Min. ambient temperature Max. ambient temperature Air flow Sound power level Sound pressure level

Connection line Locked-rotor protection Direction of rotation Direction of air flow Bearing Lifetime L10 at 40 °C Lifetime L10 at maximum temperature Mass Housing material Material of impeller Motor protection Approval

8312

DC axial compact fan

ebm-papst St. Georgen GmbH & Co. KG Hermann-Papst-Straße 1 D-78112 St. Georgen Phone +49 7724 81-0 Fax +49 7724 81-1309 info2@

ml = max. load · me = max. efficiency · rfa = running at free air · cs = customer specs · cu = customer unit Subject to alterations

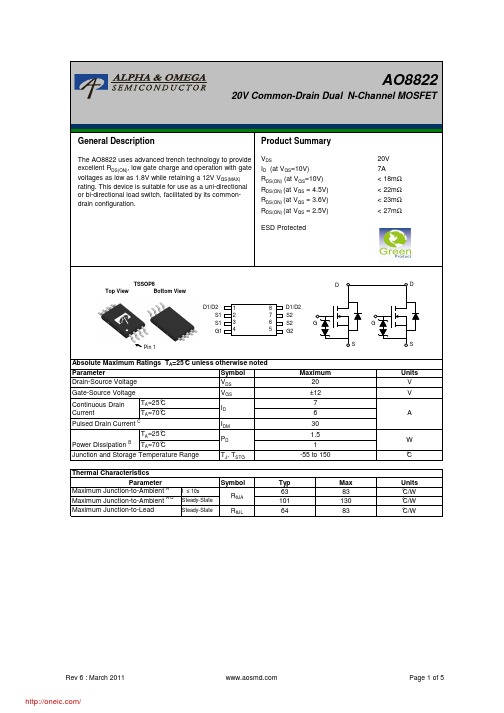

AO8822;中文规格书,Datasheet资料

Symbolt ≤ 10s Steady-State Steady-StateR θJLW Maximum Junction-to-Lead°C/W°C/W Maximum Junction-to-Ambient A D 6413083Maximum Junction-to-Ambient A T A =25°C T A =70°C Power DissipationBPulsed Drain Current CContinuous Drain T A =25°C AV Units ParameterAbsolute Maximum Ratings T A =25°C unless otherwise notedV Gate-Source Voltage Drain-Source Voltage °C/W R θJA 6310183°CThermal Characteristics Units ParameterTyp Max T A =70°CJunction and Storage Temperature Range Pin 1DSSymbolMin Typ Max Units BV DSS 20VV DS =20V, V GS =0V1T J =55°C 5I GSS 10µA BV GSO ±12V V GS(th)Gate Threshold Voltage 0.50.81V I D(ON)30A 131518T J =125°C2227151722m Ω161823m Ω182127m Ω28m Ωg FS 31S V SD 0.71V I S2A C iss 520650780pF C oss 140pF C rss60pFQ g (10V)121518nC Q g (4.5V)56.78nC Q gs 3.6nC Q gd 3nC t D(on)0.25us t r 0.45us t D(off)11us t f 4ust rr 81012ns Q rr81113.5nCTHIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT NOTICE.Body Diode Reverse Recovery TimeDrain-Source Breakdown Voltage On state drain currentI D =250µA, V GS =0V V GS =10V, V DS =5V V GS =10V, I D =7AReverse Transfer CapacitanceI F =7A, dI/dt=500A/µsV GS =0V, V DS =10V, f=1MHzSWITCHING PARAMETERS Electrical Characteristics (T J =25°C unless otherwise noted)STATIC PARAMETERS ParameterConditions I DSS µA V DS =V GS I D =250µA V DS =0V, V GS = ±10V Zero Gate Voltage Drain Current Gate-Body leakage current Gate-Source Breakdown Voltage V DS =0V, I G =±250µA Forward Transconductance Diode Forward VoltageR DS(ON)Static Drain-Source On-Resistancem ΩI S =1A,V GS =0VV DS =5V, I D =7A V GS =1.8V, I D =2AV GS =4.5V, I D =6.6A V GS =3.6V, I D =6A V GS =2.5V, I D =5.5A Turn-Off Fall TimeTotal Gate Charge V GS =10V, V DS =10V, I D =7AGate Source Charge Gate Drain Charge Total Gate Charge Body Diode Reverse Recovery Charge I F =7A, dI/dt=500A/µsMaximum Body-Diode Continuous CurrentInput Capacitance Output CapacitanceTurn-On DelayTime DYNAMIC PARAMETERS Turn-On Rise Time Turn-Off DelayTime V GS =10V, V DS =10V, R L =1.5Ω,R GEN =3ΩA. The value of R θJA is measured with the device mounted on 1in 2FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The value in any given application depends on the user's specific board design.B. The power dissipation P D is based on T J(MAX)=150°C, using ≤ 10s junction-to-ambient thermal resistance.C. Repetitive rating, pulse width limited by junction temperature T J(MAX)=150°C. Ratings are based on low frequency and duty cycles to keep initialT J =25°C.D. The R θJA is the sum of the thermal impedence from junction to lead R θJL and lead to ambient.E. The static characteristics in Figures 1 to 6 are obtained using <300µs pulses, duty cycle 0.5% max.F. These curves are based on the junction-to-ambient thermal impedence which is measured with the device mounted on 1in 2 FR-4 board with 2oz. Copper, assuming a maximum junction temperature of T J(MAX)=150°C. The SOA curve provides a single pulse ratin g.TYPICAL ELECTRICAL AND THERMAL CHARACTERISTICSTYPICAL ELECTRICAL AND THERMAL CHARACTERISTICSQ g (nC)Figure 7: Gate-Charge CharacteristicsV G S (V o l t s )48121620V DS (Volts)Figure 8: Capacitance Characteristics C a p a c i t a n c e (p F )VdsCharge Gate Charge Test Circuit & WaveformD iode RVVddVddVR esistive S w itching Test C ircuit & W aveform s分销商库存信息: AOSAO8822。

8PA14;中文规格书,Datasheet资料

If you need detailed product information, or help choosing the right product for your application, see our Interactive Catalog . Use the Interactive Catalog to access the most complete and up-to-date information available.The Interactive Catalog provides an extensive collection of product specifications, application data, and technical literature that can be searched based on criteria you select.This PDF catalog information was published in November 2000.Sensing and Control Honeywell Inc.11 West Spring Street Freeport, IL 61032/sensingSensing and ControlInteractive Catalog...Click this icon to try the Interactive Catalog.Interactive Catalog Supplements Catalog PDFsA96Honeywell ɀ Sensing and Control ɀ1-800-537-6945 USA ɀ⍣1-815-235-6847 International ɀ1-800-737-3360 CanadaSide mount with seal bootSide mount without seal bootROLLER PLUNGERACTUATED SWITCHESSide mount with seal bootFor rapid response – off the shelf service, all bold face listings are normally stocked items.Honeywell ɀSensing and Control ɀ1-800-537-6945 USA ɀ⍣1-815-235-6847 International ɀ1-800-737-3360 CanadaA97Side mountwithout seal bootONE-WAY ROLLER LEVER ACTUATED SWITCHESSide mount with seal bootLOW FORCE ROD LEVERRod can be formed in-line with the switch once, or cut, for application.Flange mount without seal bootCharacteristics: O.F. — Operating Force; P.T. — Pretravel; O.T. — Overtravel; D.T. — Differential TravelA98Honeywellɀ Sensing and Controlɀ1-800-537-6945 USAɀ⍣1-815-235-6847 Internationalɀ1-800-737-3360 CanadaHoneywellɀSensing and Controlɀ1-800-537-6945 USAɀ⍣1-815-235-6847 Internationalɀ1-800-737-3360 Canada A99A100Honeywell ɀSensing and Control ɀ1-800-537-6945 USA ɀ⍣1-815-235-6847 International ɀ1-800-737-3360 CanadaONE-WAY ROLLER LEVER ROD LEVERMANUALSide mount Flange mount Side mount with seal boot without seal boot with seal bootCOIL SPRINGROLLER LEVER (Reset)Flange mount Flange mount Side mountwith seal boot with seal boot without seal bootDesigned for demanding environmentsɀRugged zinc diecast housing with phosphate sealed epoxy finishResists harsh conditionsɀSwitch wiring cavity is epoxy filledɀWire entry area completely factory sealedɀNEMA 1, 3, 4, 12, 13switch within housingɀBroad electrical and temperature rangesEasy and economical to installɀMounts with just two screwsɀSwitch is preleaded with three (3) foot, four (4) conductor STOOW-A cable .41-.46 in. (10.4-11.7 mm)ɀConnector versions availableHoneywellɀ Sensing and Controlɀ1-800-537-6945 USAɀ⍣1-815-235-6847 Internationalɀ1-800-737-3360 Canada A101分销商库存信息: HONEYWELL8PA14。

SI2302-TP;中文规格书,Datasheet资料

Revision: A

/

3 of 5

2011/01/01

VGS, Gate to Source Voltage (V) ID, Drain Current (A)

VTH, Normalized Gate-Source Threshold Voltage

RDS(ON), Normalized RDS(ON), On-Resistance(Ohms)

IS, Source-drain current (A)

ID, Drain Current (A)

SI2302

10 25 C

Maximum Ratings @ 25OC Unless Otherwise Specified

Symbol VDS ID IDM VGS

PD R©JA

TJ

TSTG

Parameter Drain-source Voltage Drain Current-Continuous Drain Current-Pulsed a Gate-source Voltage

MCC

TM

Micro Commercial Components

5 VDS=10V ID=3.6A

4

3

2

1

0

0

2

4

6

Qg, Total Gate Charge (nC)

Figure 7. Gate Charge

VDD

RL VIN

D

VOUT

VGS

RGEN G

S

Figure 9. Switching Test Circuit

SN8P2722中文规格书

2.3.1 概述 ............................................................................................................................................................................. 24

.

SONiX TECHNOLOGY CO., LTD

Page 1

Version 1.1

版本 VER 1.0 VER 1.1

修正记录

日期 2008 年 3 月 2008 年 5 月 2009 年 6 月

修改记录 初版。 修改烧录信息章节内容。 在 T0M 寄存器中增加 TC0CKS2 和 TC0CKS1 位。

3.1

概述.................................................................................................................................................................................. 27

222 中央处理器(CPU)......................................................................................................................................................................... 9

2.1.2 编译选项 ...................................................................................................................................................................... 15

VIPER22ADIP;VIPER22AS;中文规格书,Datasheet资料

ABSOLUTE MAXIMUM RATINGS

Symbol VDS(sw) VDS(st) ID VDD IFB VESD Tj Tc Tstg Parameter Switching Drain Source Voltage (Tj=25 ... 125°C) Start Up Drain Source Voltage (Tj=25 ... 125°C) Continuous Drain Current Supply Voltage Feedback Current Electrostatic Discharge: Machine Model (R=0Ω; C=200pF) Charged Device Model Junction Operating Temperature Case Operating Temperature Storage Temperature (See note 1) (See note 2) Value -0.3 ... 730 -0.3 ... 400 Internally limited 0 ... 50 3 200 1.5 Internally limited -40 to 150 -55 to 150 Unit V V A V mA V kV °C °C °C

DESCRIPTION The VIPer22A combines a dedicated current mode PWM controller with a high voltage Power BLOCK DIAGRAM

O

bs

t e l o

VDD FB

r P e

INTERNAL SUPPLY _ 8/14.5V + + 42V _

PACKAGE

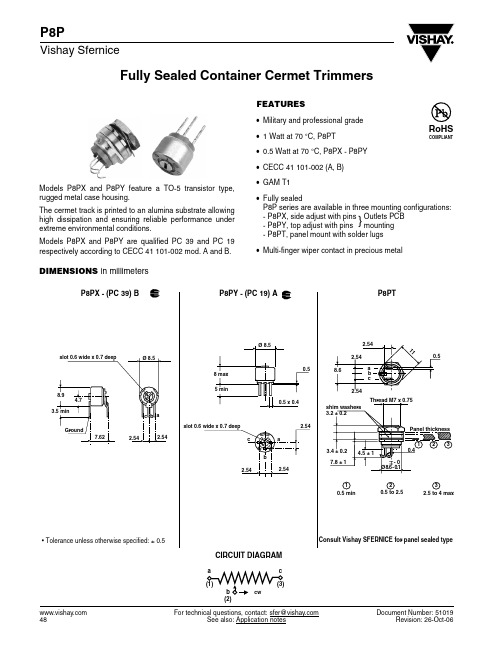

P8P中文资料

Fully Sealed Container Cermet Trimmers For technical questions, contact: sfer@See also: Application notesDocument Number: 5101948Revision: 26-Oct-06P8PVishay SferniceFEATURES•Military and professional grade •1 Watt at 70 °C, P8PT•0.5 Watt at 70 °C, P8PX - P8PY •CECC 41 101-002 (A, B)•GAM T1•Fully sealedP8P series are available in three mounting configurations:- P8PX, side adjust with pins - P8PY, top adjust with pins - P8PT, panel mount with solder lugs•Multi-finger wiper contact in precious metalModels P8PX and P8PY feature a TO-5 transistor type,rugged metal case housing.The cermet track is printed to an alumina substrate allowing high dissipation and ensuring reliable performance under extreme environmental conditions.Models P8PX and P8PY are qualified PC 39 and PC 19respectively according to CECC 41 101-002 mod. A and B.DIMENSIONS in millimetersP8PX - (PC 39) B• Tolerance unless otherwise specified: ± 0.5P8PTCIRCUIT DIAGRAM}Outlets PCB mountingDocument Number: 51019For technical questions, contact: sfer@See also: Application notes Revision: 26-Oct-0649P8PFully Sealed Container Cermet TrimmersVishay SferniceELECTRICAL SPECIFICATIONSResistive Element cermet Electrical Travel 270° ± 15°Resistance Range 10 Ω to 2.2 M ΩStandard series E3 1 - 2.2 - 4.7 and on request 1 - 2 - 5Tolerance Standard ± 10 %On Request ± 5 %Power RatingP8PX - P8PY 0.5 W at 70 °C P8PT1 W at 70 °CTemperature CoefficientSee Standard Resistance Element T ableLimiting Element Voltage (Linear Law)250 VContact Resistance Variation 2 % Rn or 1 ΩEnd Resistance (Typical) 1 Ω Dielectric Strength (RMS)1000 V Insulation Resistance (500 VDC)1 GΩMECHANICAL SPECIFICATIONSMechanical Travel300° ± 5°Operating Torque (max. Ncm)3End Stop Torque (max. Ncm)6Unit Weight (max. g)1... 3.1ENVIRONMENTAL SPECIFICATIONSTemperature Range - 55 °C to + 125 °C Climatic Category 55/125/56Sealingfully sealed container IP67POWER RATING CHARTPERFORMANCECECC 41100TYPICAL VALUES AND DRIFTS TESTSCONDITIONSΔRTRT (%)REQUIREMENTS ΔR 1-2R 1-2(%) ΔRTRT (%) ΔR 1-2R 1-2(%)Climatic SequencePhase A dry heat 125 °C Phase B damp heat Phase C cold - 55 °CPhase D damp heat 5 cycles± 2 %± 3 %± 0.5 %± 1 %Long Term Damp Heat56 days 40 °C, 93 % RH ± 2 %± 3 %± 0.5 %± 1 %Dielectric strength: 700 VInsulation resistance: > 100 M ΩDielectric strength: 1000 V Insulation resistance: > 104 M ΩRotational Life 200 cycles± 2 %± 1 %Contact res. variat.: < 5 % Rn Contact res. variat.: < 2 % Rn Load Life1000 h at rated power 90’/30’ - ambient temp. 70 °C± 2 %± 3 %± 1 %± 2 %Contact res. variat.: < 5 % Rn Contact res. variat.: < 1 % Rn Rapid Temperature Change 5 cycles- 55 °C to + 125 °C ± 1.5 %ΔV 1-2V 1-3≤ ± 1 %± 0.2 %ΔV 1-2V 1-3≤ ± 0.5 %Shock50 g at 11 m secs 3 successive shocks in 3 directions ± 1 %± 2 %± 0.1 %± 0.5 %Vibration 10 - 55 Hz 0.75 mm or 10 g during 6 hours± 1 %ΔV 1-2V 1-3≤ ± 2 %± 0.2 %ΔV 1-2V6≤ ± 0.5 % For technical questions, contact: sfer@See also: Application notesDocument Number: 5101950Revision: 26-Oct-06P8PVishay SferniceFully Sealed Container Cermet TrimmersSTANDARD RESISTANCE ELEMENT DATASTANDARD RESISTANCE VALUESP8PX - P8PYP8PT TCR - 55 °C + 125 °C MAX.POWER AT 70 °CMAX.WORKING VOLTAGEMAX. CUR.THROUGH WIPERMAX.POWER AT 70 °CMAX.WORKING VOLTAGEMAX. CUR.THROUGH WIPERΩW V mA W V mA ppm/°C 102247 0.52.23.34.822415010313.164.696.863162131460+ 2001002204701K 2.2K 4.7K 10K 22K 47K 100K 220K 470K 1M 2.2M0.50.280.130.060.028710.515.322.433.248.57.710515322425025025025070473222151074.83.22.21.11.530.250.1110.630.280.130.060.0310.014.821.731.646.968.6100.0148217250250250250250100674632211510.06.74.62.51.10.50.30.1± 100MARKINGPrinted :- VISHAY trademark - NF type if applicable - series - style- ohmic value (in Ω , k Ω, M Ω)- tolerance (in %)- manufacturing date - marking of terminal: 3PACKAGING- Plastic box of 50 pieces for P8PX and P8PY - Plastic box of 24 pieces for P8PTORDERING INFORMATIONP8MODEL PY STYLE 10 k ΩOHMIC VALUE ± 10 %TOLERANCE BL50PACKAGING e2LEAD FINISHP8PX and P8PY: BL50P8PT: BL24e2: SnAg alloyDocument Number: 91000Revision: 18-Jul-081DisclaimerLegal Disclaimer NoticeVishayAll product specifications and data are subject to change without notice.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, “Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.Product names and markings noted herein may be trademarks of their respective owners.元器件交易网。

UTS1JC124S;UTS0124P;UTS1JC104P;UTS1JC124P;UTS6JC18-32P;中文规格书,Datasheet资料

• pollution degree of the environment: - PD2 means only non conductive pollution occurs except that

occasionally a temporary conductivity caused by condensation is to be expected - PD3 means conductive pollution occurs or dry non conductive pollution occurs which becomes conductive due to condensation which is to be expected

- OV3 means a 2500V rated impulse voltage

U Nm* is not the working voltage. U Nm* has to be chosen according to the voltage of the power supply Un.

*Definition of U Nm rated insulation voltage (EN 50-1 24-1): r.m.s. withstand voltage value assigned by the manufacturer to the equipment or to a part of it, characterizing the specified (long-term) withstand capability of its insulation. NOTE: The rated insulation voltage is not necessarily equal to the-rated voltage of equipment which is primarily related to functional performance.

MIC4802YME;中文规格书,Datasheet资料

January 2011

M9999-013111-B

/

Micrel Inc.

Ordering Information

Part Number MIC4802YME

Pin Configuration

Temperature Range –40°C to +125°C

MIC4802

MIC4802

High Efficiency 800mA Single Channel Linear WLED Driver with Ultra Fast PWM™ Control

General Description

The MIC4802 is a high efficiency White LED (WLED) driver designed to drive a single LED up to 800mA. The MIC4802 constant current driver is designed to drive high power LED’s in various lighting applications. The MIC4802 provides the highest possible efficiency as this architecture has no switching losses present in traditional charge pumps or inductive boost circuits. It features a typical dropout of 280mV at 800mA. This allows the LEDs to be driven directly from the voltage source eliminating switching noise/losses present with the use of boost circuitry. The high accuracy (±1% Typical) current regulated WLED channel ensures uniform display illumination under all conditions. The brightness is controlled through an Ultra Fast PWM™ Control interface operating down to less than 1% duty cycle.

AO4818B;中文规格书,Datasheet资料

Gate-Source Voltage

VGS

Continuous Drain

TA=25°C

Current

TA=70°C

Pulsed Drain Current C

Avalanche Current C

Avalanche energy L=0.1mH C

ID

IDM IAS, IAR EAS, EAR

TA=25°C Power Dissipation B TA=70°C

VGS=10V, VDS=15V, ID=8A

6

7.5

9

nC

2.5

nC

Qgd

Gate Drain Charge

3

nC

tD(on)

Turn-On DelayTime

5

ns

tr

Turn-On Rise Time

VGS=10V, VDS=15V, RL=1.8Ω,

3.5

ns

tD(off)

Turn-Off DelayTime

B. The power dissipation PD is based on TJ(MAX)=150°C, using ≤ 10s junction-to-ambient thermal resistance. C. Repetitive rating, pulse width limited by junction temperature TJ(MAX)=150°C. Ratings are based on low frequency and duty cycles to keep initialTJ=25°C.

15 3V

10

5 VGS=2.5V

0

0

AD9952 Evaluation Board Datasheet说明书

功能框图图1.DC/PHASE CORRECTION DC/PHASE CORRECTIONC SS C L KS D I OSERIAL PORT INTERFACE15141323892325262838VPOS_3P3DECL1TO DECL4211119303136273340101VPOS_5VLDO VCOLDO 2.5VRFIN0RFIN12922POLYPHASE FILTERLOIN–REFINLOIN+I+I–Q–Q+QUAD DIVIDERPLL343935547611990-001Rev. ADocument FeedbackInformation furnished by Analog Devices is believed to be accurate and reliable. However , no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Speci cations subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2013–2014 Analog Devices, Inc. All rights reserved. Technical Support 695 MHz 至2700 MHz 正交解调器,集成小数N 分频PLL 和VCOADRF6820产品特性集成小数N 分频PLL 的I/Q 解调器RF 输入频率范围:695 MHz 至2700 MHz 内部LO 频率范围:356.25 MHz 至2850 MHz 输入P1dB :14.5 dBm (1900 MHz RF) 输入IP3:35 dBm (1900 MHz RF) 可编程HD3/IP3调整单刀双掷(SPDT) RF 输入开关RF 数字步进衰减范围:0 dB 至15 dB集成式RF 可调谐巴伦,支持单端50 Ω输入 多核集成式VCO解调1 dB 带宽:600 MHz 4个可选基带增益和带宽模式数字可编程LO 相位失调和直流零点可通过三线式串行端口接口(SPI)进行编程 40引脚、6 mm x 6 mm LFCSP 封装应用蜂窝W-CDMA/GSM/LTE 数字预失真(DPD)接收器 微波点对点无线电概述ADRF6820是一款高度集成的解调器和频率合成器,非常适合用于下一代通信系统中。

利智电子SG8P6402 8位OTP单片机 规格书说明书

Shenzhen LIZHI Electronic Technology Co.,Ltd规格说明书SG8P64028-Bit OTP MicrocontrollerVersion1.3目录1系统概述 (4)2特性简介 (4)3管脚说明及PAD MAP (6)3.1管脚说明 (6)3.2PAD MAP (8)4结构图 (10)5功能模块说明 (10)5.1SG51微控制器核 (10)5.1.1概述 (10)5.1.2特征 (10)5.1.3结构图 (11)5.1.4指令集 (12)5.1.5存储器组织 (17)5.1.6系统SFR寄存器映射 (20)5.1.7系统寄存器 (21)5.2系统模式 (24)5.2.1概述 (24)5.2.2特征 (24)5.2.3唤醒源 (24)5.2.4空闲模式(IDLE) (24)5.2.5停机模式(STOP) (25)5.2.6寄存器映射 (25)5.2.7寄存器说明 (25)5.3复位系统 (27)5.3.1概述 (27)5.3.2功能描述 (27)5.3.3寄存器映射 (28)5.3.4寄存器说明 (28)5.4中断系统 (30)5.4.1概述 (30)5.4.2特征 (30)5.4.3功能说明 (30)5.4.4SFR寄存器映射 (33)5.4.5SFR寄存器说明 (33)5.5时钟系统 (37)5.5.1概述 (37)5.5.2寄存器映射 (37)5.5.3寄存器说明 (37)5.6电源系统 (39)5.6.1概述 (39)5.6.2结构图 (39)5.6.3寄存器映射 (39)5.6.4寄存器说明 (40)5.7通用IO端口控制器 (41)5.7.1概述 (41)5.7.2特征 (41)5.7.3寄存器映射 (42)5.7.4寄存器说明 (43)5.8WatchDog(看门狗)定时器 (55)5.8.1概述 (55)5.8.2特征 (55)5.8.3WDT工作模式 (55)5.8.4超时周期 (55)5.8.5清零WDT (56)5.8.6非工作模式下WDT工作原理 (56)5.8.7寄存器映射 (56)5.8.8寄存器说明 (56)5.9定时器/计数器模块Timer0/Timer1 (59)5.9.1寄存器映射 (59)5.9.2寄存器描述 (59)5.10USB模块 (64)5.10.1概述 (64)5.10.2寄存器映射 (64)5.10.3控制寄存器说明 (65)5.10.4UDC通信流程说明 (83)5.10.5UDC通信举例 (85)6应用参考原理图 (86)7极限参数 (86)8电气参数 (87)9修订记录 (89)1系统概述SG8P6402是完全集成的混合信号片上系统型MCU。

STS2DPF80;中文规格书,Datasheet资料

1/9June 2004STS2DPF80DUAL P-CHANNEL 80V - 0.21 Ω - 2.3A SO-8STripFET™ POWER MOSFETRev.0.1■TYPICAL R DS (on) = 0.21 Ω■STANDARD OUTLINE FOR EASYAUTOMATED SURFACE MOUNT ASSEMBLYDESCRIPTIONThis application specific Power MOSFET is the second generation of STMicroelectronis unique "Single Feature Size™" strip-based process. The resulting transistor shows extremely high packing density for low on-resistance, rugged avalanche characteristics and less critical alignment steps therefore a remarkable manufacturing reproduc-ibility .APPLICATIONS■DC/DC CONVERTERS■BATTERY MANAGEMENT IN NOMADIC EQUIPMENT■POWER MANAGEMENT IN CELLULARPHONES AND DISPLAY NEW GENERATIONOrdering InformationTYPE V DSS R DS(on)I D STS2DPF8080 V<0.25 Ω2.3 ASALES TYPEMARKING PACKAGE PACKAGING STS8DPF80S8DPF80SO-8TAPE & REELABSOLUTE MAXIMUM RATINGSPulse width limited by safe operating area.Note: For the P-CHANNEL MOSFET actual polarity of voltages and current has to be reversedSymbol Parameter Value Unit V DS Drain-source Voltage (V GS = 0)80V V DGR Drain-gate Voltage (R GS = 20 k Ω)80VV GS Gate- source Voltage± 20VI D Drain Current (continuous) at T C = 25°C Single Operation Drain Current (continuous) at T C = 100°C Single Operation 2.01.3A A I DM (•)Drain Current (pulsed)8A P tot Total Dissipation at T C = 25°C 2.5W T stg Storage Temperature-55 to 150°C T jMax. Operating Junction Temperature150°COb s o l e t e P r o d uc t (s ) - O b s o l e t e P r od u c t (s ) -Ob s o l e t e P r o d uc t (s ) - O b s o l e t e P r od u c t (s ) STS2DPF802/9TAB.1 THERMAL DATA(*) When Mounted on 1 inch 2 FR-4 board, 2 oz of Cu and t [ 10 sec.ELECTRICAL CHARACTERISTICS (T CASE = 25 °C UNLESS OTHERWISE SPECIFIED)TAB.2 OFFTAB.3 ON (*)TAB.4 DYNAMICRthj-PCB (*)Thermal Resistance Junction-PCB62.5°C/WSymbol ParameterTest ConditionsMin.Typ.Max.Unit V (BR)DSS Drain-sourceBreakdown VoltageI D = 250 µA, V GS = 080V I DSSZero Gate VoltageDrain Current (V GS = 0)V DS = Max RatingV DS = Max Rating T C = 125°C 110µA µAI GSSGate-body Leakage Current (V DS = 0)V GS = ± 20 V±100nASymbol Parameter Test Conditions Min.Typ.Max.Unit V GS(th)Gate Threshold Voltage V DS = V GS I D = 250 µA 24VR DS(on)Static Drain-source On ResistanceV GS = 10 V I D = 1 A0.210.25ΩSymbol Parameter Test Conditions Min.Typ.Max.Unit g fs (*)Forward Transconductance V DS = 10V I D =1A4SC iss C oss C rssInput Capacitance Output Capacitance Reverse Transfer CapacitanceV DS = 25V, f = 1 MHz, V GS = 073989.531pF pF pFO b s o l e t e P r o d u c t (s ) - O b s o l e t e P r o d u c t (s )u c t (s ) - O b s o l e t e P r o d u c t (s ) 3/9STS2DPF80TAB.5 SWITCHING ONTAB.6 SWITCHING OFFTAB.7 SOURCE DRAIN DIODE(*)Pulsed: Pulse duration = 300 µs, duty cycle 1.5 %.(•)Pulse width limited by safe operating area.Symbol ParameterTest ConditionsMin.Typ.Max.Unit t d(on)t r Turn-on Delay Time Rise TimeV DD = 40 VI D = 1 A R G =4.7 ΩV GS = 10 V (Resistive Load, Figure 1)13.518ns ns Q g Q gs Q gdTotal Gate Charge Gate-Source Charge Gate-Drain ChargeV DD = 64V I D = 2A V GS =10V (See test circuit, Figure 2)202.54.9nC nC nCSymbol ParameterTest ConditionsMin.Typ.Max.Unit t d(off)t fTurn-off Delay Time Fall TimeV DD = 40 V I D = 1 AR G =4.7Ω,V GS = 10 V (Resistive Load, Figure 1)3213ns nsSymbol ParameterTest Conditions Min.Typ.Max.Unit I SD I SDM (•)Source-drain CurrentSource-drain Current (pulsed) 2.39.2A AV SD (*)Forward On VoltageI SD = 1 A V GS = 0 1.2Vt rr Q rrI RRMReverse Recovery Time Reverse Recovery Charge Reverse Recovery Current I SD = 2 A di/dt = 100A/µsV DD = 40 VT j = 150°C (See test circuit, Figure 3)47873.7ns nC AELECTRICAL CHARACTERISTICS (continued) t e P r o d u c t (s ) - O b s o l e t e P r o d u c t (s )STS2DPF80O b s ol e te Pr o d5/9STS2DPF80O b s o lOb s o l e t e P r o d uO b s o l e t e P r o d u c t (STS2DPF806/9Fig. 1: Switching Times Test Circuits For Resistive O b s o l e t O b s o l e t e PSTS2DPF807/9Ob s o l e t e P r o d uc t (s ) - O b s o l e t e P r od u c t (s ) STS2DPF808/9Revision HistoryDateRevisionDescription of ChangesWednesday 16 June 20040.1FIRST ISSUEO b s o l e t e P r o d u c t (s ) - O b s o l e t e P r o d u c t (s )Ob s o l e t e P r o d uc t (s ) - O b s o l e t e P r od u c t (s ) 9/9STS2DPF80Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is registered trademark of STMicroelectronicsAll other names are the property of their respective owners.© 2004 STMicroelectronics - All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco -Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.O b s o l e t e P r o d u c t (s ) - O b s o l e t e P r o d u c t (s )分销商库存信息: STMSTS2DPF80。

MB85RC64PNF-G-JNE1;中文规格书,Datasheet资料

FUJITSU SEMICONDUCTORDATA SHEETCopyright©2010-2011 FUJITSU SEMICONDUCTOR LIMITED All rights reserved 2011.6Memory FRAM64 K (8 K × 8) Bit I 2CMB85RC64■DESCRIPTIONThe MB85RC64 is a FRAM (Ferroelectric Random Access Memory) Stand-Alone chip in a configuration of 8,192 words × 8 bits, using the ferroelectric process and silicon gate CMOS process technologies for forming the nonvolatile memory cells.The MB85RC64 adopts the two-wire serial interface.Unlike SRAM, the MB85RC64 is able to retain data without using a data backup battery.The read/write endurance of the nonvolatile memory cells used for the MB85RC64 has improved to be at least 1010 cycles, significantly out performing Flash memory and E 2PROM in the number.The MB85RC64 does not need a polling sequence after writing to the memory such as the case of Flash memory nor E 2PROM.■FEATURES•Bit configuration : 8,192 words × 8 bits •Operating power supply voltage : 2.7 V to 3.6 V •Operating frequency : 400 kHz (Max) •T wo-wire serial interface : I 2C-bus specification ver. 2.1 compliant, supports Standard-mode/Fast-mode.Fully controllable by two ports: serial clock (SCL) and serial data (SDA).•Operating temperature range : − 40 °C to +85 °C •Data retention : 10 years ( + 75 °C) •Read/write endurance : 1010 times •Package : Plastic / SOP , 8-pin (FPT -8P-M02)•Low power consumption : Operating current 0.15 mA (Max: @400 kHz), Standby current 5 μA (Typ)DS05–13109–3EMB85RC64■PIN FUNCTIONAL DESCRIPTIONSPinNumberPin Name Functional Description1 to 3A0 to A2Device Address pinsThe MB85RC64 can be connected to the same data bus up to 8 devices. Device addresses are used in order to identify each of the devices. Connect these pins to VDD pin or VSS pin externally. Only if the combination of VDD and VSS pins matches a device, an address and a code inputted from the SDA pin, the device operates. In the open pin state, A0, A1, and A2 pins are pulled-down and recognized as “L”.4VSS Ground pin5SDA Serial Data I/O pinThis is an I/O pin of serial data for performing bidirectional communication of address and writing or reading data of FRAM memory cell array. It is an open drain output that may be wired OR with other open drain or open collector sig-nals on the bus, so a pull-up resistance is required to be connected to the ex-ternal circuit.6SCL Serial Clock pinThis is a clock input pin for input/output timing serial data. Data is sampled on the rising edge of the clock and output on the falling edge.7WP Write Protect pinWhen the Write Protect pin is “H”, the writing operation is disabled. When the Write Protect pin is “L”, the entire memory region can be overwritten. The read-ing operation is always enabled regardless of the Write Protect pin condition. In the open pin state, the Write Protect pin is pulled-down and recognized as “L”.8VDD Supply Voltage pinMB85RC64■I2C (Inter-Integrated Circuit)The MB85RC64 has the two-wire serial interface; the I2C bus,and operates as a slave device.The I2C bus defines communication roles of “master” and “slave” devices, with the master side holding the authority to initiate control. Furthermore, a I2C bus connection is possible where a single master device is connected to multiple slave devices in a party-line configuration. In this case, it is necessary to assign a unique device address to the slave device.2MB85RC64■I2C COMMUNICATION PROTOCOLThe I2C bus is a two wire serial interface that uses a bidirectional data bus (SDA) and serial clock (SCL). A data transfer can only be initiated by the bus master, which will also provide the serial clock for synchroni-zation. The SDA signal should change while SCL is Low. However, as an exception, when starting and stopping communication sequence, SDA is allowed to change while SCL is High.•Start ConditionTo start read or write operations by the I2C bus, set the SDA input from High to Low while the SCL input is in High in order to start reading and writing.•Stop ConditionSet the SDA input from Low to High while the SCL input is in High in order to terminate the I2C bus commu-nication. Because the MB85RC64 does not need the writing wait time unlike E2PROM, it goes to the standby state immediately after the stop condition input.Note : The FRAM device does not need the programming wait time like t WC after issuing the Stop Condition such as.MB85RC64■ACKNOWLEDGE (ACK)In the I2C bus, serial data including address or memory information is sent in units of 8 bits. The acknowledge signal indicates that every each 8 bits of the data is successfully sent and received. The information receiver side usually outputs “L” every time on the 9th SCL clock after each 8 bits are successfully transmitted. On the transmitter side, the bus is temporarily released to Hi-Z every time on this 9th clock to allow the acknowl-edge signal to be received and checked. During this Hi-Z-released period, the receiver side pulls the SDA line down to indicate “L” that the previous 8bits communication is successfully received.If the information receiver side detects Stop condition before driving the acknowledge “L”, the read operation ends and the I2C bus enters the standby state. If Stop condition is not sent, nor does the transmitter detect the acknowledge “L”, the bus remains in the released state “H” without doing anything.MB85RC64■DEVICE ADDRESS WORD (Slave address)Following the start condition, the bus master sends the 8bits device address word (Slave address) to start I2C communication. The device address word (8bits) consists of a device Type code (4bits), device address code (3bits), and a read/write code (1bit).•Device Type Code (4bits)The upper 4 bits of the device address word are a device type code that identifies the device type, and are fixed at “1010” for the MB85RC64.•Device Address Code (3bits)Following the device type code, the 3 bits of the device address code are input in order of A2, A1, and A0.Each MB85RC64 is given a unique 3bits code on the device address pin (external hardware pin A2, A1, and A0). When the device address code is received by the slave device, the slave only responds if the hardware device address of which is equal to its unique 3bits code.•Read/Write Code (1bit)The 8th bit of the device address word is the R/W (read/write) code. When the R/W code is “0”, a write operation is enabled, and the R/W code is “1”, a read operation is enabled for the MB85RC64.It turns to a stand-by state if the device code is not “1010” or device address code does not equal to pins A2, A1, and A0.MB85RC64■DATA STRUCTUREIn the I2C bus, the acknowledge “L” is output on the 9th bit after the 8 bits of the device and address word following the start condition. After confirming the acknowledge response at the slave, the I2C master outputs 8bits × 2 memory address to the I2C slave. When the memory address input ends, the slave again outputs the acknowledge “L”. After this operation, the I/O data follows in units of 8 bits, with the acknowledge “L”output after every 8bits.It is determined by the R/W code whether the data line is driven by the master or the slave. For a write operation the slave will accept 8bits from the master then send an acknowledge. If the master detects the acknowledge, the master will transfer the next 8bits. For a read operation the slave will place 8bits on the I2C bus, then wait for an acknowledge from the master.■FRAM ACKNOWLEDGE -- POLLING NOT REQUIREDThe MB85RC64 performs write operations at the same speed as read operations, so any waiting time for an ACK polling* does not occur. The write cycle takes no additional time.*: As to E2PROM, the Acknowledge Polling is performed as a progress check in the write programming step.It places NAK condition on the bus as of “not acknowledged” during the writing programming period. The busy status for the write programming is given from 9th ACK bit. That “done” condition is placed onto I2C bus by E2PROM I2C device and your program had to poll the bus in order to sense that condition.■WRITE PROTECT (WP)The entire memory array can be write protected using the Write Protect pin. When the Write Protect pin is set to “H”, the entire memory map will be write protected. When the Write Protect pin is “L”, all addresses may be overwritten. Reading is allowed regardless of the WP pin's High/Low.Note : The Write Protect pin is pulled down internally to VSS pin, therefore if the Write Protect pin is open, the pin status is detected as Low (write enabled).MB85RC64■COMMAND•Byte WriteIf the 8th bit of the device address word (R/W = 0) is sent following the start condition, the slave responds with an ACK. After this ACK, write addresses and data are sent in the same way, and the write ends byNote : In the MB85RC64, input “000” as the upper 3 bits of the MSB.•Page WriteIf additional 8bits are sent after the same command as Byte Write, a page write is performed. If more bytes are sent than will fit up to the end of the address, the address rolls over to 0000H. Therefore, if more than 8KBytes are sent, the data is overwritten in order starting from the start of the FRAM memory address that was written first. Because FRAM performs write operations at bus speed, the data will be written to FRAMNote :It is not necessary to take a period for internal write operation cycles from the buffer to the memory after the stop condition is generated.MB85RC64•Current Address ReadWhen the previous write or read operation finishes successfully up to the stop command and if the last accessed address is taken to be “n”, then the address at “n+1” is read by sending the following command unless turning the power off. If the end of the address range is reached internally, the address counter will•Random ReadThe one byte of data at the address as saved in the buffer can be read out synchronously to SCL by specifying the address in the same way as for a write, and then issuing another start condition and sending the Control Byte (R/W = 1).The final NACK is issued by the receiver that receives the data. In this case, this bit is issued by the masterMB85RC64•Sequential ReadData can be received continuously following the control byte after specifying the address the same as for Random Read. If the read reaches the end of address for the MB85RC64, the internal read address auto-分销商库存信息: FUJITSUMB85RC64PNF-G-JNE1。

CS42L52中文资料

Low Power, Stereo CODEC w/Headphone & Speaker AmpsStereo CODECHigh Performance Stereo ADC & DAC–98dB Dynamic Range (A-wtd) –-88dB THD+N Flexible Stereo Analog Input Architecture–4:1 Analog Input MUX –Analog Input Mixing–Analog Passthru with Volume Control–Analog Programmable Gain Amplifier (PGA) Programmable Automatic Level Control (ALC)–Noise Gate for Noise Suppression–Programmable Threshold & Attack/ReleaseRates Dual MIC Inputs–Differential or Single-Ended–+16dB to +32dB w/1dB step MIC Pre-Amplifiers–Programmable, Low Noise MIC Bias Levels Digital Signal Processing Engine–Bass & Treble Tone Control, De-Emphasis–Master Vol. and Independent PCM SDIN + ADC SDOUT Mix Volume Control–Soft-Ramp & Zero-Cross Transitions –Programmable Peak-Detect and Limiter –Beep Generator w/Full Tone ControlClass D Stereo/Mono Speaker AmplifierNo External Filter RequiredHigh Stereo Output Power at 10% THD+N– 2 x 1.00 W into 8Ω @ 5.0V – 2 x 550mW into 8Ω @ 3.7V – 2 x 230mW into 8Ω @ 2.5V High Mono Output Power at 10% THD+N– 1 x 1.90W into 4Ω @ 5.0V – 1 x 1.00W into 4Ω @ 3.7V – 1 x 350mW into 4Ω @ 2.5V Direct Battery Powered Operation–Battery Level Monitoring & Compensation 82% Efficiency at 800 mWPhase-Aligned PWM Output Reduces IdleChannel CurrentSpread Spectrum Modulation Low Quiescent CurrentStereo Headphone AmplifierGround Centered Outputs–No DC-Blocking Capacitors Required –Integrated Negative Voltage Regulator High Power Output at -75dB THD+N– 2 x 23mW Into 16Ω @ 1.8V – 2 x 44mW Into 16Ω @ 2.5V (Features continued on page 2)CS42L52CS42L52System Features12, 24, and 27MHz Master Clock Support inAddition to Typical Audio Clock Rates High Performance 24-bit Converters–Multi-bit Delta Sigma Architecture–Very Low 64Fs Oversampling Clock Reduces Power ConsumptionLow Power Operation–Stereo Analog Passthru: 10 mW @ 1.8 V –Stereo Playback: 14 mW @ 1.8 V–Stereo Rec. and Playback: 23 mW @ 1.8V Variable Power Supplies– 1.8 V to 2.5 V Digital & Analog – 1.6V to 5V Class D Amplifier– 1.8V to 2.5V Headphone Amplifier – 1.8 V to 3.3V Interface LogicPower Down Management–ADC, DAC, CODEC, MIC Pre-Amplifier, PGA,Headphone Amplifier, Speaker Amplifier Analog & Digital Routing/Mixes:–Line/Headphone Out =Analog In (ADCBypassed)–Line/Headphone/SpeakerOut =ADC +Digital In–Digital Out =ADC +Digital In –Internal Digital Loopback –Mono Mixes Flexible Clocking Options–Master or Slave Operation–High Impedance Digital Output Option (for easyMUXing between CODEC & other data sources)–Quarter-Speed Mode - (i.e. allows 8 kHz Fswhile maintaining a flat noise floor up to 16kHz)– 4 kHz to 96 kHz Sample Rates I²C ® Control Port OperationTemp. Monitor w/Thermal Foldback &ShutdownHeadphone/Speaker Detection Input Pop and Click SuppressionApplicationsDigital Voice Recorders, Digital Cameras &Camcorders PDA’sPersonal Media Players Portable Game ConsolesGeneral DescriptionThe CS42L52 is a highly integrated, low power stereo CODEC with headphone and Class D speaker amplifiers. The CS42L52 offers many features suitable for low power, porta-ble system applications.The ADC input path allows independent channel control of a number of features. Input summing amplifiers mix and select line-level and/or microphone level inputs for each channel.The microphone input path includes a selectable programma-ble-gain pre-amplifier stage and a low noise MIC bias voltage supply. A PGA is available for line or microphone inputs and provides analog gain with soft ramp and zero cross transi-tions. The ADC also features a digital volume control with soft ramp transitions. A programmable ALC and Noise Gate mon-itor the input signals and adjust the volume levels appropriately. To conserve power, the ADC may be bypassed while still allowing full analog volume control.The DAC output path includes a digital signal processing en-gine with various fixed function controls.Tone Control provides bass and treble adjustment of four selectable corner frequen-cies. The Digital Mixer provides independent volume control for both the ADC output and PCM input signal paths, as well as a master volume control. Digital Volume controls may be configured to change on soft ramp transitions while the analog controls can be configured to occur on every zero crossing.The DAC also includes de-emphasis, limiting functions and a BEEP generator delivering tones selectable across a range of two full octaves.The stereo headphone amplifier is powered from a separate positive supply and the integrated charge pump provides a negative supply. This allows a ground-centered analog output with a wide signal swing and eliminates external DC-blocking capacitors.The Class D stereo speaker amplifier does not require an external filter and provides the high efficiency amplification re-quired by power sensitive portable applications. The speaker amplifier may be powered directly from a battery while the in-ternal DC supply monitoring and compensation provides a constant gain level as the battery’s voltage decays. An internal temperature monitor alerts the user and automatically atten-uates and/or shuts down the PWM speaker output when an overload condition causes temperatures to exceed safe oper-ating levels.In addition to its many features, the CS42L52 operates from a low voltage analog and digital core making it ideal for portable systems that require extremely low power consumption in a minimal amount of space.The CS42L52 is available in a 40-pin QFN package in both Commercial (-40 to +85 °C) and Automotive (-40 to +105 °C)grades. The CS42L52 Customer Demonstration board is also available for device evaluation and implementation sugges-tions. Please refer to “Ordering Information” on page 82 for complete ordering information.CS42L52 TABLE OF CONTENTS1. PIN DESCRIPTIONS (8)1.1 I/O Pin Characteristics (9)2. TYPICAL CONNECTION DIAGRAM (10)3. CHARACTERISTIC AND SPECIFICATIONS (11)RECOMMENDED OPERATING CONDITIONS (11)ABSOLUTE MAXIMUM RATINGS (11)ANALOG INPUT CHARACTERISTICS (COMMERCIAL - CNZ) (12)ANALOG INPUT CHARACTERISTICS (AUTOMOTIVE - DNZ) (13)ADC DIGITAL FILTER CHARACTERISTICS (14)ANALOG OUTPUT CHARACTERISTICS (COMMERCIAL - CNZ) (15)ANALOG OUTPUT CHARACTERISTICS (AUTOMOTIVE - DNZ) (16)ANALOG PASSTHRU CHARACTERISTICS (17)PWM OUTPUT CHARACTERISTICS (Note 9) (17)LINE OUTPUT VOLTAGE LEVEL CHARACTERISTICS (18)HEADPHONE OUTPUT POWER CHARACTERISTICS (19)COMBINED DAC INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE (20)SWITCHING SPECIFICATIONS - SERIAL PORT (21)SWITCHING SPECIFICATIONS - I²C CONTROL PORT (22)DC ELECTRICAL CHARACTERISTICS (23)DIGITAL INTERFACE SPECIFICATIONS & CHARACTERISTICS (23)POWER CONSUMPTION (24)4. APPLICATIONS (25)4.1 Overview (25)4.1.1 Basic Architecture (25)4.1.2 Line & MIC Inputs (25)4.1.3 Line & Headphone Outputs (25)4.1.4 Speaker Driver Outputs (25)4.1.5 Fixed Function DSP Engine (25)4.1.6 Beep Generator (25)4.1.7 Power Management (25)4.2 Analog Inputs (26)4.2.1 MIC Inputs (27)4.2.2 Automatic Level Control (ALC) (27)4.2.3 Noise Gate (28)4.3 Analog Outputs (29)4.3.1 Beep Generator (30)4.3.2 Limiter (31)4.4 Analog In to Analog Out Passthru (32)4.4.1 Overriding the ADC Power Down (32)4.4.2 Overriding the PGA Power Down (33)4.5 PWM Outputs (33)4.5.1 Mono Speaker Output Configuration (33)4.5.2 VP Battery Compensation (33)4.5.2.1 Maintaining a Desired Output Level (34)4.6 Serial Port Clocking (34)4.7 Digital Interface Formats (36)4.7.1 DSP Mode (36)4.8 Initialization (36)4.9 Recommended Power-Up Sequence (37)4.10 Recommended Power-Down Sequence (37)4.11 Control Port Operation (38)4.11.1 I²C Control (38)CS42L524.11.2 Memory Address Pointer (MAP) (39)4.11.2.1 Map Increment (INCR) (39)5. REGISTER QUICK REFERENCE (40)6. REGISTER DESCRIPTION (42)6.1 Chip I.D. and Revision Register (Address 01h) (Read Only) (42)6.1.1 Chip I.D. (Read Only) (42)6.1.2 Chip Revision (Read Only) (42)6.2 Power Control 1 (Address 02h) (42)6.2.1 Power Down ADC Charge Pump (42)6.2.2 Power Down PGAx (42)6.2.3 Power Down ADCx (43)6.2.4 Power Down (43)6.3 Power Control 2 (Address 03h) (43)6.3.1 Power Down ADC Override (43)6.3.2 Power Down MICx (43)6.3.3 Power Down MIC Bias (43)6.4 Power Control 3 (Address 04h) (44)6.4.1 Headphone Power Control (44)6.4.2 Speaker Power Control (44)6.5 Clocking Control (Address 05h) (44)6.5.1 Auto-Detect (44)6.5.2 Speed Mode (45)6.5.3 32kHz Sample Rate Group (45)6.5.4 27 MHz Video Clock (45)6.5.5 Internal MCLK/LRCK Ratio (45)6.5.6 MCLK Divide By 2 (46)6.6 Interface Control 1 (Address 06h) (46)6.6.1 Master/Slave Mode (46)6.6.2 SCLK Polarity (46)6.6.3 ADC Interface Format (46)6.6.4 DSP Mode (46)6.6.5 DAC Interface Format (47)6.6.6 Audio Word Length (47)6.7 Interface Control 2 (Address 07h) (47)6.7.1 SCLK equals MCLK (47)6.7.2 SDOUT to SDIN Digital Loopback (47)6.7.3 Tri-State Serial Port Interface (48)6.7.4 Speaker/Headphone Switch Invert (48)6.7.5 MIC Bias Level (48)6.8 Input x Select: ADCA and PGAA (Address 08h), ADCB and PGAB (Address 09h) (48)6.8.1 ADC Input Select (48)6.8.2 PGA Input Mapping (49)6.9 Analog & HPF Control (Address 0Ah) (49)6.9.1 ADCx High-Pass Filter (49)6.9.2 ADCx High-Pass Filter Freeze (49)6.9.3 Ch. x Analog Soft Ramp (49)6.9.4 Ch. x Analog Zero Cross (49)6.10 ADC HPF Corner Frequency (Address 0Bh) (50)6.10.1 HPF x Corner Frequency (50)6.11 Misc. ADC Control (Address 0Ch) (50)6.11.1 ADC Channel B=A (50)6.11.2 Digital MUX (50)6.11.3 Digital Sum (50)6.11.4 Invert ADC Signal Polarity (50)CS42L526.11.5 ADC Mute (51)6.12 Playback Control 1 (Address 0Dh) (51)6.12.1 Headphone Analog Gain (51)6.12.2 Playback Volume Setting B=A (51)6.12.3 Invert PCM Signal Polarity (51)6.12.4 Master Playback Mute (51)6.13 Miscellaneous Controls (Address 0Eh) (52)6.13.1 Passthru Analog (52)6.13.2 Passthru Mute (52)6.13.3 Freeze Registers (52)6.13.4 HP/Speaker De-Emphasis (52)6.13.5 Digital Soft Ramp (53)6.13.6 Digital Zero Cross (53)6.14 Playback Control 2 (Address 0Fh) (53)6.14.1 Headphone Mute (53)6.14.2 Speaker Mute (53)6.14.3 Speaker Volume Setting B=A (54)6.14.4 Speaker Channel Swap (54)6.14.5 Speaker MONO Control (54)6.14.6 Speaker Mute 50/50 Control (54)6.15 MICx Amp Control:MIC A (Address 10h) & MIC B (Address 11h) (54)6.15.1 MIC x Select (54)6.15.2 MICx Configuration (55)6.15.3 MICx Gain (55)6.16 PGAx Vol. & ALCx Transition Ctl.:ALC, PGA A (Address 12h) & ALC, PGA B (Address 13h) (55)6.16.1 ALCx Soft Ramp Disable (55)6.16.2 ALCx Zero Cross Disable (55)6.16.3 PGAx Volume (56)6.17 Passthru x Volume: PASSAVOL (Address 14h) & PASSBVOL (Address 15h) (56)6.17.1 Passthru x Volume (56)6.18 ADCx Volume Control: ADCAVOL (Address 16h) & ADCBVOL (Address 17h) (57)6.18.1 ADCx Volume (57)6.19 ADCx Mixer Volume: ADCA (Address 18h) & ADCB (Address 19h) (58)6.19.1 ADC Mixer Channel x Mute (58)6.19.2 ADC Mixer Channel x Volume (58)6.20 PCMx Mixer Volume: PCMA (Address 1Ah) & PCMB (Address 1Bh) (58)6.20.1 PCM Mixer Channel x Mute (58)6.20.2 PCM Mixer Channel x Volume (58)6.21 Beep Frequency & On Time (Address 1Ch) (59)6.21.1 Beep Frequency (59)6.21.2 Beep On Time (60)6.22 Beep Volume & Off Time (Address 1Dh) (60)6.22.1 Beep Off Time (60)6.22.2 Beep Volume (61)6.23 Beep & Tone Configuration (Address 1Eh) (61)6.23.1 Beep Configuration (61)6.23.2 Beep Mix Disable (61)6.23.3 Treble Corner Frequency (62)6.23.4 Bass Corner Frequency (62)6.23.5 Tone Control Enable (62)6.24 Tone Control (Address 1Fh) (62)6.24.1 Treble Gain (62)CS42L526.24.2 Bass Gain (63)6.25 Master Volume Control: MSTA (Address 20h) & MSTB (Address 21h) (63)6.25.1 Master Volume Control (63)6.26 Headphone Volume Control: HPA (Address 22h) & HPB (Address 23h) (63)6.26.1 Headphone Volume Control (63)6.27 Speaker Volume Control: SPKA (Address 24h) & SPKB (Address 25h) (64)6.27.1 Speaker Volume Control (64)6.28 ADC & PCM Channel Mixer (Address 26h) (64)6.28.1 PCM Mix Channel Swap (64)6.28.2 ADC Mix Channel Swap (64)6.29 Limiter Control 1, Min/Max Thresholds (Address 27h) (65)6.29.1 Limiter Maximum Threshold (65)6.29.2 Limiter Cushion Threshold (65)6.29.3 Limiter Soft Ramp Disable (65)6.29.4 Limiter Zero Cross Disable (66)6.30 Limiter Control 2, Release Rate (Address 28h) (66)6.30.1 Peak Detect and Limiter (66)6.30.2 Peak Signal Limit All Channels (66)6.30.3 Limiter Release Rate (66)6.31 Limiter Attack Rate (Address 29h) (67)6.31.1 Limiter Attack Rate (67)6.32 ALC Enable & Attack Rate (Address 2Ah) (67)6.32.1 ALCx Enable (67)6.32.2 ALC Attack Rate (67)6.33 ALC Release Rate (Address 2Bh) (68)6.33.1 ALC Release Rate (68)6.34 ALC Threshold (Address 2Ch) (68)6.34.1 ALC Maximum Threshold (68)6.34.2 ALC Minimum Threshold (69)6.35 Noise Gate Control (Address 2Dh) (69)6.35.1 Noise Gate All Channels (69)6.35.2 Noise Gate Enable (69)6.35.3 Noise Gate Threshold and Boost (70)6.35.4 Noise Gate Delay Timing (70)6.36 Status (Address 2Eh) (Read Only) (70)6.36.1 Serial Port Clock Error (Read Only) (70)6.36.2 DSP Engine Overflow (Read Only) (71)6.36.3 PCMx Overflow (Read Only) (71)6.36.4 ADCx Overflow (Read Only) (71)6.37 Battery Compensation (Address 2Fh) (71)6.37.1 Battery Compensation (71)6.37.2 VP Monitor (71)6.37.3 VP Reference (72)6.38 VP Battery Level (Address 30h) (Read Only) (72)6.38.1 VP Voltage Level (Read Only) (72)6.39 Speaker Status (Address 31h) (Read Only) (72)6.39.1 Speaker Current Load Status (Read Only) (72)6.39.2 SPKR/HP Pin Status (Read Only) (73)6.39.3 Thermal Warning Status (Read Only) (73)6.39.4 Thermal Error Status (Read Only) (73)6.40 Temperature Monitor Control (Address 32h) (73)6.40.1 Temperature Acknowledge & Release (73)6.40.2 Thermal Foldback (Address 33h) (73)6.40.3 Thermal Foldback (73)CS42L526.40.4 Speaker Attenuation (74)6.41 Charge Pump Frequency (Address 34h) (74)6.41.1 Charge Pump Frequency (74)7. ANALOG PERFORMANCE PLOTS (75)7.1 Headphone THD+N versus Output Power Plots (75)8. EXAMPLE SYSTEM CLOCK FREQUENCIES (77)8.1 Auto Detect Enabled (77)8.2 Auto Detect Disabled (77)9. PCB LAYOUT CONSIDERATIONS (78)9.1 Power Supply, Grounding (78)9.2 QFN Thermal Pad (78)10. ADC & DAC DIGITAL FILTERS (79)11. PARAMETER DEFINITIONS (80)12. PACKAGE DIMENSIONS (81)THERMAL CHARACTERISTICS (81)13. ORDERING INFORMATION (82)14. REFERENCES (82)15. REVISION HISTORY (82)LIST OF FIGURESFigure 1. Typical Connection Diagram (10)Figure 2. Headphone Output Test Load (19)Figure 3. Serial Audio Interface Timing (21)Figure 4. Control Port Timing - I²C (22)Figure 5. Analog Input Signal Flow (26)Figure 6. Single-Ended MIC Configuration (27)Figure 7. Differential MIC Configuration (27)Figure 8. ALC (28)Figure 9. Noise Gate Attenuation (28)Figure 10. DSP Engine Signal Flow (29)Figure 11. PWM Output Stage (30)Figure 12. Analog Output Stage (30)Figure 13. Beep Configuration Options (31)Figure 14. Peak Detect & Limiter (32)Figure 15. Battery Compensation (34)Figure 16. I²S Format (36)Figure 17. Left-Justified Format (36)Figure 18. Right-Justified Format (DAC only) (36)Figure 19. DSP Mode Format) (36)Figure 20. Control Port Timing, I²C Write (38)Figure 21. Control Port Timing, I²C Read (38)Figure 22. THD+N vs. Output Power per Channel at 1.8V (16 Ω load) (75)Figure 23. THD+N vs. Output Power per Channel at 2.5V (16 Ω load) (75)Figure 24. THD+N vs. Output Power per Channel at 1.8V (32 Ω load) (76)Figure 25. THD+N vs. Output Power per Channel at 2.5V (32 Ω load) (76)Figure 26. ADC Passband Ripple (79)Figure 27. ADC Stopband Rejection (79)Figure 28. ADC Transition Band (79)Figure 29. ADC Transition Band Detail (79)Figure 30. DAC Passband Ripple (79)Figure 31. DAC Stopband (79)Figure 32. DAC Transition Band (79)Figure 33. DAC Transition Band (Detail) (79)CS42L52 1.PIN DESCRIPTIONSPin Name#Pin DescriptionSDA1Serial Control Data (Input/Output) - SDA is a data I/O in I²C Mode.SCL2Serial Control Port Clock (Input) - Serial clock for the serial control port.TSTN 3Test In - This pin is an input used for test purposes only. It must be tied to ground for normal oper-ation.SPKR_OUTA-SPKR_OUTB+ SPKR_OUTB-679PWM Speaker Output (Output) - Full-bridge amplified PWM speaker outputs.VP 58Power for PWM Drivers (Input)-Power supply for the PWM output driver stages.-VHPFILTpump that provides the negative rail for the headphone/line amplifiers.FLYN 11Charge Pump Cap Negative Node (Output)- Negative node for the inverting charge pump’s fly-ing capacitor.FLYPcapacitor.+VHP13Positive Analog Power for Headphone (Input)-Positive voltage rail and power for the internal headphone amplifiers and inverting charge pump.SDOUTMCLKSCLKSDINSDALRCKFLYN+VHPHP/LINE_OUTBHP/LINE_OUTAVQMICBIASAIN4A/MIC1+/MIC2AAIN2ATSTNSPKR_OUTA+VPVPVDSPKR_OUTB--VHPFILTAIN4B/MIC2+/MIC2BAIN1BAIN2BAFILTBAIN3B/MIC2-/MIC1BAFILTAAIN1AAIN3A/MIC1-/MIC1ASPKR_OUTB+SCLDGNDSPKR_OUTA-FLYPVAAGNDFILT+RESETVLSPKR/HPCS42L521.1I/O Pin CharacteristicsInput and output levels and associated power supply voltage are shown in the table below. Logic levels should not exceed the corresponding power supply voltage.FILT+cuits.VQ 19Quiescent Voltage (Output ) - Filter connection for the internal quiescent voltage.MICBIAS 20Microphone Bias (Output ) - Low noise bias supply for an external microphone. Electrical charac-teristics are specified in the DC Electrical Characteristics table.AIN3A,B 23,24Line-Level Analog Inputs (Input ) - Single-ended stereo line-level analog inputs. MIC1+,-MIC2+,-21,2322,24Differential Microphone Inputs (Input ) - Differential stereo microphone inputs. MIC1A,B 23,24Single-Ended Microphone Inputs (Input ) - Single-ended stereo microphone inputs.AIN2A,B AIN1A,B 25,2629,30Line-Level Analog Inputs (Input ) - Single-ended stereo line-level analog inputs.SPKR/HP and/or headphone outputs.RESET 32Reset (Input ) - The device enters a low power mode when this pin is driven low.VL face and host control port.VD 34Digital Power (Input ) - Positive power for the internal digital section. DGND 35Digital Ground (Input ) - Ground reference for the internal digital section.SDOUT 36Serial Audio Data Output (Output ) - Output for two’s complement serial audio data.MCLK 37Master Clock (Input ) - Clock source for the delta-sigma modulators.SCLK 38Serial Clock (Input/Output ) - Serial clock for the serial audio interface.SDIN 39Serial Audio Data Input (Input ) - Input for two’s complement serial audio data.LRCK40Left Right Clock (Input/Output ) - Determines which channel, Left or Right, is currently active on the serial audio data line.GND/Thermal Paddissipation.Power SupplyPin Name I/O DriverReceiverVLRESET Input - 1.65 V - 3.47 V, with Hysteresis SCL Input - 1.65 V - 3.47 V, with Hysteresis SDA Input/Output 1.65 V - 3.47 V, CMOS/Open Drain1.65 V - 3.47 V, with HysteresisMCLK Input - 1.65 V - 3.47 V LRCK Input/Output 1.65 V - 3.47 V, CMOS 1.65 V - 3.47 V SCLK Input/Output 1.65 V - 3.47 V, CMOS 1.65 V - 3.47 VSDOUT Output 1.65 V - 3.47 V V, CMOSSDIN Input - 1.65 V - 3.47 V VA SPKR/HP Input - 1.65 V - 2.63 VVPSPKR_OUTA+Output 1.6V - 5.25V Power MOSFET -SPKR_OUTA-Output1.6V - 5.25V Power MOSFET -SPKR_OUTB+Output 1.6V - 5.25V Power MOSFET -SPKR_OUTB-Output1.6V - 5.25V Power MOSFET-CS42L52 2.TYPICAL CONNECTION DIAGRAMFigure 1. Typical Connection DiagramCS42L523.CHARACTERISTIC AND SPECIFICATIONS RECOMMENDED OPERATING CONDITIONS(AGND=DGND=0 V, all voltages with respect to ground.)ABSOLUTE MAXIMUM RATINGS(AGND = DGND = 0 V; all voltages with respect to ground.)WARNING:Operation at or beyond these limits may result in permanent damage to the device. Normal operationis not guaranteed at these extremes.Notes:1.Any pin except supplies. Transient currents of up to ±100 mA on the analog input pins will not causeSCR latch-up.2.The maximum over/under voltage is limited by the input current.ParametersSymbol Min MaxUnitsDC Power Supply AnalogVA 1.65 2.63V Headphone Amplifier +VHP 1.65 2.63V Speaker Amplifier VP 1.60 5.25V DigitalVD 1.65 2.63V Serial/Control Port Interface VL1.65 3.47V Ambient TemperatureCommercial - CNZ Automotive - DNZT A-40-40+85+105°C °CParametersSymbolMinMaxUnitsDC Power SupplyAnalog Speaker DigitalSerial/Control Port InterfaceVA, VHP VP VD VL -0.3-0.3-0.3-0.3 3.05.53.04.0V V V V Input Current(Note 1)I in-±10mAAnalog Input Voltage(Note 2)V INAGND-0.7VA+0.7VDigital Input Voltage(Note 2)V IND -0.3VL+ 0.4V Ambient Operating Temperature (power applied)T A -50+115°C Storage TemperatureT stg-65+150°CCS42L52ANALOG INPUT CHARACTERISTICS (COMMERCIAL - CNZ)(Test Conditions (unless otherwise specified): Input sine wave (relative to digital full-scale): 1kHz through passive input filter; VL = VD = VHP = 1.8 V; T A = +25°C; Measurement Bandwidth is 10Hz to 20kHz unless otherwise specified. Sample Fre-quency = 48kHz)3.Measured with DAC delivering full-scale output into specified load.4.Measured between analog input and AGND.VA = 2.5V VA = 1.8V Parameters MinTypMaxMinTypMaxUnitAnalog In to ADC (PGA bypassed)Dynamic RangeA-weighted unweighted 93909996--90879693--dB dB Total Harmonic Distortion + Noise-1dBFS -20dBFS -60dBFS ----86-76-36-80--30----84-73-33-78--27dB dB dB Analog In to PGA to ADC Dynamic Range PGA Setting: 0 dB A-weighted unweighted 92899895--89869592--dB dB PGA Setting: +12 dBA-weighted unweighted85829188--82798885--dB dB Total Harmonic Distortion + Noise PGA Setting: 0 dB -1dBFS -60dBFS ---88-35-82-29---86-32-80-26dB dB PGA Setting: +12 dB -1dBFS --85-79--83-77dB Analog In to MIC Pre-Amp (+16 dB) to PGA to ADC Dynamic Range PGA Setting: 0 dB A-weighted unweighted --8683----8380--dB dB Total Harmonic Distortion + Noise PGA Setting: 0 dB -1dBFS --76---74-dB Analog In to MIC Pre-Amp (+32 dB) to PGA to ADC Dynamic Range PGA Setting: 0 dB A-weighted unweighted --7874----7571--dB dB Total Harmonic Distortion + Noise PGA Setting: 0 dB -2dBFS --74---71-dB Other Characteristics DC AccuracyInterchannel Gain Mismatch -0.2--0.2-dB Gain Drift -±100--±100-ppm/°C Offset Error SDOUT Code with HPF On -352--352-LSB InputInterchannel Isolation -90--90-dB HP Amp to Analog Input Isolation R L = 10 k Ω(Note 3)R L = 16 Ω--10070----10070--dB dB Speaker Amp to Analog Input Isolation -60--60-dB Full-scale Input Voltage ADC PGA (0 dB)PGA (+12 dB)MIC (+16 dB)MIC (+32 dB)0.73•VA0.73•VA 0.769•VA 0.770•VA 0.194•VA 0.115•VA 0.019•VA0.83•VA0.83•VA 0.73•VA 0.73•VA0.769•VA 0.770•VA 0.194•VA 0.115•VA 0.019•VA 0.83•VA 0.83•VAVpp Vpp Vpp Vpp Input Impedance (Note 4)ADC PGA MIC ---203950------203950---k Ωk Ωk ΩCS42L52 ANALOG INPUT CHARACTERISTICS (AUTOMOTIVE - DNZ)(Test Conditions (unless otherwise specified): Input sine wave (relative to full-scale): 1 kHz through passive input filter;VL = VD = VHP = 1.8 V; T A = -40 to +85°C; Measurement Bandwidth is 10Hz to 20kHz unless otherwise specified. Sample Frequency = 48kHz)VA = 2.37 - 2.63 V VA = 1.65 - 1.89 VParameters Min Typ Max Min Typ Max Unit Analog In to ADCDynamic Range A-weightedunweighted 91889996--88859693--dBdBTotal Harmonic Distortion + Noise -1dBFS -20dBFS-60dBFS ----86-76-36-78--28----84-73-33-76--25dBdBdBAnalog In to PGA to ADC Dynamic RangePGA Setting: 0 dB A-weightedunweighted 90879895--87849592--dBdBPGA Setting: +12 dB A-weightedunweighted 83809188--80778885--dBdBTotal Harmonic Distortion + NoisePGA Setting: 0 dB -1dBFS -60dBFS ---88-35-80-27---86-32-78-24dBdBPGA Setting: +12 dB -1dBFS--85-77--83-75dB Analog In to MIC Pre-Amp (+16 dB) to PGA to ADCDynamic RangePGA Setting: 0 dB A-weightedunweighted --8683----8380--dBdBTotal Harmonic Distortion + NoisePGA Setting: 0 dB -1dBFS--76---74-dB Analog In to MIC Pre-Amp (+32 dB) to PGA to ADCDynamic RangePGA Setting: 0 dB A-weightedunweighted --7874----7571--dBdBTotal Harmonic Distortion + NoisePGA Setting: 0 dB -2dBFS--74---71-dB Other CharacteristicsDC AccuracyInterchannel Gain Mismatch-0.1--0.1-dB Gain Drift-±100--±100-ppm/°C Offset Error SDOUT Code with HPF On-352--352-LSB InputInterchannel Isolation-90--90-dBHP Amp to Analog Input Isolation R L = 10 kΩ(Note 3)R L = 16 Ω--10070----10070--dBdBSpeaker Amp to Analog Input Isolation-60--60-dBFull-scale Input Voltage ADCPGA (0 dB)PGA (+12 dB)MIC (+16 dB)MIC (+32 dB)0.73•VA0.73•VA0.769•VA0.770•VA0.194•VA0.115•VA0.019•VA0.83•VA0.83•VA0.73•VA0.73•VA0.769•VA0.770•VA0.194•VA0.115•VA0.019•VA0.83•VA0.83•VAVppVppVppVppInput Impedance (Note 4)ADCPGAMIC 184050------184050------kΩkΩkΩCS42L52ADC DIGITAL FILTER CHARACTERISTICS5.Response is clock-dependent and will scale with Fs. Note that the response plots (Figures 26to 29 onpage 79) have been normalized to Fs and can be de-normalized by multiplying the X-axis scale by Fs.HPF parameters are for Fs = 48 kHz.Parameters (Note 5)MinTypMaxUnitPassband (Frequency Response) to -0.1 dB corner0-0.4948Fs Passband Ripple -0.09-0.17dB Stopband0.6--Fs Stopband Attenuation 33--dB Total Group Delay-7.6/Fs -s High-Pass Filter Characteristics (48 kHz Fs)Frequency Response -3.0 dB -0.13 dB-- 3.624.2--Hz Hz Phase Deviation @ 20Hz-10-Deg Passband Ripple --0.17dB Filter Settling Time-105/Fss。