[2009] Rapid Burst-mode Signal Detecting Method Based on FPGA

ULPI_v1_1

UTMI+ Low Pin Interface (ULPI)SpecificationRevision 1.1October 20, 2004Revision HistoryDate CommentRevision Issue0.9 November 12, 2003 Pre-release.1.0rc1 January 3, 2004 Introduce PHY interface “modes”.Update interface timings. Clarify 4-bit data clocking.Clarify sending of RX CMD’s and interrupts.Introduce AutoResume feature.Route int pin to data(3) during 6-pin Serial Mode.Explain VBUS thresholds.Add T&MT diagram and updated text.Add new section to explain how PHY is aborted by Link.Various clarifications.1.0rc2 January 13, 2004 Add block diagram.Tighten interface timing.Modify suspend protocol to more closely resemble UTMI.Add SPKR_L and SPKR_MIC to signal list and T&MTconnector.Various clarifications.1.0rc3 January 19, 2004 Specify that PHY must send RX CMD after Reset.Link + PHY clock startup time of no more than 5.6ms for aperipheral is now mandatory.PHY output delay reduced from 10ns to 9ns.Added link decision time numbers for low speed.Various Clarifications.1.0 February 2, 2004 1.0rc3 adopted as 1.0 release.1.1rc1 September 1, 2004 Various clarifications and fixes to hold time numbers, sendingRXCMDs, FsLsSerialMode, Vbus control and monitoring,Test_J and Tesk_K signalling, Low Power Mode,Hostdisconnect, ID detection, HS SOF packets, interrupts,Carkit Mode, interface protection, No SYNC/EOP mode,linestate filtering, and AutoResume.1.1rc2 October 4, 2004 Re-arranged text in section 3.8.7.3. Updated contributors list.1.1 October 20, 2004 1.1rc2 adopted as 1.1 release.The present Specification has been circulated for the sole benefit of legally-recognized Promoters, Adopters and Contributors of the Specification. All rights are expressly reserved, including but not limited to intellectual property rights under patents, trademarks, copyrights and trade secrets. The respective Promoter's, Adopter's or Contributor's agreement entered into by Promoters, Adopters and Contributors sets forth their conditions of use of the Specification.iiPromotersARC International Inc.Conexant Systems, Inc.Mentor Graphics CorporationPhilipsSMSCTransDimension, Inc.ContributorsVertenten PhilipsBartOkur PhilipsBatuhanBillAnderson MotorolaMcInerney TransDimensionBillBooker CypressBrianARCBelangerChrisKolb ARCChrisChrisSchell PhilipsChung Wing Yan PhilipsSrokaPhilipsDaveWang PhilipsDavidWooten TransDimensionDavidSMSCEricKawamotoPhilipsMackayFarranFrazier ConexantFrankFredRoberts SynopsysFarooqConexantHassanLee TransDimensionHyunParr MentorIanStandiford TransDimensionJayPhilipsTjiaJeromeMentorSaundersMarkMohamed Benromdhane ConexantSMSCMorganMonksISINabilTaklaTengstrand ARCPeterRamanand Mandayam ConexantDouglas MentorRobSaleemMohamed Synopsys(Author)ShaunReemeyer PhilipsCypressSimonNguyenSubramanyam Sankaran PhilipsTexasInstrumentsViningSueRemple QualcommTerryChen ConexantTimothyConexantChangVincentQuestions should be emailed to lpcwg@.iiiTable of Contents1.Introduction (1)1.1General (1)1.2Naming Convention (1)1.3Acronyms and Terms (1)1.4References (1)2.Generic Low Pin Interface (2)2.1General (2)2.2Signals (2)2.3Protocol (3)2.3.1Bus Ownership (3)2.3.2Transferring Data (3)2.3.3Aborting Data (4)3.UTMI+ Low Pin Interface (5)3.1General (5)3.2Signals (6)3.3Block Diagram (7)3.4Modes (9)3.5Power On and Reset (10)3.6Interrupt Event Notification (10)3.7Timing (11)3.7.1Clock (11)3.7.2Control and Data (13)3.8Synchronous Mode (15)3.8.1ULPI Command Bytes (15)3.8.2USB Packets (18)3.8.3Register Operations (30)3.8.4Aborting ULPI Transfers (37)3.8.5USB Operations (39)3.8.6Vbus Power Control (internal and external) (52)3.8.7OTG Operations (52)3.9Low Power Mode (55)3.9.1Data Line Definition For Low Power Mode (55)3.9.2Entering Low Power Mode (55)3.9.3Exiting Low Power Mode (56)3.9.4False Resume Rejection (57)3.10Full Speed / Low Speed Serial Mode (Optional) (58)3.10.1Data Line Definition For FsLsSerialMode (58)3.10.2Entering FsLsSerialMode (59)3.10.3Exiting FsLsSerialMode (60)3.11Carkit Mode (Optional) (61)3.12Safeguarding PHY Input Signals (62)4.Registers (65)4.1Register Map (65)4.2Immediate Register Set (67)4.2.1Vendor ID and Product ID (67)4.2.2Function Control (68)4.2.3Interface Control (69)4.2.4OTG Control (71)4.2.5USB Interrupt Enable Rising (72)4.2.6USB Interrupt Enable Falling (73)4.2.7USB Interrupt Status (74)4.2.8USB Interrupt Latch (75)4.2.9Debug (76)4.2.10Scratch Register (76)4.2.11Carkit Control (77)4.2.12Carkit Interrupt Delay (77)iv4.2.13Carkit Interrupt Enable (78)4.2.14Carkit Interrupt Status (78)4.2.15Carkit Interrupt Latch (79)4.2.16Carkit Pulse Control (79)4.2.17Transmit Positive Width (80)4.2.18Transmit Negative Width (80)4.2.19Receive Polarity Recovery (80)4.2.20Reserved (81)4.2.21Access Extended Register Set (81)4.2.22Vendor-specific (81)4.3Extended Register Set (81)4.4Register Settings for all Upstream and Downstream signalling modes (81)5.T&MT Connector (83)5.1General (83)5.2Daughter-card (UUT) Specification (83)vFiguresFigure 1 – LPI generic data bus ownership (3)Figure 2 – LPI generic data transmit followed by data receive (3)Figure 3 – Link asserts stp to halt receive data (4)Figure 4 – Creating a ULPI system using wrappers (5)Figure 5 – Block diagram of ULPI PHY (7)Figure 6 – Jitter measurement planes (12)Figure 7 – ULPI timing diagram (13)Figure 8 – Clocking of 4-bit data interface compared to 8-bit interface (14)Figure 9 – Sending of RX CMD (17)Figure 10 – USB data transmit (NOPID) (18)Figure 11 – USB data transmit (PID) (19)Figure 12 – PHY drives an RX CMD to indicate EOP (FS/LS LineState timing not to scale) (20)Figure 13 – Forcing a full/low speed USB transmit error (timing not to scale) (21)Figure 14 – USB receive while dir was previously low (22)Figure 15 – USB receive while dir was previously high (23)Figure 16 – USB receive error detected mid-packet (24)Figure 17 – USB receive error during the last byte (25)Figure 18 – USB HS, FS, and LS bit lengths with respect to clock (26)Figure 19 – HS transmit-to-transmit packet timing (29)Figure 20 – HS receive-to-transmit packet timing (29)Figure 21 – Register write (30)Figure 22 – Register read (31)Figure 23 – Register read or write aborted by USB receive during TX CMD byte (31)Figure 24 – Register read turnaround cycle or Register write data cycle aborted by USB receive (32)Figure 25 – USB receive in same cycle as register read data. USB receive is delayed (33)Figure 26 – Register read followed immediately by a USB receive (33)Figure 27 – Register write followed immediately by a USB receive during stp assertion (34)Figure 28 – Register read followed by a USB receive (34)Figure 29 – Extended register write (35)Figure 30 – Extended register read (35)Figure 31 – Extended register read aborted by USB receive during extended address cycle (36)Figure 32 – PHY aborted by Link asserting stp. Link performs register write or USB transmit (37)Figure 33 – PHY aborted by Link asserting stp. Link performs register read (38)Figure 34 – Link aborts PHY. Link fails to drive a TX CMD. PHY re-asserts dir (38)Figure 35 – Hi-Speed Detection Handshake (Chirp) sequence (timing not to scale) (40)Figure 36 – Preamble sequence (D+/D- timing not to scale) (41)Figure 37 – LS Suspend and Resume (timing not to scale) (43)Figure 38 – FS Suspend and Resume (timing not to scale) (44)Figure 39 – HS Suspend and Resume (timing not to scale) (46)Figure 40 – Low Speed Remote Wake-Up from Low Power Mode (timing not to scale) (47)Figure 41 – Full Speed Remote Wake-Up from Low Power Mode (timing not to scale) (48)Figure 42 – Hi-Speed Remote Wake-Up from Low Power Mode (timing not to scale) (49)Figure 43 – Automatic resume signalling (timing not to scale) (50)Figure 44 – USB packet transmit when OpMode is set to 11b (51)Figure 45 – RX CMD V A_VBUS_VLD ≤Vbus indication source (54)Figure 46 – Entering low power mode (55)Figure 47 – Exiting low power mode when PHY provides output clock (56)Figure 48 – Exiting low power mode when Link provides input clock (56)Figure 49 – PHY stays in Low Power Mode when stp de-asserts before clock starts (57)Figure 50 – PHY re-enters Low Power Mode when stp de-asserts before dir de-asserts (57)Figure 51 – Interface behaviour when entering Serial Mode and clock is powered down (59)Figure 52 – Interface behaviour when entering Serial Mode and clock remains powered (59)Figure 53 – Interface behaviour when exiting Serial Mode and clock is not running (60)Figure 54 – Interface behaviour when exiting Serial Mode and clock is running (60)Figure 55 – PHY interface protected when the clock is running (62)Figure 56 – Power up sequence when PHY powers up before the link. Interface is protected (63)Figure 57 – PHY automatically exits Low Power Mode with interface protected (63)Figure 58 – Link resumes driving ULPI bus and asserts stp because clock is not running (64)viFigure 59 – Power up sequence when link powers up before PHY (ULPI 1.0 compliant links) (64)Figure 60 – Recommended daughter-card configuration (not to scale) (83)viiTablesTable 1 – LPI generic interface signals (2)Table 2 – PHY interface signals (6)Table 3 – Mode summary (9)Table 4 – Clock timing parameters (11)Table 5 – ULPI interface timing (13)Table 6 – Transmit Command (TX CMD) byte format (15)Table 7 – Receive Command (RX CMD) byte format (16)Table 8 – USB specification inter-packet timings (26)Table 9 – PHY pipeline delays (27)Table 10 – Link decision times (28)Table 11 – OTG Control Register power control bits (52)Table 12 – Vbus comparator thresholds (52)Table 13 – RX CMD VbusValid over-current conditions (53)Table 14 – Vbus indicators in the RX CMD required for typical applications (54)Table 15 – Interface signal mapping during Low Power Mode (55)Table 16 – Serial Mode signal mapping for 6-pin FsLsSerialMode (58)Table 17 – Serial Mode signal mapping for 3-pin FsLsSerialMode (58)Table 18 – Carkit signal mapping (61)Table 19 – Register map (66)Table 20 – Register access legend (67)Table 21 – Vendor ID and Product ID register description (67)Table 22 – Function Control register (68)Table 23 – Interface Control register (70)Table 24 – OTG Control register (71)Table 25 – USB Interrupt Enable Rising register (72)Table 26 – USB Interrupt Enable Falling register (73)Table 27 – USB Interrupt Status register (74)Table 28 – USB Interrupt Latch register (75)Table 29 – Rules for setting Interrupt Latch register bits (75)Table 30 – Debug register (76)Table 31 – Scratch register (76)Table 32 – Carkit Control Register (77)Table 33 – Carkit Interrupt Delay register (77)Table 34 – Carkit Interrupt Enable register (78)Table 35 – Carkit Interrupt Status Register (78)Table 36 – Carkit Interrupt Latch register (79)Table 37 – Carkit Pulse Control (79)Table 38 – Transmit Positive Width (80)Table 39 – Transmit Negative Width (80)Table 40 – Receive Polarity Recovery (81)Table 41 – Upstream and downstream signalling modes (82)Table 42 – T&MT connector pin view (84)Table 43 – T&MT connector pin allocation (84)Table 44 – T&MT pin description (85)viii1. Introduction1.1 GeneralThis specification defines a generic PHY interface in Chapter 2.In Chapter 3, the generic interface is applied to the UTMI+ protocol, reducing the pin count for discrete USB transceiver implementations supporting On-The-Go, host, and peripheral application spaces.Convention1.2 NamingEmphasis is placed on normal descriptive text using underlined Arial font, e.g. must.Signal names are represented using the lowercase bold Arial font, e.g. clk.Registers are represented using initial caps, bold Arial font, e.g. OTG Control.Register bits are represented using initial caps, bold italic Arial font, e.g. USB Interrupt Enable Falling. 1.3 Acronyms and TermsA-device Device with a Standard-A or Mini-A plug inserted into its receptacleB-device Device with a Standard-B or Mini-B plug inserted into its receptacleDeviceDRD Dual-RoleFPGA Field Programmable Gate ArraySpeedFS FullHNP Host Negotiation ProtocolHS Hi-SpeedLink ASIC, SIE, or FPGA that connects to an ULPI transceiverLPI Low Pin InterfaceSpeedLS LowOTG On-The-GoPHY Physical Layer (Transceiver)PLL Phase Locked LoopSE0 Single Ended ZeroSIE Serial Interface EngineSRP Session Request ProtocolT&MT Transceiver and Macrocell TesterULPI UTMI+ Low Pin InterfaceUSB Universal Serial BusUSB-IF USB Implementers ForumUTMI USB 2.0 Transceiver Macrocell InteraceUUT Unit Under Test1.4 References[Ref 1] Universal Serial Bus Specification, Revision 2.0[Ref 2] On-The-Go Supplement to the USB 2.0 Specification, Revision 1.0a[Ref 3] USB 2.0 Transceiver Macrocell Interface (UTMI) Specification, v1.05[Ref 4] UTMI+ Specification, Revision 1.0[Ref 5] CEA-2011, OTG Transceiver Specification[Ref 6] CEA-936A, Mini-USB Analog Carkit Interface Specification[Ref 7] USB 2.0 Transceiver and Macrocell Tester (T&MT) Interface Specification, Version 1.212. Generic Low Pin Interface2.1 GeneralThis section describes a generic low pin interface (LPI) between a Link and a PHY. Interface signals are defined and the basic communication protocol is described. The generic interface can be used as a common starting point for defining multiple application-specific interfaces.Chapter 3 defines the UTMI+ Low Pin Interface (ULPI), which is based on the generic interface described here. For ULPI implementations, the definitions in chapter 3 over-ride anything defined in chapter 2.2.2 SignalsThe LPI transceiver interface signals are described in Table 1. The interface described here is generic, and can be used to transport many different data types. Depending on the application, the data stream can be used to transmit and receive packets, access a register set, generate interrupts, and even redefine the interface itself. All interface signals are synchronous when clock is toggling, and asynchronous when clock is not toggling. Data stream definition is application-specific and should be explicitly defined for each application space for inter-operability.Control signals dir, stp, and nxt are specified with the assumption that the PHY is the master of the data bus. If required, an implementation can define the Link as the master. If the Link is the master of the interface, the control signal direction and protocol must be reversed.Signal Direction DescriptionPHY Interfaceclock I/O Interface clock. Both directions are allowed. All interface signals are synchronous to clock.data I/O Bi-directional data bus, driven low by the Link during idle. Bus ownership is determined by dir. The Link and PHY initiate data transfers by driving a non-zero pattern onto the data bus. LPI defines interface timing for single-edge data transfers with respect to rising edge of clock. An implementation may optionally define double-edge data transfers with respect to both rising and falling edges of clock.dir OUT Direction. Controls the direction of the data bus. When the PHY has data to transfer to the Link, it drives dir high to take ownership of the bus. When the PHY has no data to transfer it drives dir low and monitors the bus for Link activity. The PHY pulls dir high whenever the interface cannot accept data from the Link. For example, when the internal PHY PLL is not stable.stp IN Stop. The Link asserts this signal for 1 clock cycle to stop the data stream currently on the bus. If the Link is sending data to the PHY, stp indicates the last byte of data was on the bus in the previous cycle. If the PHY is sending data to the Link, stp forces the PHY to end its transfer, de-assert dir and relinquish control of the the data bus to the Link.nxt OUT Next. The PHY asserts this signal to throttle the data. When the Link is sending data to the PHY, nxt indicates when the current byte has been accepted by the PHY. The Link places the next byte on the data bus in the following clock cycle. When the PHY is sending data to the Link, nxt indicates when a new byte is available for the Link to consume.Table 1 – LPI generic interface signals22.3 ProtocolOwnership2.3.1 BusThe PHY is the master of the LPI bi-directional data bus. Ownership of the data bus is determined by the dir signal from the PHY, as shown in Figure 1. When dir is low, the Link can drive data on the bus. When dir is high, the PHY can drive data on the bus. A change in dir causes a turnaround cycle on the bus during which, neither Link nor PHY can drive the bus. Data during the turnaround cycle is undefined and must be ignored by both Link and PHY.The dir signal can be used to directly control the data output buffers of both PHY and Link.Figure 1 – LPI generic data bus ownershipData2.3.2 TransferringAs shown in the first half of Figure 2, the Link continuously drives the data bus to 00h during idle. The Link transmits data to the PHY by driving a non-zero value on the data bus. To signal the end of data transmission, the Link asserts stp in the cycle following the last data byte.In the second half of Figure 2, the Link receives data when the PHY asserts dir. The PHY asserts dir only when it has data to send to the Link, and keeps dir low at all other times. The PHY drives data to the Link after the turnaround cycle.The nxt signal can be used by the PHY to throttle the data during transmit and receive. During transmit, nxt may be asserted in the same cycle that the Link asserts stp.Figure 2 – LPI generic data transmit followed by data receive2.3.3 AbortingDataThe PHY can assert dir to interrupt any data being transmitted by the Link. If the Link needs to interrupt data being received from the PHY, it asserts stp for one clock cycle, as shown in Figure 3. This causes the PHY to unconditionally1 de-assert dir and accept a complete data transmit from the Link. The PHY may re-assert dir again only when the data transmit from the Link has completed.Figure 3 – Link asserts stp to halt receive data1 The PHY will not de-assert dir if the ULPI interface is not usable. For example, if the internal PLL is not stable.3. UTMI+ Low Pin Interface3.1 GeneralThis section describes how any UTMI+ core can be wrapped to convert it to the smaller LPI interface. The generic interface described in chapter 2 is used as a starting point. This section always over-rides anything stated in chapter 2. While this specification details support of UTMI+ Level 3, PHY implementers may choose to support any of the Levels defined in UTMI+.ULPI defines a PHY to Link interface of 8 or 12 signals that allows a lower pin count option for connecting to an external transceiver that may be based on the UTMI+ specification. The pin count reduction is achieved by having relatively static UTMI+ signals be accessed through registers and by providing a bi-directional data bus that carries USB data and provides a means of accessing register data on the ULPI transceiver.This specification relies on concepts and terminology that are defined in the UTMI+ specification [Ref 4]. Specifically, if a ULPI PHY design is based on an internal UTMI+ core, then that core must implement the following UTMI+ features.Linestate must accurately reflect D+/D- to within 2-3 clocks. It is up to individual Link designers to use Linestate to time bus events.Filtering to prevent spurious SE0/SE1 states appearing on Linestate due to skew between D+ and D-. Filtering of 14 clock cycles is required in Low Speed, and 2 clock cycles in Full Speed and Hi-Speed modes.The PHY must internally block the USB receive path during transmit. The receive path can be unblocked when the internal Squelch (HS) or SE0-to-J (FS/LS) is seen.TxReady must be used for all types of data transmitted, including Chirp.Due to noise on the USB, it is possible that RxActive asserts and then de-asserts without any valid data being received, and RxValid will not assert. The Link should operate normally with these data-less RxActive assertions.As shown in Figure 4, a PHY or Link based on this specification can be implemented as an almost transparent wrapper around existing UTMI+ IP cores, preserving the original UTMI+ packet timing, while reducing pin count and leaving all functionality intact. This should not be taken to imply that other implementations are not possible.Figure 4 – Creating a ULPI system using wrappers3.2 SignalsTable 2 describes the ULPI interface on the PHY. The PHY is always the master of the ULPI bus. USB and Miscellaneous signals may vary with each implementation and are given only as a guide to PHY designers.Signal Direction DescriptionPHY Interfaceclock I/O Interface clock. The PHY must be capable of providing a 60MHz output clock. Support for an input 60MHz clock is optional. If the PHY supports both clock directions, it must not use the ULPI control and data signals for setting the clock direction.Data bus. Driven to 00h by the Link when the ULPI bus is idle. Two bus widths are allowed:• 8-bit data timed on rising edge of clock.data I/O• (Optional) 4-bit data timed on rising and falling edges of clock.dir OUT Controls the direction of the data bus2. The PHY pulls dir high whenever the interface cannot accept data from the Link. For example, when the internal PLL is not stable. This applies whether Link or PHY is the clock source.stp IN The Link must assert stp to signal the end of a USB transmit packet or a register write operation, and optionally to stop any receive. The stp signal must be asserted in the cycle after the last data byte is presented on the bus.nxt OUT The PHY asserts nxt to throttle all data types, except register read data and the RX CMD. Identical to RxValid during USB receive, and TxReady during USB transmit. The PHY also asserts nxt and dir simultaneously to indicate USB receive activity (RxActive), if dir was previously low. The PHY is not allowed to assert nxt during the first cycle of the TX CMD driven by the Link.USB InterfaceD+ I/O D+ pin of the USB cable. Required.D- I/O D- pin of the USB cable. Required.ID IN ID pin of the USB cable. Required for OTG-capable PHY’s.VBUS I/O V BUS pin of the USB cable. Required for OTG-capable PHY’s. Required for driving V BUS and the V BUS comparators.MiscellaneousXI IN Crystal input pin. Vendors should specify supported crystal frequencies. XO OUT Crystal output pin.C+ I/O Positive terminal of charge pump capacitor.C- I/O Negative terminal of charge pump capacitor.SPKR_L IN Optional Carkit left/mono speaker input signal.SPKR_MIC I/O Optional Carkit right speaker input or microphone output signal.RBIAS I/O Bias current resistor.Table 2 – PHY interface signals2 UTMI+ wrapper developers should note that data bus control has been reversed from UTMI to ensure that USB data reception is not interrupted by the Link.3.3 BlockDiagramAn example block diagram of a ULPI PHY is shown in Figure 5. This example is based on an internal UTMI+ Level 3 core [Ref 4], which can interface to peripheral, host, and On-The-Go Link cores. A description of each major block is given below.ULPI InterfaceUSBCableChargePumpCapacitor Figure 5 – Block diagram of ULPI PHYUTMI+ Level 3 PHY coreThe ULPI PHY may contain a core that is compliant to any UTMI+ level [Ref 4]. Signals for 16-bit data buses are not supported in ULPI. While Figure 5 shows the typical blocks for a Level 3 UTMI+ core, the PHY vendor must specify the intended UTMI+ level, and provide the functionality necessary for compliance to that level.ULPI PHY WrapperThe ULPI PHY wrapper of Figure 5 reduces the UTMI+ interface to the Low Pin Interface described in this document. All signals shown on the UTMI+ Level 3 PHY core are reduced to the ULPI interface signals clock, data, dir, stp, and nxt. The Register Map stores the relatively static signals of the UTMI+ interface. Crystal Oscillator and PLLWhen a crystal is attached to the PHY, the internal clock(s) and the external 60MHz interface clock are generated from the internal PLL. When no crystal is attached, the PHY may optionally generate the internal clock(s) from an input 60MHz clock provided by the Link.General BiasingInternal analog circuits require an accurate bias current. This is typically generated using an external, accurate reference resistor.DrvVbusExternal and ExternalVbusIndicatorThe PHY may optionally control an external VBUS power source via the optional pin DrvVbusExternal. For example, the external supply could be a charge pump or 5V power supply controlled using a power switch. The external supply is controlled by the DrvVbus and the optional DrvVbusExternal bits in the OTG Control register. The polarity of the DrvVbusExternal output pin is implementation dependent.If control of an external VBUS source is provided the PHY may optionally provide for a VBUS power source feed back signal on the optional pin ExternalVbusIndicator. If this pin is provided, the use of the pin is defined by the optional control bits in the OTG Control and Interface Control registers. See Section 3.8.6.3 for further detail.Power-On-ResetA power-on-reset circuit must be provided in the PHY. When power is first applied to the PHY, the power-on-reset will reset all circuitry and leave the ULPI interface in a usable state.Carkit OptionThe PHY may optionally support Carkit Mode [Ref 6]. While in Carkit Mode, the PHY routes speaker and microphone signals between the Link and the USB cable. In carkit mono mode, SPKR_L inputs a mono speaker signal and SPKR_MIC outputs the microphone signal, MIC. In carkit stereo mode, SPKR_L inputs the left speaker signal, and SPKR_MIC inputs the right speaker signal, SPKR_R.3.4 ModesThe ULPI interface can operate in one of five independent modes listed in Table 3. The interface is in Synchronous Mode by default. Other modes are enabled by bits in the Function Control and Interface Control registers. In Synchronous Mode, the data bus carries commands and data. In other modes, the data pins are redefined with different functionality. Synchronous Mode and Low Power Mode are mandatory.Mode Name Mode DescriptionSynchronous Mode This is the normal mode of operation. The clock is running and is stablewith the characteristics defined in section 3.6. The ULPI interface carriescommands and data that are synchronous to clock.Low Power Mode The PHY is powered down with the clock stopped. The PHY keeps dirasserted, and the data bus is redefined to carry LineState and interrupts.See section 3.9 for more information.6-pin FS/LS Serial Mode (optional) The data bus is redefined to 6-pin serial mode, including 6 pins to transmit and receive serial USB data, and 1 pin to signal interrupt events. The clock can be enabled or disabled. This mode is valid only for implementations with an 8-bit data bus. See section 3.10 for more information.3-pin FS/LS Serial Mode (optional) The data bus is redefined to 3-pin serial mode, including 3 pins to transmit and receive serial USB data, and 1 pin to signal interrupt events. The clock can be enabled or disabled. See section 3.10 for more information.Carkit Mode (optional) The data bus is redefined to Carkit mode [Ref 6], including 2 pins for serial UART data, and 1 pin to signal interrupt events. The clock may optionally be stopped. See section 3.11 for more information.Table 3 – Mode summary。

UT165(联盛)易懂教程+各类问题综合

用了一天时间学习量产和做启动。

到现在已经量产和测试了不少于50次!不过!还是菜鸟一个!所以,发个菜鸟级的教程,和各位菜鸟共同学习。

包教会!学会的请赏点M币,没学会的给我留言,教会为止!口水到此为止……友情提示:各位,既然是用来做启动的,就不要对速度要求太严厉了。

我买来的时候测还很快的。

量产后就掉一半了,呵呵。

还有就是,在不同的机器上,测试,同样是真正的USB2.0高速接口,测出来的速度是可以相差很多的!和主板芯片关系很大啊!我几台电脑测试,读取速度最大可以相差十多MB/S,写入相差一半!新的主板读写都可以有很大的提高。

另外U盘的格式化也是个很重要的问题。

先进入计算机管理,然后进入磁盘管理,选择U盘,然后右键格式化,有一个分配单位大小的选项,如果选择16K的话,中等文件读写在同一电脑上会快很多,如果选择其它参数,速度也会有所改变。

我试过在同一机器上,一开始是量产后,直接测试,后来是选择16K格式化后测试,速度相差很多。

教学开始:要确定你的U盘主控是UT165喔。

不知道自己U盘主控的请下载软件检测:/chipgenius.htm在使用相关的量产软件前,如果推荐使用影子系统保护电脑,以免使用量产软件后,电脑多些垃圾文件。

我就是这样用的。

头炮:易学易懂的图形量产软件UFDUtility!UFDUtility现在最新的版本是:v3.2.4.0。

有汉化版,大家不用担心~~ (本帖所有工具在最下面提供下载)知道这软件的朋友,很多都以为它是一个绿色软件,其实只能算半个。

你一旦使用它,它就会在C盘的Windows文件夹下生成一个UfdApp文件夹(好像是这个文件夹名,记不太清楚)。

想要删除干净,不但要删除这个软件,还要删除Windows下的这个文件夹。

而且,用这个软件量产或使用其它功能后,都会自动复制一个UFDUtility软在U盘里面,这是我最不喜欢的地方了。

不过,如果不把UFDUtility放在U盘里,那如果制作了加密区,还是要用到它才能输入密码进加密区。

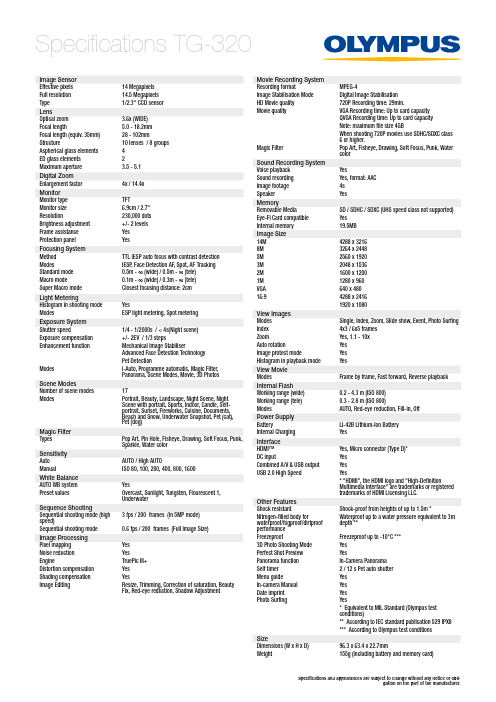

TG-320 数码相机规格说明书

Specifications TG-320Specifications and appearances are subject to change without any notice or obli-gation on the part of the manufacturer.Image Sensor Effective pixels 14 Megapixels Full resolution 14.5 Megapixels Type1/2.3'' CCD sensor LensOptical zoom 3.6x (WIDE)Focal length5.0 - 18.2mm Focal length (equiv. 35mm)28 - 102mmStructure10 lenses / 8 groups Aspherical glass elements 4ED glass elements 2Maximum aperture 3.5 - 5.1Digital Zoom Enlargement factor 4x / 14.4x Monitor Monitor type TFTMonitor size 6.9cm / 2.7''Resolution230,000 dots Brightness adjustment +/- 2 levels Frame assistance Yes Protection panel YesFocusing System Method TTL iESP auto focus with contrast detection ModesiESP , Face Detection AF, Spot, AF Tracking Standard mode 0.5m - ∞ (wide) / 0.5m - ∞ (tele)Macro mode0.1m - ∞ (wide) / 0.3m - ∞ (tele)Super Macro mode Closest focusing distance: 2cm Light MeteringHistogram in shooting mode YesModesESP light metering, Spot metering Exposure System Shutter speed1/4 - 1/2000s / < 4s(Night scene)Exposure compensation +/- 2EV / 1/3 stepsEnhancement functionMechanical Image StabiliserAdvanced Face Detection Technology Pet DetectionModesi-Auto, Programme automatic, Magic Filter, Panorama, Scene Modes, Movie, 3D Photos Scene ModesNumber of scene modes 17ModesPortrait, Beauty, Landscape, Night Scene, Night Scene with portrait, Sports, Indoor, Candle, Self-portrait, Sunset, Fireworks, Cuisine, Documents, Beach and Snow, Underwater Snapshot, Pet (cat), Pet (dog)Magic Filter Types Pop Art, Pin Hole, Fisheye, Drawing, Soft Focus, Punk, Sparkle, Water colorSensitivity Auto AUTO / High AUTOManual ISO 80, 100, 200, 400, 800, 1600White Balance AUTO WB system YesPreset valuesOvercast, Sunlight, Tungsten, Flourescent 1, UnderwaterSequence ShootingSequential shooting mode (high speed)3 fps / 200 frames (in 5MP mode)Sequential shooting mode 0.6 fps / 200 frames (Full Image Size)Image Processing Pixel mapping Yes Noise reduction YesEngineTruePic III+ Distortion compensation Yes Shading compensation YesImage EditingResize, Trimming, Correction of saturation, Beauty Fix, Red-eye reduction, Shadow AdjustmentMovie Recording System Recording formatMPEG-4Image Stabilisation Mode Digital Image Stabilisation HD Movie quality 720P Recording time: 29min.Movie qualityVGA Recording time: Up to card capacity QVGA Recording time: Up to card capacity Note: maximum file size 4GBWhen shooting 720P movies use SDHC/SDXC class 6 or higher.Magic FilterPop Art, Fisheye, Drawing, Soft Focus, Punk, Water colorSound Recording System Voice playback YesSound recording Yes, format: AAC Image footage 4s SpeakerYesMemoryRemovable MediaSD / SDHC / SDXC (UHS speed class not supported)Eye-Fi Card compatible Yes Internal memory 19.5MB Image Size 14M 4288 x 32168M 3264 x 24485M 2560 x 19203M 2048 x 15362M 1600 x 12001M 1280 x 960VGA 640 x 48016:94288 x 24161920 x 1080View Images Modes Single, Index, Zoom, Slide show, Event, Photo Surfing Index 4x3 / 6x5 frames ZoomYes, 1.1 - 10x Auto rotationYes Image protect modeYes Histogram in playback mode YesView Movie ModesFrame by frame, Fast forward, Reverse playback Internal Flash Working range (wide)0.2 - 4.3 m (ISO 800) Working range (tele)0.3 - 2.8 m (ISO 800)ModesAUTO, Red-eye reduction, Fill-in, Off Power Supply BatteryLI-42B Lithium-Ion Battery Internal ChargingYesInterface HDMI™Yes, Micro connector (Type D)*DC inputYes Combined A/V & USB output Yes USB 2.0 High SpeedYes* "HDMI", the HDMI logo and "High-DefinitionMultimedia Interface" are trademarks or registered trademarks of HDMI Licensing LLC.Other Features Shock resistantShock-proof from heights of up to 1.5m *Nitrogen-filled body forwaterproof/fogproof/dirtproof performance Waterproof up to a water pressure equivalent to 3m depth **FreezeproofFreezeproof up to -10°C ***3D Photo Shooting Mode Yes Perfect Shot Preview YesPanorama function In-Camera Panorama Self timer 2 / 12 s Pet auto shutter Menu guideYes In-camera Manual Yes Date imprint Yes Photo SurfingYes* Equivalent to MIL Standard (Olympus test conditions)** According to IEC standard publication 529 IPX8*** According to Olympus test conditions SizeDimensions (W x H x D)96.3 x 63.4 x 22.7mmWeight155g (including battery and memory card)。

视觉加速—ATI Eyefinity三屏游戏应用全面体验测试

视觉加速—ATI Eyefinity三屏游戏应用全面体验测试

微型计算机评测室(文/图)

【期刊名称】《《微型计算机》》

【年(卷),期】2009(000)034

【摘要】我们本来可以早一点将ATI Eyefinity三屏输出的测试奉献给大家,但首次测试后发现,不少问题和测试数据与“网上爆料”并不相符。

因此我们决定花更多的时间体验和测试。

通过本文,大家将了解到有关三屏游戏应用的方方面面的问题。

【总页数】6页(P115-120)

【作者】微型计算机评测室(文/图)

【作者单位】

【正文语种】中文

【中图分类】TP311.5

【相关文献】

1.全面屏手机时代来临4款全面屏手机体验 [J], 黄贞璇

2.霸气2K大屏震撼的视觉体验三星S27D850显示器体验评测 [J], 钟佳德

3.2017年全面屏手机加速普及标准、技术与资源三大挑战待解 [J], 孙永杰

4.全面屏大趋势\r小米MIX 3、荣耀Magic 2、vivo NEX\r 三款旗舰手机体验对比 [J], 李强

5.不一样的全面屏小米全面屏电视55英寸体验 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

Synopsys OptoDesigner 2020.09安装指南说明书

3. Troubleshooting scanning issues........................................................25

Accidental full scan proliferation by folder paths which include build or commit ID............................ 25 Solution......................................................................................................................................25

Contents

Contents

Preface....................................................................................................5

1. Scanning best practices......................................................................... 8

IBM推出的光学芯片组原型下载电影只需1s

厂商都在研究光学 电路 。2 0 0 6年 9 月 ,英特 尔和加州大学研究人员合 作 ,打造出 了低成本 “ 激光 芯片” . 其传输 速度 远高 于标 准铜线 连接 。 20 0 6年 1 ,I M研 究 出了使 光 2月 B 子减速运行 的方法 .使得 以光 的形 式存储数据变为可 能。 ( o 8 N.1 4 —

(I T 07 C M 2 0 ,4月 9 1 ~ 5日于 北京 )

过将激光光源从液 晶面板分 离、利 用 光 纤导 入 .便 可实 现 厚 度 不到

2 m 的平 板 液 晶显 示器 。 ( o .c 5 N.

4 61

片快 8倍 。IM表 示 ,新型芯片组 B 以光信号 的方式传输信息 ,而不是 电 子 信 号 ,预 计 这 一 产 品 将 于 21 0 0年用 于企业和消 费应用 。IM B

■

研究 部 门科技 副 总裁 TC C e 表 .. hr t

示 ,随着 电影 、音乐和 图片等数字

S o k r ae发布 新 媒体 的迅速普及 ,消费者对于大容 机 S NCRONO。 tc eY l Y

上推 出了号称全球 最快 的激光切割

型掺铒光纤

S ce a t kr l o Y e公 司 最 近 推 出一

宽只有 3 5h . i 2 m和 5 5m . m的光学 2 接 收 器 ,足 以集 成 到 印刷 电路 板

时掺杂 的铝元素更精确地控制 ,从

而 支持 任 意 增 益平 坦 滤 波器 的需 求 。Sok a t Yl c e同时 推 出一种 短 波 长 的 单 模 光 纤 产 品 ,可 以 支 持

R B成 像 系统 、激 光器 尾 纤 等应 G 用 。 (o 7 N.) 4

夜叉AX4 4-流量AX3000无线路由器数据表说明书

WiFi 6 for Today’s Smart DevicesNighthawk® AX4 WiFi 6 Router is powered by the industry’s latest WiFi 6 (802.11ax) standardwith 4 times increased data capacity provides consistent and powerful signal strength to all your connected devices. Blazing-fast combined WiFi speeds upto 3Gbps and a 1.5GHz triple-core processor ensures superiorperformance for concurrentreal-time applications such asmulitmedia streaming, onlinegaming, and audio/video chats.With NETGEAR Armor™, you getthe best-in-class cybersecurity toprotect your family from malware,stolen passwords, identity theft,and hacker attacks.4K4KWiFi 6—Ready for Today and Tomorrow’s Smart HomeDelivering four times better performance than AC WiFi, WiFi 6 allows more devices to connect and stream simultaneously, without impacting speed or reliability, by efficiently packing and scheduling data. Rising to the challenges of modern smart home demands, this new standard of WiFi is ready to support more devices with better reliability and faster speeds.CapacityWiFi 6 gives you improved network capacity for more WiFi devices. Have more fun with the uninterrupted 4K streaming, gaming, and the smart home experience. SpeedGet ultra-fast wireless speeds with moreconnections for all devices with lesscongestion. You’ll get some blazingconnection speeds of more thanone Gigabit per second or more,4K streaming, & VR/AR gaming.RangeExperience reliable and stronger WiFicoverage indoors and outdoors for allyour devices. High-performance antennas,pre-optimized for best peformance, on therouter amplify WiFi signals for maximizedrange and reliable coverage.4-Stream WiFi 6Stream HD & 4K UHD content to more devices at the same time.Faster Upload & Download SpeedsFaster WiFi download & upload speeds at the same time.Greater than 1Gbps WiFi SpeedsUnimaginable speeds now delivered. Capable of greater than 1Gbps WiFi speeds to newer mobile devices.4Powerful Triple-Core 1.5GHz ProcessorMore processing power increases the overall performance of your network.TRIPLEGet ultra-fast wireless speeds for better 4K UHD streaming, gaming or video conferencing experience.SpeedUP TO 3GBPS † SPEEDS —600Mbps + 2400Mbps with 4-stream connectivity **AX OPTIMIZED POWERFUL PROCESSOR—1.5GHz triple-coreprocessor ensures smooth 4K UHD streamingM ORE WIFI FOR MORE DEVICES— Allows efficient data transmission to devices simultaneously.§160MHZ CHANNEL SUPPORT ***—Doubles the speeds as offered by 80MHz channels to provide Gigabit speeds for compatible mobile devices and laptops1024-QAM—25% increased data efficiency and faster speeds than a 256-QAM router5 GIGABIT PORTS—Connect more wired devices for faster file transferand uninterrupted connections with 1 WAN & 4 LAN Ethernet portsSUPERSPEED USB 3.0 PORT —Up to 10X faster than USB 2.025%5G CapacityGet better performance for all your smart home devices even when your family is busy streaming videos or uploading media files during the Internet rush hour.U LTIMATE RANGE—WiFi coverage throughout small to medium homesWiFi RangeHIGH-PERFORMANCE ANTENNAS—Two (2) external antennasextend strong and reliable WiFi signals over larger areaFaster and expanded coverage throughout your home and for all your devices.There’s nothing more frustrating than lost connections! With NETGEAR’s advanced features & best-in-class technology, you’ll reduce interference & enjoy more reliable WiFi connectivity.Reliable ConnectionsSIMULTANEOUS DUAL BAND WIFI—Supports two WiFi bands simultaneously to double the available bandwidth and provide a reliable, dedicated WiFi network for smooth online gamingwithout any network congestionBEAMFORMING+—Improve range and performance for both 2.4 and 5GHz devicesStart enjoying your new device faster than ever. NETGEAR wants to make sure installation and management is simple & easy, so you can connect quickly & make sure you stay that way!Ease Of UseNIGHTHAWK ® APP —Easily set up your router and get more out of your WiFi. Includes access from anywhere to manage your network away from homeAX WIFI SUPPORTS ALL CURRENT WIFI DEVICES —WiFi 6 supports all current WiFi device and is backward compatible with WiFi 5 and earlier generation devicesVOICE CONTROLLED BY AMAZON ALEXA ® & THE GOOGLEASSISTANT ™— Control your NETGEAR WiFi network with simplevoice commandsWith NETGEAR, sharing across yournetwork is fun and easy, such as accessing stored photos & music.USB 3.0 PORT—Faster streaming, backup and easy accessto your stored mediaSharingADDITIONAL DFS CHANNELS—Reduce interference fromneighboring networksMaintain high security across your network to ensure your privacy & family is safe while online. Whether it’s preventing phishing & spyware or just limiting access for kids & guests, NETGEAR has you covered.SecurityV PN SUPPORT —On PC, MAC, & now also with OpenVPN Connect app on iOS & Android, securely access your home network & Internet connection from your mobile device remotelySTANDARDS-BASED WIFI SECURITY (802.11i, 128-bit AES encryption with PSK)GUEST NETWORK—Separate and secure network for your guests AUTOMATIC FIRMWARE UPDATE —Delivers latest security patches to the routerL ATEST SECURITY STANDARD—Supports WPA3 the latest and cutting-edge WiFi security protocolNETGEAR ARMOR ™—Cybersecurity for your home ††. Advanced cyber threat protection for your home network and your connected devices Powerful Triple-core ProcessorNighthawk AX4 WiFi Router is powered by a powerful triple-core processor designed to transfer multi-Gigs of data. Full-packet processing offload means zero load on the CPU. Enjoy smoother Ultra-HD 4K video streaming and gaming without interruptions.Gigabit WiFi to Mobile DevicesSupport for 160MHz channel allows the Nighthawk AX4 WiFi 6 Router to stream at Gigabit speeds to supported mobile devices, which are increasingly used for video streaming or gaming.Nighthawk AppThe NETGEAR Nighthawk® App makes it easy to set up your router and get more out of your WiFi. With the app, you can install your router in a few steps—just connect your mobile device to the router network and the app will walk you through the rest. Once set up, you can use the intuitive dashboard to pause the Internet on your connected devices, run a quick Internet speed test, and much more!• Anywhere Access—Easily monitor your home networkanytime, anywhere• Internet Speed Test—Check the broadband speeds fromyour service provider• Pause Internet—Pause the Internet to any device• Traffic Meter—Track Internet data usage• Guest Networks—Set up separate WiFi access for guests• Quick Setup—Get connected in just minutes• Get it at NETGEAR Armor ™identifies network s STAY SAFE EVEN WHEN AWAY FROM HOME WIFI — Stay in the know with Nighthawk App. Anywhere, anytime—Encrypts your internet connection toConnection DiagramInternetLEDon/off USB portPower on/offPackage Contents• NETGEAR ® Nighthawk ® AX4/4-Stream AX3000 WiFi Router (RAX40v2)• Ethernet cable • Quick start guide • Power adapterPhysical Specifications• Dimensions: 13.38 x 8.11 x 2.24 in (340 x 206 x 57 mm)• Weight: 1.32 lb (600 g)Technical Specifications• WiFi 6 (802.11ax) Dual Band WiFi (AX3000) - 2.4GHz AX: 2x2 (Tx/Rx) 1024/256-QAM20/40MHz, up to 600Mbps - 5GHz AX: 2x2 (Tx/Rx) 1024-QAM20/40/80/160MHz, up to 2.4Gbps - B ackwards compatible with 802.11a/b/g/n/ac WiFi • One (1) USB 3.0 port• 1024-QAM—25% data efficiency and faster speeds than a 256-QAM router • Powerful 1.5GHz triple-core processor • Memory: 256MB flash and 512MB RAM • 160MHz channel support• Additional DFS channels reduce interference from neighboring networks • Longer range with 2 high-performance antennas• Five (5) 10/100/1000Mbps Gigabit Ethernet ports - 1 WAN & 4 LAN • O n/off LED light switchKey Features• 2.5X better performance than an AC router—4-stream WiFi with up to 600 + 2400Mbps † for ultra-fast wireless speeds **• 160MHz channel support ***—Doubles the speeds as offered by 80MHz channels to provide Gigabit speeds for compatible mobile devices and laptops• Powerful processor—Dual-core processor ensures smooth 4K UHD streaming & gaming• 4 Gigabit Ethernet LAN ports—Connect more wired devices for faster file transfer and uninterrupted connections• Nighthawk ® App—Easily set up your router and get more out of your WiFi. Includes a ccess from anywhere to manage your network away from home• WiFi 6 supports all current WiFi devices and is backward compatible with WiFi 5 and earlier generation devices• NETGEAR Armor ™—Advanced cyber threat protection for your home network and your connected devices ††• Works with Amazon Alexa ® & the Google Assistant ™—Control your NETGEAR WiFi network with simple voice commandsSupport• 90-day complimentary technical supportfollowing purchase from a NETGEAR authorized reseller• J oin the NETGEAR Community Forum. Visit System Requirements• Microsoft ® Windows 7, 8, 10, Vista ®, XP ®, 2000, Mac OS ®, UNIX ®, or Linux ®• Microsoft ® Internet Explorer ® 11 or higher, Microsoft Edge, Google Chrome ® 55 or higher, Firefox ® 45 or higher, Safari ® 10 or higherSecurity• Standards-based WiFi Security (802.11i, 128-bit AES encryption with PSK)• Automatic firmware update delivers latest security patches to the router• Guest network access—separate & secure • VPN Support—Secure access to your home network away from home• S upports WPA3, the latest and cutting-edge WiFi security protocol• NETGEAR Armor ™—Advanced cyber threat protection for your home network and your connected devices ††Warranty• /warranty• Extend your warranty & technical support within 90 days of product purchase [US only]. Visit: /homeThis product comes with a limited warranty that is valid only if purchased from a NETGEAR authorized reseller.*90-day complimentary technical support following purchase from a NETGEAR authorized reseller.†Maximum wireless signal rate derived from IEEE 802.11 specifications. Actual data throughput and wireless coverage will vary and may be lowered by network and environmentalconditions, including network traffic volume and building construction. NETGEAR makes no representations or warranties about this product's compatibility with AX standards. Up to 3000Mbps wireless speeds achieved when connecting to other 802.11ax 3000Mbps devices.**When working with 160MHz clients as compared to a 2x2 AC router that does not support 160MHz.***Requires client device that supports 160MHz bandwidth on WiFi.§ Requires compatible AX clients with DL-OFDMA and UL-OFDMA support.‡As compared to an AC1200 2x2 router.††NETGEAR Armor requires a paid subscription after the initial introductory period.For indoor use only.NETGEAR, the NETGEAR Logo, NETGEAR Armor and Nighthawk are trademarks of NETGEAR, Inc. Mac, Mac OS, iPhone, and the Mac logo are trademarks of Apple Inc. App Store is a service mark of Apple Inc., registered in the U.S. and other countries. Google Play and the Google Play logo are trademarks of Google LLC. Any other trademarks mentioned herein are for reference purposes only. ©2020 NETGEAR, Inc.NETGEAR, Inc. 350 E. Plumeria Drive, San Jose, CA 95134-1911 USA, /supportD-RAX40v2-21。

5G_SA用户的短信接收容灾方案研究与实践

技术分析1 研究背景在2G/3G传统电路域中,短消息业务由短消息服务中心(SMSC)提供,业务流程均承载在七号信令网上。

随着VOLTE网络的商用,为VoLTE用户继续提供短消息业务,成为运营商在网络演进过程中必须支持的功能。

VoLTE用户使用VoLTE短信网关实现IMS 域SI P消息与短信中心M A P信令的转换,从而实现VoLTE用户的短信收发等业务[1]。

在4G网络时代,用户在4G的EPC、IMS域注册的同时,会发起联合位置更新,注册至3G的MSC上。

当VoLTE短信网关发生故障时,根据IMS域的域选功能,短信业务可以回落至3G电路域,由用户注册的MSC进行转发,同样地,当I MS域的S-C S C F发生故障时,VoLTE短信也回落至3G电路域,由3G网络进行发送[2]。

随着5G网络的发展,5G SA用户呈逐步增加状态,目前在各运营商中的占比越来越多。

因5G SA网络的特殊性,当用户处于5G SA注册及网络覆盖时,只注册在5G核心网络上,不做联合位置更新,无法附着于3G电路域网络。

由于5G SA用户的这种特性,在以下两种场景下会出现较长时间的无法接收短信情况。

(1)场景一:VoLTE短信网关主用DC发生故障,业务全部切换到容灾DC,5G SA用户无法接收短信。

(2)场景二:VoLTE网关运行正常,用户注册的S-CSCF设备发生故障时,对于5G SA用户的MT短信,VoLTE短信网关通过该S-CSCF无法投递成功,按流程再向3G电路域投递时也无法成功,会出现用户短信暂时不可达的现象。

在用户进行重注册时消除(此时5G SA用户的短信接收容灾方案研究与实践阎艳芳,郝双洋,邵 斐,杨 姣(中国联合网络通信有限公司河南省分公司,河南 郑州 450000)摘要:当VoLTE短信网关主用数据中心(DC)发生故障切换到容灾DC时,在用户刷新注册前,容灾DC收到短信中心下发的手机终呼(MT)消息会通过3G电路域网络完成消息终呼。

骇客任务秘密武器曝光

骇客任务秘密武器曝光

佚名

【期刊名称】《大众科技》

【年(卷),期】2003(000)005

【摘要】喜爱科幻电影的读者朋友大概都知道,2003年有着"骇客任务年"之称!为什么呢?因为继1999年的《骇客任务》(The Matrix)之后,今年将连续推出这部电影的第二、第三集(片名分别为《The Matrix Reloaded》与《TheMatrix Revolutions》,目前暂无中文译名)。

除了颇受影迷喜爱的基努李维(Keanu Reeves)确定续任该片主角之外,新片带来的另一话题在于前阵子于国外网站曝光的秘密武器:

【总页数】1页(P14-14)

【正文语种】中文

【中图分类】F416.6

【相关文献】

1.可变矩形束曝光机的曝光方式和曝光数据调度 [J], 罗武庭;沈国liu

2.索爱秘密武器V70魔机曝光 [J],

3.康佳平板完成"三级跳"秘密武器曝光高清路线图 [J],

4.骇客来袭《骇客帝国2》重装上阵 [J], 王新禧

5.Borland秘密武器曝光——SideWinder先睹为快 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

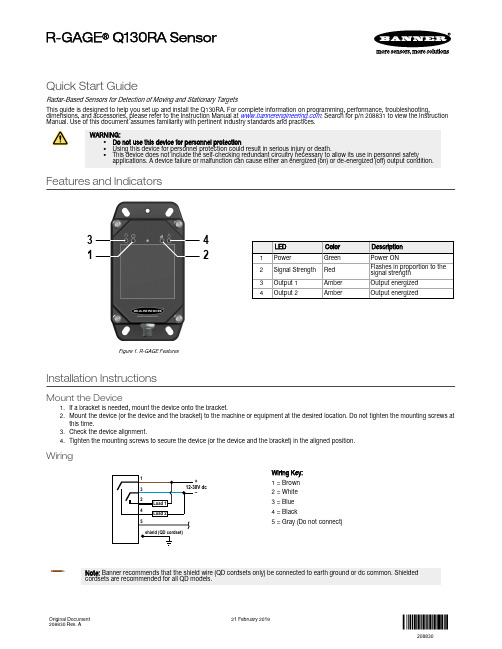

Banner Engineering Q130RA雷达传感器快速启动指南说明书

Quick Start GuideRadar-Based Sensors for Detection of Moving and Stationary TargetsThis guide is designed to help you set up and install the Q130RA. For complete information on programming, performance, troubleshooting,dimensions, and accessories, please refer to the Instruction Manual at . Search for p/n 208831 to view the InstructionManual. Use of this document assumes familiarity with pertinent industry standards and practices.WARNING:•Do not use this device for personnel protection•Using this device for personnel protection could result in serious injury or death.•This device does not include the self-checking redundant circuitry necessary to allow its use in personnel safetyapplications. A device failure or malfunction can cause either an energized (on) or de-energized (off) output condition.Features and Indicators1342Figure 1. R-GAGE FeaturesInstallation InstructionsMount the Device1.If a bracket is needed, mount the device onto the bracket.2.Mount the device (or the device and the bracket) to the machine or equipment at the desired location. Do not tighten the mounting screws atthis time.3.Check the device alignment.4.Tighten the mounting screws to secure the device (or the device and the bracket) in the aligned position.WiringWiring Key:1 = Brown2 = White3 = Blue4 = Black5 = Gray (Do not connect)Note: Banner recommends that the shield wire (QD cordsets only) be connected to earth ground or dc common. Shielded cordsets are recommended for all QD models.R-GAGE ® Q130RA SensorOriginal Document 208830 Rev. A21 February 2019208830Install the SoftwareOperating SystemMicrosoft® Windows® operating system version 101 Hard Drive Space130MB Third-Party Software.NET version 4.6.2 or higher USB PortAvailable USB portImportant: Administrative rights are required to install the Banner Radar Configuration software.1.Download the latest version of the software from .2.Navigate to and open the downloaded file.3.Click Install to begin the installation process.4.Depending on your system settings, a popup window may appear prompting to allow Banner Radar Configuration to make changes to yourcomputer. Click Yes.5.Click Close to exit the installer.Getting StartedPower up the sensor, and verify that the power LED is ON green.Connect to the Sensor1.Connect the sensor to the Pro Converter Cable.2.Connect the Pro Converter Cable to the PC.3.Open the Banner Radar Configuration Software.4.Go to Sensor > Connect.The Connection screen displays.5.Select the correct Sensor Model and Com Port for the sensor.6.Click Connect.A message displays confirming the connection to the sensor.7.Click OK.The Connection screen closes and the sensor data displays.SpecificationsRangeThe sensor is able to detect a proper object (see Detectable Objects) at the followingranges, depending on the target:9076 models: 1 m to 24 m (3.3 ft to 78.7 ft)2450 models: 1 m to 40 m (3.3 ft to 131.2 ft)Detectable ObjectsObjects containing metal, water, or similar high-dielectric materialsOperating PrincipleFrequency modulated continuous-wave (FMCW) radarOperating Frequency24.050-24.250 GHz, ISM BandMaximum Output PowerERP: 3.3 mW, 5 dBmEIRP: 100 mW, 20 dBmSupply Voltage (Vcc)12 V dc to 30 V dcPower and Current Consumption, exclusive of loadNormal Run Mode: 1.2 W, Current consumption < 50 mA at 24 V dcSupply Protection CircuitryProtected against reverse polarity and transient overvoltagesDelay at Power-up< 3 secondsOutput ConfigurationBipolar NPN/PNP outputLoad 1 on pin 2 (white wire) = NPNLoad 2 on pin 4 (black wire) = PNPOutput Ratings50 mA maximum capability each outputSaturation: < 3.5 V at 50 mAOutput ProtectionProtected against short circuit conditionsResponse TimeSoftware selectable:50 ms ON/50 ms OFF100 ms ON/100 ms OFF50 ms ON/500 ms OFF50 ms ON/1000 ms OFFIndicatorsPower LED: Green (power ON)Signal Strength LED: Red, flashes in proportion to signal strength. Steady on at 4xexcess gain. Only indicates signal amplitude, not target distance.Output LEDs: Amber (output energized)See Figure 1 on page 1ConstructionHousing: ABS/polycarbonateQD Connector: Stainless steelMounting Threads: Stainless steelOperating Temperature–40 °C to +65 °C (–40 °F to +149 °F)Environmental RatingIEC IP67ConnectionsIntegral 5-pin M12/Euro-style quick disconnect. Models with a quick disconnectrequire a mating cordsetCertificationsETSI/EN 300 440FCC part 15for others, contact Banner EngineeringCountry of Origin: USAFCC ID: UE3RGAGE1XX—This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) this device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.Beam PatternsNote:The effective beam pattern depends on the signal strength threshold and the properties of the target. - Tel: + 1 888 373 6767P/N 208830 Rev. AP/N 208830 Rev. A - Tel: + 1 888 373 67673Banner Engineering Corp. Software Copyright NoticeThis software is protected by copyright, trade secret, and other intellectual property laws. You are only granted the right to use the software and only for the purposes described by Banner. Banner reserves all other rights in this software. For so long as you have obtained an authorized copy of this software directly from Banner, Banner grants you a limited, nonexclusive, nontransferable right and license to use this software.You agree not to use, nor permit any third party to use, this software or content in a manner that violates any applicable law, regulation or terms of use under this Agreement. You agree that you will not reproduce, modify, copy, deconstruct, sell, trade or resell this software or make it available to any file-sharing or application hosting service.Disclaimer of Warranties. Your use of this software is entirely at your own risk, except as described in this agreement. This software is provided "AS-IS." To the maximum extent permitted by applicable law, Banner, it affiliates, and its channel partners disclaim all warranties, expressed or implied, including any warranty that the software is fit for a particular purpose, title, merchantability, data loss, non-interference with or non-infringement of any intellectual property rights, or the accuracy, reliability, quality or content in or linked to the services. Banner and its affiliates and channel partners do not warrant that the services are secure, free from bugs, viruses, interruption, errors, theft or destruction. If the exclusions for implied warranties do not apply to you, any implied warranties are limited to 60 days from the date of first use of this software.Limitation of Liability and Indemnity. Banner, its affiliates and channel partners are not liable for indirect, special, incidental, punitive or consequential damages, damages relating to corruption, security, loss or theft of data, viruses, spyware, loss of business, revenue, profits, or investment, or use of software or hardware that does not meet Banner minimum systems requirements. The above limitations apply even if Banner and its affiliates and channel partners have been advised of the possibility of such damages. This Agreement sets forth the entire liability of Banner, its affiliates and your exclusive remedy with respect to the software use. You agree to indemnify and hold Banner and its affiliates and channel partners harmless from any and all claims, liability and expenses, including reasonable attorney's fees and costs, arising out of your use of the Services or breach of this Agreement (collectively referred to as "Claims"). Banner reserves the right at its sole discretion and at its own expense, to assume the exclusive defense and control of any Claims. You agree to reasonably cooperate as requested by Banner in defense of any Claims.Banner Engineering Corp. Limited WarrantyBanner Engineering Corp. warrants its products to be free from defects in material and workmanship for one year following the date of shipment. Banner Engineering Corp. will repair or replace, free of charge, any product of its manufacture which, at the time it is returned to the factory, is found to have been defective during the warranty period. This warranty does not cover damage or liability for misuse, abuse, or the improper application or installation of the Banner product.THIS LIMITED WARRANTY IS EXCLUSIVE AND IN LIEU OF ALL OTHER WARRANTIES WHETHER EXPRESS OR IMPLIED (INCLUDING, WITHOUT LIMITATION, ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE), AND WHETHER ARISING UNDER COURSE OF PERFORMANCE, COURSE OF DEALING OR TRADE USAGE.This Warranty is exclusive and limited to repair or, at the discretion of Banner Engineering Corp., replacement. IN NO EVENT SHALL BANNER ENGINEERING CORP. BE LIABLE TO BUYER OR ANY OTHER PERSON OR ENTITY FOR ANY EXTRA COSTS, EXPENSES, LOSSES, LOSS OF PROFITS, OR ANY INCIDENTAL, CONSEQUENTIAL OR SPECIAL DAMAGES RESULTING FROM ANY PRODUCT DEFECT OR FROM THE USE OR INABILITY TO USE THE PRODUCT, WHETHER ARISING IN CONTRACT OR WARRANTY, STATUTE, TORT, STRICT LIABILITY, NEGLIGENCE, OR OTHERWISE.Banner Engineering Corp. reserves the right to change, modify or improve the design of the product without assuming any obligations or liabilities relating to any product previously manufactured by Banner Engineering Corp. Any misuse, abuse, or improper application or installation of this product or use of the product for personal protection applications when the product is identified as not intended for such purposes will void the product warranty. Any modifications to this product without prior express approval by Banner Engineering Corp will void the product warranties. All specifications published in this document are subject to change; Banner reserves the right to modify product specifications or update documentation at any time. Specifications and product information in English supersede that which is provided in any other language. For the most recent version of any documentation, refer to: .For patent information, see /patents.© Banner Engineering Corp. All rights reserved。

终极解码2009新年版

终极解码2009新年版感谢匿名人士的投递终极解码是一款全能型、高度集成的解码包,自带两种流行播放器并对WMP提供良好支持,可在简、繁、英3种语言平台下实现各种流行视频音频的完美回放及编码功能。

推荐安装环境的是Windows XP、DirectX 9.0C、Windows Media Player 10/11,不支持Windows9x;如需在Vista系统下使用,请在安装前先关闭Vista的UAC功能。

若与Realplayer同时使用,请在安装时不要选择Real 解码器,QuickTime类似。

终极解码 2009 新年版终极解码是一款全能型、高度集成的解码包,自带两种流行播放器并对WMP提供良好支持,可在简、繁、英3种语言平台下实现各种流行视频音频的完美回放及编码功能。

推荐安装环境的是Windows XP、DirectX 9.0C、Windows Media Player 10/11,不支持Windows9x;如需在Vista系统下使用,请在安装前先关闭Vista的UAC功能。

若与Realplayer同时使用,请在安装时不要选择Real 解码器,QuickTime类似。

用户许可协议1. 除原创工具外,“终极解码”所含各组件的版权归其各自的作者或所有人所有。

2. 您可以并仅可以在保持软件原样性和完整性的前提下,随意分发、复制和传播“终极解码”。

3. 本软件遵循“概不保证”的原则,作者不承担任何由于使用本软件所造成的损害的责任。

4. 除已授权的专用版外,本软件禁止用于任何涉及盈利目的商业用途,包括销售、出租以及在任何性质的媒体中一起出售。

纳米盘下载地址:FinalCodecs2009ny.exeMD5:0f5254db79dc91ee0b6cc4bd678f12f1 FinalCodecs2009.exe主要更新内容1. 解码中心- 增加“自动--导入用户设置”的默认选项。

影音播放时,可在自动模式下,自动导入用户自定义的解码设置。

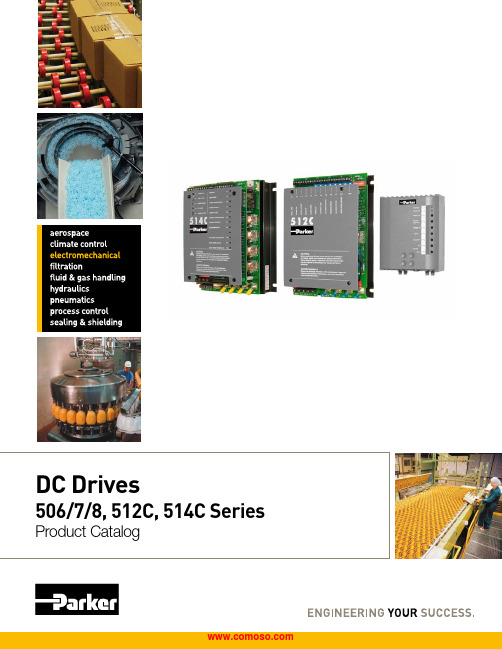

2009年DC驱动产品目录说明书

Table of Contents! WARNING - USER RESPONSIBILITYFAILURE OR IMPROPER SELECTION OR IMPROPER USE OF THE PRODUCTS DESCRIBED HEREIN OR RELATED ITEMS CAN CAUSE DEATH, PERSONAL INJURY AND PROPERTY DAMAGE.This document and other information from Parker Hannifin Corporation, its subsidiaries and authorized distributors provide product or system options for further investigation by users having technical expertise.The user, through its own analysis and testing, is solely responsible for making the final selection of the system and components and assuring that all performance, endurance, maintenance, safety and warning requirements of the application are met. The user must analyze all aspects of the application, follow applicable industry standards, and follow the information concerning the product in the current product catalog and in any other materials provided from Parker or its subsidiaries or authorized distributors.To the extent that Parker or its subsidiaries or authorized distributors provide component or system options based upon data or specifications provided by the user, the user is responsible for determining that such data and specifications are suitable and sufficient for all applications and reasonably foreseeable uses of the components or systems.OFFER OF SALEThe items described in this document are hereby offered for sale by Parker Hannifin Corporation, its subsidiaries or its authorized distributors. This offer and its acceptance by the provisions stated in the detailed ‘Offer of Sale’ which is available upon request.Global PartnershipsGlobal SupportParker is committed to helping makeour customers more productiveand more profitable through ourglobal offering of motion andcontrol products and systems. Inan increasingly competitive globaleconomy, we seek to developcustomer relationships as technologypartnerships. Working closely withour customers, we can ensure the bestselection of technologies to suit theneeds of our customers’ applications.Electromechanical Technologiesfor High Dynamic Performanceand Precision MotionParker electromechanicaltechnologies form an importantpart of Parker’s global motion andcontrol offering. Electromechanicalsystems combine high performancespeed and position control with theflexibility to adapt the systems tothe rapidly changing needs of theindustries we serve.Parker HannifinThe global leader in motion and control technologies and systemsWith annual sales exceeding$12 billion in fiscal year 2011,Parker Hannifin is the world’sleading diversified manufacturer ofmotion and control technologiesand systems, providing precision-engineered solutions for a widevariety of mobile, industrial andaerospace markets. The companyemploys approximately 58,000people in 47 countries aroundthe world. Parker has increasedits annual dividends paid toshareholders for 55 consecutiveyears, among the top five longest-running dividend-increase recordsin the S&P 500 index. For moreinformation, visit the company’s website at , or itsinvestor information site at http://About Parker Hannifin CorporationWith more than 30 years of worldwide application experience, Parker assists its customers in improving productivity and reducing energy consumption with a comprehensive, robust range of DC drives and drive systems. Parker DC drive products are sold, supported and serviced worldwide, with solutions from simple speed control to complex multi-motor coordinated process control. Parker DC drive products are easy to configure and commission, with simple but flexible function block-based configuration tools and connectivity with all major industrial fieldbus networks.Digital DC Drives Maximize Flexibility and Functionality Using the same 32-bit control architecture as our current range of AC drive products, Parker’s range of digital DC drives provides the same high level of functionality - and with it flexibility and performance - as comparable AC drive systems, while simultaneously allowing the user to integrate both AC and DC drive systems in a single machine with the same interface and software.Retrofit Existing Applications with the Latest TechnologyBy retrofitting existing DC motor applications with Parker digital DC drives, the user can avoid the cost of replacing an existing functioning, DC motor with a similar AC drive system, while still enjoying the benefits of a flexible control platform and high performance drive.DC590+ Integrator Series 2 Digital DC DriveThe DC590+ uses an advanced control platform to provide high levels of flexibility and performance for a wide range of applications. Designed for machine integrators, the DC590+ features function block programming, multiple communications and feedback options and support worldwide. Available as non-regenerative or full fourquadrant regenerative. Available from 1-2400A maximum. Fieldbus options include Profibus-DP, CANopen, Modbus RTU, Ethernet and DeviceNet.Typical applications include • Converting machinery • Hoists and cranes• Plastics processing machinery • Wire and cable manufacturing • Automotive test standsProcessSimple2400A35A15ADC Drives Product Range OverviewGlobal DC Drive Solutions to Maximize Flexibility and Increase performanceDRV Package - “Ready to Install” DC DrivesSave design time, panel space and the time and cost of component sourcing and installation with Parker’s unique DRV drive format. DRV drives include all peripheral power components typically required in a DC drive system, integrated in a self-contained package. This packagecontains the additional components within the footprint of the standard drive module and saves significant panel space while reducing complexity and improving the appearance.01010010002000HPSystemsSingle Phase Analog Non-Isolated Converter: 506/507/508Economical, compact torque and speed control of permanent magnet or shunt wound DC motors. Selectable between 110VAC or 230VAC single phase supply. Tachometer or armature voltage feedback, 3, 6, or 12A armature options.Typical applications include:• Conveyors, basic speed control • Packaging machineryDC590+ DRV - “Ready to Install” Series 2The DC590+ DRV Series version is a complete packaged drive solution, including AC line contactor, AC line fuses, DC fuse, control / field fuse and provisions for a motor blower starter. The DRV series reduces panel complexity while saving on panel space. Available to 1750 HP (2400A) maximum.Single Phase Two Quadrant Analog Isolated Converter: 512CThe 512C provides effective torque and speed control of permanent magnet or wound field DC motors. Extremely linear speed and current loops in an isolated package, ideal for single or multiple motor applications up to 32A (10 HP at highest input voltage).Typical applications include:• Centrifugal fans and pumps • Extruders and mixers• Small paper converting machinesSingle Phase Four Quadrant Analog Isolated Converter: 514CThe 514C offers full four quadrant regenerative control of permanent magnet or wound field DC motors. Ideal for applications requiring accurate or rapid deceleration of high inertia loads. Effective for single or multiple motor applications to 32A (10 HP at highest input voltage).Typical applications include:• Machine tool spindles • Wire drawing machines •Winders/Reelers01010010002000 HP1010010002000 HP010*******2000 HP010*******2000 HPAnalog DC Drives RangeDescriptionThe 506, 507 and 508 series drives break new ground in cost-effective DC motor control. Available in 3, 6 or 12A armature ratings, the feature packed minimum footprint design is ideal for speed or torque control of permanent magnet or shunt wound DC motors fed from single phase supplies.Typical applications include:• Fans and pumps • Conveyors• Packaging machineryLow cost high featured design IP20 protected coversCompact footprint and DIN rail mounting Selectable 110V or 230V supplySelectable tach or armature voltage feedbackStandardsMarkedEN61800-3 (EMC) with external filterEN50178 (safety, low voltage directive)andTechnical SpecificationAnalog DC Drives506/507/508 SeriesUp to 2 HP/12ADimensions (in/mm)Note: Color of enclosure may vary from illustrationDescriptionIsolated control circuitry, a host of features, and extremely linear control loop make the 512C ideal for single motor or multi-drive applications. The 512C is suitable for controlling permanent magnet or field wound DC motors in speed or torque control, and can be used “open loop” with armature voltage feedback, or with DC tach feedback for enhanced regulation and speed range. Chassis mount, IP00 rating. Typical applications include:• Centrifugal fans and pumps • Extruders and mixers • ConveyorsTechnical SpecificationsAnalog DC Drives512C SeriesUp to 32AStandards:Marked EN61800-3 (EMC) with external filterEN50178 (safety, low voltage directive)Common Specifications: 512C and 514C Voltage Ratings:Dimensions (in/mm):DescriptionThe regenerative 514C DC drive offers full four quadrant control of DC motors from single phase supplies. As such it is ideal for applications involving overhauling loads or where rapid and accurate deceleration is required. 514C can be used “open loop” with armature voltage feedback, or with DC tach feedback for enhanced regulation and speed range. Chassis mount, IP00 rating. Typical applications include:• Machine tool spindles • Wire drawing machines • Winders/ReelersTechnical SpecificationAnalog DC Drives514C SeriesUp to 32ANote: Color of front panel may vary from illustrationDrive mounted on a “footprint” filterEMC Filtersfor AC and DC DrivesDescriptionA range of pre-selected EMC (Electromagnetic Compatibil-ity)/RFI (Radio Frequency Interference) Filters are avail-able, suitable for all drives. These filters are a cost effective and easily implemented solution for the abatement of EMC in order to meet certain directives. Installation of the drive must be in accordance with the installation guidelines in the product manual.Filters described as “footprint” type are designed to save panel space by mounting behind the drive.Ordering© 2012 Parker Hannifin Corporation. All rights reserved.Parker Hannifin CorporationSSD Drives Division 9225 Forsyth Park Dr.Charlotte, NC 28273 USATel: (704) 588-3246 Fax: (704) 588-3249AE – UAE, Dubai Tel: +971 4 8127100 ********************AR – Argentina, Buenos Aires Tel: +54 3327 44 4129AT – Austria, Wiener Neustadt Tel: +43 (0)2622 23501-0 *************************AT – Eastern Europe, Wiener NeustadtTel: +43 (0)2622 23501 900 ****************************AU – Australia, Castle Hill Tel: +61 (0)2-9634 7777AZ – Azerbaijan, Baku Tel: +994 50 2233 458****************************BE/LU – Belgium, Nivelles Tel: +32 (0)67 280 900*************************BR – Brazil, Cachoeirinha RS Tel: +55 51 3470 9144BY – Belarus, Minsk Tel: +375 17 209 9399*************************CA – Canada, Milton, Ontario Tel: +1 905 693 3000CH – Switzerland, Etoy Tel: +41 (0)21 821 87 00*****************************CL – Chile, Santiago Tel: +56 2 623 1216CN – China, Shanghai Tel: +86 21 2899 5000CZ – Czech Republic, Klecany Tel: +420 284 083 111*******************************DE – Germany, Kaarst Tel: +49 (0)2131 4016 0*************************DK – Denmark, Ballerup Tel: +45 43 56 04 00*************************ES – Spain, Madrid Tel: +34 902 330 001 ***********************FI – Finland, Vantaa Tel: +358 (0)20 753 2500 *************************FR – France, Contamine s/Arve Tel: +33 (0)4 50 25 80 25 ************************GR – Greece, Athens Tel: +30 210 933 6450 ************************HK – Hong Kong Tel: +852 2428 8008HU – Hungary, Budapest Tel: +36 1 220 4155*************************IE – Ireland, Dublin Tel: +353 (0)1 466 6370 *************************IN – India, MumbaiTel: +91 22 6513 7081-85IT – Italy, Corsico (MI) Tel: +39 02 45 19 21 ***********************JP – Japan, Tokyo Tel: +81 (0)3 6408 3901KR – South Korea, Seoul Tel: +82 2 559 0400KZ – Kazakhstan, Almaty Tel: +7 7272 505 800****************************LV – Latvia, Riga Tel: +371 6 745 2601 ************************MX – Mexico, Apodaca Tel: +52 81 8156 6000MY – Malaysia, Shah Alam Tel: +60 3 7849 0800NL – The Netherlands, OldenzaalTel: +31 (0)541 585 000 ********************NO – Norway, Ski Tel: +47 64 91 10 00************************NZ – New Zealand, Mt Wellington Tel: +64 9 574 1744PL – Poland, Warsaw Tel: +48 (0)22 573 24 00 ************************PT – Portugal, Leca da Palmeira Tel: +351 22 999 7360**************************Parker WorldwideRO – Romania, Bucharest Tel: +40 21 252 1382*************************RU – Russia, Moscow Tel: +7 495 645-2156************************SE – Sweden, Spånga Tel: +46 (0)8 59 79 50 00 ************************SG – Singapore Tel: +65 6887 6300SK – Slovakia, Banská Bystrica Tel: +421 484 162 252**************************SL – Slovenia, Novo Mesto Tel: +386 7 337 6650**************************TH – Thailand, Bangkok Tel: +662 717 8140TR – Turkey, Istanbul Tel: +90 216 4997081 ************************TW – Taiwan, Taipei Tel: +886 2 2298 8987UA – Ukraine, Kiev Tel +380 44 494 2731*************************UK – United Kingdom, WarwickTel: +44 (0)1926 317 878 ********************US – USA, Cleveland Tel: +1 216 896 3000VE – Venezuela, Caracas Tel: +58 212 238 5422ZA – South Africa, Kempton ParkTel: +27 (0)11 961 0700*****************************。

AVP102使用说明书

安全

安全注意事项

妥善的安装、正确的操作和安装后的维护对本智能型阀门定位器的安全使用都至关重要。 本说明书中提出的安全指示分为 警告 、注意 和 注 三种类型。

警告

表示一种潜在的危险情况。若忽视该情况,则可能导致死亡或严重受伤。

注意

表示一种潜在的危险情况。若忽视该情况,则可能导致操作员轻微受伤,或者设 备损坏。

2-5-1: 接线原则...............................................................................................................................2-10 2-5-2: 接线步骤...............................................................................................................................2-10 2-6 : 用于无弹簧双作用执行机构的 SVP (双作用放大器)...................................................................2-11 2-6-1: 将双作用放大器安装到 SVP 上..............................................................................................2-12 2-6-2: 不带过滤减压阀直接安装的双作用 SVP ................................................................................2-13 2-6-3: 将双作用 SVP 安装到薄膜执行机构上 ...................................................................................2-14 2-6-4: 将双作用 SVP 安装到角行程执行机构上 ...............................................................................2-14 2-6-5: 自动设定...............................................................................................................................2-15

选项升级用户指南

包含向加拿大进口的货运相关信息的INTTRA 选项

• 收货人名称、地址和邮编 • 货物级别申报纳税身份、申报纳税国家、申报人SCAC 代码 (适用于自助报关)

Proprietary and Confidential Copyright © 2009 INTTRA, Inc.

INTTRA-ACT SI 3

包含有向美国进口的货运信息的INTTRA 选项 (卸货港在美国)

包含有向美国进口的货运相关信息的INTTRA 选项

•

必填项目:

– – – – 收货人名称、地址和邮编 通知方名称、地址和邮编 货物级别申报纳税身份、申报纳税国家、申报人SCAC 代码(适用于自助报关) 商品(HS)代码

Proprietary and Confidential Copyright © 2009 INTTRA, Inc.

如果你的收货人国家代码不是巴西,必须输入巴西的第三方详细资料

第三方名称及地址

Proprietary and Confidential Copyright © 2009 INTTRA, Inc.

集装箱皮重公斤数

集装箱皮重

Proprietary and Confidential Copyright © 2009 INTTRA, Inc.

货物毛重公斤数

货物总重

Proprietary and Confidential Copyright © 2009 INTTRA, Inc.

货物总பைடு நூலகம்积(每个集装箱货物总立方米数)

Proprietary and Confidential Copyright © 2009 INTTRA, Inc.

我为影歌狂——解密硬盘的AV串流指令集

我为影歌狂——解密硬盘的AV串流指令集

Nindon

【期刊名称】《电脑自做》

【年(卷),期】2005(000)009

【摘要】有一种新型硬盘,专为影音应用而生,在出厂前,这种硬盘已经被施放

了速度魔法——“Streaming command Set”,它的神奇之处在哪儿呢?

【总页数】4页(P87-90)

【作者】Nindon

【作者单位】无

【正文语种】中文

【中图分类】TP333.35

【相关文献】

1.神奇狂荡的山野如花灿烂的歌吹--逢二《山野歌吹》评介 [J], 黄建国

2.9影音聊天狂——影音聊天的快乐——更好地利用共享空间QQ硬盘大解密[J],

3.既是播放器,也是硬盘盒天敏炫影硬盘版DMP220 [J],

4.《我为歌狂》林夕或将搭档田震主持《我为歌狂》 [J],

5.AV平台可靠伴侣西部数据WD AV-GPSATA硬盘 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

88E1111-B2-BAB1C000_千兆网口