AV61-100中文资料

广电 可靠性实验室介绍(中文)

低气压+高低温试验

型号: QD61 温度范围:-70~150 ℃ 标称容积:1000×1000×1000mm 气压:常压~200Pa(40000m)

降压速率:≤15s ( 58.8 kPa ~ 18 kPa)

高速老化试验箱

型号: ESPEC EHS-221M 温度范围:105-142.9℃ 湿度范围:75%-100% 压力范围:0.1-0.296Mpa 工作室尺寸:400×280×270mm

机器尺寸 :1100*1000*1100 mm(W*H*D)

QUV紫外线老化机

型号: Q-Lab QUV/spray 温度范围:

50-85℃(光照),40-60℃(冷凝) 辐照强度: 0.35~1.55W/m2/nm(UVA-340,UVA-351)

0.35~1.23W/m2/nm(UVB-313) 灯管类型:

湿度

0.2L/min

样品喷淋 0.2L/min

样品架喷淋 0.2L/min

CS-6灯管冷却@7000W @3.5L/min

机器尺寸 :198H x 127W x 102D(cm)

日光式碳弧灯式耐候试验箱

型号: Q8-9706

BLACK PANEL: CONSTANTLY 63 ± 3 ℃ 83 ± 3 ℃ AUTOMATICALLY

摇摆试验台

摇摆试验台 环绕振幅:±45º 环绕周期:4~20s 纵摇振幅:0~±30º 纵摇周期:3~10s 偏航振幅:0~±10º 偏航周期:5~20s

型号:Y5212II –750 跌落高度:300~1500mm可调 最大负载:100kg 最大尺寸:1000×800×1000mm

大型跌落试验台

型号:GX500-3 跌落高度:0~1500mm可调 最大负载:500kg 最大尺寸:

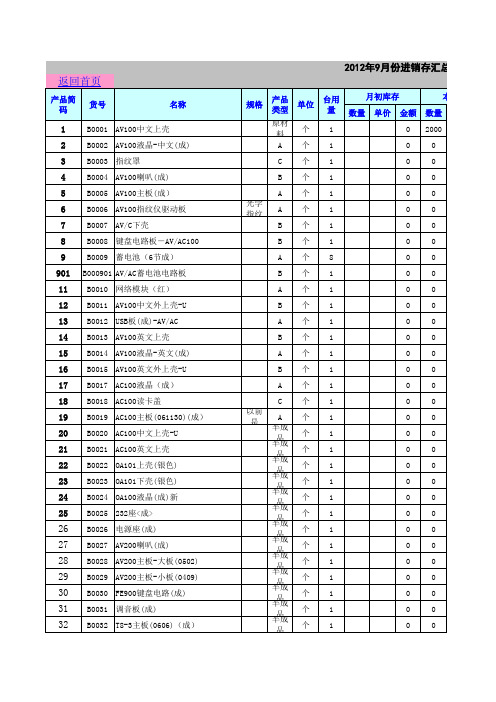

E cel进销存表格 仓库进销存表格 简单的库房做账表格 自动计算库存

半成

半品成

半品成

蓝光

半品成 半品成

有14P 半品成

座 红头 光学

半品成 半品成

指纹 半品成

半品成

半品成

半品成

半品成

半品成

半品成

半品成

半品成

半品成

半品成

半品成

半品成

半品成

不带 半品成

ANVIZ 半品成

半品成

电源 半品成

板 半品成

半品成

半品成

半品成

半品成

半品成

半品成

半品成

半品成

半品成

品

个 个 个 个 个 片 个 个 套 根 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个

套 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 块 个 个 个 个 个 个 片 个

1 1 1 1 1 1 1 1 15 3 1 1 1 1 0 1 0 3 1 1 1 1 176 1 1 2 1 1 1 1 2 2 1 3 1 1

0

0

0

0

0

18 B0018 AC100读卡盖

19 B0019 AC100主板(061130)(成)

20 B0020 AC100中文上壳-U

21 B0021 AC100英文上壳

22 B0022 OA101上壳(银色)

23 B0023 OA101下壳(银色)

24 B0024 OA100液晶(成)新

25 B0025 232座<成>

规格

产品 类型

原材 料 A

单位

个 个

台用 量

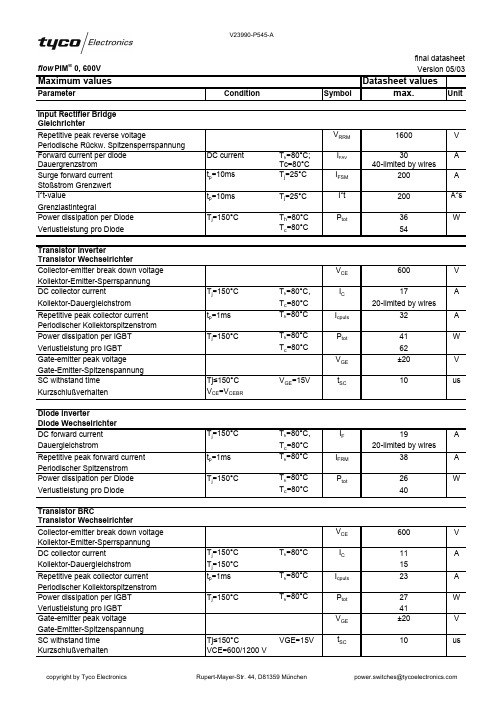

V23990-P544-A中文资料

Maximum valuesDatasheet valuesParameterConditionSymbolmax.UnitInput Rectifier Bridge GleichrichterRepetitive peak reverse voltageV RRM1600V Periodische Rückw. Spitzensperrspannung Forward current per diode DC current T h =80°C;I FAV 30A Dauergrenzstrom Tc=80°C 40-limited by wiresSurge forward current t p =10ms T j =25°C I FSM200A Stoßstrom Grenzwert I 2t-valuet p =10ms T j =25°C I 2t200A 2s GrenzlastintegralPower dissipation per Diode T j =150°CT h =80°C P tot36WVerlustleistung pro DiodeT c =80°C54Transistor InverterTransistor WechselrichterCollector-emitter break down voltage V CE600V Kollektor-Emitter-Sperrspannung DC collector current T j =150°CT h =80°C,I C 15A Kollektor-Dauergleichstrom T c =80°C 20-limited by wiresRepetitive peak collector current t p =1ms T h =80°C I cpuls 30A Periodischer Kollektorspitzenstrom Power dissipation per IGBT T j =150°CT h =80°C P tot41W Verlustleistung pro IGBT T c =80°C62Gate-emitter peak voltageV GE±20V Gate-Emitter-Spitzenspannung SC withstand time Tj ≤150°C V GE =15Vt SC 10usKurzschlußverhalten V CE =V CEBRDiode InverterDiode Wechselrichter DC forward current T j =150°CT h =80°C,I F 18A DauergleichstromT c =80°C 20-limited by wiresRepetitive peak forward current t p =1ms T h =80°C I FRM 37A Periodischer Spitzenstrom Power dissipation per Diode T j =150°C T h =80°C P tot29WVerlustleistung pro DiodeT c =80°C44Transistor BRCTransistor WechselrichterCollector-emitter break down voltage V CE600V Kollektor-Emitter-Sperrspannung DC collector current T j =150°C T h =80°CI C9A Kollektor-Dauergleichstrom T j =150°C 12Repetitive peak collector current t p =1ms T h =80°C I cpuls 17A Periodischer Kollektorspitzenstrom Power dissipation per IGBT T j =150°CT h =80°CP tot 27W Verlustleistung pro IGBT 41Gate-emitter peak voltageV GE±20V Gate-Emitter-Spitzenspannung SC withstand time Tj ≤150°CVGE=15Vt SC10usKurzschlußverhaltenVCE=600/1200 VMaximum values Datasheet values Parameter Condition Symbol max.UnitDiode BRCDiode BRCDC forward current T j=150°C T h=80°C I F13A Dauergleichstrom T j=150°C17Repetitive peak forward current t p=1ms T h=80°C I FRM26A Periodischer SpitzenstromPower dissipation per Diode T j=150°C T h=80°C P tot23W Verlustleistung pro Diode35Thermal propertiesThermische Eigenschaften150°C max. Chip temperature Tjmaxmax. Chiptemperatur-40…+125°C Storage temperature TstgLagertemperatur-40…+125°C Operation temperature TopBetriebstemperaturInsulation propertiesModulisolationInsulation voltage t=1min V4000VdcisIsolationsspannungCreepage distance min 12,7mm KriechstreckeClearance min 12,7mm LuftstreckeDescription Symbol Conditions Datasheet values UnitT(C°)Other conditions VGE(V)VR(V)VCE(V)IC(A)IF(A)(Rgon-Rgoff)VGS(V)VDS(V)Id(A)Min Typ MaxInput Rectifier BridgeGleichrichterForward voltage V F Tj=25°C301,221,45V Durchlaßpannung Tj=125°C1,21Threshold voltage (for power loss calc. only)V to Tj=25°C300,92V Schleusenspannung Tj=125°C0,81Slope resistance (for power loss calc. only)r t Tj=25°C0,01Ohm Ersatzwiderstand Tj=125°C300,013Reverse current I r Tj=25°C12000,02mA Sperrstrom Tj=150°C4Thermal resistance chip to heatsink per chip RthJH Thermal greasethickness≤50um 1,95K/WWärmewiderstand Chip-Kühlkörper pro Chip WarmeleitpasteDicke≤50umλ = 0,61 W/mK1,287Transistor Inverter, inductive loadTransistor WechselrichterGate emitter threshold voltage V GE(th)Tj=25°C VCE=VGE0,0004345V Gate-Schwellenspannung Tj=125°CCollector-emitter saturation voltage V CE(sat)Tj=25°C15152,162,8V Kollektor-Emitter Sättigungsspannung Tj=125°C2,57Collector-emitter cut-off I CES Tj=25°C06000,1mA Kollektor-Emitter Reststrom Tj=125°C2Gate-emitter leakage current I GES Tj=25°C250200nA Gate-Emitter Reststrom Tj=125°CIntegrated Gate resistor R gint -Ohm Integrirter Gate WiderstandTurn-on delay time t d(on)Tj=25°C Rgon=40Ohm1530015ns Einschaltverzögerungszeit Tj=125°C Rgoff=20Ohm18Rise time t r Tj=25°C Rgon=40Ohm1530015ns Anstiegszeit Tj=125°C Rgoff=20Ohm19Turn-off delay time t d(off)Tj=25°C Rgon=40Ohm1530015ns Abschaltverzögerungszeit Tj=125°C Rgoff=20Ohm242Fall time t f Tj=25°C Rgon=40Ohm1530015ns Fallzeit Tj=125°C Rgoff=20Ohm32Turn-on energy loss per pulse E on Tj=25°C Rgon=40Ohm1530015mWs Einschaltverlustenergie pro Puls Tj=125°C Rgoff=20Ohm0,324Turn-off energy loss per pulse E off Tj=25°C Rgon=40Ohm1530015mWs Abschaltverlustenergie pro Puls Tj=125°C Rgoff=20Ohm0,368Input capacitance C ies Tj=25°C f=1MHz0250,80,96nF Eingangskapazität Tj=125°COutput capacitance C oss Tj=25°C f=1MHz0250,0840,101nF Ausgangskapazität Tj=125°CReverse transfer capacitance C rss Tj=25°C f=1MHz0250,0520,062nF Rückwirkungskapazität Tj=125°CGate charge Q Gate Tj=25°C15480157699nC Gate Ladung Tj=125°CThermal resistance chip to heatsink per chipWärmewiderstand Chip-Kühlkörper pro Chip RthJH Thermal greasethickness≤50um 1,7K/WThermal resistance chip to case per chip Wärmewiderstand Chip-Gehause pro Chip WarmeleitpasteDicke≤50umλ = 0,61 W/mK1,122Diode InverterDiode WechselrichterDiode forward voltage V F Tj=25°C151,962,3V Durchlaßspannung Tj=125°C1,55Peak reverse recovery current I RRM Tj=25°C Rgon=40Ohm1530015A Rückstromspitze Tj=125°C19Reverse recovery time t rr Tj=25°C Rgon=40Ohm1530015ns Sperreverzögerungszeit Tj=125°C58Reverse recovered charge Q rr Tj=25°C Rgon=40Ohm1530015uC Sperrverzögerungsladung Tj=125°C0,65Reverse recovered energy Erec Tj=25°C Rgon=40Ohm1530015mWs Sperrverzögerungsenergie Tj=125°C0,078Thermal resistance chip to heatsink per chipWärmewiderstand Chip-Kühlkörper pro Chip RthJH Thermal greasethickness≤50um 2,43K/WThermal resistance chip to case per chip Wärmewiderstand Chip-Gehause pro Chip WarmeleitpasteDicke≤50umλ = 0,61 W/mK1,6038Description Symbol Conditions Datasheet values UnitT(C°)Other conditions VGE(V)VR(V)VCE(V)IC(A)IF(A)(Rgon-Rgoff)VGS(V)VDS(V)Id(A)Min Typ Max Transistor BRCTransistor BRCGate emitter threshold voltage V GE(th)Tj=25°C VCE=VGE0,0002345V Gate-Schwellenspannung Tj=125°CCollector-emitter saturation voltage V CE(sat)Tj=25°C1572,242,6V Kollektor-Emitter Sättigungsspannung Tj=125°C2,65Collector-emitter cut-off I CES Tj=25°C06000,03mA Kollektor-Emitter Reststrom Tj=125°C0,7Gate-emitter leakage current I GES Tj=25°C250200nA Gate-Emitter Reststrom Tj=125°CTurn-on delay time t d(on)Tj=25°C Rgon=80Ohm153007ns Einschaltverzögerungszeit Tj=125°C Rgof=40Ohm15Rise time t r Tj=25°C Rgon=80Ohm153007ns Anstiegszeit Tj=125°C Rgof=40Ohm17Turn-off delay time t d(off)Tj=25°C Rgon=80Ohm153007ns Abschaltverzögerungszeit Tj=125°C Rgof=40Ohm195Fall time t f Tj=25°C Rgon=80Ohm153007ns Fallzeit Tj=125°C Rgof=40Ohm28Turn-on energy loss per pulse EonTj=25°C Rgon=80Ohm153007uWs Einschaltverlustenergie pro Puls Tj=125°C Rgof=40Ohm0,151Turn-off energy loss per pulse EoffTj=25°C Rgon=80Ohm153007uWs Abschaltverlustenergie pro Puls Tj=125°C Rgof=40Ohm0,148SC withstand time tSCus KurzschlußverhaltenInput capacitance CissTj=25°C f=1MHz0250,350,42nF Eingangskapazität Tj=125°COutput capacitance C oss Tj=25°C f=1MHz0250,0380,046nF Ausgangskapazität Tj=125°CReverse transfer capacitance Cies Tj=25°C f=1MHz0250,0230,028nF Rückwirkungskapazität Tj=125°CGate charge Qgate Tj=25°C1548063242nC Gate Ladung Tj=125°CThermal resistance chip to heatsink per chipWärmewiderstand Chip-Kühlkörper pro Chip RthJH Thermal greasethickness≤50um 2,97K/WThermal resistance chip to case per chip Wärmewiderstand Chip-Gehause pro Chip WarmeleitpasteDicke≤50umλ = 0,61 W/mK1,9602Diode BRCDiode BRCDiode forward voltage VFTj=25°C71,492,15V Durchlaßspannung Tj=125°C1,38Reverse current I r Tj=25°C Rgon=80Ohm153007250uA Sperrstrom Tj=125°CReverse recovery time trrTj=25°C Rgon=80Ohm153007ns Sperreverzögerungszeit Tj=125°C202Reverse recovered charge QrrTj=25°C Rgon=80Ohm153007uC Sperrverzögerungsladung Tj=125°C0,67Reverse recovery energy E rec Tj=25°C Rgon=80Ohm153007uWs Sperrverzögerungsenergie Tj=125°C0,14Thermal resistance chip to heatsink per chipWärmewiderstand Chip-Kühlkörper pro Chip RthJH Thermal greasethickness≤50um 3,66K/WThermal resistance chip to case per chip Wärmewiderstand Chip-Gehause pro Chip Warmeleitpaste Dicke≤50um λ = 0,61 W/mKNTC-ThermistorNTC-WiderstandRated resistance R25Tj=25°C Tol. ±5%20,92223,1kOhm NennwiderstandDeviation of R100D R/R Tc=100°C R100=1503Ohm2,9%/K Abweichung von R100Power dissipation given Epcos-Typ P Tj=25°C210mW Verlustleistung Epcos-Typ angebenB-value B(25/100)Tj=25°C Tol. ±3%3980K B-WertOutput inverterFigure 1.Typical output characteristicsFigure 2.Typical output characteristicsOutput inverter IGBTOutput inverter IGBTTj = 125 °C V GE parameter:from:6V to 16V V GE parameter:from:6V to 16V in 1V stepsin 1V stepsFigure 3.Typical transfer characteristicsFigure 4.Typical diode forward current as Output inverter IGBTa function of forward voltageIc= f(V GE )Output inverter FREDI F =f(V F )parameter: tp = 250 µs V CE = 11VOutput inverterFigure 5.Typical switching energy losses Figure 6.Typical switching energy losses as a function of collector current as a function of gate resistor Output inverter IGBTOutput inverter IGBTE = f (Ic)V CE =300V V CE =300V V GE =15VV GE =15V R G on = 2*R Goff =40ΩIc =15AFigure 7.Typical switching times as aFigure 8.Typical switching times as a function of collector current function of gate resistor Output inverter IGBTOutput inverter IGBTt = f (Ic)t = f (R G )inductive load, Tj = 125 °CV CE =300V V CE =300V V GE =15VV GE =15V R G on = 2*R Goff =40ΩIc =15AOutput inverterFigure 9.Typical reverse recovery time as a Figure 10.Typical reverse recovery current as a function of IGBT turn on gate resistor function of IGBT turn on gate resistor Output inverter FRED diodeOutput inverter FRED diodet rr = f (Rgon)I RRM = f (Rgon)Tj =125°C Tj =125°C V R =300V V R =300V I F =15A I F =15AFigure 11.Typical reverse recovery charge as aFigure 12.Typical rate of fall of forward function of IGBT turn on gate resistor and reverse recovery current as aOutput inverter FRED diodefunction of IGBT turn on gate resistor Q rr = f (Rgon)Output inverter FRED diode dI0/dt,dIrec/dt = f (Rgon)Tj =125°C Tj =125°C V R =300V V R =300V I F =15A I F =15AFigure 13.IGBT transient thermal impedance Figure 14.FRED transient thermal impedance as a function of pulse width as a function of pulse widthZ th JH = f(tp)Z th JH = f(tp)IGBT thermal model values FRED thermal model valuesR (C/W)Tau (s)R (C/W)Tau (s)0,066,9E+000,051,4E+010,236,3E-010,227,9E-010,821,2E-010,981,1E-010,382,2E-020,693,3E-020,132,8E-030,353,6E-03Figure 15.Power dissipation as a Figure 16.Collector current as a function of heatsink temperature function of heatsink temperatureOutput inverter IGBTI c = f (Th)V GE=15VFigure 17.Power dissipation as a Figure 18.Forward current as a function of heatsink temperature function of heatsink temperatureOutput inverter FRED Output inverter FREDP tot = f (Th)I F = f (Th)parameter: Tj = 150°C parameter: Tj = 150°CBrakeFigure 19.Typical output characteristicsFigure 20.Typical output characteristicsBrake IGBTBrake IGBTCE parameter: tp = 250 µsTj = 125 °CV GE parameter:from:6V to16VV GE parameter:from:6V to16Vin 1V stepsin 1V stepsFigure 21.Typical transfer characteristicsFigure 22.Typical diode forward current asBrake IGBTa function of forward voltageIc= f(V GE )parameter: tp = 250 µsBrakeFigure 23.Typical switching energy lossesFigure 24.Typical switching energy losses as a function of collector current as a function of gate resistor Brake IGBTBrake IGBTE = f (Ic)E = f (R G )inductive load, Tj = 125 °CV CE =300V V CE =300V V GE =15VV GE =15V R G on = 2*R Goff =40ΩIc =7AFigure 25.Typical switching times as aFigure 26.Typical switching times as a function of collector currentfunction of gate resistor Brake IGBTBrake IGBTt = f (Ic)t = f (R G )inductive load, Tj = 125 °CV CE =300V V CE =300V V GE =15VV GE =15V R G on = 2*R Goff =40ΩIc =7AFigure 27.IGBT transient thermal impedanceFigure 28.FRED transient thermal impedance as a function of pulse widthas a function of pulse widthZ th JH = f(tp)Z th JH = f(tp)Parameter: D = tp / T RthJH=2,97K/W Parameter: D = tp / T RthJH=3,66K/WFigure 29.Power dissipation as aFigure 30.Collector current as afunction of heatsink temperature function of heatsink temperature Brake IGBTBrake IGBTP tot = f (Th)I c = f (Th)parameter: Tj = 150°Cparameter: Tj = 150°CV GE =15VFigure 32.Forward current as afunction of heatsink temperatureBrake FREDI F = f (Th)parameter: Tj = 150°Cparameter: Tj = 150°CInput rectifier bridgeFigure 33.Typical diode forward current asFigure 34.Diode transient thermal impedance a function of forward voltageas a function of pulse widthRectifier diodeI F =f(V F )Z th JH = f(tp)Figure 35.Power dissipation as aFigure 36.Forward current as afunction of heatsink temperature function of heatsink temperature Rectifier diodeRectifier diodeP tot = f (Th)I F = f (Th)parameter: Tj = 150°C parameter: Tj = 150°CThermistorFigure 37.Typical NTC characteristicas a function of temperatureR T= f (T)Output inverter applicationGeneral conditions:3 phase SPWM,Vgeon=15VVgeoff=0VRgon=40ohmsRgoff=20ohmsFigure 1.Typical avarage static lossFigure 2.Typical avarage static loss as a function of output currentas a function of output currentModulation index * cosfi Modulation index * cosfiparameter Mi*cosfi from -1,00to1,00parameter Mi*cosfi from -1,00to1,00in 0,20stepsin 0,20stepsFigure 3.Typical avarage switching lossFigure 4.Typical avarage switching loss as a function of output currentas a function of output currentIGBTPloss=f(Iout)FREDPloss=f(Iout)DC link=320V DC link=320V Switching freq.fsw from2kHz to 16kHzSwitching freq.fsw from2kHz to 16kHzparameter in* 2stepsparameter in* 2stepsOutput inverter applicationGeneral conditions:3 phase SPWM,Vgeon=15V Vgeoff=0V Rgon=40ohms Rgoff=20ohms Figure 5.Typical available 50Hz output current Figure 6.Typical available 50Hz output current as a function of Mi*cosfi as a function of switching frequencyPhase Iout=f(Mi*cosfi)Phase Iout=f(fsw)DC link=320V DC link=320Vfsw=16kHz Mi*cosfi=0,8 Heatsink temp.Th from60°C to100°C Heatsink temp.Th from60°C to100°C parameter in5°C steps parameter in5°C stepsFigure 7.Typical available 50Hz output current Figure 8.Typical available 0Hz output current as a function of Mi*cosfi and fsw as a function of switching frequencyPhase Iout=f(fsw,Mi*cosfi)Phase Ioutpeak=f(fsw)DC link=320V DC link=320VTh=80°C Heatsink temp.Th from60°C to100°Cparameter in5°C stepsOutput inverter applicationGeneral conditions:3 phase SPWM,Vgeon=15V Vgeoff=0V Rgon=40ohms Rgoff=20ohms Figure 9.Typical available electric Figure 10.Typical efficiencypeak output power as a as a function of output powerfunction of heatsink temperatureInverter Pout=f(Th)Inverter efficiency=f(Pout)Conditions:Tj=125CDC link=320VModulation index Mi=1cosfi=0,80Switching freq.fsw from2kHz to16kHz parameter in* 2steps Conditions:Tj=125CDC link=320VModulation index Mi=1cosfi=0,8Switching freq.fsw from1kHz to16kHz parameter in* 2stepsHeatsink temperature=80°CMotor efficiency=0,85。

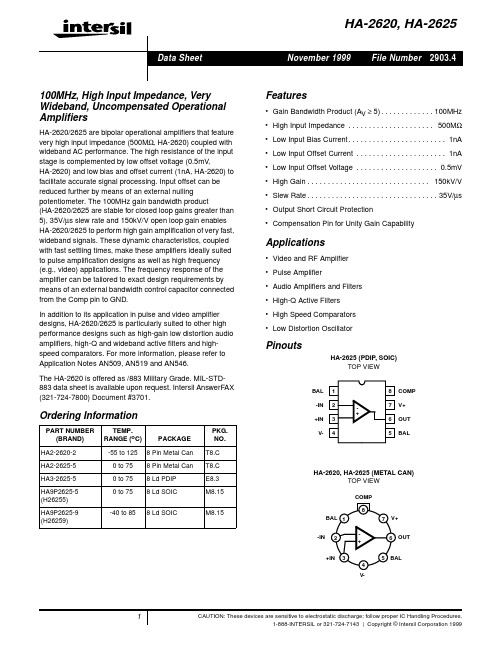

HA-2626中文资料

Maximum Storage Temperature Range . . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . 300oC

(SOIC - Lead Tips Only)

The HA-2620 is offered as /883 Military Grade. MIL-STD883 data sheet is available upon request. Intersil AnswerFAX (321-724-7800) Document #3701.

Ordering Information

元器件交易网

HA-2620, HA-2625

Absolute Maximum Ratings

Supply Voltage (Between V+ and V- Terminals) . . . . . . . . . . . . 45V Differential Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12V Peak Output Current . . . . . . . . . . . . . . . Full Short Circuit Protection

元器件交易网

Data Sheet

HA-2620, HA-2625

November 1999 File Number 2903.4

100MHz, High Input Impedance, Very Wideband, Uncompensated Operational Amplifiers

DM9000中文手册

,011)被选 中

访问类型 高电平

是访问数据 端口;低电平 是访问地址 端口

字命令标志, 默认低电平 有效

当访问 外部数据存 储器是字或 双字宽度时, 被置位

100

INT

O

中断请求信 号

高电平 有效,极性能 修改

37~53 56

SD31~16

I/O

双字模式,高 16 位数据引 脚

注意:以上介质无关端口都内部自带 60K 欧姆的下拉电阻 处理器接口引脚

1

IOR#

I

2

IOW#

I

3

AEN#

I

处理器读命 令

低电平 有效,极性能 够被 EEPRO M 修改,详细 请参考对 EE PROM 内容 的描述

处理器写命 令

低电平 有效,同样能 修改极性

芯片选择,低

4

IOWAIT

O

14

RST

外部介质无 关接口发送 时钟

外部介质无 关接口发送 数据低 4 位

输出

TXD[2: 0]决定内部 存储空间基 址:TXD [2: 0]) * 10H +

300H

54

MDIO

I/O

外部介质无

关接口串行

数据通信

57

MDC

O

外部介质无 关串行数据 通信口时钟, 且与中断引 脚有关

该引脚 高电平时候, 中断引脚低 电平有效;否 则高有效

0 0 16 位

0 1 32 位

108 位

11未 定义

66

EECK

I

时钟信号

67

EECS

I/O

片选

也做 LE D 模式选择 引脚

BY716资料

a

MAM163

Fig.1 Simplified outline (SOD61) and symbol.

MARKING Table 1 Cathode band colour codes PACKAGE CODE SOD61E SOD61E SOD61E SOD61E SOD61E SOD61G SOD61G SOD61K SOD61K SOD61K green red green blue yellow red blue red green yellow OUTER BAND brown brown red red red green green blue blue blue INNER BAND

−

ns

2001 Sep 24

5

元器件交易网

Philips Semiconductors

Product specification

Very fast high-voltage soft-recovery rectifiers

GRAPHICAL DATA

BY715 to BY724

IFRM Tstg Tj

repetitive peak forward current storage temperature junction temperature

−65 −65

2001 Sep 24

4

元器件交易网

Philips Semiconductors

Product specification

元器件交易网

Philips Semiconductors

Product specification

Very fast high-voltage soft-recovery rectifiers

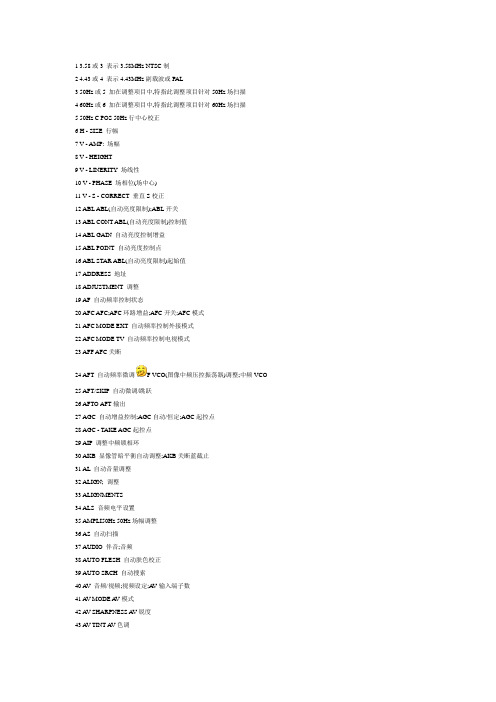

彩电总线调整中英文对照表

1 3.58或3 表示3.58MHz N TSC制2 4.43或4 表示4.43MHz副载波或PAL3 50Hz或5 加在调整项目中,特指此调整项目针对50Hz场扫描4 60Hz或6 加在调整项目中,特指此调整项目针对60Hz场扫描5 50Hz C POS 50Hz行中心校正6 H - SIZE 行幅7 V - AMP: 场幅8 V - HEIGHT9 V - LINERITY场线性10 V - PHASE 场相位(场中心)11 V - S - CORRECT 垂直S校正12 ABL ABL(自动亮度限制);ABL开关13 ABL CON T ABL(自动亮度限制)控制值14 ABL GAIN 自动亮度控制增益15 ABL POIN T 自动亮度控制点16 ABL STAR ABL(自动亮度限制)起始值17 ADDRESS 地址18 ADJUSTMEN T 调整19 AF 自动频率控制状态20 AFC AFC;A FC环路增益;AFC开关;AFC模式21 AFC MODE EX T 自动频率控制外接模式22 AFC MODE TV自动频率控制电视模式23 AFF AFC关断24 AFT 自动频率微调 F V CO(图像中频压控振荡器)调整;中频VCO25 AFT/SKIP 自动微调/跳跃26 AFTO AFT输出27 AGC 自动增益控制;AGC自动/恒定;AGC起控点28 AGC - TAKE AGC起控点29 AIP 调整中频锁相环30 AKB 显像管暗平衡自动调整;AKB关断蓝截止31 AL 自动音量调整32 ALIGN; 调整33 ALIGNMENTS34 ALS 音频电平设置35 AMPLI50Hz 50Hz场幅调整36 AS 自动扫描37 AUDIO 伴音;音频38 AUTO FLESH 自动肤色校正39 AUTO SRCH自动搜索40 A V 音频/视频;视频设定;A V输入端子数41 A V MODE A V模式42 A V SHARPNESS A V锐度43 A V TINT A V色调44 A VI ONLY Y/YN 可选择一路A V或两路A V输入45 A V-MODE A V模式46 AX AGC删除47 B;B-显像管亮平衡蓝色调整48 B BIAS;B_;B CU T OFF 蓝偏置;显像管阿暗平衡蓝色调整49 B DRIVE(GAIN) 蓝色激励(增益);显像管亮平衡蓝色激励调整50 BLUE 蓝色51 BALANCE 平衡52 BAND MODE 波段控制模式53 BAND OUT 波段输出54 BASIC 基本(型)55 BASS 低音;副低音56 BB;BC;BCF;B - CO; 蓝枪截止点;显像管暗平衡蓝枪调整57 BCT;BCU T;BCUT OFF;B-58 CU TOFF59 BCW 亮度控制范围60 BD;BDR;B-DRIVE;BDRV; 蓝激励;显像管亮平衡蓝激励调整61 BDRY62 BEL;BELL;BELLFO;BELL FILTER SECA M钟型滤波器63 BG B.G伴音制式设置64 BG;B - GAIN 蓝激励;显像管亮平衡蓝激励调整65 BH童锁66 BK时钟67 BKP 消隐图像;消隐关断图像;消隐关断时的图像数据68 BL 平衡69 BALCK STR;BLACKSTRECH黑电平扩展70 BLACK STRETCH POINT 黑电平扩展点71 BLK SW 消隐开关72 BLOCK组件73 BLU;BLUE 蓝;蓝背景;蓝背景ON/OFF74 BLUE BACK MODE 蓝背景模式75 BLUE GAIN 蓝激励;显像管亮平衡蓝激励调整76 BOW 弓形77 BR 亮度;副亮度78 BR ABL TH亮度ABL阀值;ABL起控点调整79 BRAND 商标;厂标显示80 BRC 蓝枪截止点;显像管暗平衡蓝枪调整81 BRI亮度;副亮度82 BRI ABL TH亮度ABL阀值;ABL起控点调整83 BRI CE 亮度中心调值84 BRI MA;BRI MI亮度最大(最小)值85 BRIGHT; BRIGHT-NESS 亮度;副亮度86 BR T 亮度;框亮度数据(索尼)87 BR T ABL 亮度ABL(控制量)88 BR TC 副亮度中间值;亮度调整中心数据89 BR TN 最小亮度;副亮度最小值90 BR TS 亮度调整中心数据校正;副亮度校正91 BR TX 副亮度最大值92 BT 亮度93 BTSC BTSC制立体声94 BUS 总线95 BUS CONT OK总线控制正常96 BUS LINE OK 总线正常97 BUS OFF 总线关断98 B-Y BLACK OFFSET B-Y信号黑偏移量99 C.BLK 色度信号消隐100 CANCEL 清除101 C-B 显像管暗平衡蓝色调整102 CFO色度陷波器f o调整103 C-G 显像管暗平衡绿色调整104 CHINESE OSD中文屏显105 CHINESE TUNER 中国制式高频头106 SUB R-CU TOFF 在彩色降噪接通时的红枪截止点校正107 SUB SHARP;SUB-SHARTNESS 副锐度108 SUB TINT 副色调109 SUB-VOLUME 副音量110 SU PER WIDE GEOMETRY超宽屏幕几何失真111 SURROUND 环绕声112 SV4 4.43A V(视频)副清晰度(中心值)113 SX4 4.43副清晰度最大值114 SY;SYS;SYSTEM 制式;多制式系统115 SYN;SYNC 同步;合成器116 TC 梯形失真117 TCC 色调控制中心118 T-COLOR BA R 彩条信号119 TCW 色调控制范围120 TEB 文本显示亮度121 TEC 文本显示对比度122 TELETEX T 图文电视123 TEST PA TTERN 测试图124 TEST SIGNAL 测试信号125 TEXT CON TRAST 文本对比度126 TEXT.H;TEX T.V屏显水平(垂直)位置127 TEXT/MIX文本/混合128 TINT 色调129 TINTC 色调中心值130 TLT 倾斜失真(梯形失真)131 TMN;TMX色调控制最小(最大)值132 TN 高频头133 TNTC 副色调中间值134 TNTN;TN TX 副色调最小(最大)值135 TONE 音调136 TRAP 陷波137 TPC;TR;TRAP;TRP 梯形失真138 TRAPEZIUM;TRAPEZOID 梯形失真139 TRE;TREBLE 高音140 TSC 图文对比度141 TUNER 调谐器;高频头142 TV SY STEMS 电视制式143 TXCN;TXCX屏显对比度最小(最大)值144 TXH 屏显水平位置145 TXP;TXPIC 图文图像(对比度)146 TXT 文本;图文;屏显147 TYPE 类型148 UCBOW 上部偏中弓形失真149 UCC 对比度控制中心150 UCP 上角枕形失真151 UCW 单色控制范围152 UHF ONLY Y/N可选择一路UHF接收获全接收153 ULN 上部场线性154 UNKNOWN 不能确定155 UP 上156 UTIL T;UTL 上部倾斜失真(梯形失真)157 UV UHF/VHF158 UVG 用户可变y校正159 UYB;UYBOW 垂直上角弓形失真160 V AMPLITUDE 场幅161 V CEN TERING 场中心162 V COMP 场补偿163 V FREQUENCY 场频164 V LIN;V LNEARITY场线性165 V OU T PHASE50 50Hz场中心(场输出相位) 166 V POSI 场中心167 V SC;V S-CORRECTION场S校正168 V SHIFT 场中心169 V SIZE 场幅170 V25;V 50 音量调整20%(50%)位置音量数据值171 V60 60Hz场中心调节;60Hz场幅(飞利浦)172 V A;V-A场幅度;垂直孔阑补偿173 V AD 视频输出幅度174 V AG 对角失真(平行四边形失真)175 value 数值176 V AM;V-AMPL;V-AMPLITUDE 场幅177 V-ANG 场对角形失真178 V AP 场幅179 V A W 垂直孔阑白色180 V-BIAS 场偏置181 VBW 场消隐宽度控制182 VCD MD EX T 视频时的VCD(视频/色度/扫描)模式183 VCD MD TEX T 图文时的VCD(视频/色度/扫描)模式184 VCD MD TV TV时的VCD(视频/色度/扫描)模式185 V-CENTER 场中心186 VCO压控振荡器;38MHz中频振荡187 VCOMP 亮度变化引起的场幅失真校正188 V-COMPENSA TION 场补偿189 V-CORRECT 垂直校正;场线性校正190 VCP 垂直补偿;光栅亮度变化时,场幅校正设置191 VCX压控晶体振荡器自由振荡频率192 VENH 梳状滤波器垂直加强(轮廓校正)193 VER;VERSION 版本;类型194 VERT LINEARITY场线性调整195 VFQ;VFR 场频196 VH 场幅197 VID 视频;图像检波;视频识别模式198 V-ID SW 视频识别开关199 VIDEO 视频;视频输入设定(设定为3个)200 VIDEO H.CEN 行相位;行中心201 VIDEO LEVEL 视频电平202 VIF SY S中频设定203 VL;V-L 伴音限制;场线性204 VLB 场线性校正205 VLIN;V-LIN;V-LINEAR;VLN 场线性206 CHROMA GAIN 色度增益207 CHROMA TRA P FO 色度信号陷波频率208 CHROMA TRA P Q色度信号陷波Q值209 CLC 彩色控制中心;色度控制中心210 CLOCK时钟211 CMN;CMX 色度控制最小(最大)值212 CNP;CNR 光栅角部校正失真213 CNR GAIN 彩色降噪增益214 CN T 对比度215 CN T CE 对比度中心值216 CN T MA;CNT MI对比度最大(最小)值217 CNTC 对比度调整中间值;副对比度中间值218 CNTN;CNTX (副)对比度最小(最大)值219 CO443 PA L彩色(色度)中心220 COINCIDENTDET LEVEL 符合检测电平221 COL MA彩色(色度)最大值222 COLC N制副色度中间值;色度调整中间值223 COLN 副色度最小值224 COLOR 彩色;色度225 COLOR LIMIT LEVEL 色度限制电平226 COLOR LIMIT SW 色度限制切换227 COLOUR 彩色228 COLP PAL制色度中间值AL副色度中心值229 COLS SECAM色度中间值;SECA M副色度中间值230 COLX 副色度最大值231 COMB 梳状滤波器232 COMMUNICA TION 通讯233 CONNECTION 连接234 CON;CONT;CON TRAST 对比度;副对比度235 COOL 冷;白平衡冷色调236 COR;CO RINC 核化(降噪);核化降噪峰值237 CORPN;CP;C-P;CR 四角枕形失真238 C-R 显像管暗平衡红色调整239 CRH;CRL 设定字符高(低)240 CROSS HA TCH格子信号241 CSD字符的显示位置242 CSW 彩色开关243 S-SYSTEM 彩色制式244 CT 对比度;色度陷波(索尼)245 CUT-OFF 截止;显像管截止点调整(暗平衡调整)246 CV屏显垂直位置;CV/YC(复合视频信号/Y C信号)选择247 DA TA 数据248 DA TE 日期249 D-B 显像管亮平衡蓝色调整250 DC GREEN PAL 绿枪截止(显像管暗平衡)调整251 DC RED PAL 红枪截止(显像管暗平衡)调整252 DC TRAIN RA TE 直流补偿程度253 DEFECT MODULE 产生故障的电路组件254 DEGAU 消磁;消磁功能接通/断开255 DELTA COOL 偏冷色(白平衡)256 DELTA COOL BLUE(GREEN RED) 冷色调白平衡蓝(绿\红)数据257 DELTA WARM 偏暖色白平衡258 DELTA WARM BLUE(GREEN RED) 暖色调白平衡蓝(绿\红)数据259 DEMP FO去加重频率260 DIAGNOSE 故障自检(代码)261 DID 消磁关闭262 DIGI OSD;DIGITAL OSD 数字OSD(屏显)设定263 DIGITAL SCAN数字扫描264 DISPLA Y显示;屏显语言选择265 DK D/K伴音制式设置266 DL;DLT;DLY 延迟控制;延时267 DPC 枕形失真校正(东芝);动态图像ON/OFF(索尼)268 DPCS 50Hz/60Hz校正269 DPI;D-PIC 动态图像270 D-R 显像管亮平衡红色调整271 DRG SW 以红枪或绿枪为准(DRGSW用于转换显像管红绿枪,按遥控器电平增/减键在R、G(红、枪)之间转变)272 DRV CN T 激励控制273 DSHFT 直流电平移(水平静会聚微调)274 DT 延时275 DT BW 黑白延时276 DVM VM(速度调制)静噪失效277 EAST/WEST CO RNER 光栅四角调整278 EAST/WEST PARABOLA光栅左右枕形失真279 EAST/WEST TO P COMPENSA TION 光栅顶部补偿280 EAST/WEST TRAPEZIUM 光栅梯形失真281 EEPROM 电可檫可编程存储器282 EFFECT 效果283 EHH;EHV 高压对光栅行幅(场幅)的影响284 ENGLISH ONLY 仅有英文285 EQ+DOLBY 均衡器+杜比286 EQUALIZER 均衡器287 ER;ERR;ERRORS 故障;错误;故障自检代码288 ERC 误差计数;故障计数289 EURO A V 欧洲标准A V输入290 EVG 场保护启动291 EVOL 外接信号预置音量292 EW 光栅左右枕形失真293 EW-CORNER 光栅左右角部失真294 EW-PARABO;EW-PARABOLA光栅左右枕形失真295 F TRAP 陷波微调296 FAC 工厂297 FBP BL SW 行逆程脉冲消隐开关298 F-BW 强制黑白切换299 FEA TURE-BOX 特色电路组件300 FG P FM伴音(BG、I、DK制)预置音量301 FILT;FIL TER;FL T 滤波器302 FM 调频模拟伴音303 FM GAIN 调频伴音增益304 FM LEVEL 调频伴音电平305 FMA调频伴音衰减电平306 FORCED COLOUR 强制彩色307 FRAME 桢;框308 FRU、FRV、FRY U(V、Y)信号桢309 FSW 强制开关310 FU福字设定(康佳)311 FUNCTIONAL TEST 功能测试312 FVOL FM伴音音量预刻度313 G 绿;显像管亮平衡绿色调整314 G BIAS;G CUT OFF;G_ 显像管暗平衡绿色调整315 G DRIVE;G DRIVE GAIN 绿色激励(显像管亮平衡绿色调整)316 GAM;GAMMA Y校正317 GA TE PULSE 选通脉冲318 GB;GC;GCF;GCO;GCT;GCU T;GCU T OFF绿色截止点;显像管暗平衡绿色调整319 GD;GDR;GDRV 绿激励;显像管亮平衡绿色调整320 GENERAL 一般性的(调整)321 GEOMETRIC;GEOMETRY光栅几何失真322 GG;G-GAIN 绿增益;显像管亮平衡绿色调整323 GLOBAL 全球;全球立体声324 GRC 绿色截止点;显像管暗平衡绿色调整325 GREEN 绿326 GREEN GAIN 绿增益;显像管亮平衡绿色调整327 H AFC 行A FC(增益)328 H AMPLITUDE 行幅329 H BLANK L;H BLK L 行左消隐;左黑边调整330 H BLANK R;H BLK R 行右消隐;右黑边调整331 H BLK PHASE50 50Hz行消隐相位332 H CEN TER 50 50Hz行中心333 H FREQ 行频334 H PHASE;H PHASE SHIFT 航向位;行中心335 H POSI TION 行中心;(字符)水平位置336 H SHIFT 行中心337 H AMP H.AMP(行幅)338 HAFC 行A FC;AFC中心数据339 HALF TONE SW 半色调增益选择340 HBL;HBR 水平消隐左(右)宽度341 HBS 行消隐宽度ON/OFF342 HC 四角失真(飞利浦)343 HC;H-C;H-CENTER 行中心344 HCO 高压跟踪模式345 H-COMPENSA TION行补偿346 H-CORNER 行边角失真;角部枕形失真347 H-CORRECT 水平校正348 HCP 水平补偿;光栅屏幕亮度变化时,行幅校正设置349 HD 行中心(飞利浦)350 H-FRE 行频351 HI BLUE 显像管亮平衡蓝色调整352 HI GAIN高增益;增强接受设定(康佳)353 HI GREEN 显像管亮平衡绿色调整354 HIT高度;场幅355 HITS 60Hz场扫描场幅校正数据;50/60Hz场幅差异356 HOLD 保持357 HOR 水平;行;画中画左右对称(海信)358 HORIZONTAL POS50 50Hz场频行中心359 HOTEL 旅馆模式360 HOTEL CHANNEL 旅馆频道361 HOUT CLOCK SW 行输出时钟切换362 HP;H-PARAB 水平枕形失真;左右枕形失真363 H-PHA;H-PHASE 行相位;水平中心364 HPOS;H-POS;HPS 水平位置;行中心365 HR 屏显水平位置366 HS 旅馆模式(飞利浦)367 H-S;HSF;HSH;H-SHIFT 水平位置;行中心368 HSIZE;HSZ 行幅369 HT;H TILT;H TLHTR;H-TRA P;HTRP 几何失真;水平倾斜失真(梯形失真) 370 HTR;H-TRAP;H TRP 几何失真;水平倾斜失真(梯形失真)371 HVH;HVV 高压变动引起的行幅(场幅)变化补偿372 HW;H-W;H-WIDTH行幅373 I I伴音制式设置374 IF-FRE 中频频率375 IR-PLL 中频锁相环376 IGR IGR立体声;西德制式立体声377 INDEX 索引378 INTC 色调调整中心数据379 ITL 隔行扫描380 JSW 跳跃ON/OFF开关381 KARAOKE 卡拉OK382 KEY 梯形失真校正383 KEYS 60Hz梯形失真校正384 LA音频电平调整385 LAN;LANG 语言;屏显语言设定386 LANG/LOGO 语言/标志387 LANGUAGE 语言;菜单文字设定388 LBK 左消隐宽度389 LCB;LCBOW 下部偏中弓形失真390 LCP 下角枕形失真391 LEFT 左;画中画靠左边位置(海信)392 LEV 电平393 LIM 限幅;RGB限幅ON/OFF(索尼)394 LIN 线性;场线性395 LINE WIDTH行宽396 LLN 下部场线性397 LO BLUE;LO GREEN 暗平衡蓝色(绿色)调整398 LT1 亮度信号瞬态改善(L TI)方式1399 LTIL T;LTL 下部倾斜失真(梯形失真)400 LUM LINEAR 亮度信号线性401 LYB;LYBOW 垂直下角弓形失真402 M M伴音制式设置403 M00 模式数据(M表示模式数据,数字表示第几个模式数据)404 MAIN MENU 主菜单405 M-DSP 主屏幕显示位置水平方向406 VLIS 60Hz场线性407 VM 速度调制;VM(速度调制)电平;VM(速度调制)ON/OFF;伴音静音408 VM0 视频模式0;VCD(视频/色度/扫描)模式0409 VMC 距屏幕顶1/4~3/4区域进行线性调整;垂直S校正;垂直积分补偿410 VMH VM(速度调整)限幅器(高)411 VML VM(速度调整)限幅器(低)412 VOCAL CU T 消声413 VOF 场关断414 VOL 音量415 VOL32 音量32值设定416 VOLS SCAR T接口音量417 VOLUME-CON 音量控制418 VOM 音量输出增益419 VP;VPO S;VPOSI TION;VPS 场中心420 VS 场S校正(飞利浦)421 VS;V-S 场中心422 V-S.CORR;VSC;VSCO;VSCOR 场S校正423 VSC;V-SCROLL 垂直卷动(索尼\三星)424 VS-CORRECTION场S校正425 VSD场扫描关闭,进入水平一条亮线状态426 VSF;VSH;VSHFT;VSHIFT 场中心427 VSL;V-SLOPE 场线性;场线性对称点428 VSM50 场同步范围开关(场频50Hz时)429 VSW 视频静噪开关430 VSZ 场幅431 VX 场放大432 VZW 垂直变焦433 WARM (白平衡)暖色调434 WD窗口选择435 WDS 窗口选择436 W-H 加权437 WHI TE DRIVE 显像管亮平衡调整;白平衡激励调整438 WHI TE PEAK LIMI T 峰白限制439 WHI TE TONE 白色调;白平衡色温440 WID;WIDE 宽度;行幅441 WIDE PICTURE-MU TE 图像消隐开关442 WIDE P-MU TE STAR T 图像静噪开始443 WIDE P-MU TE STOP 图像静噪停止444 WIDE V-BLK STAR T 场消隐开始445 WIDE V-BLK STOP 场消隐停止446 WIDE V-BLK SW 场消隐宽度开关447 WIDS 60Hz行幅度448 WI P 划变449 WOOFER 低音扬声器450 WRP 写入位置451 WSP 划变速度452 XBS BASS 重低音453 XTL 晶振454 XVOL 外接预置音量455 Y亮度信号456 Y SUB 副对比度457 Y SUB CONTRAST 亮度信号副对比度458 Y BLK 亮度信号消隐459 Y-BOW 场弓形失真460 YC-AJ Y C调整461 Y-CI DELA Y Y-CI(亮度/色度改善)延时462 Y-DELA Y;YDL 亮度信号延迟463 Y-DL SW PAL NTSC PAL/NTSC亮度延迟464 YFI亮度信号滤波器调整465 YNR 亮度信号降噪466 ZOOM 变焦467 ZSW 变焦开关。

BT151中文资料_数据手册_参数

SYMBOL PARAMETER

CONDITIONS

MIN.

VDRM, VRRM Repetitive peak off-state

-

voltages

IT(AV) IT(RMS) ITSM

I2t dIT/dt IGM VGM VRGM PGM PG(AV) Tstg Tj

Average on-state current half sine wave; Tmb ≤ 109 ˚C

IL(Tj) IL(25 C) 3

BT145

2.5

2

1.5

1

0.5

0 -50

Fig.8.

0

50

100

150

Tj / C

Normalised latching current IL(Tj)/ IL(25˚C), versus junction temperature Tj.

IH(Tj) IH(25 C) 3

currents, f = 50 Hz; Tmb ≤ 109˚C.

VGT(Tj) 1.6 VGT(25 C)

BT151

1.4

1.2

1

0.8

0.6

0.4-50

0

50

100

150

Tj / C

Fig.6. Normalised gate trigger voltage VGT(Tj)/ VGT(25˚C), versus junction temperature Tj.

September 1997

3

Rev 1.200

Philips Semiconductors

Thyristors

Product specification

CY7C026AV-20AC资料

3.3V 4K/8K/16K x 16/18 Dual-Port Static RAMCY7C024AV/025AV/026AV CY7C0241AV/0251AV/036AVFeatures•True dual-ported memory cells which allowsimultaneous access of the same memory location •4/8/16K × 16 organization (CY7C024AV/025AV/026AV)•4/8K × 18 organization (CY7C0241AV/0251AV)•16K × 18 organization (CY7C036AV)•0.35-micron CMOS for optimum speed/power •High-speed access: 20 and 25 ns •Low operating power—Active: I CC = 115 mA (typical)—Standby: I SB3 = 10 µA (typical)•Fully asynchronous operation •Automatic power-down•Expandable data bus to 32/36 bits or more using Master/Slave chip select when using more than one device•On-chip arbitration logic•Semaphores included to permit software handshaking between ports•INT flag for port-to-port communication •Separate upper-byte and lower-byte control •Pin select for Master or Slave•Commercial and industrial temperature ranges •Available in 100-pin TQFPNotes:1.I/O 8–I/O 15 for x16 devices; I/O 9–I/O 17 for x18 devices.2.I/O 0–I/O 7 for x16 devices; I/O 0–I/O 8 for x18 devices.3.A 0–A 11 for 4K devices; A 0–A 12 for 8K devices; A 0–A 13 for 16K devices.4.BUSY is an output in master mode and an input in slave mode.R/W L OE LI/O 8/9L –I/O 15/17LI/O Control Address DecodeA 0L –A 11/12/13L CE L OE L R/W LBUSY L I/O ControlCE L Interrupt Semaphore ArbitrationSEM L INT L M/SUB LLB L I/O 0L –I/O 7/8LR/W R OE RI/O 8/9L –I/O 15/17RCE R UB RLB R I/O 0L –I/O 7/8RUB L LB LLogic Block DiagramA 0L –A 11/1213LTrue Dual-Ported RAM Array A 0R –A 11/12/13RCE R OE R R/W R BUSY R SEM RINT R UB R LB RAddress DecodeA 0R –A 11/12/13R[1][1][2][2][4][4]12/13/148/98/912/13/148/98/912/13/1412/13/14[3][3][3][3]Pin ConfigurationsNotes:5.A12L on the CY7C025AV.6.A12R on the CY7C025AV.Top View100-Pin TQFP100 9997989623142415960611213151416454039959417269108761127283029313235343637383367666465636268697075737472718988868785939284NCNCNCNCA5LA4LINT LA2LA0LLGNDINT RA0RA1L NCNCNCNCI/O10LI/O11LI/O15LV CCGNDI/O1RI/O2RV CC9091A3LM/SR I/O14LGNDI/O12LI/O13LA1RA2RA3RA4RNCNCNCNCI/O3RI/O4RI/O5RI/O6RNCNCNCNC18192021222324258382818079787776585756555453525143444546 47484950I/O9LI/O8LI/O7LI/O6LI/O5LI/O4LI/O3LI/O2LGNDI/O1LI/OLOELSEM LVCCCELUBLLBLNCA11LA1LA9LA8LA7LA6LI/O0RI/O7RI/O8RI/O9RI/O1RI/O11RI/O12RI/O13RI/O14RGNDI/O15RŒRRWRGNDSEMRCERUBRLBRNCA11RA1RA9RA8RA7RA6RA5RCY7C024AV (4K × 16)R/W L[5][6CY7C025AV (8K × 16)Notes:7.A 12L on the CY7C0251AV.8.A 12R on the CY7C0251AVC.Pin Configurations (continued)Top View100-Pin TQFP100 9997989623142415960611213151416454039959417269108761127283029313235343637383367666465636268697075737472718988868785939284NC NC NC NC A 5L A 4L INT L A 2L A 0L BUSY L GND INT R A 0R A 1L NC NC I/O 11L I/O 12L I/O 16L V CC GND I/O 1R I/O 2R V CC 9091A 3L M/S BUSY R I/O 15L GND I/O 13L I/O 14L A 1R A 2R A 3R A 4R NC NC NC NCI/O 3R I/O 4R I/O 5R I/O 6R NC NC18192021222324258382818079787776585756555453525143444546 47484950I /O 9LI /O 7LI /O 6LI /O 5LI /O 4LI /O 3LI /O 2LI /O 10LG N DI /O 1LI /O 0LO E LS E M LV C CC E LU B LL B LN C A 11LA 10LA 9LA 8LA 7LA 6LI/O 0R I /O 7RI /O 16RI /O 9RI /O 10RI /O 11RI /O 12RI /O 13RI /O 14RG N D I /O 15RO E RR W R G N D S E M R C E R U B R L B R N C A 11R A 10R A 9R A 8RA 7R A 6RA 5RCY7C0241AV (4K × 18)I/O 8L I/O 17L I/O 8R I/O 17RR /W L[8][7]1329291908485878688898382817678777980939495969798991005960616766646563626869707573747271NC NC NC A6L A5L A4L INTL A2L A0L GND M/S A0R A1R A1L A3L BUSYR INTR A2R A3R A4R A5R NC NC NCBUSYL 5857565554535251CY7C026AV (16K × 16)NC NC NC NC I/O10L I/O11L I/O15L I/O13L I/O14L GND I/O0R VCC I/O3R GND I/O12L I/O1R I/O2R I/O4R I/O5R I/O6R NC NC NC NCVCC 17161591012111314876451819202122232425I /O 9L I /O 8L I /O 7L I /O 6L I /O 5L I /O 4L I /O 0L I /O 2L I /O 1L V C C R W L U B L L B L G N D I /O 3L S E M L C E L A 113L A 12L A 11L A 10L A 9L A 8L A 7LO E L 3435364241394038374344455048494746A 6R A 7R A 8R A 9R A 10R A 11R C E R A 13R U B R G N D R W R G N D I /O 14R L B R A 12R O E R I /O 15R I /O 13R I /O 12R I /O 11R I /O 10R I /O 9R I /O 8R I /O 7R S E M R 3332313029282726CY7C0251AV (8K × 18)Pin Configurations (continued)Top View100-Pin TQFP 100 9997989623142415960611213151416454039959417269108761127283029313235343637383367666465636268697075737472718988868785939284NC NC NC A 5L A 4L INT L A 2L A 0L BUSY L GND INT R A 0R A 1L NC NC I/O 11L I/O 12L I/O 16L V CC GND I/O 1R I/O 2R V CC 9091A 3L R I/O 15L GND I/O 13L I/O 14L A 1R A 2R A 3R A 4R NC NC NCI/O 3R I/O 4R I/O 5R I/O 6R NC NC18192021222324258382818079787776585756555453525143444546 47484950I /O 9LI /O 7LI /O 6LI /O 5LI /O 4LI /O 3LI /O 2LI /O 10LG N DI /O 1LI /O 0LO E LS E M LV C CC E LU B LL B L A 11LA 10LA 9LA 8LA 7L A 6LI/O 0R I /O 7RI /O 16RI /O 9RI /O 10RI /O 11RI /O 12RI /O 13RI /O 14RG N D I /O 15RO E R R W R G N D S E M RC E RU B RL B RA 11RA 10RA 9R A 8RA 7RA 6RA 5RI/O 8L I/O 17L I/O 8R I/O 17RR /W LCY7C036AV (16K × 18)A 13L A 13R A 12LA 12RSelection GuideCY7C024AV/025AV/026AV CY7C0241AV/0251AV/036AV-20CY7C024AV/025AV/026AV CY7C0241AV/0251AV/036AV-25Unit Maximum Access Time 2025ns Typical Operating Current 120115mA Typical Standby Current for I SB1(Both ports TTL Level)3530mA Typical Standby Current for I SB3(Both ports CMOS Level)1010µAArchitectureThe CY7C024AV/025AV/026AV and CY7C0241AV/0251AV/ 036AV consist of an array of 4K, 8K, and 16K words of 16 and 18 bits each of dual-port RAM cells, I/O and address lines, and control signals (CE, OE, R/W). These control pins permit independent access for reads or writes to any location in memory. To handle simultaneous writes/reads to the same location, a BUSY pin is provided on each port. Two Interrupt (INT) pins can be utilized for port-to-port communication. Two Semaphore (SEM) control pins are used for allocating shared resources. With the M/S pin, the devices can function as a master (BUSY pins are outputs) or as a slave (BUSY pins are inputs). The devices also have an automatic power-down feature controlled by CE. Each port is provided with its own output enable control (OE), which allows data to be read from the device.Functional DescriptionThe CY7C024AV/025AV/026AV and CY7C0241AV/0251AV /036AV are low-power CMOS 4K, 8K, and 16K ×16/18 dual-port static RAMs. Various arbitration schemes are included on the devices to handle situations when multiple processors access the same piece of data. Two ports are provided, permitting independent, asynchronous access for reads and writes to any location in memory. The devices can be utilized as standalone 16/18-bit dual-port static RAMs or multiple devices can be combined in order to function as a 32/36-bit or wider master/slave dual-port static RAM. An M/S pin is provided for implementing 32/36-bit or wider memory applications without the need for separate master and slave devices or additional discrete logic. Application areas include interprocessor/multiprocessor designs, communications status buffering, and dual-port video/graphics memory. Each port has independent control pins: Chip Enable (CE), Read or Write Enable (R/W), and Output Enable (OE). Two flags are provided on each port (BUSY and INT). BUSY signals that the port is trying to access the same location currently being accessed by the other port. The Interrupt flag (INT) permits communication between ports or systems by means of a mail box. The semaphores are used to pass a flag, or token, from one port to the other to indicate that a shared resource is in use. The semaphore logic is comprised of eight shared latches. Only one side can control the latch (semaphore) at any time. Control of a semaphore indicates that a shared resource is in use. An automatic power-down feature is controlled independently on each port by a Chip Select (CE) pin.The CY7C024AV/025AV/026AV and CY7C0241AV/0251AV/ 036AV are available in 100-pin Thin Quad Plastic Flatpacks (TQFP).Write OperationData must be set up for a duration of t SD before the rising edge of R/W in order to guarantee a valid write. A write operation is controlled by either the R/W pin (see Write Cycle No. 1 waveform) or the CE pin (see Write Cycle No. 2 waveform). Required inputs for non-contention operations are summarized in Table1.If a location is being written to by one port and the opposite port attempts to read that location, a port-to-port flowthrough delay must occur before the data is read on the output; otherwise the data read is not deterministic. Data will be valid on the port t DDD after the data is presented on the other port. Read OperationWhen reading the device, the user must assert both the OE and CE pins. Data will be available t ACE after CE or t DOE after OE is asserted. If the user wishes to access a semaphore flag, then the SEM pin must be asserted instead of the CE pin, and OE must also be asserted.Pin DefinitionsLeft Port Right Port DescriptionCE L CE R Chip Enable.R/W L R/W R Read/Write Enable.OE L OE R Output Enable.A0L–A13L A0R–A13R Address (A0–A11 for 4K devices; A0–A12 for 8K devices; A0–A13 for16K).I/O0L–I/O17L I/O0R–I/O17R Data Bus Input/Output.SEM L SEM R Semaphore Enable.UB L UB R Upper Byte Select (I/O8–I/O15 for x16 devices; I/O9–I/O17 for x18devices).LB L LB R Lower Byte Select (I/O0–I/O7 for x16 devices; I/O0–I/O8 for x18devices).INT L INT R Interrupt Flag.BUSY L BUSY R Busy Flag.M/S Master or Slave Select.V CC Power.GND Ground.NC No Connect.InterruptsThe upper two memory locations may be used for message passing. The highest memory location (FFF for the CY7C024AV/41AV, 1FFF for the CY7C025AV/51AV, 3FFF for the CY7C026AV/36AV) is the mailbox for the right port and the second-highest memory location (FFE for the CY7C024AV/ 41AV, 1FFE for the CY7C025AV/51AV, 3FFE for the CY7C026AV/36AV) is the mailbox for the left port. When one port writes to the other port’s mailbox, an interrupt is generated to the owner. The interrupt is reset when the owner reads the contents of the mailbox. The message is user defined.Each port can read the other port’s mailbox without resetting the interrupt. The active state of the busy signal (to a port) prevents the port from setting the interrupt to the winning port. Also, an active busy to a port prevents that port from reading its own mailbox and, thus, resetting the interrupt to it.If an application does not require message passing, do not connect the interrupt pin to the processor’s interrupt request input pin.The operation of the interrupts and their interaction with Busy are summarized in Table2.BusyThe CY7C024AV/025AV/026AV and CY7C0241AV/0251AV/ 036AV provide on-chip arbitration to resolve simultaneous memory location access (contention). If both ports’ CEs are asserted and an address match occurs within t PS of each other, the busy logic will determine which port has access. If t PS is violated, one port will definitely gain permission to the location, but it is not predictable which port will get that permission. BUSY will be asserted t BLA after an address match or t BLC after CE is taken LOW.Master/SlaveA M/S pin is provided in order to expand the word width by configuring the device as either a master or a slave. The BUSY output of the master is connected to the BUSY input of the slave. This will allow the device to interface to a master device with no external components. Writing to slave devices must be delayed until after the BUSY input has settled (t BLC or t BLA), otherwise, the slave chip may begin a write cycle during a contention situation. When tied HIGH, the M/S pin allows the device to be used as a master and, therefore, the BUSY line is an output. BUSY can then be used to send the arbitration outcome to a slave.Semaphore OperationThe CY7C024AV/025AV/026AV and CY7C0241AV/0251AV/ 036AV provide eight semaphore latches, which are separate from the dual-port memory locations. Semaphores are used to reserve resources that are shared between the two ports. The state of the semaphore indicates that a resource is in use. For example, if the left port wants to request a given resource, it sets a latch by writing a zero to a semaphore location. The left port then verifies its success in setting the latch by reading it. After writing to the semaphore, SEM or OE must be deasserted for t SOP before attempting to read the semaphore. The semaphore value will be available t SWRD + t DOE after the rising edge of the semaphore write. If the left port was successful (reads a zero), it assumes control of the shared resource, otherwise (reads a one) it assumes the right port has control and continues to poll the semaphore. When the right side has relinquished control of the semaphore (by writing a one), the left side will succeed in gaining control of the semaphore. If the left side no longer requires the semaphore, a one is written to cancel its request.Semaphores are accessed by asserting SEM LOW. The SEM pin functions as a chip select for the semaphore latches (CE must remain HIGH during SEM LOW). A0–2 represents the semaphore address. OE and R/W are used in the same manner as a normal memory access. When writing or reading a semaphore, the other address pins have no effect.When writing to the semaphore, only I/O0 is used. If a zero is written to the left port of an available semaphore, a one will appear at the same semaphore address on the right port. That semaphore can now only be modified by the side showing zero (the left port in this case). If the left port now relinquishes control by writing a one to the semaphore, the semaphore will be set to one for both sides. However, if the right port had requested the semaphore (written a zero) while the left port had control, the right port would immediately own the semaphore as soon as the left port released it. Table 3 shows sample semaphore operations.When reading a semaphore, all sixteen/eighteen data lines output the semaphore value. The read value is latched in an output register to prevent the semaphore from changing state during a write from the other port. If both ports attempt to access the semaphore within t SPS of each other, the semaphore will definitely be obtained by one side or the other, but there is no guarantee which side will control the semaphore.Table 1.Non-Contending Read/WriteInputs OutputsCE R/W OE UB LB SEM I/O9–I/O17I/O0–I/O8OperationH X X X X H High Z High Z Deselected: Power-DownX X X H H H High Z High Z Deselected: Power-Down L L X L H H Data In High Z Write to Upper Byte Only L L X H L H High Z Data In Write to Lower Byte Only L L X L L H Data In Data In Write to Both BytesL H L L H H Data Out High Z Read Upper Byte OnlyL H L H L H High Z Data Out Read Lower Byte OnlyL H L L L H Data Out Data Out Read Both BytesX X H X X X High Z High Z Outputs DisabledH H L X X L Data Out Data Out Read Data in Semaphore FlagX H L H H L Data Out Data Out Read Data in Semaphore FlagH X X X L Data In Data In Write D IN0 into Semaphore FlagX X H H L Data In Data In Write D IN0 into Semaphore Flag L X X L X L Not AllowedL X X X L L Not AllowedTable 2.Interrupt Operation Example (assumes BUSY L = BUSY R = HIGH)[9]Left Port Right Port Function R/W L CE L OE L A0L–13L INT L R/W R CE R OE R A0R–13R INT R Set Right INT R Flag L L X FFF[12]X X X X X L[11] Reset Right INT R Flag X X X X X X L L FFF (or 1/3FFF)H[10] Set Left INT L Flag X X X X L[10]L L X1FFE (or 1/3FFE)X Reset Left INT L Flag X L L1FFE[12]H[11]X X X X X Table 3.Semaphore Operation ExampleFunction I/O0–I/O17 Left I/O0–I/O17 Right StatusNo action11Semaphore-freeLeft port writes 0 to semaphore01Left Port has semaphore tokenRight port writes 0 to semaphore01No change. Right side has no write access to semaphore Left port writes 1 to semaphore10Right port obtains semaphore tokenLeft port writes 0 to semaphore10No change. Left port has no write access to semaphore Right port writes 1 to semaphore01Left port obtains semaphore tokenLeft port writes 1 to semaphore11Semaphore-freeRight port writes 0 to semaphore10Right port has semaphore tokenRight port writes 1 to semaphore11Semaphore freeLeft port writes 0 to semaphore01Left port has semaphore tokenLeft port writes 1 to semaphore11Semaphore-freeNotes:9.See Functional Description for specific highest memory locations by device.10.If BUSY R=L, then no change.11.If BUSY L=L, then no change.12.See Functional Description for specific addresses by device.Maximum Ratings [13](Above which the useful life may be impaired. For user guide-lines, not tested.)Storage Temperature .................................–65°C to +150°C Ambient Temperature withPower Applied.............................................–55°C to +125°C Supply Voltage to Ground Potential...............–0.5V to +4.6V DC Voltage Applied toOutputs in High-Z State..........................–0.5V to V CC + 0.5V DC Input Voltage[14]...............................–0.5V to V CC + 0.5V Output Current into Outputs (LOW).............................20 mA Static Discharge Voltage.......................................... > 2001V Latch-up Current.................................................... > 200 mA Operating RangeRange Ambient Temperature V CC Commercial0°C to +70°C 3.3V ± 300 mV Industrial[15]–40°C to +85°C 3.3V ± 300 mVElectrical Characteristics Over the Operating RangeParameter DescriptionCY7C024AV/025AV/026AVCY7C0241AV/0251AV/036AVUnit -20-25Min.Typ.Max.Min.Typ.Max.V OH Output HIGH Voltage (V CC=3.3V) 2.4 2.4V V OL Output LOW Voltage0.40.4V V IH Input HIGH Voltage 2.0 2.0V V IL Input LOW Voltage0.80.8V I OZ Output Leakage Current–1010–1010µA I IX Input Leakage Current–1010–1010µAI CC Operating Current (V CC = Max., I OUT=0mA) Outputs Disabled Com’l.120175115165mA Ind.[15]135185mAI SB1Standby Current (Both Ports TTL Level)CE L & CE R≥ V IH, f = f MAX Com’l.35453040mA Ind.[15]4050mAI SB2Standby Current (One Port TTL Level) CE L| CE R≥ V IH, f = f MAX Com’l.751106595mA Ind.[15]75105mAI SB3Standby Current (Both Ports CMOS Level)CE L & CE R≥ V CC−0.2V, f = 0Com’l.1050010500µA Ind.[15]10500µAI SB4Standby Current (One Port CMOS Level)CE L | CE R≥ V IH, f = f MAX[16]Com’l.70956080mA Ind.[15]7090mACapacitance[17]Parameter Description Test Conditions Max.UnitC IN Input Capacitance T A = 25°C, f = 1 MHz,V CC = 3.3V 10pFC OUT Output Capacitance10pF Notes:13.The Voltage on any input or I/O pin can not exceed the power pin during power-up.14.Pulse width < 20 ns.15.Industrial parts are available in CY7C026AV and CY7C036AV only.16.f MAX = 1/t RC = All inputs cycling at f = 1/t RC (except output enable). f = 0 means no address or control lines change. This applies only to inputs at CMOS level standby I SB3.17.Tested initially and after any design or process changes that may affect these parameters.AC Test Loads and Waveforms3.0V GND90%90%10%3ns3ns10%ALL INPUT PULSES(a)Normal Load (Load 1)R1=590Ω3.3VOUTPUT R2=435ΩC =30pFV TH =1.4VOUTPUTC =30pF(b)Thévenin Equivalent (Load 1)(c)Three-State Delay (Load 2)R1=590ΩR2=435Ω3.3VOUTPUTC =5pFR TH =250Ω≤≤including scope and jig)(Used for t LZ , t HZ , t HZWE , and t LZWE Switching Characteristics Over the Operating Range [18]Parameter DescriptionCY7C024AV/025AV/026AV CY7C0241AV/0251AV/036AV Unit-20-25Min.Max.Min.Max.Read Cycle t RC Read Cycle Time 2025ns t AA Address to Data Valid2025ns t OHA Output Hold From Address Change 33ns t ACE [19]CE LOW to Data Valid 2025ns t DOEOE LOW to Data Valid 1213ns t LZOE [20, 21, 22]OE Low to Low Z 33ns t HZOE [20, 21, 22]OE HIGH to High Z 1215ns t LZCE [20, 21, 22]CE LOW to Low Z 33ns t HZCE [20, 21, 22]CE HIGH to High Z 1215ns t PU [22]CE LOW to Power-Up 0ns t PD [22]CE HIGH to Power-Down 2025ns t ABE [19]Byte Enable Access Time2025nsWrite Cycle t WC Write Cycle Time 2025ns t SCE [19]CE LOW to Write End 1520ns t AW Address Valid to Write End 1520ns t HA Address Hold From Write End 00ns t SA [19]Address Set-up to Write Start 00ns t PWE Write Pulse Width 1520ns t SDData Set-up to Write End1515nsNotes:18.Test conditions assume signal transition time of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specifiedI OI /I OH and 30-pF load capacitance.19.SCE time.20.At any given temperature and voltage condition for any given device, t HZCE is less than t LZCE and t HZOE is less than t LZOE .21.Test conditions used are Load 3.22.This parameter is guaranteed but not tested. For information on port-to-port delay through RAM cells from writing port to reading port, refer to Read Timingwith Busy waveform.Data Retention ModeThe CY7C024AV/025AV/ 026AV and CY7C0241AV/ 0251AV/036AV are designed with battery backup in mind. Data retention voltage and supply current are guaranteed over temperature. The following rules ensure data retention:1.Chip Enable (CE) must be held HIGH during data retention, within V CC to V CC – 0.2V.2.CE must be kept between V CC – 0.2V and 70% of V CC during the power-up and power-down transitions.3.The RAM can begin operation >t RC after V CC reaches the minimum operating voltage (3.0V).Notes:23.For information on port-to-port delay through RAM cells from writing port to reading port, refer to Read Timing with Busy waveform.24.Test conditions used are Load 2.25.t BDD is a calculated parameter and is the greater of t WDD –t PWE (actual) or t DDD –t SD (actual).26.CE = V CC , V in = GND to V CC , T A = 25°C. This parameter is guaranteed but not tested.t HDData Hold From Write Endns t HZWE [21, 22]R/W LOW to High Z 1215ns t LZWE [21, 22]R/W HIGH to Low Z3ns t WDD [23]Write Pulse to Data Delay4550ns t DDD [23]Write Data Valid to Read Data Valid 3035ns Busy Timing [24]t BLA BUSY LOW from Address Match 2020ns t BHA BUSY HIGH from Address Mismatch 2020ns t BLC BUSY LOW from CE LOW 2020ns t BHC BUSY HIGH from CE HIGH 1717ns t PS Port Set-up for Priority 55ns t WB R/W HIGH after BUSY (Slave)00ns t WH R/W HIGH after BUSY HIGH (Slave)1517ns t BDD [25]BUSY HIGH to Data Valid 2025ns Interrupt Timing [24]t INS INT Set Time 2020ns t INR INT Reset Time2020ns Semaphore Timingt SOP SEM Flag Update Pulse (OE or SEM)1012ns t SWRD SEM Flag Write to Read Time 55ns t SPS SEM Flag Contention Window 55ns t SAASEM Address Access Time2025nsSwitching Characteristics Over the Operating Range (continued)[18]Parameter DescriptionCY7C024AV/025AV/026AV CY7C0241AV/0251AV/036AV Unit -20-25Min.Max.Min.Max.TimingParameter Test Conditions [26]Max.Unit ICC DR1@ VCC DR = 2V50µAData Retention Mode3.0V3.0VV CC > 2.0VV CC to V CC –0.2VV CCCEt RCV IHSwitching WaveformsNotes:27.R/W is HIGH for read cycles.28.Device is continuously selected CE = V IL and UB or LB = V IL . This waveform cannot be used for semaphore reads.29.OE = V IL .30.Address valid prior to or coincident with CE transition LOW.31.To access RAM, CE = V IL , UB or LB = V IL , SEM = V IH . T o access semaphore, CE = V IH , SEM = V IL .t RCt AAt OHADATA VALIDPREVIOUS DATA VALIDDATA OUTADDRESSt OHARead Cycle No.1 (Either Port Address Access)[27, 28, 29]t ACEt LZOEt DOEt HZOEt HZCEDATA VALIDt LZCEt PUt PDI SBI CCDATA OUTOECE and LB or UBCURRENTRead Cycle No.2 (Either Port CE/OE Access)[27, 30, 31]UB or LBDATA OUTt RCADDRESSt AAt OHACEt LZCEt ABEt HZCEt HZCEt ACE t LZCERead Cycle No. 3 (Either Port)[27, 29, 30, 31]Notes:32.R/W must be HIGH during all address transitions.33. A write occurs during the overlap (t SCE or t PWE ) of a LOW CE or SEM and a LOW UB or LB.34.t HA is measured from the earlier of CE or R/W or (SEM or R/W) going HIGH at the end of write cycle.35.If OE is LOW during a R/W controlled write cycle, the write pulse width must be the larger of t PWE or (t HZWE + t SD ) to allow the I/O drivers to turn off and data to be placed onthe bus for the required t SD . If OE is HIGH during an R/W controlled write cycle, this requirement does not apply and the write pulse can be as short as the specified t PWE .36.To access RAM, CE = V IL , SEM = V IH .37.To access upper byte, CE = V IL , UB = V IL , SEM = V IH .T o access lower byte, CE = V IL , LB = V IL , SEM = V IH .38.Transition is measured ±500 mV from steady state with a 5-pF load (including scope and jig). This parameter is sampled and not 100% tested.39.During this period, the I/O pins are in the output state, and input signals must not be applied.40.If the CE or SEM LOW transition occurs simultaneously with or after the R/W LOW transition, the outputs remain in the high-impedance state.Switching Waveforms (continued)t AWt WCt PWE t HDt SDt HACER/WOEDATAOUTDATA INADDRESSt HZOE t SAt HZWE t LZWEWrite Cycle No.1: R/W Controlled Timing [32, 33, 34, 35][38][38][35][36, 37]NOTE 39NOTE 39t AWt WCt SCE t HDt SDt HACER/WDATA INADDRESSt SAWrite Cycle No. 2: CE Controlled Timing [32, 33, 34, 40][36, 37]Notes:41.CE = HIGH for the duration of the above timing (both write and read cycle).42.I/O 0R = I/O 0L = LOW (request semaphore); CE R = CE L = HIGH.43.Semaphores are reset (available to both ports) at cycle start.44.If t SPS is violated, the semaphore will definitely be obtained by one side or the other, but which side will get the semaphore is unpredictable.Switching Waveforms (continued)t SOPt SAAVALID ADRESS VALID ADRESSt HD DATA IN VALID DATA OUT VALIDt OHAt AWt HAt ACEt SOPt SCEt SDt SAt PWEt SWRDt DOEWRITE CYCLEREAD CYCLEOER/WI/O 0SEMA 0–A 2Semaphore Read After Write Timing, Either Side [41]MATCHt SPSA 0L –A 2LMATCHR/W L SEM LA 0R –A 2RR/W R SEM RTiming Diagram of Semaphore Contention [42, 43, 44]。

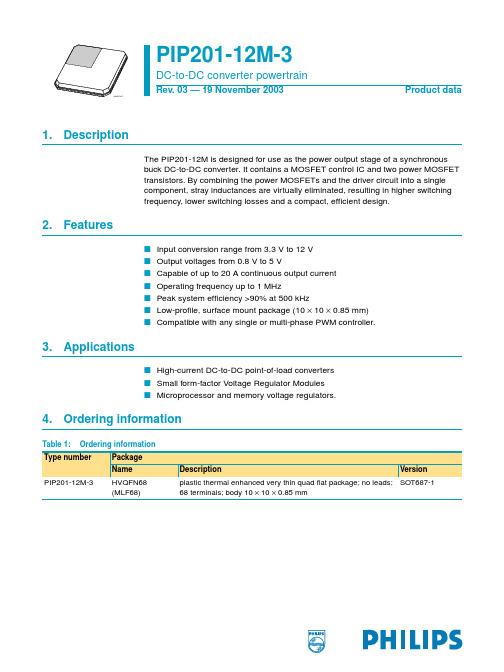

PIP201-12M-3中文资料