ASM51中文资料

51做的变频器资料,真牛

Application Note, V 2.0, Sept. 2005AP0803620XC866Optimized Space Vector Modulation and Over-modulation with the XC866MicrocontrollersXC866Revision History: 2005-09V 2.0 Previous Version: -Page Subjects (major changes since last revision)Many Updated for the XC866SW Updated for the XC866, Uses DAvE and C/Assembly mixController Area Network (CAN): License of Robert Bosch GmbHIntroduction1 IntroductionThis Application Note shows how the CAPCOM6 module found in many Infineon 8, 16 and 32-bit microcontrollers can be used to implement space vector modulation for three-phase voltage control inverter applications. A simple algorithm for overmodulation is also demonstrated. The alogorithms of this application note are implemented on the Infineon XC866 8051 based 8-bit microcontroller.Space Vector Modulation (SVM) is a method of producing 3-Phase sinusoidal voltages. The primary use for SVM is in motor control applications (mainly for induction and brushless DC motors). However SVM can also be used in Uninterruptible Power Supply (UPS) applications. SVM is popular because it generates higher voltages with low total harmonic distortion than traditional sinusoidal PWM techniques. Another advantage of SVM is that it works very well with field oriented (vector control) schemes for motor control.Figure 1 shows a typical motor control application where this Application Note could be useful.Figure 1 Typical Motor Control ApplicationSinusoidal Voltage Generation & Capture/Compare Units2 Sinusoidal Voltage Generation & Capture/CompareUnitsThe capture/compare units of Infineon 8, 16 & 32-bit microcontrollers (CAPCOM6) are designed to control many types of motors. For controlling 3-phase motors, the capture/compare unit can be used to generate the 6 PWM signals needed to drive a 3-phase inverter, including the necessary dead-time needed to eliminate shoot-through current on each phase.PWM can be used to create a sinusoidal voltage by creating a fixed frequency signal and adjusting the duty cycle. If the duty cycle varies sinusoidally, so will the output voltage. It is always assumed that the inductance of the motor will filter the PWM into a smooth signal as shown in Figure 2.Capture/Compare units are designed to create variable duty cycle PWM signals. Actually it is only the “compare” feature of a Capture/Compare unit that is used for PWM generation. The Capture/Compare unit contains a timer and several compare registers. When the timer value is the same as the compare register value, an output pin is either pulled high or low. So the duty cycle of the output signal follows the compare value linearly. The CAPCOM6 unit has 3 compare registers and a timer that can count up from 0 to any specified 16-bit “period” value. When the timer reaches the period value, it reverses direction and counts down to 0. This is useful for generatingcenter aligned PWM as shown in Figure 3.Sinusoidal Voltage Generation & Capture/Compare UnitsFigure 3 Center Aligned PWM Produced the CAPCOM6 UnitTo aid in 3-phase inverter control, the CAPCOM6 modules are capable of producing 6 compare outputs. Fore each of the 3 Compare Channels there are 2 output pins. The pins are often labeled CCx and COUTx (where x = 0, 1, 2). The polarity of each of the six pins is individually programmable. In addition to this, a programmable amount dead-time can be automatically inserted to delay the passive to active transition of both pins. This prevents shoot-through current which can destroy the inverter. Figure 4 shows how a single CCx and a COUTx pin can be used to control one phase of an inverter.Figure 4 Dead-Time Generation (CCx and COUTx with opposite polarity)Methods for Producing Sinusoidal Voltages 3 Methods for Producing Sinusoidal VoltagesThe following sections describe different methods of generating three phase sinusoidal voltages. Section 3.1 briefly describes a simple method for generating sinusoidal voltages using sinusoidal duty cycles. This method has been around for quite some time and has been the subject of other application notes. The biggest disadvantage to this method of voltage generation is that the maximum amplitude of the fundamental frequency of the generated line-to-line voltage is only about 86% of the inverter DC rail voltage.Section 3.2 describes the theory behind SVM. SVM is a method of sinusoidal voltage generation which generates voltages whose amplitude of the fundamental frequency of the line-to-line voltage is equal to the full DC rail voltage. The total harmonic distortion of SVM is also less.Section 3.3 describes over-modulation. Over-modulation is a way of increasing the amplitude of the fundamental frequency even higher (to about 1.12 times the rail voltage). Unfortunately over-modulation introduces more low order harmonics and increases the total harmonic distortion.3.1 Sinusoidally Weighted PWM (SWPWM)One simple way to create three phase sinusoidal voltages is to create a signal which has a very high constant frequency (compared to the frequency of the desired sinusoid) and a sinusoidally weighted duty cycle. This method of sinusoidal PWM will be referred to as SWPWM. SWPWM can be implemented very simply by placing sinusoidally weighted values into the three compare registers of the CAPCOM6 module. The CAPCOM6 module can then be used to control the 6 transistors that make up the inverter.SWPWM has the advantage of requiring very little calculation (assuming the appropriate look-up tables are used). Each of the three phases can be made to generate a sinusoid which is 120º out of phase. The sinusoidal phase voltages generate sinusoidal line-to-line voltages and sinusoidal line-to-neutral voltages when connected to a balanced star connected load as shown in Figure 5. Scaling the voltages can be done easily with a multiply, or through some trigonometric tricks.It should be noted that phase voltage is the voltage at one motor terminal measured with respect to the inverter negative rail voltage. Line-to-line voltage is the voltage at one motor terminal measured with respect to another terminal. Line-to-neutral voltage is the voltage at one motor terminal measured with respect to the neutral (center of the star connected load).Methods for Producing Sinusoidal VoltagesThe major disadvantage to this method of sinusoid generation is that the magnitude of the fundamental frequency of the line-to-line voltage is only ~86.6% of the inverter rail voltage.Figure 6 shows a frequency spectrum plot of the generated line-to-line voltages when creating this type of sinusoid. Notice that in addition to the fundamental frequency, the switching frequency (~20 kHz) harmonics also have a significant magnitude. ArrayFigure 5 Sinusoidal PWM values produce sinusoidalMethods for Producing Sinusoidal Voltages3.2 Space Vector Modulation (SVM)SVM is a more sophisticated PWM method which provides a higher voltage to the motor (with lower total harmonic distortion). Consider the three phase inverter of Figure 7. Note that whenever transistor A+ is on, transistor A- must be off, and visa versa, to prevent damaging shoot-through current. This makes it easy to adopt a simple notation for describing the state of the inverter. For example, the state when transistors A+, B-, and C- are “on” (and of course A-, B+, and C+ are “off”) can be represented with the notation (+, -, -). The state where transistors A-, B+, and C- areon is denoted by (-, +, -).Methods for Producing Sinusoidal VoltagesUsing this notation, consider the following sequence of states:(+, -, -), (+, +, -), (-, +, -), (-, +, +), (-, -, +), (+, -, +)Running the inverter through this switching sequence will produce the line-to-neutral voltages shown in Figure 8. This mode of operation is called “six-step mode”. Operating in six-step mode allows you to use the full capabilities of the inverter. If you were to perform an FFT on the line-to-line voltages produced in six-step mode, you would find that the amplitude of the fundamental frequency is actually greater than the inverter rail voltage. Unfortunately six-step mode also creates high magnitude low order harmonics which cannot be filtered by the motor’s inductance.Space vector modulation is based on six-step mode, but smoothes out the steps through some sophisticated averaging techniques. For example, if a voltage is required that is between two step voltages, the corresponding inverter states can be activated in such a way that the average of the step voltages produces the desired output. To develop the equations needed to generate this averaging effect, the problem is transformed into an equivalent geometrical problem. The first step in this re-definition is to transform the inverter voltages of six-step mode into space vectors. Space vectors are similar to phasors in that they are denoted by a magnitude and an angle. It is important to note that space vectors are not phasors. A Phasor is used to represent something that varies sinusoidally in time. A space vector is used to represent something that varies sinusoidally in space with respect to an angle. Forthis reason space vectors are sometimes referred to as space phasors.Methods for Producing Sinusoidal VoltagesIn general, any three time varying quantities, which always sum to zero and are spatially separated by 120º can be expressed as a space vector. Array Figure 8 Line-to-Neutral Voltages in Six-Step ModeSince the three line-to-neutral voltages sum to zero, they can easily be converted into a space vector (u s) using the following transformation:u s = V an(t) e j0 + V bn(t) e j2π/3 + V cn(t) e-j2π/3Since the components of space vectors are projected along constant angles (0, 2π/3,and -2π/3), it is easy to graphically represent a space vector as shown in Figure 9.Methods for Producing Sinusoidal VoltagesUsually, when creating space vectors, the three time-varying quantities are sinusoids of the same amplitude and frequency that have 120º phase shifts. When this is the case, the space vector at any given time maintains its magnitude. As time increases, the angle of the space vector increases, causing the vector to rotate with frequency equal to the frequency of the sinusoids.If the voltages of Figure 8 are converted into a space vector and plotted on the complex plane, it can be seen that the space vector takes on one of 6 distinct angles as time increases (instead of rotating smoothly as it would if the voltages were pure sinusoids). Figure 10 shows the values that the space vector assumes as time increase.The goal of space vector modulation is to generate the appropriate PWM signals so that any vector (u s) can be produced. Consider a space vector voltage u s located in the sector defined by u1 and u2. We can approximate u s by applying u1 for a percentage of time (t a) and u2 for a percentage of time (t b) such that:t a*u1 + t b*u2 = u sThis leads to the following formulas for t a and t b:t b = 2U(3-½)sin(α) where U = |u s| (Modulation Index)t a = U[cos(α) – (3-½)sin(α)] α = ∠u sMethods for Producing Sinusoidal VoltagesSo given a space vector of angle α (in sector 0) and modulation index U, the approximation can be constructed by applying vectors u 1 and u 2 for percentage of times t a and t b , respectively. Graphically this is represented in Figure 11. If the vector is in another sector, it can be rotated by a multiple of π/3 radians until it is in sector 0. The times can be calculated and then applied to the appropriate inverter states.Figure 10Space Vectors of Line-to-Neutral Voltages in Six-Step ModeFigure 11Approximation of the Space Vector u s by t a and t bLike many other types of PWM, space vector modulation uses pulses of constant frequency (carrier frequency) with variable duty cycle. The carrier frequency is often chosen so that it is high enough to be out of the audible range and produces littleMethods for Producing Sinusoidal Voltages current ripple, but not so high as to create excessive switching losses. The period of the carrier will be called T0.To approximate the u s in Figure 11, the inverter state that corresponds to u1 should be active for t a*T0 seconds, and the inverter state that corresponds to u2 should be active for t b*T0 seconds. When the modulation index is sufficiently small ( less than ½(3½)), the sum of t a and t b will be less than one. This means that t a*T0 + t b*T0 is less than T0. So for the left over time no voltage should be applied to the motor. The “left over” time will be referred to as t0. To be more formal:t0 = T0 (1– t a – t b)There are two ways to apply no voltage to the motor. The first way is to simply connect all three phases to the negative rail of the inverter. This will be called inverter state 0 and the corresponding switching pattern is (-, -, -). The second way to apply no voltage to the motor is to connect all three phases to the positive rail of the inverter. This will be called inverter state 7 and the corresponding switching pattern is (+, +, +). So, to approximate the voltage u s during the PWM carrier period, the pulses and timing shown in Figure 12 could be used. To obtain a better total harmonic distortion, a slightly different method of applying the switching states can be used. If the t0 time is split in half and applied at the beginning and the end of T0, then a more symmetric distribution of pulses can be generated. This method is known as symmetric or center-aligned space vector modulation. Figure 13 shows how symmetric space vector modulation is implemented over two consecutive carrier periods.Methods for Producing Sinusoidal VoltagesFigure 12Asymmetric PWM for SVMFigure 13SVM using Symmetric PWMMethods for Producing Sinusoidal VoltagesThe pulses shown in Figure 13 are very similar to those shown in Figure 3, and can be easily generated using the CAPCOM6 module. As shown in Figure 13, the switching frequency is 1/(2*T0).When the modulation index exceeds ½(3½), the value of t0 can become negative (depending on the angle). Since it is not physically possible to apply one of the zero vectors for negative time, the maximum modulation index for space vector modulation is approximately 0.866. Graphically, this means that for space vector modulation to work properly, the magnitude of the reference space vector, u s, must be small enough to ensure that the vector is totally contained inside the hexagon shown in Figure 10. When symmetric space vector modulation is implemented with a modulation index of 0.866, the ideal phase voltage (after filtering by the motor) as shown in Figure 14 is generated. The phase voltage of Figure 14 has the same shape as the compare values that should be used. These unusual voltages create sinusoidal line-to-neutral voltages (as expected) and sinusoidal line-to-line voltages are also generated.Methods for Producing Sinusoidal VoltagesAs shown in Figure 14, SVM can create sinusoidal line-to-line voltages which have amplitudes equal to the inverter rail voltage, even though the modulation index is only 0.866. SVM has also been proven to produce lower current harmonics and torque ripple than SWPWM. Figure 15 shows the frequency spectrum of the line-to-line voltage of a SVM simulation with modulation index of approximately 0.866. As Figure 15 shows, the magnitude of the fundamental frequency is higher and the magnitude ofthe switching frequency is lower than Figure 6.Methods for Producing Sinusoidal Voltages3.3 Over-modulationIt has been proven that SVM can produce higher amplitude voltages than SWPWM, even if the modulation index is limited to 0.866. There are several techniques that can be used to extend this modulation index range. These techniques are referred to as over-modulation.Figure 16 shows a graphical representation of the problem. In Figure 16, sector 0 from the hexagon of Figure 10 is shown. Over-modulation is needed when the modulation index (the length of the reference space vector, u s) causes the head of the vector to belocated outside of the hexagon.Methods for Producing Sinusoidal VoltagesIn Figure 16, t 0 will only become negative if α1 < α < α2. A simple method of overmodulation is based on the angle, α, of the reference vector u s , as shown in Table 1.Figure 16 Graphic Depiction of a Space Vector with U > 0.866Table 1Angle and Magnitude to use for Over-modulation Angle of u SαLength of u S Modulation IndexAngle to use for SVMα2 < α < α1 U α α1 < α < π/6 U α1 π/6 < α < α2 Uα2Methods for Producing Sinusoidal VoltagesWhen α is less than α1, space vector modulation can be performed as usual using U and α. Since the head of u s is inside the hexagon, t0 will be greater than zero and everything will work properly. When α is between α1 and π/6, t0 will be less than zero. To avoid this, SVM can be performed using α1 and U. This will yield a t0 of zero. When α is between π/6 and α2, again, t0 will be less than zero. To avoid this, SVM can be performed with U and α2. Once α is greater than α2, SVM can be performed normally again with α and U.This method of over-modulation will obviously not produce line-to-line and line-to-neutral voltages which are as ‘clean’ as normal space vector modulation, but it will allow the modulation index to exceed 0.866. If the frequency spectrum of the PWM is analyzed then it can be seen that the fundamental frequency does increase beyond what is capable using just SVM. Of course, the total harmonic distortion will increase. When the modulation index reaches 1.000, over-modulation will produce signals equivalent to six-step mode. In six-step mode the magnitude of the fundamental frequency of the line-to-line voltage is ~112% of the inverter rail voltage.The values of α1 and α2 can be determined by examining Figure 16:δ = acos(½(3½)/U)α1 = π/6 - δ whereα2 = π/6 + δFigure 17 shows the magnitude of the fundamental frequencies produced using SVM, over-modulation and SWPWM.Methods for Producing Sinusoidal VoltagesFigure 17 Fundamental Frequency of Line-to-Line VoltagesMicrocontroller Implementation of SVM 4 Microcontroller Implementation of SVMMicrocontroller implementation of SVM and over-modulation can be very difficult. The SVM equations can be complicated, and over-modulation adds to the complexity. Proper scaling variables can make the computations much easier. Section 4.1 describes the variable scaling and resolution used for a SVM and over-modulation implementation using the Infineon XC866 8051 based 8-bit microcontroller. An optimized flow chart for SVM and over-modulation is also given.There are several implementation options which effect SVM performance and CPU load. Section 4.2 also discusses these options and possible trade-offs a designer should consider.Section 4.3 shows the results of the SVM and over-modulation implementation with the XC866. Conclusions are also given.4.1 Variable Scaling and Resolution and Software OptimizationTo implement SVM, the microcontroller must receive (or perhaps even generate) a reference space vector. It is usually convenient if the space vector is given in terms of a magnitude (U) and an angle (α). Given U and α the switching times can be calculated by the formulas:t b = 2U(3-½)sin(α)t a = U[cos(α) – (3-½)sin(α)]t0 = T0 – t a - t bThe first step should be to decide on a switching frequency. In many cases, PWM frequencies above 20 kHz are considered to be ideal. Since the CAPCOM6 unit will operate as an up/down counter, this means that the timer period value should be above 40 kHz.To keep the calculations simple for an 8-bit microcontroller, T0 should be represented as an 8-bit value. This means that the period value for the CAPCOM6 Timer (Timer 12) should be set to 0x00FF. The XC866 operating from the internal oscillator and at the maximum PLL factor runs at 26.67MHz. So setting up the CAPCOM6 Timer 12 in symmetric PWM mode with a period value of 0x00FF and a divide by 2 pre-scaler will enable 26 kHz PWM.It is also convenient if U is scaled to be an 8-bit value. U is a “per unit” value which means that it is always between zero and one, so the resolution of U will be 1/255 or 0.00392.Microcontroller Implementation of SVMSince the equations for t a, t b, and t0 are only valid for α between 0 and π/3, it would be easier if α is represented by an 11-bit value. If the most significant 3 bits can be used to indicate the sector, the least significant 8-bits can contain the angle within the sector with a resolution of π/765 radians or 0.235 degrees. This allows the formulas for t a, t b, and t0 to be valid for any α as long as only the low byte is used.A look-up table can be used for sine and cosine so that t a and t b can be calculated, but it would require less computation if the values of t a and t b for U = 1.0 (0xFF in fixed point) are stored in look-up tables. The values can then be looked-up and scaled for the appropriate value of U. If one creates a table of t a and t b for the 255 different values of α for the case when U = 1, it can be easily seen that the table for t a is exactly the same as the table for t b except in reverse. This means that only one table is needed. Table 2 shows the digital representation of the variables needed for SVM and over-modulation.Table 2 Representation of Variables needed for SVM and Over-modulationVariable DigitalRepresentation Engineering UnitResolutionCommentsU (|u s|)8-bit value(0x00 – 0xFF)1/255(~0.00392)Input Variableα(∠u s)11-bit value(0x0000 – 0x05FF)π/765 radians(~0.235 degrees)Bits 0-7 contain α, Bits 8– 10 contain sector (inputvariable)T08-bit value(0x00 – 0xFF) CCU timer resolution(100 ns)~19.6 kHz CarrierFrequency (fixed)t b8-bit value(0x00 – 0xFF) CCU timer resolution(100 ns)Stored in a tableTable contains t b forU = 1.0 (0xFF)t a8-bit value(0x00 – 0xFF) CCU timer resolution(100 ns)Stored in a tablet b table is used in reverset08-bit value(0x00 – 0xFF) CCU timer resolution(100 ns)Calculatedt0 = ~(U*t a+U*t b)/256α1 and α28-bit values(0x00 – 0xFF)π/765 radians(~0.235 degrees)Calculated as neededfrom δThe CAPCOM6 unit relieves the CPU of much of the computational work required for symmetric PWM generation. From Figure 13, the relationship between the compare values and t a, t b, and t0 can be determined. Table 3 shows how the compare valuesMicrocontroller Implementation of SVM for phases A, B, and C can be chosen based on the sector in which the reference vector is located.Table 3 Compare Values for Symmetric SVMSector Phase A CompareValue Phase B CompareValuePhase C Compare Value0 ½ t0 ½t0 + t a T0 – ½ t01 ½ t0 + t b ½t0T0 – ½ t02 T0 – ½ t0 ½t0 ½t0 + t a3 T0 – ½ t0 ½t0 + t b ½t04 ½ t0 + t a T0 – ½ t0 ½t05 ½ t0T0 – ½ t0 ½t0 + t aFortunately, T0 is 0xFF, so T0 – ½ t0 is simply ~½ t0, and t0 is simply ~(t a + t b). Figure18 shows the flow chart (optimized for execution time) for a microcontroller implementation of SVM and overmodulation.Microcontroller Implementation of SVMFigure 18 Microcontroller Implementation of SVM and Over-modulationMicrocontroller Implementation of SVM4.2 SVM Implementation OptionsThe compare registers of the CAPCOM6 peripheral have shadow registers that allow all of the compare values to be updated at once. When the compare registers are written to by the microcontroller, the values are actually stored in the shadow registers. If the Shadow Transfer Enable bit (STE12) is set, then the contents of the shadow registers are copied to the actual compare registers as soon as the timer (T12) reaches the period value (when counting up) or 0x0001 when counting down. This shadow latch mechanism ensures that the three compare values are updated simultaneously and it also guarantees that there are no disturbed pulses.Generally SVM is performed twice every switching period as shown in Figure 13. To properly implement this, the shadow latch transfers must occur when the compare timer reaches 0x0001 and when the compare timer reaches its period value. However many times SVM is implemented so that the compare values are only updated when the timer is 0x0001 to reduce CPU load and to keep the PWM symmetric. The user can decide which option best suits his needs.With most carrier based PWM methods, the microcontroller compare value calculation is synchronized with the carrier signal (the compare timer). This ensures a more consistent latency between the time that the new input values (u s) are received until the pulses are actually present on the output pins. This synchronization is usually accomplished by performing the SVM calculations after a compare timer interrupt. The CAPCOM6 module can generate interrupts when the compare timer reaches zero and when the timer reaches its period value. This is equivalent to having an interrupt at the beginning of every T0. Using these interrupts to trigger the SVM calculations will ensure a more consistent input to output latency.SVM and over-modulation have been implemented on the XC866. The actual SVM and over-modulation code was written in assembly language to optimize the execution speed. The assembly code is part of a larger project that includes C files for initialization and testing. A conditional assembly switch is also used to enable or disable over-modulation.When implementing SVM in a motor control application, there are many factors which will influence the CPU load. Table 4 shows some of the major factors and their impact on CPU load when using the algorithms of Figure 18. It should be noted that the switching frequencies shown in Table 4 can be obtained without changing the SVM algorithm. The only modification needed is a change of the CAPCOM6 Timer 12 pre-scaler. Table 4 shows only the CPU load for the SVM algorithm (the compare timerMicrocontroller Implementation of SVMISR) without a control loop. It also assumes that the XC866 is operating at 26.67 MHzfrom internal flash with one wait-state (6.67 MIPS).In addition to SVM and over-modulation, the demo code that accompanies this application note implements a simple control loop that allows the user to adjust thelength and velocity of the input vector. Two A/D channels are used to control the amplitude and frequency of the generated voltages.Table 4 CPU Load for SVM assuming 150 ns per Instruction CycleSwitchingFrequency6.5 kHz 13 kHz 26.0 kHzSVM only 7.6% 15% 30% SVM ExecutedOnce Per SwitchingPeriodSVMw/Overmodulation9.5% 19% 38%SVM only 15% 30% 61%SVM ExecutedTwice Per Switching PeriodSVMw/Overmodulation19% 38% 76%4.3 Results and ConclusionsThe source code that accompanies this application note was executed using the XC866 microcontroller evaluation board. To view the output, either the CCx or COUTx pins of the microcontroller can be connected to an external circuit as shown in Figure 19. Capacitors are used to filter the PWM outputs so the voltages will appear smooth when viewed by an oscilloscope. The source code for this application note uses two analog inputs to control the magnitude and frequency of the generated voltage. This portion of the code will be omitted or modified in most applications.Accompanying this application note are the source code files and an Excel spreadsheet which can be used to calculate the look-up table values if different dead-times are needed.。

mcs-51单片机资料

注意的是,每当访问外部数据存储器时,将跳过一个ALE脉冲。ALE端可以驱动(吸收或输出电流)8个LS型的TTL输入电路。

对于EPROM单片机(如8751),在EPROM编程期间,此引脚用于输入编程脉冲(PROG)。

8.2k的下拉电阻,与VCC引脚之间连接一个约10μF的电容,以保证可靠地复位。

VCC掉电期间,此引脚可接上备用电源,以保证内部RAM的数据不丢失。当VCC主电源下掉到低于规定的电平,而VPD在其规定的电压范

围(5±0.5V)内,VPD就向内部RAM提供备用电源。

②ALE/PROG(30脚):当访问外部存贮器时,ALE(允许地址锁存)的输出用于锁存地址的低位字节。即使不访问外部存储器,ALE端

布尔处理功能。单片机指令系统中的布尔指令集、存储器中的位地址空间与CPU中的位操作构成了片内的布尔功能系统,它可对位

(bit)变量进行布尔处理,如置位、清零、求补、测试转移及逻辑“与”、“或”等操作。在实现位操作时,借用了程序状态标志

器(PSW)中的进位标志Cy作为位操作的“累加器”。

运算部件中的累加器ACC是一个8位的累加器(ACC也可简写为A)。从功能上看,它与一般微机的累加器相比没有什么特别之处,但

MCS-51单片机的ALU功能十分强,它不仅可对8位变量进行逻辑“与”、“或”、“异或”、循环、求补、清零等基本操作,还可以进

行加、减、乘、除等基本运算。为了乘除运算的需要,设置了B寄存器。在执行乘法运算指令时,用来存放其中一个乘数和乘积的高

8位数;在执行除法运算指令时,B中存入除数及余数。MCS-51单片机的ALU还具有一般微机ALU,如Z80、MCS-48所不具备的功能,即

(完整版)MCS-51系列单片机中英文资料对照外文翻译文献综述

MCS-51系列单片机中英文资料对照外文翻译文献综述Structure and function of the MCS-51 seriesStructure and function of the MCS-51 series one-chip computer MCS-51 is a name of a piece of one-chip computer series which Intel Company produces. This company introduced 8 top-grade one-chip computers of MCS-51 series in 1980 after introducing 8 one-chip computers of MCS-48 series in 1976. It belong to a lot of kinds this line of one-chip computer the chips have, such as 8051, 8031, 8751, 80C51BH, 80C31BH,etc., their basic composition, basic performance and instruction system are all the same.8051 daily representatives-51 serial one-chip computers.A one-chip computer system is made up of several following parts: (1) One microprocessor of 8 (CPU). ( 2) At slice data memory RAM (128B/256B),it use not depositing not can reading /data that write, such as result not middle of operation, final result and data wanted to show, etc. (3) Procedure memory ROM/EPROM (4KB/8KB ), is used to preserve theprocedure , some initial data and form in slice. But does not take ROM/EPROM within some one-chip computers, such as 8031, 8032.(4) Four 8 run side by side I/O interface P0 four P3, each mouth can use as introduction , may use as exporting too. (5) Two timer / counter, each timer / counter may set up and count in the way, used to count to the external incident, can set up into a timing way too, and can according to count or result of timing realize the control of the computer. (6) Five cut off cutting off the control system of the source. (7) One all duplex serial I/O mouth of UART (universal asynchronous receiver/transmitter (UART) ), is it realize one-chip computer or one-chip computer and serial communication of computer to use for. (8) Stretch oscillator and clock produce circuit, quartz crystal finely tune electric capacity need outer. Allow oscillation frequency as 12 megahertz now at most. Every the above-mentioned part was joined through the inside data bus .Among them, CPU is a core of the one-chip computer, it is the control of the computer and command centre, made up of such parts as arithmetic unit and controller , etc.. The arithmetic unit can carry on 8 persons of arithmetic operation and unit ALU of logic operation while including one, the 1 storing device temporaries of 8, storing device 2 temporarily, 8's accumulation device ACC, register B and procedure state register PSW, etc. Person who accumulate ACC count by 2 input ends entered of checking etc. temporarily as one operation often, come from person who store 1 operation is it is it make operation to go on to count temporarily , operation result and loop back ACC with another one. Inaddition, ACC is often regarded as the transfer station of data transmission on 8051 inside. The same as general microprocessor, it is the busiest register. Help remembering that agreeing with a express in the order. The controller includes the procedure counter, the order is deposited, the order deciphering, the oscillator and timing circuit, etc. The procedure counter is made up of counter of 8 for two, amounts to 16. It is a byte address counter of the procedure in fact, the content is the next IA that will carried out in PC. The content which changes it can change the direction that the procedure carries out. Shake the circuit in 8051 one-chip computers, only need outer quartz crystal and frequency to finely tune the electric capacity, its frequency range is its 12MHZ of 1.2MHZ. This pulse signal, as 8051 basic beats of working, namely the minimum unit of time. 8051 is the same as other computers, the work in harmony under the control of the basic beat, just like an orchestra according to the beat play that is commanded.There are ROM (procedure memory , can only read ) and RAM in 8051 slices (data memory, can is it can write ) two to read, they have each independent memory address space, dispose way to be the same with general memory of computer. Procedure 8051 memory and 8751 slice procedure memory capacity 4KB, address begin from 0000H, used for preserving the procedure and form constant. Data 8051- 8751 8031 of memory data memory 128B, address false 00FH, using for middle result to deposit operation, the data are stored temporarily and the data are buffered. In RAM of this 128B, there is unit of 32 bytes that can be appointed as the jobregister, this and general microprocessor is different, 8051 slice RAM and job register rank one formation the same to arrange the location. It is not very the same that the memory of MCS-51 series one-chip computer and general computer disposes the way in addition. General computer for first address space, ROM and RAM can arrange in different space within the range of this address at will, namely the addresses of ROM and RAM, with distributing different address space in a formation. While visiting the memory, corresponding and only an address Memory unit, can ROM, it can be RAM too, and by visiting the order similarly. This kind of memory structure is called the structure of Princeton. 8051 memories are divided into procedure memory space and data memory space on the physics structure, there are four memory spaces in all: The procedure stores in one and data memory space outside data memory and one in procedure memory space and one outside one, the structure forms of this kind of procedure device and data memory separated form data memory, called Harvard structure. But use the angle from users, 8051 memory address space is divided into three kinds: (1) In the slice, arrange blocks of FFFFH, 0000H of location, in unison outside the slice (use 16 addresses). (2) The data memory address space outside one of 64KB, the address is arranged from 0000H 64KB FFFFH (with 16 addresses) too to the location. (3) Data memory address space of 256B (use 8 addresses). Three above-mentioned memory space addresses overlap, for distinguishing and designing the order symbol of different data transmission in the instruction system of 8051: CPU visit slice, ROM orderspend MOVC , visit block RAM order uses MOVX outside the slice, RAM order uses MOV to visit in slice.8051 one-chip computer have four 8 walk abreast I/O ports, call P0, P1, P2 and P3. Each port is 8 accurate two-way mouths, accounts for 32 pins altogether. Every one I/O line can be used as introduction and exported independently. Each port includes a latch (namely special function register), one exports the driver and a introduction buffer. Make data can latch when outputting, data can buffer when making introduction, but four function of pass away these self-same. Expand among the system of memory outside having slice, four ports these may serve as accurate two-way mouth of I/O in common use. Expand among the system of memory outside having slice, P2 mouth see high 8 address off; P0 mouth is a two-way bus, send the introduction of 8 low addresses and data / export in timesharing The circuit of 8051 one-chip computers and four I/O ports is very ingenious in design. Familiar with I/O port logical circuit, not only help to use port correctly and rationally, and will inspire to designing the peripheral logical circuit of one-chip computer to some extent. Load ability and interface of port have certain requirement, because output grade, P0 of mouth and P1 end output, P3 of mouth grade different at structure, so, the load ability and interface of its door demand to have nothing in common with each other. P0 mouth is different from other mouth, its output grade draws the resistance supremely. When using it as the mouth in common use, output grade is it leak circuit to turn on, is it urge NMOS draw the resistanceon taking to be outer with it while inputting to go out to fail. When being used as introduction, should write"1" to a latch first. Every one with P0 mouth can drive 8 Model LS TTL load to export. P1 mouth is an accurate two-way mouth too, used as I/O in common use. Different from P0 mouth output of circuit its, draw load resistance link with power on inside have. In fact, the resistance is that two effects are in charge of FET and together: One FET is in charge of load, its resistance is regular. Another one can is it lead to work with close at two state, make its President resistance value change approximate 0 or group value heavy two situation very. When it is 0 that the resistance is approximate, can draw the pin to the high level fast; when resistance value is very large, P1 mouth high electricity at ordinary times, can is it draw electric current load to offer outwards, draw electric current load to offer outwards, draw the resistance on needn't answer and thinking. Here when the port is used as introduction, must write into 1 to the corresponding latch first too, make FET end relatively about 20,000 ohms because of load resistance in scene and because 40,000 ohms, will not exert an influence on the data that are input. The structure of P2 some mouth is similar to P0 mouth, there are MUX switches. Is it similar to mouth partly to urge, but mouth large a conversion controls some than P1.P3 mouth one multi-functional port, mouth getting many than P1 it have "3 doors and 4 buffers". Two parts there, make her besides accurate two-way function with P1 mouth just, can also use the second function of every pin, "and" door 3 functions one switch in fact, it determines to be to output data of latch tooutput second signal of function. Act as W=At 1 o'clock, output Q end signal; act as Q=At 1 o'clock, can output W line signal. At the time of programming, it is that the first function is still the second function but needn't have software that set up P3 mouth in advance .It hardware not inside is the automatic to have two function outputted when CPU carries on SFR and seeks the location to visit to P3 mouth/at not lasting lining, there are inside hardware latch Qs=1. The operation principle of P3 mouth is similar to P1 mouth.Output grade, P3 of mouth, P1 of P1, connect with inside have load resistance of drawing, every one of they can drive 4 Model LS TTL load to output. As while inputting the mouth, any TTL or NMOS circuit can drive P1 of 8051 one-chip computers as P3 mouth in a normal way. Because draw resistance on output grade of them have, can open a way collector too or drain-source resistance is it urge to open a way, do not need to have the resistance of drawing outer. Mouths are all accurate two-way mouths too. When the conduct is input, must write the corresponding port latch with 1 first. As to 80C51 one-chip computer, port can only offer milliampere of output electric currents, is it output mouth go when urging one ordinary basing of transistor to regard as, should contact a resistance among the port and transistor base, in order to the electricity while restraining the high level from exporting P1~P3 Being restored to the throne is the operation of initializing of an one-chip computer. Its main function is to turn PC into 0000H initially, make the one-chip computer begin to hold the conductprocedure from unit 0000H. Except that the ones that enter the system are initialized normally, as because procedure operate it make mistakes or operate there aren't mistake, in order to extricate oneself from a predicament , need to be pressed and restored to the throne the key restarting too. It is an input end which is restored to the throne the signal in 8051 China RST pin. Restore to the throne signal high level effective, should sustain 24 shake cycle (namely 2 machine cycles) the above its effective times. If 6 of frequency of utilization brilliant to shake, restore to the throne signal duration should exceed 4 delicate to finish restoring to the throne and operating. Produce the logic picture of circuit which is restored to the throne the signal: restore to the throne the circuit and include two parts outside in the chip entirely. Outside that circuit produce to restore to the throne signal (RST) hand over to Schmitt's trigger, restore to the throne circuit sample to output , Schmitt of trigger constantly in each S5P2 , machine of cycle in having one more , then just got and restored to the throne and operated the necessary signal inside. Restore to the throne resistance of circuit generally, electric capacity parameter suitable for 6 brilliant to shake, can is it restore to the throne signal high level duration greater than 2 machine cycles to guarantee. Being restored to the throne in the circuit is simple, its function is very important. Pieces of one-chip computer system could normal running, should first check it can restore to the throne not succeeding. Checking and can pop one's head and monitor the pin with the oscilloscope tentatively, push and is restored to the throne the key, the wave form that observes andhas enough range is exported (instantaneous), can also through is it restore to the throne circuit group holding value carry on the experiment to change.MCS-51系列单片机的功能和结构MSC-51系列单片机具有一个单芯片电脑的结构和功能,它是英特尔公司的系列产品的名称。

51单片机延时程序

void delay1s(void)

{

unsigned char h,i,j,k;

for(h=5;h>0;h--)

for(i=4;i>0;i--)

for(j=116;j>0;j--)

for(k=214;k>0;k--);

//

void delay(uint t)

{

for (;t>0;t--);

}

1ms延时子程序(12MHZ)

void delay1ms(uint p)//12mhz

{ uchar i,j;

for(i=0;i<p;i++)

{

for(j=0;j<124;j++)

{;}

在实际应用中,定时常采用中断方式,如进行适当的循环可实现几秒甚至更长时间的延时。使用定时器/计数器延时从程序的执行效率和稳定性两方面考虑都是最佳的方案。但应该注意,C51编写的中断服务程序编译后会自动加上PUSH ACC、PUSH PSW、POP PSW和POP ACC语句,执行时占用了4个机器周期;如程序中还有计数值加1语句,则又会占用1个机器周期。这些语句所消耗的时间在计算定时初值时要考虑进去,从初值中减去以达到最小误差的目的。

}

void Delay10us( ) //12mhz

{

_NOP_( );

_NOP_( );

_NOP_( );

_NOP_( );

_NOP_( );

_NOP_( );

}

/*****************11us延时函数*************************/

ASM51宏汇编使用手册

ASM51宏汇编使用手册2007-01-21 10:33ASM-51 宏汇编使用手册ASM-51 宏汇编主要用来开发Inter8051系列单片机,它具有宏处理,数据处理,列表处理和条件处理等多种功能。

源程序的编写完全采用 Inter标准助记符和行格式。

在编写程序过程中,可借助于文本编辑(Windows的记事本)或文字处理软件Word等编辑,经ASM-51汇编后生成列表输出文件(.LST)和目标代码文件(.HEX)。

此目标代码文件(.HEX)可直接用CZS-51或MedWin、Keil、Debug8051进行模拟/调试,或直接用于硬件仿真器上运行。

当然,这也是要烧写到单片机ROM中的代码。

1、宏汇编语言的基本语法1、1 宏汇编的特点ASM-51宏汇编完全支持Inter助记符的汇编语言,它含有宏语句,英文大小写字母,变量名,标号等不受限制,有二,十,十六进制和串参数类型,有汇编控制指令和多层条件语句,程序逻辑分段,还有模块化程序设计的连接功能,汇编速度快等特点。

1、2 汇编处理过程(1) 用行编辑EDLIN或文字处理软件WS或全屏幕编辑软件PE等,编辑宏汇编语言源程序,它的文件扩展名为。

ASM。

(2) 用ASM-51宏汇编程序对上述源程序文件进行汇编,产生扩展名为.LST的列表输出文件和扩展名为.HEX的目标代码文件(.HEX)。

列表输出文件包含源程序语句所汇编成的代码,以及有关的地址,语句和符号表等。

目标代码文件包含源程序语句所汇编成的代码,不包含任何符号信息或助记符。

进行模拟/调试,或直接用于硬件仿真器上运行。

1、3 语句汇编语言可分为两类语句:指令性语句和指示性语句。

(1)指令性语句这一类语句是指在汇编过程中能生成指令代码的语句(如 MOV ,DEC等)。

其格式为:[标号:] [指令助记符] [操作数] [;注释]其中方括号[ ]中为选择项。

下同。

(2)指示性语句这一类语句即通常所说的伪指令,它指示汇编程序后面的指示性语句如何产生代码。

第1节MCS51单片机介绍

第1章MCS51单片机介绍1.1 数字集成电路的发展历程从20世纪60年代开始,数字集成电路在集成度方面的发展经历了以下4个阶段:包含几十到几百个逻辑门的小规模集成电路(Small Scale Integration,SSI);包含几百到几千个逻辑门的中规模集成电路(Medium Scale Integration,MSI);包含几千到几万个逻辑门的大规模集成电路(Large Scale Integration,LSI);包含几万个以上逻辑门的超大规模集成电路(Very Large Scale Integration,VLSI)。

在工作原理方面,数字集成电路可以划分为标准逻辑器件、微处理器和专用集成电路。

1.1.1 标准逻辑器件标准逻辑器件在集成度方面属于中小规模集成电路,它包括基于TTL工艺的54/74系列和基于CMOS工艺的4000系列的各种逻辑门、触发器、译码器、多路选择器、计数器等器件。

这些器件的工作原理和应用在《数字电路逻辑设计》课程中有详细的介绍。

作为传统数字系统设计中使用的主要器件,标准逻辑器件的产量很大,因此它们的生产成本低廉、价格便宜。

由于这些器件的功能确定,芯片设计时主要考虑如何提高器件的性能,因此标准逻辑器件的工作速度快,但是由于集成度较低,采用它们设计的数字系统需要较多的器件,这就使得电路连线复杂,系统的可靠性降低。

由于用户无法修改这类器件的功能,修改系统设计必须通过对电路重新设计和组装来实现。

1.1.2 微处理器微处理器,包括在本书中将要学习的单片机,在集成度方面属于大规模集成电路。

它们被应用于数字系统的设计起始于20世纪70年代。

这类器件可以通过编写程序来实现系统功能。

基于微处理器所设计电路的逻辑功能可由软件配置,这个特点使得设计灵活性得到提高,当修改系统设计时,设计者不需要,或者较少需要修改电路连线。

相对于由标准逻辑器件构成的数字系统,基于微处理器设计的系统工作速度较低;其次,微处理器的工作仍需要一些标准逻辑器件或者相关逻辑器件构成的外围电路的支持。

ASM51伪指令

ASM51宏汇编本文给出了ASM5l宏汇编伪指令的简要说明及SUPER系列仿真器调试ASM51程序时有关的汇编控制项,目的是使用户快速地掌握宏汇编语言ASM51的一般方法,更复杂的用法请参阅有关汇编语言的手册。

1.1 ASM51基本成份·字符集:ASCII字符集·数字:二进制数,后缀为B八进制数,后缀为O或Q十进制数,后缀为D或无后缀十六进制数,后缀为H·符号:第一字符必须是字母‘?’或‘—’,最多31个字符·定位计数器:用$表示当前定位计数器的值·字符串:字符串必须是用单引号(’)括起来的可打印的ASCII字符序列串长度控制在0—255之内,字符串可用DB伪指令初始化。

1.2表达式和基本操作数1.2.1表达式表达式用于定义常数,表达式有三种属性:1.类型——表达式所属段的类型。

2.可重定位性——表达式分为绝对的表达式和可重定位的表达式。

绝对的表达式的值在汇编期间计算,而可重定位的表达式的值在连接定位期间计算。

绝对的表达式可出现在程序的任意位置。

唯一合法的可重定位表达式是一个可重定位的符号或一个可重定位的符号加上一个常数。

3.值——表达式的值以十六位二进制的补码形式表示。

表示式值或在汇编期间计算或在连接定位期间计算。

·1.2.2基本操作数ASM51有以下五种基本操作数:1.符号——符号用来表示地址和常数2.数字——数字可用二、八、十或十六进制表示3.$——表示定位计数器的当前值4.STACK——预定义的变量STACK表示栈底5.串——只有一或二个字符的串可用作操作数,一个字符的串被认为是值等于其ASCII码的字节常数,二个字符的串被认为是字常数。

1.2.3地址空间8051的地址空间有五种:·可被直接寻址的数据地址空间(DATA)·位地址空间(BIT)·外部的数据地址空间(XDA TA)·程序地址空间(CODE)·可间接寻址的数据空间(1DATA)在某些情况下,同一个数值对全部五种地址空间都是有效的地址。

MS-C51系列单片机的各种资料-推荐下载

三、逻辑操作 ANL A,Rn 58~5F 寄存器“与”到A ANL A,dircet 55 dircet 直接字节“与”到A ANL A,@Ri 56~57 间接RAm“与”到A ANL A,#data 54 data 立即数“与”到A ANL dircet A 52 dircet A“与”到直接字节 ANL dircet,#data 53 dircet data 立即数“与”到直接字节 ORL A,Rn 48~4F 寄存器“或”到A ORL A,dircet 45 dircet 直接字节“或”到A ORL A,@Ri 46~47 间接RAM“或”到A ORL A,#data 44 data 立即数“或”到A ORL dircet,A 42 dircet A“或”到直接字节 ORL dircet,#data 43 dircet data 立即数“或”到直接字节 XRL A,Rn 68~6F 寄存器“异或”到A XRL A,dircet 65 dircet 直接字节“异或”到A XRL A,@Ri 66~67 间接RAM“异或”到A XRL A,#data 64 data 立即数“异或”到A XRL dircet A 62 dircet A“异或”到直接字节 XRL dircet,#data 63 dircet data 立即数“异或”到直接字节 CLR A E4 清零 CPL A F4 A取反 RL A 23 A左环移 RLC A 33 A通过进位左环移 RR A 03 A右环移 RRC A 13 A通过进位右环移四、控制程序转移 ACALL addr 11 *1 addr(a7~a0) 绝对子程序调用 LCALL addr 16 12 addr(15~8) 长子程序调用 addr(7~0) RET 22 子程序调用返回 RETI addr 11 32 中断调用返回 AJMP addr 11 △1 addr(a7~a6) 绝对转移 LJMP addr 16 02addr(15~8) 长转移 addr(7~0) SJMP rel 80 rel 短转移,相对转移 JMP @A+DPTR 73 相对于DPTR间接转移 JZ rel 60 rel A为零转移 JNZ rel 70 rel A为零转移 CJNE A,dircet,rel B5 dircet rel 直接字节与A比较,不等则转移 CJNE A,#data,rel B4 data rel 立即数与A比较,不等则转移 CJNE A,Rn,#data,rel B8~BF data rel 立即数与寄存器比较,不等则转移 CJNE @Ri,#data,rel B6~B7 data rel 立即数与间接RAM比较,不等则转移 DJNZ Rn,rel D8~DF rel 寄存器减1,不为零则转移 DJNZ dircet,rel B5 dircet rel 直接字节减1,不为零则转移 NOP 00 空操作 *=a10a9a8l △=a10a9a80五、布尔变量操作 CLR C C3 清零进位 CLR bit C2 清零直接位 SETB C D3 置位进位 SETB bit D2 置位直接位 CPL C B3 进位取反 CPL bit B2 直接位取反 ANL C,bit 82 dit 直接数“与”到进位 ANL C,/bit B0 直接位的反“与”到进位 ORL C,bit 72 bit 直接位“或”到进位 ORL C,/bit A0 bit 直接位的反“或”到进位 MOV C,bit A2 bit 直接位送进位 MOV bit,C 92 bit 进位送直接位 JC rel 40 rel 进位位为1转移 JNC rel 50 rel 进位位为0转移 JB bit,rel 20 bit rel 直接位为1相对转移 JNB bit,rel 30 bit rel 直接位为0相对转移 JBC bit,rel 10 bit rel 直接位为1相对转移,然后清零该位常用单片机芯片简介 STC单片机抗内,达。

51单片机汇编语言常用程序集

MCS-MCS-515151单片机实用子程序库单片机实用子程序库单片机实用子程序库((9696年版年版年版))周 航 慈目前已有若干版本的子程序库公开发表,它们各有特色。

笔者在1988年也编制了两个 子程序库(定点子程序库和浮点子程序库),并在相容性、透明性、容错性和算法优化方 面作了一些工作。

本程序库中的开平方算法为笔者研究的快速逼近算法,它能达到牛顿迭 代法同样的精度,而速度加快二十倍左右,超过双字节定点除法的速度。

经过八年来全国 广大用户的实际使用,反馈了不少信息,陆续扩充了一些新的子程序,纠正了一些隐含错 误,成为现在这个最新版本。

本子程序库对《单片机应用程序设计技术》一书附录中的子程序库作了重大修订: (1)按当前流行的以 IBM PC 为主机的开发系统对汇编语言的规定,将原子程序库 的标号和位地址进行了调整,读者不必再进行修改,便可直接使用。

(2)对浮点运算子程序库进行了进一步的测试和优化,对十进制浮点数和二进制浮 点数的相互转换子程序进行了彻底改写,提高了运算精度和可靠性。

(3)新增添了若干个浮点子程序(传送、比较、清零、判零等),使编写数据处理 程序的工作变得更简单直观。

在使用说明中开列了最主要的几项:标号、入口条件、出口信息、影响资源、堆栈 需求,各项目的意义请参阅《单片机应用程序设计技术》第六章 6.3.7 节的内容。

程序 清单中开列了四个栏目:标号、指令、操作数、注释。

为方便读者理解,注释尽力详细。

子程序库的使用方法如下:1.将子程序库全部内容链接在应用程序之后,统一编译即可。

优点是简单方便,缺 点是程序太长,大量无关子程序也包含在其中。

2.仅将子程序库中的有关部分内容链接在应用程序之后,统一编译即可。

有些子程 序需要调用一些低级子程序,这些低级子程序也应该包含在内。

优点是程序紧凑,缺点是 需要对子程序库进行仔细删节。

(一) MCS-51定点运算子程序库及其使用说明定点运算子程序库文件名为DQ51.ASM ,为便于使用,先将有关约定说明如下:1.多字节定点操作数:用[R0]或[R1]来表示存放在由R0或R1指示的连续单元中的数 据。

51单片机教材(免费完整版)

单片机教程原作:进墨者目录单片机教程第一课:单片机概述 (2)单片机教程第二课:单片机的内部、外部结构(一) (2)单片机教程第三课:几个基本概念 (5)单片机教程第四课:第一个小程序 (8)单片机教程第五课:延时程序分析 (10)单片机教程第六课:单片机的内外部结构分析(四) (12)单片机教程第七课:单片机内部结构分析(五) (15)单片机教程第八课(寻址方式与指令系统) (19)单片机教程第九课:数据传递指令 (22)单片机教程第十课数据传递类指令指令 (25)单片机教程第十一课:算术运算类指令 (28)单片机教程第十二课:逻辑运算类指令: (32)单片机教程第十三课:逻辑与指令 (34)单片机教程第十四课:条件转移指令 (38)单片机教程第十五课:位及位操作指令 (41)单片机教程第十六课:计数器与定时器 (44)单片机教程第十七课:定时/计数器的方式控制字 (46)单片机教程第十八课:中断系统 (49)单片机教程第十九课:定时、中断练习一 (52)单片机教程第二十课:定时/计数器实验2 (57)单片机教程第二十一课:串行接口 (60)单片机教程第二十二课:串行口应用编程实例 (65)单片机教程第二十三课:LED数码显示器的连接与编程 (68)单片机教程第二十四课:动态扫描显示接口 (72)单片机教程第二十五课:键盘接口与编程 (78)单片机教程第二十六课:矩阵式键盘接口技术及编程 (83)单片机教程第二十七课:初学单片机几个不易掌握的概念 (87)单片机教程第二十八课:单片机音乐程序的设计与实验 (90)单片机教程第一课:单片机概述1、何谓单片机一台能够工作的计算机要有这样几个部份构成:CPU(进行运算、控制)、RAM(数据存储)、ROM(程序存储)、输入/输出设备(例如:串行口、并行输出口等)。

在个人计算机上这些部份被分成若干块芯片,安装一个称之为主板的印刷线路板上。

而在单片机中,这些部份,全部被做到一块集成电路芯片中了,所以就称为单片(单芯片)机,而且有一些单片机中除了上述部份外,还集成了其它部份如A/D,D/A等。

51单片机缩写的英文全称及中文名称

单片机缩写的英文全称及中文名称PC = programmer counter //程序计数器counter 计算器, 计数器, 计算者, 柜台, 筹码['kauntə]ACC = accumulate [ə'kju:mjuleit //累加器: 积累: 积聚PSW = programmer status word //程序状态字status'steitəs, 'stæ-]n. 地位;状态;情形;重要身分SP = stack point //堆栈指针stack[stæk n. 堆;堆叠vt. 使堆叠;把…堆积起来vi. 堆积,堆叠DPTR = data point register //数据指针寄存器'redʒistə寄存器IP = interrupt priority //中断优先级[,intə'rʌpt 中断[prai'ɔrəti] 优先;优先权;[数] 优先次序;优先考虑的事IE = interrupt enable // 中断使能i'neibl]使能够,使成为可能;授予权利或方法TMOD = timer mode // 定时器方式(定时器/计数器控制寄存器) ['taimə定时器,计时器mode [məud模式,方式ALE = alter (变更,可能是)['ɔ:ltə]PSEN = programmer saving enable //程序存储器使能(选择外部程序存储器的意思) EA = enable all(允许所有中断)完整应该是enable all interruptPROG = programme (程序)SFR = special funtion register //特殊功能寄存器TCON = timer control //定时器控制PCON = power control //电源控制MSB = most significant bit//最高有效位[sig'nifikənt有效的;有意义的LSB = last significant bit//最低有效位CY = carry //进位(标志)['kæri]AC = assistant carry //辅助进位[ə'sistənt n. 助手,助理,助教adj. 辅助的,助理的;有帮助的OV = overflow //溢出[,əuvə'fləu, 'əuvəfləu ORG = originally[ə'ridʒənəli //起始来源DB = define [di'fain]定义byte [bait] //字节定义EQU = equal //等于['i:kwəl]DW = define word //字定义 E = enable //使能OE = output enable //输出使能RD = read //读WR = write //写中断部分:INT0 = interrupt 0 //中断0 INT1 = interrupt 1//中断1T0 = timer 0 //定时器0 T1 = timer 1 //定时器1TF1 = timer1 flag //定时器1 标志(其实是定时器1中断标志位) [flæɡvi. 标记;衰退;枯萎vt. 标记;插旗n. 标志;旗子IE1 = interrupt exterior //(外部中断请求,可能是) ik'stiəriə]外部的IT1 = interrupt touch //(外部中断触发方式,可能是)ES = enable serial //串行使能['siəriəl, 'si:r- adj. 连续的;连载的;分期偿还的n. 电视连续剧;[图情] 期刊;连载小说serial communication [计]串行通信serial port [计]串行端口;序列埠serial interface [计]串联接口ET = enable timer //定时器使能PS = priority serial //串口优先级EX = enable exterior //外部使能(中断)[ik'stiəriə] adj. 外部的;表面的;外在的n. 外部;表面;外型;外貌PX = priority exterior //外部中断优先级PT = priority timer //定时器优先级寄存器部分:SFR:special funtion register //特殊功能寄存器(片内RAM 80H~FFH)ACC:accumulate //累加器SP:stack point //堆栈指针PSW:programmer status word //程序状态字IE:interrupt enable // 中断使能DPL,DPH:DPTR(data point register //数据指针寄存器)的低8位和高8位IP:interrupt priority //中断优先级PCON:power control //电源控制SCON:serial control //串行口控制TCON:timer control //定时器控制SBUF:serial buffer //串行数据缓冲['bʌfə] n. [计] 缓冲区;缓冲器,[车辆] 减震器vt. 缓冲TMOD:timer mode //定时器方式PSW:CY:carry (psw.7) //进位(标志)AC:auxiliary carry (psw.6) //辅助进位F0: (psw.5) //用户自定义标志位OV:overflow (psw.2) //溢出RS1,RS0:register select (psw.4,psw.3)//工作寄存器组选择位[si'lekt]挑选P:parity (psw.0) //奇偶校验位['pæriti. 平价;同等;相等IE:EA:Enable All Interrupt /CPU开/关中断控制位ET1:Enable Timer //定时器2溢出中断允许位ES:Enable Serial Port //串行口中断允许位EX:Enable External //外部中断1的中断允许位IP:PS:Priority Serial //串口优先级PT:Priority Timer //定时器优先级PX:Priority External //外部中断优先级[ik'stə:nəl] adj. 外部的;表面的;[药] 外用的;外国的;外面的n. 外部;外观;外面SCON:RI:Receive Interrupt //串行口接收中断请求标志位TI:Transmit Interrupt //串行口发送中断请求标志位[trænz'mit, træns-, trɑ:n-] vt. 传输;传播;发射;传达;遗传vi. 传输;发射信号TCON:TF1:Timer1 Overflow Flag //定时器1溢出中断请求标志TR1:Timer1 Run //定时器1启动控制位IE1:Interrupt Edge //外部中断1请求标志位[edʒ]IT1:Interrupt Type //外部中断1触发方式选择位8051引脚:RST:RESET (9)//复位,重启P3:RXD:Received eXchange [iks'tʃeindʒ Data (10,p3.0)//接收串行数据eXchange n. 交换;交流;交易所;兑换vt. 交换;交易;兑换vi. 交换;交易;兑换TXD:Transmit eXchange Data (11,p3.1)//发送串行数据INT0:interrupt 0 (12,p3.2)//中断0 INT1:interrupt 1 (13,p3.3)//中断1T0:timer 0 (14,p3.4)//定时器0 T1:timer 1 (15,p3.5)//定时器1RD:ReaD (16,p3.6)//外部数据存储器(RAM)的读信号WR:WRite (17,p3.7)//外部数据存储器(RAM)的写信号XTAL2,XTAL1:External Crystal ['kristəl晶体Oscillator ['ɔsileitə振荡器(18,19) //外部晶体振荡器PSEN:Program Store [stɔ:]Enable (29) //程序存储器(ROM)使能n. 商店;储备,贮藏;仓库vt. 贮藏,储存ALE:Address Latch Enable (30) //地址锁存Latch锁存器EA:External Address Enable (31) //外部程序存储器(ROM)地址允许其它:OE:output enable //输出使能MSB = most significant bit//最高有效位[sig'nifikənt] adj. 重大的;有效的;有意义的;值得注意的;意味深长的n. 象征;有意义的事物LSB = last significant bit//最低有效位DB = define byte //字节定义ORG = originally //起始来源EQU = equal //等于DW = define word //字定义CLKOUT:Clock out,时钟输出BUSWDITH:总线宽度Vref:参考电压(带ADC的单片机中有的)参考电压(Voltage Reference)['refərəns n. 参考,参照;HSO:High Speed Output,高速输出HSI:High Speed Input:高速输入INST:Instruction,指令READY就绪,总线中的就绪信号或引脚NMI:No Mask Interruput (Input):不可屏蔽的中断请求(输入)[mɑ:sk, mæskBHE:Bank High Enable:存储器的高位允许,如在80286系统中RAM的组织为16位的,分为高8位和低8位数据,分别的控制信号为BHE和BLE Bank n. 银行;岸;浅滩;储库vt. 将…存入银行;倾斜转弯vi. 堆积;倾斜转弯MCS-51指令(1)数据传送类指令(7种助记符)助记符英文注释功能MOV Move 对内部数据寄存器RAM和特殊功能寄存器SFR的数据进行传送MOVC Move Code 读取程序存储器数据表格的数据传送MOVX Move External RAM 对外部RAM的数据传送XCH Exchange 字节交换XCHD Exchange low-order Digit ['didʒit]低半字节交换POP Pop from Stack) 出栈PUSH Push onto ['ɔntu, -tə] Stack) 入栈(2)算术运算类指令(8种助记符)ADD Addition 加法ADDC Add with Carry 带进位加法SUBB Subtract [səb'trækt] with Borrow 带借位减法vt. 减去;扣DA Decimal ['desiməl]adj. 小数的;十进位的n. 小数Adjust [ə'dʒʌst]调整十进制调整INC Increment ['inkrimənt加1 DEC Decrement 'dekrimənt]减1MUL Multiplication、Multiply 乘法[,mʌltipli'keiʃən n. [数] 乘法;增加['mʌltiplai vt. 乘;使增加;使繁殖;使相乘vi. 乘;繁殖;增加adv. 多样地;复合地adj. 多层的;多样的DIV Division[di'viʒən n. [数] 除法;部门;分割;师(军队);赛区、Divide 除法di'vaid vt. 划分;除;分开;使产生分歧vi. 分开;意见分歧n. [地理] 分水岭,分水线(3)逻辑运算类指令(10种助记符)ANL And Logic 逻辑与'lɔdʒik] n. 逻辑;逻辑学;逻辑性adj. 逻辑的ORL OR Logic 逻辑或CLR Clear kliə]清零XRL Exclusive-OR Logic 逻辑异或[ik'sklu:siv] adj. 独有的;排外的;专一的n. 独家新闻;独家经营的项目;排外者CPL Complement 取反'kɔmplimənt] n. 补语;余角;补足物vt. 补足,补助RL Rotate left 循环左移[rəu'teit, 'rəut-, 'rəuteit vi.旋转;循环vt. 使旋转;使转动;使轮流adj. [植] 辐状的RLC Rotate Left throught the Carry flag 带进位循环左移RR Rotate Right 循环右移RRC Rotate Right throught the Carry flag 带进位循环右移SWAP Swap 低4位与高4位交换[swɔp, swɔ:p n. 交换;交换之物vt. 与...交换;以...作交换vi. 交换;交易(4)控制转移类指令(17种助记符)ACALL Absolute subroutine Call 子程序绝对调用'æbsəlju:t, ,æbsə'lju:t adj. 绝对的;完全的;专制的n. 绝对;绝对事物'sʌbru:,ti:n, ,sʌbru:'ti:n] n. [计] 子程序LCALL Long subroutine Call 子程序长调用RET Return from subroutine 子程序返回RETI Return from Interruption 中断返回SJMP Short Jump 短转移JMP Jump Indirect 间接跳越[,indi'rekt, -dai-] adj. 间接的;迂回的;非直截了当的AJMP Absolute Jump 绝对转移LJMP Long Jump 长转移CJNE Compare and Jump if Not Equal 比较不相等则转移kəm'pεə] vt. 比较;对照;比喻为vi. 比较;相比n. 比较DJNZ Decrement and Jump if Not Zero 减1后不为0则转移JZ Jump if Zero 结果为0则转移JNZ Jump if Not Zero 结果不为0则转移JC Jump if the Carry flag is set 有进位则转移JNC Jump if Not Carry 无进位则转移JB Jump if the Bit is set) B位为1则转移JNB Jump if the Bit is Not set B位为0则转移JBC Jump if the Bit is set and Clear the bit 位为1则转移,并清除该位NOP No Operation 空操作[,ɔpə'reiʃən] n. 操作;经营;[外科] 手术;[数][计] 运算(5)位操作指令(1种助记符)SETB Set Bit 置位伪指令助记符英文注释功能ORG OriginDB Define ByteDW Define WordEQU EqualDATA DataXDATA External DataBIT BitEND End51外部引脚缩写英文解释中文解释RST (9)Reset 复位信号引脚[,ri:'set, 'ri:set vi. 重置;清零vt. 重置;重新设定;重新组合n. 重新设定;重新组合;重排版RxD (10--P3.0) Receive Data 串口接收端TxD (11--P3.1) Transmit Data 串口发送端INT0(————) (12--P3.2)Interrupt0 外部中断0信号输入引脚INT1(————) (13--P3.3)Interrupt1 外部中断1信号输入引脚T0 (14--P3.4) Timer0 定时/计数器0输入信号引脚T1 (15--P3.5) Timer1 定时/计数器1输入信号引脚LSB = last significant bit//最低有效位significant [sig'nifikənt有效的WR(———) (16--P3.6) write写信号引脚RD(———) (17--P3.7) read 读信号引脚PSEN(—————) (29)programmer saving enable 外部程序存储器读选通信号ALE (30)Address Latch Enable 地址锁存允许信号EA(———) (31) enable 外部ROM选择信号51内部寄存器SFR special funtion register 特殊功能寄存器ACC accumulate 累加器A PSW programmer status word 程序状态字CY (PSW.7) carry 进位标志位AC (PSW.6) assistant carry 辅助进位标志位ə'sistənt] n. 助手,助理,助教adj. 辅助的,助理的;有帮助的OE = output enable //输出使能OV (PSW.2) overflow 溢出标志位[,əuvə'fləu, 'əuvəfləu]PC programmer counter 程序计数器DPTR data point register 数据指针寄存器SP stack point 堆栈指针TCON timer control 定时器控制寄存器TF1(TCON.7)Timer1 flag T1中断标志位TR1(TCON.6)Timer1 Run T1运行控制位TF0 (TCON.5)Timer0 flag T0中断标志位TR0 (TCON.4)Timer0 Run T0运行控制位IE1 (TCON.3) Interrupt1 exterior 外部中断1中断标志位ik'stiəriə adj. 外部的;表面的;外在的n. 外部;表面;外型;外貌MSB = most significant bit//最高有效位IT1 (TCON.2)Interrupt1 touch 外部中断1 触发方式选择位IE0 (TCON.1)Interrupt0 exterior 外部中断0中断标志位IT0 (TCON.0)Interrupt0 touch 0-电平触发1-下降沿触发IE (A8H)interrupt enable 中断允许寄存器EA (IE.7) enable all interrupt 中断总允许位ES (IE.4) enable serial 串行口中断允许位['siəriəl, 'si:r-] adj. 连续的;连载的;分期偿还的n.电视连续剧;[图情] 期刊;连载小说ET0 (IE.1)enable timer 0 T0中断允许位ET1(IE.3)enable timer 1 T1中断允许位EX1 (IE.2)enable exterior 1 外部中断1中断允许位EX0 (IE.0)enable exterior 0 外部中断0中断允许位IP (B8H)interrupt priority 中断优先级寄存器PS (IP.4) priority serial 串口优先级标志位PT1 (IP.3) priority timer 1 定时器1优先级标志位PX1 (IP.2) priority exterior 1 外部中断1优先级标志位PT0 (IP.1) priority timer 0 定时器0优先级标志位PX0 (IP.0) priority exterior 0 外部中断0优先级标志位PCON (87H) power control 电源控制和波特率选择TMOD (89H)timer mode 定时器方式控制寄存器。

ASM-51 宏汇编使用手册

ASM-51 宏汇编使用手册强烈推荐使用配套光盘中的MedWin或Keil开发环境进行编程!其中的A51与这里的ASM51基本相同ASM-51 宏汇编主要用来开发Inter8051系列单片机,它具有宏处理,数据处理,列表处理和条件处理等多种功能。

源程序的编写完全采用 Inter标准助记符和行格式。

在编写程序过程中,可借助于文本编辑(Windows的记事本)或文字处理软件Word等编辑,经ASM-51汇编后生成列表输出文件(.LST)和目标代码文件(.HEX)。

此目标代码文件(.HEX)可直接用CZS-51或MedWin、Keil、Debug8051进行模拟/调试,或直接用于硬件仿真器上运行。

当然,这也是要烧写到单片机ROM中的代码。

1、宏汇编语言的基本语法1、1 宏汇编的特点ASM-51宏汇编完全支持Inter助记符的汇编语言,它含有宏语句,英文大小写字母,变量名,标号等不受限制,有二,十,十六进制和串参数类型,有汇编控制指令和多层条件语句,程序逻辑分段,还有模块化程序设计的连接功能,汇编速度快等特点。

1、2 汇编处理过程(1) 用行编辑EDLIN或文字处理软件WS或全屏幕编辑软件PE等,编辑宏汇编语言源程序,它的文件扩展名为。

ASM。

(2) 用ASM-51宏汇编程序对上述源程序文件进行汇编,产生扩展名为.LST的列表输出文件和扩展名为.HEX的目标代码文件(.HEX)。

列表输出文件包含源程序语句所汇编成的代码,以及有关的地址,语句和符号表等。

目标代码文件包含源程序语句所汇编成的代码,不包含任何符号信息或助记符。

进行模拟/调试,或直接用于硬件仿真器上运行。

1、3 语句汇编语言可分为两类语句:指令性语句和指示性语句。

(1)指令性语句这一类语句是指在汇编过程中能生成指令代码的语句(如 MOV ,DEC等)。

其格式为:[标号:] [指令助记符] [操作数] [;注释]其中方括号[ ]中为选择项。

下同。

51汇编操作手册

行的实际机器指令码。

目标代码文件格式如下:

:cc aaaa tt dd aa dd ss <CR>

计数器 记录地址 数据类型 记录地址 代码的字节 和校验 回车

移量),或者为伪指令中的变量输初值。

为便于程序设计,常量有多种表示形式:二、十、十六进制数和字符串等,它们的格式各不相同,并采用不同的基数标记加以区分。表-

1列出其格式。

表-1

数据形式 格 式 取值范围 示 例 备

注

2进制 ********B 0,1 10110011B

10进制 ****** 0,1,2...9 32768 缺省基数标记

这一类语句即通常所说的伪指令,它指示汇编程序后面的指示性语句如何产生代码。

ASM-51宏汇编完全支持Inter助记符的汇编语言,因此汇编程序的格式,指令完全与8051汇编语言一样,这里不再介绍它们的指令系统。

1、4 常量与数值运算

(1) 常量及其表示

常量,就是在汇编时已经确定的值。 在汇编语言中,常量主要用作指令性语句中的直接操作数 , 也可用于存储器操作的组成部分(如位

综合运算规则 2: 当两个操作数之间没有参数相隔时, 第二个操作符优先于第一个操作符计算。

例如: R1 SET NOT 10011010B

其结果应为 65H。

1、5 程序分段

8051系列的处理器的结构, 把内存分成五个独立的内存段, 即代码段(段名CSEG),数据段(段名DSEG), 外部段(段名XSEG),功能段

EQU 为常量,符号名等定义符号化常量名 符号名不能重名定义

= 为常量,符号名等定义符号化常量名 符号名不能重名定义

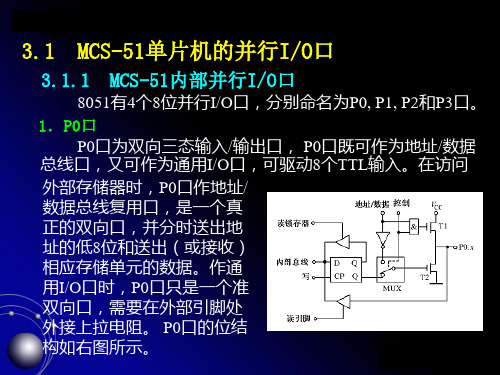

第3章MCS-51单片机的内部资源及应用

MOV P0, A ANL P0, #data ORL P0, A

(2)读端口数据方式: CPU读入的这个数据并非端口引脚线 上的数据。读端口数据可以直接读端口。例如,下面的指 令均可以从P1口输入数据,这是锁存器上的数据。

2.P2口

P2口常用做外部存储器的高8位地址 口。当不用做地址口时,P2口也可作为 通用I/O口,这时它也是一个准双向I/O 口。不必外接上拉电阻就可以驱动任何 MOS驱动电路,且只能驱动4个TTL输 入。P2口的位结构如右图所示。

3.P1口

P1口常用做通用I/O口,它也是一 个标准的准双向I/O口,不必外接上拉 电阻就可以驱动任何MOS驱动电路, 且只能驱动4个TTL输入。P1口的位结 构如右图所示。

制。

(3)中断允许控制寄存器IE (0A8H)

EA

ES ET1 EX1 ET0 EX0

(3)中断允许控制寄存器IE (0A8H)

中断与子程序的最主要区别:子程序是预先安排好的,中断 是随机发生的。

中断涉及的几个环节:中断源、 中断申请、开放中断、保护 现场、中断服务、恢复现场、中断返回。

2. 中断源

中断源是指引起中断的设备或事件,或发出中断请求的源头。

3. 中断的分类

中断按功能通常可分为可屏蔽中断、非屏蔽中断和软件中断三类。 可屏蔽中断是指CPU可以通过指令来允许或屏蔽中断的请求。 非屏蔽中断是指CPU对中断请求是不可屏蔽的,一旦出现,CPU必须响应。 软件中断则是指通过相应的中断指令使CPU响应中断。

1.I/O口直接用于输入/输出

在I/O口直接用做输入/输出时,CPU既可以把它们看做数据口,也可以看 做状态口,这是由用户决定的。

经典51单片机实用子程序库(二)

51单片机实用子程序库(二)MCS-51浮点运算子程序库及其使用说明本浮点子程序库有三个不同层次的版本,以便适应不同的应用场合:1.小型库(FQ51A.ASM):只包含浮点加、减、乘、除子程序。

2.中型库(FQ51B.ASM):在小型库的基础上再增加绝对值、倒数、比较、平方、开平方、数制转换等子程序。

3.大型库(FQ51.ASM):包含本说明书中的全部子程序。

为便于读者使用本程序库,先将有关约定说明如下:1.双字节定点操作数:用[R0]或[R1]来表示存放在由R0或R1指示的连续单元中的数据,地址小的单元存放高字节。

如果[R0]=1234H,若(R0)=30H,则(30H)=12H,(31H)=34H。

2.二进制浮点操作数:用三个字节表示,第一个字节的最高位为数符,其余七位为阶码(补码形式),第二字节为尾数的高字节,第三字节为尾数的低字节,尾数用双字节纯小数(原码)来表示。

当尾数的最高位为1时,便称为规格化浮点数,简称操作数。

在程序说明中,也用[R0]或[R1]来表示R0或R1指示的浮点操作数,例如:当[R0]=-6.000时,则二进制浮点数表示为83C000H。

若(R0)=30H,则(30H)=83H,(31H)=0C0H,(32H)=00H。

3.十进制浮点操作数:用三个字节表示,第一个字节的最高位为数符,其余七位为阶码(二进制补码形式),第二字节为尾数的高字节,第三字节为尾数的低字节,尾数用双字节BCD码纯小数(原码)来表示。

当十进制数的绝对值大于1时,阶码就等于整数部分的位数,如 876.5 的阶码是03H,-876.5 的阶码是 83H;当十进制数的绝对值小于1时,阶码就等于 80H 减去小数点后面零的个数,例如 0.00382 的阶码是 7EH,-0.00382的阶码是 0FEH。

在程序说明中,用[R0]或[R1]来表示R0或R1指示的十进制浮点操作数。

例如有一个十进制浮点操作数存放在30H、31H、32H中,数值是 -0.07315,即-0.7315乘以10的-1次方,则(30H)=0FFH,31H=73H,(32H)=15H。

51单片机的硬件结构

12

• ALE/PROG(30脚):当访问单片机外 部存储器时,ALE(地址锁存允许)输 出脉冲的下降沿用于16位地址的低8位的 锁存信号。

即使不访问外部锁存器,ALE端仍有正脉 冲信号输出,此频率约为时钟振荡器频率的 1/6。但在执行某些指令时会不发出ALE信号, 因而用户不能用做时钟源或定时。

13

• PSEN(29脚):是访问外部程序存储器的读 选通信号。

• EA(31脚):当EA端保持高电平时,51先访 问内部程序存储器,但在PC(程序计数器)值 超过0FFFH时(对于8051、8751来说),将自 动转向执行外部程序存储器内的程序。 当EA保持低电平时,不管是否有内部程序存储 器,只访问外部程序存储器。

16

运算部件:ALU、A、B

• ALU:功能强大,它不仅可对8位变量进行逻 辑“与、或、异或”、循环、求补和清零等基 本操作,还可以进行加、减、乘、除等基本运 算,ALU还具有位处理操作,如置位、清零、 求补、测试。转移及逻辑“与、或”等操作。

• 累加器A:ALU中的主要寄存器,大部分指令 都用到它。

MCS51存储器结构示意

42

I/O端口

• 简介

MCS51单片机具有4个双向8位I/O口,每个口都有 一个锁存器。

P0口是三态双向口,作为数据和低8位地址的分时 复用口,由ALE信号作为地址锁存。

P1口准双向口,供用户使用。 P2口准双向口,作为高8位地址使用,当扩展的外 部存储器小于64k时,即有未用到的P2口线,可作为一 般I/O口使用。 P3口准双向口,即可作为一般I/O口使用,也可作 为第二功能口使用。

• 时序图

每2个振荡周期作为1个状态周期,每个状态周期分 为2个时相P1、P2,每6个状态周期作为1个机器周期。