74HCT595BQ

74HC595中文手册(手工翻译,可复制)

74HC595/74HCT595

它是带控制端的8位串行输入并行输入的移位寄存器,具有3态输出。

特点

➢8位串行输入

➢8位串行或并行输出

➢带有3态输出的存储寄存器

➢移位寄存器具有清零控制端

➢100MHz移位输出频率

➢输出能力:并行输出,总线驱动;串行输出,标准输出

应用

串行数据转并行

远程控制保持寄存器

相关描述

74HC/HCT595是高速硅栅CMOS元件与低功耗肖特基TTL引脚兼容。

它们符合JEDEC第7A号标准。

“595”是一个带存储器的8级串行移位寄存器,有3态输出。

移位寄存器以及存储寄存器有独立的时钟输入端。

当SH_CP端接收一个上跳沿时数据会发生移位。

当ST_CP端接收一个上跳沿时,移位寄存器中的数据将被送入存储寄存器。

当SH_CP端和ST_CP端短接时,移位寄存器当中所存储的数据将会永远比存储寄存器中的数据状态早一个时钟周期。

移位寄存器有一个串行输入(DS端)以及一个标准的串行级联输出端(Q7’)。

该芯片的8位移位寄存器有一个复位引脚(MR,低电平有效)。

存储寄存器有8条并行的3态总线连接至输出引脚。

只要芯片的输出使能引脚(OE)处于低电平,芯片就实时将存储寄存器中的数据输出至输出引脚。

595芯片中文资料

8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。

三态。

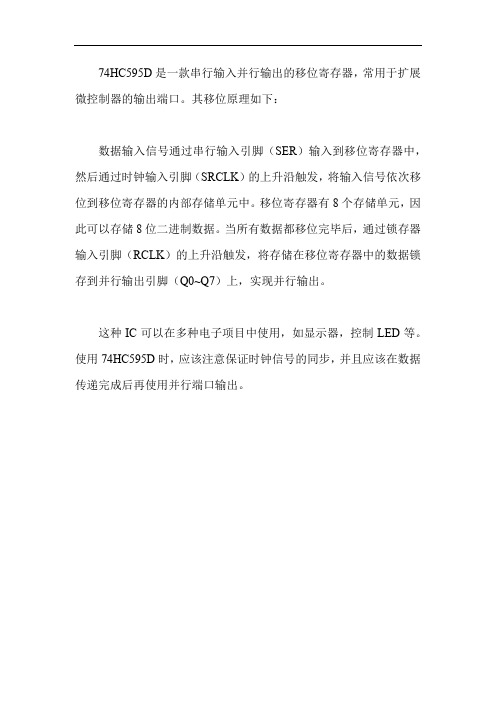

特点8位串行输入,8位串行或并行输出,存储状态寄存器,三种状态输出寄存器可以直接清除100MHz的移位频率输出能力,并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换Remote control holding register.描述595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

参考数据符号参数条件 TYP 单位HC HCt ,tPHL/tPLH 传输延时,SHcp到Q7’,STcp到Qn,MR到Q7’,CL=15pF,Vcc=5V,16,17,14, 21,20,19 Ns,Ns,Ns,fmax STcp到SHcp 最大时钟速度100,57 MHz,CL 输入电容Notes 1 3.5 , 3.5 pFCPD Power dissipation capacitance per package. Notes2 115 130 pF,CPD决定动态的能耗,PD=CPD×VCC×f1+∑(CL×VCC2×f0)F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述Q0…Q7 15, 1, 7 并行数据输出,GND 8 地,Q7’ 9 串行数据输出,MR 10 主复位(低电平),SHCP 11 移位寄存器时钟输入,STCP 12 存储寄存器时钟输入,OE 13 输出有效(低电平),DS 14 串行数据输入,VCC 16 电源功能表输入输出功能SHCP STCP OE MR DS Q7’ Qn× × L ↓ × L NC MR为低电平时紧紧影响移位寄存器× ↑ L L × L L 空移位寄存器到输出寄存器× × H L × L Z 清空移位寄存器,并行输出为高阻状态↑ × L H H Q6’ NC 逻辑高电平移入移位寄存器状态0,包含所有的移位寄存器状态移入,例如,以前的状态6(内部Q6”)出现在串行输出位。

74HC595 74HCT595 8位串行输入、串行或并行输出的移位寄存器说明书

74HC595; 74HCT5958-bit serial-in, serial or parallel-out shift register with outputlatches; 3-stateRev. 9 — 28 February 2017Product data sheet 1General descriptionThe 74HC595; 74HCT595 is an 8-bit serial-in/serial or parallel-out shift register with astorage register and 3-state outputs. Both the shift and storage register have separateclocks. The device features a serial input (DS) and a serial output (Q7S) to enablecascading and an asynchronous reset MR input. A LOW on MR will reset the shiftregister. Data is shifted on the LOW-to-HIGH transitions of the SHCP input. The data inthe shift register is transferred to the storage register on a LOW-to-HIGH transition ofthe STCP input. If both clocks are connected together, the shift register will always beone clock pulse ahead of the storage register. Data in the storage register appears atthe output whenever the output enable input (OE) is LOW. A HIGH on OE causes theoutputs to assume a high-impedance OFF-state. Operation of the OE input does notaffect the state of the registers. Inputs include clamp diodes. This enables the use ofcurrent limiting resistors to interface inputs to voltages in excess of V CC.2Features and benefits•8-bit serial input•8-bit serial or parallel output•Storage register with 3-state outputs•Shift register with direct clear•100 MHz (typical) shift out frequency•Complies with JEDEC standard no. 7A•Input levels:–For 74HC595: CMOS level–For 74HCT595: TTL level•ESD protection:–HBM JESD22-A114F exceeds 2000 V–MM JESD22-A115-A exceeds 200 V•Multiple package options•Specified from -40 °C to +85 °C and from -40 °C to +125 °C3Applications•Serial-to-parallel data conversion•Remote control holding register8-bit serial-in, serial or parallel-out shift register with output latches; 3-state 4Ordering information5Functional diagram8-bit serial-in, serial or parallel-out shift register with output latches; 3-state8-bit serial-in, serial or parallel-out shift register with output latches; 3-state6Pinning information6.1Pinning74HC59574HCT595Q1V CC Q2Q0Q3DS Q4OE Q5STCP Q6SHCP Q7MR GNDQ7S001aao24212345678109121114131615Figure 5. Pin configuration for SO16, SSOP16 and TSSOP16001aao24374HC59574HCT595Q7MRQ6SHCP Q5STCP Q4OE Q3DS Q2Q0G N DQ 7S Q 1V C CTransparent top view71061151241331421589116terminal 1index areaGND (1)(1) This is not a supply pin. The substrate is attached to this pad using conductive die attach material. There is no electrical or mechanical requirement to solder this pad.However, if it is soldered, the solder land should remain floating or be connected to GND.Figure 6. Pin configuration for DHVQFN166.2Pin description8-bit serial-in, serial or parallel-out shift register with output latches; 3-state7Functional description[1][1]H = HIGH voltage state;L = LOW voltage state;↑ = LOW-to-HIGH transition;X = don’t care;NC = no change;Z = high-impedance OFF-state.8-bit serial-in, serial or parallel-out shift register with output latches; 3-state 8Limiting valuesTable 4. Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).[1]For SO16 package: P tot derates linearly with 8 mW/K above 70 °C.[2]For SSOP16 and TSSOP16 packages: P tot derates linearly with 5.5 mW/K above 60 °C.[3]For DHVQFN16 package: P tot derates linearly with 4.5 mW/K above 60 °C.9Recommended operating conditions8-bit serial-in, serial or parallel-out shift register with output latches; 3-state 10Static characteristicsTable 6. Static characteristicsAt recommended operating conditions; voltages are referenced to GND (ground = 0 V).8-bit serial-in, serial or parallel-out shift register with output latches; 3-state8-bit serial-in, serial or parallel-out shift register with output latches; 3-state 11Dynamic characteristicsTable 7. Dynamic characteristicsVoltages are referenced to GND (ground = 0 V); for test circuit see Figure 13.8-bit serial-in, serial or parallel-out shift register with output latches; 3-state8-bit serial-in, serial or parallel-out shift register with output latches; 3-state[1]Typical values are measured at nominal supply voltage.[2]t pd is the same as t PHL and t PLH.[3]t en is the same as t PZL and t PZH.[4]t dis is the same as t PLZ and t PHZ.[5]C PD is used to determine the dynamic power dissipation (P D in μW).P D = C PD × V CC2 × f i + Σ(C L × V CC2 × f o) where:f i = input frequency in MHz;f o = output frequency in MHz;Σ(C L × V CC2 × f o) = sum of outputs;C L = output load capacitance in pF;V CC = supply voltage in V.[6]All 9 outputs switching.11.1Waveforms and test circuit8-bit serial-in, serial or parallel-out shift register with output latches; 3-state8-bit serial-in, serial or parallel-out shift register with output latches; 3-state8-bit serial-in, serial or parallel-out shift register with output latches; 3-state8-bit serial-in, serial or parallel-out shift register with output latches; 3-state 12Package outline8-bit serial-in, serial or parallel-out shift register with output latches; 3-state8-bit serial-in, serial or parallel-out shift register with output latches; 3-state8-bit serial-in, serial or parallel-out shift register with output latches; 3-state8-bit serial-in, serial or parallel-out shift register with output latches; 3-state 13Abbreviations14Revision history8-bit serial-in, serial or parallel-out shift register with output latches; 3-state 15Legal information15.1 Data sheet status[1]Please consult the most recently issued document before initiating or completing a design.[2]The term 'short data sheet' is explained in section "Definitions".[3]The product status of device(s) described in this document may have changed since this document was published and may differ in case of multipledevices. The latest product status information is available on the Internet at URL .15.2 DefinitionsDraft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local Nexperia sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.Product specification — The information and data provided in a Product data sheet shall define the specification of the product as agreed between Nexperia and its customer, unless Nexperia and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the Nexperia product is deemed to offer functions and qualities beyond those described in the Product data sheet.15.3 DisclaimersLimited warranty and liability — Information in this document is believed to be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracyor completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes no responsibility for the content in this document if provided by an information source outside of Nexperia. In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation -lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.Right to make changes — Nexperia reserves the right to make changesto information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.Suitability for use — Nexperia products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunctionof an Nexperia product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer’s own risk.Applications — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer’s sole responsibility to determine whether the Nexperia product is suitable and fit for the customer’s applications and products planned, as well as for the planned application and use of customer’s third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer’s applications or products, or the application or use by customer’s third party customer(s). Customer is responsible for doing all necessary testing for the customer’s applications and products using Nexperia products in order to avoid a default of the applications and the products or of the application or use by customer’s third party customer(s). Nexperia does not accept any liability in this respect.Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above thosegiven in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.Terms and conditions of commercial sale — Nexperia products aresold subject to the general terms and conditions of commercial sale, as published at /profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Nexperia hereby expressly objects to applying the customer’s general terms and conditions with regard to the purchase of Nexperia products by customer.No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance orthe grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.Export control — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.8-bit serial-in, serial or parallel-out shift register with output latches; 3-state74HC_HCT595All information provided in this document is subject to legal disclaimers.© Nexperia B.V. 2017. All rights reserved.Product data sheet Rev. 9 — 28 February 201721 / 22Non-automotive qualified products — Unless this data sheet expressly states that this specific Nexperia product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. Nexperia accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications. In the event that customeruses the product for design-in and use in automotive applications toautomotive specifications and standards, customer (a) shall use the productwithout Nexperia's warranty of the product for such automotive applications,use and specifications, and (b) whenever customer uses the product forautomotive applications beyond Nexperia's specifications such use shall besolely at customer’s own risk, and (c) customer fully indemnifies Nexperiafor any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond Nexperia'sstandard warranty and Nexperia's product specifications.Translations — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancybetween the translated and English versions.15.4 Trademarks Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.8-bit serial-in, serial or parallel-out shift register with output latches; 3-statePlease be aware that important notices concerning this document and the product(s)described herein, have been included in section 'Legal information'.© Nexperia B.V. 2017.All rights reserved.For more information, please visit: Forsalesofficeaddresses,pleasesendanemailto:***************************Date of release: 28 February 2017Document identifier: 74HC_HCT595Contents1General description ............................................12Features and benefits .........................................13Applications .........................................................14Ordering information ..........................................25Functional diagram .............................................26Pinning information ............................................46.1Pinning ...............................................................46.2Pin description ...................................................47Functional description ........................................58Limiting values ....................................................69Recommended operating conditions ................610Static characteristics ..........................................711Dynamic characteristics .....................................911.1Waveforms and test circuit ..............................1112Package outline .................................................1513Abbreviations ....................................................1914Revision history ................................................1915Legal information . (20)Mouser ElectronicsAuthorized DistributorClick to View Pricing, Inventory, Delivery & Lifecycle Information:N experia:74HC595BQ,11574HC595D,11274HC595DB,11274HC595DB,11874HC595D,11874HC595N,11274HC595PW,11274HC595PW,11874HCT595BQ,11574HCT595D,11274HCT595DB,11274HCT595DB,118 74HCT595D,11874HCT595N,11274HCT595PW,11274HCT595PW,11874HC595PW/AUJ。

74_HC595用法

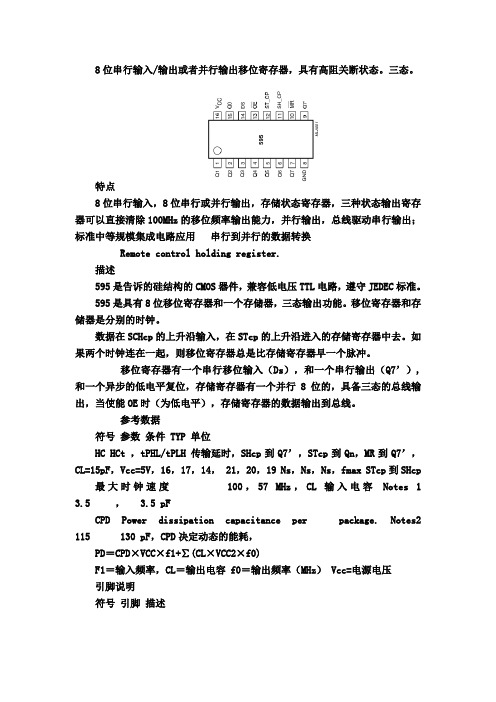

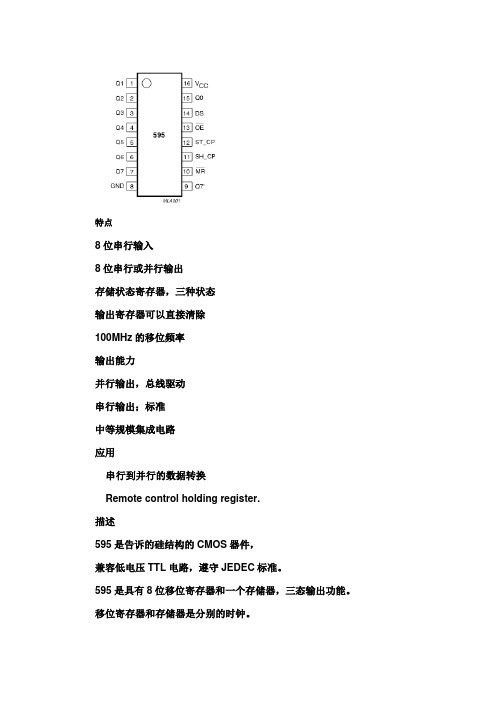

内部结构结合引脚说明就能很快理解595的工作情况74LS595,74HC595引脚图,管脚图QB--|1 16|--VccQC--|2 15|--QAQD--|3 14|--SI串行数据输入端QE--|4 13|--/GQF--|5 12|--RCKQG--|6 11|--SRCKQH--|7 10|--/SRCLRGND- |8 9|--QH'级联输出端|________|74595的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

QH': 级联输出端。

我将它接下一个595的SI端。

SI: 串行数据输入端。

74595的控制端说明:/SRCLR(10脚): 低电平时将移位寄存器的数据清零。

通常我将它接Vcc。

SRCK(11脚):上升沿时数据寄存器的数据移位。

QA-->QB-->QC-->...-->QH;下降沿移位寄存器数据不变。

(脉冲宽度:5V时,大于几十纳秒就行了。

我通常都选微秒级)RCK(12脚):上升沿时移位寄存器的数据进入数据存储寄存器,下降沿时存储寄存器数据不变。

(通常我将RCK置为低电平,) 当移位结束后,在RCK端产生一个正脉冲(5V时,大于几十纳秒就行了。

我通常都选微秒级),更新显示数据。

/G(13脚): 高电平时禁止输出(高阻态)。

如果单片机的引脚不紧张,用一个引脚控制它,可以方便地产生闪烁和熄灭效果。

比通过数据端移位控制要省时省力。

注:74164和74595功能相仿,都是8位串行输入转并行输出移位寄存器。

74164的驱动电流(25mA)比74595(35mA)的要小,14脚封装,体积也小一些。

74595的主要优点是具有数据存储寄存器,在移位的过程中,输出端的数据可以保持不变。

这在串行速度慢的场合很有用处,数码管没有闪烁感。

与164只有数据清零端相比,595还多有输出端时能/禁止控制端,可以使输出为高阻态。

注:1)74164和74595功能相仿,都是8位串行输入转并行输出移位寄存器。

74HC595史上最全的中文资料【中为电科】

X X 注:

X X

H L L L

L H H H

X H X X

L Q6S NC Q6S

Z NC QnS QnS

清空移位寄存器,并行输出高阻态 移位寄存器数据分别移动一位; 第 6 位数据 移入 Q7S 移位寄存器的内容传给存储寄存器并输出 移位寄存器的所有数据移动一位; 移位寄存 器中的所有数据转入存储寄存器并输出

7. 8. 9. 10. 11. 12. 13.

1 / 15

科技效法自然 中为电科

74HC595;74HCT595

8 位串行输入,串行或并行输出移位寄存器,输出具有锁存、三态功能

1. 简介

74HC595、 74HCT595 是一款高速硅栅 (Si‐gate) COMS 器件, 并且与低压肖特基 TTL (LSTTL) 兼容。它们符合 JEDEC 7A 号文件标准。 74HC595、74HCT595 是一个 8 位串行并且带有存储寄存器和三态输出的移位寄存器, 存储寄存器和移位寄存器同步于不同的时钟。 数据在移位寄存器时钟(SHCP)的正跳变下移动,在存储寄存器时钟(STCP)的正跳 变下数据由移位寄存器转存到存储寄存器。假如 SHCP 和 STCP 被连在一起,移位寄存器将 总是超前于存储寄存器一个时钟脉冲。 移位寄存器有一个串行输入端(DS) ,还有一个用于级联的串行输出端。8 位移位寄存 器可以异步复位 (低电平复位) 。 存储寄存器有一个 8 位三态并行输出端。 当输出使能端 (OE) 被使能(低有效)数据将从存储寄存器中输出至器件引脚。

4 / 15

科技效法自然 中为电科

6. 引脚定义

6.1 引脚图

图 4 引脚定义 6.2 引脚描述 符号 Q1 Q2 Q3 Q4 Q5 Q6 Q7 GND Q7S MR SHCP STCP OE DS Q0 Vcc 引脚号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 地(0V) 数据串行输出 复位(低有效) 移位寄存器时钟(输入) 存储寄存器时钟(输入) 输出使能(低有效) 数据串行输入 数据并行输出 0 电源 数据并行输出 1 ~ 7 描述

中微爱芯逻辑芯片通用系列AIP74HC,AIP74HCT

中微爱芯逻辑芯片通用系列AIP74HC,AIP74HCTAIP74HC138概述AIP74HC138是高速CMOS电路,管脚与LSTTL系列兼容。

AIP74HC138译码器有3个二进制加权地址输入端(A0,A1,A2),当输入有效时,输出8个互相独立的低电平有效的输出信号(Y0~Y7)。

AIP74HC138 有3个使能输入端:2个低电平有效(E1和E2)和1个高电平有效(E3)。

如果使能输入端无效,每个输出都为高。

芯片的多路使能功能方便AIP74HC138进行并行扩展,扩展成为一个32位译码器仅需要4只AIP74HC138 和一个反向器。

利用AIP74HC138的一个低有效输入作为数据输入,其他使能输入端作为信号输入的关闭闸门,AIP74HC138 可作为8输出的信号分离器。

其主要特点如下:●较宽的工作电压:2~6V●输出能驱动10个LSTTL负载●工作温度分两档:-40℃~+85℃;-40℃~+125℃●可作信号分离●多路使能功能方便扩展●可作为内存芯片的选择解码芯片●互相独立的低电平有效的输出信号●封装形式:DIP16 / SOP162.2、引脚排列图AiP74HC / HCT04概述AiP74HC / HCT04是一个十六进制逆变器。

输入端包括钳位二极管,这些钳位二极管允许使用限流电阻将输入端连接到超过VCC的电压。

主要特点:●输入级别:●对于AiP74HC04:CMOS级别●对于AiP74HCT04:TTL电平●规定温度为-40℃至+ 85℃●包装信息:DIP14 / SOP14 / TSSOP14引脚排列图AiP74HC HCT245概述AiP74HC / HCT245是具有三态输出的8位收发器。

该器件具有一个输出使能OE和用于方向控制的发送/接收(DIR)。

OE上的高电平会导致输出呈现高阻态关断状态。

输入包括钳位二极管。

这样就可以使用限流电阻将输入接口连接到超过VCC的电压。

主要特点:输入级别:对于AiP74HC245:CMOS级别对于AiP74HCT245:TTL电平八路双向总线接口同相三态输出多种包装选择规定温度为-40℃至+ 85℃包装信息:DIP20 / SOP20 / TSSOP20引脚排列图概述AiP74HC164是高速CMOS电路,管脚与低功耗肖特基TTL (LSTTL)系列兼容。

74HC_HCT595

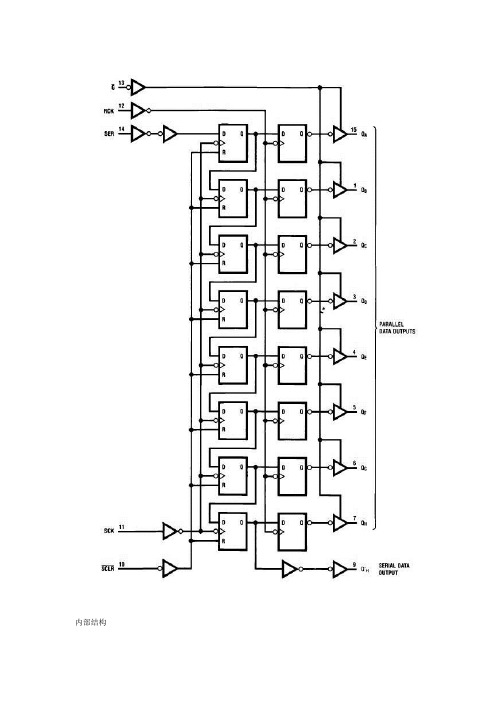

M54HC595M74HC595April 19938BIT SHIFT REGISTER WITH OUTPUT LATCHES (3STATE)B1R(Plastic Package)ORDER CODES :M54HC595F1R M74HC595M1R M74HC595B1R M74HC595C1RF1R(Ceramic Package)M1R(Micro Package)C1R (Chip Carrier)PIN CONNECTIONS (top view)NC =No Internal Connecti o n.HIGH SPEEDf MAX =55MHz (TYP.)AT V CC =5V .LOW POWER DISSIPATION I CC =4µA (MAX.)AT T A =25°C .HIGH NOISE IMMUNITYV NIH =V NIL =28%V CC (MIN.).OUTPUT DRIVE CAPABILITY15LSTTL LOADS FOR QA TO QH 10LSTTL LOADS FOR QH’.SYMMETRICAL OUTPUT IMPEDANCE |I OH |=I OL =6mA (MIN.)FOR QA TO QH |I OH |=I OL =4mA (MIN.)FOR QH’.BALANCED PROPAGATION DELAYS t PLH =t PHL.WIDE OPERATING VOLTAGE RANGE V CC (OPR)=2V TO 6V.PIN AND FUNCTION COMPATIBLE WITH LSTTL 54/74LS595DESCRIPTIONThe M54/74HC595is a high speed CMOS 8-BITSHIFT REGISTERS/OUTPUT LATCHES (3-STATE)fabricated in silicon C 2MOS technology.It has the same high speed performance of LSTTL combined with true CMOS low power consumption.This device contains an 8-bit serial-in,parallel -out shift register that feeds an 8-bit D-type storage reg-ister.The storage register has 83-STATE outputs.Separate clocks are provided for both the shift reg-ister and the storage register.The shift register has a direct-overriding clear,serial input,and serial output (standard)pins for cascad-ing.Both the shift register and storage register use positive-edge triggered clocks.If both clocks are connected together,the shift register state will al-ways be one clock pulse ahead of the storage reg-ister.All inputs are equipp ed with protection circuits against static discharge and transient excess volt-age.1/13INPUT AND OUTPUT EQUIVALENT CIRCUITTRUTH TABLEINPUTSOUTPUT SI SCK SCLR RCK GX X X X H QA THRU QH OUTPUTS DISABLE X X X X L QA THRU QH OUTPUTS ENABLE X X L X X SHIFT REGISTER IS CLEAREDL H X X FIRST STAGE OF S.R.BECOMES”L”OTHER STAGES STORE THE DATA OF PREVIOUS STAGE,RESPECTIVELYH H X X FIRST STAGE OF S.R.BECOMES”H”OTHER STAGES STORE THE DATA OF PREVIOUS STAGE,RESPECTIVELYX H X X STATE OF S.R IS NOT CHANGEDX X X X S.R.DATA IS STORED INTO STORAGE REGISTER X X X X STORAGE REGISTER STATE IS NOT CHANGED X:DON’T CARELOGIC DIAGRAMM54/M74HC5952/13M54/M74HC595 LOGIC DIAGRAMTIMING CHART3/13IEC LOGIC SYMBOLABSOLUTE MAXIMUM RATINGSSymbol ParameterValue Unit V CCSupply Voltage -0.5to +7V V I DC Input Voltage -0.5to V CC +0.5V V O DC Output Voltage-0.5to V CC +0.5V I IK DC Input Diode Current ±20mA I OK DC Output Diode Current±20mA I O DC Output Current Per Output Pin QA-QH ±35mA I O DC Output Current Per Output Pin QH’±25mA I CC or I GNDDC V CC or Ground Current ±70mA P D Power Dissipation 500(*)mW T stg Storage Temperature -65to +150o CT LLead Temperature (10sec)300oCAbsolute Maximum Ratings are those values beyond whichdamage to the device may occu r.Functiona l ope ration und er these cond ition isnotimplied.(*)500mW:≅65o C derate to 300mW by 10mW/o C:65o C to 85o CRECOMMENDED OPERATING CONDITIONSSymbol ParameterValue Unit V CCSupply Voltage 2to 6V V I Input Voltage0to V CC V V O Output Voltage0to V CC V T op Operating Temperature:M54HC SeriesM74HC Series-55to +125-40to +85oC o C t r ,t fInput Rise and Fall TimeV CC =2V 0to 1000nsV CC =4.5V 0to 500V CC =6V0to 400PIN DESCRIPTIONPIN No SYMBOL NAME AND FUNCTION 1,2,3,4,5,6,7,15QA to QH Data Outputs 9QH’Serial Data Outputs 10SCLR Shift Register Clear Input11SCK Shift Register Clock Input13G Output Enable Input 14SI Serial Data Input 12RCK Storage Register Clock Input8GND Ground (0V)16V CCPositive Supply VoltageM54/M74HC5954/13DC SPECIFICATIONSSymbol ParameterTest Conditions ValueUnit V CC(V)T A=25o C54HC and74HC-40to85o C74HC-55to125o C54HCMin.Typ.Max.Min.Max.Min.Max.V IH High Level InputVoltage 2.0 1.5 1.5 1.5V 4.5 3.15 3.15 3.156.0 4.2 4.2 4.2V IL Low Level InputVoltage 2.00.50.50.5V 4.5 1.35 1.35 1.356.0 1.8 1.8 1.8V OH High LevelOutput Voltage(for QH’output)2.0V I=V IHorV ILI O=-20µA1.92.0 1.9 1.9V 4.5 4.4 4.5 4.4 4.46.0 5.9 6.0 5.9 5.94.5I O=-4.0mA 4.18 4.31 4.13 4.106.0I O=-5.2mA 5.68 5.8 5.63 5.60V OH High LevelOutput Voltage(for QA to QHoutputs)2.0V I=V IHorV ILI O=-20µA1.92.0 1.9 1.9V 4.5 4.4 4.5 4.4 4.46.0 5.9 6.0 5.9 5.94.5I O=-6.0mA 4.18 4.31 4.13 4.106.0I O=-7.8mA 5.68 5.8 5.63 5.60V OL Low Level OutputVoltage(for QH’output)2.0V I=V IHorV ILI O=20µA0.00.10.10.1V 4.50.00.10.10.16.00.00.10.10.14.5I O=4.0mA0.170.260.330.406.0I O=5.2mA0.180.260.330.40V OL Low Level OutputVoltage(for QA to QHoutputs)2.0V I=V IHorV ILI O=20µA0.00.10.10.1V 4.50.00.10.10.16.00.00.10.10.14.5I O=6.0mA0.170.260.330.406.0I O=7.8mA0.180.260.330.40I I Input LeakageCurrent 6.0V I=V CC or GND±0.1±1±1µAI OZ3State OutputOff State Current 6.0V I=V IH or V ILV O=V CC or GND±0.5±5±10µAI CC Quiescent SupplyCurrent 6.0V I=V CC or GND44080µAM54/M74HC5955/13AC ELECTRICAL CHARACTERISTICS(C L=50pF,Input t r=t f=6ns)Symbol ParameterTest Conditions ValueUnit V CC(V)C L(pF)T A=25o C54HC and74HC-40to85o C74HC-55to125o C54HCMin.Typ.Max.Min.Max.Min.Max.t TLH t THL Output TransitionTime(Qn)2.05025607590ns4.571215186.06101315t TLH t THL Output TransitionTime(QH’)2.050307595115ns4.581519236.07131620t PLH t PHL PropagationDelay Time(SCK-QH’)2.05045125155190ns4.5152531386.013212632t PLH t PHL PropagationDelay Time(SCLR-QH’)2.05060175220265ns4.5183544536.015303745t PLH t PHL PropagationDelay Time(RCK-Qn)2.05060150190225ns4.5203038456.0172632382.015075190240285ns4.5253848576.022324148t PZL t PZH 3State OutputEnable Time2.050R L=1KΩ45135170205ns4.5152734416.0132329352.0150R L=1KΩ60175220265ns4.5203544536.017303745t PLZ t PHZ 3State OutputDisable Time2.050R L=1KΩ30150190225ns4.5153038456.014263238f MAX Maximum ClockFrequency 2.0506.017 4.84ns 4.5305024206.0355928242.01505.214 4.2 3.4ns 4.5264021176.031452520t W(H)Minimum PulseWidth(SCK,RCK)2.050177595110ns 4.561519226.06131619t W(L)Minimum PulseWidth(SCLR)2.050207595110ns 4.561519226.06131619t s Minimum Set-upTime(SI-CCK)2.05025506575ns 4.551013156.0491113M54/M74HC595 6/13AC ELECTRICAL CHARACTERISTICS(C L=50pF,Input t r=t f=6ns)Symbol ParameterTest Conditions ValueUnit V CC(V)C L(pF)T A=25o C54HC and74HC-40to85o C74HC-55to125o C54HCMin.Typ.Max.Min.Max.Min.Max.t s Minimum Set-upTime(SCK-RCK)2.050357595110ns 4.581519226.06131619t s Minimum Set-upTime(SCRL-RCK)2.05040100125145ns 4.5102025296.07172125t h Minimum HoldTime 2.050000ns 4.50006.0000t REM Minimum ClearRemuval Time 2.05015506575ns 4.531013156.0391113C IN Input Capacitance5101010pFC PD(*)Power DissipationCapacitance 184pF(*)C PD is defined as the value of the IC’s internal equivalent capac itanc e which is calculated from the operating current con sump tion without load. (Refer to Test Circuit).Average operting current can be obtained by the following equ ation.I CC(opr)=C PD•V CC•f IN+I CCSWITCHING CHARACTERISTICS TEST WAVEFORMWAVEFORM1WAVEFORM2M54/M74HC5957/13M54/M74HC595SWITCHING CHARACTERISTICS TEST WAVEFORM(continued)WAVEFORM3WAVEFORM4WAVEFORM5WAVEFORM6GNDV CCTEST CIRCUIT I CC(Opr.)INPUT WAVEFORM8/13M54/M74HC595 Plastic DIP16(0.25)MECHANICAL DATAmm inchDIM.MIN.TYP.MAX.MIN.TYP.MAX.a10.510.020B0.77 1.650.0300.065b0.50.020b10.250.010D200.787E8.50.335e 2.540.100e317.780.700F7.10.280I 5.10.201L 3.30.130Z 1.270.050P001C9/13M54/M74HC595Ceramic DIP16/1MECHANICAL DATAmm inch DIM.MIN.TYP.MAX.MIN.TYP.MAX.A200.787 B70.276D 3.30.130E0.380.015e317.780.700F 2.29 2.790.0900.110G0.40.550.0160.022H 1.17 1.520.0460.060L0.220.310.0090.012 M0.51 1.270.0200.050 N10.30.406 P7.88.050.3070.317 Q 5.080.200P053D 10/13M54/M74HC595 SO16(Narrow)MECHANICAL DATAmm inchDIM.MIN.TYP.MAX.MIN.TYP.MAX.A 1.750.068a10.10.20.0040.007a2 1.650.064b0.350.460.0130.018b10.190.250.0070.010C0.50.019c145°(typ.)D9.8100.3850.393E 5.8 6.20.2280.244e 1.270.050e38.890.350F 3.8 4.00.1490.157G 4.6 5.30.1810.208L0.5 1.270.0190.050M0.620.024S8°(max.)P013H11/13M54/M74HC595PLCC20MECHANICAL DATAmm inch DIM.MIN.TYP.MAX.MIN.TYP.MAX.A9.7810.030.3850.395 B8.899.040.3500.356D 4.2 4.570.1650.180d1 2.540.100d20.560.022E7.378.380.2900.330e 1.270.050e3 5.080.200F0.380.015G0.1010.004 M 1.270.050M1 1.140.045P027A 12/13M54/M74HC595 Information furnished is believed to be accurate and reliable.However,SGS-THOMSON Microelectronics assumes no responsability for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may results from its use.No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics.Specificationsmentioned in this publication are subject to change without notice.This publication supersedes and replaces all information previously supplied.SGS-THOMSON Microelectronics products are not authorized for use ascritical components in life support devices or systems without express written approval of SGS-THOMSON Microelectonics.©1994SGS-THOMSON Microelectronics-All Rights ReservedSGS-THOMSON Microelectronics GROUP OF COMPANIESAustralia-Brazil-France-Germany-Hong Kong-Italy-Japan-Korea-Malaysia-Malta-Morocco-The Netherlands-Singapore-Spain-Sweden-Switzerland-Taiwan-Thailand-United Kingdom-U.S.A13/13This datasheet has been downloaded from: Datasheets for electronic components.。

74HC595D中文资料_数据手册_参数

NXP Semiconductors

74HC595; 74HCT595

8-bit serial-in, serial or parallel-out shift register with output latches; 3-state

11 12

SHCP STCP

14 DS

Q7S 9 15

All information provided in this document is subject to legal disclaimers.

Rev. 6 — 12 December 2011

© NXP B.V. 2011. All rights reserved.

3 of 24

NXP Semiconductors

Fig 7. Pin configuration for DHVQFN16

74HC_HCT595

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 6 — 12 December 2011

16 VCC 15 Q0 14 DS 13 OE 12 STCP 11 SHCP 10 MR 9 Q7S

001aao241

Fig 5. Pin configuration DIP16, SO16

74HC595 74HCT595

Q1 1 Q2 2 Q3 3 Q4 4 Q5 5 Q6 6 Q7 7 GND 8

5. Functional diagram

14 DS 11 SHCP 10 MR

8-STAGE SHIFT REGISTER

SN74AHCT595DR资料

PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)SN74AHCT595D ACTIVE SOIC D1640Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT595DBR ACTIVE SSOP DB162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT595DBRE4ACTIVE SSOP DB162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT595DE4ACTIVE SOIC D1640Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT595DR ACTIVE SOIC D162500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT595DRE4ACTIVE SOIC D162500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT595N ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeSN74AHCT595NE4ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeSN74AHCT595NSR ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT595NSRE4ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT595PW ACTIVE TSSOP PW1690Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT595PWE4ACTIVE TSSOP PW1690Green(RoHS&no Sb/Br)CUNIPDAU Level-1-260C-UNLIMSN74AHCT595PWR ACTIVE TSSOP PW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHCT595PWRE4ACTIVE TSSOP PW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS),Pb-Free(RoHS Exempt),or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free(RoHS Exempt):This component has a RoHS exemption for either1)lead-based flip-chip solder bumps used between the die and package,or2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free(RoHS compatible)as defined above.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is 18-Jul-2006provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annualbasis.18-Jul-2006IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityLow Power Wireless /lpw Telephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2006, Texas Instruments Incorporated。

74HC595中文资料,74HC595D规格书,74HC595N技术文档,DATASHEET,飞利浦公司代理

CODE

SOT38-4 SOT38-4 SOT109-1 SOT109-1 SOT338-1 SOT338-1 SOT403-1 SOT403-1 SOT763-1 SOT763-1

2003 Jun 25

3

Philips Semiconductors

8-bit serial-in, serial or parallel-out shift register with output latches; 3-state

100

57

MHz

3.5

3.5

pF

115

130

pF

Notes 1. CPD is used to determine the dynamic power dissipation (PD in µW).

PD = CPD × VCC2 × fi × N + Σ(CL × VCC2 × fo) where: fi = input frequency in MHz; fo = output frequency in MHz; CL = output load capacitance in pF; VCC = supply voltage in Volts; N = total load switching outputs; Σ(CL × VCC2 × fo) = sum of the outputs. 2. For 74HC595 the condition is VI = GND to VCC. For 74HCT595 the condition is VI = GND to VCC − 1.5 V.

9??????v4544v6059vq7standardoutputio?40maio?52maqnbusdriveroutputs4537????v6052vio?60maio?78mavivihorvil4537????v6052vvollowleveloutputvoltagealloutputsio20?aq7standardoutput45??01vio40ma45??04vqnbusdriveroutputsio60ma45??????04viliinputleakagecurrentvivccorgnd551

74AHCT595D-T中文资料

4. Ordering information

Table 1. Ordering information Package Temperature range 74AHC595 74AHC595D 74AHC595PW 74AHC595BQ −40 °C to +125 °C −40 °C to +125 °C −40 °C to +125 °C SO16 TSSOP16 DHVQFN16 plastic small outline package; 16 leads; body width 3.9 mm SOT109-1 Name Description Version Type number

6.2 Pin description

Table 2. Symbol Q1 Q2 Q3 Q4 Q5 Q6 Q7 GND Q7S MR SHCP STCP OE DS Q0 VCC Pin description Pin 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 Description parallel data output 1 parallel data output 2 parallel data output 3 parallel data output 4 parallel data output 5 parallel data output 6 parallel data output 7 ground (0 V) serial data output master reset (active LOW) shift register clock input storage register clock input output enable input (active LOW) serial data input parallel data output 0 supply voltage

74HCT595N中文资料

Product specification

74HC/HCT595

handbook, full pagewidth

DS SHCP

MR

STCP OE

STAGE 0

STAGES 1 TO 6

STAGE 7

DQ

D

FF0

CP R

Q

DQ

Q7'

FF7

CP R

DQ LATCH CP

DQ LATCH CP

Q0

Q1 Q2 Q3 Q4 Q5 Q6

– parallel outputs; bus driver – serial output; standard • ICC category: MSI.

APPLICATIONS • Serial-to-parallel data conversion • Remote control holding register.

The “595” is an 8-stage serial shift register with a storage register and 3-state outputs. The shift register and storage register have separate clocks.

74HC/HCT595

handbook, full pagewidth

1998 Jun 04

14 DS 11 SHCP 10 MR

8-STAGE SHIFT REGISTER Q7' 9

12 STCP 8-BIT STORAGE REGISTER

13 OE

3-STATE OUTPUTS

Q0 15 Q1 1 Q2 2 Q3 3 Q4 4 Q5 5 Q6 6 Q7 7

74HC595PW TI运算放大器

74HC595PW 是一款具有8位移位寄存器和一个存储器,三态输出功能的驱动芯片。

移位寄存器和存储器分别具有独立的时钟信号。

数据在SHCP 的上升沿输入,在STCP 的上升沿进入到存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(DS ),和一个串行输出(Q7’),和一个异步的低电平复位(MR ),存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE 时(为低电平),存储寄存器的数据输出到总线。

FEATURES · 8位串行输入 · 8位串行或并行输出 · 带三态输出的存储寄存器 · 移位寄存器直接清除 · 100 MHz (典型)移出频率 · ESD 防护:HBM EIA/JESD22-A114-A exceeds 2000 V MM EIA/JESD22-A115-A exceeds 200 V.APPLICATIONS · S 串并数据转换 · 遥控器保持寄存器。

QUICK REFERENCE DATAGND = 0 V; T amb = 25 ︒C; t r = t f = 6 ns.DESCRIPTION74HC / HCT595是高速Si-gate CMOS 器件,并且与低功耗肖特基TTL (LSTTL )引脚兼容。

它们的指定符合JEDEC 标准No. 7A 。

74HC / HCT595是具有存储寄存器和三态输出的8级串行移位寄存器。

移位寄存器和存储寄存器具有独立的时钟。

数据在SH_CP 输入的正向跃迁上移动。

在ST_CP 输入的正向转换时,每个寄存器中的数据都会传输到存储寄存器。

如果两个时钟都连接在一起,则移位寄存器将始终比存储寄存器早一个时钟脉冲。

移位寄存器具有用于级联的串行输入(DS )和串行标准输出(Q7’)。

它还为所有8个移位寄存器级提供了异步复位(低电平有效)。

74HC165、75HC595芯片引脚及原理框图 - 电子技术

74HC165、75HC595芯片引脚及原理框图 -电子技术图 74HC165、75HC595芯片引脚及原理框图有了图引脚资料,也许还须再加上时序波形图,再加上内部功能电路图,才能有分析工作原理的条件。

也许仍然不够,还须深究对信号的处理细节。

移位寄存器芯片属于中规模集成电路,其电路结构较为复杂,这么一通搞下来,费时费力。

有简单的办法吗?可由应用电路的构成,倒推芯片所完成的功能。

也许换一个路子走,更有效率。

先看图,弄明白IC芯片在电路中起到的作用。

其中用于处理显示的相关电路部分:①5组反相器(BU5)为通讯信号传输芯片,其中9、8脚传输的为显示同步时钟(串行脉冲);1、2、3、4脚两组反相器传输的显示数据(串行脉冲),以上是数码管显示所需的两路输入信号。

②BU1、BU3用于串行脉冲的再处理,将串行输入转换为8路并行输出(专门处理数码管显示信息)。

配合后续电路分析,BU1输出信号经三极管BQ1~BQ8放大,用于数码管的8段显示驱动;BU3输出信号再经BU2进行功率放大,用于6位(7只发光二极管也算作一位,再加上5位数码显示)数码管驱动。

据此,本电路是根据由MCU主板来(主板MCU发送)的串行脉冲,被动显示的,若显示88888或-----,或无显示,仅有两个可能:①MCU主板未有串行脉冲(显示数据)送至面板,此故障概率较大;②BU5、BU1、BU2、BU3等电路异常,此故障概率较小。

先不管芯片好坏,测量BU5相关输入、输出引脚的串行脉冲信号,此处推荐采用示波器测量较为准确,若有一路是存在的,则说明主板MCU已经工作(该两路脉冲是主板MCU已经正常工作的标志)。

若两路俱无,则故障检修方向已经明确指向排线端子及主板MCU基本工作条件电路。

若脉冲正常,而显示异常,检修方向即指向面板电路。

例如针对74HC595芯片,①只要测知输入11脚串行脉冲(显示时钟)和输入14脚串行脉冲(显示数据)正常,②则其余8个“段驱动”信号输出脚,至少有数个脚应有脉冲电压(如2.5V左右)输出。

最新74HC595芯片资料汇总

74H C595芯片资料74HC595芯片资料8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。

三态。

特点8位串行输入8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换Remote control holding register.描述595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

参考数据CPD决定动态的能耗,PD=CPD×VCC×f1+∑(CL×VCC2×f0)F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明功能表H=高电平状态L=低电平状态↑=上升沿↓=下降沿Z=高阻NC=无变化×=无效当MR为高电平,OE为低电平时,数据在SHCP上升沿进入移位寄存器,在STCP上升沿输出到并行端口。

/***************************************************************************** **********/给个74HC595的"慢动作"void WriteSIOByte(unsigned char val){unsigned char i;ACC = val;for (i = 8; i > 0; i --) {SRCLK = 0;//拉低74HC595时钟_rrca_();//右移一位数据SER = CY;//发送74HC595一位串行数据SRCLK = 1;//拉高74HC595时钟_nop_();//延时}SER = 1;//释放数据总线//以下3条指令若在多字节时,应该移入多字节全发送完后在执行此3条指令 RCLK = 0;_nop_();//延时RCLK = 1;//打入并行数据}74ls595"速射"hotpowerfor(i = 0; i < buffsize; i ++){SBUF = siobuff[i];while(TI == 0);TI = 0;}RCLK = 0;_nop_();//延时RCLK = 1;//打入并行数据/************************************************************************/ 摘要:本文介绍了应用移位寄存器芯片74HC595实现LED动、静态显示的基本原理。

SN74AHC595PWRE4中文资料

PACKAGING INFORMATIONOrderable Device Status (1)Package Type Package DrawingPins Package Qty Eco Plan (2)Lead/Ball Finish MSL Peak Temp (3)SN74AHC595D ACTIVE SOIC D 1640Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AHC595DBR ACTIVE SSOP DB 162000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AHC595DBRE4ACTIVE SSOP DB 162000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AHC595DBRG4ACTIVE SSOP DB 162000Green (RoHS &no Sb/Br)CU NIPDAULevel-1-260C-UNLIM SN74AHC595DE4ACTIVE SOIC D 1640Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AHC595DG4ACTIVE SOIC D 1640Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AHC595DR ACTIVE SOIC D 162500Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AHC595DRE4ACTIVE SOIC D 162500Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AHC595DRG4ACTIVE SOIC D 162500Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AHC595N ACTIVE PDIP N 1625Pb-Free (RoHS)CU NIPDAU N /A for Pkg Type SN74AHC595NE4ACTIVE PDIP N 1625Pb-Free (RoHS)CU NIPDAU N /A for Pkg Type SN74AHC595NSR ACTIVE SO NS 162000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AHC595NSRE4ACTIVE SO NS 162000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AHC595NSRG4ACTIVE SO NS 162000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AHC595PW ACTIVE TSSOP PW 1690Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AHC595PWE4ACTIVE TSSOP PW 1690Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AHC595PWG4ACTIVE TSSOP PW 1690Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AHC595PWR ACTIVE TSSOP PW 162000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AHC595PWRE4ACTIVE TSSOP PW 162000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AHC595PWRG4ACTIVETSSOPPW162000Green (RoHS &no Sb/Br)CU NIPDAULevel-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -The planned eco-friendly classification:Pb-Free (RoHS),Pb-Free (RoHS Exempt),or Green (RoHS &no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.PACKAGE OPTION ADDENDUM4-Jun-2007Addendum-Page 1TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt):This component has a RoHS exemption for either 1)lead-based flip-chip solder bumps used between the die and package,or 2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free (RoHS compatible)as defined above.Green (RoHS &no Sb/Br):TI defines "Green"to mean Pb-Free (RoHS compatible),and free of Bromine (Br)and Antimony (Sb)based flame retardants (Br or Sb do not exceed 0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annualbasis.PACKAGE OPTION ADDENDUM4-Jun-2007TAPE AND REEL BOXINFORMATIONDevicePackage Pins SiteReel Diameter (mm)Reel Width (mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant SN74AHC595DBR DB 16SITE 41330168.2 6.6 2.51216Q1SN74AHC595DR D 16SITE 2733016 6.510.3 2.1816Q1SN74AHC595DR D 16SITE 4133016 6.510.3 2.1816Q1SN74AHC595NSR NS 16SITE 41330168.210.5 2.51216Q1SN74AHC595PWRPW16SITE 41330127.05.61.6812Q14-Oct-2007DevicePackage Pins Site Length (mm)Width (mm)Height (mm)SN74AHC595DBR DB 16SITE 41346.0346.033.0SN74AHC595DR D 16SITE 27342.9336.628.58SN74AHC595DR D 16SITE 41346.0346.033.0SN74AHC595NSR NS 16SITE 41346.0346.033.0SN74AHC595PWRPW16SITE 41346.0346.029.04-Oct-2007IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements, improvements,and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right,or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI. Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use anynon-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetworkMicrocontrollers Security /securityRFID Telephony /telephonyLow Power /lpw Video&Imaging /videoWirelessWireless /wirelessMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2007,Texas Instruments Incorporated。

74hct595d移位原理

74HC595D是一款串行输入并行输出的移位寄存器,常用于扩展微控制器的输出端口。

其移位原理如下:

数据输入信号通过串行输入引脚(SER)输入到移位寄存器中,然后通过时钟输入引脚(SRCLK)的上升沿触发,将输入信号依次移位到移位寄存器的内部存储单元中。

移位寄存器有8个存储单元,因此可以存储8位二进制数据。

当所有数据都移位完毕后,通过锁存器输入引脚(RCLK)的上升沿触发,将存储在移位寄存器中的数据锁存到并行输出引脚(Q0~Q7)上,实现并行输出。

这种IC可以在多种电子项目中使用,如显示器,控制LED等。

使用74HC595D时,应该注意保证时钟信号的同步,并且应该在数据传递完成后再使用并行端口输出。

595芯片管脚的作用

特点8位串行输入8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换Remote control holding register.描述595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

参考数据符号参数条件TYP 单位HC HCttPHL/tPLH 传输延时SHcp到Q7’STcp到QnMR到Q7’CL=15pFVcc=5V161714 212019 NsNsNsfmax STcp到SHcp最大时钟速度10057 MHzCL 输入电容Notes 1 3.5 3.5 pFCPD Power dissipation capacitance per package. Notes2115 130 pFCPD决定动态的能耗,PD=CPD×VCC×f1+∑(CL×VCC2×f0)F1=输入频率,CL=输出电容f0=输出频率(MHz)Vcc=电源电压引脚说明符号引脚描述Q0…Q7 15,1,7 并行数据输出GND 8 地Q7’ 9 串行数据输出MR 10 主复位(低电平)SHCP 11 移位寄存器时钟输入STCP 12 存储寄存器时钟输入OE 13 输出有效(低电平)DS 14 串行数据输入VCC 16 电源功能表输入输出功能SHCP STCP O E MR DS Q7’ Qn× × L ↓ × L NC MR为低电平时紧紧影响移位寄存器× ↑ L L × L L 空移位寄存器到输出寄存器× × H L × L Z 清空移位寄存器,并行输出为高阻状态↑ × L H H Q6’ NC 逻辑高电平移入移位寄存器状态0,包含所有的移位寄存器状态移入,例如,以前的状态6(内部Q6”)出现在串行输出位。

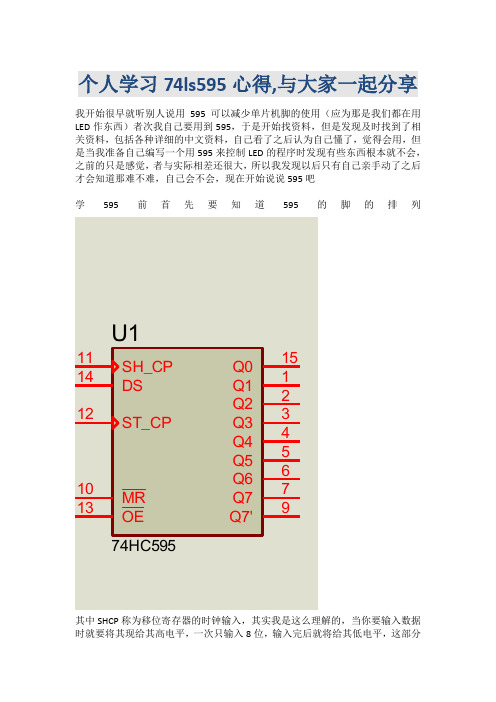

个人学习74ls595心得

个人学习74ls595心得,与大家一起分享我开始很早就听别人说用595可以减少单片机脚的使用(应为那是我们都在用LED作东西)者次我自己要用到595,于是开始找资料,但是发现及时找到了相关资料,包括各种详细的中文资料,自己看了之后认为自己懂了,觉得会用,但是当我准备自己编写一个用595来控制LED的程序时发现有些东西根本就不会,之前的只是感觉,者与实际相差还很大,所以我发现以后只有自己亲手动了之后才会知道那难不难,自己会不会,现在开始说说595吧学595前首先要知道595的脚的排列其中SHCP称为移位寄存器的时钟输入,其实我是这么理解的,当你要输入数据时就要将其现给其高电平,一次只输入8位,输入完后就将给其低电平,这部分可以做成一个输入部分,接着是DS其实他就是用来输入数据的,之前令SHCP 位高电平时就要将数据给DS这样数据就输入到了寄存器中,接着是STCP称为存储寄存器的时钟输入,其实我是将其叫做输出时钟,就是当你需要输出595中的数据时据要用到她,要输出数据时也是先给他高电平,当输出结束后就给他低电平,还有MR当他为低电平时595中的数据就没了,可以用其在开始时将595中的数据清空,还有事OE这个事输出允许位,当期为高时就阻止595输出,反正当你不是用总线或者实在很复杂的系统中,一般就将OE接地;其他Q0到Q7是串行输出,也就是输出你刚一次输入的8位(当你给SHCP高电平时一次输入的数据)Q7‘是并行输出,也就是将你输入的数据一个一个的输出。

接下来看一个程序#include<reg51.h>#define uchar unsigned char#define uint unsigned intuchar code DAT[8]={0x55};sbit DS=P2^1; //串行数据输入DSsbit SHCP =P2^0; //移位时钟脉冲SHCPsbit STCP =P2^2; //输出锁存器控制脉冲STCPuchar temp;////////////////////////////////// 延时void delay (){int i,j;for(i=20;i>0;i--)for(j=200;j>0;j--) ;}//////////////////////////// 延时子程序///////////////将显示数据送入74HC595内部移位寄存器*/void WR_595(void){uchar j;for (j=0;j<8;j++){temp=temp<<1;// 这是做一操作下面你将看到temp是你要输出的数而你输入数是以为接着一位向其输入的,所以需要一位操作将数据(十六进制)一位接着一位将其送入595也可以说是将temp的最高位送到tempDS=CY;SHCP=1; //上升沿发生移位delay ();SHCP=0; }}///////////将移位寄存器内的数据锁存到输出寄存器并显示void OUT_595(void){STCP=0;delay();STCP=1; //上升沿将数据送到输出锁存器delay ();//STCP=0;}//////////////// 主程序main(){SHCP=0;STCP=1;while(1){uchar i;for (i=0; i<8; i++){temp=DAT[i]; //放入你想要输出的数WR_595();OUT_595();delay ();}}} 下面是相应的图(上面我输入的数只有0x55一个你可以根据需要多加几个)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

X

↑

L

H

X

n.c.

Qn’

↑

↑

L

H

X

Q6’

Qn’

Note 1. H = HIGH voltage level; L = LOW voltage level; ↑ = LOW-to-HIGH transition; ↓ = HIGH-to-LOW transition; Z = high-impedance OFF-state; n.c. = no change; X = don’t care. ORDERING INFORMATION PACKAGE TYPE NUMBER 74HC595N 74HCT595N 74HC595D 74HCT595D 74HC595DB 74HCT595DB 74HC595PW 74HCT595PW 74HC595BQ 74HCT595BQ TEMPERATURE RANGE −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C PINS 16 16 16 16 16 16 16 16 16 16 PACKAGE DIP16 DIP16 SO16 SO16 SSOP16 SSOP16 TSSOP16 TSSOP16 DHVQFN16 DHVQFN16 MATERIAL plastic plastic plastic plastic plastic plastic plastic plastic plastic plastic CODE SOT38-4 SOT38-4 SOT109-1 SOT109-1 SOT338-1 SOT338-1 SOT403-1 SOT403-1 SOT763-1 SOT763-1

元器件交易网

Philips Semiconductors

Product specification

8-bit serial-in, serial or parallel-out shift register with output latches; 3-state

FUNCTION TABLE See note 1. INPUT SH_CP ST_CP X X X ↑ X ↑ X X OE L L H L MR L L L H DS X X X H OUTPUT

Product specification Supersedes data of 1998 Jun 04 2003 Jun 25

元器件交易网

Philips Semiconductors

Product specification

8-bit serial-in, serial or parallel-out shift register with output latches; 3-state

74HC595; 74HCT595

FUNCTION Q7’ L L L Q6’ Qn n.c. L Z n.c. a LOW level on MR only affects the shift registers empty shift register loaded into storage register shift register clear; parallel outputs in high-impedance OFF-state logic high level shifted into shift register stage 0; contents of all shift register stages shifted through, e.g. previous state of stage 6 (internal Q6’) appears on the serial output (Q7’) contents of shift register stages (internal Qn’) are transferred to the storage register and parallel output stages contents of shift register shifted through; previous contents of the shift register is transferred to the storage register and the parallel output stages

PINNING PIN 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 SYMBOL Q1 Q2 Q3 Q4 Q5 Q6 Q7 GND Q7’ MR SH_CP ST_CP OE DS Q0 VCC parallel data output parallel data output parallel data output parallel data output parallel data output parallel data output parallel data output ground (0 V) serial data output master reset (active LOW) shift register clock input storage register clock input output enable (active LOW) serial data input parallel data output positive supply voltage

2003 Jun 25

3

元器件交易网

Philips Semiconductors

Product specification

8-bit serial-in, serial or parallel-out shift register with output latches; 3-state

74HC595; 74HCT595

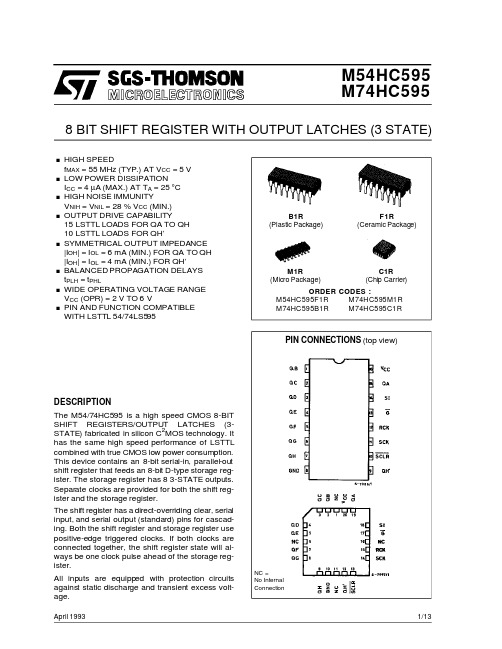

The 74HC/HCT595 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A. The 74HC/HCT595 is an 8-stage serial shift register with a storage register and 3-state outputs. The shift register and storage register have separate clocks. Data is shifted on the positive-going transitions of the SH_CP input. The data in each register is transferred to the storage register on a positive-going transition of the ST_CP input. If both clocks are connected together, the shift register will always be one clock pulse ahead of the storage register. The shift register has a serial input (DS) and a serial standard output (Q7’) for cascading. It is also provided with asynchronous reset (active LOW) for all 8 shift register stages. The storage register has 8 parallel 3-state bus driver outputs. Data in the storage register appears at the output whenever the output enable input (OE) is LOW.

元器件交易网

INTEGRATED CIRCUITS

DATA SHEET

74HC595; 74HCT595 8-bit serial-in, serial or parallel-out shift register with output latches; 3-state

74HC595; 74HCT595DESCRIPTION

handbook, halfpage

handbook, halfpage

Q1 1

VCC 16 15 14 13 Q0 DS OE ST_CP SH_CP MR

QUICK REFERENCE DATA GND = 0 V; Tamb = 25 °C; tr = tf = 6 ns. TYPICAL SYMBOL tPHL/tPLH PARAMETER propagation delay SH_CP to Q7’ SH_CP to Qn MR to Q7’ fmax CI CPD Notes 1. CPD is used to determine the dynamic power dissipation (PD in µW). PD = CPD × VCC2 × fi × N + Σ(CL × VCC2 × fo) where: fi = input frequency in MHz; fo = output frequency in MHz; CL = output load capacitance in pF; VCC = supply voltage in Volts; N = total load switching outputs; Σ(CL × VCC2 × fo) = sum of the outputs. 2. For 74HC595 the condition is VI = GND to VCC. For 74HCT595 the condition is VI = GND to VCC − 1.5 V. 2003 Jun 25 2 maximum clock frequency SH_CP and ST_CP input capacitance power dissipation capacitance per package notes 1 and 2 CONDITIONS 74HC CL = 50 pF; VCC = 4.5 V 19 20 100 100 3.5 115 25 24 52 57 3.5 130 ns ns ns MHz pF pF 74HCT UNIT