AD8403中文资料

pam8403中文资料_数据手册_参数

Recommended Operating Conditions

Supply voltage Range........................2.5V to 5.5V Max. Supply Voltage (for Max. duration of

30 minutes)................................................6.4V

Absolute Maximum Ratings

These are stress ratings only and functional operation is not implied. Exposure to absolute maximum ratings for prolonged time periods may affect device reliability. All voltages are with respect to ground.

PAM8403

Filterless 3W Class-D Stereo Audio Amplifier

Key Features

n 3W Output at 10% THD with a 4Ω Load and 5V Power Supply

n Filterless, Low Quiescent Current and Low EMI

Operation Junction Temperature.....-40°C to 125°C Storage Temperature.....................-65°C to 150°C Soldering Temperature.......................300°C, 5sec

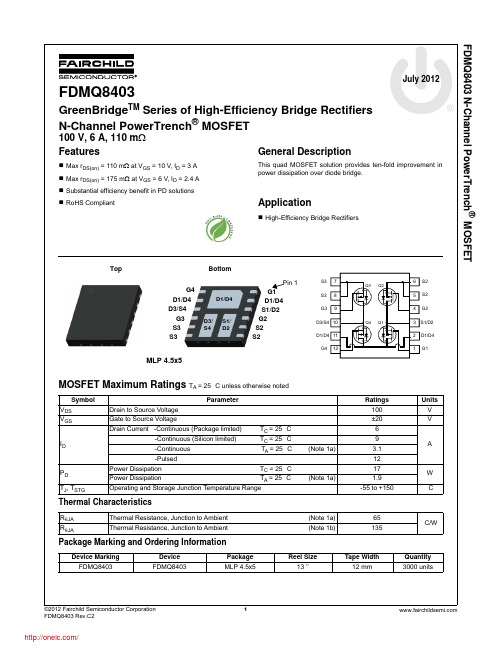

FDMQ8403;中文规格书,Datasheet资料

FDMQ8403 N-Channel PowerTrench ® MOSFETS2S1/D2G2S2D3/S4G3D1/D4G4S1/D2D1/D4D3/S4® MOSFETDynamic CharacteristicsSwitching CharacteristicsDrain-Source Diode CharacteristicsV GS = 10 V, I D = 3 A, T J = 125 °C 147191g FSForward TransconductanceV DS = 10 V, I D = 3 A6S C iss Input Capacitance V DS = 50 V, V GS = 0 V,f = 1 MHz162215pF C oss Output Capacitance4360pF C rssReverse Transfer Capacitance2.65pFt d(on)Turn-On Delay Time V DD = 50 V, I D = 3 A,V GS = 10 V, R GEN = 6 Ω4.110ns t r Rise Time1.210ns t d(off)Turn-Off Delay Time 7.215ns t f Fall Time1.810ns Q g Total Gate Charge V GS = 0 V to 10 V V DD = 50 V, I D = 3 A35nC Q g Total Gate Charge V GS = 0 V to 5 V1.73nC Q gs Gate to Source Charge 0.9nC Q gdGate to Drain “Miller” Charge0.8nCV SD Source to Drain Diode Forward Voltage V GS = 0 V, I S = 3 A (Note 2)0.86 1.3V t rr Reverse Recovery Time I F = 3 A, di/dt = 100 A/μs3353ns Q rrReverse Recovery Charge2337nCNotes :1. R θJA is determined with the device mounted on a 1in 2 pad 2 oz copper pad on a 1.5 x 1.5 in. board of FR-4 material. R θJC is guaranteed by design while R θCA is determined by the user's board design.2. Pulse Test: Pulse Width < 300 μs, Duty cycle < 2.0%.a. 65 °C/W when mounted on a 1 in 2 pad of 2 oz copper. the board designed Q1+Q3 or Q2+Q4.b. 135 °C/W when mounted on a minimum pad of 2 oz copper. the board designed Q1+Q3 or Q2+Q4.®®FDMQ8403 N-Channel PowerTrenchDimensional Outline and Pad Layout®MOSFETFDMQ8403 N-Channel PowerTrench ® MOSFET*Trademarks of System General Corporation, used under license by Fairchild Semiconductor.DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used here in:Life support devices or systems are devices or systems which, (a) areintended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.2.A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.PRODUCT STATUS DEFINITIONS Definition of Terms2Cool™AccuPower™AX-CAP™*BitSiC ®Build it Now™CorePLUS™CorePOWER™CROSSVOLT ™CTL™Current Transfer Logic™DEUXPEED ®Dual Cool™EcoSPARK ®EfficentMax™ESBC™Fairchild®Fairchild Semiconductor®FACT Quiet Series™FACT®FAST ®FastvCore™FETBench™FlashWriter ®*FPS™F-PFS™FRFET®Global Power Resource SM Green Bridge™Green FPS™Green FPS™ e-Series™G max ™GTO™IntelliMAX™ISOPLANAR™Marking Small Speakers Sound Louder and Better™MegaBuck™MICROCOUPLER™MicroFET™MicroPak™MicroPak2™MillerDrive™MotionMax™Motion-SPM™mWSaver™OptoHiT™OPTOLOGIC ®OPTOPLANAR ®PowerTrench ®PowerXS™Programmable Active Droop™QFET ®QS™Quiet Series™RapidConfigure™Saving our world, 1mW/W/kW at a time™SignalWise™SmartMax™SMART START™Solutions for Your Success™SPM ®STEALTH™SuperFET ®SuperSOT™-3SuperSOT™-6SuperSOT™-8SupreMOS ®SyncFET™Sync-Lock™®*The Power Franchise ®®TinyBoost™TinyBuck™TinyCalc™TinyLogic ®TINYOPTO™TinyPower™TinyPWM™TinyWire™TranSiC ®TriFault Detect™TRUECURRENT ®*μSerDes™UHC ®Ultra FRFET™UniFET™VCX™VisualMax™VoltagePlus™XS™®™Datasheet Identification Product Status DefinitionANTI-COUNTERFEITING POLICYFairchild Semiconductor Corporation’s Anti-Counterfeiting Policy. Fairchild’s Anti-Counterfeiting Policy is also stated on our external website, , under Sales Support .Counterfeiting of semiconductor parts is a growing problem in the industry. All manufactures of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed application, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild’s quality standards for handing and storage and provide access to Fairchild’s full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address and warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.®分销商库存信息: FAIRCHILD FDMQ8403。

ZSPM4013AA1W33中文资料(ZMDI)中文数据手册「EasyDatasheet - 矽搜」

该ZSPM4013采用电流模式反馈 正常调节PWM模式.当稳压 被禁用(EN为低电平)时,设备将小于 10uA静态电流.

该ZSPM4013集成多种防护护电路,包括: 输入欠压锁定,输出电压软启动,限流和热关断.

该ZSPM4013包括通过PG(电源良好)开漏输出 监管报告接口等组成系统.

特征

· 固定输出电压:1.5V,1.8V,2.5V,3.3V, 并用5V +/- 2%输出容差

· ZSPM1000:5A单相,单轨,真 数字PWM控制器(24引脚4×4 QFN)

提供支持

· 评估套件 · 数据表

物理特性

· 结工作温度-40°C至125°C · 包装在一个16针QFN(3×3)

ZSPM4013应用电路

可调输出

ZSPM4013

固定输出 VCC

VOUT

ZSPM4013

EN

PG

芯片中文手册,看全文,戳

2 典型性能特性................................................................................................................... 9 3 电路说明......................................................................................................................................... 12

5 引脚配置和包装......................................................................................................................... 15 5.1.标记图& Pin-out......................................................................................................................... 16 5.2.引脚说明为16引脚3x3 QFN封装....................................................................................................... 17 5.3.详细引脚说明............................................................................................................................. 17 5.3.1.未经稳压输入,VCC(引脚#2,3)....................................... .................................................. ........... 17 5.3.2.引导控制,BST(引脚#10) ......................................................................................................... 17 5.3.3.检测反馈,FB(引脚#5) ............................................................................................................... 17 5.3.4.开关量输出,VSW(引脚#12,13)....................................... .................................................. ......... 18 5.3.5.接地,GND(引脚#4) .......................................................................................................................... 18 5.3.6.电源接地,防护护接地(引脚#14,15)....................................... .................................................. .......... 18 5.3.7.启用,高电压,EN(管脚#9) ........................................................................................................ 18 5.3.8. PG输出,PG(引脚#8) ....................................................................................................................... 18

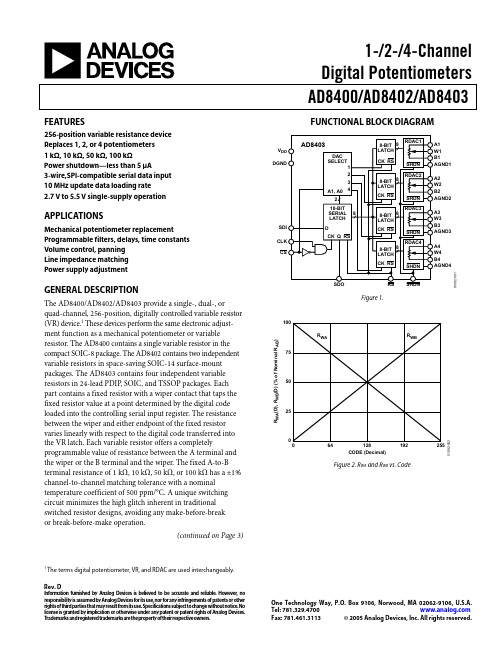

AD8400_8402_8403_cn

CK RS

SHDN

RDAC2 8-BIT 8 LATCH

CK RS

SHDN

RDAC3 8-BIT 8 LATCH

CK RS

SHDN

RDAC4 8-BIT 8 LATCH

CK RS

SHDN

A1 W1 B1 AGND1

A2 W2 B2 AGND2

A3 W3 B3 AGND3

A4 W4 B4 AGND4

01092-001

SDO

图1

RS SHDN

100 RWA

75

RWB

RWA(D), RWB(D) (% of Nominal RAB)

50

25

01092-002

0

0

64

128

192

255

CODE (Decimal)

图2. RWA和RWB与代码的关系

Rev. E

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rightsofthirdpartiesthatmayresultfromitsuse.Speci cationssubjecttochangewithoutnotice.No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

ADG733资料

REV.0Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.aADG733/ADG734One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781/329-4700World Wide Web Site: Fax: 781/326-8703© Analog Devices, Inc., 2001CMOS, 2.5 ⍀ Low Voltage,Triple/Quad SPDT SwitchesFEATURES1.8 V to 5.5 V Single Supply ؎3 V Dual Supply2.5 ⍀ On Resistance0.5 ⍀ On Resistance Flatness 100 pA Leakage Currents 19 ns Switching Times Triple SPDT: ADG733Quad SPDT: ADG734Small TSSOP and QSOP Packages Low Power ConsumptionTTL/CMOS-Compatible Inputs APPLICATIONSData Acquisition Systems Communication Systems Relay ReplacementAudio and Video Switching Battery-Powered SystemsGENERAL DESCRIPTION The ADG733 and ADG734 are low voltage, CMOS devices comprising three independently selectable SPDT (single pole,double throw) switches and four independently selectable SPDT switches respectively.Low power consumption and operating supply range of 1.8 V to 5.5 V and dual ±3 V make the ADG733 and ADG734 ideal for battery powered, portable instruments. All channels exhibit break-before-make switching action preventing momentary shorting when switching channels. An EN input on the ADG733is used to enable or disable the device. When disabled, all chan-nels are switched OFF.These 2–1 multiplexers/SPDT switches are designed on an enhanced submicron process that provides low power dissipation yet gives high switching speed, very low on resistance, high signal bandwidths and low leakage currents. On resistance is in the region of a few ohms, is closely matched between switches and very flat over the full signal range. These parts can operate equally well in either direction and have an input signal range which extends to the supplies.The ADG733 is available in small TSSOP and QSOP packages,while the ADG734 is available in a small TSSOP package.PRODUCT HIGHLIGHTS1.Single/Dual Supply Operation. The ADG733 and ADG734 are fully specified and guaranteed with 3 V and 5 V single supply rails and ±3 V dual supply rails.2.Low On Resistance (2.5Ω typical).3.Low Power Consumption (<0.01 µW).4.Guaranteed Break-Before-Make Switching Action.FUNCTIONAL BLOCK DIAGRAMSS3BD3S3A SWITCHES SHOWN FOR A “1” INPUT LOGICENADG733/ADG734–SPECIFICATIONS1(V DD = 5 V ؎ 10%, V SS = 0 V, GND = 0 V, unless otherwise noted.)B Version–40؇CParameter25؇C to +85؇C Unit Test Conditions/CommentsANALOG SWITCHAnalog Signal Range0 V to V DD VOn Resistance (R ON) 2.5Ω typ V S = 0 V to V DD, I DS = 10 mA;4.55.0Ω max Test Circuit 1On-Resistance Match between0.1Ω typ V S = 0 V to V DD, I DS = 10 mAChannels (∆R ON)0.4Ω maxOn-Resistance Flatness (R FLAT(ON))0.5Ω typ V S = 0 V to V DD, I DS = 10 mA1.2Ω maxLEAKAGE CURRENTS V DD = 5.5 VSource OFF Leakage I S (OFF)±0.01nA typ V D = 4.5 V/1 V, V S = 1 V/4.5 V;±0.1±0.3nA max Test Circuit 2Channel ON Leakage I D, I S (ON)±0.01nA typ V D = V S = 1 V, or 4.5 V;±0.1±0.5nA max Test Circuit 3DIGITAL INPUTSInput High Voltage, V INH 2.4V minInput Low Voltage, V INL0.8V maxInput CurrentI INL or I INH0.005µA typ V IN = V INL or V INH±0.1µA maxC IN, Digital Input Capacitance4pF typDYNAMIC CHARACTERISTICS2t ON19ns typ R L = 300 Ω, C L = 35 pF;34ns max V S = 3 V, Test Circuit 4t OFF7ns typ R L = 300 Ω, C L = 35 pF;12ns max V S = 3 V, Test Circuit 4ADG733t ON(EN)20ns typ R L = 300 Ω, C L = 35 pF;40ns max V S = 3 V, Test Circuit 5t OFF(EN)7ns typ R L = 300 Ω, C L = 35 pF;12ns max V S = 3 V, Test Circuit 5Break-Before-Make Time Delay, t D13ns typ R L = 300 Ω, C L = 35 pF;1ns min V S = 3 V, Test Circuit 6Charge Injection±3pC typ V S = 2 V, R S = 0 Ω, C L = 1 nF;Test Circuit 7Off Isolation–62dB typ R L = 50 Ω, C L = 5 pF, f = 10 MHz;–82dB typ R L = 50 Ω, C L = 5 pF, f = 1 MHz;Test Circuit 8Channel-to-Channel Crosstalk–62dB typ R L = 50 Ω, C L = 5 pF, f = 10 MHz;–82dB typ R L = 50 Ω, C L = 5 pF, f = 1 MHz;Test Circuit 9–3 dB Bandwidth200MHz typ R L = 50 Ω, C L = 5 pF, Test Circuit 8C S (OFF)11pF typC D, C S (ON)34pF typPOWER REQUIREMENTS V DD = 5.5 VI DD0.001µA typ Digital Inputs = 0 V or 5.5 V1.0µA maxNOTES1Temperature range is as follows: B Version: –40°C to +85°C.2Guaranteed by design, not subject to production test.Specifications subject to change without notice.–2–REV. 0REV. 0–3–ADG733/ADG734B Version–40؇CParameter25؇C to +85؇CUnit Test Conditions/CommentsANALOG SWITCH Analog Signal Range 0 V to V DDV On Resistance (R ON )6Ω typ V S = 0 V to V DD , I DS = 10 mA;1112Ω max Test Circuit 1On-Resistance Match between 0.1Ω typ V S = 0 V to V DD , I DS = 10 mA Channels (∆R ON )0.4Ω max On-Resistance Flatness (R FLAT(ON))3Ω typ V S = 0 V to V DD , I DS = 10 mA LEAKAGE CURRENTSV DD = 3.3 VSource OFF Leakage I S (OFF)±0.01nA typ V S = 3 V/1 V, V D = 1 V/3 V;±0.1±0.3nA max Test Circuit 2Channel ON Leakage I D , I S (ON)±0.01nA typ V S = V D = 1 V or 3 V;±0.1±0.5nA max Test Circuit 3DIGITAL INPUTSInput High Voltage, V INH 2.0V min Input Low Voltage, V INL 0.4V max Input Current I INL or I INH 0.005µA typ V IN = V INL or V INH±0.1µA max C IN , Digital Input Capacitance 4pF typ DYNAMIC CHARACTERISTICS 2t ON 28ns typ R L = 300 Ω, C L = 35 pF;55ns max V S = 2 V, Test Circuit 4t OFF9ns typ R L = 300 Ω, C L = 35 pF;16ns max V S = 2 V, Test Circuit 4ADG733t ON (EN )29ns typ R L = 300 Ω, C L = 35 pF;60ns max V S = 2 V, Test Circuit 5t OFF (EN )9ns typ R L = 300 Ω, C L = 35 pF;16ns max V S = 2 V, Test Circuit 5Break-Before-Make Time Delay, t D 22ns typ R L = 300 Ω, C L = 35 pF;1ns min V S = 2 V, Test Circuit 6Charge Injection ±3pC typ V S = 1 V, R S = 0 Ω, C L = 1 nF;Test Circuit 7Off Isolation–62dB typ R L = 50 Ω, C L = 5 pF, f = 10 MHz;–82dB typ R L = 50 Ω, C L = 5 pF, f = 1 MHz;Test Circuit 8Channel-to-Channel Crosstalk –62dB typ R L = 50 Ω, C L = 5 pF, f = 10 MHz;–82dB typ R L = 50 Ω, C L = 5 pF, f = 1 MHz;Test Circuit 9–3 dB Bandwidth 200MHz typ R L = 50 Ω, C L = 5 pF, Test Circuit 8C S (OFF)11pF typ CD , C S (ON)34pF typ POWER REQUIREMENTS V DD = 3.3 VI DD0.001µA typ Digital Inputs = 0 V or 3.3 V1.0µA maxNOTES 1Temperature ranges are as follows: B Version: –40°C to +85°C.2Guaranteed by design, not subject to production test.Specifications subject to change without notice.(V DD = 3 V ؎ 10%, V SS = 0 V, GND = 0 V, unless otherwise noted.)SPECIFICATIONS1ADG733/ADG734–SPECIFICATIONS1DUAL SUPPLY(V DD = +3 V ؎ 10%, V SS = –3 V ؎ 10%, GND = 0 V, unless otherwise noted.)B Version–40؇CParameter25؇C to +85؇C Unit Test Conditions/CommentsANALOG SWITCHAnalog Signal Range V SS to V DD VOn Resistance (R ON) 2.5Ω typ V S = V SS to V DD, I DS = 10 mA;4.55.0Ω max Test Circuit 1On-Resistance Match between0.1Ω typ V S = V SS to V DD, I DS = 10 mAChannels (∆R ON)0.4Ω maxOn-Resistance Flatness (R FLAT(ON))0.5Ω typ V S = V SS to V DD, I DS = 10 mA1.2Ω maxLEAKAGE CURRENTS V DD = +3.3 V, V SS = –3.3 VSource OFF Leakage I S (OFF)±0.01nA typ V S = +2.25 V/–1.25 V, V D = –1.25 V/+2.25 V;±0.1±0.3nA max Test Circuit 2Channel ON Leakage I D, I S (ON)±0.01nA typ V S = V D = +2.25 V/–1.25 V, Test Circuit 3±0.1±0.5nA maxDIGITAL INPUTSInput High Voltage, V INH 2.0V minInput Low Voltage, V INL0.4V maxInput CurrentI INL or I INH0.005µA typ V IN = V INL or V INH±0.1µA maxC IN, Digital Input Capacitance4pF typDYNAMIC CHARACTERISTICS2t ON21ns typ R L = 300 Ω, C L = 35 pF;35ns max V S = 1.5 V, Test Circuit 4t OFF10ns typ R L = 300 Ω, C L = 35 pF;16ns max V S = 1.5 V, Test Circuit 4ADG733t ON(EN)21ns typ R L = 300 Ω, C L = 35 pF;40ns max V S = 1.5 V, Test Circuit 5t OFF(EN)10ns typ R L = 300 Ω, C L = 35 pF;16ns max V S = 1.5 V, Test Circuit 5Break-Before-Make Time Delay, t D13ns typ R L = 300 Ω, C L = 35 pF;1ns min V S = 1.5 V, Test Circuit 6Charge Injection±5pC typ V S = 0 V, R S = 0 Ω, C L = 1 nF;Test Circuit 7Off Isolation–62dB typ R L = 50 Ω, C L = 5 pF, f = 10 MHz;–82dB typ R L = 50 Ω, C L = 5 pF, f = 1 MHz;Test Circuit 8Channel-to-Channel Crosstalk–62dB typ R L = 50 Ω, C L = 5 pF, f = 10 MHz;–82dB typ R L = 50 Ω, C L = 5 pF, f = 1 MHz;Test Circuit 9–3 dB Bandwidth200MHz typ R L = 50 Ω, C L = 5 pF, Test Circuit 8C S (OFF)11pF typC D, C S (ON)34pF typPOWER REQUIREMENTS V DD = 3.3 VI DD0.001µA typ Digital Inputs = 0 V or 3.3 V1.0µA maxI SS0.001µA typ V SS = –3.3 V1.0µA max Digital Inputs = 0 V or 3.3 VNOTES1Temperature range is as follows: B Version: –40°C to +85°C.2Guaranteed by design, not subject to production test.Specifications subject to change without notice.–4–REV. 0REV. 0ADG733/ADG734–5–ABSOLUTE MAXIMUM RATINGS 1(T A = 25°C unless otherwise noted)V DD to V SS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 V V DD to GND . . . . . . . . . . . . . . . . . . . . . . . . . .–0.3 V to +7 V V SS to GND . . . . . . . . . . . . . . . . . . . . . . . . . .+0.3 V to –3.5 V Analog Inputs 2 . . . . . . . . . . . . . .V SS – 0.3 V to V DD + 0.3 V or30 mA, Whichever Occurs FirstDigital Inputs 2. . . . . . . . . . . . . . . . .–0.3 V to V DD + 0.3 V or30 mA, Whichever Occurs FirstPeak Current, S or D . . . . . . . . . . . . . . . . . . . . . . . . . .100 mA(Pulsed at 1 ms, 10% Duty Cycle max)Continuous Current, S or D . . . . . . . . . . . . . . . . . . . .30 mA Operating Temperature RangeIndustrial (A, B Versions) . . . . . . . . . . . . .–40°C to +85°C Storage Temperature Range . . . . . . . . . . . .–65°C to +150°CCAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection.Although the ADG733/ADG734 features proprietary ESD protection circuitry, permanent dam-age may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . .150°C 16-Lead TSSOP, θJA Thermal Impedance . . . . . . .150.4°C/W 20-Lead TSSOP, θJA Thermal Impedance . . . . . . . .143°C/W 16-Lead QSOP, θJA Thermal Impedance . . . . . . .149.97°C/W Lead Temperature, Soldering (10 sec) . . . . . . . . . . . . .300°C IR Reflow, Peak Temperature . . . . . . . . . . . . . . . . . . . .220°CNOTES 1Stresses above those listed under Absolute Maximum Ratings may cause perma-nent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Only one absolute maximum rating may be applied at any one time.2Overvoltages at IN, S or D will be clamped by internal diodes. Current should be limited to the maximum ratings given.ORDERING GUIDEModel Temperature Range Package DescriptionPackage Option ADG733BRU –40°C to +85°C Thin Shrink Small Outline Package (TSSOP)RU-16ADG733BRQ –40°C to +85°C Quarter Size Outline Package (QSOP)RQ-16ADG734BRU–40°C to +85°CThin Shrink Small Outline Package (TSSOP)RU-20PIN CONFIGURATIONSTSSOP/QSOPTSSOPS2B DD S2A S3B D3S3A EN V SS GNDNC = NO CONNECTDDVREV. 0ADG733/ADG734–6–Table I.ADG733 Truth TableA2A1A0EN ON SwitchX X X 1None0000D1-S1A, D2-S2A, D3-S3A 0010D1-S1B, D2-S2A, D3-S3A 0100D1-S1A, D2-S2B, D3-S3A 0110D1-S1B, D2-S2B, D3-S3A 1000D1-S1A, D2-S2A, D3-S3B 1010D1-S1B, D2-S2A, D3-S3B 1100D1-S1A, D2-S2B, D3-S3B 111D1-S1B, D2-S2B, D3-S3BX = Don’t Care.Table II. ADG734 Truth TableLogic Switch A Switch B 0OFF ON 1ONOFFV DD Most Positive Power Supply Potential.V SSMost Negative Power Supply in a Dual Supply Application. In single supply applications, this should be tied to ground close to the device.I DD Positive Supply Current.I SS Negative Supply Current.GND Ground (0 V) Reference.S Source Terminal. May be an input or output.D Drain Terminal. May be an input or output.IN Logic Control Input.V D (V S )Analog Voltage on Terminals D, S R ON Ohmic Resistance between D and S.∆R ON On Resistance Match between Any Two Channels, i.e., R ON max – R ON minR FLAT(ON)Flatness is defined as the difference between the maximum and minimum value of on-resistance as measured over the specified analog signal range.I S (OFF)Source Leakage Current with the Switch “OFF.”I D , I S (ON)Channel Leakage Current with the Switch “ON.”V INL Maximum Input Voltage for Logic “0.”V INH Minimum Input Voltage for Logic “1.”I INL (I INH )Input Current of the Digital Input.C S (OFF)“OFF” Switch Source Capacitance.Measured with reference to ground.C D , C S (ON)“ON” Switch Capacitance. Measured with reference to ground.C IN Digital Input Capacitance.t ONDelay time measured between the 50% and 90% points of the digital inputs and the switch “ON” condition.t OFFDelay time measured between the 50% and 90% points of the digital input and the switch “OFF” condition.t ON (EN )Delay time between the 50% and 90% points of the EN digital input and the switch “ON”condition.t OFF (EN )Delay time between the 50% and 90% points of the EN digital input and the switch “OFF”condition.t OPEN“OFF” time measured between the 80%points of both switches when switching from one address state to another.Charge A measure of the glitch impulse transferred Injection from the digital input to the analog output during switching.Off Isolation A measure of unwanted signal coupling through an “OFF” switch.CrosstalkA measure of unwanted signal that is coupled through from one channel toanother as a result of parasitic capacitance.Bandwidth The frequency at which the output is attenuated by 3 dBs.On ResponseThe Frequency Response of the “ON” Switch.Insertion Loss The loss due to the ON resistance of the switch.TERMINOLOGYREV. 0–7–Typical Performance Characteristics–ADG733/ADG734V D , V S , DRAIN OR SOURCE VOLTAGE – V1O N R E S I S T A N C E – ⍀TPC 1. On Resistance as a Function of V D(V S ) for Single SupplyV D OR V S – DRAIN OR SOURCE VOLTAGE – V76543210O N R E S I S T A N C E – ⍀8TPC 4. On Resistance as a Function of V D (V S ) for Different Temperatures,Single Supply V S (V D ) – V0.10C U R R E N T – n A0.080.060.040.020–0.02–0.04–0.06–0.08–0.10TPC 7. Leakage Currents as a Function of V D (V S )V D , OR V S /DRAIN OR SOURCE VOLTAGE – V 876543210O N R E S I S T A N C E – ⍀TPC 2. On Resistance as a Function of V D (V S ) for Dual SupplyV D , OR V S DRAIN OR SOURCE VOLTAGE – V 1O N R E S I S T A N C E – ⍀TPC 5. On Resistance as a Function of V D (V S ) for Different Temperatures,Dual SupplyV S (V D ) – V0.15C U R R E N T – n A0.100.050–0.05–0.10–0.15TPC 8. Leakage Currents as a Function of V D (V S )V D , OR V S DRAIN OR SOURCE VOLTAGE – V876543210O N R E S I S T A N C E – ⍀TPC 3. On Resistance as a Function of V D (V S ) for Different Temperatures,Single SupplyV S (V D ) – V0.1C U R R E N T – n A0.05–0.05–0.1–0.15TPC 6. Leakage Currents as a Function of V D (V S)TEMPERATURE – ؇C0.25C U R R E N T – n A0.200.150.100.050–0.05–0.10TPC 9. Leakage Currents as a Function of TemperatureREV. 0ADG733/ADG734–8–TEMPERATURE – ؇C 0.25C U R R E N T – n A0.200.150.100.050–0.05–0.10TPC 10.Leakage Currents as a Function of TemperatureFREQUENCY – kHzC U R R E N T – A100101TPC 13.Input Current, I DD vs.Switching FrequencyVOLTAGE –V2010–10Q I N J – p CTPC 16.Charge Injection vs. Source VoltageTEMPERATURE – ؇C40T I M E – n s35302520151005TPC 11.t ON /t OFF Times vs.TemperatureFREQUENCY – kHz030kA T T E N U A T I O N – d B–20–40–60–80–100–120100k1M 10M100M TPC 14.Off Isolation vs. Frequency FREQUENCY – H Z–4–2–6O N R E S P O N S E – dBTPC 12.On Response vs. FrequencyFREQUENCY – kHz030kA T T E N U A T I O N – d B–20–40–60–80–100–120100k1M 10M 100MTPC 15.Crosstalk vs. FrequencyREV. 0ADG733/ADG734–9–V Test Circuit 1.On ResistanceTest CircuitsDV STest Circuit 2.I S (OFF)DTest Circuit 3.I D (ON)VTest Circuit 4.Switching Times, t ON , t OFFOVTest Circuit 5.Enable Delay, t ON (EN ), t OFF (EN )OUTV *A0, A1, A2 FOR ADG733, IN1-4 FOR ADG734ADDRESS3VV OUT0V V Test Circuit 6.Break-Before-Make Delay, t OPENREV. 0ADG733/ADG734–10–* IN1–4 FOR ADG734OUTV V Test Circuit 7.Charge InjectionSWITCH OPEN FOR OFF ISOLATION MEASUREMENTS SWITCH CLOSED FOR BANDWIDTH MEASUREMENTS OFF ISOLATION = 20LOG 10(V OUT /V S )INSERTION LOSS = 20LOG 10(V OUT WITH SWITCH V OUT WITHOUT SWITCH)V V OUTTest Circuit 8.OFF Isolation and BandwidthV SV NC = NO CONNECTTest Circuit 9.Channel-to-Channel CrosstalkREV. 0ADG733/ADG734–11–16-Lead TSSOP (RU-16)OUTLINE DIMENSIONSDimensions shown in inches and (mm).20-Lead TSSOP (RU-20)16-Lead QSOP(RQ-16)BSC 0.007 (0.18)C 01602–2.5–1/01 (r e v . 0)P R I N T E D I N U .S .A .元器件交易网。

NCV8403ADTRKG;NCV8403STT3G;NCV8403STT1G;中文规格书,Datasheet资料

Characteristic

Symbol

OFF CHARACTERISTICS

Drain−to−Source Clamped Breakdown Voltage (VGS = 0 Vdc, ID = 250 mAdc) (VGS = 0 Vdc, ID = 250 mAdc, TJ = −40°C to 150°C) (Note 3)

EAS

470

mJ

Load Dump Voltage (VGS = 0 and 10 V, RI = 2.0 W, RL = 4.5 W, td = 400 ms)

VLD

55

V

Operating Junction Temperature

TJ

−40 to 150

°C

Storage Temperature

RDS(on) VSD

SWITCHING CHARACTERISTICS (Note 3)

Turn−ON Time (10% VIN to 90% ID) Turn−OFF Time (90% VIN to 10% ID) Turn−ON Time (10% VIN to 90% ID) Turn−OFF Time (90% VIN to 10% ID) Slew−Rate ON (20% VDS to 50% VDS) Slew−Rate OFF (80% VDS to 50% VDS)

Y

= Year

W, WW = Work Week

xxxxx = V8403 or 8403A

G or G = Pb−Free Package

(Note: Microdot may be in either location)

ORDERING INFORMATION

SP9840资料

SPECIFICATIONS

(VDD = +5V, All VINX= 0V, VREFL = 1.625V, TA = 25° C for commercial–grade parts; TMIN ≤ TA = TMAX for industrial–grade parts; specifications apply to all DAC's unless noted otherwise.)

PARAMETER SIGNAL INPUTS Input Voltage Range Input Resistance SP9840 SP9843 Input Capacitance SP9840 SP9843 VREFL Resistance VREFL Capacitance DIGITAL INPUTS Logic High Logic Low Input Current Input Capacitance Input Coding STATIC ACCURACY Resolution Integral Nonlinearity Differential Nonlinearity Half-Scale Output Voltage Minimum Output Voltage Output Voltage Drift DYNAMIC PERFORMANCE Multiplying Gain Bandwidth Slew Rate Positive Negative Total Harmonic Distortion Output Settling Time Crosstalk Digital Feedthrough Wideband Noise SINAD Digital Crosstalk

元器件交易网

AD9833中文资料精编版

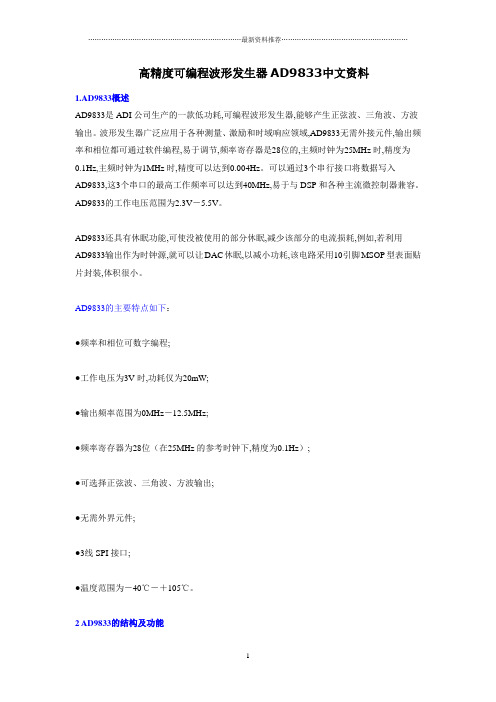

高精度可编程波形发生器AD9833中文资料1.AD9833概述AD9833是ADI公司生产的一款低功耗,可编程波形发生器,能够产生正弦波、三角波、方波输出。

波形发生器广泛应用于各种测量、激励和时域响应领域,AD9833无需外接元件,输出频率和相位都可通过软件编程,易于调节,频率寄存器是28位的,主频时钟为25MHz时,精度为0.1Hz,主频时钟为1MHz时,精度可以达到0.004Hz。

可以通过3个串行接口将数据写入AD9833,这3个串口的最高工作频率可以达到40MHz,易于与DSP和各种主流微控制器兼容。

AD9833的工作电压范围为2.3V-5.5V。

AD9833还具有休眠功能,可使没被使用的部分休眠,减少该部分的电流损耗,例如,若利用AD9833输出作为时钟源,就可以让DAC休眠,以减小功耗,该电路采用10引脚MSOP型表面贴片封装,体积很小。

AD9833的主要特点如下:●频率和相位可数字编程;●工作电压为3V时,功耗仅为20mW;●输出频率范围为0MHz-12.5MHz;●频率寄存器为28位(在25MHz的参考时钟下,精度为0.1Hz);●可选择正弦波、三角波、方波输出;●无需外界元件;●3线SPI接口;●温度范围为-40℃-+105℃。

2 AD9833的结构及功能2.1 电路结构AD9833是一块完全集成的DDS(Direct Digital Frequency Synthesis)电路,仅需要1个外部参考时钟、1个低精度电阻器和一个解耦电容器就能产生高达12.5MHz的正弦波。

除了产生射频信号外,该电路还广泛应外于各种调制解调方案。

这些方案全都用在数字领域,采用DSP技术能够把复杂的调制解调算法简化,而且很精确。

AD9833的内部电路主要有数控振荡器(NCO)、频率和相位调节器、Sine ROM、数模转换器(DAC)、电压调整器,其功能框图如图1所示。

AD933的核心是28位的相位累加器,它由加法器和相位寄存器组成,每来1个时钟,相位寄存器以步长增加,相位寄存器的输出与相位控制字相加后输入到正弦查询表地址中。

ATA8403_08中文资料

Features Array•Integrated PLL Loop Filter•ESD Protection also at ANT1/ANT2(4kV HBM/200V MM; Except Pin2: 4kV HBM/100V MM)•High Output Power (5.5 dBm) with Low Supply Current(8.5mA)•Modulation Scheme ASK/FSK–FSK Modulation is Achieved by Connecting an Additional Capacitor Between the XTAL Load Capacitor and the Open Drain Output of the Modulating Microcontroller •Easy to Design-in Due to Excellent Isolation of the PLL from the PA and Power Supply •Single Li-cell for Power Supply•Supply Voltage 2.0V to 4.0V in the Temperature Range of –40°C to +85°C•Package TSSOP8L•Single-ended Antenna Output with High Efficient Power Amplifier•CLK Output for Clocking the Microcontroller•One-chip Solution with Minimum External CircuitryApplications•Industrial/Aftermarket Remote Keyless Entry Systems•Alarm, Telemetering, and Energy Metering Systems•Remote Control Systems for Consumer and Industrial Markets•Access Control Systems•Home Automation•Home Entertainment•Toys1.DescriptionThe ATA8403 is a PLL transmitter IC, which has been developed for the demands of RF low-cost transmission systems for industrial applications at data rates up to 50kBaud ASK and 32kBaud FSK modulation scheme. The transmitting frequency range is 868MHz to 928MHz. It can be used in both FSK and ASK systems.Figure 1-1.System Block Diagram24983B–INDCO–10/08ATA84032.Pin ConfigurationFigure 2-1.Pinning TSSOP8L34983B–INDCO–10/08ATA8403Figure 2-2.Block Diagram44983B–INDCO–10/08ATA84033.General DescriptionThis fully integrated PLL transmitter allows particularly simple, low-cost RF miniature transmit-ters to be assembled. The VCO is locked to 64×f XTAL , and therefore a 13.5672MHz crystal is needed for a 868.3MHz transmitter and a 14.2969MHz crystal for a 915MHz transmitter. All other PLL and VCO peripheral elements are integrated.The XTO is a series resonance oscillator so that only one capacitor together with a crystal con-nected in series to GND are needed as external elements.The crystal oscillator together with the PLL typically needs <1ms until the PLL is locked and the CLK output is stable. There is a wait time of ≥4ms must be used until the CLK is used for the microcontroller and the PA is switched on.The power amplifier is an open-collector output delivering a current pulse, which is nearly inde-pendent from the load impedance. The delivered output power is therefore controllable via the connected load impedance.This output configuration enables a simple matching to any kind of antenna or to 50Ω. A high power efficiency of η=P out /(I S,PA ×V S ) of 24% for the power amplifier at 868.3MHz results when an optimized load impedance of Z Load =(166+j226)Ω is used at 3V supply voltage.4.Functional DescriptionIf ENABLE =L and the PA_ENABLE =L, the circuit is in standby mode, consuming only a very small amount of current, so that a lithium cell used as power supply can work for several years.With ENABLE =H the XTO, PLL, and the CLK driver are switched on. If PA_ENABLE remains L, only the PLL and the XTO are running and the CLK signal is delivered to the microcontroller.The VCO locks to 64 times the XTO frequency.With ENABLE =H and PA_ENABLE =H the PLL, XTO, CLK driver, and the power amplifier are on. The power amplifier can be switched on and off with PA_ENABLE. This is used to perform the ASK modulation.4.1ASK TransmissionThe ATA8403 is activated by ENABLE =H. PA_ENABLE must remain L for t ≥4ms, then the CLK signal can be taken to clock the microcontroller, and the output power can be modulated by means of the PA_ENABLE pin. After transmission, PA_ENABLE is switched to L, and the micro-controller switches back to internal clocking. The ATA8403 is switched back to standby mode with ENABLE =L.4.2FSK TransmissionThe ATA8403 is activated by ENABLE =H. PA_ENABLE must remain L for t ≥4ms, then the CLK signal can be taken to clock the microcontroller and the power amplifier is switched on with PA_ENABLE =H. The chip is then ready for FSK modulation. The microcontroller starts to switch on and off the capacitor between the XTAL load capacitor and GND with an open-drain output port, thus changing the reference frequency of the PLL. If the switch is closed, the output frequency is lower than if the switch is open. After transmission PA_ENABLE is switched to L and the microcontroller switches back to internal clocking. The ATA8403 is switched back to standby mode with ENABLE =L.The accuracy of the frequency deviation with XTAL pulling method is about ±25% when the fol-lowing tolerances are considered.54983B–INDCO–10/08ATA8403Figure 4-1.Tolerances of Frequency ModulationUsing C 4=9.2pF ±2%, C 5=6.8pF ±5%, a switch port with C Switch =3pF ±10%, stray capaci-tances on each side of the crystal of C Stray1=C Stray2=1pF ±10%, a parallel capacitance of the crystal of C 0=3.2pF ±10% and a crystal with C M =13fF ±10%, typically results in an FSK devi-ation of ±21.5kHz with worst case tolerances of ±16.8kHz to ±28.0kHz.4.3CLK OutputAn output CLK signal is provided for a connected microcontroller. The delivered signal is CMOS compatible if the load capacitance is lower than 10pF.4.3.1Clock Pulse Take-overThe clock of the crystal oscillator can be used for clocking the microcontroller. A special feature of Atmel ®’s ATARx9x is that it starts with an integrated RC-oscillator to switch on the ATA8403with ENABLE =H, and after 4ms assumes the clock signal of the transmission IC, so that the message can be sent with crystal accuracy.4.3.2Output Matching and Power SettingThe output power is set by the load impedance of the antenna. The maximum output power is achieved with a load impedance of Z Load,opt =(166+j226)Ω at 868.3MHz. There must be a low resistive path to V S to deliver the DC current.The delivered current pulse of the power amplifier is 7.7mA. The maximum output power is delivered to a resistive load of 475Ω if the 0.53pF output capacitance of the power amplifier is compensated by the load impedance.An optimum load impedance of:Z Load =475Ω||j/(2×p ×f ×0.53pF)=(166+j226)Ω thus results in the maximum output power of 5.5dBm.The load impedance is defined as the impedance seen from the ATA8403’s ANT1, ANT2 into the matching network. Do not confuse this large signal load impedance with a small signal input impedance delivered as input characteristic of RF amplifiers and measured from the application into the IC instead of from the IC into the application for a power amplifier.Less output power is achieved by lowering the real parallel part of 475Ω where the parallel imag-inary part should be kept constant.Output power measurement can be done with the circuit shown in Figure 4-2 on page 6. Note that the component values must be changed to compensate for the individual board parasitics until the ATA8403 has the right load impedance Z Load,opt =(166+j226)Ω at 868.3MHz. Also the damping of the cable used to measure the output power must be calibrated out.64983B–INDCO–10/08ATA8403Figure 4-2.Output Power Measurement4.4Application CircuitA value of 68nF/X7R is recommended for the supply-voltage blocking capacitor C 3 (see Figure 4-3 on page 7 and Figure 4-4 on page 8). C 1 and C 2 are used to match the loop antenna to the power amplifier where C 1 typically is 3.9pF/NP0 and C 2 is 1pF/NP0. For C 2, two capacitors in series should be used to achieve a better tolerance value and to have the possibility of realizing the Z Load,opt using standard valued capacitors.C 1, together with the pins of ATA8403 and the PCB board wires, forms a series resonance loop that suppresses the 1st harmonic. Therefore, the position of C 1 on the PCB is important. Nor-mally the best suppression is achieved when C 1 is placed as close as possible to the pins ANT1and ANT2.The loop antenna should not exceed a width of 1.5mm, otherwise the Q-factor of the loop antenna is too high.L 1(≈50nH to 100nH) can be printed on PCB. C 4 should be selected so that the XTO runs on the load resonance frequency of the crystal. Normally, a 15pF load-capacitance crystal results in a value of 12pF.74983B–INDCO–10/08ATA8403Figure 4-3.ASK Application Circuit84983B–INDCO–10/08ATA8403Figure 4-4.FSK Application Circuit94983B–INDCO–10/08ATA8403Figure 4-5.ESD Protection Circuit5.Absolute Maximum RatingsStresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Parameters Symbol MinimumMaximumUnit Supply voltage V S 5V Power dissipation P tot 100mW Junction temperature T j 150°C Storage temperature T stg –55+85°C Ambient temperature T amb –55+85°C Input voltage V maxP A_ENABLE–0.3(V S + 0.3)(1)VNote:1.If V S + 0.3 is higher than 3.7V , the maximum voltage will be reduced to 3.7V .6.Thermal ResistanceParameters Symbol Value Unit Junction ambientR thJA170K/W7.Electrical CharacteristicsV S = 2.0V to 4.0V , T amb = 25°C unless otherwise specified.T ypical values are given at V S = 3.0V and T amb = 25°C. All parameters are referred to GND (pin 7).Parameters Test ConditionsSymbol Min.Typ.Max.Unit Supply currentPower down,V ENABLE <0.25V , –40°C to 85°C V P A_ENABLE <0.25V , 25°C (100% correlation tested)I S_Off< 10350nA nA Supply currentPower up, P A off, V S = 3V ,V ENABLE >1.7V , V P A_ENABLE <0.25V I S 3.6 4.6mA Power up, V S =3.0,V ENABLE >1.7V , V P A_ENABLE >1.7V I S_T ransmit 8.511mA Output power V S =3.0V ,T amb =25°C,f =868.3 MHz, Z Load = (166 + j226)ΩP Ref3.55.58dBmNote:1.If V S is higher than 3.6V , the maximum voltage will be reduced to 3.6V .104983B–INDCO–10/08ATA8403Output power variation for the full temperature rangeT amb = 25°C,V S = 3.0V V S = 2.0V ΔP Ref ΔP Ref –1.5–4.0dB dB Output power variation for the full temperature rangeT amb = 25°C,V S = 3.0V V S = 2.0V ,P Out = P Ref + ΔP RefΔP Ref ΔP Ref –2.0–4.5dB dB Achievable output-power rangeSelectable by load impedance P Out_typ–3+5.5dBmSpurious emissionf CLK = f 0/128Load capacitance at pin CLK = 10pF f O ±1×f CLK f O ±4×f CLKOther spurious are lower–52–52dBc dBcOscillator frequency XTO(= phase comparator frequency)f XTO = f 0/64f XT AL = resonant frequency of the XTAL, C M ≤10 fF , load capacitance selected accordingly T amb = 25°Cf XTO f XT ALppmPLL loop bandwidth250kHz Phase noise of phase comparator Referred to f PC = f XT0,25 kHz distance to carrier –116–110dBc/Hz In-loop phase noise PLL 25 kHz distance to carrier –80–74dBc/Hz Phase noise VCO At 1MHz At 36MHz–89–120–86–117dBc/Hz dBc/Hz Frequency range of VCO f VCO868928MHz Clock output frequency (CMOS microcontroller compatible)f 0/256MHz Voltage swing at pin CLK C Load ≤10pFV 0h V 0l V S ×0.8V S ×0.2V V Series resonance R of the crystal Rs110ΩCapacitive load at pin XT07pF FSK modulation frequency rate Duty cycle of the modulation signal = 50%032kHz ASK modulation frequency rate Duty cycle of the modulation signal = 50%050kHz ENABLE inputLow level input voltage High level input voltage Input current high V Il V Ih I In 1.70.2520V V µA P A_ENABLE input Low level input voltage High level input voltage Input current highV Il V Ih I In1.70.25V S (1)5V V µA7.Electrical Characteristics (Continued)V S = 2.0V to 4.0V , T amb = 25°C unless otherwise specified.T ypical values are given at V S = 3.0V and T amb = 25°C. All parameters are referred to GND (pin 7).ParametersTest Conditions Symbol Min.Typ.Max.Unit Note:1.If V S is higher than 3.6V , the maximum voltage will be reduced to 3.6V .114983B–INDCO–10/08ATA84039.Package Information10.Revision History8.Ordering InformationExtended Type Number Package MOQ RemarksA T A8403-6AQYTSSOP8L5000 pcsTaped and reeled, Pb-freePlease note that the following page numbers referred to in this section refer to the specific revision mentioned, not to this document.Revision No.History4983B-INDCO-10/08• Put datasheet in the newest template• Section 7 “Electrical Characteristics” on page 10 changed4983B–INDCO–10/08HeadquartersInternationalAtmel Corporation 2325 Orchard Parkway San Jose, CA 95131USATel: 1(408) 441-0311Fax: 1(408) 487-2600Atmel Asia Room 1219Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong KongTel: (852) 2721-9778Fax: (852) 2722-1369Atmel Europe Le Krebs8, Rue Jean-Pierre Timbaud BP 30978054Saint-Quentin-en-Yvelines Cedex FranceTel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11Atmel Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Product ContactWeb SiteTechnical Support industrial@Sales Contact/contactsLiterature Requests /literatureDisclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise,to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL ’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL ’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.© 2008 Atmel Corporation. All rights reserved. Atmel ®, Atmel logo and combinations thereof, and others are registered trademarks or trade-marks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.。

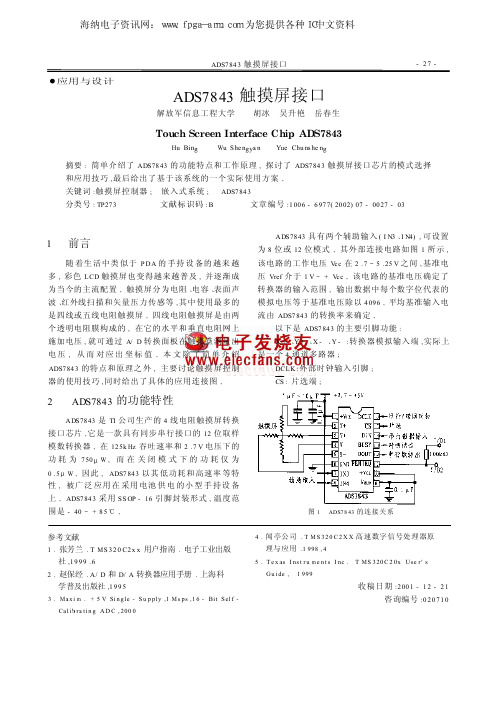

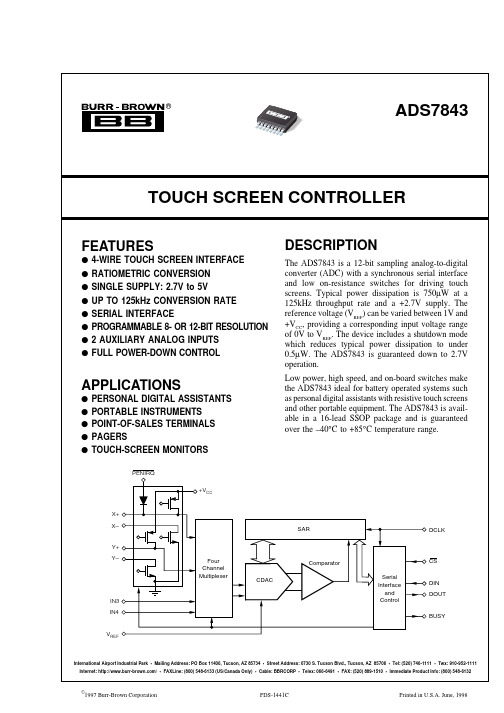

ads7843中文资料

•’—•p 应用与设计¡¤³—˜”“触摸屏接口解放军信息工程大学胡冰吴升艳岳春生Touch Scre e n Inte r f a ce Ch i p ADS7843¨Õ¢ÉÎÇ·Õ³ÈÅÎÇÙÁιÕÅ£ÈÕÎÓÈÅÎÇ摘要š简单介绍了¡¤³—˜”“的功能特点和工作原理Œ探讨了¡¤³—˜”“触摸屏接口芯片的模式选择和应用技巧Œ最后给出了基于该系统的一个实际使用方案"关键词š触摸屏控制器›嵌入式系统›¡¤³—˜”“分类号š´°’—“文献标识码š¢文章编号š‘••–•–™——ˆ’••’‰•—•••’—••“图‘¡¤³—˜”“的连接关系¡¤³—˜”“触摸屏接口‘前言随着生活中类似于°¤¡的手持设备的越来越多Œ彩色¬£¤触摸屏也变得越来越普及Œ并逐渐成为当今的主流配置"触摸屏分为电阻!电容!表面声波!红外线扫描和矢量压力传感等Œ其中使用最多的是四线或五线电阻触摸屏"四线电阻触摸屏是由两个透明电阻膜构成的Œ在它的水平和垂直电阻网上施加电压Œ就可通过¡•¤转换面板在触摸点测量出电压Œ从而对应出坐标值"本文除了简单介绍¡¤³—˜”“的特点和原理之外Œ主要讨论触摸屏控制器的使用技巧Œ同时给出了具体的应用连接图"’¡¤³—˜”“的功能特性¡¤³—˜”“是´©公司生产的”线电阻触摸屏转换接口芯片"它是一款具有同步串行接口的‘’位取样模数转换器"在‘’•Ë¨Ú吞吐速率和’Ž—¶电压下的功耗为—••L ·Œ而在关闭模式下的功耗仅为•Ž•L ·"因此Œ¡¤³—˜”“以其低功耗和高速率等特性Œ被广泛应用在采用电池供电的小型手持设备上"¡¤³—˜”“采用³³¯°•‘–引脚封装形式Œ温度范围是•”•*‹˜•e "¡¤³—˜”“具有两个辅助输入ˆ©®“!©®”‰Œ可设置为˜位或‘’位模式"其外部连接电路如图‘所示Œ该电路的工作电压¶ÃÃ在’Ž—*•Ž’•¶之间Œ基准电压¶ÒÅÆ介于‘¶*‹¶ÃÃ"该电路的基准电压确定了转换器的输入范围Œ输出数据中每个数字位代表的模拟电压等于基准电压除以”•™–"平均基准输入电流由¡¤³—˜”“的转换率来确定"以下是¡¤³—˜”“的主要引脚功能š¸‹!¹‹!¸•!¹•š转换器模拟输入端Œ实际上是一个”通道多路器›¤£¬«š外部时钟输入引脚›£³š片选端›参考文献‘Ž张芳兰Ž´-³“’•£’ØØ用户指南Ž电子工业出版社Œ‘™™™Ž–’Ž赵保经Ž¡•¤和¤•¡转换器应用手册Ž上海科学普及出版社Œ‘™™•“Ž-ÁØÉÍŽ‹•¶³ÉÎÇÌÅ•³ÕÐÐÌÙŒ‘-ÓÐÓŒ‘–•¢ÉÔ³ÅÌÆ•£ÁÌÉÂÒÁÔÉÎÇ¡¤£Œ’•••”Ž闻亭公司Ž´-³“’•£’¸¸高速数字信号处理器原理与应用Ž‘™™˜Œ”•Ž´ÅØÁÓ©ÎÓÔÒÕÍÅÎÔÓ©ÎÃŽ´-³“’•£’•ØµÓÅÒ‡Ó§ÕÉÄÅŒ‘™™™收稿日期š’••‘•‘’•’‘咨询编号š•’•—‘•海纳电子资讯网:www.fpga-arm.com 为您提供各种IC中文资料•’˜•5国外电子元器件6’••’年第—期’••’年—月¤©®š串行输入Œ其控制数据通过该引脚输入›¤¯µ´š串行数据输出Œ用于输出转换后的触摸位置数据Œ最大数为二进制的”•™•›©®“!©®”š辅助输入引脚›°¥®©²±š°¥®中断引脚Œ可用于在触摸显示屏后引发一个中断"“工作原理¡¤³—˜”“是一款连续近似记录ˆ³¡²‰的¡•¤转换器"可通过连结触摸屏¸‹将触摸信号输入到¡•¤转换器Œ同时打开¹‹和¹•驱动Œ然后数字化¸‹的电压Œ从而得到当前¹位置的测量结果"同理也可得到¸方向的坐标"具体设置和使用方法可查阅´©公司的¡¤³—˜”“数据手册Œ下面主要介绍¡¤³—˜”“的模式设置!°¥®中断引脚的使用和软件编程方法"“Ž‘模式设置¡¤³—˜”“有差分ˆ¤©¦¦¥²¥®´©¡¬‰和单端ˆ³©®2§¬¥•¥®¤¥¤-¯¤¥‰两种工作模式"这两种模式对转换后的精度和可靠性有一些影响"如果将¡•¤转换器配置为读绝对电压ˆ单端模式‰方式Œ那么驱动ˆ¤²©¶¥²‰电压的下降将导致转换输入数据的错误"而如果配置为差分模式Œ则可以避免上述错误"当触摸屏被按下时Œ有两种情况可影响接触点的电压š一种是当触摸到显示屏时Œ会导致触摸屏外层振动›另一种是触摸屏顶层和低层之间的寄生电容引起的电流振荡以及在¡¤³—˜”“输入引脚上引起的电压振荡"这两种情况都可导致触摸屏上的电压发生振荡以及增加¤£值稳定的时间"在单端模式中Œ一旦在触摸屏上检测到一次触摸事件Œ电路系统将发送一串控制字节给¡¤³—˜”“Œ并要求它进行一次转换"然后¡¤³—˜”“将在获取周期的起始点通过内部¦¥´开关给面板提供电压Œ而这将导致触摸点电压的升高"正如上面所介绍的Œ上升的电压在最终稳定之前会振荡一段时间"当获取周期结束后Œ所有的¦¥´开关关闭Œ¡•¤转换器进入转换周期"如果在转换周期期间Œ没有发出下一个控制字节Œ¡¤³—˜”“将进入低功耗模式并等待下一条指令"由于面板上分布有大量电容Œ特别是滤波噪音Œ因此Œ应该注意设置好对应于¸坐标或¹坐标上的电压"在单端模式中Œ输入电压必须在¤ÁÔÁ©Î×ÏÒÄ的最后三个时钟周期期间设置Œ否则将产生错误"除了内部¦¥´开关从获取周期开始到转换周期结束期间一直保持打开状态以外Œ差分模式的操作类似于单端模式"加在面板上的电压将成为¡•¤转换器的基准电压Œ提供一个度量比操作"这意味着如果加在面板上的电压发生变化ˆ由于电源!驱动电阻!温度或触摸屏电阻等原因‰Œ¡•¤转换器的度量比操作将对这种变化进行补偿"如果在当前转换周期发向¡¤³—˜”“的下一个控制字节所选择的通道与前一个控制字节相同Œ那么在当前转换完成后开关仍然不会关闭"在这两种模式中Œ¡¤³—˜”“只有“个时钟周期可以从触摸屏上获取ˆ取样‰输入模拟电压Œ因此Œ为了¡¤³—˜”“可以获取正确的电压Œ输入电压必须在“个时钟周期的时间范围内设置好"打开驱动将引起触摸屏的电压快速升高到最终值"为了得到正确的转换数据Œ获取必须在触摸屏完全设置好时完成"获取的方式有两种š一种是采用单端模式Œ即采用相对较慢的时钟扩展获取时间ˆ三个时钟周期‰›二是采用差分模式Œ即用相对较快的时钟在第一个转换周期内设置电压Œ在第二个转换周期获取准确电压"该方式的两个控制字节相同Œ且内部¸•¹开关在首次转换后不会关闭"由于首次转换期间电压还不稳定Œ因此应当丢弃首次转换的结果"使用第二种方式的另一个优点是功耗低"因为在全部转换后Œ¡¤³—˜”“会进入低功耗模式来等待下一次取样周期›对于慢时钟Œ下一次取样可能在当前转换结束后立即进入取样周期Œ而没有时间进入低功耗模式"实际在单端模式下不能使用快速时钟"差分模式还具有以下两个优点š第一个优点是能够在不扩展转换器获取时间的条件下用很长的设置时间处理触摸屏Œ即触摸屏电压可以有足够的时间稳定下来"第二个优点是¡¤³—˜”“通过快速时钟可以进入低功耗模式Œ从而可以节约电池能量"因此Œ通常建议使用差分模式"“Ž’°¥®中断引脚的使用°¥®中断引脚的主要作用是让设计者可以完全控制¡¤³—˜”“的低功耗操作模式"图’所示是其模式操作连接示意图"图中Œ©•¯‘和©•¯’是引自¥°—’‘’的通用目的输入•输出口"当电源加入系统且转换器被设置ˆ°¤‘Œ°¤••••‰之后Œ器件进入低功耗模式"而当未触摸面板时Œ¡¤³—˜”“内部的二极海纳电子资讯网:www.fpga-arm.com 为您提供各种IC中文资料•’™•¡¤³—˜”“触摸屏接口图“采用判断两次的方法来克服触摸屏信号的抖动图”采用最后的结果来克服触摸屏信号的抖动图’¡¤³—˜”“ˆ°¤•Œ°¤‘•••‰下的示意图管没有偏压Œ因此没有电流流过ˆ忽略漏流‰›当触摸面板时Œ¹•将提供一条电流ˆ©‰通路Œ这时¸‹!¸•和¹‹处于高阻状态Œ电流经过‘••Ë8电阻和中断二极管Œ°¥®©²±被拉低Œ从而通过©•¯’上一个不超过•Ž–•¶的电压唤醒£°µŒ然后¥°—’‘’再拉低©•¯‘和©•¯’上的电位Œ同时对¡¤³—˜”“控制寄存器写一个字节以进行转换初始化"为了转换°¥®©²±二极管上的偏置电压Œ¥°—’‘’必须拉低©•¯‘和©•¯’上的电压"否则Œ如果在转换期间二极管上有一个前向偏压Œ那么附加的电流将引起错误的输入数据"“Ž“错误触发由于¸‹输入引脚与°¥®中断输出相连Œ因此在¸‹上的噪声可能引起触摸屏的错误触发"设计时可以在°¥®中断输出引脚上连结一个²£滤波器ˆ可对地连结一个‘8的电阻和一个•Ž•‘L ¦的电容‰Œ以过滤噪声脉冲并避免错误触发"“Ž”差分模式下的软件流程图“和图”所示的两种算法假设¡¤³—˜”“配置成差分模式Œ每次转换为‘–个时钟Œ¸轴坐标的结果在¤¡´¡¸中Œ¹轴的坐标在¤¡´¡¹中"其中图“的例子采用的是判断两次的方法来克服触摸屏信号的抖动"¤¡´¡‘用于存储当前转换的结果Œ¤¡´¡’用于存储上一次转换的结果Œ当两次结果相同时Œ转换数据有效"但是Œ应当注意š当输入电压的振动频率和取样频率相近时Œ可能会漏掉正确结果"图”的例子是将最后的转换结果ˆ第Î次‰作为有效转换"可以看出š该方式更加简单Œ但该方法只对某一类触摸屏有效Œ且/Î0的具体值依赖于¡¤³—˜”“输入电压的设置时间Œ同时Œ在确定/Î0值以前还需要对一些触摸屏进行测试"参考文献‘Ž刘永智Œ杨开愚Ž液晶显示技术Ž电子科技大学出版社’Ž¡¤³—˜”“¤ÁÔÁÓÈÅÅÔ´©Œªµ¬¹Œ’••‘收稿日期š’••‘•‘’•’•咨询编号š•’•—‘‘海纳电子资讯网:www.fpga-arm.com 为您提供各种IC中文资料。

ADuC843BCP32-3中文资料

MicroConverter® 12-Bit ADCs and DACs withEmbedded High Speed 62-kB Flash MCUADuC841/ADuC842/ADuC843 Rev. 0Information furnished by Analog Devices is believed to be accurate and reliable.However, no responsibility is assumed by Analog Devices for its use, nor for anyinfringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: Fax: 781.326.8703© 2003 Analog Devices, Inc. All rights reserved.FEATURESPin compatable ugrade of ADuC812/ADuC831/ADuC832 Increased performanceSingle-cycle 20 MIPS 8052 coreHigh speed 420 kSPS 12-bit ADCIncreased memoryUp to 62 kBytes on-chip Flash/EE program memory4 kBytes on-chip Flash/EE data memoryIn-circuit reprogrammableFlash/EE, 100 year retention, 100 kCycle endurance2304 bytes on-chip data RAMSmaller package8 mm × 8 mm chip scale package52-lead PQFP—pin compatable upgradeAnalog I/O8-channel, 420 kSPS high accuracy, 12-bit ADCOn-chip, 15 ppm/°C voltage referenceDMA controller, high speed ADC-to-RAM captureTwo 12-bit voltage output DACs1Dual output PWM ∑-∆ DACsOn-chip temperature monitor function8052 based core8051 compatible instruction set (20 MHz max)High performance single-cycle core32 kHz external crystal, on-chip programmable PLL12 interrupt sources, 2 priority levelsDual data pointers, extended 11-bit stack pointerOn-chip peripheralsTime interval counter (TIC)UART, I2C®, and SPI® Serial I/OWatchdog timer (WDT)Power supply monitor (PSM)PowerNormal: 4.5 mA @ 3 V (core CLK = 2.098 MHz)Power-down: 10 µA @ 3 V2Development toolsLow cost, comprehensive development systemincorporating nonintrusive single-pin emulation,IDE based assembly and C source debugging APPLICATIONSOptical networking—laser power controlBase station systemsPrecision instrumentation, smart sensorsTransient capture systemsDAS and communications systems1 ADuC841/ADuC842 only.2 ADuC842/ADuC843 only, ADuC841 driven directly by external crystal.FUNCTIONAL BLOCK DIAGRAMREF11326--1Figure 1.GENERAL DESCRIPTIONThe ADuC841/ADuC842/ADuC843 are complete smart transducer front ends, that integrates a high performance self-calibrating multichannel ADC, a dual DAC, and an optimized single-cycle 20 MHz 8-bit MCU (8051 instruction set compatible) on a single chip.The ADuC841 and ADuC842 are identical with the exception of the clock oscillator circuit; the ADuC841 is clocked directly from an external crystal up to 20 MHz whereas the ADuC842 uses a 32 kHz crystal with an on-chip PLL generating a programmable core clock up to 16.78 MHz.The ADuC843 is identical to the ADuC842 except that the ADuC843 has no analog DAC outputs.The microcontroller is an optimized 8052 core offering up to 20 MIPS peak performance. Three different memory options are available offering up to 62 kBytes of nonvolatile Flash/EE program memory. Four kBytes of nonvolatile Flash/EE data memory, 256 bytes RAM, and 2 kBytes of extended RAM are also integrated on-chip.(continued on page 15)ADuC841/ADuC842/ADuC843Rev. 0 | Page 2 of 88TABLE OF CONTENTSSpecifications.....................................................................................3 Absolute Maximum Ratings............................................................8 ESD Caution..................................................................................8 Pin Configurations and Functional Descriptions........................9 Terminology....................................................................................11 ADC Specifications....................................................................11 DAC Specifications.....................................................................11 Typical Performance Characteristics...........................................12 Functional Description..................................................................16 8052 Instruction Set...................................................................16 Other Single-Cycle Core Features............................................18 Memory Organization...............................................................19 Special Function Registers (SFRs)............................................20 Accumulator SFR (ACC)...........................................................21 Special Function Register Banks..............................................22 ADC Circuit Information..........................................................23 Calibrating the ADC..................................................................30 Nonvolatile Flash/EE Memory.................................................31 Using Flash/EE Data Memory..................................................34 User Interface to On-Chip Peripherals....................................38 On-Chip PLL...............................................................................41 Pulse-Width Modulator (PWM)..............................................42 Serial Peripheral Interface (SPI)...............................................45 I 2C Compatible Interface...........................................................48 Dual Data Pointer.......................................................................51 Power Supply Monitor...............................................................52 Watchdog Timer.........................................................................53 Time Interval Counter (TIC)....................................................54 8052 Compatible On-Chip Peripherals...................................57 Timer/Counter 0 and 1 Operating Modes..............................62 Timer/Counter Operating Modes............................................64 UART Serial Interface................................................................65 SBUF............................................................................................65 Interrupt System.........................................................................70 Hardware Design Considerations............................................72 Other Hardware Considerations..............................................76 Development Tools....................................................................77 QuickStart Development System.............................................77 Timing Specifications , , ..................................................................78 Outline Dimensions.......................................................................86 Ordering Guides. (87)REVISION HISTORYRevision 0: Initial VersionADuC841/ADuC842/ADuC843Rev. 0 | Page 3 of 88SPECIFICATIONS 1Table 1. AV DD = DV DD = 2.7 V to 3.6 V or 4.75 V to 5.25 V; V REF = 2.5 V internal reference, f CORE = 16.78 MHz @ 5 V 8.38 MHz @ 3 V;all specifications T A = T MIN to T MAX , unless otherwise notedParameter V DD = 5 V V DD = 3 VUnit Test Conditions/CommentsADC CHANNEL SPECIFICATIONSDC ACCURACY 2, 3f SAMPLE = 120 kHz, see the TypicalPerformance Characteristics for typical performance at other values of f SAMPLEResolution 12 12 Bits Integral Nonlinearity ±1 ±1 LSB max 2.5 V internal reference ±0.3 ±0.3 LSB typ Differential Nonlinearity +1/–0.9 +1/–0.9 LSB max 2.5 V internal reference ±0.3 ±0.3 LSB typ Integral Nonlinearity 4 ±2 ±1.5 LSB max 1 V external referenceDifferential Nonlinearity 4+1.5/–0.9 +1.5/–0.9 LSB max 1 V external reference Code Distribution 1 1 LSB typ ADC input is a dc voltage CALIBRATED ENDPOINT ERRORS 5, 6 Offset Error ±3 ±2 LSB max Offset Error Match ±1 ±1 LSB typGain E rror ±3 ±2 LSB max Gain Error Match ±1 ±1 LSB typ DYNAMIC P E RFORMANC Ef IN = 10 kHz sine wave f SAMPLE = 120 kHzSignal-to-Noise Ratio (SNR)7 71 71 dB typ Total Harmonic Distortion (THD) –85 –85 dB typ Peak Harmonic or Spurious Noise –85 –85 dB typ Channel-to-Channel Crosstalk 8 –80 –80 dB typ ANALOG INPUTInput Voltage Range 0 to V REF 0 to V REF V Leakage Current ±1 ±1 µA max Input Capacitance 32 32 pF typ TEMPERATURE SENSOR 9Voltage Output at 25°C 700 700 mV typ Voltage TC –1.4 –1.4 mV/°C typ Accuracy ±1.5 ±1.5 °C typ Internal/External 2.5 V V REFDAC CHANNEL SPECIFICATIONSDAC load to AGND Internal Buffer EnabledADuC841/ADuC842 Only R L = 10 kΩ, C L = 100 pF DC ACCURACY 10Resolution 12 12 Bits Relative Accuracy ±3 ±3 LSB typ Differential Nonlinearity 11 –1 –1 LSB max Guaranteed 12-bit monotonic±1/2 ±1/2 LSB typ Offset E rror ±50 ±50 mV max V REF range Gain E rror ±1 ±1 % max AV DD range±1 ±1 % typ V REF range Gain Error Mismatch 0.5 0.5 % typ % of full-scale on DAC1 ANALOG OUTPUTSVoltage Range_0 0 to V REF 0 to V REF V typ DAC V REF = 2.5 V Voltage Range_1 0 to V DD 0 to V DD V typ DAC V REF = V DD Output Impedance0.5 0.5 Ω typADuC841/ADuC842/ADuC843Rev. 0 | Page 4 of 88ADuC841/ADuC842/ADuC843Rev. 0 | Page 5 of 88ADuC841/ADuC842/ADuC843Rev. 0 | Page 6 of 88Parameter V DD = 5 V V DD = 3 V Unit Test Conditions/Comments POWER REQUIREMENTS 19, 20Power Supply VoltagesAV DD /DV DD – AGND 2.7 V min AV DD /DV DD = 3 V nom 3.6 V max 4.75 V min AV DD /DV DD = 5 V nom 5.25 V maxPower Supply Currents Normal Mode 21DV DD Current 4 10 4.5 mA typ Core CLK = 2.097 MHz AV DD Current 1.7 1.7 mA max Core CLK = 2.097 MHz DV DD Current 38 12 mA max Core CLK = 16.78MHz/8.38 MHz 5 V/3 V 33 10 mA typ Core CLK = 16.78MHz/8.38 MHz 5 V/3 V AV DD Current 1.7 1.7 mA max Core CLK = 16.78MHz/8.38 MHz 5 V/3 V DV DD Current 4 Power Supply Currents Idle Mode 2145 N/A mA max Core CLK = 20MHz ADuC841 OnlyDV DD Current 4.5 2.2 mA typ Core CLK = 2.097 MHz AV DD Current 3 2 µA typ Core CLK = 2.097 MHzDV DD Current 412 5 mA max Core CLK = 16.78MHz/8.38 MHz 5 V/3 V 10 3.5 mA typ Core CLK = 16.78MHz/8.38 MHz 5 V/3 V AV DD Current 3 2 µA typ Core CLK = 16.78MHz/8.38 MHz 5 V/3 VPower Supply Currents Power-Down Mode 21Core CLK = any frequency DV DD Current 28 20 18 10 µA max µA typ Oscillator Off / TIMECON.1 = 0AV DD Current 2 1 µA typ Core CLK = any frequencyADuC841 OnlyDV DD Current 4 3 1 mA max TIMECON.1 = 1DV DD Current 450 40 22 15 µA max µA typ Core CLK = any frequencyADuC842/ADuC843 OnlyOscillator OnTypical Additional Power Supply CurrentsPSM Peripheral 15 10 µA typ AV DD = DV DDADC 41.02.8 1.0 1.8 mA min mA max MCLK Divider = 32MCLK Divider = 2DAC 150 130 µA typSee footnotes on the next page.ADuC841/ADuC842/ADuC8431 Temperature Range –40°C to +85°C.2 ADC linearity is guaranteed during normal MicroConverter core operation.3 ADC LSB size = V REF/212, i.e., for internal V REF = 2.5 V, 1 LSB = 610 µV, and for external V REF = 1 V, 1 LSB = 244 µV.4 These numbers are not production tested but are supported by design and/or characterization data on production release.5 Offset and gain error and offset and gain error match are measured after factory calibration.6 Based on external ADC system components, the user may need to execute a system calibration to remove additional external channel errors to achieve these specifications.7 SNR calculation includes distortion and noise components.8 Channel-to-channel crosstalk is measured on adjacent channels.9 The temperature monitor gives a measure of the die temperature directly; air temperature can be inferred from this result.10 DAC linearity is calculated using:Reduced code range of 100 to 4095, 0 V to V REF range.Reduced code range of 100 to 3945, 0 V to V DD range.DAC output load = 10 kΩ and 100 pF.11 DAC differential nonlinearity specified on 0 V to V REF and 0 V to V DD ranges.12 DAC specification for output impedance in the unbuffered case depends on DAC code.13 DAC specifications for I SINK, voltage output settling time, and digital-to-analog glitch energy depend on external buffer implementation in unbuffered mode. DAC in unbuffered mode tested with OP270 external buffer, which has a low input leakage current.14 Measured with C REF pin decoupled with 0.47 µF capacitor to ground. Power-up time for the internal reference is determined by the value of the decoupling capacitor chosen for the C REF pin.15 When using an external reference device, the internal band gap reference input can be bypassed by setting the ADCCON1.6 bit.16 Flash/EE memory reliability characteristics apply to both the Flash/EE program memory and the Flash/EE data memory.17 Endurance is qualified to 100,000 cycles as per JEDEC Std. 22 method A117 and measured at –40°C, +25°C, and +85°C. Typical endurance at 25°C is 700,000 cycles.18 Retention lifetime equivalent at junction temperature (T J) = 55°C as per JEDEC Std. 22 method A117. Retention lifetime based on an activation energy of 0.6 eV derates with junction temperature as shown in Figure 38 in the Flash/EE Memory Reliability section.19 Power supply current consumption is measured in normal, idle, and power-down modes under the following conditions:Normal Mode: Reset = 0.4 V, digital I/O pins = open circuit, Core Clk changed via CD bits in PLLCON (ADuC842/ADuC843), core executing internal software loop.Idle Mode: Reset = 0.4 V, digital I/O pins = open circuit, Core Clk changed via CD bits in PLLCON (ADuC842/ADuC843), PCON.0 = 1, core execution suspended in idle mode.Power-Down Mode: Reset = 0.4 V, all Port 0 pins = 0.4 V, All other digital I/O and Port 1 pins are open circuit, Core Clk changed via CD bits in PLLCON (ADuC842/ADuC843), PCON.0 = 1, core execution suspended in power-down mode, OSC turned on or off via OSC_PD bit (PLLCON.7) inPLLCON SFR (ADuC842/ADuC843).20 DV DD power supply current increases typically by 3 mA (3 V operation) and 10 mA (5 V operation) during a Flash/EE memory program or erase cycle.21 Power supply currents are production tested at 5.25 V and 3.3 V for a 5 V and 3 V part, respectively.Rev. 0 | Page 7 of 88ADuC841/ADuC842/ADuC843Rev. 0 | Page 8 of 88ABSOLUTE MAXIMUM RATINGSTable 2. T A = 25°C, unless otherwise notedParameter RatingAV DD to DV DD –0.3 V to +0.3 VAGND to DGND –0.3 V to +0.3 VDV DD to DGND, AV DD to AGND –0.3 V to +7 V Digital Input Voltage to DGND –0.3 V to DV DD + 0.3 V Digital Output Voltage to DGND –0.3 V to DV DD + 0.3 VV REF to AGND –0.3 V to AV DD + 0.3 VAnalog Inputs to AGND –0.3 V to AV DD + 0.3 VOperating Temperature Range,IndustrialADuC841BS,ADuC842BS,ADuC843BS ADuC841BCP, ADuC842BCP, ADuC843BCP–40°C to +85°C Storage Temperature Range –65°C to +150°C Junction Temperature 150°C θJA Thermal Impedance (ADuC84xBS) 90°C/W θJA Thermal Impedance (ADuC84xBCP) 52°C/W Lead Temperature, Soldering Vapor Phase (60 sec) Infrared (15 sec) 215°C220°CStresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.ESD CAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.S D A T ......ADC0ADC1ADC6ADC7C REFS 03260-0-002Figure 2. ADuC Block Diagram (Shaded Areas are Features Not Present on the ADuC812),No DACs on ADuC843, PLL on ADuC842/ADuC843 Only.ADuC841/ADuC842/ADuC843Rev. 0 | Page 9 of 88PIN CONFIGURATIONS AND FUNCTIONAL DESCRIPTIONSD 7D 6D 5D 4D 3D 2D 1D 0P 3.3P 3.4/T 0/P W M A P2.7/PWM1/A15/A23P2.6/PWM0/A14/A22P2.5/A13/A21P2.4/A12/A20DGND DV DD XT AL2XT AL1P2.3/A11/A19P2.2/A10/A18P2.1/A9/A17P2.0/A8/A16SDA T A/MOSI03260-0-003*EXTCLK NOT PRESENT ON THE ADuC841Figure 3. 52-Lead PQPFC V P 3.P 3.4/T 0/P W M DD D C 0/T 2D 7D 6D 5D 4D 3D 2D 1D 003260-0-004*EXTCLK NOT PRESENT ON THE ADuC841Figure 4. 56-Lead CSPADuC841/ADuC842/ADuC843Rev. 0 | Page 10 of 88ADuC841/ADuC842/ADuC843Rev. 0 | Page 11 of 88TERMINOLOGYADC SPECIFICATIONSIntegral NonlinearityThe maximum deviation of any code from a straight line passing through the endpoints of the ADC transfer function. The endpoints of the transfer function are zero scale, a point ½ LSB below the first code transition, and full scale, a point ½ LSB above the last code transition. Differential NonlinearityThe difference between the measured and the ideal 1 LSB change between any two adjacent codes in the ADC. Offset ErrorThe deviation of the first code transition (0000 . . . 000) to (0000 . . . 001) from the ideal, i.e., +½ LSB. Gain ErrorThe deviation of the last code transition from the ideal AIN voltage (Full Scale – ½ LSB) after the offset error has been adjusted out.Signal-to-(Noise + Distortion) RatioThe measured ratio of signal to (noise + distortion) at the output of the ADC. The signal is the rms amplitude of the fundamental. Noise is the rms sum of all nonfundamental signals up to half the sampling frequency (f S /2), excluding dc. The ratio depends on the number of quantization levels in the digitization process; the more levels, the smaller the quantization noise. The theoretical signal-to-(noise + distortion) ratio for an ideal N-bit converter with a sine wave input is given bySignal-to-(Noise + Distortion) = (6.02N + 1.76) dBThus for a 12-bit converter, this is 74 dB. Total Harmonic Distortion (THD)The ratio of the rms sum of the harmonics to the fundamental. DAC SPECIFICATIONSRelative AccuracyRelative accuracy or endpoint linearity is a measure of the maximum deviation from a straight line passing through the endpoints of the DAC transfer function. It is measured after adjusting for zero error and full-scale error. Voltage Output Settling TimeThe amount of time it takes for the output to settle to a specified level for a full-scale input change. Digital-to-Analog Glitch ImpulseThe amount of charge injected into the analog output when the inputs change state. It is specified as the area of the glitch in nV-sec.ADuC841/ADuC842/ADuC843Rev. 0 | Page 12 of 88TYPICAL PERFORMANCE CHARACTERISTICSThe typical performance plots presented in this section illustrate typical performance of the ADuC841/ADuC842/ ADuC843 under various operating conditions.Figure 5 and Figure 6 show typical ADC integral nonlinearity (INL) errors from ADC Code 0 to Code 4095 at 5 V and 3 V supplies, respectively. The ADC is using its internal reference (2.5 V) and is operating at a sampling rate of 152 kHz; thetypical worst-case errors in both plots are just less than 0.3 LSB. Figure 7 and Figure 8 also show ADC INL at a higher sampling rate of 400 kHz. Figure 9 and Figure 10 show the variation in worst-case positive (WCP) INL and worst-case negative (WCN) INL versus external reference input voltage.Figure 11 and Figure 12 show typical ADC differentialnonlinearity (DNL) errors from ADC Code 0 to Code 4095 at 5 V and 3 V supplies, respectively. The ADC is using its internal reference (2.5 V) and is operating at a sampling rate of 152 kHz; the typical worst-case errors in both plots are just less than 0.2 LSB. Figure 13 and Figure 14 show the variation in worst-case positive (WCP) DNL and worst-case negative (WCN) DNL versus external reference input voltage.Figure 15 shows a histogram plot of 10,000 ADC conversion results on a dc input with V DD = 5 V . The plot illustrates an excellent code distribution pointing to the low noise performance of the on-chip precision ADC.Figure 16 shows a histogram plot of 10,000 ADC conversion results on a dc input for V DD = 3 V . The plot again illustrates a very tight code distribution of 1 LSB with the majority of codes appearing in one output pin.Figure 17 and Figure 18 show typical FFT plots for the parts. These plots were generated using an external clock input. The ADC is using its internal reference (2.5 V), sampling a full-scale, 10 kHz sine wave test tone input at a sampling rate of 149.79 kHz. The resulting FFTs shown at 5 V and 3 V supplies illustrate an excellent 100 dB noise floor, 71 dB signal-to-noise ratio (SNR), and THD greater than –80 dB.Figure 19 and Figure 20 show typical dynamic performance versus external reference voltages. Again, excellent ac perform-ance can be observed in both plots with some roll-off being observed as V REF falls below 1 V .Figure 21 shows typical dynamic performance versus sampling frequency. SNR levels of 71 dB are obtained across the sampling range of the parts.Figure 22 shows the voltage output of the on-chip temperature sensor versus temperature. Although the initial voltage output at 25°C can vary from part to part, the resulting slope of −1. 4 mV/°C is constant across all parts.ADC CODES511L S B s1023204725593071–0.815353583–0.40.40.8409503260-0-05Figure 5. Typical INL Error, V DD = 5 V, fs = 152 kHzADC CODES5111023153520472559L S B s0.80.4–0.4–0.8307135830409503260-0-006Figure 6. Typical INL Error, V DD = 3 V, f s = 152 kHzADuC841/ADuC842/ADuC843Rev. 0 | Page 13 of 88ADC CODES–1.0511L S B s1023204725593071–0.815353583–0.6–0.4–0.200.20.40.60.81.0409503260-0-098Figure 7. Typical INL Error, V DD = 5 V, f S = 400 kHzADC CODES–1.0511L S B s1023204725593071–0.815353583–0.6–0.4–0.200.20.40.60.81.0409503260-0-099Figure 8. Typical INL Error, V DD = 3 V, f S = 400 kHzEXTERNAL REFERENCE (V)W C P –I N L (L S B s )0.51.0 1.52.0 2.5 5.0W C N –I N L (L S B s )03260-0-007Figure 9. Typical Worst-Case INL Error vs. V REF , V DD = 5 VEXTERNAL REFERENCE (V)W C P –I N L (L S B s )0.51.52.5W C N –IN L (L S Bs)0.80.40–0.4–0.80.60.2–0.2–0.63.02.01.003260-0-008Figure 10. Typical Worst-Case INL Error vs. V REF , V DD= 3 VADC CODES5111023153520472559LS B s0.80.4–0.4–0.8307135830409503260-0-009Figure 11. Typical DNL Error, V DD = 5 VADC CODES5111023153520472559L S B s0.80.40–0.4–0.8307135830409503260-0-010Figure 12. Typical DNL Error, V DD = 3 VADuC841/ADuC842/ADuC843Rev. 0 | Page 14 of 88EXTERNAL REFERENCE (V)–0.60.5W C P –D N L (L S B s )1.02.0 2.5 5.0–0.41.5–0.200.20.40.6W C N –D N L (L S B s )–0.4–0.6–0.20.20.40.603260-0-011Figure 13. Typical Worst-Case DNL Error vs. V REF , V DD = 5 VEXTERNAL REFERENCE (V)W C P –D N L (L S B s )0.51.0 1.52.0 2.53.0W C N –D N L (L S B s)0.70.50.1–0.5–0.70.3–0.3–0.103260-0-012Figure 14. Typical Worst-Case DNL Error vs. V REF , V DD = 3 V CODEO C C U R R E N C E03260-0-013Figure 15. Code Histogram Plot, V DD = 5 VCODE10000817818819820821O C C U RR E N C E80006000400020009000700050003000100003260-0-014Figure 16. Code Histogram Plot, V DD = 3 V200–20–40–60–80–100–120–140–160d B s20FREQUENCY (kHz)10706050403003260-0-015Figure 17. Dynamic Performance at V DD = 5 V200–20–40–60–80–100–120–140–160d B sFREQUENCY (kHz)03260-0-016Figure 18. Dynamic Performance at V DD = 3 VADuC841/ADuC842/ADuC843Rev. 0 | Page 15 of 88EXTERNAL REFERENCE (V)500.5S N R (d B s )1.02.0 2.5 5.055 1.56065707580T H D (d B s )–100–95–90–85–80–75–7003260-0-017Figure 19. Typical Dynamic Performance vs. V REF , V DD = 5 VEXTERNAL REFERENCE (V)S N R (d B s )0.51.52.5T H D (d B s )–70–75–85–100–80–95–901.02.03.003260-0-018Figure 20. Typical Dynamic Performance vs. V REF , V DD = 3 VFREQUENCY (kHz)6492.262S N R (d B s )119.050172.620199.410226.19066145.83068707276807874626065.47603260-0-019300.000350.000400.000Figure 21. Typical Dynamic Performance vs. Sampling FrequencyTEMPERATURE (°C)03260-0-1000.20.30.40.50.60.70.80.9–402585V O L T A G EFigure 22. Typical Temperature Sensor Output vs. TemperatureGENERAL DESCRIPTION (continued )The parts also incorporate additional analog functionality with two 12-bit DACs, power supply monitor, and a band gap reference. On-chip digital peripherals include two 16-bit ∑-∆. DACs, a dual output 16-bit PWM, a watchdog timer, a time interval counter, three timers/counters, and three serial I/O ports (SPI, I 2C, and UART).On the ADuC812 and the ADuC832, the I 2C and SPI interfaces share some of the same pins. For backwards compatibility, this is also the case for the ADuC841/ADuC842/ADuC843.However, there is also the option to allow SPI operate separately on P3.3, P3.4, and P3.5, while I 2C uses the standard pins. The I 2C interface has also been enhanced to offer repeated start, general call, and quad addressing.On-chip factory firmware supports in-circuit serial download and debug modes (via UART) as well as single-pin emulation mode via the EA pin. A functional block diagram of the parts is shown on the first page.ADuC841/ADuC842/ADuC843Rev. 0 | Page 16 of 88FUNCTIONAL DESCRIPTION8052 INSTRUCTION SETTable 4 documents the number of clock cycles required for each instruction. Most instructions are executed in one or two clock cycles, resulting in a 16 MIPS peak performance when operating at PLLCON = 00H on the ADuC842/ADuC843. On the ADuC841, 20 MIPS peak performance is possible with a 20 MHz external crystal.Table 4. InstructionsMnemonic DescriptionBytes CyclesArithmeticADD A,Rn Add register to A 1 1 ADD A,@Ri Add indirect memory to A 1 2 ADD A,dir Add direct byte to A 2 2 ADD A,#data Add immediate to A 2 2 ADDC A,Rn Add register to A with carry 1 1 ADDC A,@Ri Add indirect memory to A with carry 1 2 ADDC A,dir Add direct byte to A with carry 2 2 ADD A,#data Add immediate to A with carry 2 2 SUBB A,Rn Subtract register from A with borrow 1 1 SUBB A,@Ri Subtract indirect memory from A with borrow 1 2 SUBB A,dir Subtract direct from A with borrow 2 2 SUBB A,#data Subtract immediate from A with borrow 2 2 INC A Increment A 1 1 INC Rn Increment register 1 1 INC @Ri Increment indirect memory 1 2 INC dir Increment direct byte 2 2 INC DPTR Increment data pointer 1 3 DEC A Decrement A 1 1 DEC Rn Decrement register 1 1 DEC @Ri Decrement indirect memory 1 2 DEC dir Decrement direct byte 2 2 MUL AB Multiply A by B 1 9 DIV AB Divide A by B 1 9 DA A Decimal adjust A1 2 LogicANL A,Rn AND register to A 1 1 ANL A,@Ri AND indirect memory to A 1 2 ANL A,dir AND direct byte to A 2 2 ANL A,#data AND immediate to A 2 2 ANL dir,A AND A to direct byte 2 2 ANL dir,#data AND immediate data to direct byte 3 3 ORL A,Rn OR register to A 1 1 ORL A,@Ri OR indirect memory to A 1 2 ORL A,dir OR direct byte to A 2 2 ORL A,#data OR immediate to A 2 2 ORL dir,A OR A to direct byte 2 2 ORL dir,#data OR immediate data to direct byte 3 3 XRL A,Rn Exclusive-OR register to A 1 1 XRL A,@Ri Exclusive-OR indirect memory to A 2 2 XRL A,#data Exclusive-OR immediate to A 2 2 XRL dir,A Exclusive-OR A to direct byte2 2。

AD8402中文资料

REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Coefficient Full-Scale Error Zero-Scale Error

N INL DNL ∆VW/∆T

VWFSE VWZSE

VDD = 5 V, VSS = 0 V Code = 80H

Code = FFH Code = 00H

8

Bits

–1.5

+1.5 LSB

–1

+1

LSB

15

ppm/°C

–1.5

LSB

+1.5 LSB

RESISTOR TERMINALS Voltage Range5 Capacitance6 AX, BX Capacitance6 WX Shutdown Current7

Shutdown Wiper Resistance

Common-Mode Leakage

AD5207–SPECIFICATIONS

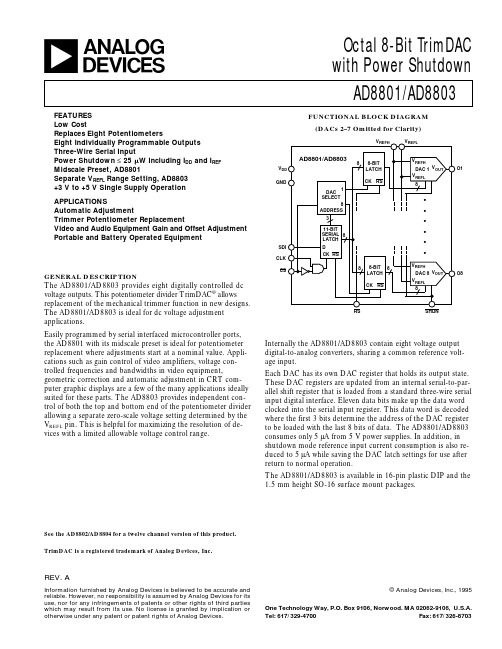

AD8803中文资料

0 0 2 25 25 2.4

VDD VDD

0.8 2.1 0.6 ±1 5 2.7 5.5 5 4 5 27.5 0.002

VIH = VDD or VIL = 0 V VIH = 2.4 V or VIL = 0.8 V, VDD= +5.5 V SHDN = 0 VIH = VDD or VIL = 0 V, VDD = +5.5 V VDD = 5 V ± 10%, VREFH = +4.5 V VDD = 3 V ± 10%, VREFH = +2.7 V ± 1/2 LSB Error Band See Note 5, f = 100 kHz Clock Level High or Low 15 5 5 10 10 60 15 10

See the AD8802/AD8804 for a twelve channel version of this product. TrimDAC is a registered trademark of Analog Devices, Inc.

REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. © Analog Devices, Inc., 1995 One Technology Way, P.O. Box 9106, Norwood. MA 02062-9106, U.S.A. Tel: 617/329-4700 Fax: 617/326-8703

AD8403中文资料,AD8403规格书PDF

TEL:139****79453W 无滤波器D 类立体声音频功分器AD8403芯片功能说明:实物图:ØAD8403立体声功率放大器能够以D 类放大器的效果提供AB 类功率放大器的性能。

采用低噪音,无滤波器结构可以省去传统D 类放大器的输出低通滤波器。

需要极少的外围元件,从而节省PCB 的空间和系统成本,是便携式应用的理想选择。

AD8403能够高于85%的效率提供3W 功率,同时具有系统关断及静音控制功能。

特殊的线路架构增强了抗噪音能力,减少了射频干扰。

芯片功能主要特性:Ø无滤波器的D 类放大器,低静态电流和低EMI Ø在4Ω负载和5V 电源条件下,提供高达3W 输出功率Ø效率高达90%Ø低THD ,低噪音Ø短路电流保护Ø热保护Ø极少的外围元器件,减少空间和成本Ø封装形式:SOP-16,无铅封装Ø关断电路16uA Ø待机电流6.3mA 芯片基本应用:ØLCD 电视、监视器Ø手机免提电话Ø笔记本电脑Ø便携式DVD 播放器,游戏机深1ØØQQÿ10936721003W无滤波器D类立体声音频功分器AD8403结构框图图1.AD8403结构框图封装引脚图图2.AD8403SOP-16封装引脚分布图深23W 无滤波器D 类立体声音频功分器AD8403典型应用图图3.AD8403典型应用电路图AD8403引脚描述深33W无滤波器D类立体声音频功分器AD8403电器特性极限参数A典型参数深43W无滤波器D类立体声音频功分器AD8403芯片封装尺寸如没有特别提示,所有尺寸标注均为:(毫米)深5。

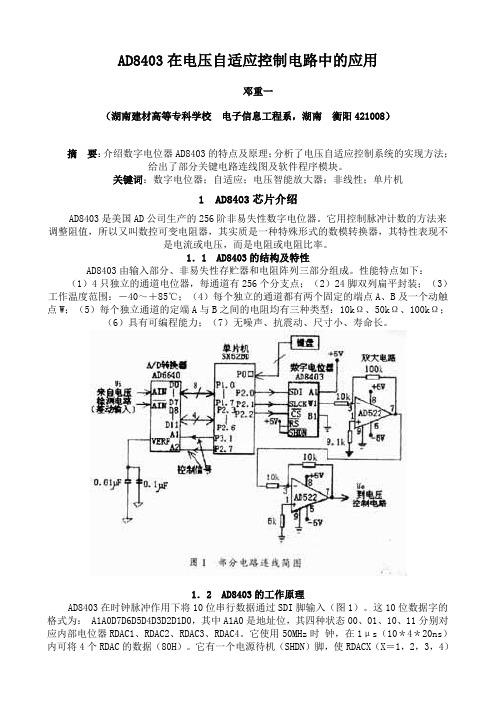

AD8403在电压自适应控制电路中的应用

AD8403在电压自适应控制电路中的应用邓重一(湖南建材高等专科学校电子信息工程系,湖南衡阳421008)摘要:介绍数字电位器AD8403的特点及原理;分析了电压自适应控制系统的实现方法;给出了部分关键电路连线图及软件程序模块。

关键词:数字电位器;自适应;电压智能放大器;非线性;单片机1 AD8403芯片介绍AD8403是美国AD公司生产的256阶非易失性数字电位器。

它用控制脉冲计数的方法来调整阻值,所以又叫数控可变电阻器,其实质是一种特殊形式的数模转换器,其特性表现不是电流或电压,而是电阻或电阻比率。

1.1 AD8403的结构及特性AD8403由输入部分、非易失性存贮器和电阻阵列三部分组成。

性能特点如下:(1)4只独立的通道电位器,每通道有256个分支点;(2)24脚双列扁平封装;(3)工作温度范围:-40~+85℃;(4)每个独立的通道都有两个固定的端点A、B及一个动触点W;(5)每个独立通道的定端A与B之间的电阻均有三种类型:10kΩ、50kΩ、100kΩ;(6)具有可编程能力;(7)无噪声、抗震动、尺寸小、寿命长。

1.2 AD8403的工作原理AD8403在时钟脉冲作用下将10位串行数据通过SDI脚输入(图1)。

这10位数据字的格式为: A1A0D7D6D5D4D3D2D1D0,其中A1A0是地址位,其四种状态00、01、10、11分别对应内部电位器RDAC1、RDAC2、RDAC3、RDAC4。

它使用50MHz时钟,在1μs(10*4*20ns)内可将4个RDAC的数据(80H)。

它有一个电源待机(SHDN)脚,使RDACX(X=1,2,3,4)置于零功耗状态,这时AX端开路,而滑动触点WX接到B端,仅产生RDACX的漏电流。

在待机方式下,内部RDACX锁存器保存设置的数据,以便从电源待机方式返回到工作方式时RDACX 输出恢复到待机之前的阻值。

它含有一个标准三线串行输入控制接口(CLK、CS、SDI),时钟上升沿有效,将数据置入寄存器。

常用AD芯片介绍共7页word资料

目前生产AD/DA的主要厂家有ADI、TI、BB、PHILIP、MOTOROLA等,武汉力源公司拥有多年从事电子产品的经验和雄厚的技术力量支持,已取得排名世界前列的模拟IC生产厂家ADI、TI 公司代理权,经营全系列适用各种领域/场合的AD/DA器件。

1. AD公司AD/DA器件AD公司生产的各种模数转换器(ADC)和数模转换器(DAC)(统称数据转换器)一直保持市场领导地位,包括高速、高精度数据转换器和目前流行的微转换器系统(MicroConvertersTM )。

1)带信号调理、1mW功耗、双通道16位AD转换器:AD7705AD7705是AD公司出品的适用于低频测量仪器的AD转换器。

它能将从传感器接收到的很弱的输入信号直接转换成串行数字信号输出,而无需外部仪表放大器。

采用Σ-Δ的ADC,实现16位无误码的良好性能,片内可编程放大器可设置输入信号增益。

通过片内控制寄存器调整内部数字滤波器的关闭时间和更新速率,可设置数字滤波器的第一个凹口。

在+3V电源和1MHz主时钟时, AD7705功耗仅是1mW。

AD7705是基于微控制器(MCU)、数字信号处理器(DSP)系统的理想电路,能够进一步节省成本、缩小体积、减小系统的复杂性。

应用于微处理器(MCU)、数字信号处理(DSP)系统,手持式仪器,分布式数据采集系统。

2)3V/5V CMOS信号调节AD转换器:AD7714AD7714是一个完整的用于低频测量应用场合的模拟前端,用于直接从传感器接收小信号并输出串行数字量。

它使用Σ-Δ转换技术实现高达24位精度的代码而不会丢失。

输入信号加至位于模拟调制器前端的专用可编程增益放大器。

调制器的输出经片内数字滤波器进行处理。

数字滤波器的第一次陷波通过片内控制寄存器来编程,此寄存器可以调节滤波的截止时间和建立时间。

AD7714有3个差分模拟输入(也可以是5个伪差分模拟输入)和一个差分基准输入。

单电源工作(+3V或+5V)。

触摸芯片ADS7843 datasheet 数据手册