4第四章ARM汇编语言程序设计.pptx

合集下载

第4章汇编语言程序设计PPT教学课件

图 分支程序结构流程图

2020/12/11

《单片机应用技术》教学课件

12Leabharlann 第4章 汇编语言程序设计条件满足? Y

A

4.2.2 分支程序结构

第4章 汇编语言程序设计

目的:1.进一步熟悉指令系统 2.会编写简单的程序 3.上机训练

内容:4.1 汇编语言程序设计概述

4.2 三种程序结构 4.3 程序设计举例

2020/12/11

《单片机应用技术》教学课件

1

第4章 汇编语言程序设计

4.1 汇编语言程序设计概述

所谓程序设计,就是按照给定的任务要求,编写 出完整的计算机程序。要完成同样的任务,使用的方 法或程序并不是唯一的。

汇编后: (1000H)=12H (1001H ) = 34H

(1002H ) = 00H ( 1003H ) = ABH (1004H ) =00H (1005H) =0AH

2020/12/11

《单片机应用技术》教学课件

7

第4章 汇编语言程序设计

• (6)定义存储区伪指令DS

• 功能:从指定地址开始预留一定数量的内 存单元,以备源程序执行过程中使用。预

(4) 编写源程序

(5) 程序优化。

(6)上机调试、修改和最后确定源程序。

2020/12/11

《单片机应用技术》教学课件

10

第4章 汇编语言程序设计

4.2.1 顺序程序设计

顺序结构程序是一种最简单、最基本的程序,按照程序编 写的顺序依次执行。

【例4-1】两个多字节数加法

1.两个三字节无符号相加,其中被加数在内部RAM的 50H、51H和52H单元中;加数在内部RAM的53H、54H和 55H单元中;要求把相加之和存放在50H、51H和52H单元中 进位存放在位寻址区的00H位中。

ARM汇编语言程序设计基础.ppt

一个汇编程序至少应该有一个代码段,由具体的设计需求,也可由多个 代码段和数据段组成,多个段在程序汇编链接时最终形成一个可执行的 映象文件。可执行映象文件通常由以下几部分构成: ① 一个或多个代码段,代码段的属性为只读。

② 零个或多个包含初始化数据的数据段,数据段的属性为可读写。 ③ 零个或多个不包含初始化数据的数据段,数据段的属性为可读写。

嵌入式系统 原理与应用

第四章 ARM汇编语言程序设计基础

XUPT

目 录

4.1 ARM汇编语言的程序结构

4.2 ARM汇编语言程序设计

4.3 C与汇编混合编程

本章小结

2

4.1 ARM汇编语言的程序结构

本章通过一个完整的ARM汇编例子入手,给出了ARM汇编程序的基本 框架,并详细介绍了编写汇编程序常用的汇编器伪指令,具备了这些基 础知识,学生就能自己动手编写汇编程序。 4.1.1 一个简单的ARM汇编程序例子 4.1.2 汇编器伪指令 4.1.3 汇编语言的规范

;定义代码段,名字为 ;定义数据段,名字为

AREA伪指令用于定义一个代码段或数据段。其中,段名若以数字开头 ,则该段名需用 “ | ” 括起来,如 |1_data| 。属性字段表示该代 码段(或数据段)的相关属性,例如:CODE(定义代码段), DATA(定义数据段),READONLY(只读),READWRITE(读 写)。多个属性用逗号分隔。

num_d

0xFB 0xFF 0xFF 0xFF 0xEF 0xCD 0xAB 0x90

SPACE 语法格式:标号 SPACE 表达式 SPACE用于分配一片连续的存储区域并初始化为0。其中,表达式为 要分配的字节数。例如: data SPACE 1024 ;分配1024个字节空间并初始化为0 LTORG LTORG用于声明一个文字池,用来存放常量,特别是不符合8位位图 数据标准的常数。其使用情景及实例见本章的4.2.1节。

第4章汇编语言程序设计ppt课件

DATA1

11

22

33 44

DATA2

11

00

22

00

44

33

DATA3

22

0

0

0

22

0

0

0

XX

66

55 44 33

28

数据定义伪指令的几点 说明

伪指令的性质决定所定义变量的类型;

定义字符串必须用DB伪指令

例:

DATA1 DB ‘ABCD’,66H

41H

‘A’

42H

‘B’

43H

‘C’

44H

‘D’

AH

DISN:T D2X1H

功能号OAH 字符串在内存中的存放地址

58

2. 定义字符缓冲区

用户自定义缓冲区格式:

N1 N2

存放字符个数:≤255

存放键入的字符 整个缓冲区

实际键入字符数 最大可键入字符数

0DH

59

输入字符串程序段

DAT1 DB 20,?,20 DUP(?)

┇

LEA DX,DAT1 MOV AH,0AH INT 21H

定义的变量为4字型(8字节)

定义的变量为10字节型

26

数据定义伪指令例

DATA1 DB 11H,22H,33H,44H DATA2 DW 11H,22H,3344H DATA3 DD 11H*2,22H,33445566H

以上变量在内存中的 存放形式

27

数据定义伪指令例_变量在内存中的

分布

DSEG SEGMENT DATA1 DB 1,2, 3 DUP(?) DATA2 DW 1234H

DSEG ENDS ESEG SEGMENT

[信息与通信]ARM汇编语言程序设计.ppt

![[信息与通信]ARM汇编语言程序设计.ppt](https://img.taocdn.com/s3/m/55993d1f0722192e4536f6c2.png)

变量类型:数字变量、逻辑变量和串变量。 GBLA GBLL GBLS和LCLA LCLL LCLS分别定义全局、 局部的数字变量、逻辑变量和串变量。

SETA SETL STES 为其赋值。

18

汇编程序的变量代换 p97

★ $字符串变量 在字符串变量的前面有一个$字符,在汇编时编译器 将用该字符串变量的内容代替该串变量。 例 $str1 ; 取其内容 例1: LCLS str1 ;定义局部串变量 LCLS str2 str1 SETS “book” ;赋值 str2 SETS “It is a $str1” ;赋值 则在汇编后,str2的值为”It is a book”。

9

注意: ARM程序中,指令、伪指令、伪操作、寄存 器助记符可以全部为大写或小写,但大小写不能混合 使用。

ARM程序中的符号 符号包括变量、标号、局部标号和数字常 量,符号是变量、标号时又代表其地址。 符号命名规则:

由大小写字母、数字和下划线组成,且字母区分大小写。

除局部标号以数字开头外,其他符号不能以数字开头。 符号不能与助记符重名,且在其作用范围内唯一。 符号一般以字母开头,由字母、数字、下划线组成。 例: a12 x1 x2

20

★ 变量名 . 使用“.”表示字符串中变量名的结束。 str2 SETS “$c” ;变量名是num1

num1是数字变量。 str2的内容为:num1的内容转换成十六进制数后拼 接ccc。 ★ |$| 一般的,在两个 | 之间的“$”并不进行变量的代换, 但如果 | 在双引号内,则将进行变量代换。

执行之

armcc -g hello.s -o hello.axf

3

4.1.1 汇编语言程序的结构

p93

在ARM(Thumb)汇编语言程序中,以程序段为单 位组织代码。

第四章ARM汇编语言程序设计-PPT精选文档

Start

AREA Init, CODE, READONLY ENTRY Start LDR R0, =0x3FF5000 LDR R1, 0xFF BL PRINT_TEXT …. …. PRINT_TEXT …. …. MOV PC, LR END

;FULL SEGMENT DEFINITION-----Intel 8086 ;-----stack segment-------STACK SEGMENT DB 64 DUP(?) STACK ENDS ;-----data segment-------DATA SEGMENT ;data definitions are placed here DATA ENDS ;-----code segment-------CODE SEGMENT MAIN PROC FAR ASSUME CS: CODE, DS: DATA, SS: STACK MOV AX, DATA MOV DS, AX - ----MOV AH, 4CH INT 21H MAIN ENDP CODE ENDS END MAIN

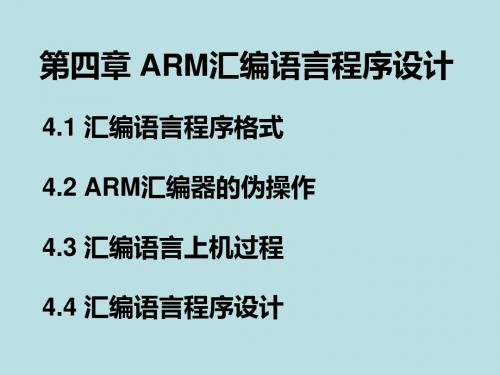

第四章 ARM汇编语言程序设计

4.1 汇编语言程序格式 4.2 ARM汇编器的伪操作

4.3 汇编语言上机过程 4.4 汇编语言程序设计

4.1 汇编语言程序格式

4.1.1 汇编语言程序的组成

AREA Init, CODE, READONLY ENTRY LDR R0, =0x3FF5000 LDR R1, 0xFF STR R1, [R0] LDR R0, =0x3FF5008 LDR R1, 0x01 STR R1, [R0] …. END

示例:

Str DCB “This is a test!”

• DCW

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

语法格式:

变量名 SETA(SETL或SETS)表达式

伪指令SETA、SETL、SETS给一个已经定义 的全局变量或局部变量赋值。

SETA伪指令用于给一个数学变量赋值; SETL伪指令用于给一个逻辑变量赋值; SETS伪指令用于给一个字符串变量赋值;

其中,变量名为已经定义过的全局变量 或局部变量,表达式为将要赋给变量的值。

GBLS Test3

;定义一个全局的字符串变量,变量名为Test3

Test3 SETS "Testing"

;将该变量赋值为"Testing"

ARM 指令系统

2、 LCLA、LCLL和LCLS

语法格式:

LCLA(LCLL或LCLS) 局部变量名

LCLA、LCLL和LCLS伪指令用于定义一个ARM程

序中的局部变量,并将其初始化。其中:

伪指令仅在汇编过程中起作用,一 旦汇编结束,伪指令的使命就完成。

指令 : 由ARM处理器执行

ARM 指令系统

在ARM的汇编程序中,有如下几种伪指令:

符号定义伪指令、 数据定义伪指令、 汇编控制伪指令、 宏指令以及其他伪指令。

ARM 指令系统

4.1.1 符号定义伪指令

符号定义伪指令用于定义ARM汇 编程序中的变量、对变量赋值以及定 义寄存器的别名等操作。

LCLA伪指令用于定义一个局部的数字变量, 并初始化为0;

LCLL伪指令用于定义一个局部的逻辑变量, 并初始化为F(假);

LCLS伪指令用于定义一个局部的字符串变量, 并初始化为空;

以上三条伪指令用A Test4 ;声明一个局部的数字变量, 变量名为Test4

Test3 SETA 0xaa ; 将 该 变 量 赋 值 为

0xaa

LCLL Test5;声明一个局部的逻辑变量,变 量名为Test5

Test4 SETL

真

{TRUE};将该变量赋值为

LCLS Test6;定义一个局部的字符串变量, 变量名为Test6

Test6 SETS “Testing” ;将该变量 赋值为“Testing”

3、 SETA、SETL和SETS

ARM 指令系统

4.1.1 符号定义伪指令

常见的符号定义伪指令有如下几种:

— 用于定义全局变量的GBLA、GBLL和 GBLS。

— 用于定义局部变量的LCLA、LCLL和 LCLS。

— 用于对变量赋值的SETA、SETL、SETS。 — 为通用寄存器列表定义名称的RLIST。

1、 GBLA、GBLL和GBLS 语法格式:

ARM 指令系统 使用示例:

LCLA Test3

;声明一个局部的

数字变量,变量名为Test3

Test3 SETA 0xaa;将该变量赋值为

0xaa

LCLL Test4

;声明一个局部的

逻辑变量,变量名为Test4

Test4 SETL {TRUE} ; 将 该 变

量赋值为真

4、 RLIST

名称 RLIST {寄存器列表}

由于以上三条伪指令用于定义全局变量,因此在整个 程序范围内变量名必须唯一。

GBLA Test1

;定义一个全局的数字变量,变量名为Test1

Test1 SETA 0xaa

;将该变量赋值为0xaa

GBLL Test2

;定义一个全局的逻辑变量,变量名为Test2

Test2 SETL {TRUE}

;将该变量赋值为真

RLIST伪指令可用于对 一个通用寄存器列表定义名称,使 用该伪指令定义的名称可在ARM指 令LDM/STM中使用。

在LDM/STM指令中,列 表中的寄存器访问次序为根据寄存 器的编号由低到高,而与列表中的 寄存器排列次序无关。

RLIST使用示例:

RegList RLIST {R0-R5,R8,R10}

— DCFS(DCFSU) 用 于 为 单 精 度 的 浮 点 数分配一片连续的字存储单元并用指定的数据 初始化。

— DCQ(DCQU) 用于分配一片以8字节 为单位的连续的存储单元并用指定的数据初始 化。

DCD(DCDU)用于分配一片连续的字存储单 元并用指定的数据初始化。

SPACE 用于分配一片连续的存储单元

分配存储单元,同时可完成已分配存储单元

的初始化。常见的数据定义伪指令有如下几 种:

— DCB

用于分配一片连续的字节存储单元并用

指定的数据初始化。

—DCW(DCWU) 用于分配一片连续的半字存储 单元并用指定的数据初始化。

— DCFD(DCFDU)用于为双精度的浮点数分配一片 连续的字存储单元并用指定的数据初始化。

将寄存器列表名称定义为RegList, 可在ARM指令LDM/STM中通过该名称 访问寄存器列表。

例:

RegList RLIST {r1-r13};必须顶格开始写

LDMIA r0,RegList

ARM 指令系统

4.1.2 数据定义(Data Definition)伪指令 数据定义伪指令一般用于为特定的数据

3. 注释可以在一行的顶格书写。

ARM 指令系统

4.1伪操作

在ARM汇编语言程序里,有一些特殊 指令助记符,这些助记符与指令系统的

助记符不同,没有相对应的操作码,通 常称这些特殊指令助记符为伪指令

他们所完成的操作称为伪操作。

ARM 指令系统

伪指令 : 由汇编器处理

伪指令是由汇编器对源程序汇编期 间进行处理的.

MAP 用于定义一个结构化的内存表首地址

GBLA(GBLL或GBLS) 全局变量名

GBLA、GBLL和GBLS伪指令用于定义一个ARM程 序中的全局变量,并将其初始化。

GBLA伪指令用于定义一个全局的数字变量,并初始 化为0;

GBLL伪指令用于定义一个全局的逻辑变量,并初始 化为F(假);

GBLS伪指令用于定义一个全局的字符串变量,并初 始化为空;

第四章 ARM汇编语言程序设计

ADS1.2环境下的汇编语句格式

1. ARM 汇编中,所有标号必须在一行的顶格书写, 其后面不要添加“:”,而所有指令均不能顶格书写。

2. ARM 汇编器对标识符大小写敏感,书写标号及 指令时字母大小写要一致,在ARM 汇编程序中,一个 ARM 指令、伪指令、寄存器名可以全部为大写字母, 也可以全部为小写字母,但不要大小写混合使用(如 果混合使用也能编译通过,如mov SP, r6能编译 通过,但是moV SP, r6则出现错误)。

变量名 SETA(SETL或SETS)表达式

伪指令SETA、SETL、SETS给一个已经定义 的全局变量或局部变量赋值。

SETA伪指令用于给一个数学变量赋值; SETL伪指令用于给一个逻辑变量赋值; SETS伪指令用于给一个字符串变量赋值;

其中,变量名为已经定义过的全局变量 或局部变量,表达式为将要赋给变量的值。

GBLS Test3

;定义一个全局的字符串变量,变量名为Test3

Test3 SETS "Testing"

;将该变量赋值为"Testing"

ARM 指令系统

2、 LCLA、LCLL和LCLS

语法格式:

LCLA(LCLL或LCLS) 局部变量名

LCLA、LCLL和LCLS伪指令用于定义一个ARM程

序中的局部变量,并将其初始化。其中:

伪指令仅在汇编过程中起作用,一 旦汇编结束,伪指令的使命就完成。

指令 : 由ARM处理器执行

ARM 指令系统

在ARM的汇编程序中,有如下几种伪指令:

符号定义伪指令、 数据定义伪指令、 汇编控制伪指令、 宏指令以及其他伪指令。

ARM 指令系统

4.1.1 符号定义伪指令

符号定义伪指令用于定义ARM汇 编程序中的变量、对变量赋值以及定 义寄存器的别名等操作。

LCLA伪指令用于定义一个局部的数字变量, 并初始化为0;

LCLL伪指令用于定义一个局部的逻辑变量, 并初始化为F(假);

LCLS伪指令用于定义一个局部的字符串变量, 并初始化为空;

以上三条伪指令用A Test4 ;声明一个局部的数字变量, 变量名为Test4

Test3 SETA 0xaa ; 将 该 变 量 赋 值 为

0xaa

LCLL Test5;声明一个局部的逻辑变量,变 量名为Test5

Test4 SETL

真

{TRUE};将该变量赋值为

LCLS Test6;定义一个局部的字符串变量, 变量名为Test6

Test6 SETS “Testing” ;将该变量 赋值为“Testing”

3、 SETA、SETL和SETS

ARM 指令系统

4.1.1 符号定义伪指令

常见的符号定义伪指令有如下几种:

— 用于定义全局变量的GBLA、GBLL和 GBLS。

— 用于定义局部变量的LCLA、LCLL和 LCLS。

— 用于对变量赋值的SETA、SETL、SETS。 — 为通用寄存器列表定义名称的RLIST。

1、 GBLA、GBLL和GBLS 语法格式:

ARM 指令系统 使用示例:

LCLA Test3

;声明一个局部的

数字变量,变量名为Test3

Test3 SETA 0xaa;将该变量赋值为

0xaa

LCLL Test4

;声明一个局部的

逻辑变量,变量名为Test4

Test4 SETL {TRUE} ; 将 该 变

量赋值为真

4、 RLIST

名称 RLIST {寄存器列表}

由于以上三条伪指令用于定义全局变量,因此在整个 程序范围内变量名必须唯一。

GBLA Test1

;定义一个全局的数字变量,变量名为Test1

Test1 SETA 0xaa

;将该变量赋值为0xaa

GBLL Test2

;定义一个全局的逻辑变量,变量名为Test2

Test2 SETL {TRUE}

;将该变量赋值为真

RLIST伪指令可用于对 一个通用寄存器列表定义名称,使 用该伪指令定义的名称可在ARM指 令LDM/STM中使用。

在LDM/STM指令中,列 表中的寄存器访问次序为根据寄存 器的编号由低到高,而与列表中的 寄存器排列次序无关。

RLIST使用示例:

RegList RLIST {R0-R5,R8,R10}

— DCFS(DCFSU) 用 于 为 单 精 度 的 浮 点 数分配一片连续的字存储单元并用指定的数据 初始化。

— DCQ(DCQU) 用于分配一片以8字节 为单位的连续的存储单元并用指定的数据初始 化。

DCD(DCDU)用于分配一片连续的字存储单 元并用指定的数据初始化。

SPACE 用于分配一片连续的存储单元

分配存储单元,同时可完成已分配存储单元

的初始化。常见的数据定义伪指令有如下几 种:

— DCB

用于分配一片连续的字节存储单元并用

指定的数据初始化。

—DCW(DCWU) 用于分配一片连续的半字存储 单元并用指定的数据初始化。

— DCFD(DCFDU)用于为双精度的浮点数分配一片 连续的字存储单元并用指定的数据初始化。

将寄存器列表名称定义为RegList, 可在ARM指令LDM/STM中通过该名称 访问寄存器列表。

例:

RegList RLIST {r1-r13};必须顶格开始写

LDMIA r0,RegList

ARM 指令系统

4.1.2 数据定义(Data Definition)伪指令 数据定义伪指令一般用于为特定的数据

3. 注释可以在一行的顶格书写。

ARM 指令系统

4.1伪操作

在ARM汇编语言程序里,有一些特殊 指令助记符,这些助记符与指令系统的

助记符不同,没有相对应的操作码,通 常称这些特殊指令助记符为伪指令

他们所完成的操作称为伪操作。

ARM 指令系统

伪指令 : 由汇编器处理

伪指令是由汇编器对源程序汇编期 间进行处理的.

MAP 用于定义一个结构化的内存表首地址

GBLA(GBLL或GBLS) 全局变量名

GBLA、GBLL和GBLS伪指令用于定义一个ARM程 序中的全局变量,并将其初始化。

GBLA伪指令用于定义一个全局的数字变量,并初始 化为0;

GBLL伪指令用于定义一个全局的逻辑变量,并初始 化为F(假);

GBLS伪指令用于定义一个全局的字符串变量,并初 始化为空;

第四章 ARM汇编语言程序设计

ADS1.2环境下的汇编语句格式

1. ARM 汇编中,所有标号必须在一行的顶格书写, 其后面不要添加“:”,而所有指令均不能顶格书写。

2. ARM 汇编器对标识符大小写敏感,书写标号及 指令时字母大小写要一致,在ARM 汇编程序中,一个 ARM 指令、伪指令、寄存器名可以全部为大写字母, 也可以全部为小写字母,但不要大小写混合使用(如 果混合使用也能编译通过,如mov SP, r6能编译 通过,但是moV SP, r6则出现错误)。