GS8640E32GT-250V中文资料

GT、GS、GE、LE显卡说明

GT、GS、GE、LE显卡说明一、相对老一些的解释:LE:NVIDA显卡型号采用的后缀。

全名为“Limited Edition”(限制版)代表系列中的低端产品,到现在为止,还有某些LE显卡因为精简过管线而被大家戏称为“阉割卡”或“太监卡”。

SE:ATI显卡型号采用的后缀。

全名为“Special Edition”(特殊版),同样代表系列中的低端产品。

通常SE后缀的显卡只有64bit内存界面,如9200SE ,9550SE,9600SE,9800SE(此型号有128 bit和256 bit),X300SE等。

又或者是像素流水线数量减少(如9800SE)。

ZT:NVIDA 新增加的型号,现在只有 GeForce FX 5900一款。

ZT 代表着比XT更低的市场定位,使系列中中低端的产品。

XT:最容易让人混淆的型号。

ATI与NVIDA显卡均在使用。

在ATI方面,代表系列中最高端的产品,如9600XT,9800XT,X800XT,X1300XT 等等。

而NVIDA则将之用作低端型号,如5900XT,6800XT等等。

GT/Pro:分别为NVIDA 和ATI公司用作中端显卡型号的后缀。

代表产品有7600GT,9600Pro,X800 Pro等,唯一例外的是新推出的GeForce 6600 GT显卡,它是系列中暂时最高端的显卡。

Ultra:NVIDA 显卡中最顶端的显卡,与ATI中的“XT”类似。

代表产品有6800 Ultra,5700Ultra。

二、系统一些的解释:nVidia的:Ultra旗舰级,在GF7系列之前代表着最高端,但7系列最高端的命名就改为GTX。

GTX是高端中的高端一般可以理解为GT eXtreme。

GT就是比GS更高一级的,是该系列中的高端,不过这在GeForce 8600系列显卡中表现得不是很明显,似乎已经成为主打产品,有点汽车中GT的味道。

GS不得而知,只知道GS是该系列中的主打产品,如之前的7600GS、7900GS。

GS881Z36BGD-150V中文资料

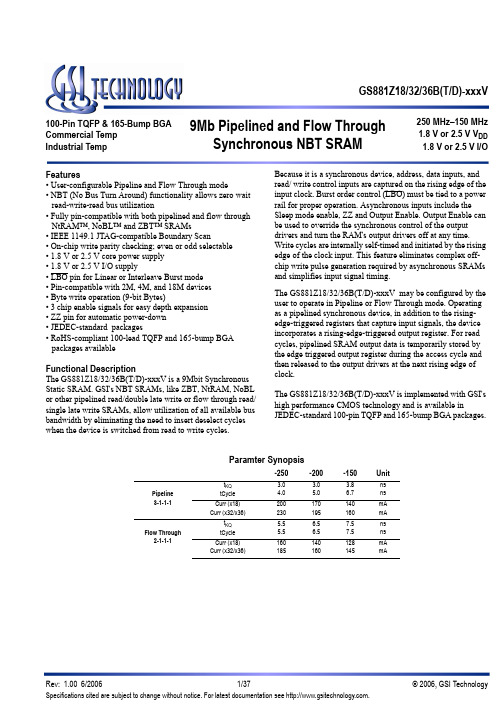

GS881Z18/32/36B(T/D)-xxxV9Mb Pipelined and Flow ThroughSynchronous NBT SRAM250 MHz–150 MHz 1.8 V or 2.5 V V DD 1.8 V or 2.5 V I/O100-Pin TQFP & 165-Bump BGA Commercial Temp Industrial Temp Features• User-configurable Pipeline and Flow Through mode• NBT (No Bus Turn Around) functionality allows zero wait read-write-read bus utilization• Fully pin-compatible with both pipelined and flow through NtRAM™, NoBL™ and ZBT™ SRAMs• IEEE 1149.1 JTAG-compatible Boundary Scan• On-chip write parity checking; even or odd selectable • 1.8 V or 2.5 V core power supply • 1.8 V or 2.5 V I/O supply• LBO pin for Linear or Interleave Burst mode • Pin-compatible with 2M, 4M, and 18M devices • Byte write operation (9-bit Bytes)• 3 chip enable signals for easy depth expansion • ZZ pin for automatic power-down • JEDEC-standard packages• RoHS-compliant 100-lead TQFP and 165-bump BGA packages availableFunctional DescriptionThe GS881Z18/32/36B(T/D)-xxxV is a 9Mbit Synchronous Static SRAM. GSI's NBT SRAMs, like ZBT, NtRAM, NoBL or other pipelined read/double late write or flow through read/single late write SRAMs, allow utilization of all available bus bandwidth by eliminating the need to insert deselect cycles when the device is switched from read to write cycles.Because it is a synchronous device, address, data inputs, and read/ write control inputs are captured on the rising edge of the input clock. Burst order control (LBO) must be tied to a power rail for proper operation. Asynchronous inputs include the Sleep mode enable, ZZ and Output Enable. Output Enable can be used to override the synchronous control of the output drivers and turn the RAM's output drivers off at any time. Write cycles are internally self-timed and initiated by the rising edge of the clock input. This feature eliminates complex off-chip write pulse generation required by asynchronous SRAMs and simplifies input signal timing.The GS881Z18/32/36B(T/D)-xxxV may be configured by the user to operate in Pipeline or Flow Through mode. Operating as a pipelined synchronous device, in addition to the rising-edge-triggered registers that capture input signals, the device incorporates a rising-edge-triggered output register. For read cycles, pipelined SRAM output data is temporarily stored by the edge triggered output register during the access cycle and then released to the output drivers at the next rising edge of clock.The GS881Z18/32/36B(T/D)-xxxV is implemented with GSI's high performance CMOS technology and is available inJEDEC-standard 100-pin TQFP and 165-bump BGA packages.Paramter Synopsis-250-200-150UnitPipeline 3-1-1-1KQ tCycle 4.0 5.0 6.7ns Curr (x18)Curr (x32/x36)200230170195140160mA mA Flow Through 2-1-1-1t KQ tCycle 5.55.5 6.56.57.57.5ns ns Curr (x18)Curr (x32/x36)160185140160128145mA mA807978777675747372717069686766656463626160595857565554535251123456789101112131415161718192021222324252627282930V DDQ V SS DQ B DQ B V SS V DDQ DQ B DQ B FT V DD NC V SS DQ B DQ B6V DD V SS DQ B DQ B DQP BV SS V DDQ V DDQ V SS DQ A DQ A V SS V DDQ DQ A DQ A V SS NC V DD ZZ DQ A DQ A V DDQ V SS DQ A DQ A V SS V DDQ L B O A A A A A 1A 0T M S T D I V S SV D DT D O T C K A A A A A A 1A A E 1E 2 N C N C B BB AE 3C K W C K E VD DV S SG A D V N C A A AA 512K x 18Top View DQP A A NC NC NC NC NC NC NC NCNC NC NC NC NC NC NCNC NC 100999897969594939291908988878685848382813132333435363738394041424344454647484950GS881Z18/32/36B(T/D)-xxxVGS881Z18BT-xxxV 100-Pin TQFP Pinout (Package T)807978777675747372717069686766656463626160595857565554535251123456789101112131415161718192021222324252627282930V DDQ V SS DQ C DQ C V SS V DDQ DQ C DQ C FT V DD NC V SS DQ D DQ D2V DDQ V SS DQ D DQ D DQ D V SS V DDQ V DDQ V SS DQ B DQ B V SS V DDQ DQ B DQ B V SS NC V DD ZZ DQ A DQ A V DDQ V SS DQ A DQ A V SS V DDQ L B O A A A A A 1A 0T M S T D I V S SV D DT D O T C K A A A A A AA A E 1E 2 B DB CB BB AE 3C K W C K E VD DV S SG A D V N C A A AA 256K x 32Top View DQB NC DQ B DQ B DQ B DQ A DQ A DQ A DQ A NCDQ C DQ C DQ C DQ D DQ D DQ D NCDQ C NC 100999897969594939291908988878685848382813132333435363738394041424344454647484950GS881Z18/32/36B(T/D)-xxxVGS881Z32BT-xxxV 100-Pin TQFP Pinout (Package T)807978777675747372717069686766656463626160595857565554535251123456789101112131415161718192021222324252627282930V DDQ V SS DQ C DQ C V SS V DDQ DQ C DQ C FT V DD NC V SS DQ D DQ D2V DDQ V SS DQ D DQ D DQ D V SS V DDQ V DDQ V SS DQ B DQ B V SS V DDQ DQ B DQ B V SS NC V DD ZZ DQ A DQ A V DDQ V SS DQ A DQ A V SS V DDQ L B O A A A A A 1A 0T M S T D I V S SV D DT D O T C K A A A A A AA A E 1E 2 B DB CB BB AE 3C K W C K E VD DV S SG A D V N C A A AA 256K x 36Top View DQB DQP B DQ B DQ B DQ B DQ A DQ A DQ A DQ A DQP ADQ C DQ C DQ C DQ D DQ D DQ D DQP DDQ C DQP C 100999897969594939291908988878685848382813132333435363738394041424344454647484950GS881Z18/32/36B(T/D)-xxxVGS881Z36BT-xxxV 100-Pin TQFP Pinout (Package T)100-Pin TQFP Pin DescriptionsSymbolTypeDescriptionA 0, A 1In Burst Address Inputs; Preload the burst counterA In Address Inputs CK In Clock Input SignalB A In Byte Write signal for data inputs DQ A1–DQ A9; active low B B In Byte Write signal for data inputs DQ B1–DQ B9; active low BC In Byte Write signal for data inputs DQ C1–DQ C9; active low BD In Byte Write signal for data inputs DQ D1–DQ D9; active lowW In Write Enable; active low E 1In Chip Enable; active lowE 2In Chip Enable—Active High. For self decoded depth expansion E 3In Chip Enable—Active Low. For self decoded depth expansionG In Output Enable; active lowADV In Advance/Load; Burst address counter control pinCKE In Clock Input Buffer Enable; active lowNC —No ConnectDQ A I/O Byte A Data Input and Output pins DQ B I/O Byte B Data Input and Output pins DQ C I/O Byte C Data Input and Output pins DQ D I/O Byte D Data Input and Output pins ZZ In Power down control; active high FT In Pipeline/Flow Through Mode Control; active lowLBO InLinear Burst Order; active low.TMS Scan Test Mode Select TDI Scan Test Data In TDO Scan Test Data Out TCK Scan Test Clock V DD In Core power supplyV SS In GroundV DDQInOutput driver power supplyGS881Z18/32/36B(T/D)-xxxVGS881Z18/32/36B(T/D)-xxxV165 Bump BGA—x18 Commom I/O—Top View 1234567891011A NC A E1BB NC E3CKE ADV A17A A A B NC A E2NC BA CK W G NC A NC B C NC NC V DDQ V SS V SS V SS V SS V SS V DDQ NC DQA C D NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA D E NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA E F NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA F G NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA G H FT MCH NC V DD V SS V SS V SS V DD NC NC ZZ H J DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC J K DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC K L DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC L M DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC M N DQB NC V DDQ V SS NC NC NC V SS V DDQ NC NC N P NC NC A A TDI A1TDO A A A NC P RLBONCAATMSA0TCKAAAAR11 x 15 Bump BGA—13 mm x 15 mm Body—1.0 mm Bump Pitch(Package D)GS881Z18/32/36B(T/D)-xxxV165 Bump BGA—x32 Common I/O—Top View 1234567891011A NC A E1BC BB E3CKE ADV A17A NC A B NC A E2BD BA CK W G NC A NC B C NC NC V DDQ V SS V SS V SS V SS V SS V DDQ NC NC C D DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB D E DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB E F DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB F G DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB G H FT MCH NC V DD V SS V SS V SS V DD NC NC ZZ H J DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA J K DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA K L DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA L M DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA M N NC NC V DDQ V SS NC NC NC V SS V DDQ NC NC N P NC NC A A TDI A1TDO A A A NC P RLBONCAATMSA0TCKAAAAR11 x 15 Bump BGA—13 mm x 15 mm Body—1.0 mm Bump Pitch(Package D)GS881Z18/32/36B(T/D)-xxxV165 Bump BGA—x36 Common I/O—Top View 1234567891011A NC A E1BC BB E3CKE ADV A A NC A B NC A E2BD BA CK W G NC A NC B C DQPC NC V DDQ V SS V SS V SS V SS V SS V DDQ NC DQPB C D DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB D E DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB E F DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB F G DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB G H FT MCH NC V DD V SS V SS V SS V DD NC NC ZZ H J DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA J K DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA K L DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA L M DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA M N DQPD NC V DDQ V SS NC NC NC V SS V DDQ NC DQPA N P NC NC A A TDI A1TDO A A A NC P RLBONCAATMSA0TCKAAAAR11 x 15 Bump BGA—13 mm x 15 mm Body—1.0 mm Bump Pitch(Package D)GS881Z18/32/36D-xxxV165-Bump BGA Pin DescriptionSymbolTypeDescriptionA 0, A 1I Address field LSBs and Address Counter Preset InputsA I Address Inputs DQ A DQB DQC DQD I/O Data Input and Output pinsB A , B B , BC , B DI Byte Write Enable for DQ A , DQ B , DQ C , DQ D I/Os; active lowNC —No ConnectCK I Clock Input Signal; active high CKE I Clock Enable; active low W I Write Enable; active low E 1I Chip Enable; active low E 3I Chip Enable; active low E 2I Chip Enable; active high G I Output Enable; active lowADV I Burst address counter advance enable; active highZZ I Sleep mode control; active high FT I Flow Through or Pipeline mode; active low LBO I Linear Burst Order mode; active lowTMS I Scan Test Mode Select TDI I Scan Test Data In TDO O Scan Test Data Out TCK I Scan Test Clock MCH —Must Connect High DNU —Do Not Use V DD I Core power supply V SS I I/O and Core Ground V DDQIOutput driver power supplyGS881Z18/32/36B(T/D)-xxxVK18S A 1S A 0Bu r s t C o u n t e rL B OA D VM e m o r y A r r a yGC KC K ED QF TN CN CD Q a –D Q nKS A 1’S A 0’D QM a t c hW r i t e A d d r e s sR e g i s t e r 2W r i t e A d d r e s sR e g i s t e r 1W r i t e D a t aR e g i s t e r 2W r i t e D a t aR e g i s t e r 1KKKKKKS e n s e A m p sW r i t e D r i v e r sR e a d , W r i t e a n dD a t a C o h e r e n c yC o n t r o l L o g i cD QKP a r i t y C h e c kF TA 0–A nE 3E 2E 1WB DB CB BB AGS881Z18/32/36B(T/D)-xxxVGS881Z18/32/36B(T/D)-xxxV NBT SRAM Functional Block DiagramGS881Z18/32/36B(T/D)-xxxVFunctional DetailsClockingDeassertion of the Clock Enable (CKE) input blocks the Clock input from reaching the RAM's internal circuits. It may be used to suspend RAM operations. Failure to observe Clock Enable set-up or hold requirements will result in erratic operation.Pipeline Mode Read and Write OperationsAll inputs (with the exception of Output Enable, Linear Burst Order and Sleep) are synchronized to rising clock edges. Single cycle read and write operations must be initiated with the Advance/Load pin (ADV) held low, in order to load the new address. Device activation is accomplished by asserting all three of the Chip Enable inputs (E 1, E 2 and E 3). Deassertion of any one of the Enable inputs will deactivate the device. Function W B A B B B C B D Read H X X X X Write Byte “a”L L H H H Write Byte “b”L H L H H Write Byte “c”L H H L H Write Byte “d”L H H H L Write all Bytes L L L L L Write Abort/NOPLHHHHRead operation is initiated when the following conditions are satisfied at the rising edge of clock: CKE is asserted low, all three chip enables (E 1, E 2, and E 3) are active, the write enable input signals W is deasserted high, and ADV is asserted low. The address presented to the address inputs is latched in to address register and presented to the memory core and control logic. The control logic determines that a read access is in progress and allows the requested data to propagate to the input of the output register. At the next rising edge of clock the read data is allowed to propagate through the output register and onto the output pins.Write operation occurs when the RAM is selected, CKE is active and the write input is sampled low at the rising edge of clock. The Byte Write Enable inputs (B A , B B , B C & B D ) determine which bytes will be written. All or none may be activated. A write cycle with no Byte Write inputs active is a no-op cycle. The pipelined NBT SRAM provides double late write functionality, matching the write command versus data pipeline length (2 cycles) to the read command versus data pipeline length (2 cycles). At the first rising edge of clock, Enable, Write, Byte Write(s), and Address are registered. The Data In associated with that address is required at the third rising edge of clock.Flow Through Mode Read and Write OperationsOperation of the RAM in Flow Through mode is very similar to operations in Pipeline mode. Activation of a read cycle and the use of the Burst Address Counter is identical. In Flow Through mode the device may begin driving out new data immediately after new address are clocked into the RAM, rather than holding new data until the following (second) clock edge. Therefore, in Flow Through mode the read pipeline is one cycle shorter than in Pipeline mode.Write operations are initiated in the same way, but differ in that the write pipeline is one cycle shorter as well, preserving the ability to turn the bus from reads to writes without inserting any dead cycles. While the pipelined NBT RAMs implement a double late write protocol, in Flow Through mode a single late write protocol mode is observed. Therefore, in Flow Through mode, address and control are registered on the first rising edge of clock and data in is required at the data input pins at the second rising edge of clock.Synchronous Truth TableOperationType Address CK CKE ADV W Bx E 1E 2E 3G ZZDQNotesRead Cycle, Begin Burst R External L-H L L H X L H L L L Q Read Cycle, Continue Burst B Next L-H L H X X X X X L L Q 1,10NOP/Read, Begin Burst R External L-H L L H X L H L H L High-Z 2Dummy Read, Continue Burst B Next L-H L H X X X X X H L High-Z 1,2,10Write Cycle, Begin Burst W External L-H L L L L L H L X L D 3Write Cycle, Continue Burst B Next L-H L H X L X X X X L D1,3,10Write Abort, Continue Burst B Next L-H L H X H X X X X L High-Z 1,2,3,10Deselect Cycle, Power Down D None L-H L L X X H X X X L High-Z Deselect Cycle, Power Down D None L-H L L X X X X H X L High-Z Deselect Cycle, Power Down D None L-H L L X X X L X X L High-Z Deselect Cycle D None L-H L L L H L H L X L High-Z 1Deselect Cycle, Continue DNone L-H L H X X X X X X L High-Z 1Sleep ModeNone X X X X X X X X X H High-Z Clock Edge Ignore, StallCurrentL-HHXXXXXXXL-4Notes:1.Continue Burst cycles, whether read or write, use the same control inputs. A Deselect continue cycle can only be entered into if a Dese-lect cycle is executed first.2.Dummy Read and Write abort can be considered NOPs because the SRAM performs no operation. A Write abort occurs when the Wpin is sampled low but no Byte Write pins are active so no write operation is performed.3.G can be wired low to minimize the number of control signals provided to the SRAM. Output drivers will automatically turn off duringwrite cycles.4.If CKE High occurs during a pipelined read cycle, the DQ bus will remain active (Low Z). If CKE High occurs during a write cycle, the buswill remain in High Z.5. X = Don’t Care; H = Logic High; L = Logic Low; Bx = High = All Byte Write signals are high; Bx = Low = One or more Byte/Writesignals are Low6.All inputs, except G and ZZ must meet setup and hold times of rising clock edge.7.Wait states can be inserted by setting CKE high.8.This device contains circuitry that ensures all outputs are in High Z during power-up.9. A 2-bit burst counter is incorporated.10.The address counter is incriminated for all Burst continue cycles.GS881Z18/32/36B(T/D)-xxxVGS881Z18/32/36B(T/D)-xxxVDeselectNew ReadNew WriteBurst ReadBurst WriteWRBRBWDDBBWRD BWRDDCurrent State (n)Next State (n+1)TransitionƒInput Command CodeKeyNotes:1. The Hold command (CKE Low) is notshown because it prevents any state change.2. W, R, B, and D represent input commandcodes as indicated in the Synchronous Truth Table.Clock (CK)CommandCurrent StateNext Stateƒnn+1n+2n+3ƒƒƒCurrent State and Next State Definition for Pipelined and Flow Through Read/Write Control State DiagramWRPipelined and Flow Through Read Write Control State DiagramGS881Z18/32/36B(T/D)-xxxVIntermediateIntermediateIntermediateIntermediateIntermediateIntermediateHigh Z (Data In)Data Out (Q Valid)High Z B W B R B DRW RWDDCurrent State (n)TransitionƒInput Command CodeKeyTransitionIntermediate State (N+1)Notes:1. The Hold command (CKE Low) is notshown because it prevents any state change.2. W, R, B, and D represent input command codes as indicated in the Truth Tables.Clock (CK)CommandCurrent StateIntermediate ƒn n+1n+2n+3ƒƒƒCurrent State and Next State Definition for Pipeline Mode Data I/O State DiagramNext StateStatePipeline Mode Data I/O State DiagramGS881Z18/32/36B(T/D)-xxxVFlow Through Mode Data I/O State Diagram High Z (Data In)Data Out (Q Valid)High Z B W B R B DRW RWDDCurrent State (n)Next State (n+1)TransitionƒInput Command CodeKeyNotes:1. The Hold command (CKE Low) is notshown because it prevents any state change.2. W, R, B, and D represent input command codes as indicated in the Truth Tables.Clock (CK)CommandCurrent StateNext Stateƒnn+1n+2n+3ƒƒƒCurrent State and Next State Definition for: Pipeline and Flow through Read Write Control State DiagramGS881Z18/32/36B(T/D)-xxxVBurst CyclesAlthough NBT RAMs are designed to sustain 100% bus bandwidth by eliminating turnaround cycle when there is transition from read to write, multiple back-to-back reads or writes may also be performed. NBT SRAMs provide an on-chip burst address generator that can be utilized, if desired, to further simplify burst read or write implementations. The ADV control pin, when driven high, commands the SRAM to advance the internal address counter and use the counter generated address to read or write the SRAM. The starting address for the first cycle in a burst cycle series is loaded into the SRAM by driving the ADV pin low, into Load mode.Burst OrderThe burst address counter wraps around to its initial state after four addresses (the loaded address and three more) have beenaccessed. The burst sequence is determined by the state of the Linear Burst Order pin (LBO). When this pin is low, a linear burst sequence is selected. When the RAM is installed with the LBO pin tied high, Interleaved burst sequence is selected. See the tables below for details.Mode Pin FunctionsMode NamePin NameStateFunctionBurst Order Control LBO L Linear Burst H Interleaved Burst Output Register Control FT L Flow Through H or NC Pipeline Power Down ControlZZL or NC Active HStandby, I DD = I SBNote:There is a pull-up device on the FT pin and a pull-down device on the ZZ pin, so this input pin can be unconnected and the chip will operate in the default states as specified in the above table.Note:The burst counter wraps to initial state on the 5th clock.Note:The burst counter wraps to initial state on the 5th clock.Linear Burst SequenceA[1:0]A[1:0]A[1:0]A[1:0]1st address 000110112nd address 011011003rd address 101100014th address11000110Interleaved Burst SequenceA[1:0]A[1:0]A[1:0]A[1:0]1st address 000110112nd address 010011103rd address 101100014th address11100100Burst Counter SequencesBPR 1999.05.18GS881Z18/32/36B(T/D)-xxxVSleep ModeDuring normal operation, ZZ must be pulled low, either by the user or by it’s internal pull down resistor. When ZZ is pulled high, the SRAM will enter a Power Sleep mode after 2 cycles. At this time, internal state of the SRAM is preserved. When ZZ returns to low, the SRAM operates normally after ZZ recovery time.Sleep mode is a low current, power-down mode in which the device is deselected and current is reduced to I SB 2. The duration of Sleep mode is dictated by the length of time the ZZ is in a high state. After entering Sleep mode, all inputs except ZZ become disabled and all outputs go to High-Z The ZZ pin is an asynchronous, active high input that causes the device to enter Sleep mode. When the ZZ pin is driven high, I SB 2 is guaranteed after the time tZZI is met. Because ZZ is an asynchronous input, pending operations or operations in progress may not be properly completed if ZZ is asserted. Therefore, Sleep mode must not be initiated until valid pending operations are completed. Similarly, when exiting Sleep mode during tZZR, only a Deselect or Read commands may be applied while the SRAM is recovering from Sleep mode.Sleep Mode Timing DiagramtZZRtZZHtZZStKLtKHtKCCKZZDesigning for CompatibilityThe GSI NBT SRAMs offer users a configurable selection between Flow Through mode and Pipelinemode via the FT signal found on Pin 14. Not all vendors offer this option, however most mark Pin 14 as V DD or V DDQ on pipelined parts and V SS on flow through parts. GSI NBT SRAMs are fully compatible with these sockets.Pin 66, a No Connect (NC) on GSI’s GS8160Z18/36 NBT SRAM, the Parity Error open drain output on GSI’s GS881Z18/36B NBT SRAM, is often marked as a power pin on other vendor’s NBT compatible SRAMs. Specifically, it is marked V DD or V DDQ on pipelined parts and V SS on flow through parts. Users of GSI NBT devices who are not actually using the ByteSafe™ parity feature may want to design the board site for the RAM with Pin 66 tied high through a 1k ohm resistor in Pipeline modeapplications or tied low in Flow Through mode applications in order to keep the option to use non-configurable devices open.Absolute Maximum Ratings(All voltages reference to V SS )SymbolDescriptionValueUnitV DD Voltage on V DD Pins –0.5 to 4.6V V DDQ Voltage on V DDQ Pins –0.5 to V DDV V I/O Voltage on I/O Pins –0.5 to V DDQ +0.5 (≤ 4.6 V max.)V V IN Voltage on Other Input Pins –0.5 to V DD +0.5 (≤ 4.6 V max.)V I IN Input Current on Any Pin +/–20mA I OUT Output Current on Any I/O Pin +/–20mA P D Package Power Dissipation 1.5WT STG Storage Temperature –55 to 125o C T BIASTemperature Under Bias–55 to 125oCGS881Z18/32/36B(T/D)-xxxVNote:Permanent damage to the device may occur if the Absolute Maximum Ratings are exceeded. Operation should be restricted to Recommended Operating Conditions. Exposure to conditions exceeding the Absolute Maximum Ratings, for an extended period of time, may affect reliability of this component. Power Supply Voltage Ranges (1.8 V/2.5 V Version)ParameterSymbolMin.Typ.Max.UnitNotes1.8 V Supply Voltage V DD1 1.7 1.82.0V 2.5 V Supply Voltage V DD2 2.3 2.5 2.7V 1.8 V V DDQ I/O Supply Voltage V DDQ1 1.7 1.8V DD V 2.5 V V DDQ I/O Supply VoltageV DDQ22.32.5V DDVNotes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn +2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.GS881Z18/32/36B(T/D)-xxxVV DDQ2 & V DDQ1 Range Logic LevelsParameterSymbolMin.Typ.Max.UnitNotesV DD Input High Voltage V IH 0.6*V DD —V DD + 0.3V 1V DD Input Low VoltageV IL–0.3—0.3*V DDV1Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn +2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.Recommended Operating TemperaturesParameterSymbolMin.Typ.Max.UnitNotesAmbient Temperature (Commercial Range Versions)T A 02570°C 2Ambient Temperature (Industrial Range Versions)T A–402585°C2Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn +2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.20% tKCV SS – 2.0 V50%V SS V IHUndershoot Measurement and TimingOvershoot Measurement and Timing20% tKCV DD + 2.0 V50%V DDV ILCapacitanceo C, f = 1 MH Z , V DD ParameterSymbolTest conditionsTyp.Max.UnitInput Capacitance C IN V IN = 0 V 45pF Input/Output Capacitance C I/OV OUT = 0 V67pFNote:These parameters are sample tested.(T A = 25= 2.5 V)AC Test ConditionsParameterConditionsDQV DDQ/250Ω30pF *Output Load 1* Distributed Test Jig CapacitanceFigure 1Input high level V DD – 0.2 V Input low level 0.2 V Input slew rate 1 V/ns Input reference level V DD /2Output reference levelV DDQ /2Output loadFig. 11.Include scope and jig capacitance.2.Test conditions as specified with output loading as shown in Fig. 1unless otherwise noted.3.Device is deselected as defined by the Truth Table. GS881Z18/32/36B(T/D)-xxxVDC Electrical CharacteristicsParameterSymbolTest ConditionsMinMaxInput Leakage Current (except mode pins)I IL V IN = 0 to V DD –1 uA 1 uA FT, ZZ Input Current I IN V DD ≥ V IN ≥ 0 V –100 uA 100 uA Output Leakage CurrentI OLOutput Disable, V OUT = 0 to V DD–1 uA1 uADC Output Characteristics (1.8 V/2.5 V Version)ParameterSymbolTest ConditionsMinMax1.8 V Output High Voltage V OH1I OH = –4 mA, V DDQ = 1.6 V V DDQ – 0.4 V —2.5 V Output High Voltage V OH2I OH = –8 mA, V DDQ = 2.375 V1.7 V —1.8 V Output Low Voltage V OL1I OL = 4 mA —0.4 V2.5 V Output Low VoltageV OL2I OL = 8 mA—0.4 VGS881Z18/32/36B(T/D)-xxxVOperating CurrentsParameterTest ConditionsModeSymbol-250-200-150Unit0to 70°C–40 to 85°C0to 70°C –40to 85°C 0 to 70°C –40to 85°COperating CurrentDevice Selected; All other inputs ≥V IH o r ≤ V IL Output open(x32/x36)PipelineI DD I DDQ 200302203017025190251402016020mA Flow Through I DD I DDQ 160251802514020160201301515015mA (x18)PipelineI DD I DDQ 185152051515515175151301015010mA Flow ThroughI DD I DDQ 1451516515130101501012081408mA Standby Current ZZ ≥ V DD – 0.2 V —Pipeline I SB 405040504050mA Flow Through I SB 405040504050mA Deselect CurrentDevice Deselected; All other inputs ≥ V IH or ≤ V IL—PipelineI DD 859075806065mA Flow Through I DD606550555055mA1.I DD and I DDQ apply to any combination of V DD1, V DD2, V DDQ1, and V DDQ2 operation.2.All parameters listed are worst case scenario.。

GS8662S08E-250I资料

PreliminaryGS8662S08/09/18/36E-333/300/250/200/16772Mb Burst of 2DDR SigmaSIO-II SRAM333 MHz–167 MHz1.8 V V DD1.8 V and 1.5 V I/O165-Bump BGA Commercial Temp Industrial Temp Features• Simultaneous Read and Write SigmaSIO™ Interface • JEDEC-standard pinout and package • Dual Double Data Rate interface• Byte Write controls sampled at data-in time• DLL circuitry for wide output data valid window and future frequency scaling• Burst of 2 Read and Write• 1.8 V +100/–100 mV core power supply • 1.5 V or 1.8 V HSTL Interface • Pipelined read operation• Fully coherent read and write pipelines• ZQ mode pin for programmable output drive strength • IEEE 1149.1 JTAG-compliant Boundary Scan • Pin-compatible with future 144Mb devices• 165-bump, 15 mm x 17 mm, 1 mm bump pitch BGA package • RoHS-compliant 165-bump BGA package availableSigmaRAM ™ Family OverviewGS8662S08/09/18/36 are built in compliance with the SigmaSIO-II SRAM pinout standard for Separate I/O synchronous SRAMs. They are 75,497,472-bit (72Mb) SRAMs. These are the first in a family of wide, very low voltage HSTL I/O SRAMs designed to operate at the speeds needed to implement economical high performance networking systems.165-Bump, 15 mm x 17 mm BGA 1 mm Bump Pitch, 11 x 15 Bump Array Bottom ViewJEDEC Std. MO-216, Variation CAB-1Clocking and Addressing SchemesA Burst of 2 SigmaSIO-II SRAM is a synchronous device. It employs dual input register clock inputs, K and K. The device also allows the user to manipulate the output register clock input quasi independently with dual output register clock inputs, C and C. If the C clocks are tied high, the K clocks are routed internally to fire the output registers instead. Each Burst of 2 SigmaSIO-II SRAM also supplies Echo Clock outputs, CQ and CQ, which are synchronized with read data output. When used in a source synchronous clocking scheme, the Echo Clock outputs can be used to fire input registers at the data’s destination.Because Separate I/O Burst of 2 RAMs always transfer data in two packets, A0 is internally set to 0 for the first read or write transfer, and automatically incremented by 1 for the next transfer. Because the LSB is tied off internally, the address field of a Burst of 2 RAM is always one address pin less than the advertised index depth (e.g., the 4M x 18 has a 1M addressable index).Parameter Synopsis- 333-300-250-200-167tKHKH 3.0 ns 3.3 ns 4.0 ns 5.0 ns 6.0 ns tKHQV0.45 ns0.45 ns0.45 ns0.45 ns0.5 ns8M x 8 SigmaQuad SRAM—Top View1234567891011ACQ SA SA R/W NW1K NC LD SA SA CQ B NC NC NC SA NC K NW0SA NC NC Q3C NC NC NC V SS SA SA SA V SS NC NC D3D NC D4NC V SS V SS V SS V SS V SS NC NC NC E NC NC Q4 V DDQ V SS V SS V SS V DDQ NC D2Q2F NC NC NC V DDQ V DD V SS V DD V DDQ NC NC NC G NC D5Q5 V DDQ V DD V SS V DD V DDQ NC NC NC H D OFF V REF V DDQ V DDQ V DD V SS V DD V DDQ V DDQ V REF ZQ J NC NC NC V DDQ V DD V SS V DD V DDQ NC Q1D1K NC NC NC V DDQ V DD V SS V DD V DDQ NC NC NC L NC Q6D6 V DDQ V SS V SS V SS V DDQ NC NC Q0M NC NC NC V SS V SS V SS V SS V SS NC NC D0N NC D7NC V SS SA SA SA V SS NC NC NC P NC NC Q7SA SA C SA SA NC NC NC RTDOTCKSASASACSASASATMSTDI11 x 15 Bump BGA—15 x 17 mm 2 Body—1 mm Bump PitchNotes:1.NW0 controls writes to D0:D3. NW1 controls writes to D4:D7.2.It is recommended that H1 be tied low for compatibility with future devices.GS8662S08/09/18/36E-333/300/250/200/1678M x 9 SigmaQuad SRAM—Top View1234567891011ACQ SA SA R/W NC K NC LD SA SA CQ B NC NC NC SA NC K BW SA NC NC Q4C NC NC NC V SS SA SA SA V SS NC NC D4D NC D5NC V SS V SS V SS V SS V SS NC NC NC E NC NC Q5 V DDQ V SS V SS V SS V DDQ NC D3Q3F NC NC NC V DDQ V DD V SS V DD V DDQ NC NC NC G NC D6Q6 V DDQ V DD V SS V DD V DDQ NC NC NC H Doff V REF V DDQ V DDQ V DD V SS V DD V DDQ V DDQ V REF ZQ J NC NC NC V DDQ V DD V SS V DD V DDQ NC Q2D2K NC NC NC V DDQ V DD V SS V DD V DDQ NC NC NC L NC Q7D7 V DDQ V SS V SS V SS V DDQ NC NC Q1M NC NC NC V SS V SS V SS V SS V SS NC NC D1N NC D8NC V SS SA SA SA V SS NC NC NC P NC NC Q8SA SA C SA SA NC D0NC RTDOTCKSASASACSASASATMSTDI11 x 15 Bump BGA—15 x 17 mm 2 Body—1 mm Bump PitchNotes:1.BW controls writes to D0:D71.It is recommended that H1 be tied low for compatibility with future devices.GS8662S08/09/18/36E-333/300/250/200/1674M x 18 SigmaQuad SRAM—Top View1234567891011ACQ V SS /SA (144Mb)SA R/W BW1K NC LD SA SA CQ B NC Q9D9SA NC K BW0SA NC NC Q8C NC NC D10V SS SA SA SA V SS NC Q7D8D NC D11Q10V SS V SS V SS V SS V SS NC NC D7E NC NC Q11 V DDQ V SS V SS V SS V DDQ NC D6Q6F NC Q12D12 V DDQ V DD V SS V DD V DDQ NC NC Q5G NC D13Q13 V DDQ V DD V SS V DD V DDQ NC NC D5H D OFF V REF V DDQ V DDQ V DD V SS V DD V DDQ V DDQ V REF ZQ J NC NC D14 V DDQ V DD V SS V DD V DDQ NC Q4D4K NC NC Q14V DDQ V DD V SS V DD V DDQ NC D3Q3L NC Q15D15 V DDQ V SS V SS V SS V DDQ NC NC Q2M NC NC D16 V SS V SS V SS V SS V SS NC Q1D2N NC D17Q16 V SS SA SA SA V SS NC NC D1P NC NC Q17SA SA C SA SA NC D0Q0RTDOTCKSASASACSASASATMSTDI11 x 15 Bump BGA—15 x 17 mm 2 Body—1 mm Bump PitchNotes:1.BW0 controls writes to D0:D8. BW1 controls writes to D9:D17.2.It is recommended that H1 be tied low for compatibility with future devices.GS8662S08/09/18/36E-333/300/250/200/1672M x 36 SigmaQuad SRAM—Top View1234567891011ACQ V SS /SA (288Mb)SA R/W BW2K BW1LD SA V SS /SA (144Mb)CQ B Q27Q18D18SA BW3K BW0SA D17Q17Q8C D27Q28D19V SS SA SA SA V SS D16Q7D8D D28D20Q19V SS V SS V SS V SS V SS Q16D15D7E Q29D29Q20 V DDQ V SS V SS V SS V DDQ Q15D6Q6F Q30Q21D21 V DDQ V DD V SS V DD V DDQ D14Q14Q5G D30D22Q22 V DDQ V DD V SS V DD V DDQ Q13D13D5H D OFF V REF V DDQ V DDQ V DD V SS V DD V DDQ V DDQ V REF ZQ J D31Q31D23 V DDQ V DD V SS V DD V DDQ D12Q4D4K Q32D32Q23V DDQ V DD V SS V DD V DDQ Q12D3Q3L Q33Q24D24 V DDQ V SS V SS V SS V DDQ D11Q11Q2M D33Q34D25 V SS V SS V SS V SS V SS D10Q1D2N D34D26Q25 V SS SA SA SA V SS Q10D9D1P Q35D35Q26SA SA C SA SA Q9D0Q0RTDOTCKSASASACSASASATMSTDI11 x 15 Bump BGA—15 x 17 mm 2 Body—1 mm Bump PitchNotes:1.BW0 controls writes to D0:D8. BW1 controls writes to D9:D17.2.BW2 controls writes to D18:D26. BW3 controls writes to D27:D35.3.It is recommended that H1 be tied low for compatibility with future devices.GS8662S08/09/18/36E-333/300/250/200/167Pin Description TableSymbolDescriptionTypeCommentsSA Synchronous Address InputsInput —NC No Connect ——R/W Read/Write Contol Pin Input Write Active Low; Read Active HighNW0–NW1Synchronous Nybble Writes Input Active Low x08 Version BW0–BW1Synchronous Byte Writes Input Active Low x18 Version BW0–BW3Synchronous Byte WritesInput Active Low x36 Version K Input Clock Input Active High C Output Clock Input Active HighTMS Test Mode Select Input —TDI Test Data Input Input —TCK Test Clock Input Input —TDO Test Data Output Output —V REF HSTL Input Reference Voltage Input —ZQ Output Impedance Matching InputInput —K Input Clock Input Active Low C Output Clock Output Active Low D OFF DLL Disable —Active Low LD Synchronous Load Pin —Active Low CQ Output Echo Clock Output Active Low CQ Output Echo Clock Output Active HighDn Synchronous Data Inputs Input Qn Synchronous Data OutputsOutput V DD Power Supply Supply 1.8 V Nominal V DDQ Isolated Output Buffer Supply Supply 1.8 or 1.5 V NominalV SSPower Supply: GroundSupply—1.C, C, K, or K cannot be set to V REF voltage.2.When ZQ pin is directly connected to V DD , output impedance is set to minimum value and it cannot be connected to ground or leftunconnected.3.NC = Not Connected to die or any other pinGS8662S08/09/18/36E-333/300/250/200/167GS8662S08/09/18/36E-333/300/250/200/167BackgroundSeparate I/O SRAMs, like SigmaQuad SRAMs, are attractive in applications where alternating reads and writes are needed. On the other hand, Common I/O SRAMs like the SigmaCIO family are popular in applications where bursts of read or write traffic are needed. The SigmaSIO SRAM is a hybrid of these two devices. Like the SigmaQuad family devices, the SigmaSIO features a separate I/O data path, offering the user independent Data In and Data Out pins. However, the SigmaSIO devices offer a control protocol like that offered on the SigmaCIO devices. Therefore, while SigmaQuad SRAMs allow a user to operate both data ports at the same time, they force alternating loads of read and write addresses. SigmaSIO SRAMs allow continuous loads of read or write addresses like SigmaCIO SRAMs, but in a separate I/O configuration.Like a SigmaQuad SRAM, a SigmaSIO-II SRAM can execute an alternating sequence of reads and writes. However, doing so results in the Data In port and the Data Out port stalling with nothing to do on alternate transfers. A SigmaQuad device would keep both ports running at capacity full time. On the other hand, the SigmaSIO device can accept a continuous stream of read commands and read data or a continuous stream of write commands and write data. The SigmaQuad device, by contrast, restricts the user from loading a continuous stream of read or write addresses. The advantage of the SigmaSIO device is that it allows twice the random address bandwidth for either reads or writes than could be acheived with a SigmaQuad version of the device. SigmaCIO SRAMs offer this same advantage, but do not have the separate Data In and Data Out pins offered on the SigmaSIO SRAMs. Therefore, SigmaSIO devices are useful in psuedo dual port SRAM applications where communication of burst traffic between two electrically independent busses is desired.Each of the three SigmaQuad Family SRAMs—SigmaQuad, SigmaCIO, and SigmaSIO—supports similar address rates because random address rate is determined by the internal performance of the RAM. In addition, all three SigmaQuad Family SRAMs are based on the same internal circuits. Differences between the truth tables of the different devices proceed from differences in how the RAM’s interface is contrived to interact with the rest of the system. Each mode of operation has its own advantages and disadvantages. The user should consider the nature of the work to be done by the RAM to evaluate which version is best suited to the application at hand.Burst of 2 Sigma SIO-II SRAM DDR ReadThe status of the Address Input, R/W, and LD pins are sampled at each rising edge of K. LD high causes chip disable. A high on the R/W pin begins a read cycle. The two resulting data output transfers begin after the next rising edge of the K clock. Data is clocked out by the next rising edge of the C if it is active. Otherwise, data is clocked out at the next rising edge of K. The next data chunk is clocked out on the rising edge of C, if active. Otherwise, data is clocked out on the rising edge of K.Burst of 2 Sigma SIO-II SRAM DDR WriteThe status of the Address Input, R/W, and LD pins are sampled at each rising edge of K. LD high causes chip disable. A low on the R/W pin, begins a write cycle. Data is clocked in by the next rising edge of K and then the rising edge of K.GS8662S08/09/18/36E-333/300/250/200/167Power-Up Sequence for SigmaQuad-II SRAMsSigmaQuad-II SRAMs must be powered-up in a specific sequence in order to avoid undefined operations.Power-Up Sequence1. Power-up and maintain Doff at low state.1a.Apply V DD .1b. Apply V DDQ .1c. Apply V REF (may also be applied at the same time as V DDQ ).2. After power is achieved and clocks (K, K, C, C) are stablized, change Doff to high.3. An additional 1024 clock cycles are required to lock the DLL after it has been enabled.Note:If you want to tie Doff high with an unstable clock, you must stop the clock for a minimum of 30 seconds to reset the DLL after the clocks become stablized.DLL Constraints•The DLL synchronizes to either K or C clock. These clocks should have low phase jitter (t KCVar on page 21).•The DLL cannot operate at a frequency lower than 119 MHz.•If the incoming clock is not stablized when DLL is enabled, the DLL may lock on the wrong frequency and cause undefined errors or failures during the initial stage.Power-Up Sequence (Doff controlled)Power UP IntervalUnstable Clocking IntervalDLL Locking Interval (1024 Cycles)Normal OperationKKV DDV DDQV REFDoffPower-Up Sequence (Doff tied High)Power UP IntervalUnstable Clocking IntervalStop Clock IntervalDLL Locking Interval (1024 Cycles)Normal OperationKKV DDV DDQV REFDoff30ns MinNote:If the frequency is changed, DLL reset is required. After reset, a minimum of 1024 cycles is required for DLL lock.GS8662S08/09/18/36E-333/300/250/200/167Special FunctionsByte Write and Nybble Write ControlByte Write Enable pins are sampled at the same time that Data In is sampled. A high on the Byte Write Enable pin associated with a particular byte (e.g., BW0 controls D0–D8 inputs) will inhibit the storage of that particular byte, leaving whatever data may be stored at the current address at that byte location undisturbed. Any or all of the Byte Write Enable pins may be driven high or low during the data in sample times in a write sequence.Each write enable command and write address loaded into the RAM provides the base address for a 2 beat data transfer. The x18 version of the RAM, for example, may write 36 bits in association with each address loaded. Any 9-bit byte may be masked in any write sequence.Nybble Write (4-bit) control is implemented on the 8-bit-wide version of the device. For the x8 version of the device, “Nybble Write Enable” and “NWx” may be substituted in all the discussion above.Example x18 RAM Write Sequence using Byte Write EnablesData In SampleBW0BW1D0–D8D9–D17TimeBeat 101Data In Don’t CareBeat 210Don’t Care Data InResulting Write OperationBeat 1Beat 2D0–D8D9–D17D0–D8D9–D17Written Unchanged Unchanged WrittenOutput Register ControlSigmaSIO-II SRAMs offer two mechanisms for controlling the output data registers. Typically, control is handled by the Output Register Clock inputs, C and C. The Output Register Clock inputs can be used to make small phase adjustments in the firing of the output registers by allowing the user to delay driving data out as much as a few nanoseconds beyond the next rising edges of the K and K clocks. If the C and C clock inputs are tied high, the RAM reverts to K and K control of the outputs.A K LD R/WA 0–A nK LD 0D 1–D nBank 0Bank 1Bank 2Bank 3R/W 0D A K R/W D A K R/W D A KR/W D LDLDLD QQQ QCCCCQ 1–Q nC LD 1R/W 1LD 2R/W 2LD 3R/W 3Note:For simplicity BWn is not shown.GS8662S08/09/18/36E-333/300/250/200/167Example Four Bank Depth Expansion SchematicGS8662S08/09/18/36E-333/300/250/200/167Burst of 2 SigmaSIO-II SRAM Depth ExpansionWrite BRead C Write D Read E Write F Read G Read H Read J NOPBCDEFGHJBB+1FF+1DD+1EE+1HH+1CC+1GG+1JK K Address LD Bank 1LD Bank 2R/W Bank 1R/W Bank 2BWx Bank 1BWx Bank 2D Bank 1D Bank 2C Bank 1C Bank 1Q Bank 1CQ Bank 1CQ Bank 1C Bank 2C Bank 2Q Bank 2CQ Bank 2CQ Bank 2GS8662S08/09/18/36E-333/300/250/200/167FLXDrive-II Output Driver Impedance ControlHSTL I/O SigmaSIO-II SRAMs are supplied with programmable impedance output drivers. The ZQ pin must be connected to V SS via an external resistor, RQ, to allow the SRAM to monitor and adjust its output driver impedance. The value of RQ must be 5X the value of the intended line impedance driven by the SRAM. The allowable range of RQ to guarantee impedance matching with a vendor-specified tolerance is between 150Ω and 300Ω. Periodic readjustment of the output driver impedance is necessary as the impedance is affected by drifts in supply voltage and temperature. The SRAM’s output impedance circuitry compensates for drifts in supply voltage and temperature every 1024 cycles. A clock cycle counter periodically triggers an impedance evaluation, resets and counts again. Each impedance evaluation may move the output driver impedance level one step at a time towards the optimum level. The output driver is implemented with discrete binary weighted impedance steps. Impedance updates for “0s” occur whenever the SRAM is driving “1s” for the same DQs (and vice-versa for “1s”) or the SRAM is in HI-Z.Separate I/O Burst of 2 Sigma SIO-II SRAM Truth TableA LD R/WCurrentOperationD D Q QK ↑(t n)K ↑(t n)K ↑(t n)K ↑(t n)K ↑(t n+1)K ↑(t n+1)K ↑(t n+1)K ↑(t n+1)X1X Deselect X—Hi-Z—V01Read X—Q0Q1 V00Write D0D1Hi-Z—Notes:1.“1” = input “high”; “0” = input “low”; “V” = input “valid”; “X” = input “don’t care”2.“—” indicates that the input requirement or output state is determined by the next operation.3.Q0 and Q1 indicate the first and second pieces of output data transferred during Read operations.4.D0 and D1 indicate the first and second pieces of input data transferred during Write operations.5.Qs are tristated for one cycle in response to Deselect and Write commands, one cycle after the command is sampled, except when pre-ceded by a Read command.6.CQ is never tristated.ers should not clock in metastable addresses.x18 Byte Write Clock Truth TableBW BW Current OperationD D K ↑(t n+1)K ↑(t n+2)K ↑(t n )K ↑(t n+1)K ↑(t n+2)TTWriteDx stored if BWn = 0 in both data transfers D1D2T F WriteDx stored if BWn = 0 in 1st data transfer only D1XF T WriteDx stored if BWn = 0 in 2nd data transfer onlyX D2F F Write AbortNo Dx stored in either data transferX XNotes:1.“1” = input “high”; “0” = input “low”; “X” = input “don’t care”; “T” = input “true”; “F” = input “false”.2.If one or more BWn = 0, then BW = “T”, else BW = “F”.GS8662S08/09/18/36E-333/300/250/200/167x36 Byte Write Enable (BWn) Truth TableBW3BW2BW1BW0D27–D35D18–D26D9–D17D0–D81111Don’t Care Don’t Care Don’t Care Don’t Care 0111Don’t Care Don’t Care Don’t Care Data In 1011Don’t Care Don’t Care Data In Don’t Care 0011Don’t Care Don’t Care Data In Data In 1101Don’t Care Data In Don’t Care Don’t Care 0101Don’t Care Data In Don’t Care Data In 1001Don’t Care Data In Data In Don’t Care 0001Don’t Care Data In Data In Data In 1110Data In Don’t Care Don’t Care Don’t Care 0110Data In Don’t Care Don’t Care Data In 1010Data In Don’t Care Data In Don’t Care 0010Data In Don’t Care Data In Data In 1100Data In Data In Don’t Care Don’t Care 0100Data In Data In Don’t Care Data In 1000Data In Data In Data In Don’t Care 0Data InData InData InData Inx8 Nybble Write Enable (NWn) Truth Table NW1NW0D9–D17D0–D811Don’t Care Don’t Care 01Don’t Care Data In 10Data In Don’t Care 0Data InData InGS8662S08/09/18/36E-333/300/250/200/167GS8662S08/09/18/36E-333/300/250/200/167State DiagramPower-UpNOPLoad NewDDR Read DDR WriteREADLOADWRITELOADLOADLOADLOADLOADAbsolute Maximum Ratings(All voltages reference to V SS )SymbolDescriptionValueUnitV DD Voltage on V DD Pins –0.5 to 2.9V V DDQ Voltage in V DDQ Pins –0.5 to V DD V V REF Voltage in V REF Pins –0.5 to V DDQV V I/O Voltage on I/O Pins –0.5 to V DDQ +0.3 (≤ 2.9 V max.)V V IN Voltage on Other Input Pins –0.5 to V DDQ +0.3 (≤ 2.9 V max.)V I IN Input Current on Any Pin +/–100mA dc I OUT Output Current on Any I/O Pin +/–100mA dcT J Maximum Junction Temperature125o C T STGStorage Temperature–55 to 125oCNote:Permanent damage to the device may occur if the Absolute Maximum Ratings are exceeded. Operation should be restricted to Recommended Operating Conditions. Exposure to conditions exceeding the Recommended Operating Conditions, for an extended period of time, may affect reliability of this component.GS8662S08/09/18/36E-333/300/250/200/167Recommended Operating ConditionsPower SuppliesParameterSymbolMin.Typ.Max.UnitSupply Voltage V DD 1.7 1.8 1.9V I/O Supply Voltage V DDQ 1.7 1.8 1.9V Reference VoltageV REF0.68—0.95VNotes:1.Unless otherwise noted, all performance specifications quoted are evaluated for worst case at both 1.4 V ≤ V DDQ ≤ 1.6 V (i.e., 1.5 V I/O)and 1.7 V ≤ V DDQ ≤ 1.95 V (i.e., 1.8 V I/O) and quoted at whichever condition is worst case.2.The power supplies need to be powered up simultaneously or in the following sequence: V DD , V DDQ , V REF , followed by signal inputs. Thepower down sequence must be the reverse. V DDQ must not exceed V DD .Operating TemperatureParameterSymbolMin.Typ.Max.UnitAmbient Temperature (Commercial Range Versions)T A 02570°C Ambient Temperature (Industrial Range Versions)T A–402585°CGS8662S08/09/18/36E-333/300/250/200/167HSTL I/O DC Input CharacteristicsParameterSymbolMinMaxUnitsNotesDC Input Logic High V IH (dc)V REF + 0.1V DDQ + 0.3mV 1DC Input Logic LowV IL (dc)–0.3V REF – 0.1mV1Note:Compatible with both 1.8 V and 1.5 V I/O driversHSTL I/O AC Input CharacteristicsParameterSymbolMinMaxUnitsNotesAC Input Logic High V IH (ac)V REF + 0.2—mV 3,4AC Input Logic LowV IL (ac)—V REF – 0.2mV 3,4V REF Peak to Peak AC VoltageV REF (ac)—5% V REF (DC)mV1Notes:1.The peak to peak AC component superimposed on V REF may not exceed 5% of the DC component of V REF .2.To guarantee AC characteristics, V IH ,V IL , Trise, and Tfall of inputs and clocks must be within 10% of each other.3.For devices supplied with HSTL I/O input buffers. Compatible with both 1.8 V and 1.5 V I/O drivers.4.See AC Input Definition drawing below.V IH (ac)V REF V IL (ac)HSTL I/O AC Input Definitions20% tKHKHV SS – 1.0 V50%V SS V IHUndershoot Measurement and TimingOvershoot Measurement and Timing20% tKHKHV DD + 1.0 V50%V DDV ILCapacitanceo C, f = 1 MH Z , V DDParameterSymbolTest conditionsTyp.Max.UnitInput Capacitance C IN V IN = 0 V 45pF Output CapacitanceC OUTV OUT = 0 V67pFNote: This parameter is sample tested.GS8662S08/09/18/36E-333/300/250/200/167AC Test ConditionsParameterConditionsInput high level V DDQ Input low level 0 V Max. input slew rate 2 V/ns Input reference level V DDQ /2Output reference levelV DDQ /2Note:Test conditions as specified with output loading as shown unless otherwise noted.DQVT = V DDQ /250ΩRQ = 250 Ω (HSTL I/O)V REF = 0.75 VAC Test Load DiagramInput and Output Leakage CharacteristicsParameterSymbolTest ConditionsMin.MaxNotesInput Leakage Current (except mode pins)I IL V IN = 0 to V DD –2 uA 2 uA DoffI INDOFF V DD ≥ V IN ≥ V IL 0 V ≤ V IN ≤ V IL –100 uA –2 uA 2 uA 2 uA Output Leakage CurrentI OLOutput Disable,V OUT = 0 to V DDQ–2 uA2 uA(T A = 25= 3.3 V)GS8662S08/09/18/36E-333/300/250/200/167Programmable Impedance HSTL Output Driver DC Electrical CharacteristicsParameterSymbolMin.Max.UnitsNotesOutput High Voltage V OH1 V DDQ /2 – 0.12V DDQ /2 + 0.12V 1, 3Output Low Voltage V OL1 V DDQ /2 – 0.12V DDQ /2 + 0.12V 2, 3Output High Voltage V OH2 V DDQ – 0.2V DDQ V 4, 5Output Low VoltageV OL2Vss0.2V4, 6Notes:1. I OH = (V DDQ /2) / (RQ/5) +/– 15% @ V OH = V DDQ /2 (for: 175Ω ≤ RQ ≤ 350Ω).2. I OL = (V DDQ /2) / (RQ/5) +/– 15% @ V OL = V DDQ /2 (for: 175Ω ≤ RQ ≤ 350Ω).3.Parameter tested with RQ = 250Ω and V DDQ = 1.5 V or 1.8 V4.Minimum Impedance mode, ZQ = V SS5.I OH = –1.0 mA6.I OL = 1.0 mAOperating CurrentsParameterSymbolTest Conditions-333-300-250-200-167Notes0to 70°C –40 to 85°C 0to 70°C –40 to 85°C 0to 70°C –40 to 85°C 0to 70°C –40 to 85°C 0to 70°C –40 to 85°C Operating Current (x36): DDR I DD V DD = Max, I OUT = 0 mA Cycle Time ≥ t KHKH Min TBDTBDTBDTBDTBDTBDTBDTBDTBDTBD2, 3Operating Current (x18): DDR I DD V DD = Max, I OUT = 0 mA Cycle Time ≥ t KHKH Min TBD TBD TBD TBD TBD TBD TBD TBD TBD TBD 2, 3Operating Current (x9): DDR I DD V DD = Max, I OUT = 0 mA Cycle Time ≥ t KHKH Min TBD TBD TBD TBD TBD TBD TBD TBD TBD TBD 2, 3Operating Current (x8): DDR I DDV DD = Max, I OUT = 0 mA Cycle Time ≥ t KHKH Min TBD TBD TBD TBD TBD TBD TBD TBD TBD TBD 2, 3Standby Current (NOP): DDR I SB1Device deselected,I OUT= 0 mA, f = Max,All Inputs ≤ 0.2 V or ≥ V DD – 0.2 VTBD TBD TBD TBD TBD TBD TBD TBD TBD TBD 2, 4Notes:1.Power measured with output pins floating.2.Minimum cycle, I OUT = 0 mA3.Operating current is calculated with 50% read cycles and 50% write cycles.4.Standby Current is only after all pending read and write burst operations are completed.GS8662S08/09/18/36E-333/300/250/200/167GS8662S08/09/18/36E-333/300/250/200/167AC Electrical CharacteristicsParameterSymbol-333-300-250-200-167UnitsN o t e sMin Max Min Max Min Max Min Max Min MaxClockK, K Clock Cycle Time C, C Clock Cycle Time t KHKH t CHCH 3.0 3.5 3.3 4.2 4.0 6.3 5.07.9 6.08.4ns tTKC Variablet KCVar —0.2—0.2—0.2—0.2—0.2ns 5K, K Clock High Pulse Width C, C Clock High Pulse Width t KHKL t CHCL 1.2— 1.32— 1.6— 2.0— 2.4—ns K, K Clock Low Pulse Width C, C Clock Low Pulse Width t KLKH t CLCH 1.2— 1.32— 1.6— 2.0— 2.4—ns K to K High C to C Hight KHKH 1.35— 1.49— 1.8— 2.2— 2.7—ns K, K Clock High to C, C Clock High t KHCH 0 1.30 1.450 1.80 2.30 2.8ns DLL Lock Time t KCLock 1024—1024—1024—1024—1024—cycle 6K Static to DLL resett KCReset 30—30—30—30—30—nsOutput TimesK, K Clock High to Data Output Valid C, C Clock High to Data Output Valid t KHQV t CHQV —0.45—0.45—0.45—0.45—0.5ns 3K, K Clock High to Data Output Hold C, C Clock High to Data Output Hold t KHQX t CHQX –0.45—–0.45—–0.45—–0.45—–0.5—ns 3K, K Clock High to Echo Clock Valid C, C Clock High to Echo Clock Valid t KHCQV t CHCQV —0.45—0.45—0.45—0.45—0.5ns K, K Clock High to Echo Clock Hold C, C Clock High to Echo Clock Hold t KHCQX t CHCQX –0.45—–0.45—–0.45—–0.45—–0.5—ns CQ, CQ High Output Valid t CQHQV —0.25—0.27—0.30—0.35—0.40ns 7CQ, CQ High Output Hold t CQHQX –0.25—–0.27—–0.30—–0.35—–0.40—ns 7K Clock High to Data Output High-Z C Clock High to Data Output High-Z t KHQZ t CHQZ —0.45—0.45—0.45—0.45—0.5ns 3K Clock High to Data Output Low-Z C Clock High to Data Output Low-Zt KHQX1t CHQX1–0.45—–0.45—–0.45—–0.45—–0.5—ns3Setup TimesAddress Input Setup Time t AVKH 0.4—0.4—0.5—0.6—0.7—ns Control Input Setup Time t IVKH 0.4—0.4—0.5—0.6—0.7—ns 2Data Input Setup Timet DVKH0.28—0.3—0.35—0.4—0.5—nsGS8662S08/09/18/36E-333/300/250/200/167Hold TimesAddress Input Hold Time t KHAX 0.4—0.4—0.5—0.6—0.7—ns Control Input Hold Time t KHIX 0.4—0.4—0.5—0.6—0.7—ns Data Input Hold Timet KHDX0.28—0.3—0.35—0.4—0.5—nsNotes:1.All Address inputs must meet the specified setup and hold times for all latching clock edges.2.Control singles are R, W, BW0, BW1, and (NW0, NW1 for x8) and (BW2, BW3 for x36).3.If C, C are tied high, K, K become the references for C, C timing parameters4.To avoid bus contention, at a given voltage and temperature tCHQX1 is bigger than tCHQZ. The specs as shown do not imply bus conten-tion because tCHQX1 is a MIN parameter that is worst case at totally different test conditions (0°C, 1.9 V) than tCHQZ, which is a MAX parameter (worst case at 70°C, 1.7 V). It is not possible for two SRAMs on the same board to be at such different voltages and tempera-tures.5.Clock phase jitter is the variance from clock rising edge to the next expected clock rising edge.6.V DD slew rate must be less than 0.1 V DC per 50 ns for DLL lock retention. DLL lock time begins once V DD and input clock are stable.7.Echo clock is very tightly controlled to data valid/data hold. By design, there is a ±0.1 ns variation from echo clock to data. The datasheetparameters reflect tester guard bands and test setup variations.AC Electrical Characteristics (Continued)ParameterSymbol-333-300-250-200-167UnitsN o t e sMin Max Min Max Min Max Min Max Min Max。

MEMORY存储芯片MT29F64G08CBABBWP-12ITB中文规格书

Micron Parallel NOR Flash Embedded Memory (P30-65nm)JS28F256P30B/TFx, RC28F256P30B/TFx, PC28F256P30B/TFx,RD48F4400P0VBQEx, RC48F4400P0VB0Ex,PC48F4400P0VB0Ex, PF48F4000P0ZB/TQExFeatures•High performance–100ns initial access for Easy BGA–110ns initial access for TSOP–25ns 16-word asychronous page read mode–52 MHz (Easy BGA) with zero WAIT states and 17ns clock-to-data output synchronous burstread mode–4-, 8-, 16-, and continuous word options for burst mode–Buffered enhanced factory programming (BEFP) at 2 MB/s (TYP) using a 512-word buffer– 1.8V buffered programming at 1.14 MB/s (TYP) using a 512-word buffer•Architecture–MLC: highest density at lowest cost–Asymmetrically blocked architecture–Four 32KB parameter blocks: top or bottom con-figuration–128KB main blocks–Blank check to verify an erased block•Voltage and power–V CC (core) voltage: 1.7V to 2.0V–V CCQ (I/O) voltage: 1.7V to 3.6V–Standy current: 65µA (TYP) for 256Mb–52 MHz continuous synchronous read current: 21mA (TYP), 24mA (MAX)•Security–One-time programmable register: 64 OTP bits, programmed with unique information from Mi-cron; 2112 OTP bits available for customer pro-gramming–Absolute write protection: V PP = V SS–Power-transition erase/program lockout–Individual zero-latency block locking–Individual block lock-down–Password access•Software–25μs (TYP) program suspend–25μs (TYP) erase suspend–Flash Data Integrator optimized–Basic command set and extended function Inter-face (EFI) command set compatible–Common flash interface•Density and Packaging–56-lead TSOP package (256Mb only)–64-ball Easy BGA package (256Mb, 512Mb)–QUAD+ and SCSP packages (256Mb, 512Mb)–16-bit wide data bus•Quality and reliabilty–JESD47 compliant–Operating temperature: –40°C to +85°C–Minimum 100,000 ERASE cycles per block–65nm process technologyStatus RegisterRead Status RegisterTo read the status register, issue the READ STATUS REGISTER command at any address.Status register information is available at the address that the READ STATUS REGISTER,WORD PROGRAM, or BLOCK ERASE command is issued to. Status register data is auto-matically made available following a word program, block erase, or block lock com-mand sequence. Reads from the device after any of these command sequences will out-put the devices status until another valid command is written (e.g. READ ARRAY com-mand).The status register is read using single asynchronous mode or synchronous burst modereads. Status register data is output on DQ[7:0], while 0x00 is output on DQ[15:8]. Inasynchronous mode, the falling edge of OE# or CE# (whichever occurs first) updatesand latches the status register contents. However, when reading the status register insynchronous burst mode, CE# or ADV# must be toggled to update status data.The device write status bit (SR7) provides the overall status of the device. SR[6:1]present status and error information about the PROGRAM, ERASE, SUSPEND, V PP, andBLOCK LOCK operations.Note: Reading the status register is a nonarray READ operation. When the operation oc-curs in asynchronous page mode, only the first data is valid and all subsequent data areundefined. When the operation occurs in synchronous burst mode, the same data wordrequested will be output on successive clock edges until the burst length requirementsare satisfied.Table 16: Status Register DescriptionNotes: 1.Default value = 0x80.2.Always clear the status register prior to resuming ERASE operations. This eliminates sta-tus register ambiguity when issuing commands during ERASE SUSPEND. If a commandsequence error occurs during an ERASE SUSPEND, the status register contains the com-mand sequence error status (SR[7,5,4] set). When the ERASE operation resumes and fin-ishes, possible errors during the operation cannot be detected via the status register be-cause it contains the previous error status.3.When bits 5:4 indicate a PROGRAM/ERASE operation error, either a CLEAR STATUS REG-ISTER 50h) or a RESET command must be issued with a 15µs delay.Clear Status RegisterThe CLEAR STATUS REGISTER command clears the status register. It functions inde-pendently of V PP. The device sets and clears SR[7,6,2], but it sets bits SR[5:3,1] withoutclearing them. The status register should be cleared before starting a command se-quence to avoid any ambiguity. A device reset also clears the status register.Configuration RegisterRead Configuration RegisterThe read configuration register (RCR) is a 16-bit read/write register used to select busread mode (synchronous or asynchronous) and to configure device synchronous burstread characteristics. To modify RCR settings, use the CONFIGURE READ CONFIGURA-TION REGISTER command. RCR contents can be examined using the READ DEVICEIDENTIFIER command and then reading from offset 0x05. On power-up or exit from re-set, the RCR defaults to asynchronous mode. RCR bits are described in more detail be-low.Note: Reading the configuration register is a nonarray READ operation. When the oper-ation occurs in asynchronous page mode, only the first data is valid, and all subsequentdata are undefined. When the operation occurs in synchronous burst mode, the sameword of data requested will be output on successive clock edges until the burst lengthrequirements are satisfied.Table 17: Read Configuration RegisterRead ModeThe read mode (RM) bit selects synchronous burst mode or asynchronous page modeoperation for the device. When the RM bit is set, asynchronous page mode is selected(default). When RM is cleared, synchronous burst mode is selected.Latency CountThe latency count (LC) bits tell the device how many clock cycles must elapse from therising edge of ADV# (or from the first valid clock edge after ADV# is asserted) until thefirst valid data word is driven to DQ[15:0]. The input clock frequency is used to deter-mine this value. The First Access Latency Count figure shows the data output latency fordifferent LC settings.Figure 13: First Access Latency CountCLK [C]Address [A]ADV# [V]DQ[15:0] [D/Q]DQ[15:0] [D/Q]DQ[15:0] [D/Q]DQ[15:0] [D/Q]DQ[15:0] [D/Q]DQ[15:0] [D/Q]DQ[15:0] [D/Q]DQ[15:0] [D/Q]Note: 1.First Access Latency Count Calculation:•1 / CLK frequency = CLK period (ns)•n x (CLK period) ≥t AVQV (ns) – t CHQV (ns)•Latency Count = n。

显卡数据库Nvidia