24LC22A-ISN;24LC22AT-ISN;24LC22A-IP;中文规格书,Datasheet资料

24lc256系列中文

1.8-5.5V 400 kHz (2) 2.5-5.5V 400 kHz 1.8-5.5V 400 kHz(2) 2.5-5.5V 400 kHz 4.5V-5.5V 400 kHz

8 字节

16 字节 16 字节

整个阵列

整个阵列 无

无

A0, A1, A2 A0, A1, A2

I I, E

I I C, I, E

装。

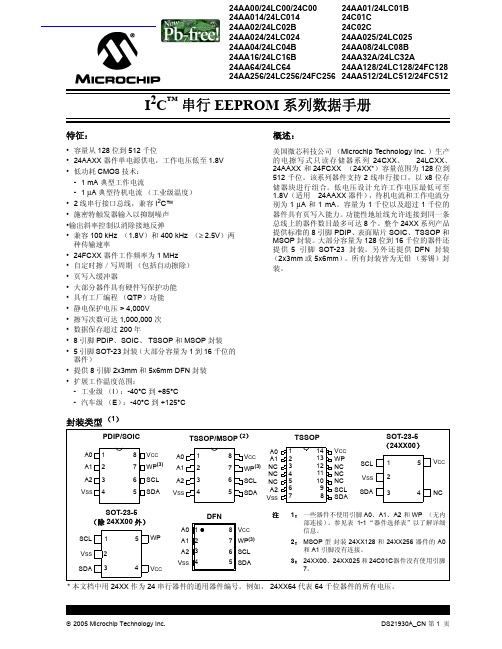

封装类型 (1)

PDIP/SOIC

TSSOP/MSOP(2)

A0 1 A1 2 A2 3 VSS 4

8 VCC

A0 1

7 WP(3) A1 2

6 SCL

A2 3

5 SDA VSS 4

8 VCC

A0 A1

7 WP(3) NC NC

6 SCL NC

5

SDA

A2 VSS

TSSOP

1

14

2

13

3

12

4

11

1.8-5.5V 2.5-5.5V 1.8-5.5V

400 kHz (2)

400 kHz 1 MHz(3)

64 字节

整个阵列

A0, A1, A2(4)

I

P, SN, SM, ST, MS, MF,

I, E ST14

I

256 千位器件

24AA256

1.8-5.5V 400 kHz (2)

24LC256 24FC256

2005 Microchip Technology Inc.

DS21930A_CN 第 3 页

24AAXX/24LCXX/24FCXX

2.0 电气特性

绝对最大额定值 (†)

VCC.............................................................................................................................................................................6.5V 相对于 Vss 的所有输入和输出 ............................................................................................................ -0.6V 到 VCC +1.0V 存储温度 ................................................................................................................................................. -65°C 到 +150°C 环境温度 (使用电源时)........................................................................................................................ -40°C 到 +125°C 所有引脚静电保护 ....................................................................................................................................................................≥ 4 kV

24LC32A-MT资料

•ISO 7816 compliant contact locations•Single supply with operation down to 2.5V -Maximum write current 3 mA at 6.0V -Maximum read current 150 µ A at 6.0V -Standby current 1 µ A max at 2.5V•T wo wire serial interface bus, I 2 C ™ compatible •100 kHz (2.5V) and 400 kHz (5V) compatibility •Self-timed ERASE and WRITE cycles •Power on/off data protection circuitry•1,000,000 ERASE/WRITE cycles guaranteed •32 byte page or byte write modes available •Schmitt trigger inputs for noise suppression•Output slope control to eliminate ground bounce • 2 ms typical write cycle time, byte or page •Electrostatic discharge protection > 4000V •Data retention > 200 years•8-pin PDIP and SOIC packages •T emperature ranges:DESCRIPTIONThe Microchip T echnology Inc. 24LC32A is a 4K x 8(32K bit) Serial Electrically Erasable PROM in an ISO micromodule for use in smart card applications. The device has a page-write capability of up to 32 bytes.-Commercial: 0˚C to +70˚C2元器件交易网24LC32A MODULE1.0ELECTRICAL CHARACTERISTICS1.1Maximum Ratings*V CC ........................................................................7.0V All inputs and outputs w.r.t. V SS ......-0.6V to VCC +1.0V Storage temperature ..........................-65˚C to +150˚C Ambient temp. with power applied......-65˚C to +125˚C Soldering temperature of leads (10 seconds)..+300˚C ESD protection on all pins .....................................≥ 4 kV*Notice: Stresses above those listed under “Maximum Ratings”may cause permanent damage to the device. This is a stress rat-ing only and functional operation of the device at those or anyother conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.TABLE 1-1:PIN FUNCTIONSName Function V SS Ground SDA Serial Data SCL Serial ClockV CC+2.5V to 6.0V Power SupplyTABLE 1-2:DC CHARACTERISTICSVcc = +2.5V to 6.0VCommercial (C):T amb = 0˚C to +70 ° CParameterSymbolMinTypMaxUnitsConditionsSCL and SDA pins:High level input voltage V IH .7 V CC —V Low level input voltage V IL —.3 Vcc V Hysteresis of Schmitt T rigger inputsV HYS .05 V CC—V Note 1Low level output voltage V OL —.40V I OL = 3.0 mA @ V CC = 4.5V I OL = 2.1 mA @ V CC = 2.5V Input leakage current I LI -1010 µ A V IN = .1V to V CC Output leakage current I LO -1010 µ A V OUT = .1V to V CC Pin capacitance (all inputs/outputs)C IN ,C OUT —10pF V CC = 5.0V (Note 1)T amb = 25˚C, f c = 1 MHz Operating current I CC Write —3mA V CC = 6.0VI CC Read —400 µ A V CC = 6.0V , SCL = 400Khz Standby currentI CCS —1 µ A5 µ A SCL = SDA = V CC = 5.0VI CCS1µ AVCC = 2.5V (Note 1)Note 1:This parameter is periodically sampled and not 100% tested.元器件交易网24LC32A MODULETABLE 1-3:AC CHARACTERISTICSParameterSymbolVcc = 2.5 - 6.0V STD. MODE Vcc = 4.5 - 6.0V FAST MODE UnitsRemarksMinMaxMinMaxClock frequency F CLK —100—400kHz Clock high time T HIGH 4000—600—ns Clock low timeT LOW 4700—1300—ns SDA and SCL rise time T R —1000—300ns Note 1SDA and SCL fall time T F —300—300ns Note 1START condition hold timeT HD : STA 4000—600—ns After this period the first clock pulse is generatedST ART condition setup timeT SU : STA 4700—600—ns Only relevant for repeated ST ART conditionData input hold time T HD : DAT 0—0—ns Data input setup time T SU : DAT 250—100—ns STOP condition setup timeT SU : STO 4000—600—ns Output valid from clock T AA —3500—900ns Note 2Bus free timeT BUF 4700—1300—ns Time the bus must be free before a new transmission can start Output fall time from V IH min to V IL maxT OF —25020 +0.1C B 250ns Note 1, CB ≤ 100 pF Input filter spike sup-pression (SDA and SCL pins)T SP—50—50nsNote 3Write cycle timeTWR —5—5ms Byte or Page modeNote 1: Not 100% tested. CB = total capacitance of one bus line in pF .2: As a transmitter, the device must provide an internal minimum delay time to bridge the undefined region (minimum 300 ns) of the falling edge of SCL to avoid unintended generation of ST ART or STOP conditions. 3: The combined T SP and VHYSspecifications are due to Schmitt trigger inputs which provide improved noise and spike suppression. This eliminates the need for a Ti specification for standard operation.元器件交易网24LC32A MODULE2.0PIN DESCRIPTIONS2.1SDA (Serial Data)This is a bidirectional pin used to transfer addresses and data into and data out of the device. It is an open drain terminal, therefore the SDA bus requires a pullup resistor to V CC (typical 10K Ω for 100 kHz, 1K Ω for 400kHz)For normal data transfer SDA is allowed to change only during SCL low. Changes during SCL high are reserved for indicating the ST ART and STOP condi-tions.2.2SCL (Serial Clock)This input is used to synchronize the data transfer from and to the device.3.0FUNCTIONAL DESCRIPTIONThe 24LC32A supports a bidirectional two-wire bus and data transmission protocol. A device that sends data onto the bus is defined as transmitter, and a device receiving data as receiver. The bus must be con-trolled by a master device which generates the serial clock (SCL), controls the bus access, and generates the ST ART and STOP conditions, while the 24LC32A works as slave. Both master and slave can operate as transmitter or receiver but the master device deter-mines which mode is activated.元器件交易网24LC32A MODULE4.0BUS CHARACTERISTICSThe following bus protocol has been defined:•Data transfer may be initiated only when the bus is not busy.•During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as a ST ART or STOP condition.Accordingly, the following bus conditions have been defined (See Figure 4-1).4.1Bus not Busy (A)Both data and clock lines remain HIGH.4.2Start Data Transfer (B)A HIGH to LOW transition of the SDA line while the clock (SCL) is HIGH determines a ST ART condition.All commands must be preceded by a START condi-tion.4.3Stop Data Transfer (C)A LOW to HIGH transition of the SDA line while the clock (SCL) is HIGH determines a STOP condition. All operations must be ended with a STOP condition.4.4Data Valid (D)The state of the data line represents valid data when,after a ST ART condition, the data line is stable for the duration of the HIGH period of the clock signal.The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data.Each data transfer is initiated with a ST ART condition and terminated with a STOP condition. The number of the data bytes transferred between the ST ART and STOP conditions is determined by the master device.4.5AcknowledgeEach receiving device, when addressed, is obliged to generate an acknowledge signal after the reception of each byte. The master device must generate an extra clock pulse which is associated with this acknowledge bit.A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course,setup and hold times must be taken into account. Dur-ing reads, a master must signal an end of data to the slave by NOT generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave (24LC32A) will leave the data line HIGH to enable the master to generate the STOP condition.(See Figure 4-2)元器件交易网24LC32A MODULE5.0DEVICE ADDRESSINGA control byte is the first byte received following the start condition from the master device. (See Figure 5-1) The control byte consists of a four bit control code;for the 24LC32A this is set as 1010 binary for read and write operations. The next three bits are device select bits on standard devices, however, for micromodules,these must be zeros. The last bit of the control byte defines the operation to be performed. When set to a one a read operation is selected, and when set to a zero a write operation is selected. The next two bytesreceived define the address of the first data byte (see Figure 5-2). Because only A11...A0 are used, the upper four address bits must be zeros. The most signif-icant bit of the most significant byte of the address is transferred first.Following the start condition, the 24LC32A monitors the SDA bus checking the device type identifier being transmitted. Upon receiving a valid control byte, the slave device outputs an acknowledge signal on the SDA line. Depending on the state of the R/W bit, the 24LC32A will select a read or write operation元器件交易网24LC32A MODULE6.0WRITE OPERATIONS6.1Byte WriteFollowing the start condition from the master, the con-trol code (four bits), the device select (three bits), and the R/W bit which is a logic low are clocked onto the bus by the master transmitter. This indicates to the addressed slave receiver that a byte with a word address will follow after it has generated an acknowl-edge bit during the ninth clock cycle. Therefore the next byte transmitted by the master is the high-order byte of the word address and will be written into the address pointer of the 24LC32A MODULE. The next byte is the least significant address byte. After receiving another acknowledge signal from the 24LC32A the master device will transmit the data word to be written into the addressed memory location.The 24LC32A acknowledges again and the master generates a stop condition. This initiates the internal write cycle, and during this time the 24LC32A will not generate acknowledge signals (see Figure 6-1).6.2Page WriteThe write control byte, word address and the first data byte are transmitted to the 24LC32A in the same way as in a byte write. But instead of generating a stop con-dition, the master transmits up to 32 bytes which are temporarily stored in the on-chip page buffer and will be written into memory after the master has transmitted a stop condition. After receipt of each word, the five lower address pointer bits are internally incremented by one.If the master should transmit more than 32 bytes prior to generating the stop condition, the address counter will roll over and the previously received data will be overwritten. As with the byte write operation, once the stop condition is received, an internal write cycle will begin. (see Figure 6-2).元器件交易网24LC32A MODULE7.0ACKNOWLEDGE POLLINGSince the device will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write com-mand has been issued from the master, the device ini-tiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the master send-ing a start condition followed by the control byte for a write command (R/W = 0). If the device is still busy with the write cycle, then no ACK will be returned. If the cycle is complete, then the device will return the ACK and the master can then proceed with the next read or write command. See Figure 7-1 for flow diagram.FIGURE 7-1:ACKNOWLEDGE POLLING8.0READ OPERATIONRead operations are initiated in the same way as write operations with the exception that the R/W bit of the slave address is set to one. There are three basic types of read operations: current address read, random read,and sequential read.8.1Current Address ReadThe 24LC32A contains an address counter that main-tains the address of the last word accessed, internally incremented by one. Therefore, if the previous access (either a read or write operation) was to address n (n is any legal address), the next current address read oper-ation would access data from address n + 1. Upon receipt of the slave address with R/W bit set to one, the 24LC32A issues an acknowledge and transmits the eight bit data word. The master will not acknowledge the transfer but does generate a stop condition and the 24LC32A discontinues transmission (see Figure 8-1).8.2Random ReadRandom read operations allow the master to access any memory location in a random manner. T o perform this type of read operation, first the word address must be set. This is done by sending the word address to the 24LC32A as part of a write operation (R/W bit set to 0).After the word address is sent, the master generates a start condition following the acknowledge. This termi-nates the write operation, but not before the internal address pointer is set. Then the master issues the con-trol byte again but with the R/W bit set to a one. The 24LC32A will then issue an acknowledge and transmit the eight bit data word. The master will not acknowl-edge the transfer but does generate a stop condition which causes the 24LC32A to discontinue transmis-sion (see Figure 8-2).元器件交易网24LC32A MODULE8.3Sequential ReadSequential reads are initiated in the same way as a ran-dom read except that after the 24LC32A transmits the first data byte, the master issues an acknowledge as opposed to the stop condition used in a random read.This acknowledge directs the 24LC32A to transmit the next sequentially addressed 8 bit word (see Figure 8-3). Following the final byte transmitted to the master,the master will NOT generate an acknowledge but will generate a stop condition.To provide sequential reads the 24LC32A contains an internal address pointer which is incremented by one at the completion of each operation. This address pointer allows the entire memory contents to be serially read during one operation. The internal address pointer will automatically roll over from address 0FFF to address 000 if the master acknowledges the byte received from the array address 0FFF .元器件交易网24LC32A MODULE9.0SHIPPING METHODThe micromodules will be shipped to customers in clear plastic trays. Each tray holds 150 modules, and the trays can be stacked in a manner similar to shipping die in waffle packs. A tray drawing with dimensions is shown in Figure 9-1.元器件交易网24LC32A MODULE元器件交易网24LC32A MODULENOTES:元器件交易网24LC32A MODULENOTES:元器件交易网24LC32A MODULENOTES:元器件交易网24LC32A MODULE24LC32A MODULE PRODUCT IDENTIFICATION SYSTEMT o order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.Sales and SupportData SheetsProducts supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recom-mended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:1.Y our local Microchip sales office.2.The Microchip Corporate Literature Center U.S. FAX: (602) 786-7277.3.The Microchip’s Bulletin Board, via your local CompuServe number (CompuServe membership NOT required).Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.元器件交易网MAll rights reserved. © 1997, Microchip T echnology Incorporated, USA. 9/97 Printed on recycled paper.元器件交易网。

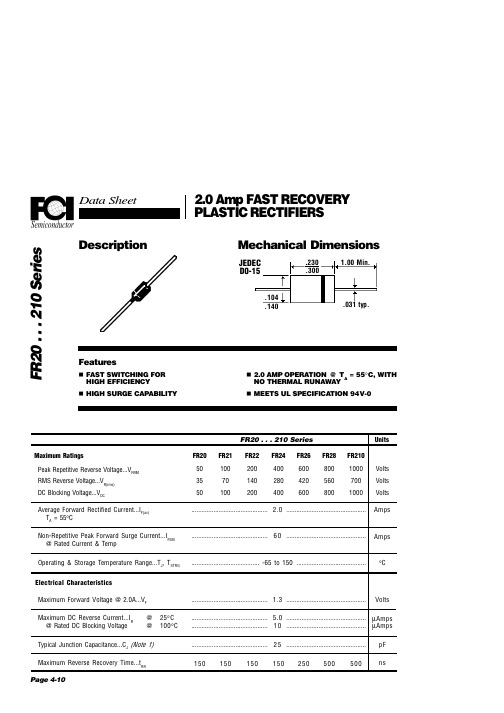

FR24中文资料

25 50 75 100 125 150 175 ° Ambient Temperature (°C)

100 10 Number of Cycles @ 60 Hz

Typical Instantaneous Forward Characteristics 100 Forward Current (A)

FR20 . . . 210 Series Maximum Ratings Peak Repetitive Reverse Voltage...VRRM RMS Reverse Voltage...VR(rms) DC Blocking Voltage...VDC Average Forward Rectified Current...IF(av) TA = 55°C Non-Repetitive Peak Forward Surge Current...IFSM @ Rated Current & Temp Operating & Storage Temperature Range...TJ, TSTRG Electrical Characteristics Maximum Forward Voltage @ 2.0A...VF Maximum DC Reverse Current...IR @ Rated DC Blocking Voltage @ @ 25°C 100°C ............................................. 1.3 ............................................... FR20 50 35 50 FR21 100 70 100 FR22 200 140 200 FR24 400 280 400 FR26 600 420 600 FR28 800 560 800 FR210 1000 700 1000

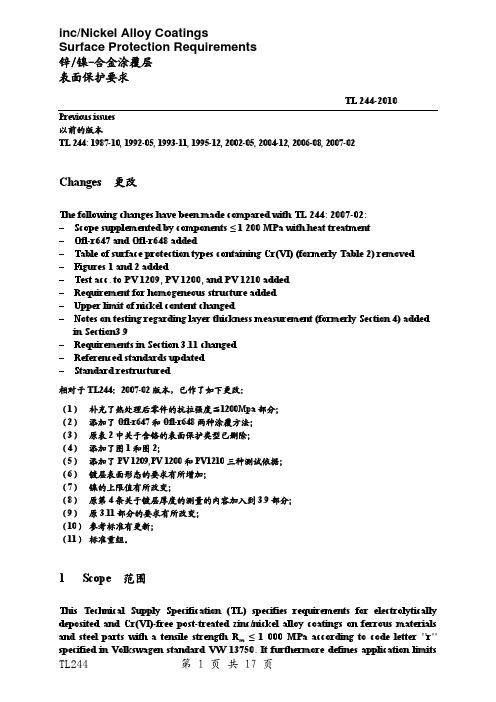

TL244-2010中英互译

表面保护要求TL 244-2010 Previous issues以前的版本TL 244: 1987-10, 1992-05, 1993-11, 1995-12, 2002-05, 2004-12, 2006-08, 2007-02Changes 更改The following changes have been made compared with TL 244: 2007-02:– Scope supplemented by components ≤ 1 200 MPa with heat treatment– Ofl-r647 and Ofl-r648 added– Table of surface protection types containing Cr(VI) (formerly Table 2) removed– Figures 1 and 2 added– Test acc. to PV 1209, PV 1200, and PV 1210 added– Requirement for homogeneous structure added– Upper limit of nickel content changed– Notes on testing regarding layer thickness measurement (formerly Section 4) added in Section3.9– Requirements in Section 3.11 changed– Referenced standards updated– Standard restructured相对于TL244:2007-02版本,已作了如下更改:(1)补充了热处理后零件的抗拉强度≦1200Mpa部分;(2)添加了Ofl-r647和Ofl-r648两种涂覆方法;(3)原表2中关于含铬的表面保护类型已删除;(4)添加了图1和图2;(5)添加了PV 1209,PV 1200和PV1210三种测试依据;(6)镀层表面形态的要求有所增加;(7)镍的上限值有所改变;(8)原第4条关于镀层厚度的测量的内容加入到3.9部分;(9)原3.11部分的要求有所改变;(10)参考标准有更新;(11)标准重组。

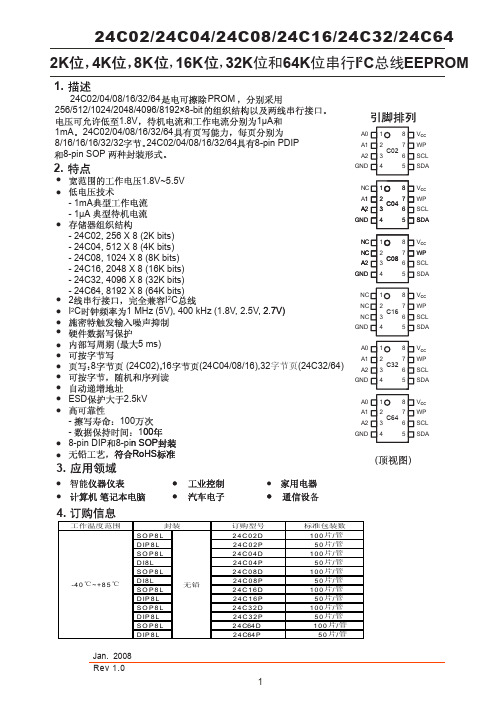

24C02中文资料

24C02/24C04/24C08/24C16/24C32/24C641.2.2K4K 8K ,16K ,32K 位和64K 位串行I C 总线EEPROM3.24C02/04/08/16/32/64PROM256/512/1024/2048/4096/8192×8-bit1.8V1μA1mA 24C02/04/08/16/32/648/16/16/16/32/3224C02/04/08/16/32/648-pin PDIP8-pin SOP ●●●●●●●●●●●●SD SCL WP V CC NC A SD A SCL WP V CC 12348765NC NC NC GND SD A SCL WP V CC 12348765 ()SD A SCL WP V CC 12348765A 0A 1A 2GND C02C1621.8V~5.5V- 1mA- 1μA- 24C02, 256 X 8 (2K bits)- 24C04, 512 X 8 (4K bits) - 24C08, 1024 X 8 (8K bits) - 24C16, 2048 X 8 (16K bits)- 24C32, 4096 X 8 (32K bits)- 24C64, 8192 X 8 (64K bits)2I CI C 1 MHz (5V), 400 kHz (1.8V, 2.5V, 2.7V) ( 5 ms)8 (24C02)16(24C04/08/16),32字节页(24C32/64)ESD 2.5kV - 100- 100 8-pin DIP 8-pin SOP RoHS ●●●●●●●22●S D A 123487651A 2GND NC NC C A 2GND C04C082.7V)00n SOP●●SD A SCL WP V CC 12348765A 0A 1A 2GND C32SD ASCL WP V CC 12348765A 0A 1A 2GNDC6424C02/24C04/24C08/24C16/24C32/24C645. Ḛ1 ḚV 6. 乱 ヺ ԡⳈ⌕կ⬉⬉ Ⳉ⌕䕧 ⬉ ⏽V CC Ⳉ⌕䕧 ⬉ V IN V OUT T STG -0.3 ~ V CC +0.3-0.3 ~ V CC +0.3-0.3 ~ +6.5°C -65 ~ +150V °C7. 㤤 ӊヺ ԡⳈ⌕կ⬉⬉ V CC ⏽T A+855.5 1.8-40(䍙 乱 㛑Ӯ 㟈 ӊ )V V ( 㤤 ӊϟ ⦄ 㛑)SDASCL WP V CCNC /NC /NC /A0NC /NC /A1/A1NC /A2/A2/A2C16/C08/C04/C02GNDSTART STOPLOGICSERIAL CONTROLLOGICDEVICE ADDRESS COMPARATORDATA WORD ADDRESS COUNTER LOADCOMPLOADINCY DECODER HIGH VOLTAGE PUMP/TIMING ENDATA RECOVERYEEPROMSERIAL MUXX D E C O D E RDOUT/ACKNOWLEDGEDINESD ⬉ (Ҏԧ )ESD ⬉ ( )V ESD2500200V V乱⬉ 䕧 ⬉ 乱 㛑Ӯ 㟈 ӊ DOUTmA 9. Ⳉ⌕⬉⇨⡍ヺ ԡ ⬉⌕կ⬉⬉⌕I CC V CC =5V⌟䆩 ӊ100kHz 3.0䕧 Ԣ⬉ ⬉μA 3.01.0-0.6V 0.4V IN = V CC GND 0.05( ӊ˖T A = 0°C ̚ +70°C, V CC = +1.8V ̚ +5.5V ˈ䰸䴲 ⊼䞞)䕧 Ԣ⬉ ⬉ μA V IL 0.4V CC0.20.4100kHz V V CC ×0.3I SB V IN = V CC GND V OUT = V CC GND μA 䕧 ⓣ⬉⌕䕧 ⓣ⬉⌕I LI I LO V IH 䕧 催⬉ ⬉ V CC +0.5V V V VV OL3V OL2V = 2.1 mA V 10. Ѹ⌕⬉⇨⡍ ( ӊ˖T A = 0°C ̚ +70°C, V = +1.8V +5.5V, C L = 100 pF ˈ䰸䴲 ⊼䞞)ヺ ԡ䩳催⬉䩳乥⥛, SCL ⌟䆩 ӊ400V CC =1.8V 1000ns 0.050.050.60.90.6 μskHz 1.20.5540V CC =5V 0.4t LOW μs ⍜䰸 䯈 䩳ϟ䰡⊓ 䕧 䯈䱨 䯈t I t AA50t HIGH䩳Ԣ⬉ μsV CC =1.8V V CC =5V V CC =1.8V V CC =5V V CC =1.8V V CC =5V V CC =1.8V V CC =5V8. 㛮⬉( ӊ˖T A = 25°C, f = 1.0 MHz, V CC = +1.8V)pFヺ ԡ䕧 /䕧 ⬉ (SDA)C I/O 䕧 ⬉ (A0, A1, A2, SCL)C IN68 pF⌟䆩 ӊV I/O = 0V V IN = 0V1.2 㒓䞞 䯈t BUF0.5μs V CC =1.8V V CC =5V䇏1.03.0 mA m 042.0C =5.0V, I OL = 3.0 mA CC ×0.7GNDOL1V CC =3.0V, I OL =2.1mA CC =1.8V, I OL = 0.15 mA =C CC = +1.8V ̚+5.5f SCL10. Ѹ⌕⬉⇨⡍ (㓁)䕧 Ϟ 䯈 䕧 䯈0ns500.650.25ns t WRns 100ns ℶ ӊ ゟ 䯈 䕧 䯈t R t DH t F 䕧 ゟ 䯈μs ms䕧 ϟ䰡 䯈t SU.STOV CC =1.8V V CC =5V V CC =1.8V V CC =5Vμs 300100300t HD.DAT t SU.DAT 2 㒓3SCLSDA_INSDA _OUTt F t LOWt SU .STAt HD.STAt AA t DHt BUFt SU.STOt Rt HD.DAT t SU.DAT t HIGH t LOW8th BIT SCLSDAACKSTOPCONDITIONSTART CONDITIONt WR (1)t HD.STAμs 䍋 ӊ 䯈䍋 ӊ ゟ 䯈t SU.STA V CC =1.8V V CC =5V V CC =1.8V V CC =5Vμs 0.60.250.60.25ヺ ԡ ⌟䆩 ӊ ⊼ 䯈W :5 ҢϔϾ ⱘ ℶ ӊ 㟇 䚼 㒧 ⱘ 䯈DŽn 08V μ3001AHIG11.3156247A0A1A2SDA SCL WP GND V CCA2A1A024C02/32/64A2A1A0824C02/32/6424C04A2A1424C04A024C08A2224C08A0A124C1616KA2A1A0/SDA V CC10kΩSCL8WP WPWPV CC12.13. 䆺㒚 䇈24CXX I C 㒓Ӵ䕧 䆂DŽI C ϔ⾡ ǃϸ㒓І㸠䗮䆃 ˈ І㸠 㒓SDA І㸠 䩳㒓SCL DŽϸḍ㒓䛑 乏䗮䖛ϔϾϞ ⬉䰏 ⬉⑤DŽ ⱘ 㒓䜡㕂 4 ⼎4 ϸ㒓 㒓䜡㕂㒓Ϟ 䗕 ⱘ ӊ㹿⿄ 䗕 ˈ ⱘ ӊ㹿⿄ DŽ Ѹ ⱘ ӊ㹿⿄Џ ӊˈ Џ ӊ ⱘ ӊ 㹿⿄Ң ӊDŽЏ ӊѻ⫳І㸠 䩳SCL ˈ㒓ⱘ䆓䯂⢊ ǃѻ⫳START STOP ӊDŽ24CXX I C 㒓ЁЎҢ ӊ DŽ㒓 Ѣぎ䯆⢊ ҹ Ӵ䕧DŽ↣ Ӵ䕧 ѢSTART ӊˈ㒧 ѢSTOP ӊˈѠ㗙П䯈ⱘ 㡖 ≵ 䰤 ⱘˈ⬅ 㒓ϞⱘЏ ӊ DŽ ҹ 㡖˄8ԡ˅Ў ԡӴ䕧ˈ9ԡ ⬅ ѻ⫳ ㄨDŽ䍋 ℶ ӊ䩳㒓䛑Ў催 ⿄ 㒓 ぎ䯆⢊ DŽ SCL Ў催⬉ SDA ⱘϟ䰡⊓˄催 Ԣ 䍋 ӊ˄START ˈㅔ ЎS ˅ˈSDA ⱘϞ ⊓˄Ԣ 催˅ ℶ ӊ˄STOP ˈㅔ ЎP ˅DŽ 㾕 5DŽ5 䍋 ӊ ℶ ӊⱘ НV CCҪ24Cxx MPU SDASCLR PR Pϸ㒓І㸠S Ў催ㅔ ЎⱘϞ ⊓˄Ԣ 㒓І㸠 㒓SS 䍋 ӊ222ԡӴ䕧↣Ͼ 䩳㛝 Ӵ䗕ϔԡ DŽSCL Ў催 SDA 乏 〇 ˈ Ўℸ SDA ⱘ 㹿䅸Ў DŽԡӴ䕧 㾕 6DŽ6 ԡӴ䕧ㄨ㒓Ϟⱘ ↣ ϔϾ 㡖 ѻ⫳ϔϾ ㄨˈЏ ӊ 乏ѻ⫳ϔϾ ⱘ乱 ⱘ 䩳㛝 ˈ㾕 7DŽ7 I C㒓ⱘ ㄨ ԢSDA 㒓㸼⼎ ㄨˈ ㄨ㛝 䯈 〇 ⱘԢ⬉ DŽ Џ ӊ ˈ 乏 Ӵ䕧㒧 ⱘ 㒭 䗕 ˈ ϔϾ 㡖П ⱘ ㄨ㛝 䯈ϡӮѻ⫳ ㄨ ˄ϡ ԢSDA ˅DŽ䖭⾡ ϟˈ 䗕 乏䞞 SDA 㒓Ў催ҹ Џ ӊѻ⫳ ℶ ӊDŽ䗕 䕧 ⱘ䕧 ⱘЏ ӊ ⱘ䍋 ӊ289䴲 ㄨㄨㄨ 䩳㛝㒓〇䆌SDASCL2ѻ⫳ϔϾ ㄨˈЏ ӊ 乏ѻ⫳ϔԢ㒓Ӵӊ ⱘSCL 䍋 ӊS1ӊ䍋 ӊՓ㛑㢃⠛䇏 ˈEEPROM 䛑㽕∖ 8ԡⱘ ӊ ˄㾕 8˅DŽӊ ⬅"1"ǃ"0" 㒘 ˈ 4ԡ Ё ⼎ˈ Ѣ І㸠EEPROM 䛑 ϔḋⱘ Ѣ24C02/32/64ˈ䱣 3ԡA2ǃA1 A0Ў ӊ ԡˈ 乏Ϣ⹀ӊ䕧 㛮 ϔ㟈DŽ Ѣ24C04ˈ䱣 2ԡA2 A1Ў ӊ ԡˈ 1ԡЎ义 ԡDŽA2 A1 乏Ϣ⹀ӊ䕧 㛮 ϔ㟈ˈ㗠A0 ぎ㛮DŽѢ24C08ˈ䱣 1ԡA2Ў ӊ ԡˈ 2ԡЎ义 ԡDŽA2 乏Ϣ⹀ӊ䕧 㛮 ϔ㟈ˈ㗠A1 A0 ぎ㛮DŽѢ24C16ˈ ӊ ԡˈ3ԡ䛑Ў义 ԡˈ㗠A2ǃA1 A0 ぎ㛮DŽ ӊ ⱘLSB Ў䇏/ 䗝 ԡˈ催Ў䇏 ˈԢЎ DŽ㢹↨䕗 ӊ ϔ㟈ˈEEPROM 䕧 ㄨ"0"DŽ ϡϔ㟈ˈ 䖨 ⢊ DŽ8 ӊ 1010A2A1A0R/W MSBLSB1010A2A1P0R/W1010A2P1P0R/W1010P2P1P0R/Wӊ EEPROM Ԣ 㗫 ⱘ⡍⚍ˈ ӊЎ˖˄1˅⬉⑤Ϟ⬉˗˄2˅ ℶ ӊ ӏԩ 䚼 DŽ24C0424C0824C16DŽ ԡ䆂Ёѻ⫳Ё ǃ ⬉ ㋏㒳 ԡ ˈI C 㒓 䗮䖛ҹϟℹ偸 ԡ˖ ˄1˅ѻ⫳9Ͼ 䩳 DŽ˄2˅ SCL Ў催 ˈSDA гЎ催DŽ ˄3˅ѻ⫳ϔϾ䍋 ӊDŽ21. 㡖㽕∖ ӊ ACK ㄨ ˈ 8ԡⱘ DŽ 䖭Ͼ EEPROM ㄨ"0"ˈ✊ ϔϾ8ԡ DŽ 8ԡ ˈEEPROM ㄨ"0"ˈ ⴔ 乏⬅Џ ӊ 䗕 ℶ ӊ 㒜ℶ DŽℸ EEPROM 䖯 䚼 t WR ˈ 䴲 Ёˈ ℸ 䯈 䕧 䛑 Ⳉ ˈEEPROM Ӯ ㄨ˄㾕 9˅DŽ9 㡖SDA 㒓䍋 ӊM S BL S B R /W A C K M S BL S B A C KA C Kӊℶ ӊDŽ24C02/32/6413.2.图10页写24C02器件按8字节/页执行页写,24C04/08/16器件按16字节/页执行页写,24C32/64器件按32字节/页执行页写。

24c02EEPROM中文官方资料手册

测试条件 FSCL=100KHz VIN=0 ~Vcc VIN=0 ~Vcc VOUT=0 ~Vcc

IOL=3 mA IOL=1.5 mA

www.fpga-arm.com 分布电容

TA=25 , f =1.0MHz, Vcc =5V

符号

测试项

CI/O

I/O 电容 SDA 脚

CIN

输出电容 A0 A1 A2 SCL WP

管脚配置

管脚描述

管脚名称

功能

A0 A1 A2 SDA SCL

器件地址选择 串行数据/地址 串行时钟

WP

写保护

Vcc

+1.8V 6.0V 工作电压

Vss

地

2

方框图

海纳电子资讯网: www.fpga-arm.com

www.fpga-arm.com 极限参数

工作温度 工业级 -55 +125 商业级 0 +75

www.fpga-arm.com

1

海纳电子资讯网: www.fpga-arm.com

CAT24WC01/02/04/08/16 1K/2K/4K/8K/16K 位串行 E2PROM

特性

与 400KHz I2C 总线兼容

1.8 到 6.0 伏工作电压范围

低功耗 CMOS 技术

写保护功能 当 WP 为高电平时进入写保护状态

数据入保持时间

0

0

ns

tSUl: DAT

数据输入建立时间

50

50

ns

tR

SDA 及 SCL 上升时间

1

0.3

s

tF

SDA 及 SCL 下降时间

300

300

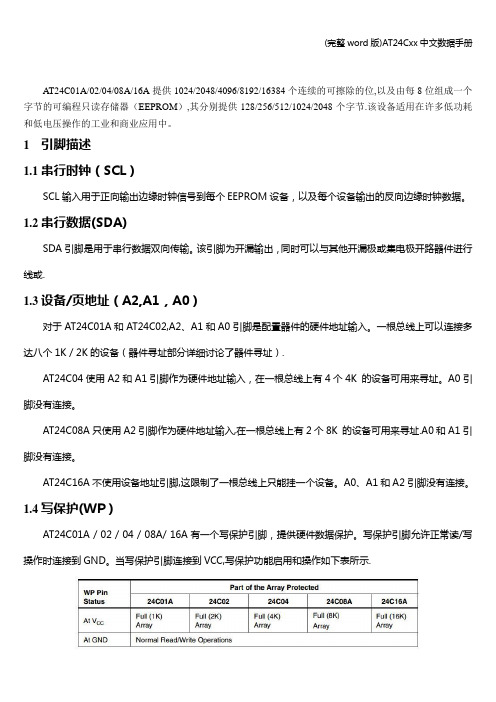

(完整word版)AT24Cxx中文数据手册

AT24C01A/02/04/08A/16A提供1024/2048/4096/8192/16384个连续的可擦除的位,以及由每8位组成一个字节的可编程只读存储器(EEPROM),其分别提供128/256/512/1024/2048个字节.该设备适用在许多低功耗和低电压操作的工业和商业应用中。

1引脚描述1.1串行时钟(SCL)SCL输入用于正向输出边缘时钟信号到每个EEPROM设备,以及每个设备输出的反向边缘时钟数据。

1.2串行数据(SDA)SDA引脚是用于串行数据双向传输。

该引脚为开漏输出,同时可以与其他开漏极或集电极开路器件进行线或.1.3设备/页地址(A2,A1,A0)对于AT24C01A和AT24C02,A2、A1和A0引脚是配置器件的硬件地址输入。

一根总线上可以连接多达八个1K / 2K的设备(器件寻址部分详细讨论了器件寻址).AT24C04使用A2和A1引脚作为硬件地址输入,在一根总线上有4个4K 的设备可用来寻址。

A0引脚没有连接。

AT24C08A只使用A2引脚作为硬件地址输入,在一根总线上有2个8K 的设备可用来寻址.A0和A1引脚没有连接。

AT24C16A不使用设备地址引脚,这限制了一根总线上只能挂一个设备。

A0、A1和A2引脚没有连接。

1.4写保护(WP)AT24C01A / 02 / 04 / 08A/ 16A有一个写保护引脚,提供硬件数据保护。

写保护引脚允许正常读/写操作时连接到GND。

当写保护引脚连接到VCC,写保护功能启用和操作如下表所示.2设备操作2.1时钟和数据转换SDA引脚通常情况下拉高.SDA引脚上的数据只能在SCL低时间段内更改,而启动条件或停止条件在SCL 为高时进行。

2.2启动条件在任何其他指令之前,SDA由高变为低,且SCL为高。

2.3停止条件SDA由低变为高,且SCL为高。

在读取序列之后,执行停止命令后EEPROM进入备用电源模式.2.4应答所有地址和数据字都是从EEPROM串行发送和接收8位字节。

24LC02中文资料

HT24LC01/021K/2K 2-Wire CMOS Serial EEPROMBlock Diagram Pin AssignmentFeatures•Operating voltage: 2.4V~5.5V •Low power consumption –Operation: 5mA max.–Standby: 5µA max.•Internal organization –1K (HT24LC01):128×8–2K (HT24LC02): 256×8•2-wire serial interface•Write cycle time: 5ms max.•Automatic erase-before-write operation•Partial page write allowed •8-byte Page write modes•Write operation with built-in timer •Hardware controlled write protection •40-year data retention•106 erase/write cycles per word •8-pin DIP/SOP package•8-pin TSSOP (HT24LC02 only)•Commerical temperature range (0°C to +70°C)General DescriptionThe HT24LC01/02 is a 1K/2K-bit serial read/write non-volatile memory device using the CMOS floating gate process. Its 1024/2048bits of memory are organized into 128/256words and each word is 8 bits. The device is optimized for use in many industrial and com-mercial applications where low power and low voltage operation are essential. Up to eight HT24LC01/02 devices may be connected to the same two-wire bus. The HT24LC01/02 is guar-anteed for 1M erase/write cycles and 40-yeardata retention.16th May ’99Pin DescriptionAbsolute Maximum RatingsOperating Temperature (Commercial) .................................................................................. 0°C to 70°C Storage Temperature ........................................................................................................ –50°C to 125°C Applied VCC Voltage with Respect to VSS ....................................................................... –0.3V to 6.0V Applied Voltage on any Pin with Respect to VSS ...................................................................–0.3V to V CC+0.3VNote: These are stress ratings only. Stresses exceeding the range specified under “Absolute Maxi-mum Ratings” may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.D.C. Characteristics Ta=0°C to 70°CNote: These parameters are periodically sampled but not 100% tested26th May ’99A.C. Characteristics Ta=0°C to 70°C* The standard mode means V CC=2.4V to 5.5VFor relative timing, refer to timing diagrams36th May ’99Functional Description•Serial clock (SCL)The SCL input is used for positive edge clock data into each EEPROM device and negative edge clock data out of each device.•Serial data (SDA)The SDA pin is bidirectional for serial data transfer. The pin is open-drain driven and may be wired-OR with any number of other open-drain or open collector devices.•A0, A1, A2The A2, A1 and A0 pins are device address inputs that are hard wired for the HT24LC01/02. As many as eight 1K/2K de-vices may be addressed on a single bus system (the device addressing is discussed in detail under the Device Addressing section).•Write protect (WP)The HT24LC01/02 has a write protect pin that provides hardware data protection. The write protect pin allows normal read/write operations when connected to the V SS. When the write protect pin is connected to Vcc, the write protection feature is enabled and oper-Memory organization•HT24LC01, 1K Serial EEPROMInternally organized with 128 8-bit words, the 1K requires a 7-bit data word address for random word addressing.•HT24LC02, 2K Serial EEPROMInternally organized with 256 8-bit words, the 2K requires an 8-bit data word address for random word addressing.Device operations•Clock and data transitionData transfer may be initiated only when thebus is not busy. During data transfer, the data line must remain stable whenever the clock line is high. Changes in data line while the clock line is high will be interpreted as a START or STOP condition.•Start conditionA high-to-low transition of SDA with SCL highis a start condition which must precede any other command (refer to Start and Stop Defi-nition Timing diagram).•Stop conditionA low-to-high transition of SDA with SCL highis a stop condition. After a read sequence, the stop command will place the EEPROM in a standby power mode (refer to Start and Stop Definition Timing Diagram).•AcknowledgeAll addresses and data words are serially transmitted to and from the EEPROM in 8-bit words. The EEPROM sends a zero to acknow-ledge that it has received each word. This happens during the ninth clock cycle.Device addressingThe 1K and 2K EEPROM devices all require an 8-bit device address word following a start con-dition to enable the chip for a read or write operation. The device address word consist of a mandatory one, zero sequence for the first four most significant bits (refer to the diagram show-ing the Device Address). This is common to all the EEPROM device.The next three bits are the A2, A1 and A0 device address bits for the 1K/2K EEPROM. These three bits must compare to their correspondinghard-wired input pins.46th May ’99The 8th bit of device address is the read/write operation select bit. A read operation is initi-ated if this bit is high and a write operation is initiated if this bit is low.If the comparison of the device address succeed the EEPROM will output a zero at ACK bit. If not, the chip will return to a standby state.Write operations•Byte writeA write operation requires an 8-bit data word address following the device address word and acknowledgment. Upon receipt of this ad-dress, the EEPROM will again respond with a zero and then clock in the first 8-bit data word. After receiving the 8-bit data word, the EEPROM will output a zero and the address-ing device, such as a microcontroller, must terminate the write sequence with a stop con-dition. At this time the EEPROM enters an internally-timed write cycle to the non-vola-tile memory . All inputs are disabled during this write cycle and EEPROM will not re-spond until the write is completed (refer to Byte write timing).•Page writeThe 1K/2K EEPROM is capable of an 8-byte page write.A page write is initiated the same as byte write, but the microcontroller does not send a stop condition after the first data word is clocked in. Instead, after the EEPROM ac-knowledges the receipt of the first data word,the microcontroller can transmit up to seven more data words. The EEPROM will respond with a zero after each data word received. The microcontroller must terminate the page write sequence with a stop condition.The data word address lower three (1K/2K)bits are internally incremented following the receipt of each data word. The higher data word address bits are not incremented, re-taining the memory page row location (refer to Page write timing).•Acknowledge pollingSince the device will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write command has been issued from the master, the device initiates the internally timed write cycle. ACK polling can be initiated immediately . This involves the master sending a start condition followed by the control byte for a write command(R/W=0). If the device is still busy with the56th May ’99write cycle, then no ACK will be returned. If the cycle is completed, then the device will return the ACK and the master can then pro-ceed with the next read or write command.•Write protectThe HT24LC01/02 can be used as a serial ROM when the WP pin is connected to VCC.Programming will be inhibited and the entire memory will be write-protected.•Read operationsRead operations are initiated the same way as write operations with the exception that the read/write select bit in the device address word is set to one. There are three read opera-tions: current address read, random address read and sequential read.•Current address readThe internal data word address counter main-tains the last address accessed during the last read or write operation, incremented by one.This address stays valid between operations as long as the chip power is maintained. The address roll over during read from the last byte of the last memory page to the first byte of the first page. The address roll over during write from the last byte of the current page to the first byte of the same page. Once the de-vice address with the read/write select bit set to one is clocked in and acknowledged by the EEPROM, the current address data word is serially clocked out. The microcontroller does not respond with an input zero but generates a following stop condition (refer to Current read timing).•Random readA random read requires a dummy byte write sequence to load in the data word address which is then clocked in and acknowledged by the EEPROM. The microcontroller must then generate another start condition. The micro-controller now initiates a current address read by sending a device address with the read/write select bit high. The EEPROM ac-knowledges the device address and serially clocks out the data word. The microcontroller does not respond with a zero but does gener-ates a following stop condition (refer to Ran-dom read timing).Acknowledge polling flow66th May ’99Timing DiagramsNote:The write cycle time t WR is the time from a valid stop condition of a write sequence to the end of the valid start condition of sequential command.•Sequential readSequential reads are initiated by either a cur-rent address read or a random address read.After the microcontroller receives a data word,it responds with an acknowledgment. As long as the EEPROM receives an acknowledgment, it will continue to increment the data word ad-dress and serially clock out sequential datawords. When the memory address limit is reached, the data word address will roll over and the sequential read continues. The se-quential read operation is terminated when the microcontroller does not respond with a zero but generates a following stopcondition.Holtek Semiconductor Inc. (Headquarters)No.3 Creation Rd. II, Science-based Industrial Park, Hsinchu, Taiwan, R.O.C.Tel: 886-3-563-1999Fax: 886-3-563-1189Holtek Semiconductor Inc. (Taipei Office)5F, No.576, Sec.7 Chung Hsiao E. Rd., Taipei, Taiwan, R.O.C.Tel: 886-2-2782-9635Fax: 886-2-2782-9636Fax: 886-2-2782-7128 (International sales hotline)Holtek Microelectronics Enterprises Ltd.RM.711, Tower 2, Cheung Sha Wan Plaza, 833 Cheung Sha Wan Rd., Kowloon, Hong KongTel: 852-2-745-8288Fax: 852-2-742-865786th May ’99。

24LC32中文资料

•ISO 7816 compliant contact locations•Single supply with operation down to 2.5V -Maximum write current 3 mA at 6.0V -Maximum read current 150 µ A at 6.0V -Standby current 1 µ A max at 2.5V•T wo wire serial interface bus, I 2 C ™ compatible •100 kHz (2.5V) and 400 kHz (5V) compatibility •Self-timed ERASE and WRITE cycles •Power on/off data protection circuitry•1,000,000 ERASE/WRITE cycles guaranteed •32 byte page or byte write modes available •Schmitt trigger inputs for noise suppression•Output slope control to eliminate ground bounce • 2 ms typical write cycle time, byte or page •Electrostatic discharge protection > 4000V •Data retention > 200 years•8-pin PDIP and SOIC packages •T emperature ranges:DESCRIPTIONThe Microchip T echnology Inc. 24LC32A is a 4K x 8(32K bit) Serial Electrically Erasable PROM in an ISO micromodule for use in smart card applications. The device has a page-write capability of up to 32 bytes.-Commercial: 0˚C to +70˚C2元器件交易网24LC32A MODULE1.0ELECTRICAL CHARACTERISTICS1.1Maximum Ratings*V CC ........................................................................7.0V All inputs and outputs w.r.t. V SS ......-0.6V to VCC +1.0V Storage temperature ..........................-65˚C to +150˚C Ambient temp. with power applied......-65˚C to +125˚C Soldering temperature of leads (10 seconds)..+300˚C ESD protection on all pins .....................................≥ 4 kV*Notice: Stresses above those listed under “Maximum Ratings”may cause permanent damage to the device. This is a stress rat-ing only and functional operation of the device at those or anyother conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.TABLE 1-1:PIN FUNCTIONSName Function V SS Ground SDA Serial Data SCL Serial ClockV CC+2.5V to 6.0V Power SupplyTABLE 1-2:DC CHARACTERISTICSVcc = +2.5V to 6.0VCommercial (C):T amb = 0˚C to +70 ° CParameterSymbolMinTypMaxUnitsConditionsSCL and SDA pins:High level input voltage V IH .7 V CC —V Low level input voltage V IL —.3 Vcc V Hysteresis of Schmitt T rigger inputsV HYS .05 V CC—V Note 1Low level output voltage V OL —.40V I OL = 3.0 mA @ V CC = 4.5V I OL = 2.1 mA @ V CC = 2.5V Input leakage current I LI -1010 µ A V IN = .1V to V CC Output leakage current I LO -1010 µ A V OUT = .1V to V CC Pin capacitance (all inputs/outputs)C IN ,C OUT —10pF V CC = 5.0V (Note 1)T amb = 25˚C, f c = 1 MHz Operating current I CC Write —3mA V CC = 6.0VI CC Read —400 µ A V CC = 6.0V , SCL = 400Khz Standby currentI CCS —1 µ A5 µ A SCL = SDA = V CC = 5.0VI CCS1µ AVCC = 2.5V (Note 1)Note 1:This parameter is periodically sampled and not 100% tested.元器件交易网24LC32A MODULETABLE 1-3:AC CHARACTERISTICSParameterSymbolVcc = 2.5 - 6.0V STD. MODE Vcc = 4.5 - 6.0V FAST MODE UnitsRemarksMinMaxMinMaxClock frequency F CLK —100—400kHz Clock high time T HIGH 4000—600—ns Clock low timeT LOW 4700—1300—ns SDA and SCL rise time T R —1000—300ns Note 1SDA and SCL fall time T F —300—300ns Note 1START condition hold timeT HD : STA 4000—600—ns After this period the first clock pulse is generatedST ART condition setup timeT SU : STA 4700—600—ns Only relevant for repeated ST ART conditionData input hold time T HD : DAT 0—0—ns Data input setup time T SU : DAT 250—100—ns STOP condition setup timeT SU : STO 4000—600—ns Output valid from clock T AA —3500—900ns Note 2Bus free timeT BUF 4700—1300—ns Time the bus must be free before a new transmission can start Output fall time from V IH min to V IL maxT OF —25020 +0.1C B 250ns Note 1, CB ≤ 100 pF Input filter spike sup-pression (SDA and SCL pins)T SP—50—50nsNote 3Write cycle timeTWR —5—5ms Byte or Page modeNote 1: Not 100% tested. CB = total capacitance of one bus line in pF .2: As a transmitter, the device must provide an internal minimum delay time to bridge the undefined region (minimum 300 ns) of the falling edge of SCL to avoid unintended generation of ST ART or STOP conditions. 3: The combined T SP and VHYSspecifications are due to Schmitt trigger inputs which provide improved noise and spike suppression. This eliminates the need for a Ti specification for standard operation.元器件交易网24LC32A MODULE2.0PIN DESCRIPTIONS2.1SDA (Serial Data)This is a bidirectional pin used to transfer addresses and data into and data out of the device. It is an open drain terminal, therefore the SDA bus requires a pullup resistor to V CC (typical 10K Ω for 100 kHz, 1K Ω for 400kHz)For normal data transfer SDA is allowed to change only during SCL low. Changes during SCL high are reserved for indicating the ST ART and STOP condi-tions.2.2SCL (Serial Clock)This input is used to synchronize the data transfer from and to the device.3.0FUNCTIONAL DESCRIPTIONThe 24LC32A supports a bidirectional two-wire bus and data transmission protocol. A device that sends data onto the bus is defined as transmitter, and a device receiving data as receiver. The bus must be con-trolled by a master device which generates the serial clock (SCL), controls the bus access, and generates the ST ART and STOP conditions, while the 24LC32A works as slave. Both master and slave can operate as transmitter or receiver but the master device deter-mines which mode is activated.元器件交易网24LC32A MODULE4.0BUS CHARACTERISTICSThe following bus protocol has been defined:•Data transfer may be initiated only when the bus is not busy.•During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as a ST ART or STOP condition.Accordingly, the following bus conditions have been defined (See Figure 4-1).4.1Bus not Busy (A)Both data and clock lines remain HIGH.4.2Start Data Transfer (B)A HIGH to LOW transition of the SDA line while the clock (SCL) is HIGH determines a ST ART condition.All commands must be preceded by a START condi-tion.4.3Stop Data Transfer (C)A LOW to HIGH transition of the SDA line while the clock (SCL) is HIGH determines a STOP condition. All operations must be ended with a STOP condition.4.4Data Valid (D)The state of the data line represents valid data when,after a ST ART condition, the data line is stable for the duration of the HIGH period of the clock signal.The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data.Each data transfer is initiated with a ST ART condition and terminated with a STOP condition. The number of the data bytes transferred between the ST ART and STOP conditions is determined by the master device.4.5AcknowledgeEach receiving device, when addressed, is obliged to generate an acknowledge signal after the reception of each byte. The master device must generate an extra clock pulse which is associated with this acknowledge bit.A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course,setup and hold times must be taken into account. Dur-ing reads, a master must signal an end of data to the slave by NOT generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave (24LC32A) will leave the data line HIGH to enable the master to generate the STOP condition.(See Figure 4-2)元器件交易网24LC32A MODULE5.0DEVICE ADDRESSINGA control byte is the first byte received following the start condition from the master device. (See Figure 5-1) The control byte consists of a four bit control code;for the 24LC32A this is set as 1010 binary for read and write operations. The next three bits are device select bits on standard devices, however, for micromodules,these must be zeros. The last bit of the control byte defines the operation to be performed. When set to a one a read operation is selected, and when set to a zero a write operation is selected. The next two bytesreceived define the address of the first data byte (see Figure 5-2). Because only A11...A0 are used, the upper four address bits must be zeros. The most signif-icant bit of the most significant byte of the address is transferred first.Following the start condition, the 24LC32A monitors the SDA bus checking the device type identifier being transmitted. Upon receiving a valid control byte, the slave device outputs an acknowledge signal on the SDA line. Depending on the state of the R/W bit, the 24LC32A will select a read or write operation元器件交易网24LC32A MODULE6.0WRITE OPERATIONS6.1Byte WriteFollowing the start condition from the master, the con-trol code (four bits), the device select (three bits), and the R/W bit which is a logic low are clocked onto the bus by the master transmitter. This indicates to the addressed slave receiver that a byte with a word address will follow after it has generated an acknowl-edge bit during the ninth clock cycle. Therefore the next byte transmitted by the master is the high-order byte of the word address and will be written into the address pointer of the 24LC32A MODULE. The next byte is the least significant address byte. After receiving another acknowledge signal from the 24LC32A the master device will transmit the data word to be written into the addressed memory location.The 24LC32A acknowledges again and the master generates a stop condition. This initiates the internal write cycle, and during this time the 24LC32A will not generate acknowledge signals (see Figure 6-1).6.2Page WriteThe write control byte, word address and the first data byte are transmitted to the 24LC32A in the same way as in a byte write. But instead of generating a stop con-dition, the master transmits up to 32 bytes which are temporarily stored in the on-chip page buffer and will be written into memory after the master has transmitted a stop condition. After receipt of each word, the five lower address pointer bits are internally incremented by one.If the master should transmit more than 32 bytes prior to generating the stop condition, the address counter will roll over and the previously received data will be overwritten. As with the byte write operation, once the stop condition is received, an internal write cycle will begin. (see Figure 6-2).元器件交易网24LC32A MODULE7.0ACKNOWLEDGE POLLINGSince the device will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write com-mand has been issued from the master, the device ini-tiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the master send-ing a start condition followed by the control byte for a write command (R/W = 0). If the device is still busy with the write cycle, then no ACK will be returned. If the cycle is complete, then the device will return the ACK and the master can then proceed with the next read or write command. See Figure 7-1 for flow diagram.FIGURE 7-1:ACKNOWLEDGE POLLING8.0READ OPERATIONRead operations are initiated in the same way as write operations with the exception that the R/W bit of the slave address is set to one. There are three basic types of read operations: current address read, random read,and sequential read.8.1Current Address ReadThe 24LC32A contains an address counter that main-tains the address of the last word accessed, internally incremented by one. Therefore, if the previous access (either a read or write operation) was to address n (n is any legal address), the next current address read oper-ation would access data from address n + 1. Upon receipt of the slave address with R/W bit set to one, the 24LC32A issues an acknowledge and transmits the eight bit data word. The master will not acknowledge the transfer but does generate a stop condition and the 24LC32A discontinues transmission (see Figure 8-1).8.2Random ReadRandom read operations allow the master to access any memory location in a random manner. T o perform this type of read operation, first the word address must be set. This is done by sending the word address to the 24LC32A as part of a write operation (R/W bit set to 0).After the word address is sent, the master generates a start condition following the acknowledge. This termi-nates the write operation, but not before the internal address pointer is set. Then the master issues the con-trol byte again but with the R/W bit set to a one. The 24LC32A will then issue an acknowledge and transmit the eight bit data word. The master will not acknowl-edge the transfer but does generate a stop condition which causes the 24LC32A to discontinue transmis-sion (see Figure 8-2).元器件交易网24LC32A MODULE8.3Sequential ReadSequential reads are initiated in the same way as a ran-dom read except that after the 24LC32A transmits the first data byte, the master issues an acknowledge as opposed to the stop condition used in a random read.This acknowledge directs the 24LC32A to transmit the next sequentially addressed 8 bit word (see Figure 8-3). Following the final byte transmitted to the master,the master will NOT generate an acknowledge but will generate a stop condition.To provide sequential reads the 24LC32A contains an internal address pointer which is incremented by one at the completion of each operation. This address pointer allows the entire memory contents to be serially read during one operation. The internal address pointer will automatically roll over from address 0FFF to address 000 if the master acknowledges the byte received from the array address 0FFF .元器件交易网24LC32A MODULE9.0SHIPPING METHODThe micromodules will be shipped to customers in clear plastic trays. Each tray holds 150 modules, and the trays can be stacked in a manner similar to shipping die in waffle packs. A tray drawing with dimensions is shown in Figure 9-1.元器件交易网24LC32A MODULE元器件交易网24LC32A MODULENOTES:元器件交易网24LC32A MODULENOTES:元器件交易网24LC32A MODULENOTES:元器件交易网24LC32A MODULE24LC32A MODULE PRODUCT IDENTIFICATION SYSTEMT o order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.Sales and SupportData SheetsProducts supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recom-mended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:1.Y our local Microchip sales office.2.The Microchip Corporate Literature Center U.S. FAX: (602) 786-7277.3.The Microchip’s Bulletin Board, via your local CompuServe number (CompuServe membership NOT required).Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.元器件交易网MAll rights reserved. © 1997, Microchip T echnology Incorporated, USA. 9/97 Printed on recycled paper.元器件交易网。

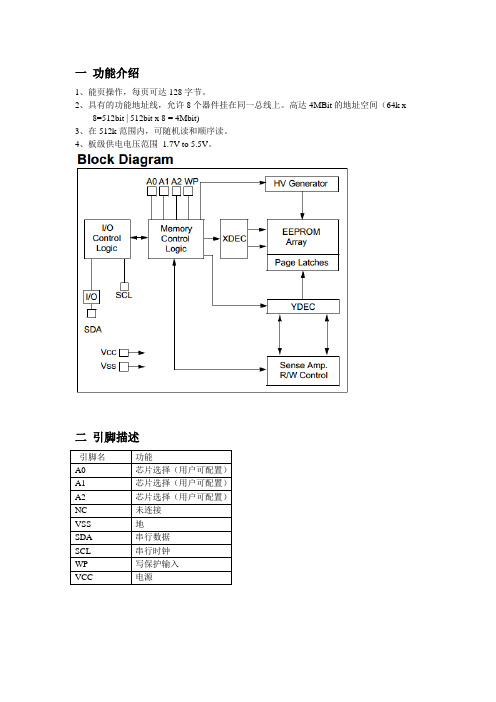

24LCXX eeprom

一功能介绍1、能页操作,每页可达128字节。

2、具有的功能地址线,允许8个器件挂在同一总线上。

高达4MBit的地址空间(64k x8=512bit | 512bit x 8 = 4Mbit)3、在512k范围内,可随机读和顺序读。

4、板级供电电压范围1.7V to 5.5V。

二引脚描述引脚名功能A0 芯片选择(用户可配置)A1 芯片选择(用户可配置)A2 芯片选择(用户可配置)NC 未连接VSS 地SDA 串行数据SCL 串行时钟WP 写保护输入VCC 电源2.0 A0,A1 AND A2 芯片地址输入⏹芯片地址引脚允许8个芯片挂在同一条总线上。

当引脚的逻辑电平与芯片内部相应的设备地址相同时,芯片使能。

⏹芯片引脚的输入使能时VCC 和VSS⏹在大多数的应用中,地址线是被硬件拉高和拉低的。

在那些引脚受microcontroller 和可编程器件控制的应用中,在访问该EEPROM芯片之前,EEPROM的引脚要先拉高或拉低。

2.1 Serial Data (SDA)⏹该双向引脚是用来传输数据和地址的。

该引脚是内部开漏,所以SDA引脚要接一个上拉电阻到VCC( 典型的是10kohm/100khz, 2kohm/400Khz,1Mhz).⏹在数据传输中,SDA只有在SCL线为低时才发生改变。

在SCL线为高时SDA发生改变则被认为是开始或停止。

2.2 Serial Clock (SCL)数据同步时钟2.3 Write-Protect(WP) 写保护⏹该引脚只能连接VCC 或者VSS。

⏹当连接VCC时,允许对芯片写操作,当连接VSS,对芯片写操作禁止。

该引脚对芯片读操作没有任何影响。

三功能描述⏹24XX512支持双向2线制总线和数据传输协议。

在总线数据发送数据的成为发送方,接收数据的为接收方。

⏹当24XX512为从设备时,串行时钟(SCL)由主设备产生,来控制总线的访问和产生开始和结束条件。

⏹主设备和从设备都可以作为接收方和发送方,但是只有主设备才能决定处于那种模式。

24LC256IP中文资料

-40°C to +85°C

- Automotive (E):

-40°C to +125°C

DESCRIPTION

The Microchip Technology Inc. 24AA256/24LC256 (24xx256*) is a 32K x 8 (256K bit) Serial Electrically Erasable PROM, capable of operation across a broad voltage range (1.8V to 5.5V). It has been developed for advanced, low power applications such as personal communications or data acquisition. This device also has a page-write capability of up to 64 bytes of data. This device is capable of both random and sequential reads up to the 256K boundary. Functional address lines allow up to eight devices on the same bus, for up to 2 Mbit address space. This device is available in the standard 8-pin plastic DIP, and 8-pin SOIC (208 mil) packages.

- Standby current 100 nA typical at 5.5V

• 2-wire serial interface bus, I2C compatible

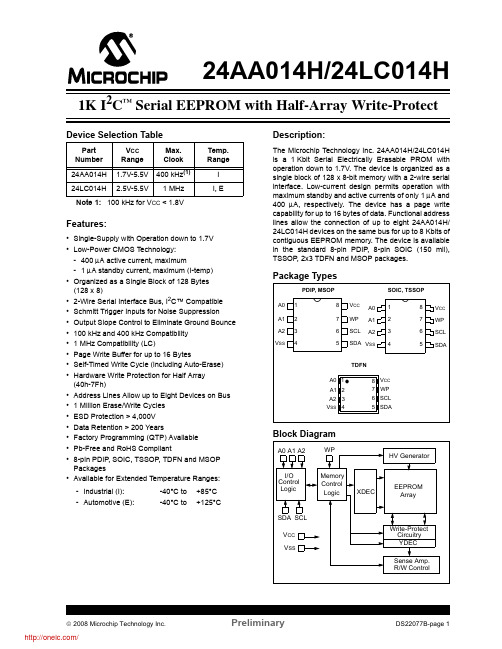

24AA014H-ISN;24LC014H-IMS;24LC014HT-IMNY;24AA014HT-IMNY;24AA014H-IP;中文规格书,Datasheet资料

24AA014H/24LC014HDevice Selection TableFeatures:•Single-Supply with Operation down to 1.7V •Low-Power CMOS Technology:-400 μA active current, maximum- 1 μA standby current, maximum (I-temp)•Organized as a Single Block of 128 Bytes(128 x 8)•2-Wire Serial Interface Bus, I2C™ Compatible •Schmitt Trigger Inputs for Noise Suppression •Output Slope Control to Eliminate Ground Bounce •100 kHz and 400 kHz Compatibility• 1 MHz Compatibility (LC)•Page Write Buffer for up to 16 Bytes•Self-Timed Write Cycle (including Auto-Erase)•Hardware Write Protection for Half Array(40h-7Fh)•Address Lines Allow up to Eight Devices on Bus • 1 Million Erase/Write Cycles•ESD Protection > 4,000V•Data Retention > 200 Years•Factory Programming (QTP) Available•Pb-Free and RoHS Compliant•8-pin PDIP, SOIC, TSSOP, TDFN and MSOP Packages•Available for Extended Temperature Ranges:Description:The Microchip Technology Inc. 24AA014H/24LC014H is a 1Kbit Serial Electrically Erasable PROM with operation down to 1.7V. The device is organized as a single block of 128 x8-bit memory with a 2-wire serial interface. Low-current design permits operation with maximum standby and active currents of only 1 μA and 400 μA, respectively. The device has a page write capability for up to 16 bytes of data. Functional address lines allow the connection of up to eight 24AA014H/ 24LC014H devices on the same bus for up to 8Kbits of contiguous EEPROM memory. The device is available in the standard 8-pin PDIP, 8-pin SOIC (150 mil), TSSOP, 2x3 TDFN and MSOP packages. Package TypesBlock DiagramPart NumberV CCRangeMax.ClockTemp.Range24AA014H 1.7V-5.5V400kHz(1)I 24LC014H 2.5V-5.5V 1 MHz I, E Note1:100 kHz for V CC < 1.8V-Industrial (I):-40°C to+85°C -Automotive (E):-40°C to+125°CA0A1A2V SSV CCWPSCLSDA12348765PDIP, MSOP SOIC, TSSOPA0A1A2V SS12348765V CCWPSCLSDATDFNA0A1A2V SSWPSCLSDAV CC87651234I/OControlLogicMemoryControlLogic XDECHV GeneratorEEPROMArrayWrite-ProtectCircuitryYDEC V CCV SSSense Amp.R/W ControlSDA SCLA0 A1 A2WP1K I2C™ Serial EEPROM with Half-Array Write-Protect© 2008 Microchip Technology Inc.Preliminary DS22077B-page 124AA014H/24LC014HDS22077B-page 2Preliminary© 2008 Microchip Technology Inc.1.0ELECTRICAL CHARACTERISTICSAbsolute Maximum Ratings (†)V CC .............................................................................................................................................................................6.5V All inputs and outputs w.r.t. V SS .........................................................................................................-0.6V to V CC +1.0V Storage temperature ...............................................................................................................................-65°C to +150°C Ambient temperature with power applied................................................................................................-40°C to +125°C ESD protection on all pins ......................................................................................................................................................≥ 4 kV † NOTICE : Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.TABLE 1-1:DC CHARACTERISTICSAll parameters apply across the specified operating ranges unless otherwise noted.Electrical Characteristics:Industrial (I):V CC = +1.7V to 5.5V T A = -40°C to +85°C Automotive (E):V CC = +2.5V to 5.5V T A = -40°C to +125°CParameterSymbol Min.Max.Units ConditionsSCL and SDA pins:High-level input voltage V IH 0.7 V CC—V Low-level input voltageV IL —0.3 V CCV Hysteresis of Schmitt Trigger inputs V HYS 0.05 V CC—V (Note 1)Low-level output voltage V OL —0.40V I OL = 3.0 mA, V CC = 4.5V I OL = 2.1 mA, V CC = 2.5V Input leakage current I LI —±1μΑV IN = V SS or V CC , WP = Vss Output leakage currentI LO —±1μA V OUT = V SS or V CC Pin capacitance (all inputs/outputs)C IN , C OUT —10pF V CC = 5.0V (Note 1)T A = 25°C, f = 1 MHz Operating current I CC Read —400μA V CC = 5.5V, SCL = 400 kHz I CC Write —3mA V CC = 5.5VStandby currentI CCS—1μAV CC = 5.5V, SDA = SCL = V CC WP = V SS , A0, A1, A2 = V SS Note 1:This parameter is periodically sampled and not 100% tested.24AA014H/24LC014H TABLE 1-2:AC CHARACTERISTICSAC CHARACTERISTICS Electrical Characteristics:Industrial (I):V CC = +1.7V to 5.5V T A = -40°C to +85°C Automotive (E):V CC = +2.5V to 5.5V T A = -40°C to +125°CParam.No.Symbol Characteristic Min.Max.Units Conditions1F CLK Clock frequency———1004001000kHz 1.7V ≤ V CC < 1.8V1.8V ≤ V CC≤ 5.5V2.5V ≤ V CC≤ 5.5V (24LC014H)2T HIGH Clock high time4000600500———ns 1.7V ≤ V CC < 1.8V1.8V ≤ V CC≤ 5.5V2.5V ≤ V CC≤ 5.5V (24LC014H)3T LOW Clock low time47001300500———ns 1.7V ≤ V CC < 1.8V1.8V ≤ V CC≤ 5.5V2.5V ≤ V CC≤ 5.5V (24LC014H)4T R SDA and SCL rise time (Note1)———1000300300ns 1.7V ≤ V CC < 1.8V1.8V ≤ V CC≤ 5.5V2.5V ≤ V CC≤ 5.5V (24LC014H)5T F SDA and SCL fall time (Note1)———1000300300ns 1.7V ≤ V CC < 1.8V1.8V ≤ V CC≤ 5.5V2.5V ≤ V CC≤ 5.5V (24LC014H)6T HD:STA Start condition hold time4000600250———ns 1.7V ≤ V CC < 1.8V1.8V ≤ V CC≤ 5.5V2.5V ≤ V CC≤ 5.5V (24LC014H)7T SU:STA Start condition setup time4700600250———ns 1.7V ≤ V CC < 1.8V1.8V ≤ V CC≤ 5.5V2.5V ≤ V CC≤ 5.5V (24LC014H)8T HD:DAT Data input hold time0—ns(Note2)9T SU:DAT Data input setup time250100100———ns 1.7V ≤ V CC < 1.8V1.8V ≤ V CC≤ 5.5V2.5V ≤ V CC≤ 5.5V (24LC014H)10T SU:STO Stop condition setup time4000600250———ns 1.7V ≤ V CC < 1.8V1.8V ≤ V CC≤ 5.5V2.5V ≤ V CC≤ 5.5V (24LC014H)11T SU:WP WP setup time4000600600———ns 1.7V ≤ V CC < 1.8V1.8V ≤ V CC≤ 5.5V2.5V ≤ V CC≤ 5.5V (24LC014H)12T HD:WP WP hold time4700600600———ns 1.7V ≤ V CC < 1.8V1.8V ≤ V CC≤ 5.5V2.5V ≤ V CC≤ 5.5V (24LC014H)13T AA Output valid from clock (Note2)———3500900400ns 1.7V ≤ V CC < 1.8V1.8V ≤ V CC≤ 5.5V2.5V ≤ V CC≤ 5.5V (24LC014H)14T BUF Bus free time: Time the bus mustbe free before a new transmissioncan start 130047004700———ns 1.7V ≤ V CC < 1.8V1.8V ≤ V CC≤ 5.5V2.5V ≤ V CC≤ 5.5V (24LC014H)16T SP Input filter spike suppression(SDA and SCL pins)—50ns24AA014H(Note1 and Note3)17T WC Write cycle time (byte or page)—5ms—18—Endurance1M—cycles25°C, V CC = 5.5V, Block mode(Note4)Note1:Not 100% tested. C B = total capacitance of one bus line in pF.2:As a transmitter, the device must provide an internal minimum delay time to bridge the undefined region (minimum 300ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.3:The combined T SP and V HYS specifications are due to new Schmitt Trigger inputs, which provide improved noise spike suppression. This eliminates the need for a T I specification for standard operation.4:This parameter is not tested but ensured by characterization. For endurance estimates in a specific application, please consult the Total Endurance™ Model which can be obtained from Microchip’s web site at .© 2008 Microchip Technology Inc.Preliminary DS22077B-page 324AA014H/24LC014HDS22077B-page 4Preliminary© 2008 Microchip Technology Inc.FIGURE 1-1:BUS TIMING DATA(unprotected)(protected)SCL SDA InSDA OutWP 57616328913D441011121424AA014H/24LC014H2.0PIN DESCRIPTIONSThe descriptions of the pins are listed in Table2-1.TABLE 2-1:PIN FUNCTION TABLE2.1SDA Serial DataThis is a bidirectional pin used to transfer addresses and data into and out of the device. It is an open drain terminal. Therefore, the SDA bus requires a pull-up resistor to V CC (typical 10 kΩ for 100 kHz, 2 kΩ for 400kHz).For normal data transfer SDA is allowed to change only during SCL low. Changes during SCL high are reserved for indicating the Start and Stop conditions.2.2SCL Serial ClockThe SCL input is used to synchronize the data transfer to and from the device.2.3A0, A1, A2The A0, A1 and A2 inputs are used by the 24AA014H/ 24LC014H for multiple device operations. The levels on these inputs are compared with the corresponding bits in the slave address. The chip is selected if the compare is true.Up to eight 24AA014H/24LC014H devices may be connected to the same bus by using different Chip Select bit combinations. These inputs must be connected to either V CC or V SS.In most applications, the chip address inputs A0, A1 and A2 are hard-wired to logic ‘0’ or logic ‘1’. For applications in which these pins are controlled by a microcontroller or other programmable device, the chip address pins must be driven to logic ‘0’ or logic ‘1’before normal device operation can proceed.2.4WPWP is the hardware write-protect pin. It must be tied to V CC or V SS. If tied to V CC, the hardware write protection is enabled and will protect half of the array (40h-7Fh). If the WP pin is tied to V SS the hardware write protection is disabled.2.5Noise ProtectionThe 24AA014H/24LC014H employs a V CC threshold detector circuit that disables the internal erase/write logic if the V CC is below 1.5 volts at nominal conditions. The SCL and SDA inputs have Schmitt Trigger and filter circuits that suppress noise spikes to assure proper device operation even on a noisy bus.Name 8-pinPDIP8-pinSOIC8-pinTSSOP8-pinMSOP8-pinTDFNFunctionA011111User Configurable Chip SelectA122222User Configurable Chip SelectA233333User Configurable Chip SelectV SS44444GroundSDA55555Serial DataSCL66666Serial ClockWP77777Write-Protect InputV CC88888+1.7V to 5.5V (24AA014H)+2.5V to 5.5V (24LC014H)© 2008 Microchip Technology Inc.Preliminary DS22077B-page 524AA014H/24LC014HDS22077B-page 6Preliminary© 2008 Microchip Technology Inc.3.0FUNCTIONAL DESCRIPTIONThe 24AA014H/24LC014H supports a bidirectional,2-wire bus and data transmission protocol. A device that sends data onto the bus is defined as transmitter,and a device receiving data as receiver. The bus has to be controlled by a master device that generates the Serial Clock (SCL), controls the bus access and gen-erates the Start and Stop conditions while the 24AA014H/24LC014H works as slave. Both master and slave can operate as transmitter or receiver, but the master device determines which mode is activated.4.0BUS CHARACTERISTICSThe following bus protocol has been defined:•Data transfer may be initiated only when the bus is not busy.•During data transfer, the data line must remain stable whenever the clock line is high. Changes in the data line while the clock line is high will be interpreted as a Start or Stop condition.Accordingly, the following bus conditions have been defined (Figure 4-1).4.1Bus Not Busy (A)Both data and clock lines remain high.4.2Start Data Transfer (B)A high-to-low transition of the SDA line while the clock (SCL) is high determines a Start condition. All commands must be preceded by a Start condition.4.3Stop Data Transfer (C)A low-to-high transition of the SDA line while the clock (SCL) is high determines a Stop condition. All operations must be ended with a Stop condition.4.4Data Valid (D)The state of the data line represents valid data when,after a Start condition, the data line is stable for the duration of the high period of the clock signal.The data on the line must be changed during the low period of the clock signal. There is one bit of data per clock pulse.Each data transfer is initiated with a Start condition and terminated with a Stop condition. The number of the data bytes transferred between the Start and Stop conditions is determined by the master device and is,theoretically, unlimited, though only the last sixteen will be stored when doing a write operation. When an overwrite does occur, it will replace data in a first-in first-out fashion.4.5AcknowledgeEach receiving device, when addressed, is required to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse which is associated with this Acknowledge bit.The device that acknowledges has to pull down the SDA line during the Acknowledge clock pulse in such a way that the SDA line is stable low during the high period of the acknowledge-related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an Acknowledge bit on the last byte that has been clocked out of the slave. In this case,the slave must leave the data line high to enable the master to generate the Stop condition (Figure 4-2).Note:The 24AA014H/24LC014H does not gen-erate any Acknowledge bits if an internal programming cycle is in progress.24AA014H/24LC014H© 2008 Microchip Technology Inc.Preliminary DS22077B-page 724AA014H/24LC014HDS22077B-page 8Preliminary© 2008 Microchip Technology Inc.5.0DEVICE ADDRESSINGA control byte is the first byte received following the Start condition from the master device (Figure 5-1).The control byte consists of a four-bit control code; for the 24AA014H/24LC014H this is set as ‘1010’ binary for read and write operations. The next three bits of the control byte are the Chip Select bits (A2, A1, A0). The Chip Select bits allow the use of up to eight 24AA014H/24LC014H devices on the same bus and are used to select which device is accessed. The Chip Select bits in the control byte must correspond to the logic levels on the corresponding A2, A1 and A0 pins for the device to respond. These bits are in effect the three Most Significant bits of the word address.The last bit of the control byte defines the operation to be performed. When set to a ‘1’, a read operation is selected. When set to a ‘0’, a write operation is selected. Following the Start condition, the 24AA014H/24LC014H monitors the SDA bus, checking the control byte being transmitted. Upon receiving a ‘1010’ code and appropriate Chip Select bits, the slave device outputs an Acknowledge signal on the SDA line.24LC014H will select a read or write operation.FIGURE 5-1:CONTROL BYTE FORMAT5.1Contiguous Addressing Across Multiple DevicesThe Chip Select bits A2, A1 and A0 can be used to expand the contiguous address space for up to 8K bits by adding up to eight 24AA014H/24LC014H devices on the same bus. In this case, software can use A0 of the control byte as address bit A8, A1 as address bit A9,and A2 as address bit A10. It is not possible to sequentially read across device boundaries.11A2A1A0SACKR/W Control CodeChip SelectBits Slave AddressAcknowledge BitStart BitRead/Write Bit© 2008 Microchip Technology Inc.PreliminaryDS22077B-page 924AA014H/24LC014H6.0WRITE OPERATIONS6.1Byte WriteFollowing the Start signal from the master, the device code(4 bits), the Chip Select bits (3 bits) and the R/W bit (which is a logic low) are placed onto the bus by the master transmitter. The device will acknowledge this control byte during the ninth clock pulse. The next byte transmitted by the master is the word address and will be written into the Address Pointer of the 24AA014H/24LC014H. After receiving another Acknowledge signal from the 24AA014H/24LC014H, the master device will transmit the data word to be written into the addressed memory location. The 24AA014H/24LC014H acknowledges again and the master generates a Stop condition. This initiates the internal write cycle and the 24AA014H/24LC014H will not generate Acknowledge signals during this time (Figure 6-1). If an attempt is made to write to the protected portion of the array when the hardware write protection has been enabled, the device will acknowledge the command, but no data will be written.The write cycle time must be observed even if write protection is enabled.6.2Page WriteThe write-control byte, word address and the first data byte are transmitted to the 24AA014H/24LC014H in the same way as in a byte write. But instead of generating a Stop condition, the master transmits up to 15additional data bytes to the 24AA014H/24LC014H that are temporarily stored in the on-chip page buffer and will be written into the memory once the master has transmitted a Stop condition. Upon receipt of each word, the four lower order Address Pointer bits are internally incremented by one.The higher order four bits of the word address remain constant. If the master should transmit more than 16bytes prior to generating the Stop condition, the address counter will roll over and the previously received data will be overwritten. As with the byte write operation, once the Stop condition is received, an internal write cycle will begin (Figure 6-2). If an attempt is made to write to the protected portion of the array when the hardware write protection has been enabled,the device will acknowledge the command, but no data will be written. The write cycle time must be observed even if write protection is enabled.6.3Write ProtectionThe WP pin must be tied to V CC or V SS . If tied to V CC ,half of the array will be write-protected (40h-7Fh). If the WP pin is tied to V SS , write operations to all address locations are allowed.FIGURE 6-1:BYTE WRITEFIGURE 6-2:PAGE WRITENote:Page write operations are limited to writing bytes within a single physical page,regardless of the number of bytes actually being written. Physical page boundaries start at addresses that are integer multiples of the page buffer size (or ‘page size’) and end at addresses that are integer multiples of [page size – 1]. If a Page Write command attempts to write across a physical page boundary, the result is that the data wraps around to the beginning of the current page (overwriting data previously stored there), instead of being written to the next page, as might be expected. It is therefore necessary that the application software prevent page write operations that would attempt to cross a page boundary.SPBus Activity Master SDA Line Bus ActivityS T A R T S T O P Control ByteWord AddressDataA C KA C KA C KSPBus Activity Master SDA Line Bus ActivityS T A R T Control ByteWord Address (n)Data (n)Data (n + 15)S T O P A C KA C KA C KA C KA C KData (n +1)24AA014H/24LC014HDS22077B-page 10Preliminary© 2008 Microchip Technology Inc.7.0ACKNOWLEDGE POLLINGSince the device will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the Stop condition for a write command has been issued from the master, the device initiates the internally-timed write cycle and ACK polling can be initiated immediately. This involves the master sending a Start condition followed by the control byte for a Write command (R/W = 0). If the device is still busy with the write cycle, no ACK will be returned. If no ACK is returned, the Start bit and control byte must be re-sent. If the cycle is complete, the device will return the ACK and the master can then proceed with the next Read or Write command. See Figure 7-1 for a flow diagram of this operation.FIGURE 7-1:ACKNOWLEDGE POLLING FLOWSendWrite CommandSend Stop Condition to Initiate Write CycleSend StartSend Control Byte with R/W = 0Did Device Acknowledge (ACK = 0)?Next OperationNoYes分销商库存信息:MICROCHIP24AA014H-I/SN24LC014H-I/MS24LC014HT-I/MNY 24AA014HT-I/MNY24AA014H-I/P24AA014HT-I/SN 24LC014HT-I/SN24AA014H-I/MS24LC014H-I/ST24AA014H-I/ST24AA014HT-I/MS24AA014HT-I/ST 24LC014HT-I/MS24LC014HT-I/ST24LC014H-E/SN24LC014HT-E/SN24LC014H-E/MS24LC014H-E/ST24LC014HT-E/ST24LC014HT-E/MS24LC014HT-E/MNY 24LC014H-E/P24LC014H-I/SN24LC014H-I/P。

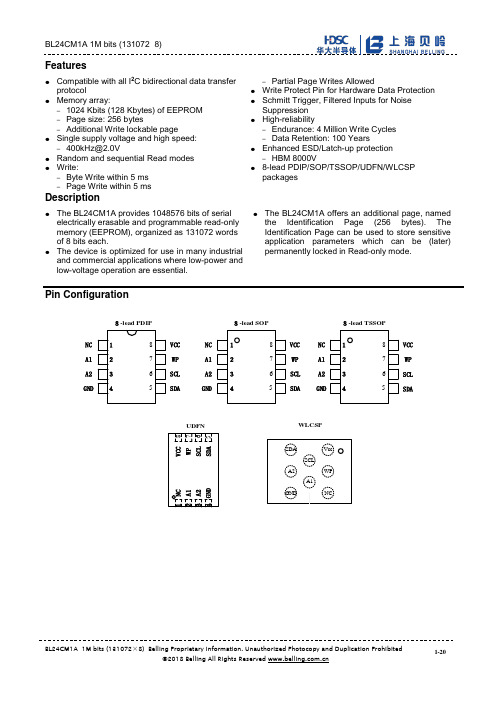

Belling BL24CM1A 1M位 EEPROM 产品说明书