AS3693C-ZTQT;中文规格书,Datasheet资料

LTC3706EGN#PBF;LTC3706EGN#TRPBF;LTC3706IGN#PBF;LTC3706IGN#TRPBF;中文规格书,Datasheet资料

13706fdTYPICAL APPLICATIONDESCRIPTIONForward Controller with PolyPhase CapabilityThe L TC ®3706 is a PolyPhase capable secondary-side controller for synchronous forward converters. When used in conjunction with the L TC3705 gate driver and primary-side controller , the part creates a complete isolated power supply that combines the power of PolyPhase operation with the speed of secondary-side control.The L TC3706 has been designed to simplify the design of highly efficient, secondary-side forward converters. Working in concert with the L TC3705, the L TC3706 forms a robust, self-starting converter that eliminates the need for the separate bias regulator that is commonly used in secondary-side control applications. In addition, a pro-prietary scheme is used to multiplex gate drive signals and DC bias power across the isolation barrier through a single, tiny pulse transformer .The L TC3706 provides remote sensing, accurate power good and overvoltage monitoring circuits to support preci-sion, high current applications. A linear regulator controller with thermal protection is also provided to simplify the generation of secondary-side bias voltage.The L TC3706 is available in a 24-lead SSOP package.36V-72V to 3.3V/20A Isolated Forward ConverterFEATURESAPPLICATIONSnIsolated 48V Telecommunication Systems n Internet Servers and Routersn Distributed Power Step-Down Converters nAutomotive and Heavy EquipmentnSecondary-Side Control for Fast T ransient Response n Self-Starting Architecture Eliminates Need for Separate Bias Regulatorn Proprietary Gate Drive Encoding Scheme Reduces System Complexityn PolyPhase ® Operation Reduces C INRequirements n Current Mode Control Ensures Current Sharing n PLL Fixed Frequency: 100kHz to 500kHz n ±1% Output Voltage Accuracy n T rue Remote Sense Differential Amplifier n Power Good Output Voltage Monitor n High Voltage Linear Regulator Controller n Wide Supply Range: 5V to 30Vn Available in a Narrow 24-Lead SSOP PackageV IN –V IN +3OUT –OUT +L , L T , L TC, L TM, PolyPhase, Burst Mode, Linear Technology and the Linear logo are registered trademarks and No R SENSE and ThinSOT are trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents including 6144194, other patents pending./23706fdPIN CONFIGURATIONABSOLUTE MAXIMUM RATINGSV CC ........................................................... –0.3V to 10V V IN ........................................................... –0.3V to 33V SW ............................................................... –5V to 50V NDRV ......................................................... –0.3V to 13V ITH, RUN/SS, V SOUT , V S +, V S –, REGSD ....... –0.3V to 7VAll Other Pins ............................................ –0.3V to 10VOperating Temperature Range (Note 2) LTC3706E GN .......................................–40°C to 85°C LTC3706IGN ........................................–40°C to 85°C Junction Temperature (Note 3) ............................ 125°C Storage Temperature Range ..................–65°C to 150°C Lead Temperature (Soldering, 10 sec) ...................300°C(Note 1)ORDER INFORMATIONLEAD FREE FINISH TAPE AND REEL PART MARKING PACKAGE DESCRIPTION TEMPERATURE RANGE L TC3706EGN#PBF L TC3706EGN#TRPBF L TC3706EGN 24-Lead Plastic SSOP –40°C to 85°C L TC3706IGN#PBF L TC3706IGN#TRPBF L TC3706IGN 24-Lead Plastic SSOP –40°C to 85°C LEAD BASED FINISH TAPE AND REEL PART MARKING PACKAGE DESCRIPTION TEMPERATURE RANGE L TC3706EGN L TC3706EGN#TR L TC3706EGN 24-Lead Plastic SSOP –40°C to 85°C L TC3706IGNL TC3706IGN#TRL TC3706IGN24-Lead Plastic SSOP–40°C to 85°CConsult L TC Marketing for parts specified with wider operating temperature ranges.For more information on lead free part marking, go to: http://www.linear .com/leadfree/For more information on tape and reel specifications, go to: http://www.linear .com/tapeandreel//ELECTRICAL CHARACTERISTICSThel indicates specifications which apply over the full operating temperature range, otherwise specifications are at T A = 25°C. V CC = 7V, V IN = 15V, GND = PGND = 0V, unless otherwise noted.SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS Main Control LoopV FB Regulated Feedback Voltage(Note 4) ITH = 1.2V l0.5940.6000.606V I FB Feedback Input Current(Note 4)2100nA ∆V FB(LINREG)Feedback Voltage Line Regulation V IN = 6V to 30V, ITH = 1.2V0.001%/V ∆V FB(LOADREG)Feedback Voltage Load Regulation Measured in Servo Loop,ITH = 0.5V to 2Vl–0.01–0.1%V ISMAX Maximum Current Sense Threshold R SENSE Mode, 0V < V IS– < 5VV IS– = V CC, 0V < V IS+ < 2V (CT Mode)681.15781.28881.4mVVV ISOC Over-Current Shutdown Threshold R SENSE Mode, 0V < V IS– < 5VV IS– = V CC, 0V < V IS+ < 2V (CT Mode)871.451001.651131.85mVVg m T ransconductance Amplifier g m 2.40 2.75 3.10mS I RUN/SS(C)Soft-Start Charge Current V RUN/SS = 2V–4–5–6µA I RUN/SS(D)Soft-Start Discharge Current3µA V RUN/SS RUN/SS Pin On Threshold V RUN/SS Rising l0.40.450.5V t ON,MIN Minimum On-Time200ns FG, SG R UP FG, SG Driver Pull-Up On Resistance FG, SG Low 1.5 2.7ΩFG, SG R DOWN FG, SG Driver Pull-Down On Resistance FG, SG High 1.5 2.7ΩPT+, PT– R UP PT+, PT– Driver Pull-Up Resistance PT+, PT– Low 1.5 2.7ΩPT+, PT– R DOWN PT+, PT– Driver Pull-Down Resistance PT+, PT– High 1.5 2.7Ω∆V FB(OV)Output Overvoltage Threshold V FB Rising151719% V CC SupplyV CCOP Operating Voltage Range510V V CCREG Regulated Output Voltage 6.67.07.4VI CC Supply CurrentOperatingShutdown f OSC = 200kHz (Note 5)V RUN/SS = GND4.2240mAµAV UVLO UV Lockout V CC Rising l 4.52 4.60 4.70V V HYS UV Hysteresis0.4V V IN SupplyV INOP Operating Voltage Range530VI IN Supply CurrentNormal ModeShutdown f OSC = 200kHzV RUN/SS = GND900460µAµAV INUVLO UV Lockout V IN Rising l 3.90 4.30 4.51V V INHYS0.2V V REGSD REGSD Shutdown Threshold V REGSD Rising4Vg m,REGSD REGSD T ransconductance5µS /33706fd43706fdELECTRICAL CHARACTERISTICS Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.Note 2: The L TC3706E is guaranteed to meet the performance specifica-tions over the 0°C to 85°C operating temperature range. Specifications over the –40°C to 85°C operating temperature range are assured by design, characterization and correlation with statistical process controls. The L TC3706I is guaranteed and tested over the full –40°C to 85°C operating temperature range.Note 3: Junction temperature T J (in °C) is calculated from the ambient tem-perature T A and the average power dissipation P D (in Watts) by the formula: T J = T A + θJA • P DRefer to the Applications Information section for details.Note 4: The L TC3706 is tested in a feedback loop that servos V FB to a voltage near the internal 0.6V reference voltage to obtain the specified ITH voltage (V ITH = 1.2V).Note 5: Operating supply current is measured in test mode. Dynamic supply current is higher due to the internal gate charge being delivered at the switching frequency. See the Typical Performance Characteristics section.SYMBOL PARAMETERCONDITIONSMINTYP MAXUNITSOscillator and Phase-Locked LoopI FS FS/SYNC Pin Sourcing Current 20µA f LOW Oscillator Low Frequency Set Point V FS/SYNC = GND 165200235kHz f HIGH Oscillator High Frequency Set Point V FS/SYNC = VCC247300353kHz ∆f (R FS )Oscillator Resistor Set Accuracy 75kΩ < R FS/SYNC < 175kΩ–2220%f PLL(MAX)Maximum PLL Sync Frequency 500kHz f PLL(MIN)Minimum PLL Sync Frequency75kHzPGOOD Output V FBH /0.6Power Good Upper Threshold V FB Rising 115117119%V FBL1/0.6Power Good Lower Threshold V FB Rising 91.59394.5%V FBL2/0.6Power Good Lower Threshold V FB Falling89.59192.5%Differential Amplifier (V SENSE AMP)ADA GainV S – = GND, 1V ≤ V S + ≤ 5V0.9901 1.010V/V CMRR DA Common Mode Rejection Ratio 75dB R IN Input Resistance 80kΩf BW–3dB Bandwidth3MHzThe l indicates specifications which apply over the full operatingtemperature range, otherwise specifications are at T A = 25°C. V CC = 7V, V IN = 15V, GND = PGND = 0V, unless otherwise noted./53706fdTYPICAL PERFORMANCE CHARACTERISTICSMaximum Current Sense RUN/SS ON Threshold Oscillator Frequency T A = 25°C, unless otherwise noted.Maximum Current Sense IS Pins Source Current V CC Supply Current V CC Regulator Output Voltage Maximum Current Sense /63706fdGate Driver On-Resistance TYPICAL PERFORMANCE CHARACTERISTICST A = 25°C, unless otherwise noted.Undervoltage Lockout REGSD Shutdown Threshold /PIN FUNCTIONSSG (Pin 1): Gate Drive for the “Synchronous” MOSFET. FG (Pin 2): Gate Drive for the “Forward” MOSFET. PGOOD (Pin 3): Open-Drain Power Good Output. The FBpin is monitored to ensure that the output is in regulation. When the output is not in regulation, the PGOOD pin is pulled low.MODE (Pin 4): Tie to either GND or V CC to set the maxi-mum duty cycle at either 50% or 75% respectively. Tie to ground through either a 200k or 100k resistor (50% or 75% maximum duty cycle) to disable pulse encoding. In this mode, normal PWM signals will be generated at the PT+ pin, while a clock signal is generated at the PT– pin. PHASE (Pin 5): Control Input to the Phase Selector. This pin determines the phasing of the controller CLK relative to the synchronizing signal at the FS/SYNC pin.FB (Pin 6): The Inverting Input of the Main Loop Error Amplifier.ITH (Pin 7): The Output of the Main Loop Error Amplifier. Place compensation components between the ITH pin and GND.RUN/SS (Pin 8): Combination Run Control and Soft-Start Inputs. A capacitor to ground sets the ramp time of the output voltage. Holding this pin below 0.4V causes the IC to shut down all internal circuitry.V SOUT, V S+, V S– (Pins 9, 10, 11): V SOUT is the output of a precision, unity-gain differential amplifier. Tie V S+ and V S– to the output of the main DC/DC converter to achieve true remote differential sensing. This allows DCR error effects to be minimized.GND (Pin 12): Signal Ground.FS/SYNC (Pin 13): Combination Frequency Set and SYNC pin. Tie to GND or V CC to run at 200kHz and 300kHz respectively. Place a single resistor to ground at this pin to set the frequency between 100kHz and 500kHz. To synchronize, drive this pin with a clock signal to achieve PLL synchronization from 75kHz to 500kHz. Sources 20µA of current.SLP (Pin 14): Slope Compensation Input. Place a single resistor to ground to set the desired amount of slope compensation.I S– (Pin 15): Negative Input to the Current Sense Circuit. When using current sense transformers, this pin may be tied to V CC for single-ended sensing with a 1.28V maximum current trip level.I S+ (Pin 16): Positive Input to the Current Sense Circuit. Connect to the positive end of a current sense resistor or to the output of a current sense transformer. REGSD (Pin 17):T his p in i s u sed t o p revent o verheating o f t he external linear regulator pass device that generates the V CC supply voltage from the V IN voltage. A current proportional to the voltage across the external pass device flows out of this pin. The IC shuts down the linear regulator when the voltage on this pin exceeds 4V. Place a resistor (or a resistor and capacitor in parallel) between this pin and GND to limit the temperature rise of the external pass device. NDRV (Pin 18): Drive Output for the External Pass Device of the V CC Linear Regulator. Connect to the base (NPN) or gate (NMOS) of an external N-type device.V IN (Pin 19): Connect to a higher voltage bias supply, typically the output of a peak detected bias winding. When not used, tie together with the V CC and NDRV pins.SW (Pin 20): Connect to the drain of the “synchronous” MOSFET. This input is used for adaptive shoot-through prevention and leading edge blanking.PT–, PT+ (Pins 21, 22): Pulse T ransformer Driver Outputs. For most applications, these connect to a pulse trans-former (with a series DC blocking capacitor). The PWM information is multiplexed together with DC power and sent through a single pulse transformer to the primary side. This information may be decoded by the L TC3705 gate driver and primary-side controller.PGND (Pin 23): Gate Driver Ground Pin.V CC (Pin 24): Main V CC Input for all Driver and Control Circuitry./73706fdBLOCK DIAGRAM83706fd/OPERATIONMain Control LoopThe L TC3706 is designed to work in a constant frequency, current mode 2-transistor forward converter. During normal operation, the primary-side MOSFETs (both top and bottom) are “clocked” on together with the forward MOSFET on the secondary side. This applies the reflected input voltage across the inductor on the secondary side. When the current in the inductor has ramped up to the peak value as commanded by the voltage on the ITH pin, the current sense comparator is tripped, turning off the primary-side and forward MOSFE Ts. To avoid turning on the synchronous MOSFET prematurely and causing shoot-through, the voltage on the SW pin is monitored. This voltage will usually fall below 0V soon after the primary-side MOSFETs have turned completely off. When this condition is detected, the synchronous MOSFET is quickly turned on, causing the inductor current to ramp back downwards. The error amplifier senses the output voltage, and adjusts the ITH voltage to obtain the peak current needed to maintain the desired main-loop output voltage. The L TC3706 always operates in a continuous current, synchronous switching mode. This ensures a rapid transient response as well as a stable bias supply voltage at light loads. A maximum duty cycle (either 50% or 75%) is internally set via clock dividers to prevent saturation of the main transformer. In the event of an overvoltage on the output, the synchronous MOSFET is quickly turned on to help protect critical loads from damage.Gate Drive EncodingSince the L TC3706 controller resides on the secondary side of an isolation barrier, communication to the primary-side power MOSFETs is generally done through a transformer. Moreover, it is often necessary to generate a low voltage bias supply for the primary-side gate drive circuitry. In order to reduce the number of isolated windings present in the system, the L TC3706 uses a proprietary scheme to encode the PWM gate drive information and multiplex it together with bias power for the primary-side drive and control, using a single pulse transformer. Note that, unlike optoisolators and other modulation techniques, this multiplexing scheme does not introduce a significant time delay into the system.For most forward converter applications, the PT+ and PT– outputs will contain a pulse-encoded PWM signal. These outputs are driven in a complementary fashion with an essentially constant 50% duty cycle. This results in a stable volt-second balance as well as an efficient transfer of bias power across the pulse transformer. As shown in Figure 1, the beginning of the positive half-cycle coincides with the turn-on of the primary-side MOSFETs. Likewise, the beginning of the negative half-cycle coincides with the maximum duty cycle (forced turn-off of primary switches). At the appropriate time during the positive half-cycle, the end of the on-time (PWM going LOW) is signaled by briefly applying a zero volt differential across the pulse transformer. Figure 1 illustrates the operation of this multiplexing scheme.The L TC3705 primary-side controller and gate driver will decode this PWM information as well as extract the power needed for primary-side gate drive.Figure 1. Gate Drive Encoding Scheme (V MODE = GND)DUTY CYCLE = 15%V PT1+ – V PT1DUTY CYCLE = 0%/93706fd103706fdOPERATIONvalues using the SLP pin as shown in Table 1. Note that the amount of slope compensation doubles when the duty cycle exceeds 50%.Table 1SLP PIN SLOPE (D < 0.5)SLOPE (D > 0.5)GND 0.05 • I SMAX • f OSC0.1 • I SMAX • f OSCV CCNone None 400kΩ to GND 0.1 • I SMAX • f OSC 0.2 • I SMAX • f OSC 200kΩ to GND 0.15 • I SMAX • f OSC 0.3 • I SMAX • f OSC 100kΩ to GND 0.25 • I SMAX • f OSC 0.5 • I SMAX • f OSC 50kΩ to GND0.5 • I SMAX • f OSC1.0 • I SMAX • f OSCIn Table 1 above, I SMAX is the maximum current limit, and f OSC is the switching frequency.Current Sensing and Current LimitFor current sensing, the L TC3706 supports either a current sense resistor or a current sense transformer . The current sense resistor may either be placed in series with the inductor (either high side or ground lead sensing), or in the source of the “forward” switch. If a current sense transformer is used, the I S – input should be tied to V CC and the I S + pin to the output of the current sense transformer . This causes the gain of the internal current sense amplifier to be reduced by a factor of 16×, so that the maximum current sense voltage (current limit) is increased from 78mV to 1.28V . An internal, adaptive leading edge blanking circuit ensures clean operation for “switch” current sensing applications.Current limit is achieved in the L TC3706 by limiting the maximum voltage excursion of the error signal (ITH volt-age). Note that if slope compensation is used, the precise value at which current limit occurs will be a function of duty cycle (See the Typical Performance Characteristics section). If a short circuit is applied, an independent overcurrent comparator may be tripped. In this case, the L TC3706 will enter a “hiccup” mode using the soft-start circuitry.Self-Starting ArchitectureWhen the LTC3706 is used in conjunction with the LTC3705 primary-side controller and gate driver , a complete self-starting isolated supply is formed. When input voltage is first applied in such an application, the L TC3705 will begin switching in an “open-loop” fashion, causing the main output to slowly ramp upwards. This is the primary-side soft-start mode. On the secondary side, the L TC3706 derives its operating bias voltage from a peak-charged capacitor . This peak-charged voltage will rise more rapidly than the main output of the converter , so that the L TC3706 will become operational well before the output voltage has reached its final value.When the L TC3706 has adequate operating voltage, it will begin the procedure of assuming control from the primary side. To do this, it first measures the voltage on the power supply’s main output and then automatically advances its own soft-start voltage to correspond to the main output voltage. This ensures that the output voltage increases monotonically as the soft-start control is transferred from primary to secondary. The L TC3706 then begins sending PWM signals to the L TC3705 on the primary side through a pulse transformer . When the L TC3705 has detected a stable signal from the secondary controller , it transfers control of the primary switches over to the L TC3706, beginning the secondary-side soft-start mode. The L TC3706 continues in this mode until the output voltage has ramped up to its final value. If for any reason, the L TC3706 either stops sending (or initially fails to send) PWM information to the L TC3705, the L TC3705 will detect a FAUL T and initiate a soft-start retry. (See the L TC3705 data sheet.) Slope CompensationSlope compensation is added at the input of the PWM comparator to improve stability and noise margin of the peak current control loop. The amount of slope compen-sation can be selected from one of five preprogrammed/分销商库存信息:LINEAR-TECHNOLOGYLTC3706EGN#PBF LTC3706EGN#TRPBF LTC3706IGN#PBF LTC3706IGN#TRPBF。

AD9516-3BCPZ;AD9516-3BCPZ-REEL7;AD9516-3PCBZ;中文规格书,Datasheet资料

14-Output Clock Generator withIntegrated 2.0 GHz VCO Data Sheet AD9516-3Rev. BInformation furnished by Analog Devices is believed to be accurate and reliable. However, noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113 ©2007–2012 Analog Devices, Inc. All rights reserved.FEATURESLow phase noise, phase-locked loop (PLL)On-chip VCO tunes from 1.75 GHz to 2.25 GHzExternal VCO/VCXO to 2.4 GHz optional1 differential or2 single-ended reference inputs Reference monitoring capabilityAutomatic revertive and manual referenceswitchover/holdover modesAccepts LVPECL, LVDS, or CMOS references to 250 MHz Programmable delays in path to PFDDigital or analog lock detect, selectable6 pairs of 1.6 GHz LVPECL outputsEach output pair shares a 1-to-32 divider with coarsephase delayAdditive output jitter: 225 fs rmsChannel-to-channel skew paired outputs of <10 ps4 pairs of 800 MHz LVDS clock outputsEach output pair shares two cascaded 1-to-32 dividerswith coarse phase delayAdditive output jitter: 275 fs rmsFine delay adjust (Δt) on each LVDS outputEach LVDS output can be reconfigured as two 250 MHzCMOS outputsAutomatic synchronization of all outputs on power-up Manual output synchronization available64-lead LFCSPAPPLICATIONSLow jitter, low phase noise clock distribution10/40/100 Gb/sec networking line cards, including SONET, Synchronous Ethernet, OTU2/3/4Forward error correction (G.710)Clocking high speed ADCs, DACs, DDSs, DDCs, DUCs, MxFEs High performance wireless transceiversATE and high performance instrumentationGENERAL DESCRIPTIONThe AD9516-31 provides a multi-output clock distribution function with subpicosecond jitter performance, along with an on-chip PLL and VCO. The on-chip VCO tunes from 1.75 GHz to 2.25 GHz. Optionally, an external VCO/VCXO of up to 2.4 GHz can be used.The AD9516-3 emphasizes low jitter and phase noise to maximize data converter performance, and it can benefit other applications with demanding phase noise and jitter requirements.FUNCTIONAL BLOCK DIAGRAM REFINCLK6422-1Figure 1.The AD9516-3 features six LVPECL outputs (in three pairs) and four LVDS outputs (in two pairs). Each LVDS output can be reconfigured as two CMOS outputs. The LVPECL outputs operate to 1.6 GHz, the LVDS outputs operate to 800 MHz, and the CMOS outputs operate to 250 MHz.Each pair of outputs has dividers that allow both the divide ratio and coarse delay (or phase) to be set. The range of division for the LVPECL outputs is 1 to 32. The LVDS/CMOS outputs allow a range of divisions up to a maximum of 1024.The AD9516-3 is available in a 64-lead LFCSP and can be operated from a single 3.3 V supply. An external VCO, which requires an extended voltage range, can be accommodatedby connecting the charge pump supply (VCP) to 5 V. A separate LVPECL power supply can be from 2.5 V to 3.3 V (nominal). The AD9516-3 is specified for operation over the standard industrial range of −40°C to +85°C.1 AD9516 is used throughout to refer to all the members of the AD9516 family. However, when AD9516-3 is used, it refers to that specific member of the AD9516 family.AD9516-3Data SheetRev. B | Page 2 of 80TABLE OF CONTENTSFeatures..............................................................................................1 Applications.......................................................................................1 General Description.........................................................................1 Functional Block Diagram..............................................................1 Revision History...............................................................................3 Specifications.....................................................................................4 Power Supply Requirements.......................................................4 PLL Characteristics......................................................................4 Clock Inputs..................................................................................6 Clock Outputs...............................................................................6 Timing Characteristics................................................................7 Clock Output Additive Phase Noise (Distribution Only; VCO Divider Not Used)........................................................................8 Clock Output Absolute Phase Noise (Internal VCO Used)....9 Clock Output Absolute Time Jitter (Clock Generation Using Internal VCO).............................................................................10 Clock Output Absolute Time Jitter (Clock Cleanup Using Internal VCO).............................................................................10 Clock Output Absolute Time Jitter (Clock Generation Using External VCXO).........................................................................10 Clock Output Additive Time Jitter (VCO Divider Not Used).......................................................................................................11 Clock Output Additive Time Jitter (VCO Divider Used).....11 Delay Block Additive Time Jitter..............................................12 Serial Control Port.....................................................................12 PD , RESET , and SYNC Pins.....................................................13 LD, STATUS, and REFMON Pins............................................13 Power Dissipation.......................................................................14 Timing Diagrams............................................................................15 Absolute Maximum Ratings..........................................................16 Thermal Resistance....................................................................16 ESD Caution................................................................................16 Pin Configuration and Function Descriptions...........................17 Typical Performance Characteristics...........................................19 Terminology....................................................................................25 Detailed Block Diagram................................................................26 Theory of Operation......................................................................27 Operational Configurations......................................................27 Digital Lock Detect (DLD).......................................................36 Clock Distribution.....................................................................40 Reset Modes................................................................................48 Power-Down Modes..................................................................49 Serial Control Port.........................................................................50 Serial Control Port Pin Descriptions.......................................50 General Operation of Serial Control Port...............................50 The Instruction Word (16 Bits)................................................51 MSB/LSB First Transfers...........................................................51 Thermal Performance....................................................................54 Register Map Overview.................................................................55 Register Map Descriptions............................................................59 Applications Information..............................................................77 Frequency Planning Using the AD9516..................................77 Using the AD9516 Outputs for ADC Clock Applications....77 LVPECL Clock Distribution.....................................................78 LVDS Clock Distribution..........................................................78 CMOS Clock Distribution........................................................79 Outline Dimensions.......................................................................80 Ordering Guide.. (80)Data SheetAD9516-3Rev. B | Page 3 of 80REVISION HISTORY1/12—Rev. A to Rev. BChanges to 0x232 Description Column, Table 62 (76)12/10—Rev. 0 to Rev. AChanges to Features, Applications, and General Description.....1 Change to CPRSET Pin Resistor Parameter in Table 1................4 Change to P = 2 DM (2/3) Parameter in Table 2..........................5 Changes to Table 4............................................................................6 Changes to V CP Supply Parameter in Table 17.............................14 Change to θJA Value and Endnote in Table 19.............................16 Added Exposed Paddle Notation to Figure 6; Changes toTable 20.............................................................................................17 Added Figure 41; Renumbered Sequentially...............................24 Change to High Frequency Clock Distribution—CLK orExternal VCO > 1600 MHz Section; Change to Table 22..........27 Changes to Table 24........................................................................29 Change to Configuration and Register Settings Section............31 Change to Phase Frequency Detector (PFD) Section................32 Changes to Charge Pump (CP), On-Chip VCO, PLLExternal Loop Filter, and PLL Reference Inputs Sections.........33 Change to Figure 47; Added Figure 48.........................................33 Changes to Reference Switchover and VCXO/VCOFeedback Divider N—P , A, B, R Sections....................................34 Changes to Table 28........................................................................35 Change to Holdover Section..........................................................37 Changes to VCO Calibration Section...........................................39 Changes to Clock Distribution Section........................................40 Added Endnote to Table 34...........................................................41 Changes to Channel Dividers—LVDS/CMOS OutputsSection; Added Endnote to Table 39............................................43 Changes to Write Section...............................................................50 Change to the Instruction Word (16 Bits) Section.....................51 Change to Figure 65........................................................................52 Added Thermal Performance Section..........................................54 Changes to Register Address 0x003 in Table 52..........................55 Changes to Table 53........................................................................59 Changes to Table 54........................................................................60 Changes to Table 55........................................................................66 Changes to Table 56........................................................................68 Changes to Table 57........................................................................71 Changes to Table 58........................................................................73 Changes to Table 59........................................................................74 Changes to Table 60 and Table 61.................................................76 Added Frequency Planning Using the AD9516 Section............77 Changes to Figure 71 and Figure 73; Added Figure 72..............78 Changes to LVPECL Clock Distribution and LVDS ClockDistribution Sections......................................................................78 Updated Outline Dimensions........................................................80 6/07—Revision 0: Initial VersionAD9516-3Data SheetRev. B | Page 4 of 80SPECIFICATIONSTypical is given for V S = V S_LVPECL = 3.3 V ± 5%; V S ≤ V CP ≤ 5.25 V; T A = 25°C; RSET = 4.12 kΩ; CPRSET = 5.1 kΩ, unless otherwise noted. Minimum and maximum values are given over full V S and T A (−40°C to +85°C) variation.POWER SUPPLY REQUIREMENTSTable 1.Parameter Min Typ Max Unit Test Conditions/Comments V S 3.135 3.3 3.465 V 3.3 V ± 5% V S_LVPECL 2.375 V S V Nominally 2.5 V to 3.3 V ± 5% V CP V S 5.25 V Nominally 3.3 V to 5.0 V ± 5% RSET Pin Resistor 4.12 kΩ Sets internal biasing currents; connect to ground CPRSET Pin Resistor 2.7 5.1 10 kΩ Sets internal CP current range, nominally 4.8 mA (CP_lsb = 600 μA);actual current can be calculated by: CP_lsb = 3.06/CPRSET; connect to groundBYPASS Pin Capacitor 220 nF Bypass for internal LDO regulator; necessary for LDO stability;connect to groundPLL CHARACTERISTICSData SheetAD9516-3Rev. B | Page 5 of 80Parameter Min Typ Max Unit Test Conditions/Comments CHARGE PUMP (CP) I CP Sink/Source Programmable High Value 4.8 mA With CP RSET = 5.1 kΩ Low Value 0.60 mA Absolute Accuracy 2.5 % CP V = V CP /2 CP RSET Range 2.7/10 kΩ I CP High Impedance Mode Leakage 1 nA Sink-and-Source Current Matching 2 % 0.5 < CP V < V CP − 0.5 V I CP vs. CP V 1.5 % 0.5 < CP V < V CP − 0.5 V I CP vs. Temperature 2 % CP V = V CP /2 PRESCALER (PART OF N DIVIDER) See the VCXO/VCO Feedback Divider N—P , A, B, R section Prescaler Input Frequency P = 1 FD 300 MHz P = 2 FD 600 MHz P = 3 FD 900 MHz P = 2 DM (2/3) 200 MHz P = 4 DM (4/5) 1000 MHz P = 8 DM (8/9) 2400 MHz P = 16 DM (16/17) 3000 MHz P = 32 DM (32/33) 3000 MHz Prescaler Output Frequency 300 MHz A, B counter input frequency (prescaler input frequency dividedby P)PLL DIVIDER DELAYS Register 0x019: R, Bits[5:3]; N, Bits[2:0]; see Table 54 000 Off ps 001 330 ps 010 440 ps 011 550 ps 100 660 ps 101 770 ps 110 880 ps 111 990 ps NOISE CHARACTERISTICS In-Band Phase Noise of the Charge Pump/Phase Frequency Detector (In-Band Is Within the LBW of the PLL) The PLL in-band phase noise floor is estimated by measuring the in-band phase noise at the output of the VCO and subtracting 20log(N) (where N is the value of the N divider) At 500 kHz PFD Frequency −165 dBc/Hz At 1 MHz PFD Frequency −162 dBc/Hz At 10 MHz PFD Frequency −151 dBc/Hz At 50 MHz PFD Frequency −143 dBc/Hz PLL Figure of Merit (FOM) −220 dBc/Hz Reference slew rate > 0.25 V/ns; FOM + 10log (f PFD ) is an approxi-mation of the PFD/CP in-band phase noise (in the flat region)inside the PLL loop bandwidth; when running closed loop, the phase noise, as observed at the VCO output, is increased by 20log(N)PLL DIGITAL LOCK DETECT WINDOW 2 Signal available at LD, STATUS, and REFMON pins when selectedby appropriate register settingsRequired to Lock (Coincidence of Edges) Selected by Register 0x017[1:0] and Register 0x018[4] Low Range (ABP 1.3 ns, 2.9 ns) 3.5 ns Register 0x017[1:0] = 00b, 01b,11b; Register 0x018[4] = 1b High Range (ABP 1.3 ns, 2.9 ns) 7.5 ns Register 0x017[1:0] = 00b, 01b, 11b; Register 0x018[4] = 0b High Range (ABP 6.0 ns) 3.5 ns Register 0x017[1:0] = 10b; Register 0x018[4] = 0bTo Unlock After Lock (Hysteresis)2Low Range (ABP 1.3 ns, 2.9 ns) 7 ns Register 0x017[1:0] = 00b, 01b, 11b; Register 0x018[4] = 1b High Range (ABP 1.3 ns, 2.9 ns) 15 ns Register 0x017[1:0] = 00b, 01b, 11b; Register 0x018[4] = 0b High Range (ABP 6.0 ns) 11 ns Register 0x017[1:0] = 10b; Register 0x018[4] = 0b1 REFIN and REFIN self-bias points are offset slightly to avoid chatter on an open input condition.2For reliable operation of the digital lock detect, the period of the PFD frequency must be greater than the unlock-after-lock time.AD9516-3 Data Sheet CLOCK INPUTS1 Below about 1 MHz, the input should be dc-coupled. Care should be taken to match V CM.CLOCK OUTPUTSRev. B | Page 6 of 80Data Sheet AD9516-3 TIMING CHARACTERISTICSTable 5.Parameter Min Typ Max Unit Test Conditions/CommentsLVPECL Termination = 50 Ω to V S − 2 V; level = 810 mVOutput Rise Time, t RP70 180 ps 20% to 80%, measured differentiallyOutput Fall Time, t FP70 180 ps 80% to 20%, measured differentiallyPROPAGATION DELAY, t PECL, CLK-TO-LVPECL OUTPUTHigh Frequency Clock Distribution Configuration 835 995 1180 ps See Figure 43Clock Distribution Configuration 773 933 1090 ps See Figure 45Variation with Temperature 0.8 ps/°COUTPUT SKEW, LVPECL OUTPUTS1LVPECL Outputs That Share the Same Divider 5 15 psLVPECL Outputs on Different Dividers 13 40 psAll LVPECL Outputs Across Multiple Parts 220 psLVDS Termination = 100 Ω differential; 3.5 mA Output Rise Time, t RL170 350 ps 20% to 80%, measured differentially2Output Fall Time, t FL160 350 ps 20% to 80%, measured differentially2PROPAGATION DELAY, t LVDS, CLK-TO-LVDS OUTPUT Delay off on all outputsOUT6, OUT7, OUT8, OUT9For All Divide Values 1.4 1.8 2.1 nsVariation with Temperature 1.25 ps/°COUTPUT SKEW, LVDS OUTPUTS1Delay off on all outputsLVDS Outputs That Share the Same Divider 6 62 psLVDS Outputs on Different Dividers 25 150 psAll LVDS Outputs Across Multiple Parts 430 psCMOS Termination = openOutput Rise Time, t RC495 1000 ps 20% to 80%; C LOAD = 10 pFOutput Fall Time, t FC475 985 ps 80% to 20%; C LOAD = 10 pFPROPAGATION DELAY, t CMOS, CLK-TO-CMOS OUTPUT Fine delay offFor All Divide Values 1.6 2.1 2.6 nsVariation with Temperature 2.6 ps/°COUTPUT SKEW, CMOS OUTPUTS1Fine delay offCMOS Outputs That Share the Same Divider 4 66 psAll CMOS Outputs on Different Dividers 28 180 psAll CMOS Outputs Across Multiple Parts 675 psDELAY ADJUST3LVDS and CMOSShortest Delay Range4Register 0xA1 (0xA4, 0xA7, 0xAA), Bits[5:0] = 101111b Zero Scale 50 315 680 ps Register 0xA2 (0xA5, 0xA8, 0xAB), Bits[5:0] = 000000b Full Scale 540 880 1180 ps Register 0xA2 (0xA5, 0xA8, 0xAB), Bits[5:0] = 101111b Longest Delay Range4Register 0xA1 (0xA4, 0xA7, 0xAA), Bits[5:0] = 000000b Zero Scale 200 570 950 ps Register 0xA2 (0xA5, 0xA8, 0xAB), Bits[5:0] = 000000b Quarter Scale 1.72 2.31 2.89 ns Register 0xA2 (0xA5, 0xA8, 0xAB), Bits[5:0] = 001100b Full Scale 5.7 8.0 10.1 ns Register 0xA2 (0xA5, 0xA8, 0xAB), Bits[5:0] = 101111b Delay Variation with TemperatureShort Delay Range5Zero Scale 0.23 ps/°CFull Scale −0.02 ps/°CLong Delay Range5Zero Scale 0.3 ps/°CFull Scale 0.24 ps/°C1 This is the difference between any two similar delay paths while operating at the same voltage and temperature.2 Corresponding CMOS drivers set to A for noninverting and B for inverting.3 The maximum delay that can be used is a little less than one-half the period of the clock. A longer delay disables the output.4 Incremental delay; does not include propagation delay.5 All delays between zero scale and full scale can be estimated by linear interpolation.Rev. B | Page 7 of 80AD9516-3Data SheetRev. B | Page 8 of 80CLOCK OUTPUT ADDITIVE PHASE NOISE (DISTRIBUTION ONLY; VCO DIVIDER NOT USED)Table 6.Parameter Min Typ Max Unit Test Conditions/Comments CLK-TO-LVPECL ADDITIVE PHASE NOISE Distribution section only; does not include PLL and VCO CLK = 1 GHz, Output = 1 GHz Input slew rate > 1 V/ns Divider = 1 At 10 Hz Offset −109 dBc/Hz At 100 Hz Offset −118 dBc/Hz At 1 kHz Offset −130 dBc/Hz At 10 kHz Offset −139 dBc/Hz At 100 kHz Offset −144 dBc/Hz At 1 MHz Offset −146 dBc/Hz At 10 MHz Offset −147 dBc/Hz At 100 MHz Offset −149 dBc/Hz CLK = 1 GHz, Output = 200 MHz Input slew rate > 1 V/ns Divider = 5 At 10 Hz Offset −120 dBc/Hz At 100 Hz Offset −126 dBc/Hz At 1 kHz Offset −139 dBc/Hz At 10 kHz Offset −150 dBc/Hz At 100 kHz Offset −155 dBc/Hz At 1 MHz Offset −157 dBc/Hz >10 MHz Offset −157 dBc/Hz CLK-TO-LVDS ADDITIVE PHASE NOISE Distribution section only; does not include PLL and VCO CLK = 1.6 GHz, Output = 800 MHz Input slew rate > 1 V/ns Divider = 2 At 10 Hz Offset −103 dBc/Hz At 100 Hz Offset −110 dBc/Hz At 1 kHz Offset −120 dBc/Hz At 10 kHz Offset −127 dBc/Hz At 100 kHz Offset −133 dBc/Hz At 1 MHz Offset −138 dBc/Hz At 10 MHz Offset −147 dBc/Hz At 100 MHz Offset −149 dBc/Hz CLK = 1.6 GHz, Output = 400 MHz Input slew rate > 1 V/ns Divider = 4 At 10 Hz Offset −114 dBc/Hz At 100 Hz Offset −122 dBc/Hz At 1 kHz Offset −132 dBc/Hz At 10 kHz Offset −140 dBc/Hz At 100 kHz Offset −146 dBc/Hz At 1 MHz Offset −150 dBc/Hz >10 MHz Offset −155 dBc/Hz CLK-TO-CMOS ADDITIVE PHASE NOISE Distribution section only; does not include PLL and VCO CLK = 1 GHz, Output = 250 MHz Input slew rate > 1 V/ns Divider = 4 At 10 Hz Offset −110 dBc/Hz At 100 Hz Offset −120 dBc/Hz At 1 kHz Offset −127 dBc/Hz At 10 kHz Offset −136 dBc/Hz At 100 kHz Offset −144 dBc/Hz At 1 MHz Offset −147 dBc/Hz >10 MHz Offset −154 dBc/HzData SheetAD9516-3Rev. B | Page 9 of 80Parameter Min Typ Max Unit Test Conditions/Comments CLK = 1 GHz, Output = 50 MHz Input slew rate > 1 V/ns Divider = 20 At 10 Hz Offset −124 dBc/Hz At 100 Hz Offset −134 dBc/Hz At 1 kHz Offset −142 dBc/Hz At 10 kHz Offset −151 dBc/Hz At 100 kHz Offset −157 dBc/Hz At 1 MHz Offset −160 dBc/Hz >10 MHz Offset −163 dBc/HzCLOCK OUTPUT ABSOLUTE PHASE NOISE (INTERNAL VCO USED)Table 7.Parameter Min Typ Max Unit Test Conditions/Comments LVPECL ABSOLUTE PHASE NOISE Internal VCO; direct to LVPECL output VCO = 2.25 GHz; Output = 2.25 GHz At 1 kHz Offset −49 dBc/Hz At 10 kHz Offset −79 dBc/Hz At 100 kHz Offset −104 dBc/Hz At 1 MHz Offset −123 dBc/Hz At 10 MHz Offset −143 dBc/Hz At 40 MHz Offset −147 dBc/Hz VCO = 2.00 GHz; Output = 2.00 GHz At 1 kHz Offset −53 dBc/Hz At 10 kHz Offset −83 dBc/Hz At 100 kHz Offset −108 dBc/Hz At 1 MHz Offset −126 dBc/Hz At 10 MHz Offset −142 dBc/Hz At 40 MHz Offset −147 dBc/Hz VCO = 1.75 GHz; Output = 1.75 GHz At 1 kHz Offset −54 dBc/Hz At 10 kHz Offset −88 dBc/Hz At 100 kHz Offset −112 dBc/Hz At 1 MHz Offset −130 dBc/Hz At 10 MHz Offset −143 dBc/Hz At 40 MHz Offset −147 dBc/HzAD9516-3Data SheetRev. B | Page 10 of 80CLOCK OUTPUT ABSOLUTE TIME JITTER (CLOCK GENERATION USING INTERNAL VCO)Table 8.ParameterMin Typ Max Unit Test Conditions/Comments LVPECL OUTPUT ABSOLUTE TIME JITTERApplication example based on a typicalsetup where the reference source is clean, so a wider PLL loop bandwidth is used; reference = 15.36 MHz; R = 1VCO = 1.97 GHz; LVPECL = 245.76 MHz; PLL LBW = 143 kHz129 fs rms Integration BW = 200 kHz to 10 MHz303 fs rms Integration BW = 12 kHz to 20 MHz VCO = 1.97 GHz; LVPECL = 122.88 MHz; PLL LBW = 143 kHz 135 fs rms Integration BW = 200 kHz to 10 MHz302 fs rms Integration BW = 12 kHz to 20 MHz VCO = 1.97 GHz; LVPECL = 61.44 MHz; PLL LBW = 143 kHz 179 fs rms Integration BW = 200 kHz to 10 MHz343 fs rms Integration BW = 12 kHz to 20 MHzCLOCK OUTPUT ABSOLUTE TIME JITTER (CLOCK CLEANUP USING INTERNAL VCO)Table 9.ParameterMin Typ Max Unit Test Conditions/Comments LVPECL OUTPUT ABSOLUTE TIME JITTERApplication example based on a typicalsetup where the reference source is jittery, so a narrower PLL loop bandwidth is used; reference = 10.0 MHz; R = 20VCO = 1.87 GHz; LVPECL = 622.08 MHz; PLL LBW = 125 Hz400 fs rms Integration BW = 12 kHz to 20 MHz VCO = 1.87 GHz; LVPECL = 155.52 MHz; PLL LBW = 125 Hz 390 fs rms Integration BW = 12 kHz to 20 MHz VCO = 1.97 GHz; LVPECL = 122.88 MHz; PLL LBW = 125 Hz485 fs rms Integration BW = 12 kHz to 20 MHzCLOCK OUTPUT ABSOLUTE TIME JITTER (CLOCK GENERATION USING EXTERNAL VCXO)Table 10.Parameter Min Typ Max Unit Test Conditions/Comments LVPECL OUTPUT ABSOLUTE TIME JITTER Application example based on a typical setupusing an external 245.76 MHz VCXO (Toyocom TCO-2112); reference = 15.36 MHz; R = 1LVPECL = 245.76 MHz; PLL LBW = 125 Hz 54 fs rms Integration BW = 200 kHz to 5 MHz 77 fs rms Integration BW = 200 kHz to 10 MHz 109 fs rms Integration BW = 12 kHz to 20 MHz LVPECL = 122.88 MHz; PLL LBW = 125 Hz 79 fs rms Integration BW = 200 kHz to 5 MHz 114 fs rms Integration BW = 200 kHz to 10 MHz 163 fs rms Integration BW = 12 kHz to 20 MHz LVPECL = 61.44 MHz; PLL LBW = 125 Hz 124 fs rms Integration BW = 200 kHz to 5 MHz 176 fs rms Integration BW = 200 kHz to 10 MHz 259 fs rms Integration BW = 12 kHz to 20 MHz分销商库存信息:ANALOG-DEVICESAD9516-3BCPZ AD9516-3BCPZ-REEL7AD9516-3/PCBZ。

IRF7313;中文规格书,Datasheet资料

Fig 5. Normalized On-Resistance Vs. Temperature

Fig 6. Typical On-Resistance Vs. Drain Current

RDS (on) , Drain-to-Source On Resistance (Ω)

E AS , Single Pulse Avalanche Energy (mJ)

Min. Typ. Max. Units 2.5 A 30 1.0 68 87 V ns nC 0.78 45 58

Conditions MOSFET symbol showing the G integral reverse p-n junction diode. TJ = 25°C, IS = 1.7A, VGS = 0V TJ = 25°C, IF = 1.7A di/dt = 100A/µs

0.12

200

TOP

160

0.10

BOTTOM

IID D 1.8A 3.2A 4.0A

0.08

120

0.06

I D = 5.8A

/

IRF7313

RDS(on) , Drain-to-Source On Resistance (Normalized)

ID = 5.8A

RDS (on) , Drain-to-Source On Resistance (Ω)

2.0

0.040

0.036

V GS = 4.5V

4.5 5.0

A

1 0.4 0.6 0.8 1.0 1.2

VGS = 0V

1.4

A

1.6

VGS , Gate-to-Source Voltage (V)

AS3691A-ZQFT;AS3691A EB;中文规格书,Datasheet资料

1 General DescriptionThe AS3691 (AS3691A and AS3691B) features four high precision current sources for lighting of up to four LED strings (RGB or single color leds). Each of the four currents sources can be controlled independently by PWM inputs. The full scale current value is set by external resistors.2 Key Features4 x up to 0.4A constant current outputs Programmable with external resistors 4 independent PWM inputs Absolute current accuracy +/-0.5%’Automatic Supply Regulation’ to reduce powerdissipation 1) 1)Patent PendingVery wide output voltage current source voltage compliance − Down to 0.41V− Up to 15V 2)Integrated overtemperature protectionSeparate sense pads (Rfb1-Rfb4) for easy andprecise PCB Layout Package− DIE − QFN24 4x4mm − eP-TSSOP2)15V is sufficient for most applications as the AS3691 dose not switch off the LED current completely3 ApplicationsGeneral Lighting BacklightingRGB Backlighting for LCD TV/Monitors withWhite Color Balancing4 Application DiagramsFigure 1 – Application Diagram of AS3691 for Single Color LightingVSS VSS VDDVDDUVUV PWMPWMDatasheetAS36914 Precision 400mA Current Sources for RGB and Single Color LedsFigure 2 – Application Diagram of AS3691 for RGB LightingVSS VSS VDDRVDDRUVRUVRUVB UVB UVG UVG PWMRPWMRPWMB PWMB PWMG PWMG VDDB VDDB VDDG VDDGTable of Contents1 General Description.........................................................................................................................................12 Key Features....................................................................................................................................................13 Applications......................................................................................................................................................14 Application Diagrams.......................................................................................................................................1 5Pinout...............................................................................................................................................................4 5.1 Pin Assignments.......................................................................................................................................4 5.2 Pin Descriptions........................................................................................................................................4 6 Characteristics. (6)6.1 Absolute Maximum Ratings......................................................................................................................6 6.2 Operating Conditions................................................................................................................................6 6.3 Electrical Characteristics (7)7 Typical Operation Characteristics....................................................................................................................8 8Detailed Functional Description .....................................................................................................................12 8.1 Shunt Regulator......................................................................................................................................12 8.2 Overtemperature Protection....................................................................................................................12 8.3Automatic Supply Regulation (13)9 Application Information ..................................................................................................................................14 9.1 Design Example......................................................................................................................................15 9.1.1 Using Automatic Supply Regulation.................................................................................................16 9.2 Layout Recommendations. (16)10 Package Drawings and Markings (17)10.1 QFN 4x4 Package Drawings and Marking..............................................................................................17 10.2 ePTSSOP Package Drawings and Marking............................................................................................19 10.3 DIE Delivery............................................................................................................................................20 11 Ordering Information . (21)Revision HistoryRevisionDateOwnerDescription2.3 30.10.2007 ptr- Added Trays as delivery option (order code AS3691A-ZQFT)5 Pinout5.1 Pin AssignmentsFigure 3 – Pin UsageVREG VSS ON1ON2ON3ON4CURR1CURR2CURR3CURR4RES1RES2RES3RES4UV1UV2UV3UV4RFB1RFB2RFB3RFB4Pad5.2 Pin DescriptionsTable 1 – Pin Type DescriptionsPin Type DescriptionAI/O Analog Pin AI Analog Input Pin AO Analog Output Pin DI Digital Input SSupply PinTable 2 – Pin DescriptionsPin Number QFN Package Pin NumberePTSSOP PackagePin Name Type Description1 10 CURR1 AI/O Current Source 1 Output2 11 RFB1 AI Connect to current set resistor R1 directly atresistor itself 3 12 nc nc Leave open4 13 RFB4 AI Connect to current set resistor R4 directly at resistor itself5 14 CURR4 AI/O Current Source 4 Output6 15 RES4AI/OConnect to current set resistor R4Pin NumberQFN Package Pin NumberePTSSOPPackagePin Name Type Description7 16 ON4 DI Current source CURR4 control; internal pullup resistor to VREG (can be left open, if CURR4 is always switched on)High … 100% CurrentLow … 5% Current8 17 UV4 AO Automatic supply regulation for CURR4; if not used, leave open9 18 TEST AI Digital Test input; Leave open or connect to VSS; internal pulldown to VSS10 19 UV3 AO Automatic supply regulation for CURR3; if not used, leave open11 20 ON3 DI Current source CURR3 control; internal pullup resistor to VREG (can be left open, if CURR3 is always switched on)High … 100% CurrentLow … 5% Current12 21 RES3 AI/O Connect to current set resistor R313 22 CURR3 AI/O Current Source 3 Output14 23 RFB3 AI Connect to current set resistor R3 directly at resistor itself15 24 VREG S Shunt regulator supply; connect to Rvdd and Cvdd16 1 RFB2 AI Connect to current set resistor R2 directly at resistor itself17 2 CURR2 AI/O Current Source 2 Output18 3 RES2 AI/O Connect to current set resistor R219 4 ON2 DI Current source CURR2 control; internal pullup resistor to VREG (can be left open, if CURR2 is always switched on)High … 100% CurrentLow … 5% Current20 5 UV2 AO Automatic supply regulation for CURR2; if not used, leave open21 6 VSS S VSS Supply connection22 7 UV1 AO Automatic supply regulation for CURR1; if not used, leave open23 8 ON1 DI Current source CURR1 control; internal pullup resistor to VREG (can be left open, if CURR1 is always switched on)High … 100% CurrentLow … 5% Current24 9 RES1 AI/O Connect to current set resistor R1Pad Pad VSS S VSS Supply connection; add as many vias to ground plane as possible6 Characteristics6.1 Absolute Maximum RatingsStresses beyond those listed in Table 1 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Section 5 Electrical Characteristics is not implied.Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Table 3 – Absolute Maximum RatingsSymbol Parameter Min Max Unit NoteV DDMAXSupply for LEDs-0.3 >17 V See notes 1V INVREG VREG Supply voltage-0.37.0 V Applicable for pin VREG V IN5V 5V Pins -0.3 VREG+ 0.3VVApplicable for 5V pins 2V IN15V 15V Pins -0.3 17 VApplicable for CURR1, CURR2, CURR3 and CURR4 I IN Input Pin Current -25 +25 mA At 25ºC, Norm: Jedec 17 T STRGStorage Temperature Range-55125°CHumidity 5 85 % Non condensing V ESD Electrostatic Discharge -2000 2000VNorm: MIL 883 E Method 3015PT Total Power Dissipation 2.0 W At 50ºC, no airflow for QFN24 on two layer FR4-Cu PCB 3P DERATE PT Derating Factor 23 mW/°C See notes 3 T BODY Body Temperature duringSoldering260°Caccording to IPC/JEDEC J-STD-020CNotes:1. As the AS3691 is not directly connected to this supply. Only the parameters V INVREG , V IN5V andV IN15V have to be guaranteed by the application2. All pins except CURR1, CURR2, CURR3 and CURR43. Depending on actual PCB layout and especially number of vias below the exposed pad – see layoutrecommendations; can be improved e.g. with Al-PCB or airflow6.2 Operating ConditionsTable 4 – Operating ConditionsSymbol Parameter Min Typ Max Unit NoteVDD Main Supply NotLimited VSupply is not directly connected tothe AS3691 – see section ‘Shunt Regulator’VDD TOL Main Supply Voltage Tolerance -20 +20 %Applies only for supply VREG isconnected via Rvdd VREG INTSupply (shunt regulated byAS3691)5.05.25.4 VIf internally (shunt-)regulated byD1VREG EXT4.5 4.755.0 VIf externally suppliedIVREG Supply Current2.5 mA Excluding current through shuntregulator (D1) – see section‘Shunt Regulator’ T AMB Ambient Temperature -20 25 85°C6.3 Electrical CharacteristicsTable 5 – Analog Electrical CharacteristicsSymbol ParameterMin Typ Max Unit Note0.9 15.0 Vat 400mA; total power dissipationlimit PT must not be exceeded V CURRCurrent Source CURR1 toCURR4 Voltage Compliance 0.41 15.0 V at 100mAI CURRCurrent Source Range10 400(1) mAONx = high ICURRx = 250mV / Rix (x=1...4) -0.5+0.5 %@25C T JUNCTION , excluding variation of external resistors; V(CURRx) <= 4.0VI CURR, TOLCurrent Source Tolerance-1.5+1.5 %-20°C to +100°C (2)T JUNCTION , -20°C to +85°C T AMB , excludingvariation of external resistors; V(CURRx) <= 4.0VV C Automatic Supply Regulationcompare voltage 1.0 VSee section ‘Automatic SupplyRegulation’ V C,GAINAutomatic Supply Regulationgain2.0 mA/VVoltage to current ratio; output current range typ 0 to 200uA1.0 mA V(CURRx) <= 15V I 1-4 Parallel Current0.1 mA V(CURRx) <= 5.0V T OVTEMP Overtemperature Limit 140°C Maximum junction temperatureNotes:1. To obtain higher currents connect more than one current source in parallel2. Accuracy at +100°C guaranteed by design and verified by laboratory characterizationTable 6 – Digital Input pins characteristics for pins ON1, ON2, ON3 and ON4Symbol Parameter Min Typ Max Unit NoteV IH High Level Input voltage 2.3 VREGVV ILLow Level Input voltage0.00.9 V R PU Pullup resistor 70k ΩInternal pullup resistor R1 to R4 toVREGf ON Input Frequency Range 020 kHzThis defines the actual inputfrequency seen on the input ON1 to ON4; the basic frequency to generate the PWM signal is not limited by this parameter7 Typical Operation CharacteristicsFigure4 – Output Current versus Voltage on Current Source – High Current RangeFigure5 – Output Current versus Voltage on Current Source – Low Current RangeFigure 6 – Internal voltage reference versus Temperature, V(CURR1) = 2.0V, Ri1=250Ω247248249250251252253020406080100120140Temperature [C]V (R E S 1) [m V ]11)1(Ri RES V ICURR =Figure 7 – Output Currnent versus Temperature, V(CURR1) = 2.0V, Ri1 = 2.5Ω (Note: temperature coefficient of Ri1 = -200ppm/°C)Figure 8 – Cross coupling of pwm on CURR1 to CURR2; I(CURR1) = 100mA to 4mA, I(CURR2) = 100mA; AS3691A9899100101102010203040506070Temperature [C]I (C U R R 1) [m A]Figure 9 – PWM performance of Current Source CURR1, I(CURR1) changed between 400mA (ON1=1) and 20mA (ON1=0); AS3691AFigure 10 – Shunt Regulator Voltage VREG versus supply VDD with Rfb=1kΩ分销商库存信息:AMSAS3691A-ZQFT AS3691A EB。

CG2145MS,CG2800MS,CG75MS,CG75LTR,CG2800LTR,CG2600LTR,CG2470L,CG75L, 规格书,Datasheet 资料

CG/CG2 Series

CG/CG2 Series

Description

Littelfuse highly reliable CG/CG2 Series GDTs provide a high degree of surge protection in a small size ideal for board level circuit protection. GDTs function as switches which dissipate a minimum amount of energy and therefore handle currents that far surpass other types of transient voltage protection. Their gas-filled, rugged ceramic metal construction make them well suited to adverse environments. The CG/CG2 series comes in a variety of forms including surface mount, core, straight and shaped leads, to serve a variety of mounting methods.

AGENCY FILE NUMBER

Agency Approvals

AGENCY

& &

2 Electrode GDT Graphical Symbol

The CG Series (75-110V) is ideal for protection of test and communication equipment and other devices in which low voltage limits and extremely low arc voltages are required. The CG2 Series (145V-1000V) is ideal for protecting equipment where higher voltage limits and holdover voltages are necessary.

FDS8949;中文规格书,Datasheet资料

tmOctober 2006FDS8949 Dual N-Channel Logic Level PowerTrench®MOSFET FDS8949Dual N-Channel Logic Level PowerTrench® MOSFET40V, 6A, 29mΩFeaturesMax r DS(on)= 29mΩ at V GS = 10VMax r DS(on)= 36mΩ at V GS = 4.5VLow gate chargeHigh performance trench technology for extremely lowr DS(on)High power and current handling capabilityRoHS compliantGeneral DescriptionThese N-Channel Logic Level MOSFETs are producedusing Fairchild Semiconductor’s advancedPowerTrench® process that has been especially tailoredto minimize the on-state resistance and yet maintainsuperior switching performance.These devices are well suited for low voltage andbattery powered applications where low in-line powerloss and fast switching are required.ApplicationsInverterPower suppliersMOSFET Maximum Ratings TA = 25°C unless otherwise notedThermal CharacteristicsPackage Marking and Ordering InformationSymbol Parameter Ratings UnitsV DS Drain to Source Voltage40VV GS Gate to Source Voltage±20VI DDrain Current -Continuous (Note 1a)6A -Pulsed 20E AS Drain-Source Avalanche Energy (Note 3)26mJP DPower Dissipation for Dual Operation 2W Power Dissipation for Single Operation (Note 1a)(Note 1b)1.60.9T J, T STG Operating and Storage Junction Temperature Range-55 to 150°CRθJA Thermal Resistance-Single operation, Junction to Ambient (Note 1a)81°C/WRθJA Thermal Resistance-Single operation, Junction to Ambient (Note 1b)135RθJC Thermal Resistance, Junction to Case (Note 1)40Device Marking Device Reel Size Tape Width Quantity FDS8949FDS894913’’12mm2500 unitsPin 1SO-8D1D1D2D2S2S1G1G2FDS8949 Dual N-Channel Logic Level PowerTrench ® MOSFETElectrical Characteristics TJ = 25°C unless otherwise notedSymbolParameterTest ConditionsMinTypMaxUnitsOff Characteristics BV DSS Drain to Source Breakdown Voltage I D = 250µA, V GS = 0V 40 V ∆BV DSS ∆T J Breakdown Voltage Temperature CoefficientI D = 250µA, referenced to 25°C33mV/°C I DSS Zero Gate Voltage Drain Current V DS = 32V, V GS = 0V1µA T J = 55°C10µA I GSSGate to Source Leakage CurrentV GS = ±20V,V DS = 0V±100nAOn Characteristics V GS(th)Gate to Source Threshold Voltage V GS = V DS , I D = 250µA 1 1.93V ∆V GS(th) ∆T J Gate to Source Threshold Voltage Temperature Coefficient I D = 250µA, referenced to 25°C -4.6 mV/°Cr DS(on)Drain to Source On Resistance V GS = 10V, I D = 6A2129m ΩV GS = 4.5V, I D = 4.5A 2636V GS = 10V, I D = 6A,T J = 125°C 2943g FSForward TransconductanceV DS = 10V,I D = 6A22S (Note 2)Dynamic CharacteristicsC iss Input Capacitance V DS = 20V, V GS = 0V,f = 1MHz 715955pF C oss Output Capacitance105140pF C rss Reverse Transfer Capacitance6090pF R gGate Resistancef = 1MHz1.1ΩSwitching Characteristicst d(on)Turn-On Delay Time V DD = 20V, I D = 1A V GS = 10V, R GEN = 6Ω918ns t r Rise Time510ns t d(off)Turn-Off Delay Time 2337ns t f Fall Time36ns Q g Total Gate ChargeV DS = 20V, I D = 6A,V GS = 5V 7.711nC Q gs Gate to Source Gate Charge 2.4nC Q gdGate to Drain “Miller”Charge2.8nCDrain-Source Diode Characteristics V SD Source to Drain Diode Forward Voltage V GS = 0V, I S = 6A (note 2) 0.8 1.2V t rr Reverse Recovery Time (note 3)I F = 6A, d iF /d t = 100A/µs1726ns Q rrReverse Recovery Charge711nCand Maximum RatingsNotes:1: R θJA is the sum of the junction-to-case and case-to- ambient thermal resistance where the case thermal reference is defined as the solder mounting surface of the drain pins. R θJC is guaranteed by design while R θJA is determined by the user’s board design.2: Pulse Test: Pulse Width < 300 us, Duty Cycle < 2.0%.3: Starting T J = 25°C, L = 1mH, I AS = 7.3A, V DD = 40V, V GS = 10V.Scale 1:1 on letter size papera) 81°C/W when mounted on a 1in 2 pad of 2 oz copperb) 135°C/W when mounted on a minimum pad .MOSFETMOSFETMOSFETFDS8949 Rev. 6FDS8949 Dual N-Channel Logic Level PowerTrench ® MOSFETTRADEMARKSThe following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.PRODUCT STATUS DEFINITIONS Definition of TermsACEx™ActiveArray™Bottomless™Build it Now™CoolFET™CROSSVOLT ™DOME™EcoSPARK™E 2CMOS™EnSigna™FACT™FAST ®FASTr™FPS™FRFET™FACT Quiet Series™ GlobalOptoisolator™GTO™HiSeC™I 2C™i-Lo ™ImpliedDisconnect ™IntelliMAX™ISOPLANAR™LittleFET™MICROCOUPLER™MicroFET™MicroPak™MICROWIRE™MSX ™MSXPro ™OCX ™OCXPro ™OPTOLOGIC ®OPTOPLANAR™PACMAN™POP™Power247™PowerEdge™PowerSaver™PowerTrench ®QFET ®QS™QT Optoelectronics™Quiet Series™RapidConfigure ™RapidConnect ™µSerDes ™ScalarPump ™SILENT SWITCHER ®SMART START™SPM™Stealth™SuperFET™SuperSOT™-3SuperSOT™-6SuperSOT™-8SyncFET™TCM™TinyBoost™TinyBuck™TinyPWM™TinyPower™TinyLogic ®TINYOPTO™TruTranslation™UHC™UniFET™UltraFET ®VCX™Wire™Across the board. Around the world.™The Power Franchise ®Programmable Active Droop™Datasheet Identification Product Status DefinitionAdvance InformationFormative or In Design This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.PreliminaryFirst ProductionThis datasheet contains preliminary data, andsupplementary data will be published at a later date.Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.No Identification Needed Full ProductionThis datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design. Obsolete Not In ProductionThis datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor.The datasheet is printed for reference information only.Rev. I20分销商库存信息: FAIRCHILDFDS8949。

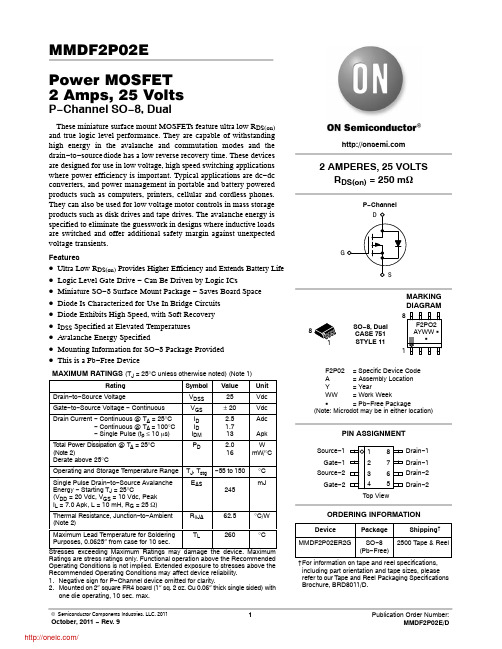

MMDF2P02ER2G;中文规格书,Datasheet资料

TJ, Tstg EAS

RqJA

−55 to 150 245 62.5

°C mJ

°C/W

Maximum Lead Temperature for Soldering

TL

Purposes, 0.0625″ from case for 10 sec.

Drain−1 Drain−1 Drain−2 Drain−2

ORDERING INFORMATION

Device

Package

Shipping†

MMDF2P02ER2G SO−8 2500 Tape & Reel (Pb−Free)

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

RDS(on)

gFS

Ciss Coss Crss

td(on) tr

td(off) tf

td(on) tr

td(off) tf QT Q1 Q2 Q3

VSD trr ta tb QRR

Min

Typ

Max Unit

25

−

−

2.2

Vdc

−

−

mV/°C

mAdc

−

−

1.0

−

−

10

−

−

100 nAdc

PZT3906T1;PZT3906T1G;中文规格书,Datasheet资料

PZT3906T1Preferred DeviceGeneral Purpose Transistor PNP SiliconFeatures•Pb−Free Package is AvailableMAXIMUM RATINGSRating Symbol Value Unit Collector−Emitter Voltage V CEO−40Vdc Collector−Base Voltage V CBO−40Vdc Emitter−Base Voltage V EBO−5.0Vdc Collector Current − Continuous I C−200mAdc THERMAL CHARACTERISTICSCharacteristic Symbol Max Unit Total Device Dissipation (Note 1)TA = 25°C P D 1.512WmW/°CThermal Resistance Junction−to−Ambient(Note 1)R q JA83.3°C/W Thermal Resistance Junction−to−Lead #4R q JA35°C/W Junction and Storage Temperature Range T J, T stg−55 to+150°CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.FR−4 with 1 oz and 713 mm2of copper area.COLLECTOR1BASEEMITTERPreferred devices are recommended choices for future use and best overall value.†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our T ape and Reel Packaging Specifications Brochure, BRD8011/D.Device Package Shipping†ORDERING INFORMATIONPZT3906T1SOT−2231000 / Tape & Reel PZT3906T1G SOT−223(Pb−Free)1000 / Tape & ReelMARKINGDIAGRAM1AYW2A GG2A= Specific Device CodeA= Assembly LocationY= YearW= Work WeekG= Pb−Free Package(Note: Microdot may be in either location)ELECTRICAL CHARACTERISTICS (T A = 25°C unless otherwise noted)CharacteristicSymbolMinMaxUnitOFF CHARACTERISTICS (Note 2)Collector −Emitter Breakdown Voltage (Note 2)(I C = −1.0 mAdc, I B = 0)V (BR)CEO −40−VdcCollector −Base Breakdown Voltage (I C = −10 m Adc, I E = 0)V (BR)CBO −40−Emitter −Base Breakdown Voltage (I E = −10 m Adc, I C = 0)V (BR)EBO−5.0−Base Cutoff Current(V CE = −30 Vdc, V EB = −3.0 Vdc)I BL −−50nAdc Collector Cutoff Current(V CE = −30 Vdc, V EB = −3.0 Vdc)I CEX−−50ON CHARACTERISTICS (Note 2)DC Current Gain(I C = −0.1 mAdc, V CE = −1.0 Vdc)(I C = −1.0 mAdc, V CE = −1.0 Vdc)(I C = −10 mAdc, V CE = −1.0 Vdc)(I C = −50 mAdc, V CE = −1.0 Vdc)(I C = −100 mAdc, V CE = −1.0 Vdc)H FE60801006030−−300−−−Collector −Emitter Saturation Voltage (I C = −10 mAdc, I B = −1.0 mAdc)(I C = −50 mAdc, I B = −5.0 mAdc)V CE(sat)−−−0.25−0.4VdcBase −Emitter Saturation Voltage (I C = −10 mAdc, I B = −1.0 mAdc)(I C = −50 mAdc, I B = −5.0 mAdc)V BE(sat)−0.65−−0.85−0.95SMALL −SIGNAL CHARACTERISTICS Current −Gain − Bandwidth Product(I C = −10 mAdc, V CE = −20 Vdc, f = 100 MHz)f T 250−MHz Output Capacitance(V CB = −5.0 Vdc, I E = 0, f = 1.0 MHz)C obo − 4.5pFInput Capacitance(V EB = −0.5 Vdc, I C = 0, f = 1.0 MHz)C ibo −10Input Impedance(I C = −1.0 mAdc, V CE = −10 Vdc, f = 1.0 kHz)h ie 2.012k W Voltage Feedback Ratio(I C = −1.0 mAdc, V CE = −10 Vdc, f = 1.0 kHz)h re 0.110X 10−4Small −Signal Current Gain(I C = −1.0 mAdc, V CE = −10 Vdc, f = 1.0 kHz)h fe 100400−Output Admittance(I C = −1.0 mAdc, V CE = −10 Vdc, f = 1.0 kHz)h oe 3.060m mhos Noise Figure(I C = −100 m Adc, V CE = −5.0 Vdc, R S = 1.0 k W , f = 1.0 kHz)NF−4.0dB SWITCHING CHARACTERISTICS Delay Time (V CC = −3.0 Vdc, V BE = 0.5 Vdc,I C = −10 mAdc, I B1 = −1.0 mAdc)t d −35nsRise Time t r −35Storage Time (V CC = −3.0 Vdc, I C = −10 mAdc,I B1 = I B2 = −1.0 mAdc)t s −225Fall Timet f−752.Pulse Width ≤ 300 m s, Duty Cycle ≤ 2.0%.Figure 1. Delay and Rise Time Equivalent Test Circuit Figure 2. Storage and Fall Time Equivalent Test Circuit10 < t1 < 500* T otal shunt capacitance of test jig and connectorsTYPICAL TRANSIENT CHARACTERISTICSFigure 3. CapacitanceREVERSE BIAS (VOLTS)2.03.05.07.0101.0Figure 4. Charge DataI C , COLLECTOR CURRENT (mA)C A P A C I T A N C E (p F )T J = 25°C T J = 125°CFigure 5. Turn −On Time I C , COLLECTOR CURRENT (mA)7010020030050050T I M E (n s )1.02.03.01020705100Figure 6. Fall TimeI C , COLLECTOR CURRENT (mA)5.07.0305020010307201.02.03.010*******5.07.03050200TYPICAL AUDIO SMALL −SIGNAL CHARACTERISTICSNOISE FIGURE VARIATIONS(V CE = −5.0 Vdc, T A = 25°C, Bandwidth = 1.0 Hz)Figure 7. f, FREQUENCY (kHz)2.03.04.05.01.00.1Figure 8.R g , SOURCE RESISTANCE (k OHMS)N F , N O I S E F I G U R E (d B )1.02.0 4.01020400.20.401000.1 1.0 2.0 4.01020400.20.4100h PARAMETERS(V CE = −10 Vdc, f = 1.0 kHz, T A = 25°C)Figure 9. Current GainI C , COLLECTOR CURRENT (mA)7010020030050Figure 10. Output AdmittanceI C , COLLECTOR CURRENT (mA)h , D C C U R R E N T G A I Nh , O U T P U T A D M I T T A N C E ( m h o s )Figure 11. Input Impedance I C , COLLECTOR CURRENT (mA)Figure 12. Voltage Feedback RatioI C , COLLECTOR CURRENT (mA)301005010202.03.05.07.0101.00.10.21.02.0 5.00.5100.30.5 3.00.72.05.010201.00.20.5o e h , V O L T A G E F E E D B A C K R A T I O (X 10 )r e h , I N P U T I M P E D A N C E (k O H M S )i e 0.10.21.02.0 5.0100.30.5 3.00.10.21.02.0 5.0100.30.5 3.0750.10.21.02.0 5.0100.30.5 3.0f e m −470300.77.00.77.07.03.00.70.30.77.00.77.0TYPICAL STATIC CHARACTERISTICSFigure 13. DC Current GainI C , COLLECTOR CURRENT (mA)0.30.50.71.02.00.20.1h , D C C U R R E N T G A I N (N O R M A L I Z E D )0.5 2.0 3.010500.20.30.11.00.730205.07.0F E Figure 14. Collector Saturation RegionI B , BASE CURRENT (mA)0.40.60.81.00.20.1V , C O L L E C T O R E M I T T E R V O L T A G E (V OL T S )0.5 2.0 3.0100.20.301.00.7 5.07.0CE 0.070.050.030.020.01Figure 15. “ON” Voltages I C , COLLECTOR CURRENT (mA)0.40.60.81.00.2Figure 16. Temperature CoefficientsI C , COLLECTOR CURRENT (mA)V , V O L T A G E (V O L T S )PACKAGE DIMENSIONSSOT −223 (TO −261)CASE 318E −04ISSUE LSTYLE 1:PIN 1.BASE2.COLLECTOR3.EMITTER4.COLLECTORNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.DIM A MIN NOM MAX MIN MILLIMETERS1.50 1.63 1.750.060INCHESA10.020.060.100.001b 0.600.750.890.024b1 2.90 3.06 3.200.115c 0.240.290.350.009D 6.30 6.50 6.700.249E 3.30 3.50 3.700.130e 2.20 2.30 2.400.0870.850.94 1.050.0330.0640.0680.0020.0040.0300.0350.1210.1260.0120.0140.2560.2630.1380.1450.0910.0940.0370.041NOM MAX L1 1.50 1.75 2.000.0606.707.007.300.2640.0690.0780.2760.287H E −−e10°10°0°10°q*For additional information on our Pb −Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION分销商库存信息:ONSEMIPZT3906T1PZT3906T1G。

AA3528SESJ3-AMT;中文规格书,Datasheet资料

3.5x2.8mm SURFACE MOUNT LED LAMP 3. The specifications, characteristics and technical data described in the datasheet are subject to change without prior notice.Selection GuideNotes:1. θ1/2 is the angle from optical centerline where the luminous intensity is 1/2 of the optical peak value.2. Luminous intensity/ luminous Flux: +/-15%.Part No.DiceLens TypeIv (mcd) [2] @ 20mA Viewing Angle [1] Code. Min. Max. 2θ1/2AA3528SES/J3-AMT Hyper Red (AlGaInP) Water Clear120°V 1300 1600W 1600 1900 X 1900 2300 Y 2300 2700ParameterSymbol Value Unit Power dissipation P D 140 mW Reverse Voltage V R 5 V Junction temperature T J 120 °C Operating Temperature Top -40 To +100 °C Storage Temperature Tstg -40 To +120°C DC Forward Current[1] I F 50 mA Peak Forward Current [2]I FM150 mA Electrostatic Discharge Threshold (HBM) 3000 V Thermal Resistance (Junction/ambient) [1]R th j-a 350°C/WNotes:1.The dominant Wavelength (λ d) above is the setup value of the sorting machine. (Tolerance λ d : ±1nm. )2. Forward Voltage: +/-0.1V.Electrical / Optical Characteristics at T a =25°CNotes:1. Rth(j-a) Results from mounting on PC board FR4 (pad size ≥16 mm 2 per pad),2. 1/10 Duty Cycle, 0.1ms Pulse Width.Absolute Maximum Ratings at T a =25°CParameterSymbol Value Unit Wavelength at peak emission I F =20mA [Typ.]λpeak 640 nm Dominant Wavelength I F =20mA [Min.] λ dom [1] 615 nm Dominant Wavelength I F =20mA [Max.] λ dom [1] 635 nm Spectral bandwidth at 50%ΦREL MAXI F =20mA [Typ.]Δλ25 nmForward Voltage I F =20mA [Min.] V F [2]-VForward Voltage I F =20mA [Typ.] 2.2 Forward Voltage I F =20mA [Max.] 2.8Reverse Current (V R = 5V) [Max.] I R 10 uA Temperature coefficient of λpeak I F =20mA, -10°C ≤ T ≤100°C [Typ.] TC λpeak 0.14 nm/°C Temperature coefficient of λdom I F =20mA, -10°C ≤ T ≤100°C [Typ.] TC λdom 0.04 nm/°C Temperature coefficient of V FI F =20mA, -10°C ≤ T ≤100°C [Typ.]TC V-2.0mV/°CReliability Test Items And ConditionsThe reliability of products shall be satisfied with items listed below Lot Tolerance Percent Defective (LTPD) : 10%No. Test Item Standards Test Condition Test Times /CyclesNumber ofDamaged1 Continuous operating test - Ta =25°C ,IF = maximum rated current* 1,000 h 0 / 222 High Temp. operating test EIAJ ED-4701/100(101)Ta = 100°C IF = maximum rated current* 1,000 h 0 / 223 Low Temp. operating test - Ta = -40°C, IF = maximum rated current* 1,000 h 0 / 224 High temp. storage test EIAJ ED-4701/100(201)Ta = maximum rated storage temperature 1,000 h 0 / 225 Low temp. storage test EIAJ ED-4701/100(202)Ta = -40°C 1,000 h 0 / 226 High temp. & humidity storage test EIAJ ED-4701/100(103)Ta = 60°C, RH = 90% 1,000 h 0 / 227 High temp. & humidity operating test EIAJ ED-4701/100(102)Ta = 60°C, RH = 90%IF = maximum rated current*1,000 h 0 / 228 Soldering reliability test EIAJ ED-4701/100(301)Moisture soak : 30°C,70% RH, 72hPreheat : 150~180°C(120s max.)Soldering temp : 260°C(10s)3 times 0 / 189 Thermal shock operating test - Ta = -40°C(15min) ~ 100°C(15min)IF = derated current at 100°C1,000 cycles 0 / 2210 Thermal shock test - Ta = -40°C(15min) ~ maximum ratedstorage temperature(15min)1,000 cycles 0 / 2211 Electric Static Discharge (ESD) EIAJ ED-4701/100(304)C = 100pF , R2 = 1.5KΩ V = 3000VOnce eachPolarity0 / 2212 Vibration test - a = 196m/s² , f = 100~2KHz ,t = 48min for all xyz axes4 times 0 / 22* : Refer to forward current vs. derating curve diagramItems Symbols Conditions Failure Criterialuminous Intensity lv I F = 20mA Testing Min. Value <Spec.Min.Value x 0.5 Forward Voltage V F I F = 20mA Testing Max. Value ≥Spec.Max.Value x 1.2 Reverse Current I R V R = Maximum Rated Reverse Voltage Testing Max. Value ≥Spec.Max.Value x 2.5High temp. storage test - - Occurrence of notable decoloration, deformation and crackingFailure Criteria分销商库存信息: KINGBRIGHTAA3528SES/J3-AMT。

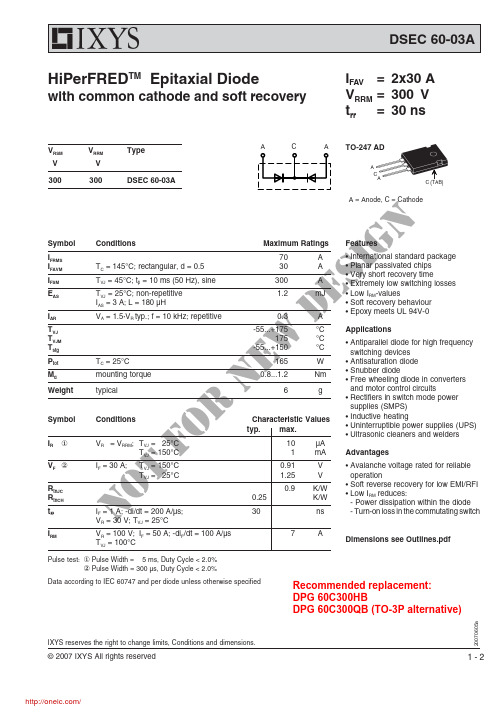

DSEC60-03A;中文规格书,Datasheet资料

Conditions

or VR = VRRM; TVJ = 25°C TVJ = 150°C

f IF = 30 A; TVJ = 150°C

TVJ = 25°C

ot IF = 1 A; -di/dt = 200 A/µs; NVR = 30 V; TVJ = 25°C

10

µA

1 mA Advantages

0.91

V

• Avalanche voltage rated for reliable

1.25

V

operation

0.25

0.9

K/W K/W

• Soft reverse recovery for low EMI/RFI • Low IRM reduces:

- Power dissipation within the diode

.+175

°C

175

°C

-55...+150

°C

w165

W

e0.8...1.2

Nm

n6

g

Applications

• Antiparallel diode for high frequency switching devices

• Antisaturation diode • Snubber diode • Free wheeling diode in converters

DSEC 60-03A

HiPerFREDTM Epitaxial Diode

with common cathode and soft recovery

IFAV = 2x30 A VRRM = 300 V trr = 30 ns

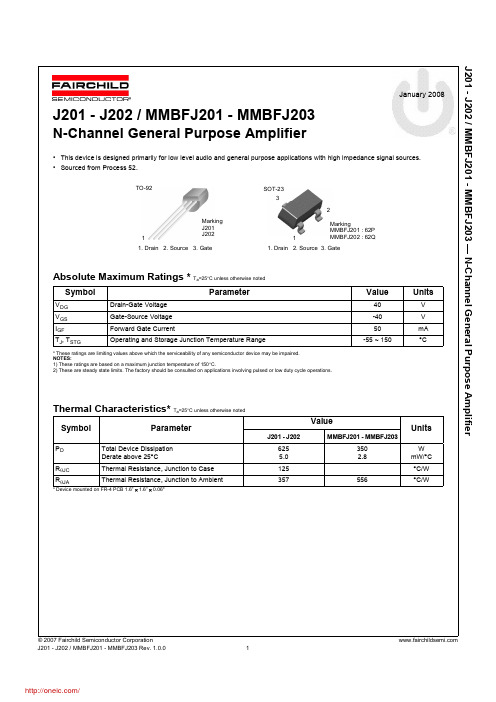

MMBFJ201;中文规格书,Datasheet资料