基于 FPGA 的 AD 采样设计

FPGA实现的AD采样控制程序的源码

采用双进程有限状态机的方法来实现。

设计st0~st7八个工作状态。

st0:初始化。

st1:产生ALE的上升沿将模拟通道IN1的地址锁存。

st2:产生START信号上升沿,启动A/D转换。

st3:START信号延时一个脉冲。

st4:A/D转换中,等待。

st5:转换结束,开启输出允许信号OE。

st6:OE延时一个脉冲,并开启数据锁存信号LOCK。

st7:延时一个时钟,输出数据。

状态转换方式见下面程序段。

case current_state iswhen st0=> ale<='0';start<='0';oe<='0';lock<='0'; next_state<=st1;---初始态ST0向下一状态ST1转换,0809采样控制信号初始化;when st1=> ale<='1';start<='0';oe<='0';lock<='0'; next_state<=st2;---由ALE的上升沿将通道地址'001'锁入0809的地址寄存器;when st2=> ale<='1';start<='1';oe<='0';lock<='0'; next_state<=st3; ---启动采样信号;when st3=> ale<='0';start<='1';oe<='0';lock<='0';if(eoc='0') then next_state<=st4; ---转换即将结束,转换至下一状态;else next_state<=st3; ---转换未结束,继续在状态ST3中等待;end if;when st4=> ale<='0';start<='0';oe<='0';lock<='0';if(eoc='1') then next_state<=st5; ---EOC由0恢复1,转换结束;else next_state<=st4; ---转换未结束,等待;end if;when st5=> ale<='0';start<='0';oe<='1';lock<='0'; next_state<=st6; --开启输出允许OE;when st6=> ale<='0';start<='0';oe<='1';lock<='1'; next_state<=st7; --开启数据锁存LOCK;when st7=> ale<='0';start<='0';oe<='0';lock<='1'; next_state<=st0;when others=>next_state<=st0; ---其它状态返回ST0;end case;---------------------------------------------------------------________________________________________ A/D采样控制与数据转换的部分程序及仿真采用QuartusⅡ软件平台下的VHDL语言编程实现。

基于fpga的adc采样控制电路设计

基于fpga的adc采样控制电路设计FPGA(现场可编程门阵列)是一种高度可编程的数字电路设计工具,可用于实现各种应用。

ADC(模拟数字转换器)是一种电子设备,用于将模拟信号转换为数字信号。

在本文中,我们将设计一个基于FPGA的ADC采样控制电路。

首先,我们需要选择一个合适的ADC芯片,以满足我们的需求。

ADC芯片通常具有不同的分辨率(以位为单位)和采样速率(以样本/秒为单位)。

选择适当的芯片将取决于被测信号的频率范围和精度要求。

一旦我们选择了ADC芯片,我们可以开始设计采样控制电路。

ADC采样控制电路的主要任务是控制ADC芯片的采样频率和采样精度。

首先,我们需要使用FPGA来生成一个时序信号,用于控制ADC芯片的采样。

此时序信号应具有适当的频率,以保证ADC芯片的采样和转换过程正常运行。

然后,我们需要将ADC芯片的采样结果传递给FPGA。

为此,我们可以使用串行通信接口(如SPI或I2C),在ADC芯片和FPGA之间建立一个数据通道。

通过该通道,ADC芯片的采样结果将传输到FPGA中进行后续处理。

一旦ADC芯片的采样结果进入FPGA,我们可以进行进一步的数字信号处理。

我们可以使用FPGA内部的逻辑电路和存储器来实现数字滤波、数字滤波等功能。

这些功能可以根据特定应用的需求进行定制。

最后,我们可以将FPGA处理后的数字信号输出到外部设备(如计算机)或其他电路中。

这些输出信号可以用于进一步分析、控制或存储。

总之,基于FPGA的ADC采样控制电路是一种常见的电路设计方法,可用于实现各种实时信号处理和控制应用。

通过适当选择ADC芯片和设计有效的采样控制电路,我们可以在FPGA上实现高性能、低功耗的ADC系统。

这种设计方法具有灵活性和可扩展性,适用于各种应用领域,如通信、医疗、工业控制等。

基于FPGA的高速多通道AD采样系统的设计与实现_徐加彦

数转换芯片, 具有 8 通道同时采样,16 位输出的特

点,是一款高分辨率、双极性输入、同步采样的高性

能 模 数 转 换 芯 片 。 采 用 Altera 公 司 的EP2C35F672

可编程逻辑控制器件对 AD7606 进行时序控制。 并

在 FPGA 里设置一块双口 RAM,存储 AD7606 的数

输出条件

输出

图 2 有限状态机模型 Fig.2 Model of finite state machine

在数字电路中,状态机可用可编程逻辑控制器 件来建造,通过寄存器来储存状态变量,确定状态 转移的一块组合逻辑和确定状态机输出的另一块 组合逻辑。 2.3 时序程序的设计

有限状态机的设计对系统的高速性能、高可靠 性、稳定性都具有决定性作用。 采用状态机的形式, 在每个状态中,状态机可并行同步完成许多运算和 控制操作, 相比于 CPU 按照指令逐条运行的方式, 一 般 有 状 态 机 构 成 的 硬 件 系 统 比 对 应 的CPU 完 成 同样功 能 的 软 件 系 统 的 工 作 速 度 要 高 出 3~5 个 数 量级。 在可靠性能方面,状态机是在FPGA 通 过 纯 硬 件 电 路 构 成 , 其 运 行 不 依 赖 软 件 指 令 逐 条执行,因 此不存在 CPU 运行软件过程中的许多缺陷[3]。

基于FPGA的多路AD自动采集系统设计初稿

基于FPGA多路A/D自动采集采集系统设计摘要:在以往AD采集中,通过微控制器控制A/D芯片复杂的逻辑,不仅增加了微控制器干预,从而影响处理器运行速度,同时由于微控制器不断介入A/D控制会影响程序正常运行。

本文概述了基于FPGA的多路数据自动采集系统的设计和实现过程。

该系统采用高速A/D转换器将多路模拟信号转换成数字信号,以FPGA为控制核心产生各种控制时序,控制A/D和模拟量开关切换,并对转换结果进行数据读取保存在双口RAM中,通过试验验证表明该系统工作稳定,能够实现对多路采集信号实时采集处理,检测效果良好。

关键词:FPGA A/D转换自动采集Design of automatic acquisition and acquisition system based on FPGA multi A/DAbstract: In the past, A/D acquisition through the micro controller to control the complexity of the A/D chip logic. That not only increased the micro controller intervention, so that affecting the operating speed of the processor, but also affected the normal operation of the program when the micro controller continuous intervention the A/D conversion. This paper Summary the design and implementation of high speed multi channel data acquisition system based on FPGA, The system uses high speed A/D converter to convert multiple analog signals into digital signals. The FPGA is used as control core to generate various control timing, which is used to control A/D and analog switch, at the same time, the data that is converted is stored in dual port RAM. Through the experiment, the system is proved to can stably real-time process for multi-channel signal acquired system, and the examination effect is good. Key words: A/D FPGA Automatic Acquisition1 引言在高速多路数据采集系统中,通常采用数字信号处理器DSP或单片机作为微控制器,控制模数转换器AD及其他外围设备的工作。

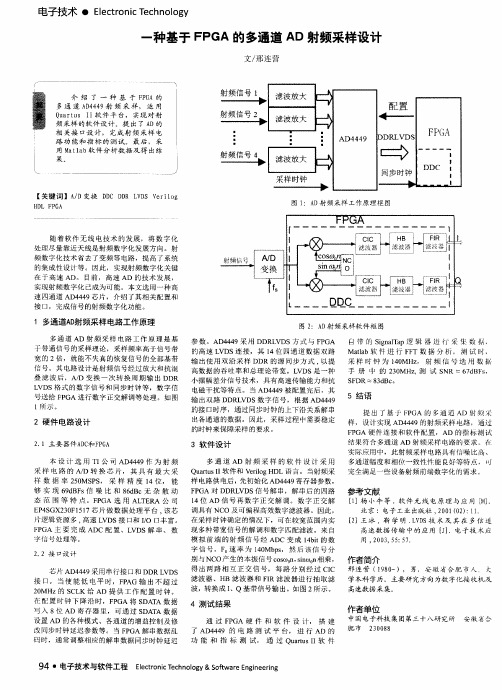

一种基于FPGA的多通道AD射频采样设计

参 数 。AD4449采 用 DDRLVDS方 式 与 FPGA 的高速 LVDS连接,其 14位 四通道 数据双路 输 出使 用 双 沿 采 样 DDR 的源 同步 方 式 ,以提 高 数 据 的吞 吐 率 和 总 理 论 带 宽 。LVDS是 一 种 小 摆 幅 差 分 信 号 技 术 , 具 有 高速 传 输 能 力和 抗 电磁 干 扰 等 特 点 。当 AD4449被 配 置 完 后 , 其 输 出双路 DDRLVDS数 字信 号,根据 AD4449 的接 口时序,通 过同步时钟的上下沿 关系解 串 出 各 通 道 的 数 据 。 因 此 , 采样 过 程 中 需 要稳 定 的 时 钟 来 保 障采 样 的要 求 。

2 硬 件 电 路 设 计

2.1 主要 器 件 ADC和 FPGA

本 设 计 选 用 TI公 司 AD4449作 为 射 频 采 样 电 路 的 A/D 转 换 芯 片 , 其 具 有 最 大 采 样 数 据 率 250MSPS, 采 样 精 度 14位, 能 够 实 现 69dBFs信 噪 比 和 86dBc无 杂 散 动 态 范 围 等 特 点 。FPGA 选 用 ALTERA 公 司 EP4SGX230F1517芯 片 做 数 据 处 理 平 台 .该 芯 片 逻 辑 资 源 多 ,高速 LVDS接 口和 I/O 口丰 富 。 FPGA 主 要 完 成 ADC 配 置 、LVDS解 串 、 数 字 信 号 处 理 等 。

基于FPGA的ADC采集系统的设计_毕业设计论文

基于FPGA的ADC采集系统的设计摘要基于FPGA在高速数据采集方面有单片机和DSP无法比拟的优势,FPGA具有时钟频率高,内部延时小,全部控制逻辑由硬件完成,速度快,效率高,组成形式灵活等特点。

因此,本文研究并开发了一个基于FPGA的数据采集系统。

FPGA的IO口可以自由定义,没有固定总线限制更加灵活变通。

本文中所提出的数据采集系统设计方案,就是利用FPGA作为整个数据采集系统的核心来对系统时序和各逻辑模块进行控制。

依靠FPGA强大的功能基础,以FPGA作为桥梁合理的连接了ADC、显示器件以及其他外围电路,最终实现了课题的要求,达到了数据采集的目的。

关键词FPGA A/D转换AbstractFPGA is better than microcontroller and DSP in high speed data acquisition, FPGA has higher internal clock frequency, smaller delay than DSP,and all the control logic of FPGA is completed by hardware, FPGA has fast speed, high efficiency, and so on. Therefore, this paper introduces and develops a data acquisition system which is based on FPGA.The I/O pin of FPGA can be defined yourself without fixed limit,it’s very flexible. This design of data acquisition system use FPGA as the data acquisition system core to control the timing and the logic control module. Relying on the powerful function of FPGA, FPGA can connect ADC, display devices and other peripheral circuits, finally we can achieve the requirements of the subject, and the purpose of the data collection。

基于FPGA的高速A/D采样的实现

一

、

。GA P

F G 是 现 场 可 编 程 门 阵 列 ( id Porm b G t PA Fe rga mal a l e e

Ar ) r y 的简称 , a 是一种由用户实现芯片功能的器件 , 用户在设计 完成之后 可以进行功能和时序仿真 , 也可 以现场编程进行验证 ,

在4 K波特至 6 0 0 4 K波特之 间, 我们对信 号采用 I0解调Fra bibliotek式 , / 对

表 3 客户端速度测试结果

测试用例 同时传输会话数 传输时间( 秒) 】5 7 25 9

24 6 26 5

25 5 26 5

结果 7 MBS j2 , 43 4MBS /

C l A ry , C 由 可 配 置 逻 辑 模 块 C B( o f ual oi e r ) L A l a L C n grbe gc i L

Bok 、 l )输出输入模块 l B Ip tO tu lc ) c O (n u up tBok 和内部连线 3 类

可编 程单 元 组 成 。 其特 点 主要 有 : 用 FG 采 P A设 计 专 用 集 成 电 路 A I SC ( p l a o pcf n ga d Crut)真 正 达 到 用 户 自行 设 A pi t n S eicIt rt i i , ci i e e c s

1 " 3 , 526 节 0 144 , 字 0 9 1 " 3 , 526 节 0 144 , 字 0 9

1 I 44 5 2 0 3 .0 .96 l 3 .0 , 9 0 l 44 5 2 6

基于FPGA的多通道采样系统设计课程设计论文

FPGA课程设计题目:基于FPGA的多通道采样系统设计院(系):电气工程及其自动化学院专业:电子信息工程12-01摘要本论文介绍了基于FPGA的多通道采样系统的设计。

用FPGA设计一个多通道采样控制器,利用VHDL语言设计有限状态机来实现对AD7892的控制。

由于FPGA器件的特性是可以实现高速工作,为此模拟信号选用音频信号。

由于音频信号的频率是20Hz-20KHz,这样就对AD转换的速率有很高的要求.因为FPGA的功能很强大,所以我们把系统的许多功能都集成到FPGA器件中,例如AD通道选择部分,串并输出控制模块,这样使得整个系统的外围电路简单、系统的稳定性强。

FPGA的配置模式选用被动串行模式,这样就增强了系统的可扩展性。

输出模式可选择性使得系统的应用相当广泛,串行输出可以用于通信信号的采集,方便调制后发射到远程接受端,远程接收端对采集的数据进行解调;而并行输出模式则可以通过高速存储器将采集的信号放到微机或者其他的处理器上,根据采集的数据进行相应的控制。

此系统的缺点是由于FPGA器件配置是基于SRAM查找表单元,编程的信息是保持在SRAM中,但SRAM在掉电后编程信息立即丢失,所以每次系统上电都需要重新配置芯片,这对在野外作业的工作人员很不方便,解决的方法是专用的配置器件来配置FPGA,在每次系统上电的时候会自动把编程信息配置到FPGA芯片中。

但设计中没有采用到这种配置方案主要是考虑到专用配置器件的价格问题。

本文开始介绍了多通道系统的组成部分,然后分别介绍了各个组成部分的原理和设计方法,其中重点介绍了FPGA软件设计部分。

还对当前十分流行的基于FPGA的设计技术作了简单的阐述,最后对系统的调试和应用作了简短的说明。

关键词:音频放大;滤波器;FPGA;VHDL;AD7892;有限状态机;目录摘要 (2)引言 (3)1题目来源 (3)2研究意义 (3)3多通道采样系统的组成 (3)4方案设计 (4)5 单元电路的设计 (4)5.1音频放大、滤波部分 (4)(1)音频放大部分 (4)(2)有源滤波器的设计 (4)5.2 AD采样电路 (5)5.3 FPGA控制部分 (5)(1)通道选择模块 (6)(2)延时模块的设计 (6)(3)串并输出选择控制 (7)5.4 FPGA的硬件设计 (8)6 软件介绍 (8)7 整机调试 (8)7.1 硬件电路的调试步骤 (8)(1)音频放大部分调试 (8)(2)滤波部分调试 (8)(3)FPGA硬件电路调试 (9)(4)AD采样模块调试 (9)(5) 联机调试 (9)8 结论 (9)参考文献 (10)附录 (11)引言FPGA(Field-Programmable Gate Array 现场可编程门阵列)是近年来广泛应用的超大规模、超高速的可编程逻辑器件,由于其具有高集成度(单片集成的系统门数达上千万门)、高速(200MHz 以上)、在线系统可编程等优点,为数字系统的设计带来了突破性变革,大大推动了数字系统设计的单片化、自动化,提高了单片数字系统的设计周期、设计灵活性和可靠性。

基于FPGA的AD采样实现

十簟科覃|: 一一—叫!卢mm

∞3 MI}m#∞F11GA;m

用~III¨_语j宴&盯【)采样的程序Ⅻ下

d“hilellum

h,hav

nf

n{8x1198

ratqe 0

is m 7・

一一signal㈣umI:inl。ger }F*…

…ss(…Ik

I’gin

I,r1411k)

1”c8f“

…,b—爿mm。・'

pJljIk时钟班4群将幂统时钟I,ll一一1k进{imj}糖后犄m一路

辘小f二哮ad—elk作~Maxll98的1.fi:nf钟时钟的-1i±比为i:i;

日路信号…,I

c

tIk作为内部采样寄存器的输^时钟占±m

在50MHz输^壤半和100MsPs采样建半F.达到48I—IB的情号

与雌声自啦捶& YPGj.采Ⅲ^lIt ra*-d生J6的EI'2CSQ2()8 0H内雌县有 8256个l船.36个M4K RAM块.总RAM数达到165 888忙另外 内部集J赴两个锁栩环f PII).镄相环地庙辅出时钟顿牢Ⅲ逃

自日2¨孙岩^m的辖^时钟cI K的J.升沿到达时射起到 60目■#拄∞10121

■4帅{#H■∞■

奉m笔舌利用pFG s,完成高4熬据采集具有采样速丰高 电路实现简单的优点通过&宴际的XtI[}幕境中也喟验《填 *芷r系统要求■

万方数据

}|{米.进{r数卒情#姓埋和存赭转换篝t怍从Ⅲ挺高rI)SI’的

变时处理能力和上作效阜 =,器件的选择 AI]C采ⅢM“…-公q的M 4X1198.E屉3 3V.Ⅱ墟堪H位模 数转换器.H籍仝牟分宽带鬻忏/保持(T/It)输^可U州时W 动2蹄ADC T怍干2

7V一3 6V单电埠潲耗功率倥为264m日,

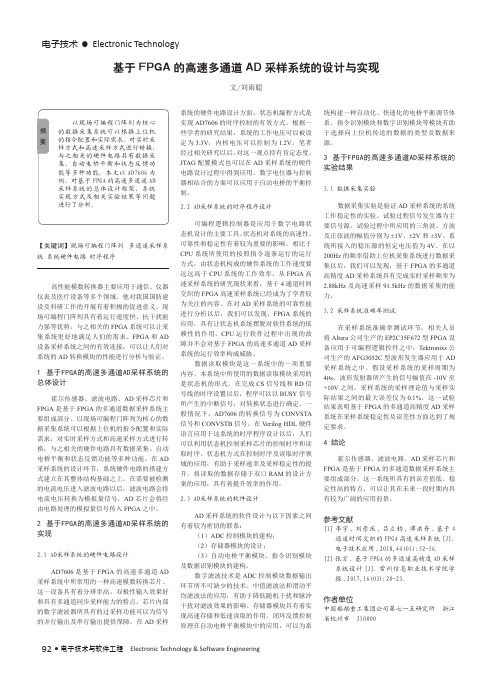

基于FPGA的高速多通道AD采样系统的设计与实现

电子技术• Electronic Technology92 •电子技术与软件工程 Electronic Technology & Software Engineering【关键词】现场可编程门阵列 多通道采样系统 系统硬件电路 时序程序高性能模数转换器主要应用于通信、仪器仪表及医疗设备等多个领域。

他对我国国防建设及科研工作的开展有着积极的促进意义。

现场可编程门阵列具有着运行速度快、抗干扰能力强等优势,与之相关的FPGA 系统可以让采集系统更好地满足人们的需求。

FPGA 和AD 设备采样系统之间的有效连接,可以让人们对系统的AD 转换模块的性能进行分析与验证。

1 基于FPGA的高速多通道AD采样系统的总体设计霍尔传感器、滤波电路、AD 采样芯片和FPGA 是基于FPGA 的多通道数据采样系统主要组成部分。

以现场可编程门阵列为核心的数据采集系统可以根据上位机的指令配置和实际需求,对实时采样方式和高速采样方式进行转换,与之相关的硬件电路具有数据采集、自动电桥平衡和状态反馈功能等多种功能。

在AD 采样系统的设计环节,系统硬件电路的搭建方式建立在其整体结构基础之上。

在需要被检测的电流电压进入滤波电路以后,滤波电路会将电流电压转换为模拟量信号,AD 芯片会将经由电路处理的模拟量信号传入FPGA 之中。

2 基于FPGA的高速多通道AD采样系统的实现2.1 AD采样系统的硬件电路设计AD7606是基于FPGA 的高速多通道AD 采样系统中所常用的一种高速模数转换芯片。

这一设备具有着分辨率高、双极性输入效果好和具有多通道同步采样能力的特点。

芯片内部的数字滤波器所具有的过采样功能可以为信号的并行输出及串行输出提供保障。

在AD 采样基于FPGA 的高速多通道AD 采样系统的设计与实现文/刘雨聪系统的硬件电路设计方面,状态机编程方式是实现AD7606的时序控制的有效方式。

根据一些学者的研究结果,系统的工作电压可以被设定为3.3V ,内核电压可以控制为1.2V 。

基于FPGA的多通道高精度AD采样系统设计

第16卷第3期2017年6月常州信息职业技术学院学报Journal of Changzhou College of Information TechnobgyVoL16 No.3Jun.2017基于F P G A的多通道高精度A D采样系统设计张言(西安电子科技大学陕西西安710071)摘要:在基于F P G A的永磁直线电机直接推力控制系统中,控制算法需要精确采样永磁直线电机的三相电压与电流,以提高 控制系统的性能。

针对这一问题,设计了一套基于F P G A的多通道高精度数据采集系统。

详细介绍了系统中三相电 压与电流的采集电路、输人滤波电路、采样芯片AD7606与F P G A的接口电路以及A D转换的软件设计。

通过A D采 样程序的仿真,验证了采样系统设计的正确性。

通过实验检测,证明系统A D采样结果精度高、误差小,有助于解决直 接推力控制算法中电压电流的采样问题,提高系统可靠性。

关键词:采样系统;AD7606; A D转换;FPGA中图分类号:TP274.2 文献标志码:A文章编号:1672-2434(2017)03-0020-04Design of MuM-channel High Precision ADSanqjfing System Based on FPGAZHANG Yan(Xidian University, Xi'an 710071, China)Absteact:In the direct thrust control system of permanent magnet linear motor based on FPGA, the control algorithm needs to accurate^ san^)le the three-phase voltage and current of permanent magnet linear motor, in order to in^rove the performance of the control system. In view of this problem, a data collection system with multi-channel based on AD7606 is designed. Design of the three-phase voltage and current acquisition circuit, input filtering circuit, interface circuit between FPGA and AD7606, AD conversion program of the system are covered in the paper. The function of the program is verified by the simulation. Voltage test result shows that AD conversion result has high precision and small error, and it greatfy improves the reliability of the thrust control system.Key words: san^ling system; AD7606; AD conversion; FPGA0引言在基于FPGA的永磁直线电机直接推力控制系 统中,需要对电机的三相电流与三相电压进行实时 的采样。

基于FPGA的多通道高精度AD采样系统设计

1 系统硬件电路概述1.1 多通道数据采样系统的特点在基于FPGA的大背景下,多通道数据采样系统有着固定的结构特点。

该系统的硬件电路有固定的程序发展模式。

而永磁直接电机的运转亦有固定的步骤流程,它利用霍尔传感器传感作用,将三相电流电压传送到滤波电路,滤波电路运用数据处理能力,将相关数据转化为模拟量信号,然后通过AD7606芯片的转换功能,变成数字信号,最后传送到FPGA,通过算法处理的方式来保证控制电机的运行。

1.2 基于FPGA下,采集电机的电流电压三相电流和三相电压存在于永磁直线电机中,采集系统为了更好地采集电流电压,可以利用霍尔电流传感器LA55P和霍尔电压传感器LEM_LV25P的采集功能,研究人员在运用霍尔效应原理的基础上,研发了霍尔电流传感器,再根据安培定律。

实现电流霍尔线圈能顺利与直线电机导线相接触,保证载流导体附近存在磁场,由于系统采样电流情况与霍尔器件所存在的磁场情况成正相关关系。

电流信号保存在传感器采样后,再经过RC滤波电路和过采样电阻,最后到达输出端,电压电流采集电路经过处理,其所输出的电压信号会进入到AD采样滤波电路中,以此完成整个流转过程[1]。

2 系统设计概述2.1 AD7606的运行情况根据AD7606的工作情况,电流电压数据采集系统在利用并行模式的基础上,与AD进行转换,采集系统能对相关数据进行读取,其工作原理为先将一个高电平脉冲信号发送到在RESET引脚,利用高电平脉冲的作用,实现AD7606的复位,然后再发送一个低电平脉冲信号到CONVSTB和CONVSTA引脚,以此来促使AD转换,将BUSY引脚转化成高电平,在AD进行转换时,AD转换会发生变化,一旦AD转换完成后,BUSY引脚会转换成低电平,并且对AD7606开展读处理,并行数据总线会形成的大量数据信息,而AD7606会对这些数据信息进行读取。

AD7606能够同步采样全部8路模拟输入通道的信息。

一旦两个CONVST引脚交接起来时,全部的通过进入同步采样状态。

基于FPGA的高精度AD采样实现

49科技创新导报 Science and Technology Innovation Herald 工 业 技 术1 系统原理FP GA 可以根据用户的需要将多种芯片的功能集中实现,在可靠性要求较高,电路板要求越来越小的趋势下,FPGA的应用越来越广。

在设计完后,设计者可以对芯片的功能进行仿真验证,在线修改,大大减少了设计的复杂性。

AD7606-4是ADI公司推出的新一代16位、4通道同步采样的模拟数字转换器。

它采用5V单电源供电,不再需要正负双电源,并支持真正10V或5V的双极性信号输入。

所有的通道均能以高达200kSPS的速率进行采样。

本文研究了基于F P G A 的A /D 转换控制,图1是A /D 与FP GA 的连接框图。

A /D 的转换时间最快是5u s。

由FPG A发出转换控制信号AD_CONVST,A/D复位信号AD_R E S E T ,A/D读信号A D_RD ,读使能信号A D_CS 。

采用并行字节方式将A/D转换的信号通过数据线D A 0-D A 7读到F PG A 中。

A D 7606-4先发高字节,再发低字节;先对通道1进行转换,再对通道2,最后对通道3进行转换。

A D _R E S E T 为高电平时A /D 复位,AD _C ON VS T出现上升沿时,A /D 开始模拟信号转换,转换时间最快为5u s,设计者可以根据应用设计转换时间,在本程序中转换时间设置为10us。

模拟信号转换完的时间是2us,本程序中设计转换开始5us后,FPGA 发出AD _R D信号,可以把转换完的数字信号读到FPG A中。

图2是采用并行字节读模式的时序图。

2 VHDL 实现及仿真在Quartus II集成开发环境中,采用V H D L 实现F P G A 对A /D 的采集,系统时钟选用24Mh z,以下程序实现转换控制信号A D _C O N V S T 和读使能信号A D _C S :if clk_global'event and clk_global='1'thencount<=count+1;if count=2 then------------------实现转换信号AD_convst<='0';elsif count>=3 and count<=239 thenAD_convst<='1';end if;if count>=120 and count<=134 then -----实现C S 信号CS <='0';e ls eC S<='1';end if;if count>=239 then --计数器回零count<=0;end if;end if;仿真结果如图3所示,其中AD_data_in 是送给F P G A 的A D 转换后的数字信号,A D 1_d a t a _o u t ,A D 2_d a t a _o u t ,AD3_data_out,表示三路通道输出的16位数字信号,在本程序中只使用3路通道。

FPGA直接控制ADC0809对模拟信号进行采样设计方案

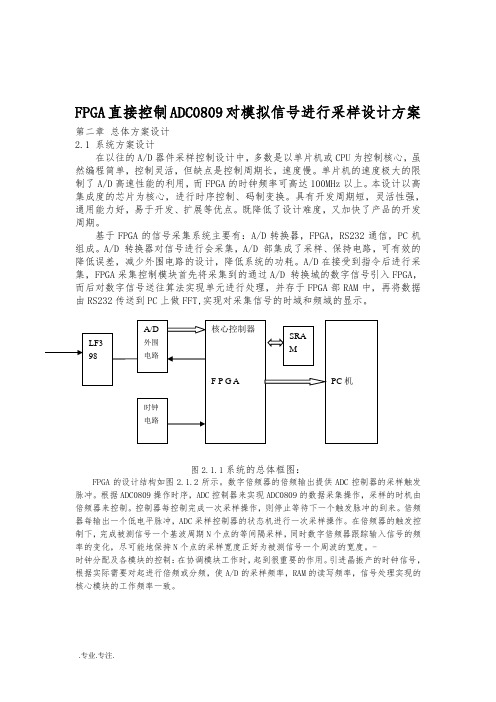

FPGA直接控制ADC0809对模拟信号进行采样设计方案第二章总体方案设计2.1 系统方案设计在以往的A/D器件采样控制设计中,多数是以单片机或CPU为控制核心,虽然编程简单,控制灵活,但缺点是控制周期长,速度慢。

单片机的速度极大的限制了A/D高速性能的利用,而FPGA的时钟频率可高达100MHz以上。

本设计以高集成度的芯片为核心,进行时序控制、码制变换。

具有开发周期短,灵活性强,通用能力好,易于开发、扩展等优点。

既降低了设计难度,又加快了产品的开发周期。

基于FPGA的信号采集系统主要有:A/D转换器,FPGA,RS232通信,PC机组成。

A/D 转换器对信号进行会采集,A/D 部集成了采样、保持电路,可有效的降低误差,减少外围电路的设计,降低系统的功耗。

A/D在接受到指令后进行采集,FPGA采集控制模块首先将采集到的通过A/D 转换城的数字信号引入FPGA,而后对数字信号送往算法实现单元进行处理,并存于FPGA部RAM中,再将数据由RS232传送到PC上做FFT,实现对采集信号的时域和频域的显示。

图2.1.1系统的总体框图:FPGA的设计结构如图2.1.2所示。

数字倍频器的倍频输出提供ADC控制器的采样触发脉冲。

根据ADC0809操作时序,ADC控制器来实现ADC0809的数据采集操作,采样的时机由倍频器来控制。

控制器每控制完成一次采样操作,则停止等待下一个触发脉冲的到来。

倍频器每输出一个低电平脉冲,ADC采样控制器的状态机进行一次采样操作。

在倍频器的触发控制下,完成被测信号一个基波周期N个点的等间隔采样,同时数字倍频器跟踪输入信号的频率的变化,尽可能地保持N个点的采样宽度正好为被测信号一个周波的宽度。

-时钟分配及各模块的控制:在协调模块工作时,起到很重要的作用。

引进晶振产的时钟信号,根据实际需要对起进行倍频或分频,使A/D的采样频率,RAM的读写频率,信号处理实现的核心模块的工作频率一致。

图2.1.2系统具体流程框图2.2 各功能模块的设计方案2.2.1 FPGA最小系统板方案设计FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物[4]。

基于FPGAad数据采集存储处理报告(含Verilog源代码)

基于FPGAad数据采集存储处理报告(含Verilog源代码)基于FPGA AD数据采集存储处理项目报告(XILINX ALTEARA 都可用)组员:华、文、杰一、实验目的本次实验利用Basys2开发板完成一个开发小项目,即开发AD数据采集存储处理系统,旨在掌握FPGA开发基本方法以及锻炼解决开发过程中出现问题的能力。

二、关键词Basys2、FPGA、AD转换、RAM、串口通信、MATLAB处理三、方案设计要实现本次项目,首先确定器件,其次根据器件时序写出模块的使用程序,最后综合成一个工程,然后进行仿真,上板实验。

本次实验的器件:32M8位模数转换器、Basys2开发板、串口转RS232cp2102模块、基于三极管的电平转换电路。

选择好器件后,根据器件的时序完成模块的代码书写。

写好AD模块、串口通信模块后,现在就需要处理采样速率与串口通讯速率不匹配的问题了。

根据香农采样定理,采样频率得高于信号频率的两倍才能完成信号复现,我们这里使用25M的高速采样频率,而串口dps9600传送一个位104us明显比采样慢许多。

所以这里需要解决速率不匹配的问题。

我们想到可以利用FPGA的RAM先存储采样来的数据,然后再提取数据经过串口通信送至PC经由MATLAB处理。

本次小项目最为关键的是控制好采样与串口通信的时序问题。

关于时序的控制,留到模块介绍里面说明。

方案小结:本次实验基于片内RAM存储AD采样过来的数据,然后待采样完成后提取数据串口通信至PC,最后经由matlab处理。

四、模块介绍1.Verilog开发程序介绍如下给出基于QuartusII绘制出的Block Diagram图,涵盖了所有的模块以及模块之间的连线。

图4.1 综合模块图如下给出程序目录(txt格式):现在分别介绍各个模块的端口以及功能。

AD外设:电路图、实物图、接口这个外设提供最大32M采样速率,包括一个模拟信号输入和一个采样时钟输入以及八个数字信号输出。

FPGA+DSP的高速AD采集处理开发详解

FPGA+DSP的⾼速AD采集处理开发详解⼀、案例说明1. Kintex-7 FPGA使⽤SRIO IP核作为Initiator,通过AD9613模块采集AD数据。

AD9613采样率为250MSPS,双通道12bit,12bit按照16bit发送,因此数据量为16bit * 2 * 250M = 8Gbps;2. AD数据通过SRIO由Kintex-7发送到C6678 DSP(Target)的0x0C3F0000~0x0C3F7FFF的地址空间,数据量为32KByte,使⽤SWRITE⽅式,期间每传16KByte数据后就发送⼀个DOORBELL信息,让C6678做乒乓处理。

Kintex-7通过SRIO与C6678连接,共4个lane,每个lane的通信速率为5Gbps,数据有效带宽为20Gbps * 80% = 16Gbps;3. 采集到的AD数据可分别通过Xilinx Vivado和TI CCS软件查看波形,并在C6678做FFT处理。

此开发案例基于创龙Kintex-7+C6678评估板TL6678F-EasyEVM进⾏。

⼆、案例框图三、案例演⽰硬件连接:将创龙AD9613⾼速AD模块TL9613/9706F(此模块集成⾼速DA,DA芯⽚为AD9706)通过FMC接⼝与评估板连接。

信号发⽣器设置成两路正弦波输出,幅度设置:1.5Vpp以及⽆直流偏置,频率设置:1MHz。

信号发⽣器的两路输出分别连接到模块的ADC_CHA、ADC_CHB。

1. FPGA端参考TL6678F-EasyEVM评估板光盘⽤户⼿册《基于下载器的程序固化与加载》⽂档中“Vivado下bit⽂件加载步骤”章节,将tl_fmc_ad9613_srio_tl6678f_xc7k325t.bit⽂件烧录到FPGA。

烧写bit⽂件时,指定调试⽂件tl_fmc_ad9613_srio_tl6678f_xc7k325t.ltx,可以观察到ILA调试信号,查看ADC采样波形。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2 系统 硬 件 整 体 设 计

AD采样 控 制 的核 心 部 分 采 用 Xi l i n x公 司 的

式, 分 析原 始 数 据 和 F P GA 输 出信 号 的 幅值 和 频

率特 性 。

的数 据采 集 系统 。在本 研究 中 , 多 通道 AD 7 6 5 6采 样芯 片 实现对 模拟 信号 的转换 , 该 芯 片最 高 采样 率

2 5 0 KHz ; F P GA提 供逻 辑控 制 , 虽 然 以传 统 的 D S P 或单 片 机作 为 C P U 的 AD采 样 系 统 控 制 简 单 , 但

Ab s t r a c t Al o n g wi t h t h e d e v e l o p me n t o f t h e c o mmu n i c a t i o n t e c h n o l o g y,Re a bt i me AD S a mp l i n g a n d t h e e f f e c t i v e p r o c e s s i n g p l a y a n i mp o r t a n t r o l e i n t h e d e s i g n o f d i g i t a l s i g n a l r e c e i v e r . A k i n d o f AD S a mp l i n g b a s e d o n F P GA i s p r o p o s e d , t h e d e s i g n o f t h e s y n c h r o n o u s s a mp l i n g c l o c k a n d F P GA c o n f i g u r a t i o n me t h o d f o r t h e AD7 6 5 6 i s p r o p o s e d,t h e s a mp l i n g d a t a a r e p r o c e s s e d b y s i n e c a r r i e r mo d u l a t i o n a n d l o w- p a s s f i l t e r i n g .F i n a l l y,t h e p r o c e s s e d d a t a a r e s h o wn i n t h e Ma t l a b .Th e e x — p e r i me n t r e s u l t s s h o w t h a t t h e d e s i g n i s s i mp l e a n d e f f e c t i v e ,h i g h l y v e r s a t i l e . K e y Wo r d s F P GA ,AD7 6 5 6 ,AD s a mp l i n g,M a t l a b s i mu l a t i o n Cl a s s Nu mb e r TP 3 3 6

De s i g n o f AD Sa mp l i ng Bas e d o n FPGA

XU Me n g j i e L I U We n c h e n g 2 L I U Y u n

( 1 .W u h a n Di g i t a l En g i n e e r i n g I n s t i t u t e ,W u h a n 4 3 0 0 7 4 ) ( 2 .Da l i a n S h i p b u i l d i n g I n d u s t r y CD. Lt d ,Da l i a n l 1 6 0 0 0 )

行 了正弦载波调制和低通滤波处理 , 最终在 Ma t l a b中显示处理后的数据 , 结果显示该设计方案简单有效 , 通用性较强 。

关键词 F P GA; AD 7 6 5 6 ; AD采样 ; Ma t l a b 仿 真 T P 3 3 6 D O I : 1 0 . 3 9 6 9 / j . i s s n 1 6 7 2 — 9 7 3 0 . 2 0 1 5 . 0 1 . 0 3 0 中图分类号

( 1 . 武汉数字工程研究所

摘 要

云

1 1 6 0 0 0 )

武汉

4 3 0 0 7 4 ) ( 2 . 大连船舶重工集 团有 限公 司 大连

随着现代通信技术的发展, A D信号的实时采样和有效处理在数字化信号接 收机 的设计 中起到重要作用E 。提

出了一种基于 F P G A的 A D采样设计 , 给出了同步采样 时钟设计 方案及 F P G A对 A D 7 6 5 6的相关 配置方法 , 并对采样数 据进

1 引 言

随着 电子 技术 的发展 , 嵌入 式 系统 结 构 的复 杂 化, 现 代工 业生 产和科 学研 究越 来 越青 睐 简单实 际 硬件 环境 供 调试

分析 , 所 以 采 用 MOD E L S I M 与 Ma t l a b联 调 的 方

Vo 1 . 3 5 No . 1

1 1 4

舰 船 电 子 工 程

S h i p El e c t r o n i c En g i n e e r i n g

总第 2 4 7 期 2 0 1 5年 第 1 期

基于 F P G A 的 AD 采 样 设 计

许 孟 杰 刘 文 臣 。 刘