RKV604KL中文资料

达克制造公司60英寸冷藏背部计数器数字说明书

OPERATION AND INSTALLATION MANUAL for 48” REFRIGERATED BACK COUNTER (RBC 48) DIGITAL60” REFRIGERATED BACK COUNTER (RBC 60) DIGITALPlease read this manual completely before attemptingto install, operate or service this equipmentThis manual is Copyright ©2012 Duke Manufacturing Company. All rights reserved.Reproduction without written permission is prohibited. Duke is a registeredtrademark of the Duke Manufacturing Company.Duke Manufacturing Company2305 N. Broadway St. Louis, MO 63102Phone: 314-231-1130 Toll Free: 1-800-735-3853Fax: 314-231-5074 RBC 60RBC 48IMPORTANT WARNING AND SAFETY INFORMATION WARNING: READ THIS MANUAL THOROUGHLY BEFORE OPERATING,INSTALLING OR PERFORMING MAINTENANCE ON THE EQUIPMENT.FAILURE TO FOLLOW INSTRUCTIONS IN THIS MANUAL CAN CAUSEPROPERTY DAMAGE, INJURY OR DEATH.DO NOT STORE OR USE GASOLINE OR OTHER FLAMMABLE VAPORSOR LIQUIDS IN THE VICINITY OF THIS OR ANY OTHER APPLIANCE.UNLESS ALL COVER AND ACCESS PANELS ARE IN PLACE ANDPROPERLY SECURED, DO NOT OPERATE THIS EQUIPMENT.CAUTION: OBSERVE THE FOLLOWING:•Minimum clearances must be maintained from all walls and combustible materials.• Keep the equipment area free and clear of combustible material.• Adequate clearance for air openings.• Unit exhausts air to the bottom and the rear.• Do not set unit on a curb or seal to the wall.• Do not block the slots in the front kickplate• Operate equipment only on the type of electricity indicated on the specification plate.• Retain this manual for future reference.Table of Contents: Introduction (4)Serial Number (4)Receiving & Inspecting the Equipment (5)Specifications (5)Installation (5)Location (5)Inside Unit (6)Leveling (6)Stabilizing (6)Electrical Connection (6)Operation (7)Location of Controls (7)Operating Procedure (7)Energy Mode Switch (7)Maintenance (7)Stainless Steel care & Cleaning (7)Cleaning the Condensor Coil (8)Door Gasket Care (9)Drain Maintenance (9)Drain Pan Access (10)INTRODUCTIONThis publication contains information regarding the installation and operation of Duke Refriger-ated Back Counter units. The information contained within applies to the models RBC 48 and RBC 60. Please read this manual completely before attempting to install and/or operate this equipment.Model number RBC 48 describes the 48” wide version of the Refrigerated Back Counter. (Fig. 1)Model number RBC 60 describes the 60” wide version of the Refrigerated Back Counter. (Fig. 2)SERIAL NUMBERAlways have the serial number of your unit available when calling for parts or service.Figure. 1 RBC 48Figure. 2 RBC 60RECEIVING & INSPECTING THE EQUIPMENTCare should be taken during unloading so the equipment is not damaged while being moved into the building.1. Visually inspect the exterior of the package and skid or container. Any damage should be noted and reported to the delivering carrier immediately.2. If damaged, open and inspect the contents with the carrier.3. In the event that the exterior is not damaged, yet upon opening, there is concealed damage to the equipment notify the carrier. Notification should be made verbally as well as in written form.4. Request an inspection by the shipping company of the damaged equipment. This should be done within 10 days from receipt of the equipment.5. Check the lower portion of the unit to be sure legs/casters are not bent.6. Also view compressor compartment housing and visually inspect the refrigeration package. Be sure lines are secure and base is still intact.7. Freight carriers can supply the necessary damage forms upon request. 8. Retain all shipping material until an inspection has been made or waived.SPECIFICATIONSINSTALLATION - LocationUnits represented in this manual are intended for indoor use only. Be sure the location chosen has a floor or counter strong enough to support the total weight of the units. Reinforce the floor or counter if necessary to provide for maximum loading. For the most efficient operation, be sure to provide good air circulation inside and out. These units should be located so that they can be moved for service. Major service to the refrigeration system is done from the end of the cabinet.The outline dimensional drawings for the units are shown in Figures 3 and 4.MODEL DESCRIPTIONVOLTAGE AMPS PHRBC 4848” Refrigerated Back Counter48” Refrigerated Back Counter with Energy Star120 VAC (60 Hz) 230 VAC (50 Hz)120 VAC (60Hz) 220 VAC (50Hz) 6 (max) 3 (max)5.5 (max) 2.5 (max) 1 1 1 1RBC 6060” Refrigerated Back Counter60” Refrigerated Back Counter with Energy Star120 VAC (60 Hz) 220 VAC (50 Hz)120 VAC (60 Hz) 220 VAC (50 Hz) 6 (max) 3 (max)5.5 (max) 2.5 (max) 1 1 1 1MODEL DESCRIPTIONHEIGHT WIDTH LENGTHRBC 48 48” Refrigerated Back Counter40.00 In.29.50 In.48.00 In.RBC 6060” Refrigerated Back Counter40.00 In.29.50 In.60.00 In.INSTALLATION – Inside UnitTake care not to block air flow to the fans and allow space along the front, back and sides.INSTALLATION – Outside UnitBe sure that the unit has access to ample air; avoid hot corners and locations near stoves and ovens.CAUTION:This unit exhausts air to the bottom and the back. Do not seal the unit to the wall or set unit on a curb. The ventilation slots in the kickplate must remain open.INSTALLATION – LevelingBe sure that the units are placed on a firm, flat surface/floor. Check for cracks in flooring or tile and avoid these areas if possible. If necessary place support pads, properly rated for the weight of the unit, to “bridge” uneven or cracked flooring. Level unit accordingly.INSTALLATION – StabilizingUse the leg adjustments to insure that the unit is solid to the floor surface at all four contact points. Insure that the unit does not “rock” when pressure is applied to the top corners.INSTALLATION – Electrical WiringThe RBC 48 and RBC 60 are available as a 120VAC, 60 Hz or as 220VAC, 50 Hz dependent on model. All electrical connections should be performed by a certified electrician and should comply with local electrical codes for your municipality.WARNING:REFER TO THE AMPERAGE DATA LIST IN THE SPECIFICATIONS OR THE SERIAL TAG DATA AND YOUR LOCAL CODE OR THE NATIONAL ELECTRICAL CODE TO BE SURE UNIT IS CONNECTED TO THE PROPER POWER SOURCE. A PROTECTED CIRCUIT OF THE CORRECT VOLTAGE AND AMPERAGE MUST BE RUN FOR CONNECTION OF THE SUPPLY CORD OR PERMANENT CONNECTION TO THE UNIT. THE POWER MUST BE TURNED OFF AND DISCONNECTED WHENEVER PERFORMING MAINTENANCE OR REPAIR FUNCTIONS.Figure. 3 RBC 48Figure. 4RBC 60OPERATION – Location of ControlsThe refrigeration control/temperature setting adjustment is located on the back splash. The energy saving mode switch (if equipped) is located inside the right front access panel. (See figure 5 & 6.) Remove front panel and access plate.These are the only user adjustable components on the unit.OPERATION – Operating ProcedurePress and hold the (i) button to display setpoint. Keep (i) button pressed and use the up/down arrows to adjust setpoint. When the (i) button is released, the new setpoint is stored. To exit from the setup, press the power button or wait 30 seconds. Display will display “dEF” while unit is in defrost mode. Check the cooling specifications required for the products/goods to be stored.Use a simple thermometer to set to a specific temperature. Allow time for temperature chang -es before making a final temperature check.OPERATION – Energy Mode SwitchWhen the mode switch (if equipped) is set to “energy save” mode, the condensate heaters around the door openings are de-energized to reduce power consumption. If condensation forms around the doors, then turn this switch to “normal” mode.MAINTENANCE – Stainless Steel Care & CleaningTo prevent discoloration or rust on stainless steel several important steps need to be taken. Stainless steel contains 70-80% iron which will rust. It also contains 12-30% chromium which forms an invisible passive film over the steels surface which acts as a shield against corrosion. As long as the protective layer is intact, the metal will not corrode. If the film is broken or contaminated, outside elements can begin to breakdown the steel and begin to form rust or discoloration.Figure. 6MAINTENANCE – Stainless Steel Care & Cleaning – cont.Proper cleaning of stainless steel requires soft cloths or plastic scouring pads.CAUTION: Never use steel pads, wire brushes or scrapers.Cleaning solutions need to be alkaline based or non-chloride cleaners. Any cleaner containing chlorides will damage the protective film of the stainless steel. Chlorides are also commonly found in hard water, salts and household and industrial cleaners. If cleaners containing chlorides are used, be sure to rinse repeatedly and dry thoroughly upon completion.Routine cleaning of stainless steel can be done with soap and water. Extreme stains or grease should be cleaned with a non-abrasive cleaner and plastic scrub pad. It is always good to rub with the grain of the steel. There are also stainless steel cleaners available which can restore and preserve the finish of the steels protective layer.Early signs of stainless steel breakdown can consist of small pits and cracks. If this has begun, clean thoroughly and start to apply stainless steel cleaners in attempt to restore the passivity ofMAINTENANCE – Cleaning the Condenser CoilThe condenser coil is located behind the filter panel and is accessed through the front of the unit (See Figure 7). Filter can be cleaned by rinsing with water. Allow to dry completely before reinstalling. The condenser coil requires regular cleaning and is recommended every 60 days. However, in some instances you may find that there is a large amount of debris, dust or grease that has accumulated prior to the 60 day time frame. In these cases the condenser coil should be cleaned every 30 days.Figure. 7MAINTENANCE – Cleaning the Condenser Coil – cont.If the build up on the coil consists of only light dust and debris the condenser coil can be cleaned with a simple brush, heavier dust buildup may require a vacuum or even compressed air to blow through the condensor coil.If heavy grease is present degreasing agents are available for refrigeration use and specifically for the condenser coils. The condenser coil may require a spray with the degreasing agent and then blown through with compressed air.Failure to maintain a clean condenser coil can initially cause high temperatures and excessive run times. Continuous operation with dirty or clogged condenser coils can result in compressor failures. Neglecting the condenser coil cleaning procedures will void any warranties associated with the compressor or cost to replace the compressor.CAUTION:NEVER USE A HIGH-PRESSURE WATER WASH FOR THIS CLEANING PROCEDURE AS WATER CAN DAMAGE ELECTRICAL COMPONENTS LOCATED NEAR OR AT THE CONDENSER COIL. MAINTENANCE – Door Gasket CareGaskets require regular cleaning to prevent mold and mildew build up and also to keep the elasticity of the gasket. Gasket cleaning can be done with the use of warm soapy water. Avoid full strength cleaning products on gaskets as this can cause them to become brittle and prevent proper seals. Also, never use sharp tools or knives to scrape or clean the gasket which could possibly tear the gasket and rip the bellows.Gaskets can easily be replaced and do not require the use of tools or authorized service persons. The gaskets are “Dart” style and can be pulled out of the grove in the door and new gaskets can be “pressed” back into place.MAINTENANCE – DrainEach unit has a copper drain tube located inside the unit which removes condensation from the evaporator coil and deposits it onto a drain pan where it can evaporate (See Fig. 8). If you notice excessive water accumulation on the inside of the unit be sure that the drain tube is connected from the evaporator housing to the condensate evaporator drain pan. If water is collecting underneath the unit you may want to check the condensate evaporator drain tube to be sure it is still located above the drain pan. The leveling of the unit is also important as the units are designed to drain properly when on a level surface, if your floor is not level this can also cause drain problems. Be sure the drain pan is kept free of dirt, dust and other debris as excessive amounts wi ll cause water to back up and overflow from the drain pan.MAINTENANCE – Drain Pan AccessThe drain pan and drain tube can be accessed from the rear of the unit. Pull the unit away from wall to expose the opening in the rear of the cabinet. The drain pan is located under the refrigeration system unit (see fig. 8)NOTES229917 11 10/03/16229917 12 10/03/16Duke Manufacturing Company 2305 N. Broadway St. Louis, MO 63102 Phone: 314-231-1130 Toll Free: 1-800-735-3853 Fax: 314-231-5074 。

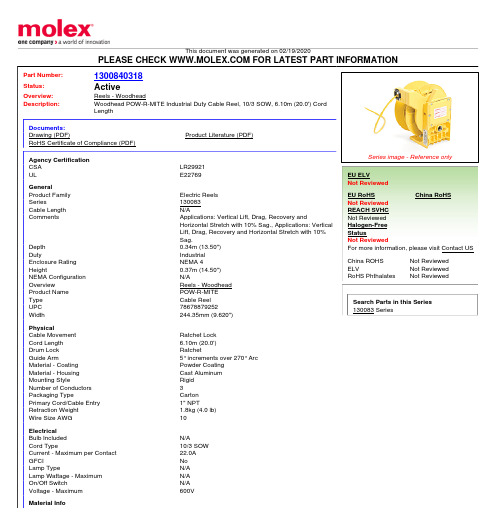

摩克斯电缆储藏轮胎产品说明说明书

Documents: Drawing (PDF) RoHS Certificate of Compliance (PDF)

Electrical Bulb Included Cord Type Current - Maximum per Contact GFCI Lamp Type Lamp Wattage - Maximum On/Off Switch Voltage - Maximum

Material Info

Product Literature (PDF)

Physical Cable Movement Cord Length Drum Lock Guide Arm Material - Coating Material - Housing Mounting Style Number of Conductors Packaging Type Primary Cord/Cable Entry Retraction Weight Wire Size AWG

N/A 10/3 SOW 22.0A No N/A N/A N/A 600V

Engineering Number

Reference - Drawing Numbers Sales Drawing

9242 SD-130084-007

This document was generated on 02/19/2020

PLEASE CHECK FOR LATEST PART INFORMATION

LR29921 E22769

k60介绍(中文)

第2章简介2.1 概要本章提供了Kinetis组合和K60系列产品的概述。

同时,本章提供了本文件所包涵设备的高水准的描述。

2.2 Kinetis组合Kinetis是低功耗可扩展和在工业上使用混合信号ARM®Cortex™-M4系列MCU的最好的组合。

第一部分介绍超过200引脚、外围设备和软件兼容性的5个MCU系列。

每个系列提供了优良的性能,与普通外设内存,内存映射,并提供内部和系列之间轻松迁移包和功能可扩展性。

Kinetis MCUs使用了飞思卡尔的新的90nm带有独特FlexMemory的薄膜存储器(TFS)闪存技术。

Kinetis系列MCU结合了最新的低功耗革新技术和高性能,高精密混合信号功能与连通,人机界面,安全及外设广泛。

Kinetis MCUs使用了飞思卡尔和ARM第三方合作伙伴的市场领先的捆绑模式。

表示低功耗混合信号USB 段LCD以太网加密和篡改检测DDR所有Kinetis系列都包涵强大的逻辑、通信和时序阵列和带有伴随着闪存大小和I/O数量的集成度等级的控制外围部件。

所有的kinetis系列包涵一下共同特征:· 内核:· ARM Cortex-M4内核提供1.25 DMIPS / MHz的DSP指令(浮点单元在kinetis系列可用)。

· 高达32位的DMA,同时尽可能减小CPU干预。

· 提供50MHz、72MHz和100MHz几种CPU频率(120MHz和150MHz在kinetis可用)。

· 超低功耗:· 10种低功耗操作模式通过优化外设执行和唤醒时间来延长电池寿命。

· 为了增加低功耗的灵活性,增加了低漏唤醒单元、低功耗定时器和低功耗RTC。

· 业界领先的快速换醒时间。

· 内存:· 从32 KB闪存/ 8 KB的RAM可扩展为1 MB闪存/128 KB的RAM。

同时使空白的独立闪存执行代码和固件更新。

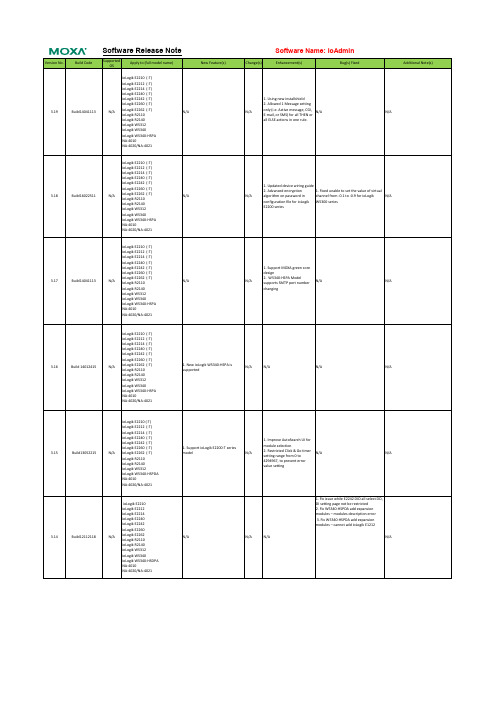

ioLogik设备说明书

ioLogik W5340

ioLogik W5340-HSPA

NA-4010

NA-4020/NA-4021

Change(s)

Software Name: ioAdmin

Enhancement(s)

Bug(s) Fixed

Additional Note(s)

1. Using new installshield

E2200 series

1. Support MOXA green core

design

N/A

2. W5340-HSPA Model supports SMTP port number

N/A

N/A

changing

ioLogik E2210 (-T)

ioLogik E2212 (-T)

ioLogik E2214 (-T)

N/A

ioLogik E2262 (-T) ioLogik R2110

N/A

ioLogik R2140

ioLogik W5312

ioLogik W5340

ioLogik W5340-HSPA

NA-4010

NA-4020/NA-4021

ioLogik E2210 (-T)

ioLogik E2212 (-T)

NA-4020/NA-4021

New Feature(s)

ioLogik E2210 (-T)

ioLogik E2212 (-T)

ioLogik E2214 (-T)

ioLogik E2240 (-T)

ioLogik E2242 (-T)

ioLogik E2260 (-T)

3.18

Build16022511

60460;中文规格书,Datasheet资料

TB-2056January 2009 Page 1 of 2Figure 1. 60460 Ionizer Mounting ArmThe Desco 60460 Ionizer Mounting Arm is designed as a mounting alternative for the 60500 Chargebuster Jr.Ionizer. The 60460 allows a Jr. Ionizer to be mounted off the bench top, saving valuable work bench space.The articulated movement of the arm assembly allows the user to focus the ionizer’s output directly onto the desired areas, or across the entire work area.The Ionizer Mounting Arm includes a C-clamp style mounting system for ease of installation. The arm also includes a three prong power cord with an IEC termination.InstallationRemove the mounting arm from the carton and inspect for damage.Included with the unit should be:C-clamp mountingsystemArm with IEC cordinstalled.Figure 2. Installing mounting arm on workbenchthe stand assembly. The 0.5" square, 20 gauge, cold rolled 40" extended 3.0 - 4.0 lbs.Figure 3. Installing Chargebuster Jr. to Ionizer Mounting ArmDESCO WEST - 3651 Walnut Avenue, Chino, CA - One Colgate Way, Canton, MA 02021-1407 • (781) 821-8370 • Fax (781) 575-0172 • Web Site: Desco expressly warrants that for a period of one (1) year from the date of purchase, Desco Ionizer Mounting Arms will be free of defects in material (parts) and workmanship (labor). Within the warranty period, a unit will be tested, repaired or replaced atDesco’s option, free of charge. Call Customer Service at 909-627-8178 (Chino, CA) or (781) 821-8370 (Canton, MA) for Return/TB-2056Page 2 of 2DESCO INDUSTRIES INC.Employee OwnedThe 19585 ionizer has been designed to be mounted at the workbench, and is controlled by a foot pedal.This allows the operator to keep both hands inoperation by controlling the ionization process by foot.This unit incorporates a filter at the point of ionization so that moisture and oil will not contaminate theionizer. The unit can also be used with a photo-electric sensor to actuate the ionizer. For detailed information on this product ask for Technical Bulletin TB-2079.Critical Environment Ionizer (Item 60478)The Desco Critical Environment Ionizer is a minimal contamination ionizer designed for use in cleanrooms.It facilitates rapid static charge neutralization ofinsulators via multiple high output fans. The patented emitter cassettes slide out easily for cleaning and replacement allowing for faster and better cleaning 91710 • (909) 627-8178 • Fax (909) 627-744902021-1407 • (781) 821-8370 • Fax (781) 575-0172 • Web Site: The Chargebuster Jr. H/O is a self-contained, auto-balancing bench top ionizer which features replaceable emitter cassettes. The state of the art auto-balancing design ensures that ion output remains balanced,despite variations in the voltage, speed and thecondition of the emitter points. The Jr.'s compact and lightweight design makes the unit highly portable and takes up minimum bench space. This unit is ideally suited for field service technicians or any other application where mobility is a requirement. Fordetailed information on this product ask for Technical Bulletin TB-2095./分销商库存信息: DESCO60460。

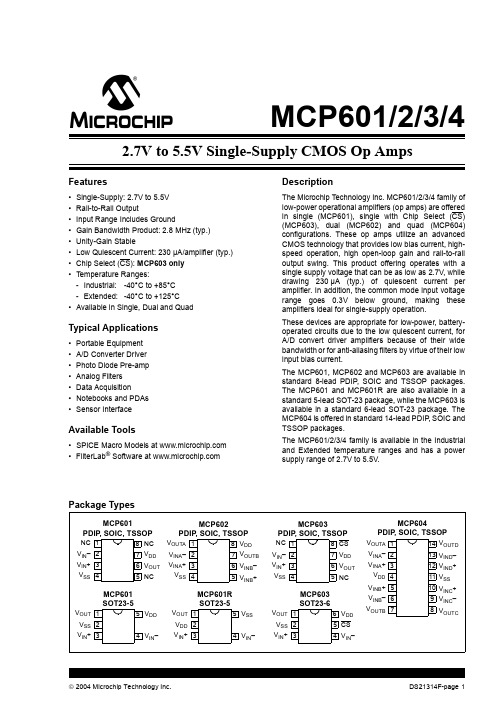

MCP604T中文资料

DS21314F-page 1

元器件交易网

MCP601/2/3/4

1.0 ELECTRICAL CHARACTERISTICS PIN FUNCTION TABLE

Name VIN +, VINA+, VINB+, VINC+, VIND+ VIN –, VINA–, VINB–, VINC–, VIND– VDD VSS VOUT, VOUTA, VOUTB, VOUTC , VOUTD CS NC Function Non-inverting Inputs Inverting Inputs Positive Power Supply Negative Power Supply Outputs Chip Select No Internal Connection

DC CHARACTERISTICS

Electrical Specifications: Unless otherwise specified, TA = +25°C, VDD = +2.7V to +5.5V, VSS = GND, VCM = VDD/2, VOUT ≈ VDD /2 and RL = 100 kΩ to VDD /2. Parameters Input Offset Input Offset Voltage Industrial Temperature Extended Temperature Input Offset Temperature Drift Power Supply Rejection Input Current and Impedance Input Bias Current Industrial Temperature Extended Temperature Input Offset Current Common Mode Input Impedance Differential Input Impedance Common Mode Common Mode Input Range Common Mode Rejection Ratio Open-loop Gain DC Open-loop Gain (large signal) Sym VOS VOS VOS ∆VOS/∆TA PSRR IB IB IB IOS ZCM ZDIFF VCMR CMRR A OL AOL Output Maximum Output Voltage Swing Linear Output Voltage Swing Output Short Circuit Current Min -2 -3 -4.5 — 80 — — — — — — VSS – 0.3 75 100 95 Typ ±0.7 ±1 ±1 ±2.5 88 1 20 450 ±1 1013||6 1013||3 — 90 115 110 Max +2 +3 +4.5 — — — 60 5000 — — — VDD – 1.2 — — — Units mV mV mV µV/°C dB Conditions

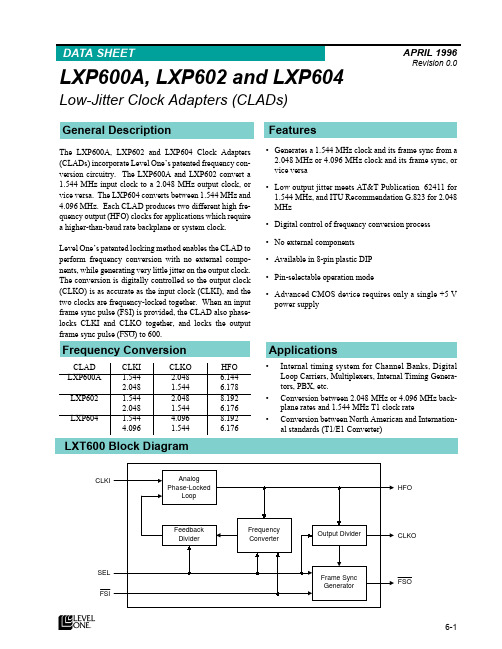

LXP604中文资料

MHz for LXP604) is converted to 1.544 MHz CLKO. When SEL = Low, 1.544 MHz CLKI is converted to higher frequency CLKO (2.048 for LXP600A and LXP602, or 4.096 MHz for LXP604).

and to FSI (if FSI is provided).

ë

+)2 2 High Frequency Outputï HFO is used to derive CLKO. HFO can also clock external

devices. HFO is always a multiple of CLKO (CLKO x2, x3, or x4). Actual frequencies are determined by device, CLKI and CLKO frequencies and Mode Select (SEL) input, as listed in Table 2.

è

‡ 1R H[WHUQDO FRPSRQHQWV

‡ $YDLODEOH LQ åðSLQ SODVWLF ',3

ç

‡ 3LQðVHOHFWDEOH RSHUDWLRQ PRGH

‡ $GYDQFHG &026 GHYLFH UHTXLUHV RQO\ D VLQJOH òè 9 SRZHU VXSSO\

æ

å

$SSOLFDWLRQV

‡ ,QWHUQDO WLPLQJ V\VWHP IRU &KDQQHO %DQNVñ 'LJLWDO /RRS &DUULHUVñ 0XOWLSOH[HUVñ ,QWHUQDO 7LPLQJ *HQHUDð WRUVñ 3%;ñ HWFï

K60功能介绍

一、超低功耗:1. 10 种带有功率和时脉闸控的低功耗模式,可优化外围设备活动和恢复时间。

停止电流<500 nA,运行电流<200 uA/MHz,停止模式唤醒时间4μs。

2. 完整内存,模拟运行可降至1.71V,令电池寿命延长。

3. 低漏电唤醒单元,可带有8 个内置模块和16 个引脚,作为低漏电停止(LLS)/超低漏电停止(VLLS) 模式的唤醒源。

4. 低功耗定时器支持在低功耗状态下系统的持续运行。

二、闪存、SRAM和FlexMemory5. 256 KB-1 MB闪存。

快速接入、高可靠性具备四级安全保护6. 64 KB-128 KB SRAM7. FlexMemory:32 字节- 16 KB 用户可分段的字节写入/清除EEPROM,适用于数据表/系统数据。

EEPROM 具有超过10M 的周期和70 μsec 写入时间的闪存(出现电力故障时不会发生数据丢失或损坏)。

没有用户或系统干预便可完成编程和清除功能,完全运行状态下可降至 1.71V。

此外,从256KB-512KB 的FlexNVM 还适用于额外编程代码、数据或EEPROM 备份三、混合信号功能:8. 多达四种可配置分辨率的高速16位ADC。

可采用单路或差分输出模式改善噪声抑制。

可编程延迟块触发功能转换时间可达500 ns9. 多达两个12位DAC可用于音频应用模拟波形生成10. 具有3 个高速比较器,通过将PWM 保持在安全状态,提供快速准确的电机过电流保护。

11. 多达四个64倍可编程增益放大器用于小型振幅信号转换12. 模拟基准电压为模拟块、ADC 和DAC 提供精确的基准值,可以替换外部基准电压,降低系统成本。

四、性能:13. ARM Cortex-M4 内核+ DSP。

100-180MHz、单周期MAC、单指令多数据(SIMD) 扩展、可选的单精度浮点单元。

14. 具有32 通道的DMA 适用于外围设备和内存,可降低CPU 负载,实现更快的系统吞吐量。

VJ 6040 用户指南说明书

Document Number: 45189For technical questions, contact: ***************V I S H AY V I T R A M O NCeramic Chip AntennaEVK 6040 User GuideA P P L I C A T I O N N O T EThe company’s products are covered by one or more of the following:WO2008250262 (A1), US2008303720 (A1), US2008305750 (A1), WO2008154173 (A1). Other patents pending.GENERALThis document is designed to serve as a user guide for the VJ 6040 evaluation kit. It is recommended that this document be read after the following documents were viewed:•VJ 6040 datasheet •VJ 6040 application notesEVALUATION KIT COMPONENTSThe evaluation kit is shown in figure 1. Table 1 details the kit components.Fig. 1 - Evaluation Kitning TABLE 1 - KIT COMPONENTSITEM FUNCTIONALITYAntenna Actual ceramic chip antennaSMA connector Connect a 50 Ω RF cable to this connector, to get signals received on the antenna end Tuning circuit A digital tuning circuit used to cover the entire UHF band with 2 control pinsDip switch array Used to control the tuning circuit manually. Only pins 3 and 4 (marked D0 and D1) are in use.Pins 1 and 2 are not connectedDigital control pins Used to control the tuning circuit electrically. Pins D0 and D1 are standard CMOS level digital control pins capable of supplying at least 1 mADC connectorUsed to feed power to the tuning circuit. This connector is used only in the manual tuning alternative set upEVK 6040 User Guide For technical questions, contact: ***************Document Number: 45189Application NoteVishay VitramonA P P L I C A T I O N N O T EKIT SETUPThere are 2 recommended alternative ways to set up the evaluation kit for testing and use. The difference between these alternatives is in the way the tuning circuit is controlled. Both alternatives are described hereafter.SET UP ALTERNATIVE 1 - MANUAL CONTROLIn this alternative, the tuning circuit is controlled by the on board mechanical dip switch array. The control line voltage in this setup should be applied to the on board DC connector.A voltage of 2 V to 30 V will ensure good performance. The evaluation kit is supplied with a battery house designed to provide 3 V using two AAA batteries.Fig. 2 - Manual ControlIn set up alternative 1, the tuning circuit is driven and controlled by dip switches D0 and D1. The other two switches in the array are not connected. Maximum current consumed by the tuning circuit is less than 2 mA when operating at 3 V.A 50 Ω RF cable, connected to the SMA connector, can be used to guide the received signals from the antenna to the desired applicable receiver/test equipment.Note•See table 3 for details regarding channel selectionSET UP ALTERNATIVE 2 - ELECTRICAL CONTROLIn this alternative, the tuning circuit is controlled by the 5 pin digital connector. In order to function properly in this alternative and avoid short circuit, the following rules need to be followed:1. Remove the batteries from the battery housing. Disconnect the DC jack from the DC connector2. Leave all dip switches in L position (in this position, the tuning circuit control pins are in High-Z impedance, and can be controlled by the external pins).3. Connect the GND pin on the EVK to the common ground used by the external digital control circuit.Fig. 3 - Electrical ControlThe 3 pin digital connector is expected to be connected to an external control circuit. The digital control signals D0 and D1are standard CMOS level signals.Note•Signal integrity is detailed in table 2EVK 6040 User GuideApplication NoteVishay VitramonA P P L I C A T I O N N O T EDocument Number: 45189For technical questions, contact: ***************CONTROL SIGNAL INTEGRITYTable 2 describes the desired control signal properties:OPERATING THE KITTo properly operate the kit, the antenna needs to be tuned to the required band. The kit is offering coverage of the entire UHF band, by dividing it into 4 sub-bands. Selecting the correct band is critical for antenna performance.EVK 6040 User Guide For technical questions, contact: ***************Document Number: 45189Application NoteVishay VitramonA P P L I C A T I O N N O T ETable 3 describes channel selection for both manual and electrical set up alternatives and typical...Comment: The EVK tuning circuit is optimized to cover the band of 474 MHz to 800 MHz. There is an alternative tuning circuit available, to cover the band of 474 MHz to 860 MHz. For more information see “VJ 3505 application notes - tuning circuit”.EVK 6040 User GuideApplication NoteVishay VitramonA P P L I C A T I O N N O T EDocument Number: 45189For technical questions, contact: ***************VJ 3505 EVALUATION KIT ANTENNA PERFORMANCE MEASURED PEAK GAIN AND EFFICIENCYThe Antenna radiation characteristics are influenced by several factors including ground plane dimensions and impedance matching network.The antenna parameters presented hereafter were measured using to the configuration suggested by the VJ 6040 evaluation board.Figure 4 shows radiation patterns of the EVK 6040 in various frequencies across the UHF band:Fig. 4 - Peak Gain vs. FrequencyApplications that do not require full coverage of the UHF band can enjoy additional efficiency by removing the tuning circuit. In this case the antenna can be fixed to any 150 MHz band within the UHF range.Figure 5 shows simulated peak gain and radiation efficiency of the VJ 6040 antenna over frequency throughout the UHF band,compared with the MBRAI requirements:Fig. 5 - Peak Gain vs. FrequencyEVK 6040 User Guide For technical questions, contact: ***************Document Number: 45189Application NoteVishay VitramonA P P L I C A T I O N N O T ESCHEMATIC DRAWINGFigure 6 below shows the schematic drawing of the evaluation kit. See tuning circuit application note for details regarding recommended BOM.Fig. 6 - EVK 3505 SchematicFeatures are subject to revisions or changes without notificationTABLE 4 - EVK6040 BOM LISTVALUE REFERENCE QUANTITY PER CIRCUIT PART NUMBERMANUFACTURERAntenna VJ 35051VJ 3505M011SXMSRA0Vishay 120 nH l3, l4, l53HK1005R12J-T Taiyo Yuden PIN diode D1, D22BAR63-02V Infineon 27 nH L11IMC0402ER27NJ Vishay 39 nH L21IMC0402ER39NJ Vishay 3.3 pF C11VJ0402A3R3BXACW1BC Vishay 2.2 pF C51VJ0402A2R2BXACW1BC Vishay 220 pF C2, C4, C6, C74VJ0402A221JXACW1BC Vishay 1 k ΩR1, R32CRCW1KJNED Vishay 0 ΩR21CRCW0R0Z0EDVishayEVK 6040 User GuideApplication NoteVishay VitramonA P P L I C A T I O N N O T EDocument Number: 45189For technical questions, contact: ***************ELECTRICAL CHARACTERISTICS AND FUNCTIONAL DESCRIPTIONThe tuning circuit herein is effectively an inductor, connected in series with a capacitor. The total impedance generated by this circuit can be described in the following equation (excluding the capacitors C2, C3 and C4):By connecting PIN diodes in parallel to C1 and L2, the tuning circuit can electrically short-circuit one of the two reactants or both. Table 2 is detailing all logical states of the tuning circuit,and the electrical effect as presented in the impedance Z. For the sake of small signal analysis, when the PIN diode is in forward conductance mode, it is represented as a 2 Ωresistor.As evident from table 2, each one of the 4 possible logicstates represents a different tuning circuit between the antenna and the receiver port.By applying the values shown in table 1 to L1, C1 and L2 the 4 states cover the entire UHF band.SELECTING THE RESISTIVE VALUES OF RR1 resistor is used to DC bias the PIN diodes. Selecting the value for R1 can be derived for the following equation:When:R = resistive value (in Ω) for R1V control = control voltage (in volts) as generated by the controllerV d = forward voltage (in V) generated on the PIN diode when biasedI d = forward current (in A) through the PIN diode when biasedExample:The PIN diode should be forward biased at 0.8 V to allow just over 1 mA to pass through it (see the graphs below). At 1 mA,the diode small signal impedance drops to its required value of 2 Ω.Let's assume that the digital control line is 1.8 V when high.To allow a current of 1 mA, R1 should be set as follows:EVK 6040 User Guide For technical questions, contact: ***************Document Number: 45189Application NoteVishay VitramonA P P L I C A T I O N N O T EFig. 7 - PIN Diode CharacteristicsGROUND PLANE CONFIGURATIONGeneralThe VJ 6040 antenna is unbalanced, therefore requiring a ground plane for its operation. The ground plane dimensions significantly influence the antenna performance. The rule of thumb in unbalanced antenna ground plane design is that antenna efficiency increases with ground plane size. The evaluation board demonstrates how the antenna complies with the EMBRAI standard when set against a ground plane small enough to fit into most cellular phone designs.Applications that allow larger ground planes can enjoy higher efficiency.An important consideration in the design of this product into cell phone applications is the coexistence of the cell phone antenna with VJ 6040. The recommended ground plane configuration presented below includes recommendations regarding how to set the cellular antenna relative to the VJ 6040 to minimize losses to both antennas.VJ 6040 evaluation board demonstrates exceptional antenna performance achieved with a 40 mm by 80 mm ground plane.Figure 4 describes a recommended reference ground plane configuration.The areas marked in green in the close proximity to the antenna should remain empty from large conducting surfaces including ground planes (outer or inner layers),batteries, connectors, buttons, or other large components.Applications that require additional antennas, such as cell phones, should position the cellular antenna at the top left hand side while maintaining maximum distance from VJ 6040. The presence of an additional antenna might cause loss of efficiency to both antennas.Fig. 8 - Recommended Ground Plane。

RKC系列温控表详细说明书(带注释)

RKC使用¥说明书仲克飞RKC使用说明书感谢您购买本系列温控器,请事先详细阅读此“使用说明书”,本说明书中的资料如改动恕不通知,敬请谅解。

$本温控器的制造经过严格地品质管理,如遇有不正常的状态或显示,请即刻与北京四通股份公司工控部或您的供应商联络。

第1章准备篇 1.型号定义┄┄┄┄┄┄┄┄┄┄┄┄┄┄┄┄┄1-12.安装┄┄┄┄┄┄┄┄┄┄┄┄┄┄┄┄┄1-2外形尺寸安装方法3.接线端子构成接线注意事项|4.规格输入设定显示输出第2章功能篇 1.控制1.1PID控制1.2加热、冷却控制1.3正动作、逆动作1.4`1.5自动演算(AT)功能1.6自主校正(ST)功能1.7设定数据锁(LCK)功能2.报警温度报警加热器断线报警(HBA)控制环断线报警(LBA)3.输入异常时的动作第3章操作篇 1.设定前状态/2 SV设定模式3.参数设定模式4工程师参数设定模式第4篇通讯篇(仅限CD系列表)第5篇其它第1篇准备篇1.(2.型号定义请参照下列代码表确认产品是否与您指定的型号一致。

CD/CH □01/02□□□-□□*□□-□□①②③④⑤⑥⑦⑧⑨⑩①规格尺寸详见第1篇节②控制类型F:PID动作及自动演算(逆动作)D:PID动作及自动演算(正动作)|W:加热/冷却PID动作及自动演算(水冷)*1A:加热/冷却PID动作及自动演算(风冷)*1③输入类型:见输入范围表④范围代码:见输入范围表⑤第一控制输出(OUT1)(加热侧)M:继电器接点输出8:电流输出(DC4~20mA)V:电压脉冲输出G:闸流控制管驱动用触发器输出T:闸流控制管输出⑥第二控制输出(OUT2)(制冷侧)*2无记号:当控制动作是F或D时—M:继电器接点输出T:闸流控制管输出V:电压脉冲输出8:电流输出(DC4~20mA)⑦第一报警(ALM1),⑧第二报警(ALM2)*2N;未设报警J:下限输入值报警A:上限偏差报警K:附待机上限输入值报警B:下限偏差报警L:附待机下限输入值报警C:上、下限偏差报警P:加热器断线报警(CTL-6)*3 D:范围内报警S:加热器断线报警(CTL-12)*3 E:附待机上限偏差报警R:控制环断线报警*4F:附待机下限偏差报警V:上限设定值报警·G;附待机上下限偏差报警W:下限设定值报警H:上限输入值报警⑨通信功能(仅限CD系列)N:无通信功能5:RS-485(双线系统)⑩防水/防尘功能N:无防水/防尘功能1:有防水/防尘功能注:*1W或A型无自主校正功能:*2第二控制输出(OUT2)﹑第二报警(ALM2)为选项*3不能被定为第一报警(ALM1)*4控制环断线报警只能在第一报警和第二报警中选择其一3.安装外形尺寸#安装方法⑴按照盘面开孔尺寸在盘面上打出用来安装仪器的矩形孔。

KL03 芯片系列参考手册说明书

KL03 Sub-Family Reference Manual Supports: MKL03Z8VFG4(R), MKL03Z16VFG4(R), MKL03Z32VFG4(R), MKL03Z32CAF4R, MKL03Z8VFK4(R),MKL03Z16VFK4(R), and MKL03Z32VFK4(R)Document Number: KL03P24M48SF0RMRev 3, June, 2014ContentsSection number Title PageChapter 1About This Document1.1Overview (27)1.1.1Purpose (27)1.1.2Audience (27)1.2Conventions (27)1.2.1Numbering systems (27)1.2.2Typographic notation (28)1.2.3Special terms (28)Chapter 2Introduction2.1KL03 sub-family introduction (29)2.2Module functional categories (29)2.2.1ARM Cortex-M0+ core modules (30)2.2.2System modules (31)2.2.3Memories and memory interfaces (32)2.2.4Clocks (32)2.2.5Analog modules (32)2.2.6Timer modules (33)2.2.7Communication interfaces (33)2.2.8Human-machine interfaces (34)2.3Module to module interconnects (34)2.3.1Interconnection overview (34)2.3.2Analog reference options (35)2.4Orderable part numbers (36)Chapter 3Core Overview3.1ARM Cortex-M0+ core introduction (37)3.1.1Buses, interconnects, and interfaces (37)3.1.2System tick timer (37)3.1.3Debug facilities (37)3.1.4Core privilege levels (38)3.2Nested vectored interrupt controller (NVIC) (38)3.2.1Interrupt priority levels (38)3.2.2Non-maskable interrupt (38)3.2.3Interrupt channel assignments (38)3.3AWIC introduction (41)3.3.1Wake-up sources (41)Chapter 4Memory and Memory Map4.1Flash memory (43)4.1.1Flash memory map (43)4.1.2Flash security (44)4.1.3Flash modes (44)4.1.4Erase all flash contents (44)4.1.5FTFA_FOPT register (44)4.2SRAM (45)4.2.1SRAM sizes (45)4.2.2SRAM ranges (45)4.2.3SRAM retention in low power modes (46)4.3System Register file (46)4.4Memory map (47)4.4.1Introduction (47)4.4.2System memory map (47)4.4.3Flash memory map (48)4.4.4SRAM memory map (48)4.4.5Bit Manipulation Engine (49)4.4.6Peripheral bridge (AIPS-Lite) memory map (49)4.4.7Private Peripheral Bus (PPB) memory map (54)Chapter 5Clock Distribution5.1Introduction (55)5.2Programming model (55)5.3High-level device clocking diagram (55)5.4Clock definitions (56)5.4.1Device clock summary (57)5.5Internal clocking requirements (59)5.5.1Clock divider values after reset (59)5.5.2VLPR mode clocking (60)5.6Clock gating (60)5.7Module clocks (60)5.7.1PMC 1-kHz LPO clock (61)5.7.2COP clocking (62)5.7.3RTC clocking (62)5.7.4RTC_CLKOUT and CLKOUT32K clocking (63)5.7.5LPTMR clocking (63)5.7.6TPM clocking (64)5.7.7LPUART clocking (64)Chapter 6Reset and Boot6.1Introduction (67)6.2Reset (67)6.2.1Power-on reset (POR) (68)6.2.2System reset sources (68)6.2.3MCU resets (71)6.2.4RESET pin (72)6.3Boot (72)6.3.1Boot sources (72)6.3.2FOPT boot options (73)6.3.3Boot sequence (75)Chapter 7Power Management7.1Introduction (77)7.2Clocking modes (77)7.2.1Partial Stop (77)7.2.2Compute Operation (78)7.2.3Peripheral Doze (79)7.2.4Clock gating (79)7.3Power modes (80)7.4Entering and exiting power modes (82)7.5Module operation in low-power modes (82)Chapter 8Security8.1Introduction (87)8.1.1Flash security (87)8.1.2Security interactions with other modules (87)Chapter 9Debug9.1Introduction (89)9.2Debug port pin descriptions (89)9.3SWD status and control registers (90)9.3.1MDM-AP Control Register (91)9.3.2MDM-AP Status Register (92)9.4Debug resets (94)9.5Micro Trace Buffer (MTB) (94)9.6Debug in low-power modes (95)9.7Debug and security (96)Chapter 10Signal Multiplexing and Signal Descriptions10.1Introduction (97)10.2Signal multiplexing integration (97)10.2.1I/O Port control and interrupt module features (98)10.2.2Clock gating (98)10.2.3Signal multiplexing constraints (98)10.3Pinout (98)10.3.1KL03 signal multiplexing and pin assignments (98)10.3.2KL03 pinouts (100)10.4Module Signal Description Tables (101)10.4.1Core modules (101)10.4.2System modules (102)10.4.3Clock modules (102)10.4.4Memories and memory interfaces (103)10.4.5Analog (103)10.4.6Timer Modules (103)10.4.7Communication interfaces (104)10.4.8Human-machine interfaces (HMI) (105)Chapter 11Kinetis ROM Bootloader11.1Introduction (107)11.2Functional Description (108)11.2.1Memory Maps (108)11.2.2The Kinetis Bootloader Configuration Area (BCA) (109)11.2.3Start-up Process (110)11.2.4Clock Configuration (112)11.2.5Bootloader Entry Point (113)11.2.6Bootloader Protocol (114)11.2.7Bootloader Packet Types (117)11.2.8Bootloader Command API (123)11.2.9Bootloader Exit state (135)11.3Peripherals Supported (136)11.3.1I2C Peripheral (136)11.3.2SPI Peripheral (138)11.3.3UART Peripheral (140)11.4Get/SetProperty Command Properties (143)11.4.1Property Definitions (144)11.5Kinetis Bootloader Status Error Codes (145)Chapter 12Port Control and Interrupts (PORT)12.1Chip-specific PORT information (147)12.1.1GPIO instantiation information (147)12.1.2Port control and interrupt summary (148)12.2Introduction (149)12.3Overview (149)12.3.1Features (149)12.3.2Modes of operation (149)12.4External signal description (150)12.5Detailed signal description (150)12.6Memory map and register definition (151)12.6.1Pin Control Register n (PORT x_PCR n) (154)12.6.2Global Pin Control Low Register (PORT x_GPCLR) (156)12.6.3Global Pin Control High Register (PORT x_GPCHR) (157)12.6.4Interrupt Status Flag Register (PORT x_ISFR) (157)12.7Functional description (158)12.7.1Pin control (158)12.7.2Global pin control (159)12.7.3External interrupts (159)Chapter 13General-Purpose Input/Output (GPIO)13.1Chip-specific GPIO information (161)13.2Introduction (161)13.2.1Features (161)13.2.2Modes of operation (162)13.2.3GPIO signal descriptions (162)13.3Memory map and register definition (163)13.3.1Port Data Output Register (GPIO x_PDOR) (164)13.3.2Port Set Output Register (GPIO x_PSOR) (165)13.3.3Port Clear Output Register (GPIO x_PCOR) (165)13.3.4Port Toggle Output Register (GPIO x_PTOR) (166)13.3.5Port Data Input Register (GPIO x_PDIR) (166)13.3.6Port Data Direction Register (GPIO x_PDDR) (167)13.4FGPIO memory map and register definition (167)13.4.1Port Data Output Register (FGPIO x_PDOR) (168)13.4.2Port Set Output Register (FGPIO x_PSOR) (169)13.4.3Port Clear Output Register (FGPIO x_PCOR) (169)13.4.4Port Toggle Output Register (FGPIO x_PTOR) (170)13.4.5Port Data Input Register (FGPIO x_PDIR) (170)13.4.6Port Data Direction Register (FGPIO x_PDDR) (171)13.5Functional description (171)13.5.1General-purpose input (171)13.5.2General-purpose output (171)13.5.3IOPORT (172)Chapter 14System Integration Module (SIM)14.1Chip-specific COP information (173)14.2COP clocks (173)14.3COP watchdog operation (173)14.4Introduction (175)14.4.1Features (175)14.5Memory map and register definition (176)14.5.1System Options Register 1 (SIM_SOPT1) (177)14.5.2System Options Register 2 (SIM_SOPT2) (178)14.5.3System Options Register 4 (SIM_SOPT4) (180)14.5.4System Options Register 5 (SIM_SOPT5) (181)14.5.5System Options Register 7 (SIM_SOPT7) (182)14.5.6System Device Identification Register (SIM_SDID) (184)14.5.7System Clock Gating Control Register 4 (SIM_SCGC4) (186)14.5.8System Clock Gating Control Register 5 (SIM_SCGC5) (187)14.5.9System Clock Gating Control Register 6 (SIM_SCGC6) (189)14.5.10System Clock Divider Register 1 (SIM_CLKDIV1) (190)14.5.11Flash Configuration Register 1 (SIM_FCFG1) (192)14.5.12Flash Configuration Register 2 (SIM_FCFG2) (193)14.5.13Unique Identification Register Mid-High (SIM_UIDMH) (194)14.5.14Unique Identification Register Mid Low (SIM_UIDML) (194)14.5.15Unique Identification Register Low (SIM_UIDL) (195)14.5.16COP Control Register (SIM_COPC) (195)14.5.17Service COP (SIM_SRVCOP) (197)14.6Functional description (197)Chapter 15System Mode Controller (SMC)15.1Chip-specific SMC information (199)15.2Introduction (199)15.3Modes of operation (199)15.4Memory map and register descriptions (201)15.4.1Power Mode Protection register (SMC_PMPROT) (202)15.4.2Power Mode Control register (SMC_PMCTRL) (203)15.4.3Stop Control Register (SMC_STOPCTRL) (204)15.4.4Power Mode Status register (SMC_PMSTAT) (206)15.5Functional description (206)15.5.1Power mode transitions (206)15.5.2Power mode entry/exit sequencing (209)15.5.3Run modes (211)15.5.4Wait modes (212)15.5.5Stop modes (213)15.5.6Debug in low power modes (215)Chapter 16Power Management Controller (PMC)16.1Introduction (217)16.2Features (217)16.3Low-voltage detect (LVD) system (217)16.3.1LVD reset operation (218)16.3.2LVD interrupt operation (218)16.3.3Low-voltage warning (LVW) interrupt operation (218)16.4I/O retention (219)16.5Memory map and register descriptions (219)16.5.1Low Voltage Detect Status And Control 1 register (PMC_LVDSC1) (220)16.5.2Low Voltage Detect Status And Control 2 register (PMC_LVDSC2) (221)16.5.3Regulator Status And Control register (PMC_REGSC) (222)Chapter 17Miscellaneous Control Module (MCM)17.1Introduction (225)17.1.1Features (225)17.2Memory map/register descriptions (225)17.2.1Crossbar Switch (AXBS) Slave Configuration (MCM_PLASC) (226)17.2.2Crossbar Switch (AXBS) Master Configuration (MCM_PLAMC) (226)17.2.3Platform Control Register (MCM_PLACR) (227)17.2.4Compute Operation Control Register (MCM_CPO) (229)Chapter 18Crossbar Switch Lite (AXBS-Lite)18.1Introduction (231)18.1.1Features (231)18.2Memory Map / Register Definition (231)18.3Functional Description (232)18.3.1General operation (232)18.3.2Arbitration (233)18.4Initialization/application information (234)Chapter 19Low-Leakage Wakeup Unit (LLWU)19.1Chip-specific LLWU information (235)19.2Introduction (235)19.2.1Features (235)19.2.2Modes of operation (236)19.2.3Block diagram (237)19.3LLWU signal descriptions (238)19.4Memory map/register definition (238)19.4.1LLWU Pin Enable 1 register (LLWU_PE1) (239)19.4.2LLWU Pin Enable 2 register (LLWU_PE2) (240)19.4.3LLWU Module Enable register (LLWU_ME) (241)19.4.4LLWU Flag 1 register (LLWU_F1) (243)19.4.5LLWU Flag 3 register (LLWU_F3) (244)19.4.6LLWU Pin Filter 1 register (LLWU_FILT1) (246)19.4.7LLWU Pin Filter 2 register (LLWU_FILT2) (247)19.5Functional description (248)19.5.1VLLS modes (249)19.5.2Initialization (249)Chapter 20Peripheral Bridge (AIPS-Lite)20.1Introduction (251)20.1.1Features (251)20.1.2General operation (251)20.2Functional description (252)20.2.1Access support (252)Chapter 21Reset Control Module (RCM)21.1Introduction (253)21.2Reset memory map and register descriptions (253)21.2.1System Reset Status Register 0 (RCM_SRS0) (254)21.2.2System Reset Status Register 1 (RCM_SRS1) (255)21.2.3Reset Pin Filter Control register (RCM_RPFC) (256)21.2.4Reset Pin Filter Width register (RCM_RPFW) (257)21.2.5Force Mode Register (RCM_FM) (259)21.2.6Mode Register (RCM_MR) (259)21.2.7Sticky System Reset Status Register 0 (RCM_SSRS0) (260)21.2.8Sticky System Reset Status Register 1 (RCM_SSRS1) (261)Chapter 22Bit Manipulation Engine (BME)22.1Introduction (263)22.1.1Overview (264)22.1.2Features (264)22.1.3Modes of operation (265)22.2Memory map and register definition (265)22.3Functional description (266)22.3.1BME decorated stores (266)22.3.2BME decorated loads (273)22.3.3Additional details on decorated addresses and GPIO accesses (279)22.4Application information (280)Chapter 23Micro Trace Buffer (MTB)23.1Introduction (283)23.1.1Overview (283)23.1.2Features (286)23.1.3Modes of operation (287)23.2External signal description (287)23.3Memory map and register definition (288)23.3.1MTB_RAM Memory Map (288)23.3.2MTB_DWT Memory Map (301)23.3.3System ROM Memory Map (311)Chapter 24Multipurpose Clock Generator Lite (MCG_Lite)24.1Introduction (317)24.1.1Features (317)24.1.2Block diagram (317)24.2Memory map and register definition (318)24.2.1MCG Control Register 1 (MCG_C1) (319)24.2.2MCG Control Register 2 (MCG_C2) (319)24.2.3MCG Status Register (MCG_S) (320)24.2.4MCG Status and Control Register (MCG_SC) (321)24.2.5MCG Miscellaneous Control Register (MCG_MC) (321)24.3Functional description (322)24.3.1Clock mode switching (322)24.3.2LIRC divider 1 (323)24.3.3LIRC divider 2 (323)24.3.4Enable LIRC in Stop mode (324)24.3.5MCG-Lite in Low-power mode (324)Chapter 25Oscillator (OSC)25.1OSC modes of operation with MCG_Lite and RTC (325)25.2Introduction (325)25.3Features and Modes (325)25.4Block Diagram (326)25.5OSC Signal Descriptions (327)25.6External Crystal / Resonator Connections (327)25.7External Clock Connections (328)25.8Memory Map/Register Definitions (329)25.8.1OSC Memory Map/Register Definition (329)25.9Functional Description (330)25.9.1OSC module states (330)25.9.2OSC module modes (332)25.9.3Counter (333)25.9.4Reference clock pin requirements (333)25.10Reset (334)25.11Low power modes operation (334)25.12Interrupts (334)Chapter 26Flash Memory Controller (FMC)26.1Introduction (335)26.1.1Overview (335)26.1.2Features (335)26.2Modes of operation (336)26.3External signal description (336)26.4Memory map and register descriptions (336)26.5Functional description (336)Chapter 27Flash Memory Module (FTFA)27.1Introduction (339)27.1.1Features (339)27.1.2Block Diagram (340)27.1.3Glossary (341)27.2External Signal Description (342)27.3Memory Map and Registers (342)27.3.1Flash Configuration Field Description (342)27.3.2Program Flash IFR Map (343)27.3.3Register Descriptions (343)27.4Functional Description (352)27.4.1Flash Protection (352)27.4.2Interrupts (353)27.4.3Flash Operation in Low-Power Modes (354)27.4.4Functional Modes of Operation (354)27.4.5Flash Reads and Ignored Writes (354)27.4.6Read While Write (RWW) (355)27.4.7Flash Program and Erase (355)27.4.8Flash Command Operations (355)27.4.9Margin Read Commands (360)27.4.10Flash Command Description (361)27.4.11Security (375)27.4.12Reset Sequence (377)Chapter 28Analog-to-Digital Converter (ADC)28.1Chip-specific ADC information (379)28.1.1ADC0 connections/channel assignment (379)28.1.2ADC analog supply and reference connections (380)28.1.3ADC Reference Options (380)28.1.4Alternate clock (381)28.2Introduction (381)28.2.1Features (381)28.2.2Block diagram (382)28.3ADC signal descriptions (383)28.3.1Analog Power (VDDA) (384)28.3.2Analog Ground (VSSA) (384)28.3.3Analog Channel Inputs (ADx) (384)28.4Memory map and register definitions (384)28.4.1ADC Status and Control Registers 1 (ADC x_SC1n) (385)28.4.2ADC Configuration Register 1 (ADC x_CFG1) (389)28.4.3ADC Configuration Register 2 (ADC x_CFG2) (390)28.4.4ADC Data Result Register (ADC x_R n) (391)28.4.5Compare Value Registers (ADC x_CV n) (392)28.4.6Status and Control Register 2 (ADC x_SC2) (393)28.4.7Status and Control Register 3 (ADC x_SC3) (395)28.4.8ADC Offset Correction Register (ADC x_OFS) (397)28.4.9ADC Plus-Side Gain Register (ADC x_PG) (397)28.4.10ADC Plus-Side General Calibration Value Register (ADC x_CLPD) (398)28.4.11ADC Plus-Side General Calibration Value Register (ADC x_CLPS) (398)28.4.12ADC Plus-Side General Calibration Value Register (ADC x_CLP4) (399)28.4.13ADC Plus-Side General Calibration Value Register (ADC x_CLP3) (399)28.4.14ADC Plus-Side General Calibration Value Register (ADC x_CLP2) (400)28.4.15ADC Plus-Side General Calibration Value Register (ADC x_CLP1) (400)28.4.16ADC Plus-Side General Calibration Value Register (ADC x_CLP0) (401)28.5Functional description (401)28.5.1Clock select and divide control (402)28.5.2Voltage reference selection (403)28.5.3Hardware trigger and channel selects (403)28.5.4Conversion control (404)28.5.5Automatic compare function (411)28.5.6Calibration function (412)28.5.7User-defined offset function (414)28.5.8Temperature sensor (415)28.5.9MCU wait mode operation (416)28.5.10MCU Normal Stop mode operation (416)28.5.11MCU Low-Power Stop mode operation (417)28.6Initialization information (418)28.6.1ADC module initialization example (418)28.7Application information (420)28.7.1External pins and routing (420)28.7.2Sources of error (422)Chapter 29Comparator (CMP)29.1Chip-specific CMP information (427)29.1.1CMP input connections (427)29.1.2CMP external references (428)29.1.3CMP trigger mode (428)29.2Introduction (429)29.2.1CMP features (429)29.2.26-bit DAC key features (430)29.2.3ANMUX key features (430)29.2.4CMP, DAC and ANMUX diagram (430)29.2.5CMP block diagram (431)29.3Memory map/register definitions (432)29.3.1CMP Control Register 0 (CMP x_CR0) (433)29.3.2CMP Control Register 1 (CMP x_CR1) (434)29.3.3CMP Filter Period Register (CMP x_FPR) (435)29.3.4CMP Status and Control Register (CMP x_SCR) (436)29.3.5DAC Control Register (CMP x_DACCR) (437)29.3.6MUX Control Register (CMP x_MUXCR) (437)29.4Functional description (438)29.4.1CMP functional modes (438)29.4.2Power modes (442)29.4.3Startup and operation (443)29.4.4Low-pass filter (443)29.5CMP interrupts (445)29.6Digital-to-analog converter (446)29.7DAC functional description (446)29.7.1Voltage reference source select (446)29.8DAC resets (447)29.9DAC clocks (447)29.10DAC interrupts (447)29.11CMP Trigger Mode (447)Chapter 30Voltage Reference (VREF)30.1Chip specific VREF information (449)30.1.1Clock Gating (449)30.2Introduction (449)30.2.1Overview (450)30.2.2Features (450)30.2.3Modes of Operation (451)30.2.4VREF Signal Descriptions (451)30.3Memory Map and Register Definition (452)30.3.1VREF Trim Register (VREF_TRM) (452)30.3.2VREF Status and Control Register (VREF_SC) (453)30.4Functional Description (454)30.4.1Voltage Reference Disabled, SC[VREFEN] = 0 (455)30.4.2Voltage Reference Enabled, SC[VREFEN] = 1 (455)30.4.3Internal voltage regulator (456)30.5Initialization/Application Information (457)Chapter 31Timer/PWM Module (TPM)31.1Chip-specific TPM information (459)31.1.1Clock options (459)31.1.2Trigger options (460)31.1.3Global timebase (460)31.1.4TPM interrupts (460)31.2Introduction (461)31.2.1TPM Philosophy (461)31.2.2Features (461)31.2.3Modes of operation (462)31.2.4Block diagram (462)31.3TPM Signal Descriptions (463)31.3.1TPM_EXTCLK — TPM External Clock (463)31.3.2TPM_CHn — TPM Channel (n) I/O Pin (464)31.4Memory Map and Register Definition (464)31.4.1Status and Control (TPM x_SC) (465)31.4.2Counter (TPM x_CNT) (466)31.4.3Modulo (TPM x_MOD) (467)31.4.4Channel (n) Status and Control (TPM x_C n SC) (468)31.4.5Channel (n) Value (TPM x_C n V) (469)31.4.6Capture and Compare Status (TPM x_STATUS) (470)31.4.7Configuration (TPM x_CONF) (472)31.5Functional description (473)31.5.1Clock domains (474)31.5.2Prescaler (474)31.5.3Counter (475)31.5.4Input Capture Mode (478)31.5.5Output Compare Mode (478)31.5.6Edge-Aligned PWM (EPWM) Mode (480)31.5.7Center-Aligned PWM (CPWM) Mode (481)31.5.8Registers Updated from Write Buffers (483)31.5.9Output triggers (484)31.5.10Reset Overview (484)31.5.11TPM Interrupts (484)Chapter 32Low-Power Timer (LPTMR)32.1Chip-specific LPTMR information (487)32.1.1LPTMR pulse counter input options (487)32.1.2LPTMR prescaler/glitch filter clocking options (487)32.2Introduction (488)32.2.1Features (488)32.2.2Modes of operation (488)32.3LPTMR signal descriptions (489)32.3.1Detailed signal descriptions (489)32.4Memory map and register definition (489)32.4.1Low Power Timer Control Status Register (LPTMR x_CSR) (490)32.4.2Low Power Timer Prescale Register (LPTMR x_PSR) (491)32.4.3Low Power Timer Compare Register (LPTMR x_CMR) (493)32.4.4Low Power Timer Counter Register (LPTMR x_CNR) (493)32.5Functional description (494)32.5.1LPTMR power and reset (494)32.5.2LPTMR clocking (494)32.5.3LPTMR prescaler/glitch filter (494)32.5.4LPTMR compare (496)32.5.5LPTMR counter (496)32.5.6LPTMR hardware trigger (497)32.5.7LPTMR interrupt (497)Chapter 33Real Time Clock (RTC)33.1Chip-specific RTC information (499)33.1.1RTC_CLKOUT options (499)33.2Introduction (499)33.2.1Features (499)33.2.2Modes of operation (500)33.2.3RTC signal descriptions (500)33.3Register definition (500)33.3.1RTC Time Seconds Register (RTC_TSR) (501)33.3.2RTC Time Prescaler Register (RTC_TPR) (501)33.3.3RTC Time Alarm Register (RTC_TAR) (502)33.3.4RTC Time Compensation Register (RTC_TCR) (502)33.3.5RTC Control Register (RTC_CR) (504)33.3.6RTC Status Register (RTC_SR) (506)33.3.7RTC Lock Register (RTC_LR) (507)33.3.8RTC Interrupt Enable Register (RTC_IER) (508)33.4Functional description (509)33.4.1Power, clocking, and reset (509)33.4.2Time counter (510)33.4.3Compensation (510)33.4.4Time alarm (511)33.4.5Update mode (511)33.4.6Register lock (512)33.4.7Interrupt (512)Chapter 34Serial Peripheral Interface (SPI)34.1Chip-specific SPI information (513)34.2Introduction (513)34.2.1Features (513)34.2.2Modes of operation (514)34.2.3Block diagrams (515)34.3External signal description (517)34.3.1SPSCK — SPI Serial Clock (517)34.3.2MOSI — Master Data Out, Slave Data In (518)34.3.3MISO — Master Data In, Slave Data Out (518)34.3.4SS — Slave Select (518)34.4Memory map/register definition (519)34.4.1SPI Status Register (SPI x_S) (519)34.4.2SPI Baud Rate Register (SPI x_BR) (520)34.4.3SPI Control Register 2 (SPI x_C2) (521)34.4.4SPI Control Register 1 (SPI x_C1) (523)34.4.5SPI Match Register (SPI x_M) (524)34.4.6SPI Data Register (SPI x_D) (525)34.5Functional description (525)34.5.1General (525)34.5.2Master mode (526)34.5.3Slave mode (527)34.5.4SPI clock formats (529)34.5.5SPI baud rate generation (532)34.5.6Special features (532)34.5.7Error conditions (534)34.5.8Low-power mode options (535)34.5.9Reset (536)34.5.10Interrupts (537)34.6Initialization/application information (538)34.6.1Initialization sequence (538)34.6.2Pseudo-Code Example (539)Chapter 35Inter-Integrated Circuit (I2C)35.1Chip-specific I2C information (543)35.2Introduction (543)35.2.1Features (543)35.2.2Modes of operation (544)35.2.3Block diagram (544)35.3I2C signal descriptions (545)35.4Memory map/register definition (546)35.4.1I2C Address Register 1 (I2C x_A1) (546)35.4.2I2C Frequency Divider register (I2C x_F) (547)35.4.3I2C Control Register 1 (I2C x_C1) (548)35.4.4I2C Status register (I2C x_S) (549)35.4.5I2C Data I/O register (I2C x_D) (551)35.4.6I2C Control Register 2 (I2C x_C2) (552)35.4.7I2C Programmable Input Glitch Filter Register (I2C x_FLT) (553)35.4.8I2C Range Address register (I2C x_RA) (554)35.4.9I2C SMBus Control and Status register (I2C x_SMB) (555)35.4.10I2C Address Register 2 (I2C x_A2) (556)35.4.11I2C SCL Low Timeout Register High (I2C x_SLTH) (557)35.4.12I2C SCL Low Timeout Register Low (I2C x_SLTL) (557)35.4.13I2C Status register 2 (I2C x_S2) (558)35.5Functional description (558)35.5.1I2C protocol (558)35.5.210-bit address (564)35.5.3Address matching (565)35.5.4System management bus specification (566)35.5.5Resets (569)35.5.6Interrupts (569)35.5.7Programmable input glitch filter (571)35.5.8Address matching wake-up (572)35.5.9Double buffering mode (573)35.6Initialization/application information (574)Chapter 36Low Power Universal Asynchronous Receiver/Transmitter (LPUART)36.1Chip-specific LPUART information (579)36.2Introduction (579)36.2.1Features (579)36.2.2Modes of operation (580)36.2.3Signal Descriptions (581)36.2.4Block diagram (581)36.3Register definition (583)36.3.1LPUART Baud Rate Register (LPUART x_BAUD) (584)36.3.2LPUART Status Register (LPUART x_STAT) (586)36.3.3LPUART Control Register (LPUART x_CTRL) (590)36.3.4LPUART Data Register (LPUART x_DATA) (595)36.3.5LPUART Match Address Register (LPUART x_MATCH) (597)36.4Functional description (597)36.4.1Baud rate generation (597)36.4.2Transmitter functional description (598)36.4.3Receiver functional description (600)36.4.4Additional LPUART functions (605)36.4.5Interrupts and status flags (607)Chapter 1About This Document1.1Overview1.1.1PurposeThis document describes the features, architecture, and programming model of the Freescale microcontroller.1.1.2AudienceA reference manual is primarily for system architects and software application developers who are using or considering using a Freescale product in a system.1.2Conventions1.2.1Numbering systemsThe following suffixes identify different numbering systems:1.2.2Typographic notationThe following typographic notation is used throughout this document:1.2.3Special termsThe following terms have special meanings:Chapter 2Introduction2.1KL03 sub-family introductionThe device is highly-integrated, market leading ultra low-power 32-bit microcontroller based on the enhanced Cortex-M0+ (CM0+) core platform. The features of the KL03 family derivatives are as follows.•Core platform clock up to 48 MHz, bus clock up to 24 MHz•Memory option is up to 32 KB flash, 2 KB RAM and 8 KB ROM with build-in boot loader•Wide operating voltage ranges from 1.71–3.6 V with fully functional flash program/ erase/read operations•Multiple package options from 16-pin to 24-pin•Ambient operating temperature ranges from –40 °C to 85 °C for WLCSP package and –40 °C to 105 °C for all the other packages.The family acts as an ultra low-power, cost-effective microcontroller to provide developers an appropriate entry-level 32-bit solution. The family is the next-generation MCU solution for low-cost, low-power, high-performance devices applications. It’s valuable for cost-sensitive, portable applications requiring long battery life-time.2.2Module functional categoriesThe modules on this device are grouped into functional categories. Information found here describes the modules assigned to each category in more detail.2.2.1ARM Cortex-M0+ core modules The following core modules are available on this device.2.2.2System modulesThe following system modules are available on this device.2.2.3Memories and memory interfacesThe following memories and memory interfaces are available on this device.2.2.4ClocksThe following clock modules are available on this device.2.2.5Analog modulesThe following analog modules are available on this device:。

RK系列说明书

TPS604中文资料

SLVS324 - 2001年7月功能∙反转输入电压∙高达60 mA的输出电流∙只有三个小1 - μF陶瓷电容器的∙输入电压范围从1.6 V至5.5 V,∙省电模式在低输出电流(TPS60400),以提高效率∙器件的静态电流典型的100 μ∙综合活动肖特基二极管应用•LCD偏置∙砷化镓射频功率放大器的偏置∙便携式仪器在传感器电源∙双极放大器的电源∙医疗器械∙电池供电设备DBV封装(顶视图)CFLY +接地启动进入负载输出∙小型5引脚SOT23封装中•评估模块TPS60400EVM-178CFLY-描述TPS6040x是一个不受管制的负输出电压的输入电压范围从1.6 V至5.5 V的设备通常是由一个5 V或3.3 preregulated电源轨五,由于它的宽输入电压范围提供了设备产生的家庭,两个或三个镍镉电池,镍氢电池或碱性电池,以及一个锂离子电池功率他们还可以。

只有三个外部1 - μ F电容需要建立一个完整的电荷泵DC / DC逆变器。

5引脚SOT23封装,组装,完整的转换器,可建50毫米2的电路板面积。

额外的电路板面积和减少元件数量达到取代肖特基二极管通常需要启动到集成电路的负载。

TPS6040x可提供的最大输出电流60毫安的典型转换效率大于90%以上的宽输出电流范围。

20千赫,50千赫,250 kHz固定频率操作设备三个选项可供选择。

一个装置带有一个可变开关频率,以降低工作电流在一个宽负载范围内的应用,使价值低电容设计。

典型应用电路TPS6040 0的输出VOLTAG é V S 输入电压产量-1.6 V至-5V,最大60 mA至五Ø -输出电压- V的-1-2-3-4-5012345VI - 输入电压- V的请注意,一个重要的通知有关可用性,标准保修,并使用在关键应用德州仪器公司的半导体产品和免责条款及其出现在此数据表的结束。

版权所有© 2001年,德州仪器生产数据信息是当前出版日期。

山拖凯泰604说明书

山拖凯泰604说明书一、产品概述山拖凯泰604是一款多功能拖拉机,广泛应用于农田耕作、种植、收割等农业生产环节。

该款拖拉机采用先进的技术和设计,具备卓越的性能和可靠的品质,为农民朋友提供了高效便捷的农业机械解决方案。

二、产品特点1. 强劲动力:山拖凯泰604搭载高性能发动机,动力强劲,能够满足不同农业作业的需求。

2. 燃油经济:该拖拉机采用先进的燃油喷射技术,燃油利用率高,节能环保。

3. 多功能操作:山拖凯泰604配备了多种作业装置,可以根据需要进行耕作、种植、收割等不同农业作业。

4. 操控简便:该款拖拉机采用人性化设计,操控简便易学,即使是没有农机操作经验的农民朋友也能轻松上手。

5. 舒适驾乘:山拖凯泰604配备了舒适的座椅和悬挂系统,有效减轻驾驶员的疲劳感,提高工作效率。

三、使用方法1. 上车准备:确认拖拉机处于停止状态,检查燃油、润滑油等液位是否充足,确认作业装置是否安装完好。

2. 启动拖拉机:插入钥匙,拧动启动开关,拖拉机发动机会启动。

3. 操作控制杆:根据需要,将控制杆放到对应的位置,如需要前进,将控制杆推向前方。

4. 进行作业:根据农田的具体情况和作业需求,选择对应的作业装置,进行耕作、种植、收割等作业。

5. 停车关机:完成作业后,将控制杆置于停止位置,拉起手刹,关闭燃油开关,拔下钥匙,即可完成停车关机。

四、安全注意事项1. 在操作拖拉机时,务必佩戴好安全帽和防护眼镜,确保自身安全。

2. 避免在陡坡、湿滑地面等危险环境下操作拖拉机,以防发生意外。

3. 在进行维修和保养时,必须先关闭发动机,并等待其冷却后再进行操作,以免烫伤。

4. 长时间操作拖拉机后,注意休息,避免疲劳驾驶,确保自身和他人的安全。

5. 定期对拖拉机进行保养和维修,保持其良好的工作状态,延长使用寿命。

五、维护保养1. 定期更换机油和滤清器,确保发动机的正常运行。

2. 定期检查轮胎气压,保持适当的气压,以确保行驶的稳定性。

60MM行程双联直滑电位器

60MM行程双联直滑电位器电位器型号SA6005GOA0A-HA1应用领域调音台、电子琴、吉他等特点较长的可调行程,性能稳定,手感较好,可以过波峰焊接,推柄可带LED,产品可以带中点定位。

有多种丰富的产品可以选择,可应对各种不同的需求。

主要功能调节音量、调节音调、调节平衡等主要格规参数滑动行程:60mm额定功率:0.2W最高使用电压:AC100V;工作温度:-10℃~70℃;滑动寿命:10,000次以上;SA6005规格参数一、MECHANICAL CHARACTERISTIC机械特性1、Sliding force滑动力矩:15~150gf.cm2、Click force定位推动力:80~330gf.cm3、Total travel slide全滑动行程:60mm4、Lever Stop Strength柄止档强度:≥3Kgf.cm5、Lever Wobble(mm p-p)滑柄偏摆量:1.6mm Max二、ELECTRICAL CHARACTERISTIC电气特性1、Total Resistance Range总阻及误差:1KΩ<R<1MΩ,±20%;1KΩ≥R or R≥1MΩ,±30%2、Resistance Taper电阻特性曲线:B3、Rating Power额定功率:0.2W4、Max.Operating Voltage最大工作电压:100V AC5、Residual Resistance残留电阻:R1,2≤10Ω;R2,3≤20Ω6、Insulation Resistance绝缘电阻:100MΩ1Minute at DC250V7、Dielectric Voltage耐电压:1Minute at AC250V三、ENDURANCE CHARACTERISTIC耐久特性1、Sliding Life滑动寿命:10,000cycles MinNote:In this catalog,if some parame ters lr drawings are different from the"Approval sheet",it's subject to the"Approval sheet".注明:如说明书与承认书规格参数、图面有异,均以承认书为准。

力纳克桌面电动升降系统产品手册说明书

/DESKLINE力纳克- 我们改善您的生活自1990年以来,力纳克®(LINAK®)一直致力于通过开发适用于全球办公桌和工作站的电动升降系统——持续与制造商或外部室内设计师密切合作,帮助重新定义现代工作场所的室内设计。

力纳克立足于真正的创新和持续改善供应链所有环节的坚定决心。

如今的力纳克是一家全球性公司,在丹麦、斯洛伐克、美国和中国均建有现代、灵活和高度自动化的生产设施,同时在全球约35个国家设有办事处。

1DESKLINE®-智能的升降Plug & Play TM 即插即用系统力纳克在电动升降办公家具领域拥有行业内最广的产品线。

我们为客户研发和提供从基础到更高级智能的办公升降系统,并且系统真正做到即插即用 (Plug & Play TM),简单使用。

使用力纳克DESKLINE®办公系列产品,您可以专注于家具的美学设计和耐用性。

作为领先全球的升降系统供应商,我们提供的即插即用的电动高度调整升降方案,应用于人们每天工作生 活使用的桌子、柜台、工作台等各种家具当中。

PVC-Free TM 系统为了用户的健康考虑,力纳克决定逐步将DESKLINE®办公系列产品实行全面无PVC化。

此举是对用户的健康负责,也是作为一个企业对社会环境负责的体现。

在我们的产品上标有PVC-Free TM标志的产品,都使用不含PVC的原材料生产而成。

ZERO TM 技术人们对节省资源、保护环境的意识开始逐渐增强。

力纳克采用独创的ZERO TM技术,降低升降系统的待机能耗,低至0.1W。

所有力纳克DESKLINE®办公系统控制盒,都已将此低待机能耗作为标准设置。

含有此标志的产品,表明均已应用此技术。

PIEZO TM 安全防撞技术PIEZO TM是力纳克基于硬件设计的安全防撞技术。

此技术可防止家具升降时因碰撞其他物体带来的损坏。

PIEZO感应器完全融入到力纳克升降柱的设计中,外观上无任何区别,也不需要额外安装其它设备。

无线电遥控器操作手册

F24-60系列工业用无线电遥控器操作手册F24-60安装及操作说明书保固质量确保禹鼎企业确保本产品出厂时, 完全符合其所公布之各项规格, 只要合适地安装,都能够正常使用, 不过禹鼎企业并不确保本产品操作是亳无中止或零错误。

确保期间本产品自出厂日起享受一年保固期, 确保用户在一年内不会有任何产品上问题, 若在保固期间内, 只要证实产品质量有瑕疵, 禹鼎企业愿意维修。

任何需要修护产品都必需送往禹鼎企业指定服务处, 该用户必需负担产品运往服务处单程运费, 而禹鼎企业服务处于确保期间内将会负担回程费用, 寄还该产品。

未包含事项前述确保范围, 并未包含按键、继电器、保险丝、电池等损耗性零件或是装机错误所造成基板损坏等, 且未包含因用户不妥使用、维修不足、操作环境规格忽略、未经许可变更、错误使用或用户自行设置接口而造成之故障。

备注◎前述之确保事项,并无其它明述或隐含保固事项。

◎保固所提供赔偿是用户唯一赔偿, 禹鼎企业并不负任何直接、间接、特殊、意外或因果损毁责任。

注意事项通常注意事项◎未经专业训练之人员, 不得拆开本机器, 不然可能损坏。

◎使用后天车总电源应关闭, 以切断接收机电源, 并将发射器之钥匙开关拔除。

◎天车应有总电源继电器、极限开关, 及其它安全性设施。

安装注意事项(一)接收机安装位置必需远离变频器、马达及其连接电缆越远越好以避免接收机受到噪声之干扰。

安装注意事项(二)接收机不可安装于电控箱内, 正确之安装方法是将接收机固定于电控箱顶部(或外部)之合适位置, 然后再将接收机输出电缆穿入电控箱内做合适之接线。

紧急情况之处理当紧急情况出现时, 请依下列步骤处理, 并立即通知经销商。

1.按下STOP紧急停止按键。

2.将发射机之钥匙开关拔除。

3.关闭天车总电源。

4.通知经销商, 找出原因。

F24-60操作方法日常操作1.将电量饱满之AA型(5号)电池四颗放入电池盒内。

2.依正确方向将电池盒放入发射器之电池放置区内, 并锁上电池盖。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Rev.1.00 Apr 05, 2006 page 2 of 4

元器件交易网

RKV604KL

Main Characteristic

10–6 10

–7

4.5 f = 1MHz 4.0 3.5

Reverse current IR (A)

Capacitance C (pF)

元器件交易网

RKV604KL

Package Dimensions

Package Name EFP JEITA Package Code RENESAS Code PXSF0002ZA-A Previous Code EFP / EFPV MASS[Typ.] 0.0007g

Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

1. Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap. Notes regarding these materials 1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party. 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials. 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein. The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors. Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (). 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein. 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use. 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials. 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination. Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited. 8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

元器件交易网

RKV604KL

Variable Capacitance Diode for VCO

REJ03G1363-0100 Rev.1.00 Apr 05, 2006

Features

• High capacitance ratio. (n = 1.73 to 2.10) • Low series resistance. (rs = 0.70 Ω max) • Extremely small Flat Lead Package (EFP) is suitable for surface mount design.

Note: For EFP package, the material of lead is exposed for cutting plane. There for, soldering nature of lead tip part is considered as unquestioned. Please kindly consider soldering nature.