PCBLayout工程师笔试题目

线路板考试题

线路板考试题PADS设计线路板工程师中级考试试题一、单项选择(30分)1、PADS Logic在线路设计过程中的作用是否 ( B )A绘制电路板B绘制线路图C前两者都是2、PADS Layout在线路设计过程中的作用是 ( A )A绘制电路板B绘制线路图C前两者都是3、PADS Logic中我们用的工具栏有几个 ( A )A1个B2个C3个4、PADS Logic进入元件封装的是以下哪个 ( A )A Part EditorB Part attribute managerC Part New5、绘制线路图Bue总线输入方式有几种 ( B )A1B2C36、绘制线路图光标模式有几种(C)A2B3C47、Pad2005元件库管理中有几种封装形式 ( C )A2B3C48、Pad Logic进入系统参数设定是 ( B )A Sheer…B Preference…C Deign Rule…9、Pad Logic中有几种栅格设定 ( A )A2种B3种C4种10、 Pad Logic中不是的系统提供的电源电压是 ( C )A+5VB+12VCVCC11、Pad Logic中网络表传导到POWER PCB的工具栏下有几个按钮( B )A5B6C712、在Pad Layout中不是系统提供了的单位是 ( B )AMILBCMCMM13、 Pad Logic中PART封装中可以包含多少个PCB封装 ( A )A不限B1个C2个14、 Pad Logic中PART封装中可以包含多少个CAE封装 ( A )A不限B1个C2个15、 Pad Logic导入Layout时会弹出记事本错误的是 ( A )A Logic和Layout库不对应B Logic里文件没画完C文件里元件太多16、Pad logict和Pad Layout关系说法不正确的是( C )A都可以直接输入中文B都可以互导网络C都可以生成CAM文件17、线路板设计时对部局说法正确的是(A)A先大的元件—中的元件—小的元件B先小的元件—中的元件—大的元件C以上说法都对18、线路板设计层定义分为几种(B)A2B3C419、线路板设计工作界面中对设计工具和修改工具的区别哪种说法是对的(B)A都能添加新的走线B都能移动元件位置C前两者都是错的20、PADS Layout文件与Protel99文件说法正确的( C )A 两者可以互导 B两者不可以互导 C只能PADS文件导入Protel9921、线路板设计中键盘放大的快捷键是以下哪个(B)A Paue breakB Page UpC Page Down22、下列哪一个是正确表达了光标会自动定位在C1上,并高亮显示(C)AC1SSBRRC1CSSC123、生产Layout走线宽度最小可以做到多少MM ( A )A0。

layout知识竞赛题库2

EDA知识竞赛题库(EDA岗位适用)初级篇 (2)一、填空题 (2)二、判断题 (2)三、单项选择题 (4)四、不定项选择题 (6)五、分析解答题 (10)高级篇 (3)一、填空题 (11)二、判断题 (3)三、单项选择题 (3)四、不定项选择题 (3)五、分析解答题 (3)初级篇一、填空题()1、BGA本体四周边缘与连接器通常是(250mil)最小间距(210mil)。

2、So系列器件本体贴片器件本体边缘gap为(40mil),引脚到贴片器件边缘gap为(50mil),引脚到贴片器件引脚gap为(50Mil)。

3、PLCC系类器件引脚到贴片器件本体边缘间距为(60mil),到引脚之间的gap为(50mil)4、申请物料导入comex库的流程分为两种,其中PLM已经有料号的直接走(零件封装申请)流程,没有料号的则走(电子新物料编码申请)流程。

5、PCB料号申请需要走(PCB物料编码申请)流程,料号描述厂牌变更需走(物料基础性变更)流程6、项目立项后,硬件工程师要EDA工程师画板,需要走(Layout工作申请)流程。

7、研发样机阶段,因为工艺原因需要做PCB修改,可以申请在PLM系统走(PCB改版申请)流程去做Gerber变更。

8、2层板,1.6mm板厚,要保证阻抗50欧姆,走线W/S为 20/5 mil9、贴片电容器件距离V-CUT必须满足 5mm 以上间距,如果不能满足,则需要加捞槽处理,对于垂直于V-CUT边的0805及以上贴片电容器件,距离少于10mm 必须加捞槽处理。

10、在布局完成后和出图前,需要导出 2D零件位置图(DXF文档)和3D文档给结构工程师确认。

11、邮票孔中心距离Trace边缘至少0.5mm。

12、光学点中心距离轨道边为(5.5)mm以上13、FR-4板厚(0.8mm)以下,板与板之间的连接使用邮票孔设计,14、T=板厚,t=V_CUT残厚,T=1.6mm时,t=(0.63mm),T=1.2mm时,t=(0.5mm),T=0.8mm时,t=(0.4),公差为+/-0.1mm15、USB 2.0走线的阻抗控制是(差分90)欧姆16、目前通用的PCB上最小VIA是(V16D8)17、排插与smt器件本体边缘为(40mil)18、在QFN、QFP等IC的散热PAD上打VIA,但为保证不漏锡到背面,这些VIA需要采用(半塞孔)设计。

28道《PCB布线及设计》考试题及答案(面试题一)

28道《PCB布线及设计》考试题及答案(面试题一)一、如何处理实际布线中的一些理论冲突的问题?问:在实际布线中,很多理论是相互冲突的;例如:1。

处理多个模/数地的接法:理论上是应该相互隔离的,但在实际的小型化、高密度布线中,由于空间的局限或者绝对的隔离会导致小信号模拟地走线过长,很难实现理论的接法。

我的做法是:将模/数功能模块的地分割成一个完整的孤岛,该功能模块的模/数地都连接在这一个孤岛上。

再通过沟道让孤岛和“大”地连接。

不知这种做法是否正确?2。

理论上晶振与CPU的连线应该尽量短,由于结构布局的原因,晶振与CPU的连线比较长、比较细,因此受到了干扰,工作不稳定,这时如何从布线解决这个问题? 诸如此类的问题还有很多,尤其是高速PCB布线中考虑EMC、EMI问题,有很多冲突,很是头痛,请问如何解决这些冲突?答:1. 基本上, 将模/数地分割隔离是对的。

要注意的是信号走线尽量不要跨过有分割的地方(moat), 还有不要让电源和信号的回流电流路径(returning current path)变太大。

2. 晶振是模拟的正反馈振荡电路, 要有稳定的振荡信号, 必须满足loop gain与phase的规范, 而这模拟信号的振荡规范很容易受到干扰, 即使加ground guard traces可能也无法完全隔离干扰。

而且离的太远, 地平面上的噪声也会影响正反馈振荡电路。

所以, 一定要将晶振和芯片的距离进可能靠近。

3. 确实高速布线与EMI的要求有很多冲突。

但基本原则是因EMI 所加的电阻电容或ferrite bead, 不能造成信号的一些电气特性不符合规范。

所以, 最好先用安排走线和PCB叠层的技巧来解决或减少EMI的问题, 如高速信号走内层。

最后才用电阻电容或ferrite bead的方式, 以降低对信号的伤害。

二、在高速设计中,如何解决信号的完整性问题?差分布线方式是如何实现的?对于只有一个输出端的时钟信号线,如何实现差分布线?答:信号完整性基本上是阻抗匹配的问题。

集成电路版图设计笔试面试大全

集成电路版图设计笔试面试大全1. calibre语句2. 对电路是否了解。

似乎这个非常关心。

3. 使用的工具。

, 熟练应用UNIX操作系统和L_edit,Calibre, Cadence, Virtuoso, Dracula 拽可乐(DIVA),等软件进行IC版图绘制和DRC,LVS,ERC等后端验证4. 做过哪些模块其中主要负责的有Amplifier,Comparator,CPM,Bandgap,Accurate reference,Oscillator,Integrated Power MOS,LDO blocks 和Pad,ESD cells以及top的整体布局连接5. 是否用过双阱工艺。

工艺流程见版图资料在高阻衬底上同时形成较高的杂质浓度的P阱和N阱,NMOS、PMOS分别做在这两个阱中,这样可以独立调节两种沟道MOS管的参数,使CMOS电路达到最优特性,且两种器件间距离也因采用独立的阱而减小,以适合于高密度集成,但是工艺较复杂。

制作MOS管时,若采用离子注入,需要淀积Si3N4,SiO2不能阻挡离子注入,进行调沟或调节开启电压时,都可以用SiO2层进行注入。

双阱CMOS采用原始材料是在P+衬底(低电阻率)上外延一层轻掺杂的外延层P-(高电阻率)防止latch-up效应(因为低电阻率的衬底可以收集衬底电流)。

N阱、P阱之间无space。

6. 你认为如何能做好一个版图,或者做一个好版图需要注意些什么需要很仔细的回答~答:一,对于任何成功的模拟版图设计来说,都必须仔细地注意版图设计的floorplan,一般floorplan 由设计和应用工程师给出,但也应该考虑到版图工程师的布线问题,加以讨论调整。

总体原则是模拟电路应该以模拟信号对噪声的敏感度来分类。

例如,低电平信号节点或高阻抗节点,它们与输入信号典型相关,因此认为它们对噪声的敏感度很高。

这些敏感信号应被紧密地屏蔽保护起来,尤其是与数字输出缓冲器隔离。

可靠性知识竞赛题库 Layout工程师岗位适用

可靠性知识竞赛试题(Layout工程师岗位适用)初级篇 (2)一、填空题 (2)二、单项选择题 (2)三、不定项选择题 (3)四、判断题 (5)五、分析解答题 (5)高级篇 (8)一、填空题 (8)二、单项选择题 (8)三、不定项选择题 (8)四、判断题 (10)五、分析解答题 (11)初级篇一、填空题1.在正常条件下,SELV电路要求任意导体间或者导体与地之间的电压值不能超过42.4Vpeak或60Vdc。

2.安规的七大危险是:能量危险、点击危险、火灾危险、热危险、机械危险、辐射危险、化学危险3.安规距离一般是量测空间距离和爬电距离4.全球范围内,一般民用产品的输入电压是100-240Vac。

5.按照IEC 60950的标准,加强绝缘的耐压测试电压值是3000Vac或者4242Vdc6.如产品需申请UL认证,接地阻抗测试,测试电流为40A,测试时间为2min。

7.(EU) No 801/2013中要求设备需在合理的最短时间内自动切换至网络待机模式,该最短时间是 20min。

(初级,/)8.产品按防电击保护类别可分为I类设备、II类设备、III类设备。

9.一次电路是直接与交流电网电源连接,二次电路是不与一次电路直接连接,而是由位于设备内的变压器、变换器或等效的隔离装置供电或由电池供电的一种电路。

10.附加绝缘是基本绝缘除以外施加的独立的绝缘,基本绝缘用以在一旦失效时减小电击的危险。

11.爬电距离是沿绝缘表面测得的两个导电零部件之间或导电零部件与设备防护界面之间的最短路径。

12.最小爬电距离取决于有效值工作电压,最小电气间隙和抗电强度试验电压取决于峰值工作电压。

13.海拔要求低于2000m时,A 型可插式设备的外壳上接地的可触及的导电零部件与带危险电压的零部件之间起基本绝缘作用的空气间隙为2mm,爬电距离为2.5 mm。

14.在评估安全距离时,除了作为外壳用的零部件以外的组件和零部件应当承受10±1N的恒定作用力。

PCB工程师试题

PCB工程师试题富士康拥有所有企业最为严格的考核制度和最为完善的养才智能。

只有有很好的考核制度才能真正的识别人才直至留住人才。

才能为公司服务直至使公司常青。

下面举两个例子说明之IE工程师试题IE工程师/助理工程师考核试题(试题答问时间为100分钟,满分为100分答题时间为90分钟)一, 填空题(43分,每空一分)1, 最早提出科学管理的人是______国的______;2, 工业工程-‘IE’是__________________两英文单词的缩写;3, 标准时间由__________和__________组成;4, 生产的四要素指的是__________,__________,___________,和__________;5, 生产效率指的是在单位时间内实际生产的合格品数量与__________的比值;6, 作业周期指的是_______________________________________________;7, 写出以下工程记号分别代表的内容:○-----------___________; ◇----------____________;□-----------___________; ▽----------____________;8, 通常作业的基本动作有:__________,____________,_____________,____________,____________ ,____________等等;9, 通常产品投放流水线时主要依据____________文件进行排拉作业;10, 影响生产品质的因素有:_________,___________,__________,__________,___________等;11,品质改善循环‘PDCA’指的是__________,__________,__________,__________;12,ISO是_____________组织,英文是:________________________;13, ‘5S’管理中,5S指的是_________,________,________,_______ ,_________;14, 品质管制七大手法中的特性要因图右称之___________,通过先提出问题,然后分析问题造成的原因;15, ISO-2000版体系文件包括:__________,__________,___________,__________四阶文件;二,选择题;(每题2分)1, 以下哪些是组成标准时间的宽放时间____:A, 现场宽放; B, 作业宽放; C, 方便宽放; D, 疲劳宽放;2, 以下哪些属于工厂布置改善的手法_____;A, P-Q分析法; B, 物品流程分析法; C, 改善对象物品的分析法D,PST分析法;3, ‘不必要的动作要减少’是动作经济原则的____之一点;A, 着眼点; B, 基本思想; C, 基本方法; D, 基本动作;4, ‘PTS’指的是_____;A, 动作经济分析法; B, 标准动作标准法; C,基本动作时间分析法; D,预定动作时间标准法;5, 以下哪些不属于2000版ISO9000的标准族:_____A, ISO9001; B,ISO9002; C,ISO9003; D,ISO9004;6, 生产作业时,________决定流水线的下线速度;A,流水节拍; B,标准时间; C,作业周期; D,作业周期;7, 以下哪些现象可以判断流水线不平衡?____;A, 连续堆机; B,工位等待; C, 不良品增加; D, 工具损坏;8, 工位作业员的操作依据是_____A,检验规范; B, 作业指导书; C, 作业流程图; D, 检查表;9, 以下关于质量方针和质量目标的关系哪项是错误的______;A, 质量方针和质量目标是毫无关系; B, 质量方针可以提供制定质量目标;C, 质量目标是建立在质量方针的基础上; D, 质量目标是定量的;10, 下列哪句话是对的:_____;A, 不良品肯定是不合格品; B,不合格品肯定是不良品;C, 合格品绝对是良品; D,良品绝对是合格品;三,判断题:(每体1分)1, 作业指导书内包含的内容有作业名称,作业方法,使用工具和使用物料等; ( )2, 流水线的人员配给是根据生产订单量的数量配给的; ( )3, 产品既有硬件产品,也有软件产品; ( )4, ISO是国际化的产品质量检验标准; ( )5, 配合制程的需要,减少物料的搬运,充分利用空间都是工场布置的关键; ( )6﹐一天内时针和分针相交的次数是23次﹔ ( )7﹐一天内超出8小时外的工作叫加班﹔ ( )8﹐使用工装治具的目的就是提高作业的效率和品质﹔ ( )9﹐焊接使用的6/4锡﹐指的是锡线含60%锡﹐含40%铅﹔ ( )10﹐应用CADR14软件时﹐一次只能开启一个窗口﹔ ( )四,综合问答题:(17分)1, 请写出IE七大手法?(3分)2, 简述什么叫生产线平衡?(3分)3, 通常在解决现场问题时,会使用到‘5W2H’管理方法,试问其所指的是什幺(3分)?4, 一般在什幺情况下必须进行现场改善?(5分)5,请说说作为一名IE工程师应具备哪些条件? (3分)五, 计算机知识题:(每题2分)1,当你用CAD软件绘制的某一图档丢失时,请问恢复档案最简单办法是什幺?2,CAD绘图软件中的‘TRIM’是什么命令?3,在EXCEL软件应用中,如何在同一单元格内打写多行文字?4,请问CAD软件绘制的图案可以用在WORD软件的文档上吗?如何操作?5,小胡在2001/8/21月制作了一份WORD文件,可是他不清楚存放在计算机的哪个位置,可现在他上司又急需要此份文件,假如你是小胡,你用什么方法找到这份文件?六,附加题(每一题4分)1,简述你过去服务的公司担任的职务及其取得的成绩?2,当生产效率达到目标效率时,你会做哪方面的工作?3,假如你对生产线某一工位进行作业改善时,你是如何去执行完成的?4,作为一名IE工程师,你认为应该做哪些工作?5,如果本公司给你机会做位工程师,你将如何展示你的工作能力?IE工程师/助理工程师考核试题答案一, 填空题:1, (美国,泰勒)2, (INDUSTRIAL ENGINEERING)3, (作业时间,宽放时间)4, (人员,机械设备,原材料和方法)5, (标准产能)6, (加工对象从投入至产出所需要的总时间)7, ○--- (加工) ◇---- (品质检查)□--- (数量检查) ▽----- (储存)8, (伸手,搬运,抓取,放手,拆卸,安置,旋转,加压等)9, (工程作业流程图)10, (人员,机器,设备,方法,环境及材料等)11, (计划,执行,检查,矫正)12, (国际化标准,INTERNATIONAL ORGANIZATION FOR STANDARDIZATION/ INTERNATIONALORGANIZATION STANDARDIZATION)13, (整理,整顿,清扫,清洁,素养)14, (鱼骨图/因果图)15, (品质手册/QM,程序文件/QP,作业指导书/OP,窗体/WI)二,选择题; 1,(A,B,C,D) 2,(A,B,C) 3,(B)4,(D)5,(B,C) 6,(A)7,(A,B) 8,(B)9, (A) 10,(A) 三,判断题: 1, (对) 2, (错) 3, (对)4, (错)5, (对)6﹐(错)7﹐(错)8﹐(对)9﹐(对)10﹐(对)四,综合问答题:1, 1)工程分析法;2)搬运工程分析法;3)稼动分析法(工作抽查法);4)生产线平衡法;5)动作分析法;6)动作经济原则;7)工场布置改善;2,答:依照流动生产线的工程顺序,从生产目标算出作业周期时间,将作业分割或结合,使各个工位的工作负荷达到均匀,提高生产效率的技法叫生产线平衡;3,答:分别是:WHO ----------何人WHAT ---------何事WHEN --------何时WHERE -------何处HOW ----------如何WHY ----------为何HOW MUCH—多少钱4,答, 1), 生产系统发生变更时;2), 因技术的进步变化时;3), 设计变更时;4), 现状的工场布置效率低时;5), 生产量常有增减时;6), 现场必须移动时;7), 新产品投入时;5,答: 问题的创造能力,问题的解决能力,抽象化能力,综合能力,创造能力,经济性价值判断能力,理解人际关系能力,表现能力,推销自己的能力等;五, 1,答,最简单的办法就是利用备份文件转换为DWG档案;2,答:是剪除命令;3,答:可以在储存格格式中的对齐项的文字控制选取‘自动换列’项;4,答: 可以的,打开以上两软件画面,首先在CAD图文件上选取所需图案进行复制,然后粘贴于WORD档案上即可;5,答:可以使用计算机的‘开始栏’的‘寻找档案或资料夹’功能,把已知的文件类型和日期输入条件格式内,然后进行查询,这样就很容易找出小胡所需的文件;六,附加题PCB Layout基礎篇試題一.填空題:(1)“PCB”這三個字母分別代表的意思:___________ __________ __________。

PCB板工程师中级考试试题1

PCB板工程师中级考试试题1一、单选题(每题5分,共10题)1.PCB代表什么?– A. Printed Circuit Board(印刷电路板)– B. Printed Control Board(印刷控制板)– C. Programmable Control Board(可编程控制板)– D. Personal Computer Board(个人电脑板)2.PCB设计中,通过什么工具可以实现电路连线的自动布线?– A. PCB Layout– B. PCB Router– C. PCB Editor– D. PCB Compiler3.在PCB设计中,什么是DRC错误?– A. Direct Current Reference– B. Design Rule Check– C. Digital Resistance Control– D. Data Retrieval Conflict4.PCB设计中,通过贴片工艺可安装的元器件包括以下哪些?– A. 轴向元件– B. 贴装元件– C. 插件元件– D. 异形元件5.PCB板中的通孔是用来连接什么之间的电路?– A. 表面电路与表面电路– B. 表面电路与内层电路– C. 表面电路与封装电路– D. 表面电路与外部电路6.在PCB设计中,什么是布局规则?– A. 定义元件的尺寸和形状– B. 控制元件之间的间距和方向– C. 确定元件的安装位置– D. 指定参考层和电源层7.PCB板设计中,通孔的类型包括以下哪些?– A. 盲孔、盖孔、贯通孔– B. 垂直孔、水平孔、导电孔– C. 圆孔、方孔、椭圆孔– D. 外层孔、内层孔、中间孔8.PCBA是指什么?– A. Printed Circuit Board Assembly(印刷电路板装配)– B. Printed Circuit Board Analysis(印刷电路板分析)– C. Personal Computer Build Assembly(个人电脑组装)– D. Processor Circuit Board Assembly(处理器电路板装配)9.PCB逻辑设计中,什么是电路图?– A. 显示元件和连接线之间关系的图形表示– B. 显示元件的位置和尺寸的图形表示– C. 显示元件和信号之间关系的图形表示– D. 显示元件和电源之间关系的图形表示10.PCB布图是指什么?– A. 将具体的元器件放置在PCB板上的过程– B. 将元件和连接线排列在PCB板上的过程– C. 将元件位置和尺寸确定在PCB板上的过程– D. 将元件和信号之间关系确定在PCB板上的过程二、多选题(每题5分,共10题)1.在PCB设计中,以下哪些元器件是通过贴片工艺安装的?– A. 轴向电解电容– B. 贴装电感– C. 插件电阻– D. 无源贴装元件– E. 压敏电阻2.在PCB布图时,以下哪些因素需要考虑?– A. 信号完整性– B. 散热问题– C. 电磁兼容性– D. PCB尺寸– E. 元件布局3.在PCB板设计过程中,以下哪些层是常见的板层结构?– A. 信号层– B. 电源层– C. 地平面层– D. 控制层– E. 丝印层4.在PCB设计中,以下哪些元器件需要考虑EMC设计?– A. 射频模块– B. 高速数字信号– C. 电源电路– D. 低速模拟信号– E. 独立电路单元5.PCB板的最小测量单位是什么?– A. mm(毫米)– B. cm(厘米)– C. inch(英寸)– D. μm(微米)6.PCB设计中,以下哪些因素会影响信号完整性?– A. 电流– B. 电压– C. 带宽– D. 阻抗– E. 延迟7.在PCB布局中,以下哪些规则需要遵守?– A. 硬规则– B. 软规则– C. 整数规则– D. 奇偶规则– E. 电源规则8.在PCB设计过程中,以下哪些检查是必须的?– A. DFM检查(Design for Manufacturability)– B. DRC检查(Design Rule Check)– C. SI检查(Signal Integrity)– D. PI检查(Power Integrity)– E. EMI检查(Electromagnetic Interference)9.PCB设计中,以下哪些软件是常用的PCB设计工具?– A. Altium Designer– B. Cadence Allegro– C. Mentor Graphics PADS– D. KiCad EDA– E. Eagle PCB10.在PCB板设计中,通过加入填充铜可以实现以下哪些目的?– A. 提高导热性– B. 提高信号完整性– C. 提高电流承载能力– D. 提高防护性能– E. 提高电容性能三、简答题(每题10分,共5题)1.PCB板设计中,什么是飞线?–飞线指的是通过导线或覆铜连接两个或多个元件或节点的连接方式。

PCBlayout面试试题

LAYOUT 面试试题1 ) 请简单说明LAYOUT 的流程?简要流程:原理图——新建库需求,网表输入其他需求——(倒入网表)设计要求分析——布局,规则导入——布局确认——(OK)PCB 布线、验证、优化——布线确认——设计资料输出——最终确认,结束2 ) 哪些因数会影响布线的阻抗及差分阻抗?不同阻抗如何在同一块板子上实现?答:影响因数:线宽,铜厚,介质介电常数叠层结构,同时影响差分阻抗的还有差分对的间距。

不同阻抗通常采用不同线宽或换层来达到要求3 ) 请问您做过哪此方面的板子,做过主机板吗?请对主机板一此主要零件如VGA 、LAN 、1394layout 时需注意事项做简要描述。

VGA: 基本走线要求:1. RED 、GREEN 、BLUE 必须绕在一起,视情况包GND. R.G.B 不要跨切割。

2 HSYNC 、VSYNC 必须绕在一起, 视情况包GND.LAN: 基本走线要求1. 同一组线,必须绕在一起。

2 Net: RX ,TX :必须differential pair 绕线.1394: 基本走线要求:1. Differential pair 绕线,同层,平行, 不要跨切割.2. 同一组线,必须绕在一起。

3 与高速信号线间距不小于50milUSB: 基本走线要求:1 Differential pair 绕线,同层,平行,不要跨切割.2 同一组线,必须绕在一起4 ) ALLEGRO 中零件PAD 共分这此层,请分别解释图中regular pad 、thermal relief 、anti pad 的意思及三者之间的关系。

Top 、bottom 、soldermask-top 、soldermask-bottom 、pastemask_top 、pastemask_bottom 之间的关系。

5 ) 在高速PCB 设计时我们使用的软件都只不过是对设置好的EMC 、EMI 规则进行检查,而设计者应该从那些方面去考虑EMC 、EMI 的规则?怎样设置规则?6 ) 电源以及电源转换部分是系统的心脏,请描述TRACE 宽度与流过电流大小的关系。

PCB--LAYOUT面试基本试题(doc 12页)

PCB--LAYOUT面试基本试题(doc12页)部门: xxx时间: xxx整理范文,仅供参考,可下载自行编辑LAYOUT面试试题1)请简单说明LAYOUT的流程?简要流程:原理图——新建库需求,网表输入其他需求——(倒入网表)设计要求分析——布局,规则导入——布局确认——(OK)PCB布线、验证、优化——布线确认——设计资料输出——最终确认,结束2)哪些因数会影响布线的阻抗及差分阻抗?不同阻抗如何在同一块板子上实现?答:影响因数:线宽,铜厚,介质介电常数叠层结构,同时影响差分阻抗的还有差分对的间距。

不同阻抗通常采用不同线宽或换层来达到要求3)请问您做过哪此方面的板子,做过主机板吗?请对主机板一此主要零件如VGA、LAN、1394layout时需注意事项做简要描述。

VGA:基本走线要求:1. RED、GREEN、BLUE 必须绕在一起,视情况包GND. R.G.B 不要跨切割。

2 HSYNC、VSYNC 必须绕在一起, 视情况包GND.LAN:基本走线要求1. 同一组线,必须绕在一起。

2 Net: RX,TX:必须differential pair 绕线.1394:基本走线要求:1. Differential pair 绕线,同层,平行,不要跨切割.2. 同一组线,必须绕在一起。

3 与高速信号线间距不小于50milUSB:基本走线要求:1 Differential pair 绕线,同层,平行,不要跨切割.2 同一组线,必须绕在一起4) ALLEGRO中零件PAD共分这此层,请分别解释图中regular pad、thermal relief 、anti pad的意思及三者之间的关系。

Top 、bottom、soldermask-top、soldermask-bottom、pastemask_top、pastemask_bottom之间的关系。

5)在高速PCB设计时我们使用的软件都只不过是对设置好的EMC、EMI规则进行检查,而设计者应该从那些方面去考虑EMC、EMI的规则?怎样设置规则?6)电源以及电源转换部分是系统的心脏,请描述TRACE宽度与流过电流大小的关系。

PCB板工程师中级考试试题1

基础知识一、单项选择(30分)1、PowerLogic在线路设计过程中的作用是( A )A 绘制线路图B 绘制电路板C 绘制元件封装2、PowerPCB在线路设计过程中的作用是( A )A 绘制电路板B 绘制线路图C 绘制元件封装3、PowerLogic中我们用的工具栏有几个( A )A 3个B 4个C 5个4、PowerLogic进入元件封装的是( B )A Part attribute managerB Part EditorC Part New5、线路图界面下快捷键进入颜色工作界面是( C )A Ctrl+Alt+VB Ctrl+ Alt +GC Ctrl+Alt+C6、全屏十字交叉光标模式是以下哪个( C )A Small crossB Full crossC Full screen7、PowerLogic进入库管理是以下哪个( A )A Library…B Report…C Print setup8、PowerLogic进入系统参数设定是( B )A Sheers…B Preferences…C Design Rules…9、PowerLogic中总路线设计有几种类型( B )A 1种B 2种C 3种10、PowerLogic中系统提供的地线形式有几种( C )A 1种B 2种C 3种11、PowerLogic中以下哪一个是将网络表传导到POWER PCB ( C )A Rules to pcbB Rules from pcbC Synchronize pcb12、在POWER PCB中系统提供了多少种单位进行换算( C )A 1种B 2种C 3种13、在PowerLogic中文件导出形式有几种( A )A 2种B 3种C 4种14、在PowerLogic中报表文件输出是以下哪个进入的( B )A Library…B Report…C Print setup15、在PowerLogic中输入备注是以下哪个( A )A Insert new object…B Insert new pcb object…C Insert old object…16、Power pcb安装运行环境的CPU要求最合理的是( B )A Pentium Ⅲ 400MHZ以上B Pentium Ⅲ 500MHZ以上C Pentium Ⅲ 600MHZ以上17、POWER PCB5。

PCB_LAYOUT(台湾资深硬体工程师15年Layout资料)道

LAYOUT REPORT目录Ver.0.2 LAYOUTREPORT .................................................................................................................. 1 目录...........................................................................................................................................1 1. PCB LAYOUT 术语解释TERMS.........................................................................................2 2. Test Point : ATE 测试点供工厂ICT 测试治具使用.................................................... 2 3. 基准点光学点-for SMD:........................................................................................... 4 4. 标记LABEL ING............................................................................................................. 5 5. VIA HOLE PAD..................................................................................................................... 5 6. PCB Layer 排列方式.......................................................................................................... 5 7.零件布置注意事项PLACEMENT NOTES........................................................................... 5 8. PCB LAYOUT 设计................................................................................................................ 6 9. Transmission Line 传输线. (8)10.General Guidelines –跨Plane (8)11. General Guidelines –绕线 (9)12. General Guidelines – Damping Resistor............................................................. 10 13. General Guidelines - RJ45 to Transformer......................................................... 10 14. Clock Routing Guideline........................................................................................... 12 15. OSC amp CRYSTAL Guideline...........................................................................................12 16. CPU RAM FLASH....................................................................................................14 17. General Guidelines –Decoupling Capacitor (14)18.POWER 部分........................................................................................................................ 15 19. GND amp Vcc Plan 切割...................................................................................................17 20. DRC : Design Rule Check...........................................................................................19 21. CAM 输出/输出文件参考gerber file 流程图........................................................20 22. 其他注意事项................................................................................................................. 21 23.PCB 制作规范填写注意事项............................................................................................ 23 11. PCB LAYOUT 术语解释TERMS 1. COMPONENT SIDE零件面、正面∶大多数零件放置之面。

PCB工程师试题-附答案

PCB工程师试题-附答案(某公司招聘试题)一.填空1.PCB上的互连线按类型可分为_微带线_和带状线2引起串扰的两个因素是_容性耦合和_感性耦合3.EMI的三要素:发射源传导途径敏感接收端4.1OZ铜的厚度是1.4 MIL5.信号在PCB(Er为4)带状线中的速度为:6inch/ns6.PCB的表面处理方式有:喷锡,沉银,沉金等7.信号沿50欧姆阻抗线传播.遇到一阻抗突变点.此处阻抗为75欧姆.则在此处的信号反身系数为_(0.2)8.按IPC标准.PTH孔径公差为: +/-3mil NPTH孔径公差为:+/-2mil9.1mm宽的互连线(1OZ铜厚)可以承载1 A电流10.差分信号线布线的基本原则:等距,等长11.在高频PCB设计中,信号走线成为电路的一部分,在高于500MHz频率的情况下,走线具有电阻、电容、电感特性。

12.最高的EMI频率也称为EMI发射带宽,它是信号上升时间而不是信号频率的函数。

(注释:计算EMI发射带宽公式为f=0.35/tr式中f-频率(GHZ); tr-信号上升时间或下降时间(10%~90%的上升或下降区间的时间)ns).13.大多数天线的长度等于某一特定频率的λ/4或λ/2(λ为波长)。

因此在EMC 规范中,不容许导线或走线在某一特定频率的λ/20以下工作,因为这会使它突然变成一根高效能的天线,电感和电容会造成谐振。

14.铁氧体磁珠可以看作一个电感并联一个电阻。

在低频时,电阻被电感短路,电流流向电感;在高频时,电感的高感抗迫使电流流向电阻。

在高频时,使用铁氧体磁珠代替电感器。

15.布局布线的最佳准则是磁通量最小化。

二.判断1.PCB上的互连线就是传输线. (x)2.PCB的介电常数越大.阻抗越大.(X)3.降底PP介质的厚度可以减小串扰.(X )4.信号线跨平面时阻抗会发生变化.(Y)5.差分信号不需要参考回路平面.(X)6.回流焊应用于插件零件.波峰焊应用于贴片零件.(X)7.高频信号的回路是沿着源端与终端两点距离最短路径返回.(X)B2.0差分的阻抗是100欧姆.(X.印象中是90)9.PCB板材参数中TG的含义是分解温度.(X.Tg为高耐热性.)10信号电流在高频时会集中在导线的表面.(Y)三选择1影响阻抗的因素有(A D)A.线宽B.线长C.介电常数D.PP厚度E.绿油2减小串扰的方法(BCDE)A.增加PP厚度B.3W原则(注释:走线间距是走线宽度的2倍)C.保持回路完整性;D.相邻层走线正交E.减小平行走线长度3.哪些是PCB板材的基本参数(A C D)A.介电常数B.损耗因子C.厚度'D.耐热性E.吸水性4.EMI扫描显示在125MHZ点频率超标.则这一现象可能由下面哪个频率引起的(B.A有点像,但倍频与B差得太远了A.12.5MHZB.25MHZC.32MHZD.64MHZ5.PCB制作时不需要下面哪些文件(B D )A.silkcreenB.pastmaskC.soldermaskD.assembly6.根据IPC标准.板翘应<= (C)A.0.5%B.0.7%C.0.8%D.1%7.哪些因素会影响到PCB的价格(A B Cd)A.表面处理方式B.最小线宽线距8 C.VIA的孔径大小及数量D.板层数8.导网表时出现如下错误:ERROR:Canot find device file for'CN-MINPCI-126'原因可能是(A)A.封装名有错B.封装PIN与原理图PIN对应有误C.库里缺少此封装的PADD.零件库里没有此封装四.术语解释微带线(Microstrip):指得是只有一边具有参考平面的PCB走线。

CEAC-PCB设计工程师-试卷

一、单选题(20题,每题2分,共40分)1、计算机辅助设计软件的英文缩写为? BA、CAMB、CADC、EDAD、CAE2、印制电路板的英文全称为? AA:Printed Circuit BoardB:Power Circuit BoardC:PCBD:Schematic3、Protel 推出的最新产品为? CA、Protel 99 SEB、Protel 2000C、Protel DXPD、Protel 20034、Protel 99 SE 中电路原理图设计模块为? AA:Advanced Schematic 99B:Advanced PCB 99C:Advanced SIM 99D:Advanced Route 995、Protel 99 SE 中印制电路板设计模块为? BA、Advanced Schematic 99B、Advanced PCB 99C、Advanced SIM 99D、Advanced Route 996、印制电路板图的文件名后缀为? CA、.libB、.schC、.pcbD、.ddb7、印制电路板图的设计规则检查的英文缩写为? CA、ERCB、PCBC、DRCD、PLD8、绘制电路原理图时,放置电源对象的快捷键为? BA、Alt + P, PB、Alt + P, OC、Alt + P, WD、Alt + P, N9、绘制电路原理图时,放置导线的快捷键为? CA、Alt + P, PB、Alt + P, OC、Alt + P, WD、Alt + P, N10、绘制电路原理图时,放置网络标号的快捷键为? DA、Alt + P, PB、Alt + P, OC、Alt + P, WD、Alt + P, N11、在画电路原理图时,编辑元器件电气属性中,哪一项为元器件类型? DA、Lib RefB、FootprintC、DesignatorD、Part Type12、在画电路原理图时,编辑元器件电气属性中,哪一项为元器件封装形式?BA、Lib RefB、FootprintC、DesignatorD、Part Type13、编辑电路原理图时,放置元器件的工具为Place菜单下的哪一项命令?BA、TrackB、PartC、WireD、Component14、编辑电路原理图时,画连线的工具为Place菜单下的哪一项命令? CA、TrackB、PartC、WireD、Component15、在画印制电路板图时,编辑覆铜线属性中,哪一项为覆铜线宽度? AB、SelectionC、NetD、Layer16、编辑印制电路板图时,放置文字的工具为Place菜单下的哪一项命令?CA、AnnotationB、Net LabelC、StringD、Timension17、在画印制电路板图时,放置铺铜的工具为Place菜单下的哪一项命令?CA、FillB、PadC、Polygon PlaneD、Track18、编辑印制电路板图时,放置铜箔走线的工具为Place菜单下的哪一项命令?AA、TrackB、PartC、WireD、Component19、编辑印制电路板图时,放置元器件封装的工具为Place菜单下的哪一项命令?DA、TrackB、PartC、WireD、Component20、印制电路板自动布线时,为什么会修改事先已布的线? BA、线宽设置不正确B、先布的线没有锁定C、网络不正确D、拐弯角度不正确二、多选题(10题,每题3分,共30分)1、网络表是描述电路元器件的?ACDA:编号B:功能C:封装D:管脚之间连接关系2、下列选项中哪些属于印制电路板图的设计对象?ACDB:网络标号C:过孔D:多边形铺铜3、布线设计完成后,一般设计规则检查(DRC)哪些方面?ABC A:走线规则检查B:电路板制造规则检查C:高频电路设计规则检查D:电气规则检查4、画印制电路板图时,放置元器件封装命令有以下几种途径?ACDA、菜单命令:Place\ComponentB、使用快捷键:Alt+P, FC、使用快捷键:Alt+P, CD、单击工具栏上的PlaceComponent 按钮5、画电路原理图时,放置总线命令有以下几种途径?( 5 分) ACDA、菜单命令:Place\BusB、使用快捷键:Alt+P, uC、使用快捷键:Alt+P, BD、单击连线工具栏上的Place Bus 按钮6、画电路原理图时,放置总线引入线命令有以下几种途径?ABA、菜单命令:Place\Bus EntryB、使用快捷键:Alt+P, uC、使用快捷键:Alt+P, BD、单击连线工具栏上的Place Bus 按钮7、画电路原理图时,放置导线命令有以下几种途径?ACDA、菜单命令:Place\WireB、使用快捷键:Alt+P, PC、使用快捷键:Alt+P, WD、单击连线工具栏上的Place Wire 按钮8、画印制电路板图时,放置过孔命令有以下几种途径?ACDA、菜单命令:Place\ViaB、使用快捷键:Alt+P, PC、使用快捷键:Alt+P, VD、单击工具栏上的PlaceVia 按钮9、画印制电路板图时,放置焊盘命令有以下几种途径?ABDA、菜单命令:Place\PadB、使用快捷键:Alt+P, PC、使用快捷键:Alt+P, VD、单击工具栏上的PlacePad 按钮10、自动布线后,在元器件的引脚附近会出现杂乱的走线,这问题怎么避免?BDA、合理设置元件网格B、重新自动布线C、不理睬它D、手工修正三、判断题(10题,每题3分,共30分)1、为了印制电路板自动布线,在画电路原理图时每个元器件必须有封装,而且元器件封装的焊盘与电路原理图元器件管脚之间必须有对应关系。

PCB--LAYOUT面试基本试题

LAYOUT面试试题1)请简单说明LAYOUT的流程?简要流程:原理图——新建库需求,网表输入其他需求——(倒入网表)设计要求分析——布局,规则导入——布局确认——(OK)PCB布线、验证、优化——布线确认——设计资料输出——最终确认,结束2)哪些因数会影响布线的阻抗及差分阻抗?不同阻抗如何在同一块板子上实现?答:影响因数:线宽,铜厚,介质介电常数叠层结构,同时影响差分阻抗的还有差分对的间距。

不同阻抗通常采用不同线宽或换层来达到要求3)请问您做过哪此方面的板子,做过主机板吗?请对主机板一此主要零件如VGA、LAN、1394layout时需注意事项做简要描述。

VGA:基本走线要求:1. RED、GREEN、BLUE 必须绕在一起,视情况包GND. R.G.B 不要跨切割。

2 HSYNC、VSYNC 必须绕在一起, 视情况包GND.LAN:基本走线要求1. 同一组线,必须绕在一起。

2 Net: RX,TX:必须differential pair 绕线.1394:基本走线要求:1. Differential pair 绕线,同层,平行,不要跨切割.2. 同一组线,必须绕在一起。

3 与高速信号线间距不小于50milUSB:基本走线要求:1 Differential pair 绕线,同层,平行,不要跨切割.2 同一组线,必须绕在一起4)ALLEGRO中零件PAD共分这此层,请分别解释图中regular pad、thermal relief 、anti pad的意思及三者之间的关系。

Top 、bottom、soldermask-top、soldermask-bottom、pastemask_top、pastemask_bottom之间的关系。

5)在高速PCB设计时我们使用的软件都只不过是对设置好的EMC、EMI规则进行检查,而设计者应该从那些方面去考虑EMC、EMI的规则?怎样设置规则?6)电源以及电源转换部分是系统的心脏,请描述TRACE宽度与流过电流大小的关系。

PCB工程师试题-附答案

PCB工程师试题-附答案(某公司招聘试题)一.填空1.PCB上的互连线按类型可分为_微带线_和带状线2引起串扰的两个因素是_容性耦合和_感性耦合3.EMI的三要素:发射源传导途径敏感接收端4.1OZ铜的厚度是1.4 MIL5.信号在PCB(Er为4)带状线中的速度为:6inch/ns6.PCB的表面处理方式有:喷锡,沉银,沉金等7.信号沿50欧姆阻抗线传播.遇到一阻抗突变点.此处阻抗为75欧姆.则在此处的信号反身系数为_(0.2)8.按IPC标准.PTH孔径公差为: +/-3mil NPTH孔径公差为:+/-2mil9.1mm宽的互连线(1OZ铜厚)可以承载1 A电流10.差分信号线布线的基本原则:等距,等长11.在高频PCB设计中,信号走线成为电路的一部分,在高于500MHz频率的情况下,走线具有电阻、电容、电感特性。

12.最高的EMI频率也称为EMI发射带宽,它是信号上升时间而不是信号频率的函数。

(注释:计算EMI发射带宽公式为f=0.35/tr式中f-频率(GHZ); tr-信号上升时间或下降时间(10%~90%的上升或下降区间的时间)ns).13.大多数天线的长度等于某一特定频率的λ/4或λ/2(λ为波长)。

因此在EMC 规范中,不容许导线或走线在某一特定频率的λ/20以下工作,因为这会使它突然变成一根高效能的天线,电感和电容会造成谐振。

14.铁氧体磁珠可以看作一个电感并联一个电阻。

在低频时,电阻被电感短路,电流流向电感;在高频时,电感的高感抗迫使电流流向电阻。

在高频时,使用铁氧体磁珠代替电感器。

15.布局布线的最佳准则是磁通量最小化。

二.判断1.PCB上的互连线就是传输线. (X)2.PCB的介电常数越大.阻抗越大.(X)3.降底PP介质的厚度可以减小串扰.(X )4.信号线跨平面时阻抗会发生变化.(Y)5.差分信号不需要参考回路平面.(X)6.回流焊应用于插件零件.波峰焊应用于贴片零件.(X)7.高频信号的回路是沿着源端与终端两点距离最短路径返回.(X)B2.0差分的阻抗是100欧姆.(X.印象中是90)9.PCB板材参数中TG的含义是分解温度.(X.Tg为高耐热性.)10信号电流在高频时会集中在导线的表面.(Y)三选择1影响阻抗的因素有(A D)A.线宽B.线长C.介电常数D.PP厚度E.绿油2减小串扰的方法(BCDE)A.增加PP厚度B.3W原则(注释:走线间距是走线宽度的2倍)C.保持回路完整性;D.相邻层走线正交E.减小平行走线长度3.哪些是PCB板材的基本参数(A C D)A.介电常数B.损耗因子C.厚度'D.耐热性E.吸水性4.EMI扫描显示在125MHZ点频率超标.则这一现象可能由下面哪个频率引起的(B.A有点像,但倍频与B差得太远了A.12.5MHZB.25MHZC.32MHZD.64MHZ5.PCB制作时不需要下面哪些文件(B D )A.silkcreenB.pastmaskC.soldermaskD.assembly6.根据IPC标准.板翘应<= (C)A.0.5%B.0.7%C.0.8%D.1%7.哪些因素会影响到PCB的价格(A B C d)A.表面处理方式B.最小线宽线距8 C.VIA的孔径大小及数量D.板层数8.导网表时出现如下错误:ERROR:Canot find device file for'CN-MINPCI-126 '原因可能是(A)A.封装名有错B.封装PIN与原理图PIN对应有误C.库里缺少此封装的PADD.零件库里没有此封装四.术语解释微带线(Microstrip):指得是只有一边具有参考平面的PCB走线。

PCB Layout工程师笔试题目

PCB Layout工程师笔试题目

一,填空

串扰的两个因素是( )和( )

的三要素( ),( ),( )

表面处理方式有( ),( ),( )等

差分信号线的布线的基本原则( ),( )

二,选择

影响阻抗的因素有( )

线宽 线长 介电常数 厚度 绿油

减少串扰的方法( )

增加 厚度 原则 保持回路完整性 相邻层走线正交 减小平行走线长度

三,回答题

的过程

管、 、电容的封装有哪些(每个不少于 例)

常用的画图软件有哪几种?

用 管搭出一个二输入与非门?

画出 的符号真值表?

、 的区别?

简单描述一个单片机系统的主要组成模块,并说明各模块之间的数据流流向和控制流流向?简述单片机应用系统的设计原则?

单片机上电后没有运转,首先要检查什么? 青年人首先要树雄心,立大志,其次就要决心作一个有用的人才。

集成电路应用工程师招聘笔试题及解答(某大型集团公司)

招聘集成电路应用工程师笔试题及解答(某大型集团公司)(答案在后面)一、单项选择题(本大题有10小题,每小题2分,共20分)1、在数字逻辑电路设计中,一个基本的二进制加法器如果需要完成1位二进制数的加法运算,它通常由哪两个部分组成?A. 半加器与全加器B. 仅半加器C. 仅全加器D. 或门与非门2、在模拟信号处理中,当一个信号通过一个RC滤波器时,如果RC时间常数τ远大于信号周期T,则该滤波器最有可能是?A. 高通滤波器B. 低通滤波器C. 带通滤波器D. 带阻滤波器3、题干:以下哪种技术不是用于提高集成电路集成度的方法?A. 金属化技术B. 双极性工艺C. CMOS工艺D. 三维集成电路技术4、题干:在集成电路设计中,以下哪个选项描述的是晶体管的工作原理?A. 晶体管通过控制电流来控制电压B. 晶体管通过控制电压来控制电流C. 晶体管通过控制电压来控制电荷D. 晶体管通过控制电荷来控制电流5、在集成电路设计中,以下哪种类型的设计是在芯片制造过程中需要考虑热设计的?A. 数字逻辑设计B. 模拟电路设计C. 集成电源设计D. 封装设计6、在集成电路测试中,用于检测芯片功能完整性的测试方法称为:A. 逻辑分析仪测试B. 静态测试C. 动态测试D. 芯片级测试7、集成电路应用工程师在电路设计中,以下哪种元件通常用于提供稳定的直流电源?A、电阻B、电容C、电感D、稳压二极管8、在数字集成电路中,以下哪种逻辑门可以实现与门和或门的组合功能?A、与非门(NAND)B、或非门(NOR)C、异或门(XOR)D、异或非门(XNOR)9、在集成电路设计中,以下哪个概念描述了电路中信号从一个元件到另一个元件传输时的信号衰减?A. 阻抗B. 增益C. 插入损耗D. 噪声 10、以下哪种类型的集成电路设计通常具有更高的集成度和更小的尺寸?A. 小规模集成电路(SSI)B. 中规模集成电路(MSI)C. 大规模集成电路(LSI)D. 超大规模集成电路(VLSI)二、多项选择题(本大题有10小题,每小题4分,共40分)1、以下哪些技术或工具通常用于集成电路设计验证阶段?()A、HDL(硬件描述语言)模拟B、FPGA(现场可编程门阵列)原型测试C、静态时序分析D、功耗分析E、电路板级测试2、以下哪些因素会影响集成电路的可靠性?()A、温度B、电压C、材料缺陷D、电路设计E、制造工艺3、以下哪些技术是集成电路设计中所常用的模拟信号处理技术?()A. 电压分压器B. 运算放大器电路C. 数字滤波器D. 模数转换器(ADC)E. 模数转换器(DAC)4、以下哪些是集成电路设计中常用的设计工具?()A. SPICEB. CadenceC. Altium DesignerD. MATLABE. Verilog5、以下哪些是集成电路设计中的模拟电路部分?()A、数字信号处理器B、模拟信号放大器C、滤波器D、A/D转换器E、时钟发生器6、以下哪些是集成电路制造过程中的关键步骤?()A、光刻B、蚀刻C、离子注入D、化学气相沉积E、封装7、以下哪些技术是集成电路设计中常用的模拟信号处理技术?()A. 运算放大器电路设计B. 滤波器设计C. ADC(模数转换器)设计D. DAC(数模转换器)设计E. 微控制器编程8、以下哪些是集成电路设计中常用的版图(Layout)设计工具?()A. Cadence VirtuosoB. Synopsys Design VisionC. Mentor Graphics EldoD. Altium DesignerE. Microsoft PowerPoint9、以下哪些技术或工具通常用于集成电路应用工程师的日常工作中?()A. FPGA(现场可编程门阵列)B. PCB(印刷电路板)设计软件C. SPICE(半导体器件模型和仿真)工具D. VHDL/Verilog(硬件描述语言)E. Python编程语言 10、在集成电路设计中,以下哪些因素会影响功耗?()A. 电路的工作频率B. 电路的晶体管类型C. 电源电压D. 电路的面积E. 电路的散热设计三、判断题(本大题有10小题,每小题2分,共20分)1、集成电路应用工程师在电路设计阶段需要参与整个芯片的开发过程,包括前端设计、后端布局布线以及生产测试。

pcb工程师面试问题汇总

pcb layout工程师的面试试题?1.PCB Layout 流程、工艺要求及注意事项;2.相关产品PCB Layout的安规规范和EMC要求;3.标准且常用的零件封闭尺寸(如SOP-8);4.基本的电路知识;5.PCB 的制作流程(注意及Layout流程区别)等。

6.实际操作能力(重要PCB工程师笔试题及答案一.填空1.PCB上的互连线按类型可分为 _微带线_和带状线2引起串扰的两个因素是_容性耦合和_感性耦合[hide]3.EMI的三要素:发射源传导途径敏感接收端4.1OZ铜的厚度是1.4 MIL5.信号在PCB(Er为4)带状线中的速度为:6inch/ns6.PCB的表面处理方式有:喷锡,沉银,沉金等pcb layout工程师的工作是需要很好的耐心的,而且更需要细心。

面试是你整个求职过程中最重要的阶段。

成败均决定于你面试时的表现。

每个人都能够学会怎么出色地面试,而且绝大多数的错误都可以预期并且避免,下面这些将给你带来成功的契机。

精心准备所有面试有可能需要的东西,比如文凭,身份证复印件,pcb 设计简历,相片等等,绝不能在这点上让人感到你是一个不认真的人。

完整地填妥公司的表格–即使你已经有简历。

即使你带了简历来,很多公司都会要求你填一张表。

你愿意并且有始有终地填完这张表,会传达出你做事正规、做事善始善终的信息。

面试前先自己预演一下,尝试你会被问及的各种问题和答案,即使你不能猜出所有你可能被问的问题,但思考它们的过程会让你减轻紧张而且在面试时心里有底。

用减轻紧张的技巧来减少你的不安,深呼吸以使自己冷静下来。

公众人物有很多舒缓压力的方法会帮助你进行面试。

在面试临近时练习一下如何放松自己,譬如放慢语速,你越放松越会觉得舒适自然,也会流露出更多的自信。

留心你自己的身体语言,尽量显得精警、有活力、对主考人礼貌。

用眼神交流,在不言之中,你会展现出对对方的兴趣。

PADS把你碰到的每一个人看成是面试中的重要人物,一定要对每一个你接触的人都彬彬有礼,不管他们是谁以及他们的职务是什么,每个人对你的看法对面试来说都可能是重要的。

PCB工程师试题-附答案

PCB工程师试题-附答案PCB工程师试题-附答案(某公司招聘试题)一.填空1.PCB上的互连线按类型可分为_微带线_和带状线2引起串扰的两个因素是_容性耦合和_感性耦合3.EMI的三要素:发射源传导途径敏感接收端4.1OZ铜的厚度是1.4 MIL5.信号在PCB(Er为4)带状线中的速度为:6inch/ns6.PCB的表面处理方式有:喷锡,沉银,沉金等7.信号沿50欧姆阻抗线传播.遇到一阻抗突变点.此处阻抗为75欧姆.则在此处的信号反身系数为_(0.2)8.按IPC标准.PTH孔径公差为: +/-3mil NPTH孔径公差为:+/-2mil9.1mm宽的互连线(1OZ铜厚)可以承载1 A电流10.差分信号线布线的基本原则:等距,等长11.在高频PCB设计中,信号走线成为电路的一部分,在高于500MHz频率的情况下,走线具有电阻、电容、电感特性。

12.最高的EMI频率也称为EMI发射带宽,它是信号上升时间而不是信号频率的函数。

(注释:计算EMI发射带宽公式为f=0.35/tr式中f-频率(GHZ); tr-信号上升时间或下降时间(10%~90%的上升或下降区间的时间)ns).13.大多数天线的长度等于某一特定频率的λ/4或λ/2(λ为波长)。

因此在EMC 规范中,不容许导线或走线在某一特定频率的λ/20以下工作,因为这会使它突然变成一根高效能的天线,电感和电容会造成谐振。

14.铁氧体磁珠可以看作一个电感并联一个电阻。

在低频时,电阻被电感短路,电流流向电感;在高频时,电感的高感抗迫使电流流向电阻。

在高频时,使用铁氧体磁珠代替电感器。

15.布局布线的最佳准则是磁通量最小化。

二.判断1.PCB上的互连线就是传输线. (X)2.PCB的介电常数越大.阻抗越大.(X)3.降底PP介质的厚度可以减小串扰.(X )4.信号线跨平面时阻抗会发生变化.(Y)5.差分信号不需要参考回路平面.(X)6.回流焊应用于插件零件.波峰焊应用于贴片零件.(X)7.高频信号的回路是沿着源端与终端两点距离最短路径返回.(X)B2.0差分的阻抗是100欧姆.(X.印象中是90)9.PCB板材参数中TG的含义是分解温度.(X.Tg为高耐热性.)10信号电流在高频时会集中在导线的表面.(Y)三选择1影响阻抗的因素有(A D)A.线宽B.线长C.介电常数D.PP厚度E.绿油2减小串扰的方法(BCDE)A.增加PP厚度B.3W原则(注释:走线间距是走线宽度的2倍)C.保持回路完整性;D.相邻层走线正交E.减小平行走线长度3.哪些是PCB板材的基本参数(A C D)A.介电常数B.损耗因子C.厚度'D.耐热性E.吸水性4.EMI扫描显示在125MHZ点频率超标.则这一现象可能由下面哪个频率引起的(B.A有点像,但倍频与B差得太远了A.12.5MHZB.25MHZC.32MHZD.64MHZ5.PCB制作时不需要下面哪些文件(B D )A.silkcreenB.pastmaskC.soldermaskD.assembly6.根据IPC标准.板翘应<= (C)A.0.5%B.0.7%C.0.8%D.1%7.哪些因素会影响到PCB的价格(A B C d)A.表面处理方式B.最小线宽线距8 C.VIA的孔径大小及数量D.板层数8.导网表时出现如下错误:ERROR:Canot find device file for'CN-MINPCI-126 '原因可能是(A)A.封装名有错B.封装PIN与原理图PIN对应有误C.库里缺少此封装的PADD.零件库里没有此封装四.术语解释微带线(Microstrip):指得是只有一边具有参考平面的PCB走线。

LAYOUT 版图布局复习题

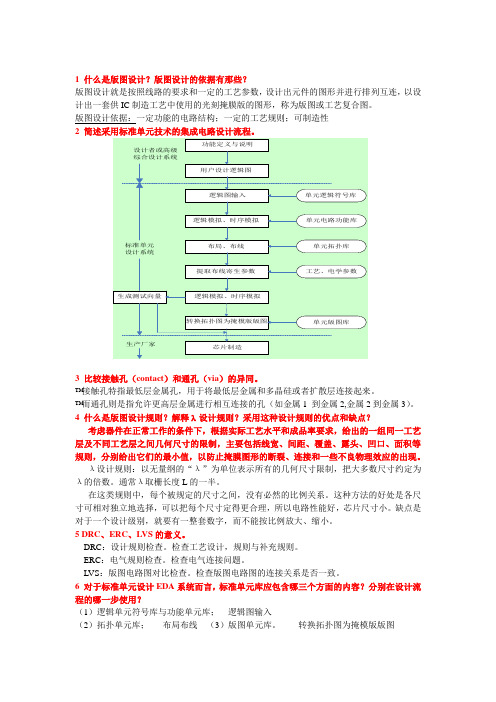

1 什么是版图设计?版图设计的依据有那些?版图设计就是按照线路的要求和一定的工艺参数,设计出元件的图形并进行排列互连,以设计出一套供IC制造工艺中使用的光刻掩膜版的图形,称为版图或工艺复合图。

版图设计依据:一定功能的电路结构;一定的工艺规则;可制造性23 比较接触孔(contact)和通孔(via)的异同。

™接触孔特指最低层金属孔,用于将最低层金属和多晶硅或者扩散层连接起来。

™而通孔则是指允许更高层金属进行相互连接的孔(如金属1 到金属2,金属2到金属3)。

4 什么是版图设计规则?解释 设计规则?采用这种设计规则的优点和缺点?考虑器件在正常工作的条件下,根据实际工艺水平和成品率要求,给出的一组同一工艺层及不同工艺层之间几何尺寸的限制,主要包括线宽、间距、覆盖、露头、凹口、面积等规则,分别给出它们的最小值,以防止掩膜图形的断裂、连接和一些不良物理效应的出现。

λ设计规则:以无量纲的“λ”为单位表示所有的几何尺寸限制,把大多数尺寸约定为λ的倍数。

通常λ取栅长度L的一半。

在这类规则中,每个被规定的尺寸之间,没有必然的比例关系。

这种方法的好处是各尺寸可相对独立地选择,可以把每个尺寸定得更合理,所以电路性能好,芯片尺寸小。

缺点是对于一个设计级别,就要有一整套数字,而不能按比例放大、缩小。

5 DRC、ERC、LVS的意义。

DRC:设计规则检查。

检查工艺设计,规则与补充规则。

ERC:电气规则检查。

检查电气连接问题。

LVS:版图电路图对比检查。

检查版图电路图的连接关系是否一致。

6 对于标准单元设计EDA系统而言,标准单元库应包含哪三个方面的内容?分别在设计流程的哪一步使用?(1)逻辑单元符号库与功能单元库;逻辑图输入(2)拓扑单元库;布局布线(3)版图单元库。

转换拓扑图为掩模版版图7 什么是ESD?请画出双二极管的ESD保护电路。

Electrostatic discharge 静电放电。

8 输入I/O PAD的主要作用是什么?输出I/O PAD的主要作用有哪些?输入单元的结构主要是输入保护电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PCB Layout 工程师笔试题目

填空

1 串扰的两个因素是( )和( )

2 EMI 的三要素( ),( ),( )

3 PCB 表面处理方式有( ),( ),( )等

4 差分信号线的布线的基本原则( ),( ) 二, 选择

1 影响阻抗的因素有( )

2 减少串扰的方法( )

A 增加PP 厚度

B 3W 原则

C 保持回路完整性

层走线正交 E 减小平行走线长度 三, 回答题

1 PCB Layout 的过程

2 MOS 管、IC 、电容的封装有哪些(每个不少于 3例)

3 常用的画图软件有哪几种?

A 线宽

B 线长

C 介电常数

D PP 厚度

E

绿油 D 相邻

4 用MOS 管搭出一个二输入与非门?

5 画出NOT,NAND,NOR 的符号真值表?

6 RS232、RS458 的区别?

7 简单描述一个单片机系统的主要组成模块,并说明各模块之间的数据流流向和控制流流向?简述单片机应用系统的设计原则?。