Allegro导入网表步骤

Allegro流程详解

Allegro流程详解Allegro流程详解⼀.零件建⽴在Allegro 中, Symbol 有五种, 它们分别是Package Symbol 、Mechanical Symbol、Format Symbol、Shape Symbol、Flash Symbol。

每种Symbol 均有⼀个Symbol Drawing File(符号绘图⽂件), 后缀名均为*.dra。

此绘图⽂件只供编辑⽤, 不能给Allegro 数据库调⽤。

Allegro 能调⽤的Symbol 如下:1、Package Symbol⼀般元件的封装符号, 后缀名为*.psm。

PCB 中所有元件像电阻、电容、电感、IC 等的封装类型即为Package Symbol。

2、Mechanical Symbol由板外框及螺丝孔所组成的机构符号, 后缀名为*.bsm。

有时我们设计PCB 的外框及螺丝孔位置都是⼀样的, ⽐如显卡, 电脑主板, 每次设计PCB时要画⼀次板外框及确定螺丝孔位置, 显得较⿇烦。

这时我们可以将PCB的外框及螺丝孔建成⼀个Mechanical Symbol, 在设计PCB 时, 将此Mechanical Symbol 调出即可。

3、Format Symbol由图框和说明所组成的元件符号, 后缀名为*.osm。

⽐较少⽤。

4、Shape Symbol供建⽴特殊形状的焊盘⽤, 后缀为*.ssm。

像显卡上⾦⼿指封装的焊盘即为⼀个不规则形状的焊盘, 在建⽴此焊盘时要先将不规则形状焊盘的形状建成⼀个Shape Symbol, 然后在建⽴焊盘中调⽤此Shape Symbol。

5、Flash Symbol焊盘连接铜⽪导通符号, 后缀名为*.fsm。

在PCB 设计中, 焊盘与其周围的铜⽪相连, 可以全包含, 也可以采⽤梅花辨的形式连接,我们可以将此梅花辨建成⼀个Flash Symbol, 在建⽴焊盘时调⽤此Flash Symbol。

其中应⽤最多的就是Package symbol即是有电⽓特性的零件,⽽PAD是Package symbol构成的基础.Ⅰ建⽴PAD启动Padstack Designer来制作⼀个PAD,PAD按类型分分为:1.Through,贯穿的;2.Blind/Buried,盲孔/埋孔;3.Single,单⾯的.按电镀分:1.Plated,电镀的;2.Non-Plated,⾮电镀的.a.在Parameters选项卡中, Size值为钻孔⼤⼩;Drill symbol中Figure为钻孔标记形状,Charater为钻孔标记符号,Width为钻孔标记得宽度⼤⼩,Height为钻孔标记得⾼度⼤⼩;/doc/c98e12f0f61fb7360b4c654b.html yers选项卡中,Begin Layer为起始层,Default Internal为默认内层,End Layer 为结束层,SolderMask_Top为顶层阻焊, ,SolderMask_Bottom为底层阻焊PasteMask_Top为顶层助焊, PasteMask_Bottom为底层助焊;Regular Pad为正常焊盘⼤⼩值,Thermal Relief为热焊盘⼤⼩值,Anti Pad为隔离⼤⼩值.Ⅱ建⽴Symbol1.启动Allegro,新建⼀个Package Symbol,在Drawing Type中选Package Symbol,在Drawing Name中输⼊⽂件名,OK.2.计算好坐标,执⾏Layout→PIN,在Option⾯板中的Padstack中找到或输⼊你的PAD,Qty代表将要放置的数量,Spacing代表各个Pin之间的间距,Order则是⽅向Right为从左到右,Left为从右到左,Down为从上到下,Up为从下到上;Rotation是Pin要旋转的⾓度,Pin#为当前的Pin脚编号,Text block为⽂字号数;3.放好Pin以后再画零件的外框Add→Line,Option⾯板中的Active Class and Subclass分别为Package Geometry和Silkscreen_Top,Line lock为画出的线的类型:Line直线;Arc弧线;后⾯的是画出的⾓度;Line width为线宽.4.再画出零件实体⼤⼩Add→Shape→Solid Fill, Option⾯板中的Active Class and Subclass分别为Package Geometry和Place_Bound_Top,按照零件⼤⼩画出⼀个封闭的框,再填充之Shape→Fill.5.⽣成零件Create Symbol,保存之Ⅲ编写Device若你从orCad中直接⽣成PCB的话就⽆需编写这个⽂件,这个⽂件主要是⽤来描述零件的⼀些属性,⽐如PIN的个数,封装类型,定义功能等等!以下是⼀个实例,可以参考进⾏编写:74F00.txt(DEVICE FILE: F00 - used for device: 'F00')PACKAGE SOP14 ? 对应封装名,应与symbol相⼀致CLASS IC ? 指定封装形式PINCOUNT 14 ? PIN的个数PINORDER F00 A B Y ? 定義Pin NamePINUSE F00 IN IN OUT ? 定義Pin 之形式PINSWAP F00 A B ? 定義可Swap 之PinFUNCTION G1 F00 1 2 3 ? 定義可Swap 之功能(Gate) PinFUNCTION G2 F00 4 5 6 ? 定義可Swap 之功能(Gate) PinFUNCTION G3 F00 9 10 8 ? 定義可Swap 之功能(Gate) PinFUNCTION G4 F00 12 13 11 ? 定義可Swap 之功能(Gate) PinPOWER VCC; 14 ? 定義電源Pin 及名稱GROUND GND; 7 ? 定義Ground Pin 及名稱END⼆.⽣成⽹表以orCad⽣成⽹表为例:在项⽬管理器下选取所要建⽴⽹络表的电路图系■Tools>>Create Netlist…■或按这个图标:有两种⽅式⽣成⽹表:◆按value值(For Allegro).◆按Device 值(For Allegro)◆按value值建⽴⽹络表1.编辑元件的封装形式在Allegro元件库中value形式为“!0_1uf__bot_!”,在ORCAD元件属性中已有相应value项“0.1uf (bot)”。

Allegro16.x导入网表介绍

Allegro 16.x 导入网表介绍

今天我们看下Allegro是怎么样导入原理图网表的,有的小白总认为导入网表很难,其实不然只要我们借助下一个Skill工具就可以很简单把原理图网表导入我们的板子里。

先来说下我们要用的Skill工具,这款工具的名字叫CITNO Skill这个工具里包含了很多平时我们设计当中用到的各种功能,比如快速拉取元件到当前光标(不需要拖动屏幕)这在元件布局很有用吧;还有就比较档案间的差异,还有最重要的就自动光绘功能太强了,按菜单顺序执行无需手动设置任何参数就可以把很多文件输出。

不多说了,工具自己搜索下就找到了。

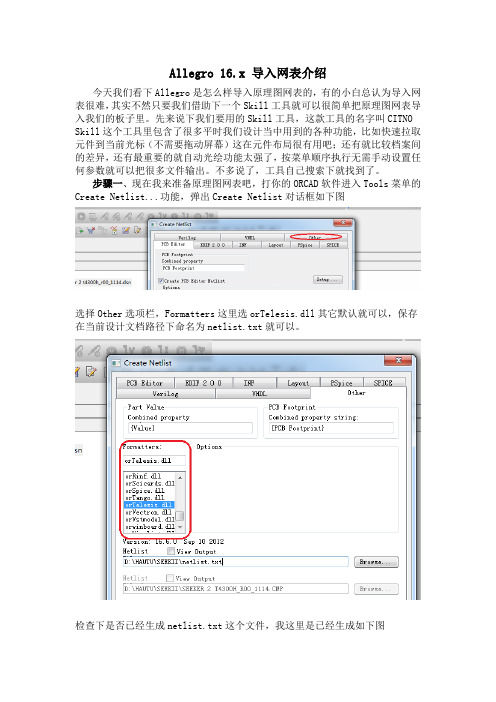

步骤一、现在我来准备原理图网表吧,打你的ORCAD软件进入Tools菜单的Create Netlist...功能,弹出Create Netlist对话框如下图

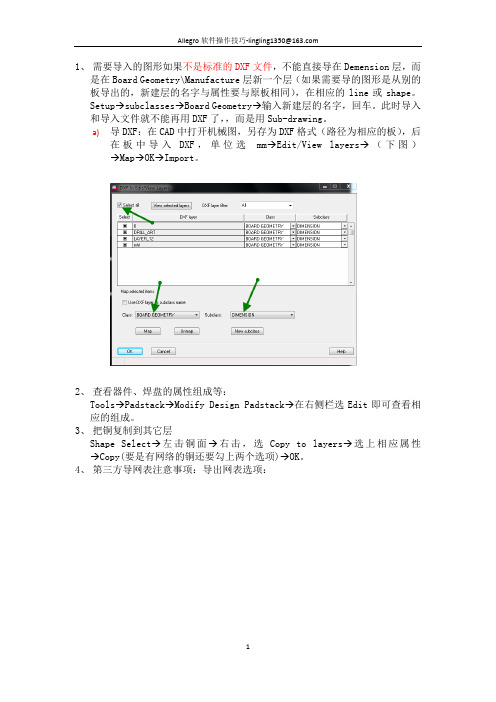

选择Other选项栏,Formatters这里选orTelesis.dll其它默认就可以,保存在当前设计文档路径下命名为netlist.txt就可以。

检查下是否已经生成netlist.txt这个文件,我这里是已经生成如下图

步骤二,准备已经导入Outline 的PCB档案,下面是我的板子已经有Outline

现在我们的板子是有零件库的,所以必须设置库路径。

现在把CITNO Skill菜单调出来,运行命令:CTRL+z

CITNO Skilll菜单界面图如下

其中Netin,3rd Party这是导入网表功能,即第三方网表导入现在我们开始执行此命令

过几秒钟之后,导入成功

现在我们把器件放置进来,下图我已经成功放置器件。

到这里我们的导入原理图网表教程已经结束,谢谢!。

Allegro软件操作技巧

5

Allegro 软件操作技巧-lingling1350@

2) (如上右图,其它操作同前) 3)上两步得到的网络列表分别拷到《U_管脚调整》表中。

再做成 lis 文件。

14、让两孔间的线等间距:ROUTE---RESIZE/RESPACE---SPREAD BETWEEN VOIDS。 对于两孔间有多跟线的情况同样适用。当然假如所有的线都用这种方法等间 距的话必然很费时, 修线时可以把格点改大、采用偶数小格点的方法就很容易让 两根线等间距了。 15、添加测试点 分为自动添加和手动添加两种,关键在于参数设置。 1) 自动添加

6

Allegro 软件操作技巧-lingling1350@

设置好参数后,点 Generetetesrpoints 就会给底层每个网络加上测试点。

7

Allegro 软件操作技巧-lingling1350@

另外,测试点之间保持 75mil 以上的间距、测试点与焊盘之间要也保持适当 的间距。

12

Allegro 软件操作技巧-lingling1350@

Байду номын сангаас

图a

图b

3)加粗:EDITCHANGE线宽为 50,如下图 c 所示: 实际上,电源平面比顾平面内缩 40,结合第一步 OFFSET 填 15、第三步加粗 到 50,不难得出,经过这一番折腾后,确实内缩了 40 吧。如果需要改变内缩大 小,自己算一下具体数值就行了。

2)16.3: 16.3 创建区域规则:Shanpe Add Rect,Options 参数设置如下图(区域 名称 BGA08 自动会出现在规则管理器中) 画区域铜 在规则管理器中的

3

Allegro 软件操作技巧-lingling1350@

Allegro操作说明(中文)Word文档

Allegro操作说明(中⽂)Word⽂档26、⾮电⽓引脚零件的制作1、建圆形钻孔:(1)、parameter:没有电器属性(non-plated)(2)、layer:只需要设置顶层和底层的regular pad,中间层以及阻焊层和加焊层都是null。

注意:regular pad要⽐drill hole⼤⼀点27、Allegro建⽴电路板板框步骤:1、设置绘图区参数,包括单位,⼤⼩。

2、定义outline区域3、定义route keepin区域(可使⽤Z-copy操作)4、定义package keepin区域5、添加定位孔28、Allegro定义层叠结构对于最简单的四层板,只需要添加电源层和底层,步骤如下:1、Setup –> cross-section2、添加层,电源层和地层都要设置为plane,同时还要在电⽓层之间加⼊电介质,⼀般为FR-43、指定电源层和地层都为负⽚(negtive)4、设置完成可以再Visibility看到多出了两层:GND和POWER5、铺铜(可以放到布局后再做)6、z-copy –> find⾯板选shape(因为铺铜是shape)–> option⾯板的copy to class/subclass选择ETCH/GND(注意选择create dynamic shape)完成GND层覆铜7、相同的⽅法完成POWER层覆铜Allegro⽣成⽹表1、重新⽣成索引编号:tools –> annotate2、DRC检查:tools –> Design Rules Check,查看session log。

3、⽣成⽹表:tools –> create netlist,产⽣的⽹表会保存到allegro⽂件夹,可以看⼀下session log内容。

29、Allegro导⼊⽹表1、file –> import –> logic –> design entry CIS(这⾥有⼀些选项可以设置导⼊⽹表对当前设计的影响)2、选择⽹表路径,在allegro⽂件夹。

Allegro中网络表的导入以及回编到Capture中的一些注意事项

Allegro中网络表的导入以及回编到Capture中的一些注意事项前言:网络表(Netlist)是沟通电路原理图和Layout实际板子的桥梁。

网络表包含的内容有零件Pin的连接线关系以及零件的包装等基本信息,Cadence提供的Capture到Allegro新的网络表的转发除了可以把一基本信息带到PCB Layout中,还可以把一些layout时用到的设定、约束通过网络表带到Allegro中,使工程师在设计电路时就可以大致了解PCB板子上的布线情况,从而也节省了Layout工程师的时间,提高了工作效率!例如:电子工程师可以在原理图中把一些Power线设定好最小线宽,这样用新转法时就可以直接把设定带入Allegro,可以防止Layout工程师疏忽忘了设定走线没有达到要求。

相反把PCB上的信息反馈到原理图中,这过程一般称为回编(Backannotation),以保证实物PCB与原理图同步。

例如:Layout工程师会对PCB上的零件作swap,rename等动作,为了保持PCB与原理图的统一必须把PCB中更改的内容回编到原理图中。

用Capture设计的原理图转入Allegro中有两种方式:第一种,第三方软件导入netlist的方式第二种,针对Cadence产品的直接导入方式,也称为新转法下面内容将会对这两种方式的特定和操作做相应介绍。

第一种,第三方软件导入netlist的方式优点:在Capture中定义可以相对简单,缺点:导入网络表和回编原理图都相对复杂,导入时需要Device file,回编时需要提供.swp file主要特点:这种方式是Capture 9.2以前的版本产生网络表导入Allegro的唯一方法,就是通过Capture Create Netlist的Other方式,格式选Allegro.dll就可以了,现在很多公司还常使用这种方式。

注意,在9.2以后的Capture中已经取消了这种转法,不过用户可以在9.2以前的版本中将allegro.dll复制到9.2以后的版本,放置路径预设C:\Cadence\PSD14.1\Capture\Netforms ,就可以使用这种转法了。

Allegro基本操作-机构图及网表的导入

三.网表的导入

需要資料: 1, Schematics 2, Library

Net-in的基本步驟

1.Export netlist

1.Export netlist

2.设定Library的路径

点击 Setup→User preferences,在出现的对 话框中编辑NET-IN时的Library的相关路径: Pad package symbols Device Type

3.Import netlist

1).首先打开allegro,选择菜单栏中的File→new,在 弹出的对话框中(Broswe)选择板子的名称和路径, Drawing Type选Board,选好后点击OK即可开启一个 全新的板子。

2).菜单File→import→logic,如下图:

3).弹出的对话框:

Add your company slogan

4.打开机构图所在的层面

菜单display→color/visibility或者直接点击图标 弹出以下对话框:

存放路径的根目录

存放路径的子目录 编辑显示的颜色

二.制作outline

1.菜单shape下 前三个分别可以 画多边形,矩形,圆形

2.或者点击菜单

3.界面右边选项如下图:

4.然后在主界面画出所需要的outline,就完成outline的制 作了。

Allegro基本操作 机构图及网表的导入

目录

一.机构图的导入 二.Outline的制作 三.网表的导入(netin)

一.机构图的导入

入

1.首先点击图标 打开Allegro文件 然后点File→Import →DXF,如右图所示:

机构图是DXF的形式才能被导

Allegro教程-17个步骤

Allegro教程-17个步骤Allegro是Cadence推出的先进PCB设计布线工具。

Allegro提供了良好且交互的工作接口和强大完善的功能,和它前端产品CadenceOrCADCapture的结合,为当前高速、高密度、多层的复杂PCB设计布线提供了最完美解决方案。

Allegro拥有完善的Constraint设定,用户只须按要求设定好布线规则,在布线时不违反DRC就可以达到布线的设计要求,从而节约了烦琐的人工检查时间,提高了工作效率!更能够定义最小线宽或线长等参数以符合当今高速电路板布线的种种需求。

软件中的Constraint Manger提供了简洁明了的接口方便使用者设定和查看Constraint宣告。

它与Capture的结合让E.E.电子工程师在绘制线路图时就能设定好规则数据,并能一起带到Allegro 工作环境中,自动在摆零件及布线时依照规则处理及检查,而这些规则数据的经验值均可重复使用在相同性质的电路板设计上。

Allegro除了上述的功能外,其强大的自动推挤push和贴线hug走线以及完善的自动修线功能更是给用户提供极大的方便;强大的贴图功能,可以提供多用户同时处理一块复杂板子,从而大大地提高了工作效率。

或是利用选购的切图功能将电路版切分成各个区块,让每个区块各有专职的人同时进行设计,达到同份图多人同时设计并能缩短时程的目的。

用户在布线时做过更名、联机互换以及修改逻辑后,可以非常方便地回编到Capture线路图中,线路图修改后也可以非常方便地更新到Allegro中;用户还可以在Capture与Allegro之间对对象的互相点选及修改。

对于业界所重视的铜箔的绘制和修改功能,Allegro提供了简单方便的内层分割功能,以及能够对正负片内层的检阅。

对于铺铜也可分动态铜或是静态铜,以作为铺大地或是走大电流之不同应用。

动态铜的参数可以分成对所有铜、单一铜或单一对象的不同程度设定,以达到铜箔对各接点可设不同接续效果或间距值等要求,来配合因设计特性而有的特殊设定。

Allegro高级教程-17个步骤让你掌握

二、导入网表 Ⅰ. 网表转化 在调入前,应该将要增加的定位孔和定位光标以及安装孔加到网表中,定位孔用 M*表示,定位光标用 I*表示 Ⅱ . 进入 Allegro,File/Import/Logic 调入网表,若显示"0 errs,0 warnings" 则表示没有错误,可以进行下一步,否则,应用 File/Viewlog 查看原因,根据提 示要求电路设计者修改原理图或自己在元器件库中加新器件.

4. 再画出零件实体大小 Add→Shape→Solid Fill, Option 面板中的 Active Class and Subclass 分别为 Package Geometry 和 Place_Bound_Top,按照 零件大小画出一个封闭的框,再填充之 Shape→Fill.

5. 生成零件 Create Symbol,保存之!!!

3. Format Symbol 由图框和说明所组成的元件符号, 后缀名为*.osm。比较少用。

4. Shape Symbol 供建立特殊形状的焊盘用, 后缀为*.ssm。像显卡上金手指封装的焊盘即 为一个不规则形状的焊盘, 在建立此焊盘时要先将不规则形状焊盘的形 状建成一个 Shape Symbol, 然后在建立焊盘中调用此 Shape Symbol。

用户在布线时做过更名、联机互换以及修改逻辑后,可以非常方便地回编 到 Capture 线路图中,线路图修改后也可以非常方便地更新到 Allegro 中; 用户还可以在 Capture 与 Allegro 之间对对象的互相点选及修改。

6 网络表的导入

Netlist导入网络表是连接原理图和Allegro Layout图档的桥梁。

在这里所介绍的Netlist的导入只是针对从Captrue9.2.3(原理图部分)产生的Netlist导入Allegro14.2(Layout部分)。

1.在Orcad Captrue中设计好原理图。

2.然后由Orcad Captrue产生Netlist(annotate是在进行原理图根据第五步产生的资料进行编改)。

3.把产生的Netlist导入Allegro(layout工作系统)。

4.在Allegro中进行PCB的layout。

5.把在Allegro中产生的back annotate(Logic)导出(在实际layout时可能对原有的Netlist有改动过),并导入Orcad Captrue里进行回编。

Netin的两种常用的方式:第一种:在Capture里输出netlist时选Allgero的方式;Allegro中导入的时候选Capture;第二种:在Capture里输出netlist时选Other,再选Allegro.dll的方式;Allegro中导入的时候选Other;下面内容会涉及到Device File这概念,下面先对Device File 介绍一下:Device 是一个文本文件,内容是描述零件以及Pin的一些网络属性。

包含的内容参考下面:可选(推荐)必备项目可选项目必备项目◆Captrue中的电路图整理在Captrue中可以加入一些对以后layout有帮助的定义,在下面会介绍这些定义。

零件的定义在零件的定义中和layout最有关的是定义零件中可以swap的pin和Functions。

下面就来详细介绍一下这个定义。

◆在原理图部分的定义如果用第一种方法导出Netlist的话,就要在原理图中就进行定义。

Swap Pin1.用鼠标点选想定义的零件。

2.点选菜单中Edit>Part。

3.点选菜单中View>Package。

ALLEGO导入网表快速指南

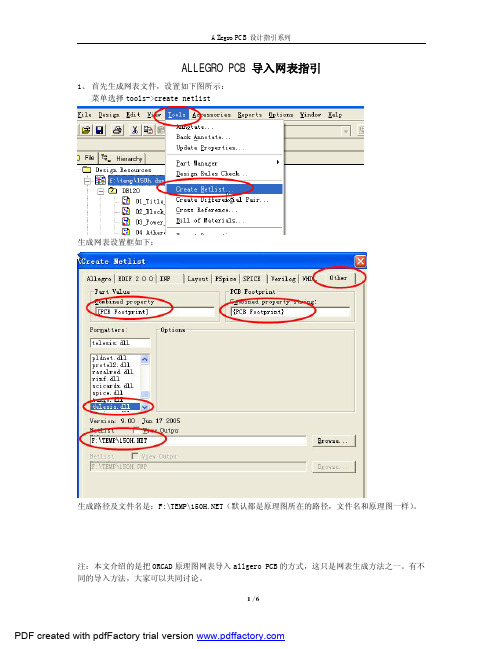

ALLEGRO PCB 导入网表指引

1、首先生成网表文件,设置如下图所示:

菜单选择tools->create netlist

生成网表设置框如下:

生成路径及文件名是:F:\TEMP\(默认都是原理图所在的路径,文件名和原理图一样)。

注:本文介绍的是把ORCAD原理图网表导入allgero PCB的方式,这只是网表生成方法之一。

有不同的导入方法,大家可以共同讨论。

2、打开一个PCB文件,然后设置元件库。

选择菜单:setup->user preferences

在跳出的user preferences 选项框设置design_paths->devpath的路径,在devpath右边的‘value’对应方框点击,必须放置对应的PCB封装库路径。

方法如下:

然后,继续在user preferences 选项框设置两个路径:padpath、psmpath,如下图所示:

3 然后,开始在Allegro PCB里面导入网表文件,如下图所示:File->import->logic

跳出的方框是:

选择others,

在import list 格内,选择好网表文件所在的路径及网表文件后,点击”import other”,导入网表文件!

4 在pcb放置文件。

如果没有错误,就可以在PCB里面采单Place选项放置元件。

有错误请检查原理图相关项目。

如下图所示,采用的是系统自动放置的方式quick place:

点击“PLACE”后,放置完元件后,点击“OK”即可完成!

如果出现错误,请在PCB目录下面查找netin文件并更正错误,然后重复以上工作。

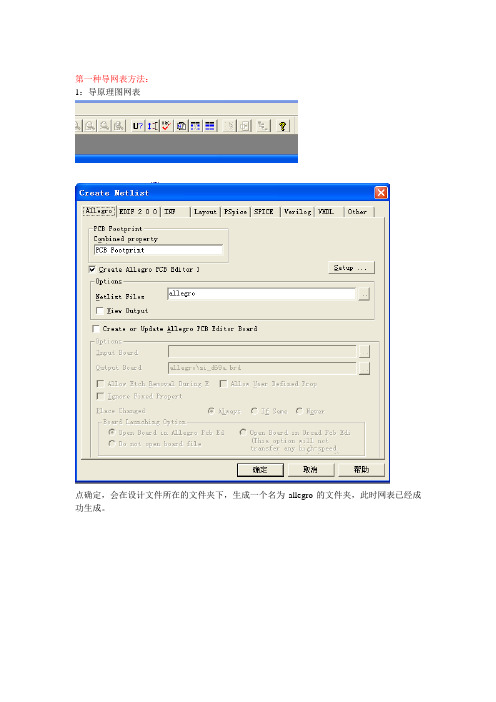

Allegro导网表的几种方法

第一种导网表方法:1:导原理图网表点确定,会在设计文件所在的文件夹下,生成一个名为allegro的文件夹,此时网表已经成功生成。

2:打开BRD文件,导网表点File-Import-Logic,弹出Import Logic的对话框,见下图点Import Cadence,成功导入器件。

第二种导网表方法:1:如果不是从CIS中导入网表,采用第3网表进行的话,可以采用下面的步骤此时要注意的是,要将TXT文件中的,NETS中有空格的地方都要去掉,比如SCR_LOCK GREEN修改成SCR_LOCKGREEN或着SCR_LOCK_GREEN,网络名中不可以有空格等特殊符号。

修改好就可以进行网表的导入了。

2:打开BRD文件,导网表点File-Import-Logic,弹出Import Logic的对话框,见下图选择other选项,找到2222.txt文件,点Import Other,器件就成功导入BRD文件中。

不画原理图进行设计1:如果器件PIN数很少的话,就完全没有必要进行原理图的绘制。

可以直接添加器件,依照下边的步骤进行点击Logic-Part Logic,弹出对话框,见下图在Parts List对话框中,找到Refdes选项,填入你所需要的器件名称,点Allegro Components选项,弹出以下对话框点所需要的TXT文件,后点OK确定。

在Parts List对话框中,点OK。

就成功添加了一个器件。

在以下对话框中查看添加的器件,并把器件放到板子中来。

点Place-Manually…直接放置元件的时候(不画原理图),在logic-net logic无法进行,同样也拿不出元件SET UP –USER PREFERENCES-MICS-logic-edit-enabled,将此选项勾上即可。

后弹出下面对话框,点Create,输入X1(28),就可以添加一个新的网络X1(28)选择NET:X1(28),点所要添加的PIN,就可以把网络加到指定的PIN中。

Allegro导入网表步骤

Allegro 如何导入网表一.首先要保证原理图Design rule check 没有问题。

二.从原理图中导出Netlist 。

原理图中Tools->Create Netlist 或者直接点击快捷键;出来如下图所示选择框,选择网表放置的文件夹,点击确定。

导出完成后会生成Netlist 文件(共三个文件)。

注意:导出网表时有时候会提示有error ,如果有error 则无法生成网表,需要按提示将error 解决,然后重新导出。

三.从PCB 中导入Netlist 。

1.打开allegro 新建一个.brd 文件。

2.绘制PCB 边框。

选择菜单项Add->Line 。

Options 窗口设置如下图所示,Line width(线宽)选择0.15mm 。

然后在工作区域内画出一个PCB边框的区域。

3.设置library路径。

选择Setup->User Preferences,弹出User Preferences Editor 对话框,点击 Paths 前面的‘+’号展开来,再点击Library,需要设置其中三个参数,将封装库添加到目录下,如下图所示。

4.导入网络表。

选择菜单File->Import->Logic,如下图所示。

Import dirctionary选择网表放置的文件夹。

点击Import Candence,开始导入。

5.放置元器件。

点击Place->Quickplace菜单,弹出Quickplace对话框,如下图所示。

点击Place 按钮后,元件自动的摆放出来,单击OK 按钮就可以关闭对话框。

完成后如下图所示。

至此,网表导入结束。

Allegro PCB Editor使用流程简介

本文档主要介绍Cadence的PCB设计软件Allegro PCB Editor的基本使用方法,其中封装库的建立不再赘述,参见“Cadence软件库操作管理文档”。

目录一、创建电路板 (2)1、新建电路板文件 (2)2、设置页面尺寸 (2)3、绘制电路板外框outline (3)4、电路板倒角 (4)5、添加装配孔 (5)6、添加布局/布线允许区域(可选) (7)二、网表导入和板层设置 (7)1、网表导入 (7)2、板层设置 (8)三、布局 (9)1、手动布局 (9)2、布局时对元器件的基本操作 (10)3、快速布局 (11)4、按ROOM方式布局 (12)5、布局复用 (15)四、设置约束规则 (17)1、设置走线宽度 (17)2、设置过孔类型 (18)3、间距规则设置 (19)五、布线 (20)1、设置走线格点 (20)2、添加连接线 (20)3、添加过孔 (21)4、优化走线 (21)5、删除走线 (21)六、敷铜 (22)1、设置敷铜参数 (22)2、敷铜 (23)七、PCB后处理 (25)1、检查电路板 (25)2、调整丝印文本 (27)3、导出钻孔文件 (28)4、导出光绘文件 (29)一、创建电路板1、新建电路板文件原理图成功导出网表进行PCB设计之前,首先需要根据实际情况建立电路板文件(.brd),主要是设置PCB板的外框尺寸(软件中称为outline)、安装孔等基本信息。

启动Allegro PCB Editor软件:选择“File-New”,在新建对话框中设置电路板存放路径,名称等信息:点击“OK”2、设置页面尺寸这里的页面尺寸并不是电路板的实际尺寸,而是软件界面的允许范围,根据实际电路板的大小设置合理的页面尺寸。

选择“Setup-Design Parameters”范围设置(Extents)中的Left X和Lower Y分别代表页面最坐下角的坐标,初次启动软件时,默认原点(0,0)为页面的最左下角。

allegro 中输入网表

在Allegro 中执行File→Import→Logic…命令,得到输入逻辑(Import Logic)对话框。

在输入逻辑(Import Logic)对话框的Cadence 表格中选择相应的原理图输入类型(Import logic type)。

例如,HDL-Concept、Capture (包括Capture CIS)或SCALD。

当你选择输入逻辑类型(Import logic type)为HDL-Concept 时,你可以选择仅仅输入改变(Import changes only)确认框,以便仅仅输入原理图中改变的内容,当前的设计没有进行任何其它修改;选择覆盖当前约束(Overwrite current constraints)确认框,将修改设计中当前所有的内容。

放置改变的元件(Place Changed Component)的选择缺省值为总是(Always),它表示在设计中使用新的元件,根据在封装编辑器中的参考编号(Reference Designator),替换所有的元件。

它让你使用完全不同的元件类型替换一类元件。

选择Never,则不进行在封装编辑器中的新元件替换元件,你必须交互地完成这些改变。

选择如果符号相同(If same symbol),则在设计中使用封装编辑器中的新的元件,根据它们的参考编号(Reference Designator),仅仅当设计中元件的封装/元件符号、数值和公差等相同时,才进行替换。

对于在ECO 期间允许删除铜(Allow etch removal during ECO)确认框,如果你选择了,则意味着你希望交互地撤除并重新布线。

如果你选择了,则意味着你希望节约时间,由Allegro 撤除这些管脚到T 型连接处或管脚的铜,并重新布线。

忽略固定属性(Ignore FIXED property)则表示在设计元件输入时,忽略元件的固定属性。

选择适当的输入路径(Import directory)。

allegro网络表导入

在使用DXP的时候,不存在网表导入等问题,大多数的行为已经是软件自动完成了,但是在Allegro中却不行,需要自己手动来完成。

注意在绘制电路板的时候,要先确定绘制区域,以及各个层的状况,边界,安装孔等,都不是随意的来修改。

网表的生成,首先要重新编辑元件编号,先选择dsn文件,然后选择Tools -> Annotate。

scope要选择整个工程,entire。

action中要先选择reset part references to "?"来取消所有的编号,然后再选择无条件的索引更行,Unconditional reference update 来进行全部重新跟新。

然后进行DRC检查,先选择dsn文件,然后再选择Tools -> Design Rules Check。

DRC只能检查出原理图的连接问题,和元器件的属性等。

接着再来查阅器件的封装,在确定器件封装的时候,我有一点点建议,虽然稍微麻烦一点,但是却能够减小出问题的概率。

原理图检查之后,不仅仅要保证没有DRC错误,还要保证没有原理上的错误,这样就生成一张器件清单列表,方法为:在dsn文件被选中的情况下,Tools -> Bill of Materials。

可以不做任何修改的生成bom清单,路径在最下面的Browse可以看到,不做修改会放在同一工程目录下的。

查阅工程目录表,可以看见Outputs下面就有一个.bom后缀名的文件,双击这个文件就可以看见使用了哪一些器件,以及个数。

生成元件清单除了是.bom的方式外,也可以是excel表格,但是由于生成的速度比较慢,所以我就直接选择复制粘贴到excel表格中了。

生成的这个表格有两个作用:一是采购元件的时候有一个详细列表,能够方便的采购人员来查阅;二是将各种器件的封装记录下来,保证每一个封装都存在。

器件封装的绘制见之前的博文。

封装的添加,在原理图中,在dsn文件出右键,选择Editor Object Property, 查阅PCB Footprint这一栏中是不是每一个器件的封装都已经填写上了,并且是不是和相应的原理图对应。

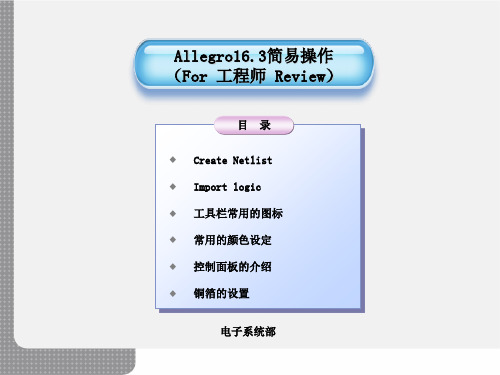

Allegro16.3操作

格点显示的颜色

钻孔的颜色

工作区域的底色

Stack-Up

Conductor

Etch:走线层

Anti Ehch:负片时 电源层的分割线

勾选All这一栏, 每一层的颜色将全 部打开

Stack-Up

Non-Conductor

Areas

用于某一特定的区域,通常建零件时会有用到

Board Geometry

铜箔的设置

在review layout时,如果想将铜箔隐藏,点菜单栏的setup---Display---shape_fill--勾选no_shape_fill,

铜箔设置前

铜箔设置后

Via 显示当前命令下的NET名 Line和Arc 线宽的设定 走线的几种推挤模式 勾选拉线在格点上 勾选上,走线时当同一 条网络有重复线段时会 自动取消原来的那条

Show Element命令下的Find

群组

铜箔 具有电气特性的局 部走线中某一线段

零件

网络

不具有电气特Байду номын сангаас二 维线中的某一线段

Pin脚 DRC 过孔 文字

具有电气特性的同 一层的整条走线

不具有电气特性 二维线

举例说明一

要查看某一颗零件时: 点工具栏 图标,在上图中勾选 然后从工作

区域选中你要查看的那颗零件

举例说明二

要测量线间距时: 点工具栏 图标,在上图中勾选 然后从工作

区域选中你要查看的网络

点击左图中的下拉菜单弹出右图所示,可以快速的打开你想要显示的层,这些层只 有在Artwork里添加后才会出现

用来放置尺寸的标 示,如:零件,板 框的大小等 板框

板子上添加的文字。 如PCB版次,编号等

Cadence(5)网表的导入和初步布局设置

Cadence(5)网表的导入和初步布局设置Cadence(5)网表的导入和初步布局设置1,布局前的工作:导入网表,file---import---logic,cadence 自己集成的有capture,所以选Cadence(design entry CIS),若是其他类型的网表,则选other。

下面always...找到网表路径目录(一般是原理图工程文件夹下的allegro下),点击import cadence导入网表。

之后,可在place manually中查看(有无元件等)之。

原理图与PCB封装的对应,靠的是元件属性里面的pcb footprint的名字和PCB封装的名字相同。

2,设置栅格点。

setup---grids,grids分电气属性的和非电气属性的,一般非电气属性的选100mil,如电路板板框,电气属性的选25mil,如assembly top。

奇怪的一点,手工放置元器件采用的是非电气属性的grids。

3,然后setup---drawing options中,设置一些常用的选项即可。

关于元件的放置:1,镜像mirror。

用于放置底层,就是起个镜像的作用。

法1,右栏中选mirror再放置元件;法2,选中元件后放置时右键,点mirror;法3,setup--drawing option---symbol,勾选symbol的mirror,这是全局变mirror。

若想改变已经放置好的元件,edit---mirror,点一下要改变的元件即可。

2,旋转rotate。

在edit---move时,右键选rotate即可,选装角度在右栏中选。

3,原理图和PCB的交互设置。

在原理图工程文件中选中.dsn文件,选option---preference---miscellaneous,选中enable intertool communication,然后将allegro中的place---manually 状态激活。

allegro-NET IN

2. 网络表的导入NET IN

1. 从电子工程师处拿到的任何NET文件先将其文件名改为:

orcad.dat。

2. 打开or2a.exe程序,在其中输入字母Y,将orcad.dat转换成

档案,如下图所示。

将文件,及所有零件封装与board放同一文件夹symbols下再进行后续工作。

3. 执行指令FILE\IMPORT\LOGIC(执行该指令之前必须先将已导入

结构图的公板放入SYMBOLS文件夹下),设定如下图所示:

4.按图所示设定好后就可以点击Import Cadence,导入NETIN。

5.对于NETIN成功与否,可以察看软件平台的左下角文字叙述,例如下图所示:

6,如果netin未成功,则打开netin过程中自动生成的netin.log 文件(记事本文档),在编辑/查找中输入error,到出现如下信息:ERROR: Cannot find device file for 'EXPCARD-1CX412P2-GC-26P-FM5'.

则说明缺少footprints(封装)为EXPCARD-1CX412P2-GC-26P-FM5的零件。

IN过程中可能出现的错误有:

A,零件库中不存在某零件;

B,零件pin不对;

C,出现single net.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Allegro 如何导入网表

一.首先要保证原理图Design rule check 没有问题。

二.从原理图中导出Netlist 。

原理图中Tools->Create Netlist 或者直接点击快捷键

;出来如下图所示选择框,选择网表放

置的文件夹,点击确定。

导出完成后会生成Netlist 文件(共三个文件)。

注意:导出网表时有时候会提示有error ,如果有error 则无法生成网表,需要按提示将error 解决,然后重新导出。

三.从PCB 中导入Netlist 。

1.打开allegro 新建一个.brd 文件。

2.绘制PCB 边框。

选择菜单项Add->Line 。

Options 窗口设置如下图所示,Line width(线宽)选择0.15mm 。

然后在工作区域内画出一个PCB边框的区域。

3.设置library路径。

选择Setup->User Preferences,弹出User Preferences Editor 对话框,点击 Paths 前面的‘+’号展开来,再点击Library,需要设置其中三个参数,将封装库添加到目录下,如下图所示。

4.导入网络表。

选择菜单File->Import->Logic,如下图所示。

Import dirctionary选择网表放置的文件夹。

点击Import Candence,开始导入。

5.放置元器件。

点击Place->Quickplace菜单,弹出Quickplace对话框,如下图所示。

点击Place 按钮后,元件自动的摆放出来,单击OK 按钮就可以关闭对话框。

完成后如下图所示。

至此,网表导入结束。