I2C总线应用下的EEPROM测试

I2C读写EEPROM文档说明

通过I2C通讯协议对EEPROM进行读写操作发送串口进行通讯一.描述I2CI2C协议有启动,终止,应答,非应答四种信号,有按位发送数据,按位接收数据,有读操作和写操作。

1.启动I2C程序如下,保持SCL为高电平,SDA为高电平,当检测到SDA下降沿时,启动传送,如果2个信号没有被高则返回0。

程序启动成功返回1。

uint8 I2C_Start(void){CyDelayUs(10);SDA_Write(1);CyDelayUs(10);SCL_Write(1);CyDelayUs(10);if ( SDA_Read() == 0) return 0;if ( SCL_Read() == 0) return 0;SDA_Write(0);CyDelayUs(10);SCL_Write(0);CyDelayUs(10);return 1;}上面是模仿I2C启动时序2.终止传送程序如下SDA保持低电平SCL保持高电平而后拉高SDA,系统检测到SDA上升沿则终止传送。

void I2C_Stop(void){CyDelayUs(10);SDA_Write(0);CyDelayUs(10);SCL_Write(1);CyDelayUs(10);SDA_Write(1);CyDelayUs(10);}3.模拟应答信号,让SDA的低电平时间大于SCL的高电平时间,即可应答;也就是SDAvoid I2C_Ack(void){CyDelayUs(10);SDA_Write(0);CyDelayUs(10);SCL_Write(1);CyDelayUs(10);SCL_Write(0);CyDelayUs(10);}4.模拟非应答信号,让SDA的高电平时间大于SCL高电平时间,就是非应答void I2C_Nack(void){CyDelayUs(10);SDA_Write(1);CyDelayUs(10);SCL_Write(1);CyDelayUs(10);SCL_Write(0);CyDelayUs(10);}5.按位发送数据,按位发送数据的要求是数据位高电平的时间大于SCL,SCL高电平时不允许数据位电平变化,只有SCL低电平时才可以任意变换。

用IO模拟IIC方式读写EEPROM容易出现的问题

用IO模拟IIC方式读写EEPROM容易出现的问题 在嵌入式软件开发过程中,经常会用模拟IO的方式读写EEPROM 的操作。

有时会因程序编码的问题,出现读写数据不正确的情况。

根据笔者多年的开发经验与大家分享希望对大家有所帮助。

对EEPROM的操作常见的有两种方式:I2C,SPI;在应用中经常会用到模拟IO方式读写EEPROM。

在编写此类代码时必须要掌握I2C 与SPI协议。

I2C总线上的数据稳定规则,SCL为高电平时SDA上的数据保持稳定,SCL为低电平时允许SDA变化。

如果SCL处于高电平时,SDA上产生下降沿,则认为是起始位,SDA上的上升沿认为是停止位。

通信速率分为常规模式(时钟频率100kHz)和快速模式(时钟频率400kHz)。

同一总线上可以连接多个带有I2C接口的器件,每个器件都有一个唯一的地址,既可以是单接收的器件,也可以是能够接收发送的器件。

SPI,串行外围设备接口。

是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便。

在操作中出现读取数据不正确,或者不能读取数据可能有以下原因:1.没有遵照通信协议:这两种通信方式都有各自独立的协议,如果在编写程序时不按通信协议,自然就不能正常通信了;2.时序不对:两处通讯方式都有严格的时序,编写程序时要严格按对应的时序;3.IO口方式方向设置不正确:在通信中数据有输入与输出的时候,特别是在I2C的方式下,有数据输入时相应的IO口要设置为输入,反之亦然,初学都容易犯这样的错误;4.看页的大小,超过一个页连续写就回滚,前面的就被覆盖。

其实里面有一个页地址计数器,如果页是8个byte,那么这个计数器就3bit,增加的地址(连续写的地址范围)就相当于溢出或者相当于按页取模。

在应用中的建议:1. SCL与SDA引脚用2.2K--4.7K电阻上拉;2. IO口与EEPROM的相应引脚不能直接相连,串一个几百欧电阻;3.为保证数据的正确性,在写入数据时最好对数据进行检验;4.采用循环地址的方式进行存储,避免只在一个固定地址上读写数据;。

使用Verilog来实现EEPROM的读写,进行一个简单的I2C实战应用

这个 I2C 总线的时序是一致的。 EEPROM 应答 输出应答 sclk 的第九个周期给出,低电平应答。如果主机没有收到应答, 需要重新配置。 数据传输时序 sda 数据线在 scl 时钟的下降沿中间变化,可以避免产生误触开始结束标 志。 I2C Design i2c_start 为高电平有效,传输完成后会产生一个 i2c_done 结束标志,表示 操作完成。 I2C 状态转移图 I2C 写操作

SDA 双向 Pin A2,A1,A0 Device Addr default all 0,只操作一片可悬空引脚。 WP 接地正常读写,WP 接 Vcc 写操作被禁止 字节寻址地址ห้องสมุดไป่ตู้是由 12(AT24C32)或 13bit(AT24C64)的地址组成, 需要操作 16 位字地址高 3 或 4 位忽略即可。 Device Address 8’hA0 写器件地址,8’hA1 读器件地址 写字节操作 随机读字节操作 我这个芯片是双字节数据地址,所以在写数据地址时要写两次,先是高字 节后是低字节。 开始结束标志

(1)产生 start 位 (2)传送器件地址 ID_Address,器件地址的最后一位为数据的传输方向 位,R/W,低电平 0 表示主机往从机写数据(W),1 表示主机从从机读数据 (R)。这里按照手册给出的操作图,应该是 W 即低电平。ACK 应答,应答 是从机发送给主机的应答,这里不用管。 (3)传送写入器件寄存器地址,即数据要写入的位置。同样 ACK 应答 不用管。 (4)传送要写入的数据。ACK 应答不用管。 (5)产生 stop 信号。 I2C 读操作 (1)产生 start 信号

其他部分没啥好说的根据时序图写就行了,需要注意的一点是我们应该在 sclk 的高电平的中间采样数据,在 sclk 低电平的中间改变数据,当 sclk 为高 电平的时候,sda 为出现下降沿为 start 位, sda 出现上升沿为 stop 位,所以 在 sclk 为高电平的时候 sda 应该保持稳定不能随意乱动。这就又回到了数据 传输有效的条件,只有在 sclk 为低电平期间,才允许数据变化,在高电平期 间,不允许数据变化,否则就会出现起始位或结束位。 EEPROM 有个仿真模型,在夏雨闻老师的书里面就有,这个模型默认是 200khz 的 sclk 驱动,仿真的时候可以将时间参数改小,我这里也分享出来。 仿真模型代码点击阅读原文可以查看。 根据仿真模型仿真的话基本不会有什幺问题,需要注意的是操作的完成标 志。从仿真上看到输入读写都没问题,但是 stop 标志没产生好,仿真看到读 写操作没问题,但实际还是不行的,需要严格按照 EEPROM 的手册操作时序 进行,差一点就不行。 我最后使用拨码开关作为读写使能,数码管显示读出来的输出,最后实现 了对指定存储地址读写数据。

I2C总线与EEPROM

I2C通信时序

• I2C总线规定了严格的数据通信格式,所有具有I2C总线 接口的器件都必须遵守。

• I2C总线上主机与从机之间一次传送的数据称为一帧, 由起始信号、数据传输部分和停止信号组成。数据传送 的基本单元为一位数据。对比UART的数据帧格式。

空闲状态:I2C总线的SDA和SCL两条信号线同时处于高 电平时,规定为总线的空闲状态。此时各个器件的输出级 场效应管均处在截止状态,即释放总线,由两条信号线各 自的上拉电阻把电平拉高。 起始信号:I2C 通信的起始信号的定义是 SCL 为高电平期 间, SDA 由高电平向低电平变化产生一个下降沿。

/* I2C 总线写操作, dat-待写入字节,返回值-从机应答位的值 *

bit I2CWrite(unsigned char dat) { bit ack; //用于暂存应答位的值 unsigned char mask; //用于探测字节内某一位值的掩码变量 for (mask=0x80; mask!=0; mask>>=1) //从高位到低位依次 { if ((mask&dat) == 0) //该位的值输出到 SDA 上 I2C_SDA = 0; else I2C_SDA = 1; I2CDelay.1 SCL/P1.0

>4.7μ s >4.0μ s

SDA/P1.1 SCL/P1.0

>4.0μ s

>4.7μ s

(a)启动

SDA/P1.1 SDA/P1.1 SCL/P1.0

>4.0μ s

(b)终止

SCL/P1.0

>4.0μ s

(c)发送0/发送应答位

(d)发送1/发送非应答位

I2C简介

• I2C总线支持多主(multi-mastering)和主从(master-slave)两 种工作方式。 • 多主方式下,I2C总线上可以有多个主机。I2C总线需通 过硬件和软件仲裁来确定主机对总线的控制权。 • 主从工作方式时,系统中只有一个主机,总线上的其它 器件均为从机(具有I2C总线接口),只有主机能对从机 进行读写访问,因此,不存在总线的竞争等问题。在主 从方式下,I2C总线的时序可以模拟 ,I2C总线的使用不 受主机是否具有I2C总线接口的制约。80C51 单片机本身 不具有I2C总线接口,可以用其I/O口线模拟I2C总线 。

周立功—I2C 总线实验

I2C 总线实验(实时时钟、EEPROM 和ZLG7290 的实验)一.实验目的加深用户对I2C 总线的理解,熟悉I2C 器件的使用,提供用户实际开发的能力。

二.实验设备及器件IBM PC 机一台DP-51PROC 单片机综合仿真实验仪一台三.实验内容进行I2C 总线控制的实时时钟、EEPROM、ZLG7290 键盘LED 控制器实验。

四.实验要求熟练掌握I2C 总线的控制,灵活运用I2C 主控器软件包,深刻理解实时时钟、EEPROM、ZLG7290 键盘LED 控制的各种功能。

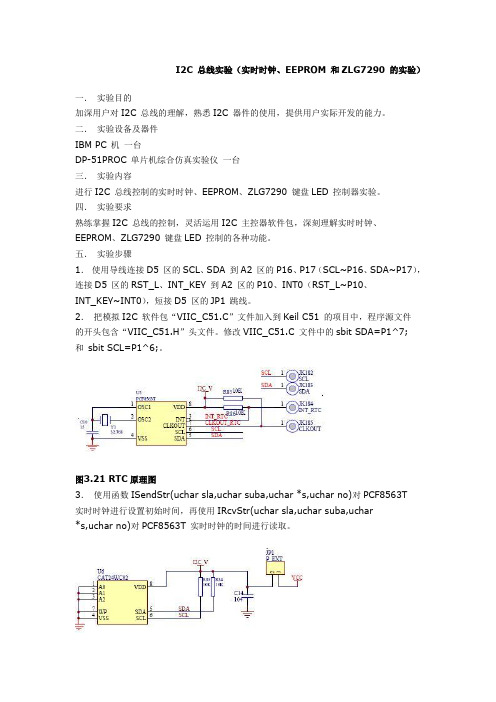

五.实验步骤1.使用导线连接D5 区的SCL、SDA 到A2 区的P16、P17(SCL~P16、SDA~P17),连接D5 区的RST_L、INT_KEY 到A2 区的P10、INT0(RST_L~P10、INT_KEY~INT0),短接D5 区的JP1 跳线。

2.把模拟I2C 软件包“VIIC_C51.C”文件加入到Keil C51 的项目中,程序源文件的开头包含“VIIC_C51.H”头文件。

修改VIIC_C51.C 文件中的sbit SDA=P1^7;和sbit SCL=P1^6;。

图3.21 RTC原理图3.使用函数ISendStr(uchar sla,uchar suba,uchar *s,uchar no)对PCF8563T实时时钟进行设置初始时间,再使用IRcvStr(uchar sla,uchar suba,uchar*s,uchar no)对PCF8563T 实时时钟的时间进行读取。

EEPROM 原理图4.使用函数ISendStr(uchar sla,uchar suba,uchar *s,uchar no);对24WC02EEPROM 进行写入,再使用IRcvStr(uchar sla,uchar suba,uchar *s,uchar no);对24WC02 EEPROM 进行读取。

ZLG7290 原理图5.对ZLG7290 键盘LED 控制器的操作也同理,只是在程序开始的地方增加复位操作和程序中间增加查询是否有键按下。

EEPROMI2C操作说明

EEPROMI2C操作说明EEPROM (Electrically Erasable Programmable Read-Only Memory)是一种非易失性存储器,可以通过电子方式擦除和编程,同时可以通过I2C总线进行操作。

本文将详细介绍EEPROM的I2C操作说明。

I2C(Inter-Integrated Circuit)是一种串行通信接口协议,可以在多个设备之间进行通信。

在EEPROM的I2C操作中,需要了解以下几个重要的概念和步骤。

1.设备地址:每个通过I2C连接的设备都有一个唯一的设备地址。

在EEPROM的I2C操作中,需要使用设备地址来与EEPROM进行通信。

2.起始条件和停止条件:I2C通信中,起始条件表示通信的开始,停止条件表示通信的结束。

起始条件由一个高电平到低电平的SCL上升沿和一个低电平的SDA下降沿组成,停止条件由一个低电平到高电平的SCL上升沿和一个高电平的SDA上升沿组成。

3. 数据传输:I2C通信中,数据可以以字节的形式进行传输。

每个字节由8个bit组成,包括7个数据位和1个校验位。

在进行EEPROM的I2C操作时,通常需要经过以下几个步骤:1.发送起始条件:将SCL和SDA引脚拉高,然后将SDA引脚拉低,形成起始条件。

2.发送设备地址和写命令:根据EEPROM的设备地址,将设备地址和写命令(0)发送到SDA引脚。

3.发送要写入的地址:将要写入数据的地址发送到SDA引脚。

4.发送数据:将要写入的数据发送到SDA引脚。

5.发送停止条件:将SCL引脚拉高,然后将SDA引脚拉高,形成停止条件。

实际的EEPROM的I2C操作可能还包括以下一些操作:1.读操作:通过发送读命令(1)和读取数据的地址,可以从EEPROM 中读取数据。

读操作与写操作类似,只是需要在发送设备地址时,将写命令(0)改为读命令(1)。

2.擦除操作:EEPROM的主要特点之一是可以擦除数据。

通过发送擦除命令和要擦除的数据的地址,可以将指定数据段擦除为初始值。

EEPROM I2C操作说明知识讲解

E E P R O M I2C操作说明I2C协议2条双向串行线,一条数据线SDA,一条时钟线SCL。

SDA传输数据是大端传输,每次传输8bit,即一字节。

支持多主控(multimastering),任何时间点只能有一个主控。

总线上每个设备都有自己的一个addr,共7个bit,广播地址全0.系统中可能有多个同种芯片,为此addr分为固定部分和可编程部份,细节视芯片而定,看datasheet。

1.1 I2C位传输数据传输:SCL为高电平时,SDA线若保持稳定,那么SDA上是在传输数据bit;若SDA发生跳变,则用来表示一个会话的开始或结束(后面讲)数据改变:SCL为低电平时,SDA线才能改变传输的bit1.2 I2C开始和结束信号开始信号:SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据。

结束信号:SCL为高电平时,SDA由低电平向高电平跳变,结束传送数据。

1.3 I2C应答信号Master每发送完8bit数据后等待Slave的ACK。

即在第9个clock,若从IC发ACK,SDA会被拉低。

若没有ACK,SDA会被置高,这会引起Master发生RESTART或STOP流程,如下所示:1.4 I2C写流程写寄存器的标准流程为:1. Master发起START2. Master发送I2C addr(7bit)和w操作0(1bit),等待ACK3. Slave发送ACK4. Master发送reg addr(8bit),等待ACK5. Slave发送ACK6. Master发送data(8bit),即要写入寄存器中的数据,等待ACK7. Slave发送ACK8. 第6步和第7步可以重复多次,即顺序写多个寄存器9. Master发起STOP写一个寄存器写多个寄存器1.5 I2C读流程读寄存器的标准流程为:1. Master发送I2C addr(7bit)和w操作1(1bit),等待ACK2. Slave发送ACK3. Master发送reg addr(8bit),等待ACK4. Slave发送ACK5. Master发起START6. Master发送I2C addr(7bit)和r操作1(1bit),等待ACK7. Slave发送ACK8. Slave发送data(8bit),即寄存器里的值9. Master发送ACK10. 第8步和第9步可以重复多次,即顺序读多个寄存器读一个寄存器读多个寄存器1.前言对于大多数工程师而言,I2C永远是一个头疼的问题。

带I2C串行2k位CMOS EEPROM的双电压监控电路-CAT1026,CAT1027

带I2C串行2k位CMOS EEPROM的双电压监控电路-CAT1026、CAT1027特性精确监控Vcc电源电压—5V,3.3V和3V系统—5个复位门槛电压供选择辅助的电压检测—外部可调节到1.25V看门狗定时器(CAT1027)高、低电平复位有效—Vcc=1V时复位仍有效400KHz的I2C总线工作电压范围:3.0V~5.5V低功耗CMOS技术16字节的页写缓冲区内置误写保护1,000,000个编程/擦除周期手动复位输入数据保存时间长达100年8脚DIP、SOIC、TSSOP、MSOP或TDFN(面积为3×3mm)封装-TDFN封装的最大高度为0.8mm工业级和扩展的温度范围概述CAT1026和CAT1027是基于微控制器系统的存储器和电源监控的完全解决方案。

它们利用低功耗CMOS技术将2K位的串行EEPOM和用于掉电保护的系统电源监控电路集成在一块芯片内。

存储器采用400KHz的I2C总线接口。

CAT1026和CAT1027包含一个精密的Vcc监控电路,有5个复位门槛电压,可支持5V、3.3V和3V 的系统。

CAT1026/27的电源监控电路和复位电路可在系统上/下电时保护存储器和系统控制器,防止掉电条件的产生。

如果电源电压超出允许范围,复位信号将有效,禁止系统微控制器、ASIC或外围器件的操作。

CAT1026有两个开漏复位输出:RESET和RESET。

当Vcc低于复位门槛电压时,RESET引脚将变为高电平,RESET将变为低电平。

在电源电压超出门槛电压后的200ms内,复位信号仍保持有效。

高电平有效和低电平有效的复位信号使CAT1026/27与微控制器和其它IC器件的连接变得很简单。

CAT1027只有一个RESET,可用作手动按键复位输入。

CAT1026和CAT1027还有一个辅助的电压监测输入V SENSE,用来监控第二个系统电源。

一旦监测到电压低于1.25V的门槛电压,辅助的高阻抗比较器将驱动开漏输出V LOW。

I2C读写EEPROM 问题总结

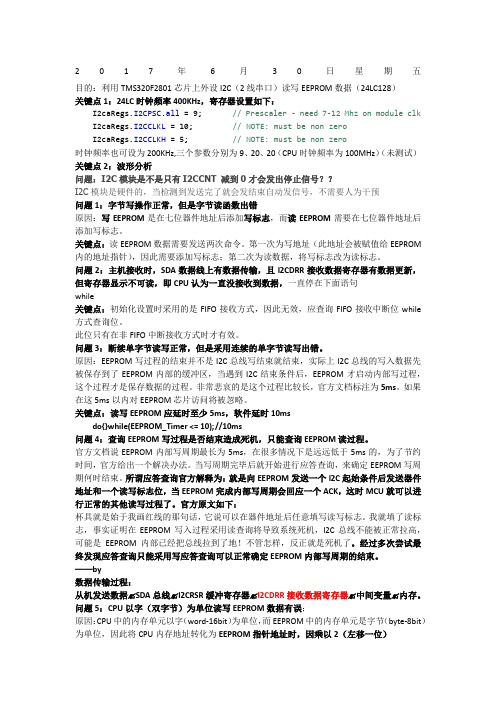

2017年6月30日星期五目的:利用TMS320F2801芯片上外设I2C(2线串口)读写EEPROM数据(24LC128)关键点1:24LC时钟频率400KHz,寄存器设置如下:I2caRegs.I2CPSC.all = 9; // Prescaler - need 7-12 Mhz on module clk I2caRegs.I2CCLKL = 10; // NOTE: must be non zeroI2caRegs.I2CCLKH = 5; // NOTE: must be non zero时钟频率也可设为200KHz,三个参数分别为9、20、20(CPU时钟频率为100MHz)(未测试)关键点2:波形分析问题:I2C模块是不是只有I2CCNT 减到0才会发出停止信号??I2C模块是硬件的,当检测到发送完了就会发结束自动发信号,不需要人为干预问题1:字节写操作正常,但是字节读函数出错原因:写EEPROM是在七位器件地址后添加写标志,而读EEPROM需要在七位器件地址后添加写标志。

关键点:读EEPROM数据需要发送两次命令。

第一次为写地址(此地址会被赋值给EEPROM 内的地址指针),因此需要添加写标志;第二次为读数据,将写标志改为读标志。

问题2:主机接收时,SDA数据线上有数据传输,且I2CDRR接收数据寄存器有数据更新,但寄存器显示不可读,即CPU认为一直没接收到数据,一直停在下面语句while关键点:初始化设置时采用的是FIFO接收方式,因此无效,应查询FIFO接收中断位while 方式查询位。

此位只有在非FIFO中断接收方式时才有效。

问题3:断续单字节读写正常,但是采用连续的单字节读写出错。

原因:EEPROM写过程的结束并不是I2C总线写结束就结束,实际上I2C总线的写入数据先被保存到了EEPROM内部的缓冲区,当遇到I2C结束条件后,EEPROM才启动内部写过程,这个过程才是保存数据的过程。

DSP28030中I2C模块学习&EEPROM 24c08读写(原创)

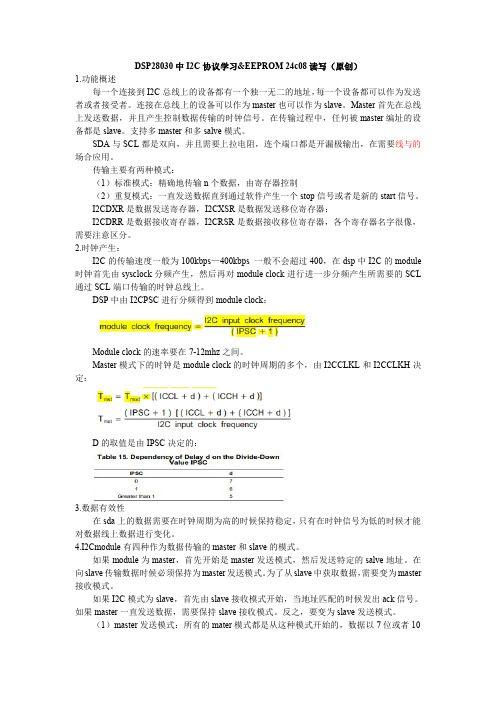

DSP28030中I2C协议学习&EEPROM24c08读写(原创)1.功能概述每一个连接到I2C总线上的设备都有一个独一无二的地址,每一个设备都可以作为发送者或者接受者。

连接在总线上的设备可以作为master也可以作为slave。

Master首先在总线上发送数据,并且产生控制数据传输的时钟信号。

在传输过程中,任何被master编址的设备都是slave。

支持多master和多salve模式。

SDA与SCL都是双向,并且需要上拉电阻,连个端口都是开漏极输出,在需要线与的场合应用。

传输主要有两种模式:(1)标准模式:精确地传输n个数据,由寄存器控制(2)重复模式:一直发送数据直到通过软件产生一个stop信号或者是新的start信号。

I2CDXR是数据发送寄存器,I2CXSR是数据发送移位寄存器;I2CDRR是数据接收寄存器,I2CRSR是数据接收移位寄存器,各个寄存器名字很像,需要注意区分。

2.时钟产生:I2C的传输速度一般为100kbps—400kbps一般不会超过400,在dsp中I2C的module 时钟首先由sysclock分频产生,然后再对module clock进行进一步分频产生所需要的SCL 通过SCL端口传输的时钟总线上。

DSP中由I2CPSC进行分频得到module clock:Module clock的速率要在7-12mhz之间。

Master模式下的时钟是module clock的时钟周期的多个,由I2CCLKL和I2CCLKH决定:D的取值是由IPSC决定的:3.数据有效性在sda上的数据需要在时钟周期为高的时候保持稳定,只有在时钟信号为低的时候才能对数据线上数据进行变化。

4.I2Cmodule有四种作为数据传输的master和slave的模式。

如果module为master,首先开始是master发送模式,然后发送特定的salve地址。

在向slave传输数据时候必须保持为master发送模式。

多思计组实验报告

多思计组实验报告一、实验目的测试多思计组开发板上的I2C总线模块的读写功能,并实现与EEPROM的通信。

二、实验器材多思计组开发板、EEPROM芯片、电脑。

三、实验原理I2C总线(Inter-Integrated Circuit)是一种全双工的串行通信总线,其工作中有两种通信设备:主设备(Master)和从设备(Slave)。

主设备负责发起总线操作,而从设备接收并响应主设备的数据传输请求,并将数据传输回主设备。

EEPROM(Electrically Erasable Programmable Read-Only Memory)是可编程的电子存储器,与只读存储器(ROM)不同,它可以反复地编程和擦除,存储的数据可以长期保存。

四、实验步骤2. 将多思计组开发板连接到电脑上,打开Arduino IDE。

3. 在Arduino IDE的顶部工具栏中选择“工具” -> “开发板” -> “多思计组开发板”。

5. 利用Arduino IDE自带的Wire库,编写读写EEPROM的代码。

6. 将代码上传到多思计组开发板上进行测试,查看EEPROM是否被正确读写。

五、实验结果首先,我们测试了I2C总线模块的读写功能。

通过编写代码,我们成功地向芯片发送了一个字节数据,并读取了一个字节数据并输出到串口监视器中,验证了I2C总线模块的读写功能。

接着,我们通过EEPROM进行了通信。

我们首先写入了一个数据到EEPROM中,并通过对EEPROM的地址进行读取,确认数据已经成功地被写入到了EEPROM中。

接着,我们又将这个数据从EEPROM中读取出来,并将其输出到串口监视器上,检测读出的数据是否与写入的数据相同。

实验结果表明,我们成功地读写了EEPROM。

六、实验分析本次实验我们成功地测试了多思计组开发板上的I2C总线模块的读写功能,并实现了与EEPROM的通信。

在编写代码过程中,我们遇到了一些问题,比如地址码的确定、芯片地址的设置、数据的读写等,但通过查阅资料、对比实验代码、询问老师同学等多种方法,我们逐渐掌握了相关操作方法,并最终成功地完成实验。

基于STM32F103的I2C总线EEPROM的读写(带超时检测)

基于STM32F103的I2C总线EEPROM的读写(带超时检测)————————————————————————————————作者:————————————————————————————————日期:【原创】基于STM32F103的I2C总线EEPROM的读写(带超时检测)本人最近参考了st 公司关于STM32的I2C的例程,觉得不是很适合我的应用,于是自己写了一个基于STM32F103的I2C总线EEPROM(24C256)的读写程序,总线的最高速度可达400K,现在将源代码原原本本的公布如下,希望得到高手的指点,也希望能够给和我有同样想法的同仁们一些参考价值。

注意:最好将固件库升级一下,st网站上面有V2。

03库的补丁。

u32 ulTimeOut_Time;/***********************************************************************************************************I2C_EE_WriteStr()** Description : 将一个数据块写入EEPROM 的指定的地址**Argument(s) : xChip - 从器件地址* xAddr — EEPROM存储空间地址*xpBuf —数据缓冲区指针* xLen - 数据长度**Return(s) : none.**Caller(s) : Application.** Note(s) :(1)*——--—-——----————--—-——---——--—--—---—-—----———--—-—-————-——-——---—-—--—————----——--—————-—-——--——-———--*Modified by :* Modified date :* Description :*—---———----———-—------——--—--—-——————-—-————-——-———-——---—--——-——————--—————----———-—---—-——-——-—-——--—**********************************************************************************************************/void I2C_EE_WriteStr(u8 xChip, u16 xAddr, u8 *xpBuf, u16 xLen){u8 *pbuf;u8 err;u8 retry;u16 addr;u16 len;个人收集整理,勿做商业用途本文为互联网收集,请勿用作商业用途//pbuf = xpBuf;addr = xAddr;len = xLen;I2C_EE_Drv_BusEn(); // 允许总线,写允许retry = 5; // 重试5次while(len){err = I2C_EE_Drv_WriteByte(xChip,addr, *pbuf);if(err){if(--retry == 0 ) // 已经试了5次,写下一个数据{retry = 5;pbuf++;addr++;len——;}}else // 顺利,写下一个数据{pbuf++;addr++;len--;}}I2C_EE_Drv_BusDis(); // 失能总线,写保护}/*********************************************************************************************************** I2C_EE_ReadStr()**Description :从EEPROM 的指定的地址读出一个数据块** Argument(s) : xChip —从器件地址* xAddr - EEPROM存储空间地址*xpBuf - 数据缓冲区指针*xLen - 数据长度**Return(s) : none.** Caller(s) : Application。

WINCE下I2C总线对EEPROM读写的实现

取模 块 上 , 实现 了对 系统 基 本设 置信 息的存储 、 取 。 同 时 , 读 还提 供 了一套 完整 、 细 的 Wid w E流驱 动 详 n o sC

设计 方案 。 以借鉴 用于其他 基 于 I 可 C总线设 备 的流驱 动 开发 。

[ 关键 词 ]2 I C总线 ;流驱动 程序 ; 拟地 址 虚 [ 中图分 类号 ] P 3 . T 337 [ 献标 识码 ] 文 B

I 2 C总线最主要的优点是其简单性和有效性 。 由 于接 口直接在组件之上 ,因此 I c总线 占用的空 间 非常小 , 减少 了电路板的空间和芯片管脚的数量 , 降 低了互联成本。总线的长度可高达 2 英尺 , 5 并且能 够以 1K p 的最大传输速率支持 4 个组件。 C总 0 bs O I 2 线的另一个优点是 , 它支持多主控 , 其中任何能够进 行发送和接收的设备都可以成为主总线 。一个主控

泛的应用。 目 前有很多半导体集成电路上都集成了 I 2 口。很多外围器件如存储器、 C接 监控芯片等也提 供F C接 口。 本文 采用 对 I 2 C接 口查 询 的方式 对 2 C系列 串 4 行EPO E R M进行读写 , 从而验证 I 2 C总线通信 的高 效与可靠性。根据 F C总线协议 ,实现 sc40和 32 1

第3 期

被 控 器 )又 是 发送 器 ( 接 收器 )这 取 决 于 它所 要 , 或 ,

完成的功能 。主模式用于初始化总线的数据传输并 产生允许传输时钟信号 S L C ;而从模式则被主器件 寻址 , 并被动的发送或接收数据 。各控制 电路虽然 挂在同一条总线上 , 却彼此独立 , 互不相关 , 方便地 构成多机系统和外 围器件扩展系统 。

总线仅仅依靠两根连线就实现了完善的全双工同步 数据传送 : 一根为串行数据线 S A, D 一根为 串行时 钟线 S L 可发送和接收数据。 C U与被控 I C。 在 P c之 间、 I C与 I C之 间进 行 双 向传 送 ,最 高传 送 速率 10b s 0 k p。各种被控制电路均并联在这条总线上 , 每

IIC接口EEPROM的控制

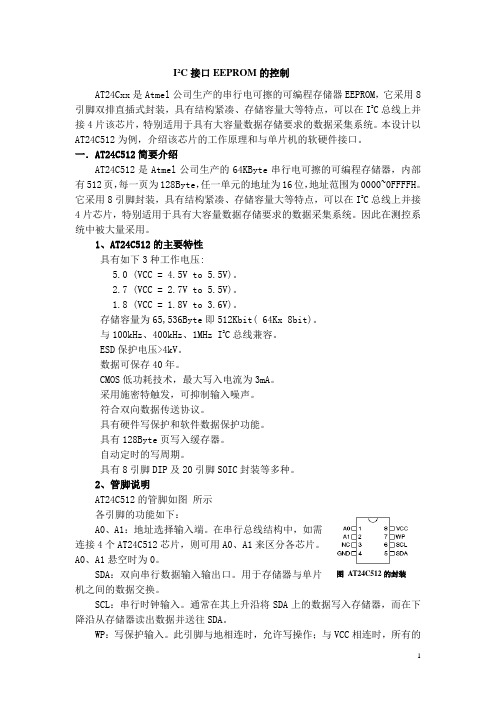

I 2C 接口EEPROM 的控制AT24Cxx 是Atmel 公司生产的串行电可擦的可编程存储器EEPROM ,它采用8引脚双排直插式封装,具有结构紧凑、存储容量大等特点,可以在I 2C 总线上并接4片该芯片,特别适用于具有大容量数据存储要求的数据采集系统。

本设计以AT24C512为例,介绍该芯片的工作原理和与单片机的软硬件接口。

一.AT24C512简要介绍AT24C512是Atmel 公司生产的64KByte 串行电可擦的可编程存储器,内部有512页,每一页为128Byte ,任一单元的地址为16位,地址范围为0000~0FFFFH 。

它采用8引脚封装,具有结构紧凑、存储容量大等特点,可以在I 2C 总线上并接4片芯片,特别适用于具有大容量数据存储要求的数据采集系统。

因此在测控系统中被大量采用。

1、AT24C512的主要特性具有如下3种工作电压:5.0 (VCC = 4.5V to 5.5V)。

2.7 (VCC = 2.7V to 5.5V)。

1.8 (VCC = 1.8V to 3.6V)。

存储容量为65,536Byte 即512Kbit( 64Kx 8bit)。

与100kHz 、400kHz 、1MHz I 2C 总线兼容。

ESD 保护电压>4kV 。

数据可保存40年。

CMOS 低功耗技术,最大写入电流为3mA 。

采用施密特触发,可抑制输入噪声。

符合双向数据传送协议。

具有硬件写保护和软件数据保护功能。

具有128Byte 页写入缓存器。

自动定时的写周期。

具有8引脚DIP 及20引脚SOIC 封装等多种。

2、管脚说明AT24C512的管脚如图 所示各引脚的功能如下:A0、A1:地址选择输入端。

在串行总线结构中,如需连接4个AT24C512芯片,则可用A0、A1来区分各芯片。

A0、A1悬空时为0。

SDA :双向串行数据输入输出口。

用于存储器与单片机之间的数据交换。

SCL :串行时钟输入。

DSP中i2c存储eeprom实例分析

1.示例程序中几种状态说明第一次看i2c_eeprom示例程序,对程序中的MsgStatus信息状态切换非常懵懂,为什么要有这几个状态?状态切换顺序如何安排?一大堆的状态,让人有些摸不着头脑。

先把程序中的头文件涉及的7种状态分析一下。

// I2C Message Commands for I2CMSG struct#define I2C_MSGSTAT_INACTIVE 0x0000 //未激活状态:一般成功发送数据或者//接受数据后可以设置信息状态为此状态,告诉用户可进行下一次的写数据或读数据。

#define I2C_MSGSTAT_SEND_WITHSTOP 0x0010 //发送带停止位数据:这是为写数据而设///的状态,写入地址和数据之后发个停止位告诉存储器数据写入完毕。

#define I2C_MSGSTAT_WRITE_BUSY 0x0011 //写数据忙状态:在将待写的数据放入//缓存后,就可以使能IIC传输数据了,然后把信息状态设为该状态,意在告诉用户:数据//已经在传送过程中。

当然是否传送完毕,还需要通过查询SCD位来判断。

#define I2C_MSGSTAT_SEND_NOSTOP 0x0020//发送无停止位数据:这个状态是为了读//取数据而设的,有查阅过AT24C1024EEPROM存储器使用手册的读者知道,在读数据之前//要发送数据的地址,发完地址不能产生停止位,这是存储器硬件设计决定的。

设为这个状//态意在告诉读者,可以发送要读取的数据的地址了。

#define I2C_MSGSTAT_SEND_NOSTOP_BUSY 0x0021//发送无停止位数据忙状态:这个状态是//为了读取数据而设的,似于I2C_MSGSTAT_WRITE_BUSY,说明地址数据已经在传送过程中。

//传送是否成功,还要看ARDY的状态。

#define I2C_MSGSTAT_RESTART 0x0022//重发开始位状态:这个状态也是为读取////数据而设。

i2c读写eeprom手册

i2c读写eeprom手册

I2C读写EEPROM的手册主要包括以下步骤:

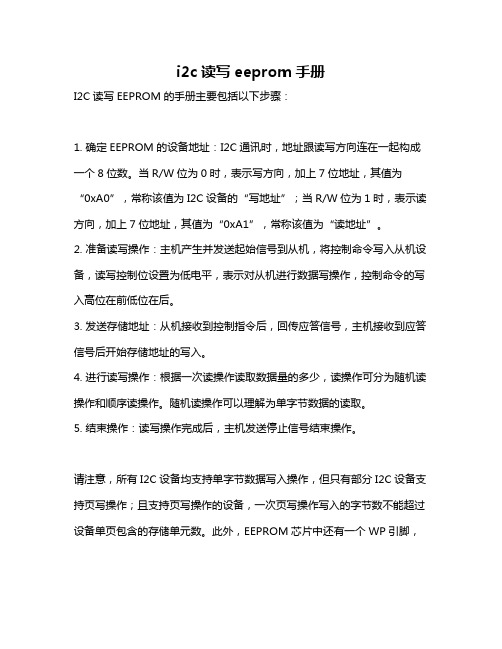

1. 确定EEPROM的设备地址:I2C通讯时,地址跟读写方向连在一起构成一个8位数。

当R/W位为0时,表示写方向,加上7位地址,其值为

“0xA0”,常称该值为I2C设备的“写地址”;当R/W位为1时,表示读方向,加上7位地址,其值为“0xA1”,常称该值为“读地址”。

2. 准备读写操作:主机产生并发送起始信号到从机,将控制命令写入从机设备,读写控制位设置为低电平,表示对从机进行数据写操作,控制命令的写入高位在前低位在后。

3. 发送存储地址:从机接收到控制指令后,回传应答信号,主机接收到应答信号后开始存储地址的写入。

4. 进行读写操作:根据一次读操作读取数据量的多少,读操作可分为随机读操作和顺序读操作。

随机读操作可以理解为单字节数据的读取。

5. 结束操作:读写操作完成后,主机发送停止信号结束操作。

请注意,所有I2C设备均支持单字节数据写入操作,但只有部分I2C设备支持页写操作;且支持页写操作的设备,一次页写操作写入的字节数不能超过设备单页包含的存储单元数。

此外,EEPROM芯片中还有一个WP引脚,

具有写保护功能,当该引脚电平为高时,禁止写入数据,当引脚为低电平时,可写入数据。

以上步骤仅供参考,如果使用实验板EEPROM的型号、设备地址或控制引

脚不一样,需根据实际工程修改。

I2C读写EEPROM问题总结

2017 年6 月3 0 日星期五目的:利用TMS320F2801芯片上外设I2C (2线串口)读写EEPROM数据(24LC128)关键点1 : 24LC时钟频率400KHZ,寄存器设置如下://Prescaler- need7-12Mhzo nm oduleclk=10; 〃NOTE:mustbe non zero=5; 〃NOTE:mustbe non zero时钟频率也可设为200KHz,三个参数分别为9、20、20(CPU时钟频率为100MHz)(未测试)关键点2 :波形分析问题:I2C模块是不是只有I2CCNT减到0才会发出停止信号I2C模块是硬件的,当检测到发送完了就会发结束自动发信号,不需要人为干预问题1:字节写操作正常,但是字节读函数出错原因:写EEPROM是在七位器件地址后添加写标志,而读EEPROM需要在七位器件地址后添加写标志。

关键点:读EEPROM数据需要发送两次命令。

第一次为写地址(此地址会被赋值给EEPROM 内的地址指针),因此需要添加写标志;第二次为读数据,将写标志改为读标志。

问题2:主机接收时,SDA数据线上有数据传输,且I2CDRR接收数据寄存器有数据更新,但寄存器显示不可读,即CPU认为一直没接收到数据,一直停在下面语句while!=1);关键点:初始化设置时采用的是FIF O接收方式,因此无效,应查询FIF O接收中断位while!=1);//FIFORX 方式查询位。

此位只有在非FIFO中断接收方式时才有效。

问题3:断续单字节读写正常,但是采用连续的单字节读写出错。

原因:EEPRO M写过程的结束并不是I2C总线写结束就结束,实际上I2C总线的写入数据先被保存到了EEPRO M内部的缓冲区,当遇到I2C结束条件后,EEPROM才启动内部写过程,这个过程才是保存数据的过程。

非常悲哀的是这个过程比较长,官方文档标注为5ms。

如果在这5ms以内对EEPROM芯片访问将被忽略。

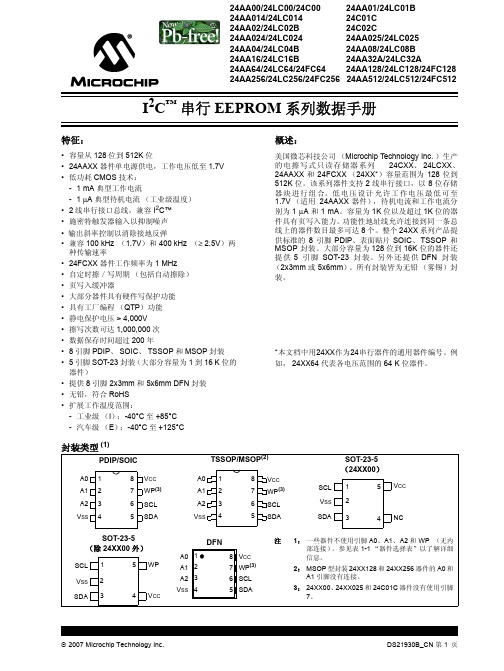

I2C串行EEPROM系列数据手册

器件选择表 (续)

VCC 范围 最大时钟 页大小 写保护方案 频率 功能性 温度范围 地址引脚 封装 (5)

1.7-5.5V(3) 1 MHz

1: VCC <4.5V,频率为 100 kHz。 2: VCC <2.5V,频率为 100 kHz。 3: VCC <2.5V,频率为 400 kHz。 4: MSOP 型封装 24XX128 和 24XX256 器件的引脚 A0 和 A1 没有连接。 5: P = 8-PDIP,SN = 8-SOIC (3.90 mm JEDEC) , ST = 8-TSSOP,OT = 5 或 6-SOT23,MC = 2x3mm DFN, MS = 8-MSOP, SM = 8-SOIC (200 mil EIAJ) , MF = 5x6mm DFN。

2007 Microchip Technology Inc.

DS21930B_CN 第 1 页

24AAXX/24LCXX/24FCXX

表 1-1:

器件型号 128 位器件 24AA00 24LC00 24C00 1K 位器件 24AA01 24LC01B 24AA014 24LC014 24C01C 2K 位器件 24AA02 24LC02B 24AA024 24LC024 24AA025 24LC025 24C02C 4K 位器件 24AA04 24LC04B 8K 位器件 24AA08 24LC08B 16K 位器件 24AA16 24LC16B 32K 位器件 24AA32A 24LC32A 64K 位器件 24AA64 24LC64 24FC64 注 1.7-5.5V 2.5-5.5V 1.7-5.5V 400 kHz (2) 400 kHz 1 MHz(3) 32 字节 整个阵列 A0, A1, A2 I I, E I P, SN, SM, ST, MS,MC 1.7-5.5V 2.5-5.5V 400 kHz (2) 400 kHz 32 字节 整个阵列 A0, A1, A2 I I, E P, SN, SM, ST, MS,MC 1.7-5.5V 2.5-5.5V 400 kHz (2) 400 kHz 16 字节 整个阵列 无 I I, E P, SN, ST, MS, OT, MC 1.7-5.5V 2.5-5.5V 400 kHz (2) 400 kHz 16 字节 整个阵列 无 I I, E P, SN, ST, MS, OT, MC 1.7-5.5V 2.5-5.5V 400 kHz (2) 400 kHz 16 字节 整个阵列 无 I I, E P, SN, ST, MS, OT, MC 1.7-5.5V 2.5-5.5V 1.7-5.5V 2.5-5.5V 1.7-5.5V 2.5-5.5V 4.5-5.5V 400 kHz (2) 400 kHz 400 kHz(2) 400 kHz 400 kHz(2) 400 kHz 400 kHz 8 字节 16 字节 16 字节 16 字节 整个阵列 整个阵列 无 无 A0, A1, A2 A0, A1, A2 I I, E I I I I I, E P, SN, ST, MC P, SN, ST,MS, MC P, SN, ST, MS, MC P, SN, ST, MS, OT, MC 1.7-5.5V 2.5-5.5V 1.7-5.5V 2.5-5.5V 400 kHz (2) 400 kHz 400 kHz(2) 400 kHz 8 字节 16 字节 16 字节 整个阵列 整个阵列 无 无 A0, A1, A2 A0, A1, A2 I I, E I I I, E P, SN, ST, MC P, SN, ST, MS, MC P, SN, ST, MS, OT, MC 1.7-5.5V 2.5-5.5V 4.5-5.5V 400 kH(1) 400 kHz(1) 400 kHz — 无 无 I I I, E P, SN, ST, OT, MC

I2C总线信号完整性测试

I2C总线信号完整性测试目录CONTENTS•信号完整性测试条件•I2C信号完整性测试一、信号完整性测试条件12<1>.熟悉逻辑电平及I2C总线协议的基本知识,熟练掌握示波器的使用方法;<2>.测试人员在测试操作仪器时必须穿戴防静电服、静电鞋和防静电帽;<3>.在用手持握被测电路板时必须戴防静电手套;<4>.测试人员在使用时必须要按照示波器的具体要求来操作。

31、测试点尽量不要引飞线,非引不可也要尽量短2、尽量减少探头探针与探头地线所构成的环路面积3、手不要触摸测试信号4、2个探头不能共用同一地线5、测量时,使输入信号达到最大示波器的满刻度6、测量时,示波器探头和电缆要远离潜在串扰源的地方7、测试过程中,禁止在测试环境附近打电话或使用其他有强辐射的设备,避免对测试结果产生干扰8、测量时,如果测量结果超出规格,须再次确认测试点与芯片规格,确认测量条件及测量方法无误后,更换新的PCBA板测量,若测量结果仍是Fail,则定性为Bug并与硬件/软件人员确认。

并提单至禅道Bug管理系统或Jira系统4示波器及探头<a>.为了确保测量数据的精度,应尽量采用高输入阻抗、小电容值、高带宽的有源探头和高带宽的示波器<b>.仪器预热:为了避免温度变化带来的误差,在测试进行前,仪器需要预热30分钟。

<c>.测量前,要校准仪器<d>.测量前,保证测试仪器与被测试单板/系统共地<e>.探头和示波器的带宽要超过被测信号带宽的3倍以上<f>.示波器的采样速率至少要超过被测信号最高频率成分的2倍<g>.建议使用示波器厂家推荐的示波器和探头组合进行测量<h>.不允许在探头还连接着被测试电路时插拔探头5根据电路原理图,遍历所有I2C总线信号,详细测试项如下表(1),表(2)所示:(标准速度)表(1)I2C总线SCL信号测试项及标准表(2)I2C总线SDA信号测试项及标准6测试点一般选择信号宿端,尽量在芯片的输入管脚上测量,或者尽量靠近输入管脚对于I2C写操作过程,测试点选择在信号宿端(从设备端)对于I2C读操作过程,测试点选择在驱动端(主设备端)71、满足单板/系统工作在特定的功能状态、业务状态下所测到的信号才是有效信号(I2C总线有通信)2、要求有效信号能够重复出现要求3、能够满足较长时间观察的要求81、《示波器使用操作手册》2、《UM10204-I2C总线协议》3、线路原理图、位置图及各芯片规格书二、I2C总线信号完整性测试1测试目的:验证I2C总线的信号质量是否符合芯片要求,测试指标项应根据具体芯片要求制定,具体指标有SCL和SDA的低电平电压,高电平电压,上升沿时间,下降沿时间,上过冲和下过冲。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

I2C总线应用下的EEPROM测试

作者:盛帅能

作者单位:华越微电子有限公司,浙江,绍兴,312000

刊名:

半导体技术

英文刊名:SEMICONDUCTOR TECHNOLOGY

年,卷(期):2004,29(4)

被引用次数:2次

1.李文雄.陆俭国.刘明生.商书元.LI Wen-xiong.LU Jian-guo.LIU Ming-sheng.SHANG Shu-yuan基于I2C总线的EEPROM在智能电器中的应用[期刊论文]-低压电器2005(11)

2.庞媛媛.崔建明.PANG Yuan yuan.CUI Jian-ming一种I2C总线接口设计在EEPROM的应用[期刊论文]-电脑知识与技术2011,07(30)

3.苏琦.刘宇.田敬民EEPROM基于I2C总线的一种读写方法[期刊论文]-山西电子技术2001(1)

4.郭文华.GUO Wen-hua基于I2C总线的串行E2PROM及其应用[期刊论文]-常熟理工学院学报2008,22(10)

5.麦胤.柳沁.Mai Yin.Liu Qin基于Nios Ⅱ的EEPROM Controller Core的设计[期刊论文]-自动化仪表

2008,29(1)

6.杨正进.王玉霞基于I2C总线的EEPROM与单片机接口技术[期刊论文]-重庆工学院学报2001,15(2)

7.刘冰.杜道山.周士侃.李从心基于I2C总线协议的EEPROM与DSP的接口技术[期刊论文]-电子工程师2004,30(9)

8.李和太.蒋晶鑫.陆虹.LI He-tai.JANG Jing-xin.LU Hong嵌入式串行EEPROM研究[期刊论文]-微处理机2007,28(1)

9.徐飞.贺祥庆.张莉.XU Fei.HE Xiang-qing.ZHANG Li一种40ns 16kb EEPROM的设计与实现[期刊论文]-微电子学2005,35(2)

10.意法半导体推出超小型封装的增强型512 kbit I2C和SPI低压串行EEPROM存储器[期刊论文]-电子与电脑

2005(5)

1.沈华.王俞心基于FPGA的I2C总线主控器的设计与实现[期刊论文]-航空计算技术 2007(6)

2.张必超存储器测试技术及其在质量检验中的应用研究[学位论文]硕士 2005

本文链接:/Periodical_bdtjs200404018.aspx。