ADS8326电路图

高速电路设计实验之ADS--实验八 眼图观察

實驗八眼圖觀察ㄧ、原理說明高速電路產品的發展現況及其傳輸速度,很清楚顯示已經進入gigabit時代了,訊號傳輸的穩定性變得很重要,如何觀察其穩定性呢?目前廣泛使用的技術為眼圖或抖動(jitter)的量測,利用眼圖來觀測訊號的品質。

影響訊號傳輸品質的因素很多,其中傳輸線的損耗影響很大,特別是gigabit訊號的傳輸,以下就模擬設計一個有損耗之傳輸線,經由傳送不同之距離觀測其眼圖特性即可清楚知道其訊號傳輸品質的好壞。

如下左(50cm)右(5cm)兩圖,可清楚知道右圖之訊號傳輸品質比左圖好,其眼睛張的比較大,訊號上升或下降時間比較正常。

二、下面在ADS中建立一個新的模擬Project “eye_diagram”從Window XP 工具列中 開始 程式集 Advanced Design System 2005A 點選Advanced Design System 選項,開啟ADS主視窗。

ADS主視窗在ADS主視窗中點選進入資料夾C:/users/default/ ,如下圖所示在default資料夾上點選兩下,立即進入default資料夾內,如下圖所示在功能表上選擇【File】 【New Project】開啟建立【New project】的視窗,如下圖所示在【Name】c:\users\default\下鍵入eye_diagram,如下圖所示按ok鍵,進入【eye_diagram】資料夾中;一併開啟Schematic 視窗,如下圖所示在schematic視窗中點選功能表中【File】>【Save Design】存】鍵結束此視窗,並返回Schematic視窗中請在Schematic視窗中TLines-Multilayer元件庫中選取【MLSUBSTRATE2】元件,並放入視窗中以滑鼠左鍵連續點擊【MLSUBSTRATE2】元件兩下,進入元件的屬性視窗,並一一輸入其參數值Er=4.45,H=0.7mm,TanD=0.02,T[1]=0.05mm,T[2]=0.05mm,如下圖所示,輸入完後點選OK鍵結束視窗在TLines-Multilayer元件庫中選取【ML2CTL_C】元件,並放入視窗中CLIN1及CLIN2選取功能表中Tools>LineCalc>StartLineCalc開啟LineCalc 視窗。

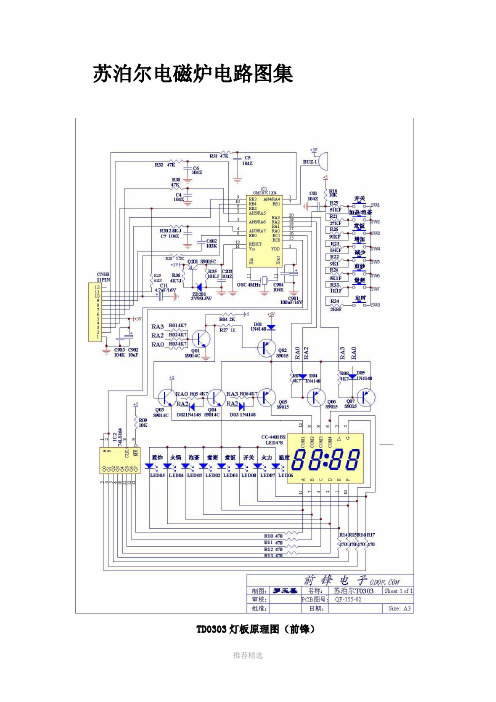

苏泊尔电磁炉电路图大全Word版

苏泊尔电磁炉电路图集TD0303灯板原理图(前锋)TD0303主板电路原理图(前锋)QF-139-08(主)TD0305灯板电路原理图(前锋)TD0305主板电路原理图(前锋)QF-096-05(主) QF-100-08T0306灯板电路原理图(前锋)T0307主板、灯板电路原理图(前锋)QF-101-02(主) QF-078-02推荐精选TD0309主板、灯板电路原理图(前锋) QF-134-06(主) QF-136-03TD0310主板、灯板电路原理图(前锋)前锋-134-06(主)前锋-136-03TD0322灯板电路原理图(前锋) QF-836TD0322主板电路原理图(前锋)QF-7TD0411灯板电路原理图(前锋) QF-SL395TD0411主板电路原理图(前锋) QF-876-01CTD0412灯板电路原理图(一)(前锋)TD0412主板电路原理图(一) (前锋)TD0413灯板电路原理图(前锋)TD0413主板电路原理图(前锋)TD0418灯板电路原理图(前锋)TD0418主板电路原理图(前锋)TD0418灯板电路原理图(瑞德)TD0418主板电路原理图(瑞德)2005年电路图集TD0501CT、TD0501T灯板(一)电路原理图(前锋)TD0501CT、TD0501T灯板(二)电路原理图(前锋)TD0501CT、TD0501T主板(二)电路原理图(前锋QF-1058-02)TD0501T、TD0501CT灯板电路原理图(瑞德)TD0501T、TD0501CT主板电路原理图(瑞德)TD0501T、TD0501CT灯板电路原理图(拓邦)TD0501T、TD0501CT主板电路原理图(拓邦)TD0503T主板电路原理图(前锋)TD0504灯板电路原理图(前锋)。

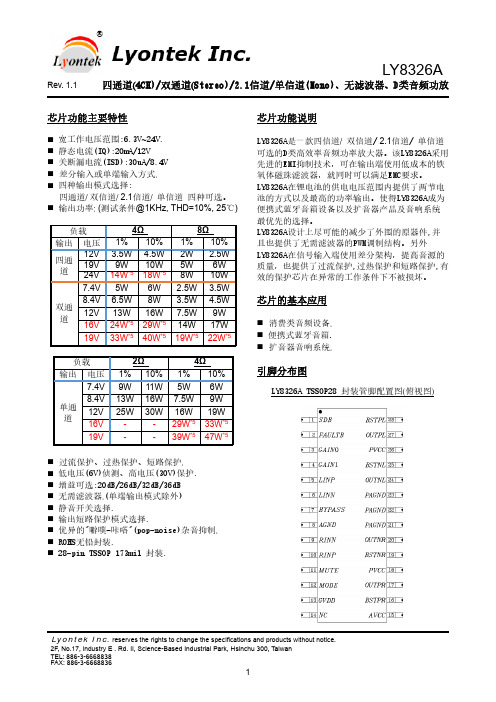

LY8326A

1

Rev. 1.1

LY8326A

四通道(4CH)/双通道(Stereo)/2.1信道/单信道(Mono)、无滤波器、D类音频功放

13W 16W

25W 30W

-

-

-

-

4Ω 1% 10% 5W 6W 7.5W 9W 16W 19W 29W*5 33W*5 39W*5 47W*5

过流保护、过热保护、短路保护. 低电压(6V)侦测、高电压(30V)保护. 增益可选:20dB/26dB/32dB/36dB 无需滤波器.(单端输出模式除外) 静音开关选择. 输出短路保护模式选择. 优异的"噼噗-咔嗒"(pop-noise)杂音抑制. ROHS无铅封装. 28-pin TSSOP 173mil 封装.

13W 16W 24W*5 29W*5

33W*5 40W*5

8Ω 1% 10% 2W 2.5W 5W 6W 8W 10W 2.5W 3.5W

3.5W 4.5W 7.5W 9W 14W 17W

19W*5 22W*5

负载

输出 电压

7.4V

单通 道

8.4V 12V 16V

19V

2Ω

1% 10%

9W 11W

Lyontek Inc. reserves the rights to change the specifications and products without notice.

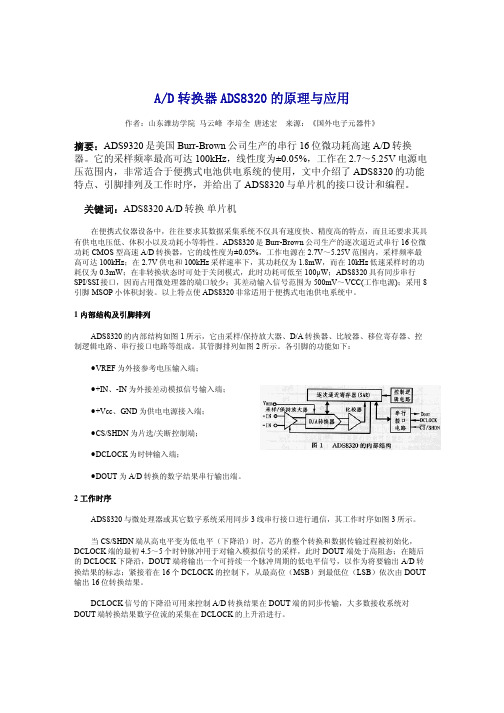

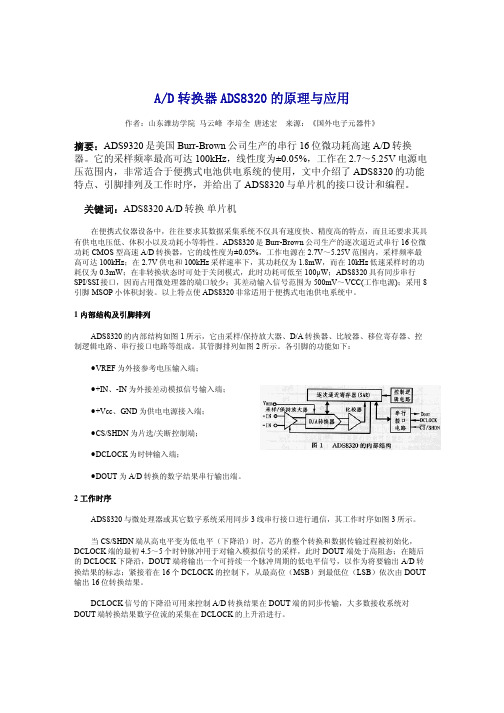

AD转换器ADS8320的原理与应用

A/D转换器ADS8320的原理与应用作者:山东潍坊学院马云峰李培全唐述宏来源:《国外电子元器件》摘要:ADS9320是美国Burr-Brown公司生产的串行16位微功耗高速A/D转换器。

它的采样频率最高可达100kHz,线性度为±0.05%,工作在2.7~5.25V电源电压范围内,非常适合于便携式电池供电系统的使用,文中介绍了ADS8320的功能特点、引脚排列及工作时序,并给出了ADS8320与单片机的接口设计和编程。

关键词:ADS8320 A/D转换单片机在便携式仪器设备中,往往要求其数据采集系统不仅具有速度快、精度高的特点,而且还要求其具有供电电压低、体积小以及功耗小等特性。

ADS8320是Burr-Brown公司生产的逐次逼近式串行16位微功耗CMOS型高速A/D转换器,它的线性度为±0.05%,工作电源在2.7V~5.25V范围内,采样频率最高可达100kHz;在2.7V供电和100kHz采样速率下,其功耗仅为1.8mW,而在10kHz低速采样时的功耗仅为0.3mW;在非转换状态时可处于关闭模式,此时功耗可低至100µW;ADS8320具有同步串行SPI/SSI接口,因而占用微处理器的端口较少;其差动输入信号范围为500mV~VCC(工作电源);采用8引脚MSOP小体积封装。

以上特点使ADS8320非常适用于便携式电池供电系统中。

1 内部结构及引脚排列ADS8320的内部结构如图1所示,它由采样/保持放大器、D/A转换器、比较器、移位寄存器、控制逻辑电路、串行接口电路等组成。

其管脚排列如图2所示。

各引脚的功能如下:●VREF为外接参考电压输入端;●+IN、-IN为外接差动模拟信号输入端;●+Vcc、GND为供电电源接入端;●CS/SHDN为片选/关断控制端;●DCLOCK为时钟输入端;●DOUT为A/D转换的数字结果串行输出端。

2 工作时序ADS8320与微处理器或其它数字系统采用同步3线串行接口进行通信,其工作时序如图3所示。

利用IBIS模型完善信号完整性计算和PCB设计

利用IBIS模型完善信号完整性计算和PCB设计利用IBIS模型完善信号完整性计算和PCB设计本文是关于在印刷电路板(PCB)开发阶段使用数字输入/输出缓冲信息规范(IBIS)模拟模型的文章。

本文将介绍如何使用一个IBIS 模型来提取一些重要的变量,用于信号完整性计算和确定 PCB 设计解决方案。

请注意,该提取值是 IBIS 模型不可或缺的组成部分。

图1 错配端接阻抗 PCB 装置。

信号完整性问题当观察传输线两端的数字信号时,设计人员会吃惊于将信号驱动至某条 PCB 线迹时出现的结果。

通过相对较长的距离,相比瞬时变化信号,电信号更像行波。

描述电路板上电波行为的较好模拟是池中波(wave in a pool)。

纹波穿过池顺利传播,因为体积相同的两组水具有相同的“阻抗”。

然而,池壁的阻抗差异明显,并以相反方向反射波。

注入PCB 线迹的电信号也出现相同的现象,其在阻抗错配时以类似方式反射。

图 1 显示了错配端接阻抗的一个 PCB 装置。

微控制器即TI MSP430 向 TI ADS8326 ADC 发送一个时钟信号,其将转换数据发送回 MSP430。

图 2 显示了该装置中阻抗错配所形成的反射。

这些反射在传输线迹上引起信号完整性问题。

让一端或者两端的 PCB 线迹电阻抗相匹配可极大地减少反射。

图2:图1中错配端接阻抗促发反射。

要解决系统电阻抗匹配问题,设计人员需要理解集成电路(IC)的阻抗特性,以及起到传输线迹作用的PCB 线迹的阻抗特性。

知道这些特性,让设计人员能够将各连接单元建模为分布式传输线迹。

传输线迹为各种电路服务,从单端和差分端器件到开漏输出器件。

本文主要介绍单端传输线迹,其驱动器有一个推拉输出电路设计。

图3 显示了用于设计该举例传输线迹的各组成部分。

图3 实例单端传输线电路。

另外,还需要如下 IC 引脚规范:发送器输出电阻 Z T (Ω)发送器上升时间t Rise和下降时间t Fall (秒)接收机输入电阻Z R (Ω)接收机引脚电容值C R_Pin (F)这些规范一般没有在 IC 制造厂商的产品说明书中。

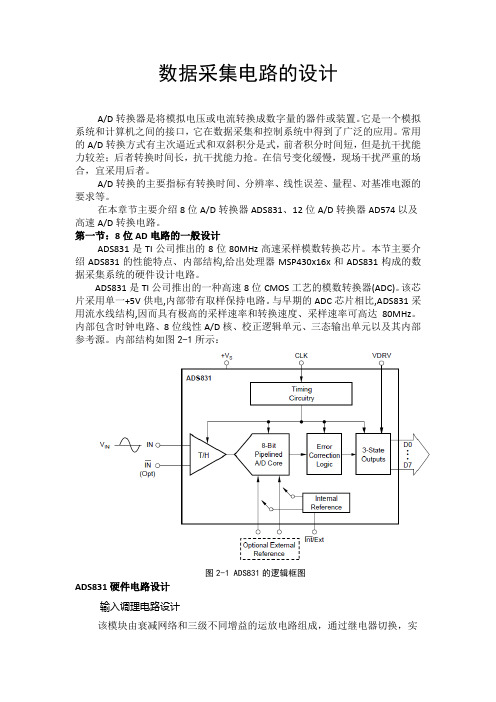

数据采集电路的设计

数据采集电路的设计A/D转换器是将模拟电压或电流转换成数字量的器件或装置。

它是一个模拟系统和计算机之间的接口,它在数据采集和控制系统中得到了广泛的应用。

常用的A/D转换方式有主次逼近式和双斜积分是式,前者积分时间短,但是抗干扰能力较差;后者转换时间长,抗干扰能力抢。

在信号变化缓慢,现场干扰严重的场合,宜采用后者。

A/D转换的主要指标有转换时间、分辨率、线性误差、量程、对基准电源的要求等。

在本章节主要介绍8位A/D转换器ADS831、12位A/D转换器AD574以及高速A/D转换电路。

第一节:8位AD电路的一般设计ADS831是TI公司推出的8位80MHz高速采样模数转换芯片。

本节主要介绍ADS831的性能特点、内部结构,给出处理器MSP430x16x和ADS831构成的数据采集系统的硬件设计电路。

ADS831是TI公司推出的一种高速8位CMOS工艺的模数转换器(ADC)。

该芯片采用单一+5V供电,内部带有取样保持电路。

与早期的ADC芯片相比,ADS831采用流水线结构,因而具有极高的采样速率和转换速度、采样速率可高达80MHz。

内部包含时钟电路、8位线性A/D核、校正逻辑单元、三态输出单元以及其内部参考源。

内部结构如图2-1所示:图2-1 ADS831的逻辑框图ADS831硬件电路设计输入调理电路设计该模块由衰减网络和三级不同增益的运放电路组成,通过继电器切换,实现衰减、直通和小信号放大的功能。

三级电路均采用OPA690精密仪表放大器构成,该运放具有输入阻抗高、低噪声、速度快等优点,增益带宽积达500MHz。

第一级运放构成射级跟随器,输入阻抗3.5MΩ,第二级运放放大系数约为5倍,第三级运放当放大系数约为10倍,级联实现约50倍放大增益,最终将输出电压峰-峰值保持在1.6V左右。

单元电路如图2-2所示。

图2-2输入调理电路设计采样保持电路设计将A/D转换器设计成单极性输入,采用ADS831内部基准源REFT(+3V)和运放OPA2652构成2.5V恒压源,从而使采样电压有效值保持在+2.5 V。

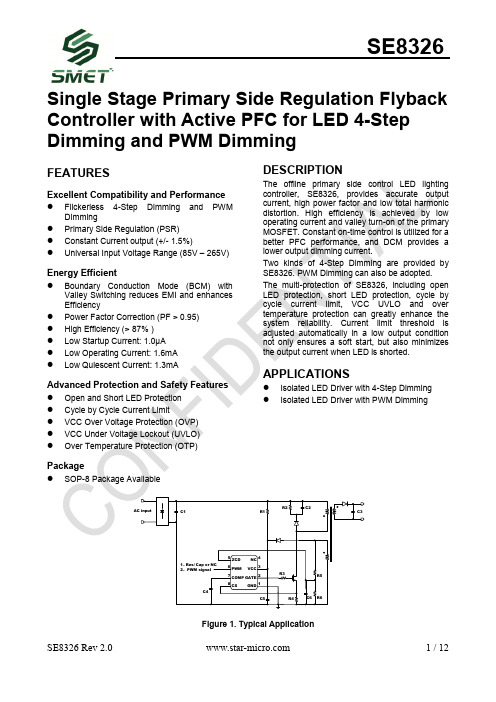

SE8326 PWM 四段调光Datasheet_Rev 2.0

SOP-8 Package Available

DESCRIPTION

The offline primary side control LED lighting controller, SE8326, provides accurate output current, high power factor and low total harmonic distortion. High efficiency is achieved by low operating current and valley turn-on of the primary MOSFET. Constant on-time control is utilized for a better PFC performance, and DCM provides a lower output dimming current.

APPLICATIONS

Isolated LED Driver with 4-Step Dimming

Isolated LED Driver with PWM Dimming

AC input

C1

R2

C2

R1

C3

SE8326 Rev 2.0

1 . Res/ Cap or NC 2 . PWM signal

GATE DRIVER SECTION (TA = -40°C to 125°C)

VCLAMP Output Clamp Voltage IG-SOURCE Max Source Current

IG-SINK Max Sink Current

ZERO CURRENT DETECTOR SECTION

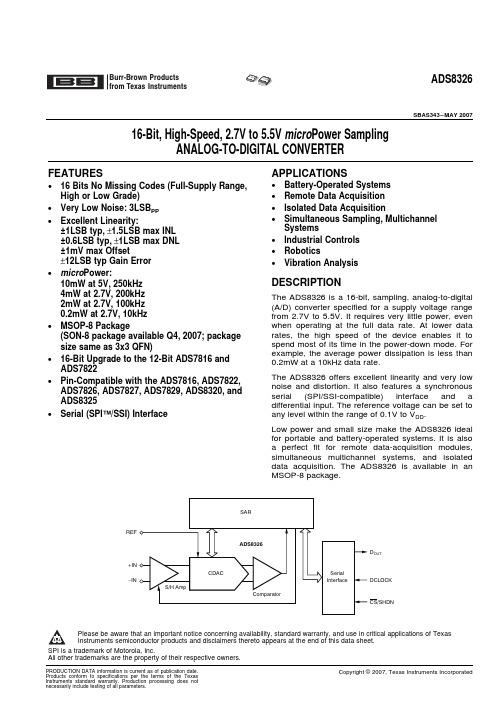

ads8326(16位SPIAD)

DESCRIPTION

The ADS8326 is a 16-bit, sampling, analog-to-digital (A/D) converter specified for a supply voltage range from 2.7V to 5.5V. It requires very little power, even when operating at the full data rate. At lower data rates, the high speed of the device enables it to spend most of its time in the power-down mode. For example, the average power dissipation is less than 0.2mW at a 10kHz data rate. The ADS8326 offers excellent linearity and very low noise and distortion. It also features a synchronous serial (SPI/SSI-compatible) interface and a differential input. The reference voltage can be set to any level within the range of 0.1V to VDD. Low power and small size make the ADS8326 ideal for portable and battery-operated systems. It is also a perfect fit for remote data-acquisition modules, simultaneous multichannel systems, and isolated data acquisition. The ADS8326 is available in an MSOP-8 package.

六通道同步采样AD芯片ADS8364在数据采集中的应用

该系统选择的复杂可编程逻辑器件 CPLD 是 Altera 公司的 EPM7128S,采用 CMOS 工艺,是一种基于 EPROM 的器件。该芯片有 84 个引脚,其中 5 个用于 ISP(in system programmable)下载,可以方便地对其进行 在系统编程。器件内集成了 6 000 个门,其中典型可用 门为 2 500 个,有 128 个逻辑单元,60 个可用 I/O 口, 可以单独配置为输入、输出及双向工作方式,2 个全局

图 3 数据采集流程图 Fig. 3 Data acquisition flow chart 注:整个流程完成时间应在一个采样周期 5 ms 内。

万方数据

44

中国科技论文在线 Sciencepaper Online

#define AD_DATA_BASE

0x90140000

#define ORDER

表 1 ADS8364 通道选择模式

Table 1 Channel selection mode of ADS8364

A2

A1 A0 通道模式

0

0

0

CHA0

0

0

1

CHA1

0

1

0

CHB0

图 1 系统硬件实体简图

Fig. 1 Diagram of system hardware

敏感轴正交放置的 3 个陀螺仪与 3 个加速度计的信 号通过由 CPLD 控制的 16 位 6 通道同步采样 A/D 芯片 ADS8364 来采集并完成模数转换,转换结果送入高速 浮点 DSP TMS320C6713 中进行处理和导航解算。因此, 导航计算机(DSP TMS320C6713)的高性能决定了该系 统的实时性,而采集惯性器件测量数据的 A/D 芯片则直 接决定了该系统的精度。

ADS8326中文资料

• • • 16 Bits No Missing Codes (Full-Supply Range, High or Low Grade) Very Low Noise: 3LSBPP Excellent Linearity: ±1LSB typ, ±1.5LSB max INL ±0.6LSB typ, ±1LSB max DNL ±1mV max Offset ±12LSB typ Gain Error microPower: 10mW at 5V, 250kHz 4mW at 2.7V, 200kHz 2mW at 2.7V, 100kHz 0.2mW at 2.7V, 10kHz MSOP-8 Package (SON-8 package available Q4, 2007; package size same as 3x3 QFN) 16-Bit Upgrade to the 12-Bit ADS7816 and ADS7822 Pin-Compatible with the ADS7816, ADS7822, ADS7826, ADS7827, ADS7829, ADS8320, and ADS8325 Serial (SPI™/SSI) Interface

元器件交易网

BurrĆBrown Products from Texas Instruments

ADS8326

SBAS343 – MAY 2007

16-Bit, High-Speed, 2.7V to 5.5V microPower Sampling ANALOG-TO-DIGITAL CONVERTER

ORDERING INFORMATION (1)

MAXIMUM INTEGRAL LINEARITY ERROR (LSB) (2) NO MISSING CODES ERROR (LSB) SPECIFIED TEMPERATURE RANGE TRANSPORT MEDIA, QUANTITY Tape and Reel, 250 Tape and Reel, 2500 Tape and Reel, 250 Tape and Reel, 2500 Tape and Reel, 250 Tape and Reel, 2500 Tape and Reel, 250 Tape and Reel, 2500

AD转换器ADS8320的原理与应用

A/D转换器ADS8320的原理与应用作者:山东潍坊学院马云峰李培全唐述宏来源:《国外电子元器件》摘要:ADS9320是美国Burr-Brown公司生产的串行16位微功耗高速A/D转换器。

它的采样频率最高可达100kHz,线性度为±0.05%,工作在2.7~5.25V电源电压范围内,非常适合于便携式电池供电系统的使用,文中介绍了ADS8320的功能特点、引脚排列及工作时序,并给出了ADS8320与单片机的接口设计和编程。

关键词:ADS8320 A/D转换单片机在便携式仪器设备中,往往要求其数据采集系统不仅具有速度快、精度高的特点,而且还要求其具有供电电压低、体积小以及功耗小等特性。

ADS8320是Burr-Brown公司生产的逐次逼近式串行16位微功耗CMOS型高速A/D转换器,它的线性度为±0.05%,工作电源在2.7V~5.25V范围内,采样频率最高可达100kHz;在2.7V供电和100kHz采样速率下,其功耗仅为1.8mW,而在10kHz低速采样时的功耗仅为0.3mW;在非转换状态时可处于关闭模式,此时功耗可低至100µW;ADS8320具有同步串行SPI/SSI接口,因而占用微处理器的端口较少;其差动输入信号范围为500mV~VCC(工作电源);采用8引脚MSOP小体积封装。

以上特点使ADS8320非常适用于便携式电池供电系统中。

1 内部结构及引脚排列ADS8320的内部结构如图1所示,它由采样/保持放大器、D/A转换器、比较器、移位寄存器、控制逻辑电路、串行接口电路等组成。

其管脚排列如图2所示。

各引脚的功能如下:●VREF为外接参考电压输入端;●+IN、-IN为外接差动模拟信号输入端;●+Vcc、GND为供电电源接入端;●CS/SHDN为片选/关断控制端;●DCLOCK为时钟输入端;●DOUT为A/D转换的数字结果串行输出端。

2 工作时序ADS8320与微处理器或其它数字系统采用同步3线串行接口进行通信,其工作时序如图3所示。

射频接收系统的设计_物联网:ADS射频电路仿真与实例详解_[共6页]

![射频接收系统的设计_物联网:ADS射频电路仿真与实例详解_[共6页]](https://img.taocdn.com/s3/m/b8010e0c6f1aff00bed51eef.png)

║526 物联网:ADS射频电路仿真与实例详解521.1.2 射频接收系统射频接收系统由天线、带通滤波器、低噪声放大器、混频器、本振信号源、中频滤波器和中频放大器构成,常用的射频接收机有两种类型,一种为超外差式接收机,另一种为零中频接收机,这两种接收机特性如下。

1.超外差式接收机若天线接收的射频信号频率与本振信号源产生的本振信号频率不同,接收机称为超外差式接收机,常用的超外差式接收机中频在几十至几百MHz之间。

超外差式接收机与零中频接收机相比,优点在于噪声比较低。

超外差式接收机与零中频接收机的构成主要在于中频滤波器不同,超外差式接收机的中频滤波器为带通滤波器,除此之外,两种接收机的构成基本相同。

本章利用ADS软件设计仿真超外差式接收机系统。

2.零中频接收机若天线接收的射频信号频率与本振信号源产生的本振信号频率相同,接收机称为零中频接收机,零中频接收机在经过混频后信号直接为基带信号,这是这种接收机的优点,但这种接收机的噪声与超外差式接收机相比比较大。

零中频接收机与超外差式接收机的差异主要在中频滤波器,零中频接收机的中频滤波器为低通滤波器。

21.1.3 射频发射系统射频发射系统与射频接收系统的构成相反,由中频放大器、混频器、本振信号源、带通滤波器、功率放大器和天线构成,在发射系统中,系统的增益是最重要的指标。

21.2 射频接收系统的仿真射频接收系统的设计与仿真使用行为级功能模块实现,行为级功能模块包括滤波器、放大器和混频器等,这些行为级功能模块在ADS软件中由系统级元器件构成,可以运用S参数仿真、交流仿真和谐波平衡仿真等对一个射频接收系统进行多种仿真,从而确定该射频接收系统的各种性能指标。

21.2.1 射频接收系统的设计1.创建项目下面将创建一个射频系统的项目,本章所有的设计都将保存在这个项目之中。

创建射频系统项目的步骤如下。

(1)启动ADS软件,弹出主视窗。

(2)选择主视窗中【File】菜单→【New Project】,弹出【New Project】对话框,在【New第21章 射频接收与发射系统的仿真 527║Project】对话框中,可以看见已经存在了默认的工作路径“C:\ADSuser\”,在路径的末尾输入项目的名称,这里项目名称定为RF_System,并且在【Project Tech-nology Files】栏选择这个项目默认的长度单位,默认的长度单位选为mill imeter。