BAR64V-06-GS08中文资料

BAR 64-06中文资料

V(BR) IR VF

200

-

-

-

-

-

-V 50 nA 1.1 V

AC characteristics

Diode capacitance VR = 20 V, f = 1 MHz

CT

- 0.23 0.35 pF

Forward resistance

IF = 1 mA, f = 100 MHz IF = 10 mA, f = 100 MHz IF = 100 mA, f = 100 MHz

BAR 64 ...

Silicon PIN Diodes

• High voltage current controlled RF resistor for RF attenuator and switches

• Frequency range above 1 MHz • Low resistance and short carrier lifetime • For frequencies up to 3 GHz

RthJS

10 3

10 2

K/W

IFmax / IFDC

10 2

10 1

0.5

0.2

0.1

0.05

10 0

0.02

0.01

0.005

D=0

10

-1

1

10 -2

s

10 0

tp

3

-

D=0

0.005

0.01

0.02

0.05

0.1

10 1

0.2

0.5

10

0

10

-6

10 -5

10 -4

10 -3

CS42448_06中文资料

Control Port & Serial Audio Port Supply = 1.8 V to 5 V

Digital Supply = 3.3 V to 5 V

Analog Supply = 3.3 V to 5 V

I2C/SPI Software Mode

Control Data

Interrupt Reset

All eight DAC channels provide digital volume control and can operate with differential or single-ended outputs.

An auxiliary serial input is available for an additional two channels of PCM data.

Level Translator

Register Configuration

ADC Overflow & Clock Error

Interrupt

Internal Voltage Reference

External Mute Control

Mute Control

Serial Audio Input

DC ELECTRICAL CHARACTERISTICS .............................................................................................. 23

DIGITAL INTERFACE SPECIFICATIONS & CHARACTERISTICS ..................................................... 23

GS864436资料

Product PreviewGS864418(B/E)/GS864436(B/E)/GS864472(C)4M x 18, 2M x 36, 1M x 7272Mb S/DCD Sync Burst SRAMs250 MHz –133MHz 2.5 V or 3.3 V V DD 2.5 V or 3.3 V I/O119-, 165-, & 209-Pin BGA Commercial Temp Industrial Temp Features• FT pin for user-configurable flow through or pipeline operation • Single/Dual Cycle Deselect selectable• IEEE 1149.1 JTAG-compatible Boundary Scan• ZQ mode pin for user-selectable high/low output drive • 2.5 V or 3.3 V +10%/–10% core power supply • LBO pin for Linear or Interleaved Burst mode• Internal input resistors on mode pins allow floating mode pins • Default to SCD x18/x36 Interleaved Pipeline mode • Byte Write (BW) and/or Global Write (GW) operation • Internal self-timed write cycle• Automatic power-down for portable applications• JEDEC-standard 119-, 165-, and 209-bump BGA packageFunctional DescriptionApplicationsThe GS864418/36/72 is a 75,497,472-bit high performancesynchronous SRAM with a 2-bit burst address counter. Although of a type originally developed for Level 2 Cache applications supporting high performance CPUs, the device now finds application insynchronous SRAM applications, ranging from DSP main store to networking chip set support.ControlsAddresses, data I/Os, chip enable (E1), address burst control inputs (ADSP, ADSC, ADV), and write control inputs (Bx, BW, GW) are synchronous and are controlled by a positive-edge-triggered clock input (CK). Output enable (G) and power down control (ZZ) are asynchronous inputs. Burst cycles can be initiated with either ADSP or ADSC inputs. In Burst mode, subsequent burst addresses are generated internally and are controlled by ADV. The burst address counter may be configured to count in either linear or interleave order with the Linear Burst Order (LBO) input. The Burst function need not be used. New addresses can be loaded on every cycle with no degradation of chip performance.Flow Through/Pipeline ReadsThe function of the Data Output register can be controlled by the user via the FT mode . Holding the FT mode pin low places the RAM in Flow Through mode, causing output data to bypass the Data Output Register. Holding FT high places the RAM in Pipeline mode, activating the rising-edge-triggered Data Output Register.SCD and DCD Pipelined ReadsThe GS864418/36/72 is a SCD (Single Cycle Deselect) and DCD (Dual Cycle Deselect) pipelined synchronous SRAM. DCD SRAMs pipeline disable commands to the same degree as read commands. SCD SRAMs pipeline deselect commands one stage less than read commands. SCD RAMs begin turning off their outputs immediately after the deselect command has been captured in the input registers. DCD RAMs hold the deselect command for one full cycle and then begin turning off their outputs just after the second rising edge of clock. The user may configure this SRAM for either mode of operation using the SCD mode input.Byte Write and Global WriteByte write operation is performed by using Byte Write enable (BW) input combined with one or more individual byte write signals (Bx). In addition, Global Write (GW) is available for writing all bytes at one time, regardless of the Byte Write control inputs.FLXDrive™The ZQ pin allows selection between high drive strength (ZQ low) for multi-drop bus applications and normal drive strength (ZQ floating or high) point-to-point applications. See the Output Driver Characteristics chart for details.Sleep ModeLow power (Sleep mode) is attained through the assertion (High) of the ZZ signal, or by stopping the clock (CK). Memory data is retained during Sleep mode.Core and Interface VoltagesThe GS864418/36/72 operates on a 2.5 V or 3.3 V power supply. All input are 3.3 V and 2.5 V compatible. Separate output power (V DDQ ) pins are used to decouple output noise from the internal circuits and are 3.3 V and 2.5 V compatible.Parameter Synopsis-250-225-200-166-150-133UnitPipeline 3-1-1-1t KQ (x18/x36)t KQ (x72)tCycle 2.53.04.0 2.73.04.4 3.03.05.0 3.53.56.0 3.83.86.7 4.04.07.5ns ns ns Curr (x36)Curr (x72)450540415505385460345405325385295345mA mA Flow Through 2-1-1-1t KQ tCycle 6.5 6.5 6.57.07.58.5ns Curr (x36)Curr (x72)290345290345290345280335265315245300mA mAGS864418(B/E)/GS864436(B/E)/GS864472(C) GS864472C Pad Out—209-Bump BGA—Top View (Package C)1234567891011A DQ G DQ G A E2ADSP ADSC ADV E3A DQB DQ B AB DQ G DQ G BC BG NC BW A BB BF DQ B DQ B BC DQ G DQ G BH BD NC E1NC BE BA DQ B DQ B CD DQ G DQ G V SS NC NC G GW NC V SS DQ B DQ B DE DQP G DQP C V DDQ V DDQ V DD V DD V DD V DDQ V DDQ DQPF DQP B EF DQ C DQ C V SS V SS V SS ZQ V SS V SS V SS DQ F DQ F FG DQ C DQ C V DDQ V DDQ V DD MCH V DD V DDQ V DDQ DQ F DQ F GH DQ C DQ C V SS V SS V SS MCL V SS V SS V SS DQ F DQ F H J DQ C DQ C V DDQ V DDQ V DD MCL V DD V DDQ V DDQ DQ F DQ F J K NC NC CK NC V SS MCL V SS NC NC NC NC K L DQ H DQ H V DDQ V DDQ V DD FT V DD V DDQ V DDQ DQ A DQ A L M DQ H DQ H V SS V SS V SS MCL V SS V SS V SS DQ A DQ A M N DQ H DQ H V DDQ V DDQ V DD SCD V DD V DDQ V DDQ DQ A DQ A N P DQ H DQ H V SS V SS V SS ZZ V SS V SS V SS DQ A DQ A P R DQP D DQP H V DDQ V DDQ V DD V DD V DD V DDQ V DDQ DQP A DQP E R T DQ D DQ D V SS NC NC LBO NC NC V SS DQ E DQ E T U DQ D DQ D A A A A A A A DQ E DQ E U V DQ D DQ D A A A A1A A A DQ E DQ E V W DQ D DQ D TMS TDI A A0A TDO TCK DQ E DQ E W11 x 19 Bump BGA—14 x 22 mm2 Body—1 mm Bump PitchGS864418(B/E)/GS864436(B/E)/GS864472(C)GS864472 209-Bump BGA Pin DescriptionSymbol Type DescriptionA0, A1I Address field LSBs and Address Counter Preset Inputs.A I Address InputsDQ ADQ BDQ CDQ DI/O Data Input and Output pinsDQ EDQ FDQ GDQ HB A, B B I Byte Write Enable for DQ A, DQ B I/Os; active lowB C,B D I Byte Write Enable for DQ C, DQ D I/Os; active lowB E, B F, B G,B H I Byte Write Enable for DQ E, DQ F, DQ G, DQ H I/Os; active lowNC—No ConnectCK I Clock Input Signal; active highGW I Global Write Enable—Writes all bytes; active lowE1I Chip Enable; active lowE3I Chip Enable; active lowE2I Chip Enable; active highG I Output Enable; active lowADV I Burst address counter advance enable; active low ADSP, ADSC I Address Strobe (Processor, Cache Controller); active low ZZ I Sleep Mode control; active highFT I Flow Through or Pipeline mode; active lowLBO I Linear Burst Order mode; active lowSCD I Single Cycle Deselect/Dual Cycle Deselect Mode ControlMCH I Must Connect HighGS864418(B/E)/GS864436(B/E)/GS864472(C)MCL Must Connect Low BW I Byte Enable; active lowZQ I FLXDrive Output Impedance Control(Low = Low Impedance [High Drive], High = High Impedance [Low Drive])TMS I Scan Test Mode Select TDI I Scan Test Data In TDO O Scan Test Data Out TCK I Scan Test Clock V DD I Core power supply V SS I I/O and Core Ground V DDQIOutput driver power supplyGS864472 209-Bump BGA Pin Description (Continued)SymbolType DescriptionGS864418(B/E)/GS864436(B/E)/GS864472(C) 165-Bump BGA—x18 Commom I/O—Top View (Package E)1234567891011A NC A E1BB NC E3BW ADSC ADV A A AB NC A E2NC BA CK GW G ADSP A NC BC NC NC V DDQ V SS V SS V SS V SS V SS V DDQ NC DQPA CD NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA DE NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA EF NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA FG NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA GH FT MCL NC V DD V SS V SS V SS V DD NC ZQ ZZ HJ DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC JK DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC KL DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC LM DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC MN DQPB SCD V DDQ V SS NC A NC V SS V DDQ NC NC NP NC A A A TDI A1TDO A A A A PR LBO A A A TMS A0TCK A A A A R11 x 15 Bump BGA—15 mm x 17 mm Body—1.0 mm Bump PitchGS864418(B/E)/GS864436(B/E)/GS864472(C) 165-Bump BGA—x36 Common I/O—Top View (Package E)1234567891011A NC A E1BC BB E3BW ADSC ADV A NC AB NC A E2BD BA CK GW G ADSP A NC BC DQPC NC V DDQ V SS V SS V SS V SS V SS V DDQ NC DQPB CD DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB DE DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB EF DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB FG DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB GH FT MCL NC V DD V SS V SS V SS V DD NC ZQ ZZ HJ DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA JK DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA KL DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA LM DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA MN DQPD SCD V DDQ V SS NC A NC V SS V DDQ NC DQPA NP NC A A A TDI A1TDO A A A A PR LBO A A A TMS A0TCK A A A A R11 x 15 Bump BGA—15 mm x 17 mm Body—1.0 mm Bump PitchGS864418(B/E)/GS864436(B/E)/GS864472(C)GS864418/36 165-Bump BGA Pin DescriptionSymbol Type DescriptionA0, A1I Address field LSBs and Address Counter Preset InputsA I Address InputsDQ ADQ BDQ CDQ DI/O Data Input and Output pinsB A, B B, B C, B D I Byte Write Enable for DQ A, DQ B, DQ C, DQ D I/Os; active low (x36 Version)NC—No ConnectCK I Clock Input Signal; active highBW I Byte Write—Writes all enabled bytes; active lowGW I Global Write Enable—Writes all bytes; active lowE1I Chip Enable; active lowE3I Chip Enable; active lowE2I Chip Enable; active highG I Output Enable; active lowADV I Burst address counter advance enable; active l0w ADSC, ADSP I Address Strobe (Processor, Cache Controller); active low ZZ I Sleep mode control; active highFT I Flow Through or Pipeline mode; active lowLBO I Linear Burst Order mode; active lowZQ I FLXDrive Output Impedance Control (Low = Low Impedance [High Drive], High = High Impedance [LowDrive])TMS I Scan Test Mode SelectTDI I Scan Test Data InTDO O Scan Test Data OutTCK I Scan Test ClockMCL—Must Connect Low SCD—Single Cycle Deselect/Dual Cyle Deselect Mode Control V DD I Core power supplyV SS I I/O and Core GroundV DDQ I Output driver power supplyGS864418(B/E)/GS864436(B/E)/GS864472(C) GS864436B Pad Out—119-Bump BGA—Top View (Package B)1234567A V DDQ A A ADSP A A V DDQ AB NC A A ADSC A A NC BC NC A A V DD A A NC CD DQ C DQP C V SS ZQ V SS DQP B DQ B DE DQ C DQ C V SS E1V SS DQ B DQ B EF V DDQ DQ C V SSG V SS DQ B V DDQ FG DQ C DQ C BC ADV BB DQ B DQ B GH DQ C DQ C V SS GW V SS DQ B DQ B HJ V DDQ V DD NC V DD NC V DD V DDQ JK DQ D DQ D V SS CK V SS DQ A DQ A KL DQ D DQ D BD SCD BA DQ A DQ A LM V DDQ DQ D V SS BW V SS DQ A V DDQ MN DQ D DQ D V SS A1V SS DQ A DQ A NP DQ D DQP D V SS A0V SS DQP A DQ A PR NC A LBO V DD FT A NC RT NC A A A A A ZZ TU V DDQ TMS TDI TCK TDO NC V DDQ U7 x 17 Bump BGA—14 x 22 mm2 Body—1.27 mm Bump PitchGS864418(B/E)/GS864436(B/E)/GS864472(C) GS864418B Pad Out—119-Bump BGA—Top View (Package B)1234567A V DDQ A A ADSP A A V DDQ AB NC A A ADSC A A NC BC NC A A V DD A A NC CD DQ B NC V SS ZQ V SS DQP A NC DE NC DQ B V SS E1V SS NC DQ A EF V DDQ NC V SSG V SS DQ A V DDQ FG NC DQ B BB ADV NC NC DQ A GH DQ B NC V SS GW V SS DQ A NC HJ V DDQ V DD NC V DD NC V DD V DDQ JK NC DQ B V SS CK V SS NC DQ A KL DQ B NC NC SCD BA DQ A NC LM V DDQ DQ B V SS BW V SS NC V DDQ MN DQ B NC V SS A1V SS DQ A NC NP NC DQP B V SS A0V SS NC DQ A PR NC A LBO V DD FT A NC RT A A A A A A ZZ TU V DDQ TMS TDI TCK TDO NC V DDQ U7 x 17 Bump BGA—14 x 22 mm2 Body—1.27 mm Bump PitchGS864418(B/E)/GS864436(B/E)/GS864472(C)GS864418/36 119-Bump BGA Pin DescriptionSymbol Type DescriptionA0, A1I Address field LSBs and Address Counter Preset InputsA I Address InputsDQ ADQ BDQ CDQ DI/O Data Input and Output pinsB A, B B, B C, B D I Byte Write Enable for DQ A, DQ B, DQ C, DQ D I/Os; active lowNC—No ConnectCK I Clock Input Signal; active highBW I Byte Write—Writes all enabled bytes; active lowGW I Global Write Enable—Writes all bytes; active lowE1I Chip Enable; active lowG I Output Enable; active lowADV I Burst address counter advance enable; active low ADSP, ADSC I Address Strobe (Processor, Cache Controller); active low ZZ I Sleep mode control; active highFT I Flow Through or Pipeline mode; active lowLBO I Linear Burst Order mode; active lowZQ I FLXDrive Output Impedance Control (Low = Low Impedance [High Drive], High = High Impedance [LowDrive])SCD I Single Cycle Deselect/Dual Cyle Deselect Mode Control TMS I Scan Test Mode SelectTDI I Scan Test Data InTDO O Scan Test Data OutTCK I Scan Test ClockV DD I Core power supplyV SS I I/O and Core GroundV SS I I/O and Core GroundV DDQ I Output driver power supplyGS864418(B/E)/GS864436(B/E)/GS864472(C)GS864418/36/72 Block DiagramA1A0A0A1D0D1Q1Q0Counter LoadD QDQRegisterRegisterDQRegisterDQRegisterDQRegisterD QRegisterD QRegisterD QRegisterDQR e g i s t e rDQRegisterA0–An LBO ADV CK ADSC ADSP GW BW E 1FT GZZPower Down ControlMemory Array36364AQD DQx1–DQx93636Note: Only x36 version shown for simplicity.SCD3636B AB BB CB DGS864418(B/E)/GS864436(B/E)/GS864472(C)Note:There are pull-up devices onthe ZQ, SCD, and FT pins and a pull-down device on the ZZ pin, so those input pins can be unconnected and the chip will operate in the default states as specified in the above tables.Burst Counter SequencesBPR 1999.05.18Mode Pin FunctionsMode NamePin NameStateFunctionBurst Order Control LBO L Linear Burst H Interleaved Burst Output Register Control FT L Flow Through H or NC Pipeline Power Down Control ZZ L or NC Active H Standby, I DD = I SB Single/Dual Cycle Deselect Control SCD L Dual Cycle Deselect H or NC Single Cycle Deselect FLXDrive Output Impedance ControlZQL High Drive (Low Impedance)H or NCLow Drive (High Impedance)Note:The burst counter wraps to initial state on the 5th clock.Note:The burst counter wraps to initial state on the 5th clock.Linear Burst SequenceA[1:0]A[1:0]A[1:0]A[1:0]1st address 000110112nd address 011011003rd address 101100014th address11000110Interleaved Burst SequenceA[1:0]A[1:0]A[1:0]A[1:0]1st address 000110112nd address 010011103rd address 101100014th address11100100GS864418(B/E)/GS864436(B/E)/GS864472(C)1.All byte outputs are active in read cycles regardless of the state of Byte Write Enable inputs.2.Byte Write Enable inputs B A , B B , B C , and/or B D may be used in any combination with BW to write single or multiple bytes.3.All byte I/Os remain High-Z during all write operations regardless of the state of Byte Write Enable inputs.4.Bytes “C ” and “D ” are only available on the x36 version.Byte Write Truth TableFunctionGWBWB AB BB CB DNotesRead H H X X X X 1Read H L H H H H 1Write byte a H L L H H H 2, 3Write byte b H L H L H H 2, 3Write byte c H L H H L H 2, 3, 4Write byte d H L H H H L 2, 3, 4Write all bytesHLLLLL2, 3, 4Write all bytes L X X X X XGS864418(B/E)/GS864436(B/E)/GS864472(C) Synchronous Truth TableOperation Address UsedStateDiagramKey5E1ADSP ADSC ADV W3DQ4Deselect Cycle, Power Down None X H X L X X High-Z Read Cycle, Begin Burst External R L L X X X Q Read Cycle, Begin Burst External R L H L X F Q Write Cycle, Begin Burst External W L H L X T D Read Cycle, Continue Burst Next CR X H H L F Q Read Cycle, Continue Burst Next CR H X H L F Q Write Cycle, Continue Burst Next CW X H H L T D Write Cycle, Continue Burst Next CW H X H L T D Read Cycle, Suspend Burst Current X H H H F Q Read Cycle, Suspend Burst Current H X H H F Q Write Cycle, Suspend Burst Current X H H H T D Write Cycle, Suspend Burst Current H X H H T D Notes:1.X = Don’t Care, H = High, L = Low2.W = T (True) and F (False) is defined in the Byte Write Truth Table preceding3.G is an asynchronous input. G can be driven high at any time to disable active output drivers. G low can only enable active drivers (shownas “Q” in the Truth Table above).4.All input combinations shown above are tested and supported. Input combinations shown in gray boxes need not be used to accomplishbasic synchronous or synchronous burst operations and may be avoided for simplicity.5.Tying ADSP high and ADSC low allows simple non-burst synchronous operations. See BOLD items above.6.Tying ADSP high and ADV low while using ADSC to load new addresses allows simple burst operations. See ITALIC items above.GS864418(B/E)/GS864436(B/E)/GS864472(C)Simplified State DiagramFirst WriteFirst ReadBurst WriteBurst ReadDeselect R WCRCWX XWRRWRXXX S i m p l e S y n c h r o n o u s O p e r a t i o nS i m p l e B u r s t S y n c h r o n o u s O p e r a t i o nCR RCWCRCRNotes:1.The diagram shows only supported (tested) synchronous state transitions. The diagram presumes G is tied low.2.The upper portion of the diagram assumes active use of only the Enable (E1) and Write (B A , B B , B C , B D , BW, and GW) control inputs, andthat ADSP is tied high and ADSC is tied low.3.The upper and lower portions of the diagram together assume active use of only the Enable, Write, and ADSC control inputs andassumes ADSP is tied high and ADV is tied low.GS864418(B/E)/GS864436(B/E)/GS864472(C)Simplified State Diagram with GFirst WriteFirst ReadBurst WriteBurst ReadDeselect R WCRCWXXWRRWRXXX CRR CW CRCRW CWW CWNotes:1.The diagram shows supported (tested) synchronous state transitions plus supported transitions that depend upon the use of G.e of “Dummy Reads” (Read Cycles with G High) may be used to make the transition from read cycles to write cycles without passingthrough a Deselect cycle. Dummy Read cycles increment the address counter just like normal read cycles.3.Transitions shown in grey tone assume G has been pulsed high long enough to turn the RAM’s drivers off and for incoming data to meetData Input Set Up Time.GS864418(B/E)/GS864436(B/E)/GS864472(C)Note:Permanent damage to the device may occur if the Absolute Maximum Ratings are exceeded. Operation should be restricted to Recommended Operating Conditions. Exposure to conditions exceeding the Absolute Maximum Ratings, for an extended period of time, may affect reliability of this component.Absolute Maximum Ratings(All voltages reference to V SS )SymbolDescriptionValueUnitV DD Voltage on V DD Pins –0.5 to 4.6V V DDQ Voltage in V DDQ Pins –0.5 to 4.6V V I/O Voltage on I/O Pins –0.5 to V DDQ +0.5 (≤ 4.6 V max.)V V IN Voltage on Other Input Pins –0.5 to V DD +0.5 (≤ 4.6 V max.)V I IN Input Current on Any Pin +/–20mA I OUT Output Current on Any I/O Pin +/–20mA P D Package Power Dissipation 1.5WT STG Storage Temperature –55 to 125o C T BIASTemperature Under Bias–55 to 125oCPower Supply Voltage RangesParameterSymbolMin.Typ.Max.UnitNotes3.3 V Supply Voltage V DD3 3.0 3.3 3.6V 2.5 V Supply Voltage V DD2 2.3 2.5 2.7V 3.3 V V DDQ I/O Supply Voltage V DDQ3 3.0 3.3 3.6V 2.5 V V DDQ I/O Supply VoltageV DDQ22.32.52.7VNotes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn +2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.GS864418(B/E)/GS864436(B/E)/GS864472(C)V DDQ3 Range Logic LevelsParameter Symbol Min.Typ.Max.Unit Notes V DD Input High Voltage V IH 2.0—V DD + 0.3V1V DD Input Low Voltage V IL–0.3—0.8V1V DDQ I/O Input High Voltage V IHQ 2.0—V DDQ + 0.3V1,3V DDQ I/O Input Low Voltage V ILQ–0.3—0.8V1,3 Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn+2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.3.V IHQ (max) is voltage on V DDQ pins plus 0.3 V.V DDQ2 Range Logic LevelsParameter Symbol Min.Typ.Max.Unit Notes V DD Input High Voltage V IH0.6*V DD—V DD + 0.3V1V DD Input Low Voltage V IL–0.3—0.3*V DD V1V DDQ I/O Input High Voltage V IHQ0.6*V DD—V DDQ + 0.3V1,3V DDQ I/O Input Low Voltage V ILQ–0.3—0.3*V DD V1,3 Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn+2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.3.V IHQ (max) is voltage on V DDQ pins plus 0.3 V.Recommended Operating TemperaturesParameter Symbol Min.Typ.Max.Unit Notes Ambient Temperature (Commercial Range Versions)T A02570°C2 Ambient Temperature (Industrial Range Versions)T A–402585°C2 Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn+2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.GS864418(B/E)/GS864436(B/E)/GS864472(C)Note:These parameters are sample tested.Capacitance(T A = 25o C, f = 1 MH Z , V DD = 2.5 V)ParameterSymbolTest conditionsTyp.Max.UnitInput Capacitance C IN V IN = 0 V 810pF Input/Output Capacitance C I/OV OUT = 0 V1214pFAC Test ConditionsParameterConditionsInput high level V DD – 0.2 V Input low level 0.2 V Input slew rate 1 V/ns Input reference level V DD /2Output reference levelV DDQ /2Output loadFig. 1Notes:1.Include scope and jig capacitance.2.Test conditions as specified with output loading as shown in Fig. 1unless otherwise noted.3.Device is deselected as defined by the Truth Table. 20% tKCV SS – 2.0 V50%V SS V IHUndershoot Measurement and TimingOvershoot Measurement and Timing20% tKCV DD + 2.0 V50%V DDV ILDQV DDQ/250Ω30pF *Output Load 1* Distributed Test Jig CapacitanceGS864418(B/E)/GS864436(B/E)/GS864472(C)DC Electrical CharacteristicsParameter Symbol Test Conditions Min Max Input Leakage Current(except mode pins)I IL V IN = 0 to V DD–1 uA 1 uAZZ Input Current I IN1V DD≥V IN ≥V IH0 V≤ V IN ≤ V IH–1 uA–1 uA1 uA100 uAFT, SCD, and ZQ Input Current I IN2V DD≥V IN ≥V IL0 V≤ V IN ≤ V IL–100 uA–1 uA1 uA1 uAOutput Leakage Current I OL Output Disable, V OUT = 0 to V DD–1 uA 1 uA Output High Voltage V OH2I OH = –8 mA, V DDQ = 2.375 V 1.7 V—Output High Voltage V OH3I OH = –8 mA, V DDQ = 3.135 V 2.4 V—Output Low Voltage V OL I OL = 8 mA—0.4 VGS864418(B/E)/GS864436(B/E)/GS864472(C)N o t e s : 1.I D D a n d I D D Q a p p l y t o a n y c o m b i n a t i o n o f V D D 3, V D D 2, V D D Q 3, a n d V D D Q 2 o p e r a t i o n .2.A l l p a r a m e t e r s l i s t e d a r e w o r s t c a s e s c e n a r i o .O p e r a t i n g C u r r e n t sP a r a m e t e r T e s t C o n d i t i o n s M o d eS y m b o l -250-225-200-166-150-133U n i t0t o 70°C –40 t o 85°C0t o 70°C–40 t o 85°C 0t o 70°C –40t o 85°C 0 t o 70°C –40t o 85°C 0 t o 70°C –40t o 85°C 0 t o 70°C –40t o 85°C O p e r a t i n g C u r r e n tD e v i c e S e l e c t e d ; A l l o t h e r i n p u t s ≥V I H o r ≤ V I LO u t p u t o p e n(x 72)P i p e l i n eI D DI D D Q480605156044560480604105044550365404004034540380403153035030m AF l o w T h r o u g hI D DI D D Q315303403031530340303153034030305303303028530310302802030520m A(x 36)P i p e l i n eI D DI D D Q400504355037045405453454038040310353453529530330302702530525m AF l o w T h r o u g hI D DI D D Q270202952027020295202702029520260202852024520270202301525515m A(x 18)P i p e l i n eI D DI D D Q360253952533525370253152035020285203202027520310202501528515m AF l o w T h r o u g hI D DI D D Q250152751525015275152501527515240152601522515250152101523515m AS t a n d b y C u r r e n tZ Z ≥ V D D – 0.2 V—P i p e l i n eI S B 120160120160120160120160120160120160m AF l o w T h r o u g hI S B120160120160120160120160120160120160m AD e s e l e c t C u r r e n tD e v i c e D e s e l e c t e d ; A l l o t h e r i n p u t s ≥ V I H o r ≤ V I L—P i p e l i n eI D D200230190220180210170200170200160190m AF l o w T h r o u g hI D D170200170200160190160190150180140170m AGS864418(B/E)/GS864436(B/E)/GS864472(C)Notes:1.These parameters are sampled and are not 100% tested.2.ZZ is an asynchronous signal. However, in order to be recognized on any given clock cycle, ZZ must meet the specified setup and holdtimes as specified above.AC Electrical CharacteristicsParameterSymbol-250-225-200-166-150-133UnitMinMaxMinMaxMinMaxMinMaxMinMaxMinMaxPipelineClock Cycle Time tKC 4.0— 4.4— 5.0— 6.0— 6.7—7.5—ns Clock to Output Valid(x18/x36)tKQ — 2.5— 2.7— 3.0— 3.5— 3.8— 4.0ns Clock to Output Valid(x72)tKQ — 3.0— 3.0— 3.0— 3.5— 3.8— 4.0ns Clock to Output Invalid tKQX 1.5— 1.5— 1.5— 1.5— 1.5— 1.5—ns Clock to Output in Low-ZtLZ 1 1.5— 1.5— 1.5— 1.5— 1.5— 1.5—ns Setup time tS 1.3— 1.3— 1.4— 1.5— 1.5— 1.5—ns Hold Time tH 0.2—0.3—0.4—0.5—0.5—0.5—ns Flow ThroughClock Cycle Time tKC 6.5— 6.5— 6.5—7.0—7.5—8.5—ns Clock to Output ValidtKQ — 6.5— 6.5— 6.5—7.0—7.5—8.5ns Clock to Output Invalid tKQX 3.0— 3.0— 3.0— 3.0— 3.0— 3.0—ns Clock to Output in Low-ZtLZ 1 3.0— 3.0— 3.0— 3.0— 3.0— 3.0—ns Setup time tS 1.5— 1.5— 1.5— 1.5— 1.5— 1.5—ns Hold time tH 0.5—0.5—0.5—0.5—0.5—0.5—ns Clock HIGH Time tKH 1.3— 1.3— 1.3— 1.3— 1.5— 1.7—ns Clock LOW Time tKL 1.5—1.5—1.5—1.5— 1.7—2—ns Clock to Output inHigh-Z (x18/x36)tHZ 1 1.5 2.5 1.5 2.7 1.5 3.0 1.5 3.0 1.5 3.0 1.5 3.0ns Clock to Output in High-Z (x72)tHZ 1 1.5 3.0 1.5 3.0 1.5 3.0 1.5 3.0 1.5 3.0 1.5 3.0ns G to Output Valid (x18/x36)tOE — 2.5— 2.7— 3.2— 3.5— 3.8— 4.0ns G to Output Valid(x72)tOE — 3.0— 3.0— 3.2— 3.5— 3.8— 4.0ns G to output in Low-Z tOLZ 10—0—0—0—0—0—ns G to output in High-Z (x18/x36)tOHZ 1— 2.5— 2.7— 3.0— 3.0— 3.0— 3.0ns G to output in High-Z (x72)tOHZ 1— 3.0— 3.0— 3.0— 3.0— 3.0— 3.0ns ZZ setup time tZZS 25—5—5—5—5—5—ns ZZ hold time tZZH 21—1—1—1—1—1—ns ZZ recoverytZZR20—20—20—20—20—20—ns。

Keysight Technologies六氟化硫高压容器产品说明书

(707) 577-3000营业时间 早8:00-下午5:00化学品安全技术说明书紧急电话号码(带值班时间):化学名:六氟化硫供应商/ 制造商:Keysight Technologies, Inc.1400 Fountaingrove Parkway Santa Rosa, California 95403Sulfur Hexafluoride物质或混合物相关的确定的用途和使用防止建议 :E7200-80009,E7200-80059,E7200-89009&89059,E7200-89009&89059-DEF,N7210-80009, N7210-80059产品号:物质用途:分析化学。

(用于波导和X射线管)依据 GB/T 16483-2008 的安全数据表物质或混合物的分类警示词:警告危险性说明:H280 - 内装高压气体;遇热可能爆炸。

:防范说明预防措施:不适用。

事故响应:不适用。

贮存:P410 - 防日晒。

P403 - 存放在通风良好的地方。

废弃处置:不适用。

不导致分类的其他危险:充当简单的窒息物。

在非常高的浓度下,可取代标准空气并因缺氧而导致窒息。

液体可导致类似冻伤的烧伤。

化学品分类和标记全球协调体系(GHS)标签要素危险象形标记物质或混合物根据GB 13690-2009 化学品分类和危险性公示通则的分类H280压力下气体 - 液化气体没有出现就供应商当前所知可应用的浓度,被分类为对健康或环境有害及因此需要在本节报告的添加剂。

化学名:六氟化硫CAS号码:2551-62-4美国化学文摘社(CAS)编号/其它标识号EC 号:219-854-2职业暴露限制, 如果有的话, 列在第 8 节中。

将患者转移到空气新鲜处,休息,保持利于呼吸的体位。

如有害的健康影响持续存在或加重,应寻求医疗救治。

摄入液体会导致类似于冻伤的灼伤。

如果发生冻伤,就医。

切勿给失去意识者任何口服物。

如失去知觉,应置于康复位置并立即寻求医疗救治。

BAR64-02V(PIN二极管)

0.2

0.5

Permissible Puls Load RthJS = (tp)

BAR64-04T

10 3 K/W

10 2

10 1

D=0.5

0.2

0.1

0.05

0.02

0.01

10 0

0.005 0

IFmax/IFDC RthJS

10

0

10

-6

10 -5

10 -4

10 -3

10 -2

s

10 0

tP

Charge carrier life time

IF = 10 mA, IR = 6 mA, measured at IR = 3 mA,

RL = 100

I-region width Insertion loss1)

IF = 3 mA, f = 1.8 GHz IF = 5 mA, f = 1.8 GHz IF = 10 mA, f = 1.8 GHz Isolation1)

IF

120 mA

100 90 80 70 60 50 40 30 20 10 00 15 30 45 60 75 90 105 120 °C 150

TS

120 mA

IF

100 90 80 70 60 50 40 30 20 10 00 15 30 45 60 75 90 105 120 °C 150

10 -3

10 -2

10 -1

s 10 1

tp

10

-1

10

-6

10 -5

10 -4

10 -3

10 -2

s

10 0

tP

Permissible Pulse Load

波士顿-克洛德电气系统有限公司产品说明书:压力序列阀门,直接操作型DZ6DP

/6Informationen zu lieferbaren Ersatzteilen: /spcPressure sequence valve, direct operatedType DZ 6 DPNominal size 6Series 5XMaximum operating pressure 3 5 bar Maximum flow 60 l/minRE 26076/04.07Replaces: 02.03Overview of contentsFeatures– For subplate mounting– Connection location to DIN 24340 form A (without locating bore), (standard)– Connection location to ISO 440 -03-02-0-05 (with locating bore), (ordering code (60)– Subplates see catalogue sheet RE 45052(separate order)– 5 pressure stages– 4 adjustment elements, optional: • Rotary knob• Set screw with hexagon and protective cap • Lockable rotary knob with scale • Rotary knob with scale – Check valve, optionalContents PageFeatures Order code 2Preferred types 2Symbols 2Function, section 3T echnical data 4Characteristic curves 4Unit dimensions5K 4297-9y o f C M A /F l o d y n e /H y d r a d y n e ▪ M o t i o n C o n t r o l ▪ H y d r a u l i c ▪ P n e u m a t i c ▪ E l e c t r i c a l ▪ M e c h a n i c a l ▪ (800) 426-5480 ▪ w w w .c m a f h .c o mOrder codeStandard types2) Only with adjustment element …2“ and without check valve 3) Locating pin ISO 8752-3x8-St, Material No. R900005694(separate order)TypeMaterial number DZ 6 DP2-5X/25Y R900403077DZ 6 DP2-5X/75Y R90048 060DZ 6 DP2-5X/ 50Y R90048 06 DZ 6 DP2-5X/2 0Y R90048 062DZ 6 DP2-5X/3 5YMR9005 3984SymbolsVersion …No code“Version …X“Version …Y“Version …XY“y o f C M A /F l o d y n e /H y d r a d y n e ▪ M o t i o n C o n t r o l ▪ H y d r a u l i c ▪ P n e u m a t i c ▪ E l e c t r i c a l ▪ M e c h a n i c a l ▪ (800) 426-5480 ▪ w w w .c m a f h .c oThe valve type DZ 6 DP is a direct operated pressure se-quence valve. It is used for the pressure dependent connection of a second system. The setting of the sequence pressure is via the adjustment element (4).The compression spring (3) holds the control spool (2) in its initial position, the valve is closed. The pressure in port P is ap-plied to the piston area of the control spool (2) via the control line (6) at the opposite side to the spring (3).When the pressure in port P reaches the set value of the spring (3), then the control spool (2) is moved to the left and the connection P to A is opened. The system connected to port A is connected without a pressure decrease occuring in port P.The control signal originates internally via the control line (6) from port P or externally via port B (X).Depending on the use of the valve the leakage oil drain is exter-nally via port T (Y) or internally via A.With internal leakage oil drain the set opening pressure in-creases by the pressure present in port ”A”.For the free return of the pressure fluid from port A to port P a check valve (5) may optionally be installed.A pressure gauge port ( ) enables the monitoring of the se-quence pressure set at the valve.Function, sectiony o f C M A /F l o d y n e /H y d r a d y n e ▪ M o t i o n C o n t r o l ▪ H y d r a u l i c ▪ P n e u m a t i c ▪ E l e c t r i c a l ▪ M e c h a n i c a l ▪ (800) 426-5480 ▪ w w w .c m a f h .c o010605020304050100150200250300350010605203040501015202512Technical data (for applications outside these parameters, please consult us!)GeneralWeight kgApprox. .2InstallationOptionalAmbient temperature range°C –30 to +80 (NBR seals) –20 to +80 (FKM seals)) Suitable for NBR and FKM sesals 2) Only suitable for FKM seals3) The cleanliness class stated for the components must beadhered too in hydraulic systems. Effective filtration preventsfaults from occurring and at the same time increases the component service life.For the selection of filters see catalogue sheets RE 50070, RE 50076, RE 5008 , RE 50086, RE 50087 and RE 50088.Characteristic curves (measured with HLP46, ϑoil = 40 °C ± 5 °C)p -q V -characteristic curves The characteristic curves are valid for the output pressure = zero over the entire flow rangeS e q u e n c e p r e s s u r e i n b a r →Flow in l/min →P r e s s u r e d i f f e r e n t i a l i n b a r →Flow in l/min →1 via check valve, flow from A to P2 P to A∆p -q V -characteristic curvesHydraulicMaximum operating pressure– Ports P, A, B (X)bar 3 5– Ports T (Y)bar 60Maximum sequence pressure (adjustable)bar 25; 75; 50; 2 0; 3 5Maximum flow l/min60Pressure fluidMineral oil (HL, HLP) to DIN 5 524 ); Fast bio-degradable pressure fluids to VDMA 24568 (also see RE 9022 ); HETG (rape seed oil) ); HEPG (polyglycols) 2); HEES (synthetic ester) 2); other pressure fluids on request Pressure fluid temperature range °C –30 to +80 (NBR seals) –20 to +80 (FKM seals)Viscosity rangemm 2/s0 to 800Max. permissible degree of contamination of the hydraulic fluid – cleanliness class to ISO 4406 (c)Class 20/ 8/ 5 3)y o f C M A /F l o d y n e /H y d r a d y n e ▪ M o t i o n C o n t r o l ▪ H y d r a u l i c ▪ P n e u m a t i c ▪ E l e c t r i c a l ▪ M e c h a n i c a l ▪ (800) 426-5480 ▪ w w w .c m a f h .c oUnit dimensions (dirmensions in mm)1Name plate2Adjustment element … “3Adjustment element …2“4Adjustment element …3“5Adjustment element …7“6Space required to remove the key 7Valve fixing holes 8Locknut 24A/F 9Hexagon 0A/F10Same seal rings for portsA, B(X), P, T(Y)11Pressure gauge connection G /4;2 deep; internal hexagon 6A/F 12Without check valve 13With check valve14Connection locationto DIN 24340 Form A (without locating bore), orISO 440 -03-02-0-05 (with loca-ting bore for locating pin ISO 8752-3x8-St, Material No. R900005694, order separately)Subplates to data sheet RE 45052 (order separately)(without locating bore) G 34 /0 (G /4) G 342/0 (G3/8) G 502/0 (G /2)(with locating bore) G 34 /60 (G /4) G 342/60 (G3/8)G 502/60 (G /2)Valve fixing screws (order separately)4 socket head cap screws (SHCS) ISO 4762 - M5 x 50 - 10.9-flZn-240h-L friction coefficient μtotal = 0.09 bis 0. 4, tightening torque M T = 7 Nm ± 0%, material number R913000064Pipe thread (G..) to ISO 228/y o f C M A /F l o d y n e /H y d r a d y n e ▪ M o t i o n C o n t r o l ▪ H y d r a u l i c ▪ P n e u m a t i c ▪ E l e c t r i c a l ▪ M e c h a n i c a l ▪ (800) 426-5480 ▪ w w w .c m a f h .c oBosch Rexroth AG HydraulicsZum Eisengießer978 6 Lohr am Main, Germany Phone +49 (0) 93 52 / 8-0 Fax +49 (0) 93 52 / 8-23 58*****************************www.boschrexroth.de© This document, as well as the data, specifications and other information set forth in it, are the exclusive property of Bosch Rexroth AG. It may not be reproduced or given to third parties without its consent.The data specified above only serve to describe the product. No state-ments concerning a certain condition or suitability for a certain application can be derived from our information. The information given does not release the user from the obligation of own judgment and verification. It must be remembered that our products are subject to a natural process of wear and aging.Notesy o f C M A /F l o d y n e /H y d r a d y n e ▪ M o t i o n C o n t r o l ▪ H y d r a u l i c ▪ P n e u m a t i c ▪ E l e c t r i c a l ▪ M e c h a n i c a l ▪ (800) 426-5480 ▪ w w w .c m a f h .c oBosch Rexroth AG HydraulicsZum Eisengießer978 6 Lohr am Main, Germany Phone +49 (0) 93 52 / 8-0 Fax +49 (0) 93 52 / 8-23 58*****************************www.boschrexroth.de© This document, as well as the data, specifications and other information set forth in it, are the exclusive property of Bosch Rexroth AG. It may not be reproduced or given to third parties without its consent.The data specified above only serve to describe the product. No state-ments concerning a certain condition or suitability for a certain application can be derived from our information. The information given does not release the user from the obligation of own judgment and verification. It must be remembered that our products are subject to a natural process of wear and aging.Notesy o f C M A /F l o d y n e /H y d r a d y n e ▪ M o t i o n C o n t r o l ▪ H y d r a u l i c ▪ P n e u m a t i c ▪ E l e c t r i c a l ▪ M e c h a n i c a l ▪ (800) 426-5480 ▪ w w w .c m a f h .c oBosch Rexroth AG HydraulicsZum Eisengießer978 6 Lohr am Main, Germany Phone +49 (0) 93 52 / 8-0 Fax +49 (0) 93 52 / 8-23 58*****************************www.boschrexroth.de© This document, as well as the data, specifications and other information set forth in it, are the exclusive property of Bosch Rexroth AG. It may not be reproduced or given to third parties without its consent.The data specified above only serve to describe the product. No state-ments concerning a certain condition or suitability for a certain application can be derived from our information. The information given does not release the user from the obligation of own judgment and verification. It must be remembered that our products are subject to a natural process of wear and aging.Notesy o f C M A /F l o d y n e /H y d r a d y n e ▪ M o t i o n C o n t r o l ▪ H y d r a u l i c ▪ P n e u m a t i c ▪ E l e c t r i c a l ▪ M e c h a n i c a l ▪ (800) 426-5480 ▪ w w w .c m a f h .c o。

bat 64中文资料

3

Oct-07-1999

Type BAT 64 BAT 64-04 BAT 64-05 BAT 64-06

Marking 63s 64s 65s 66s 1=A 1 = A1 1 = A1 1 = C1

Pin Configuration 2 n.c. 2 = C2 2 = A2 2 = C2 3=C 3 = C1/A2 3 = C1/2 3 = A1/2

300

BAT 64... EHB00153

ΙF

mA

ΙF

mA

200 TS TA 100

200 TS TA 100

0

0

50

100

˚C

150

0

0

50

100

˚C

150

TA ;TS

TA ;TS

Diode capacitance CT = f (VR)

f = 1MHz

10 CT pF 8 7 6 5 4 3 2 1 0 0 10 20 V VR 30

V

30

2

Oct-07-1999

元器件交易网

BAT 64

Forward current IF = f (TA *;TS ) *Package mounted on epoxy BAT 64

300

BAT 64 EHB00152

Forward current IF = f (TA*;TS) *Package mounted on epoxy BAT 64-04... (I F per Diode)

元器件交易网

BAT 64

Silicon Schottky Diodes • For low-loss, fast-recovery, meter protection, bias isolation and clamping applications • Integrated diffused guard ring • Low forward voltage

Omega DVG-64电子真空压力计说明书

DVG-64Electronic Vacuum Gauge1Display Updated every second. 1 micron resolution below 200 micron of vacuumSensor T y pe ThermistorConnector T ype Standard 1/4 inch male flare fittingV a cuum R ange0 - 12,000 Microns (0 - 1,600 Pascals) with vacuum increasing/decreasing indicator when above 12,000 MicronsScale Microns, PSI, InHg, milliBars, Pascals, T orr, milliT orr Operating T emp. Range 2 to 52°C (35 to 125°F) Overpressure 300 PSI max (20 Bar) Accuracy ±10% (0 to 1000 microns)P o wer S ource 9 V o lt Alkaline battery (not included)Continuous Usage Over 35 hours Auto Shut off After 10 minutes when vacuum reading is above 12,000 Microns (12 T orr) W e ightFEATURES• Reads v acuum in 7 international units• Uses the batter y power than other models• Cleaning por t provides quick cleaning and drying of sensor • Uses standard 9V Alkaline batter y • Con venient built-in hangerOPERATING CONTROLS• T urning the vacuum gauge ON: Press and hold the ON button for about 3 seconds, until "POWER UP" appears on the display. • T urning the vacuum gauge OFF: Press the OFF button T o prolong battery life, when vacuum reading is above 12,000 Microns for about 10 minutes, the unit will automatically turn OFF . • Changing the scale: Press the Scale button to change the display to the next scale. The scale order is: Microns, PSI, Inches of mercury (InHg), milliBars, Pascals, T orr and milliT orr. DVG64 will keep the scale settings even if the power is turned OFF .UNDERSTANDING THE DISPLAY• When the vacuum reading is above 12,000 Microns (1,600 Pascals), the first line of the display shows "Atm." The second line displays a bar graph to indicate the direction in which the vacuum is moving. When the bar graph is moving from left to right, the pressure is increasing. When the bar graph is moving from right to left, the pressure is decreasing. The speed of the bar graph indicates how fast the pressure is increasing ordecreasing. The bar graph indicator may be inaccurate for a few seconds after the evacuation of the system has begun.• The bar graph disappears if the vacuum does not change for about 10 seconds. When the vacuum reading is below 12,000 Microns (1,600 Pascals), the vacuum in the selected units is displayed.CONNECTING TO THE VACUUM SYSTEMThe VG64 should only be connected to the vacuum system at the vacuum port. The "Auxiliary Port" is primarily for cleaning and should normally be closed with the supplied cap.CLEANING THE VACUUM SENSORIt is recommended that the sensor be cleaned periodically to maintain unit accuracy . Oil and other contaminants reduce the accuracy of the unit. Follow the instructions below for cleaning. • Close the Vacuum port with the supplied cap. Open the Auxiliary port.• Use an eyedropper to pour about 2 teaspoons of ordinary rubbing alcohol into the Auxiliary port.• Close the Auxiliary port with the supplied cap. Both the Vacuum and Auxiliary ports should now be closed. • Shake the DVG64 unit for about 10 seconds. A slightmovement of the vacuum sensor in the case is normal and does not affect the internal connection in any way. • Open both the Vacuum and the Auxiliary ports. Empty the alcohol, and air dry the sensor.• Close both the Vacuum and the Auxiliary ports with the supplied caps when the DVG64 is not used. This prevents contamination of the sensor.0.2 kg (6.7 oz)WARRANTY/DISCLAIMEROMEGA ENGINEERING, INC. warrants this unit to be free of defects in materials and workmanship for a period of 13 months from date of purchase. OMEGA’s WARRANTY adds an additional one (1) month grace period to the normal one (1) year product warranty to cover handling and shipping time. This ensures that OMEGA’s customers receive maximum coverage on each product.If the unit malfunctions, it must be returned to the factory for evaluation. OMEGA’s Customer Service Department will issue an Authorized Return (AR) number immediately upon phone or written request. Upon examination by OMEGA, if the unit is found to be defective, it will be repaired or replaced at no charge. OMEGA’s WARRANT Y does not apply to defects resulting from any action of the purchaser, including but not limited to mishandling, improper interfacing, operation outside of design limits, improper repair, or unauthorized modification. This WARRANTY is VOID if the unit shows evidence of having been tampered with or shows evidence of having been damaged as a result of excessive corrosion; or current, heat, moisture or vibration; improper specification; misapplication; misuse or other operating conditions outside of OMEGA’s control. Components in which wear is not warranted, include but are not limited to contact points, fuses, and triacs.OMEGA is pleased to offer suggestions on the use of its various products. However, OMEGA neither assumes responsibility for any omissions or errors nor assumes liability for any damages that result from the use of its products in accordance with information provided by OMEGA, either verbal or written. OMEGA warrants only that the parts manufactured by the company will be as specified and free of defects. OMEGA MAKES NO OTHER W ARRANTIES OR REPRESENTATIONS OF ANY KIND W HATSOEVER, EXPRESSED OR IMPLIED, EXCEPT THAT OF TITLE, AND ALL IMPLIED W ARRANTIES INCLUDING ANY W ARRANTY OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE HEREBY DISCLAIMED. LIMITATION OF LIABILITY: The remedies of purchaser set forth herein are exclusive, and the total liability of OMEGA with respect to this order, whether based on contract, warranty, negligence, indemnification, strict liability or otherwise, shall not exceed the purchase price of the component upon which liability is based. In no event shall OMEGA be liable for consequential, incidental or special damages.CONDITIONS: Equipment sold by OMEGA is not intended to be used, nor shall it be used: (1) as a “Basic Component” under 10 CFR 21 (NRC), used in or with any nuclear installation or activity; or (2) in medical applications or used on humans. Should any Product(s) be used in or with any nuclear installation or activity, medical application, used on humans, or misused in any way, OMEGA assumes no responsibility as set forth in our basic WARRANTY / DISCLAIMER language, and, additionally, purchaser will indemnify OMEGA and hold OMEGA harmless from any liability or damage whatsoever arising out of the use of the Product(s) insuch a manner.FOR WARRANTY RETURNS, please have the following information available BEFORE contacting OMEGA:1. P urchase Order number under which the product was PURCHASED,2. M odel and serial number of the product under warranty, and 3. R epair instructions and/or specific problems relative to the product.FOR NON-WARRANTY REPAIRS, consult OMEGA for current repair charges. Have the following information available BEFORE contacting OMEGA:1. Purchase Order number to cover the COST of the repair,2. Model and serial number of the product, and3. R epair instructions and/or specific problems relative to the product.OMEGA’s policy is to make running changes, not model changes, whenever an improvement is possible. T his affords our customers the latest in technology and engineering. OMEGA is a registered trademark of OMEGA ENGINEERING, INC.© Copyright 2017 OMEGA ENGINEERING, INC. All rights reserved. This document may not be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine-readable form, in whole or in part, without the prior written consent of OMEGA ENGINEERING, INC.RETURN REQUESTS / INQUIRIESDirect all warranty and repair requests/inquiries to the OMEGA Customer Service Department. BEFORE RET URNING ANY PRODUCT (S) T O OMEGA, PURCHASER MUST OBT AIN AN AUT HORIZED RET URN (AR) NUMBER FROM OMEGA’S CUST OMER SERVICE DEPARTMENT (IN ORDER TO AVOID PROCESSING DELAYS). The assigned AR number should then be marked on the outside of the return package and on any correspondence.The purchaser is responsible for shipping charges, freight, insurance and proper packaging to prevent breakage in transit.***********************The information contained in this document is believed to be correct, but OMEGA accepts no liability for any errors it contains, and reserves theright to alter specifications without notice.2Servicing North America:U.S.A.Omega Engineering, Inc.Headquarters:Toll-Free: 1-800-826-6342 (USA & Canada only)Customer Service: 1-800-622-2378 (USA & Canada only) Engineering Service: 1-800-872-9436 (USA & Canada only) Tel: (203) 359-1660 Fax: (203) 359-7700 e-mail:**************For Other Locations Visit /worldwide。

TA7640中文资料

UTC TA7640AP LINEAR INTEGRATED CIRCUITUTC UNISONIC TECHNOLOGIES CO., LTD.1QW-R110-007,AAM/FM IF PROCESSORDESCRIPTIONThe UTC TA7640AP Is A Monolithic Integrated Circuit Designed For The Radios Cassette Tape Recorder.FEATURES*Low Operating Current *Low External Component *Internal AM/FM Switch*Wide Operating Voltage : Vcc=3.8VBLOCK DIAGRAMUTC TA7640AP LINEAR INTEGRATED CIRCUITUTC UNISONIC TECHNOLOGIES CO., LTD.2QW-R110-007,AABSOLUTE MAXIMUM RATINGS (Ta=25°C)PARAMETERSYMBOL VALUE UNIT VoltageVCC 8V Led Driving Current ILAMP 10mA Power Dissipation PD 750mW Operating Temperature TOPR -25 ~-+75°C Storage Temperature TSTG-55~-+150°CNOTE :Ta>25°C,6mw/°CDC ELECTRICAL CHARACTERISTICS (VCC=5V)PARAMETERSYMBOLTYP UNITAMFM Pin 1 AM Mixer Input V1 1.50V Pin 2 AM Mixer Bypass V2 1.50V Pin 3 AM Local OSC V3 2.3 2.3V Pin 4 Voltage Regulator V4 2.3 2.3V Pin 5 AM IF Out V510.9V Pin 6 Level Meter Out V610.9V Pin 7 Led Driver Output V7VPin 8 GND V800V Pin 9 Dectector V9 1.4 1.5V Pin 10 VccV1055V Pin 11 FM Decter Out V1155V Pin 12 AM IF Bypass V12 1.5 1.5V Pin 13 AM IF Input V13 1.5 1.5V Pin 14 AM IFBypass V14 1.5 1.5V Pin 15 FM IF Input V15 1.5 1.5V Pin 16 AM Mixer OutputV1655VAC ELECTRICAL CHARACTERISTICS (Ta=25°C,V CC =5V,FM;f=10.7MHz, ∆f=22.5KHz, FM=400Hz AM;f=1MHz, Mod=30%,FM=400Hz)PARAMETER SYMBOL CHART TEST CONDITIONSMIN TYP MAX UNIT Supply Current ICC(1)1FM VIN=01015mAICC(2)AM VIN=0710FMInput Limiting Voltage VIN(lim)1-3dB 4046dB µDetector Output VOD 1VIN=66dB µ5785114mVrms Signal Noise Ratio S/N 1VIN=80dB µ65dB Total Harmonic Distortion THD 1VIN=80dB µ0.05%Am RejectionAMR1VIN=80dB µ38dB µUTC TA7640AP LINEAR INTEGRATED CIRCUITUTC UNISONIC TECHNOLOGIES CO., LTD.3QW-R110-007,APARAMETER SYMBOL CHART TEST CONDITIONSMIN TYP MAX UNIT Leverl Meter Driving VoltageVM1VIN=100dB µ1.61.751.9VLed Driving Sensitivity VL1IL=1mA4652dBAM GainGV 1VIN=26dB µ203060mVrms Detector Output Voltage VOD 1VIN=60dB µ6595125mVrms Signal To Noise Ratio S/N 1VIN=60dB µ47dB Total Harmonic DistortionTHD1VIN=60dB µ1%Signal Meter Output VM 1VIN=100dB µ 1.61.75 1.9V Level Meter Driving VoltageVL1IL=1mA32dB µOscillation Stop Voltage Vstop 1RDUMP=∝ 1.5V Pin 5 Output ImpedanceR09f=1KHZ3K ΩTEST CIRCUIT。

【精品】爆破监测仪说明书

设备信息型号主机编号传感器号A灵敏度系数XYZ1 / 19B设备量程Xcm/s-—cm/sYcm/s——cm/sZcm/s—-cm/s校准时间:年月日内部校准:出厂校准:公司盖章:2 / 19目录※监测目的 (05)※传感器安装 (06)※爆破记录 (07)※结果预览 (08)※软件通讯 (09)※通用监测报告生成 (10)※爆破安全距离判定 (11)※使用注意事项 (13)※常见问题处理办法 (14)※保修条款 (16)版权所有,保留所有权利Copyright@2009成都交博科技有限公司未经成都市交博科技有限公司明确书面许可,任何单位或个人不得擅自仿(复)制、誉抄或转译本书部分或全部内容.不得以任何形式或2 / 19者任何方式(电子、机械、影印、录制或其他可能的方式)进行商品传播或用于任何商业、盈利目的.本手册所提及的产品规格和咨询仅供参考,如有内容更新,恕不另行通知,除非有特殊约定,本手册仅作为使用指导,本手册中的所有陈述、信息等均不构成任何形式的担保。

重要提示本手册只提供最基本的操作说明,如需要更高级的操作说明,请登录我们的网站()下载更详细的操作指南文档。

3 / 19●名词解释●爆破振动blastvibration爆破引起传播介质沿其平衡位置作直线或曲线往返运动的过程●质点振动速度particlexibrationvelocity爆破振动发生时的质点振动的速度●振动峰值xibrationmaxvelocity描述爆破振动的强度,即质点的最大振动速度●振动频率vibrationfrequency质点每秒钟振动的次数●振动主频mainvibrationfrequency介质质点最大振幅所对应波的频率●持续时长recordlength测点运动开始到全部停止所持续的时间●量程range量化爆破振动速度的范围(交大测振仪量程为0.0007cm/s—35.5cm/s)●记录时长duration在手动模式下,设置仪器记录爆破振动信号的时长●触发电平triggerlevel手动模式下,依靠经验预估的触发门阀,超过门阀的振动信号才能设备记录并储存3 / 19配件清单如果您购买的产品包装盒里缺少或损坏了某些部件,请及时与销售商联系。

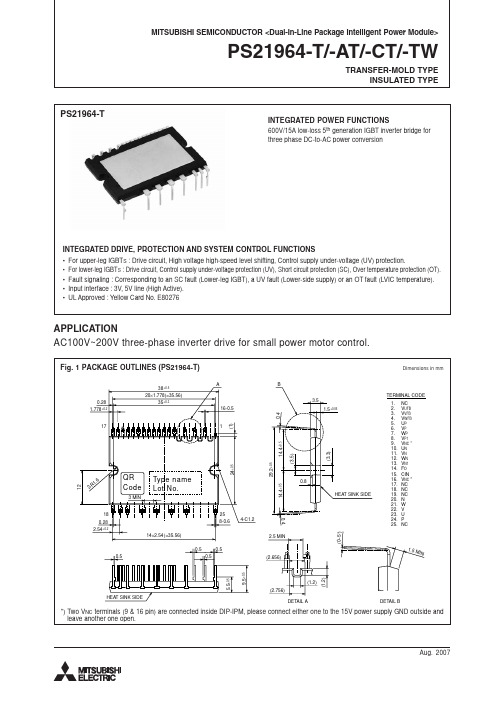

PS21964-AT中文资料

High-side input (PWM) (3V, 5V line)(Note 1, 2)

Input signal conditioning Level shifter

Protection circuit (UV)

Input signal conditioning Level shifter

Input signal conditioning Level shifter

25 8-0.6 4-C1.2

0.5 0.5 0.5 (2.656)

(0~5°)

(0~5°)

0.4

1.5 M

IN

±0.5

5.5±0.5

(1.2) (2.756) DETAIL A

HEAT SINK SIDE

(1.2)

9.5

DETAIL B

*) Two VNC terminals (9 & 16 pin) are connected inside DIP-IPM, please connect either one to the 15V power supply GND outside and leave another one open.

HEAT SINK SIDE

(1.2)

DETAIL B

*) Two VNC terminals (9 & 16 pin) are connected inside DIP-IPM, please connect either one to the 15V power supply GND outside and leave another one open.

Fig. 5 INTERNAL FUNCTIONS BLOCK DIAGRAM (TYPICAL APPLICATION EXAMPLE)

S6B0108A中文资料

CONTENTS

INTRODUCTION ............................................................................................................................................. 1 BLOCK DIAGRAM .......................................................................................................................................... 2 PIN CONFIGURATION .................................................................................................................................... 3 100 QFP.................................................................................................................................................. 3 PAD DIAGRAM (CHIP LAYOUT FOR THE 100QFP).................................................................................... 4 PAD CENTER COORDINATES (100QFP).................................................................................................. 5 100TQFP (S6B2108)................................................................................................................................. 6 PAD DIAGRAM (CHIP LAYOUT FOR THE 100TQFP).................................................................................. 7 PAD CENTER COORDINATES (100TQFP- S6B2108).................................................................................. 8 PIN DESCRIPTION ........................................................................................................................................ 9 MAXIMUM ABSOLUTE LIMIT ......................................................................................................................11 ELECTRICAL CHARACTERISTICS ................................................................................................................12 DC CHARACTERISTICS ..........................................................................................................................12 AC CHARACTERISTICS (V DD = +5V ± 10%, VSS = 0V, Ta =-30 to +85°C) ..................................................13 OPERATING PRINCIPLES AND METHODS ....................................................................................................17 I/O BUFFER ...........................................................................................................................................17 RESET...................................................................................................................................................18 DISPLAY CONTROL INSTRUCTION.............................................................................................................21 DISPLAY ON/OFF...................................................................................................................................22 STATUS READ.......................................................................................................................................23 APPLICATION CIRCUIT................................................................................................................................24 1/64 DUTY COMMON DRIVER (S6B0107) INTERFACE CIRCUIT ................................................................24 TIMING DIAGRAM (1/64 DUTY)................................................................................................................25 LCD PANEL INTERFACE APPLICATION CIRCUIT .....................................................................................26

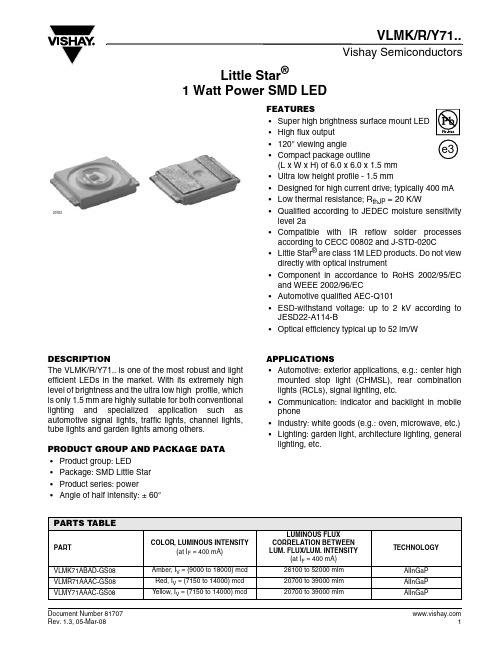

VLMK71ABAD-GS08中文资料

Vishay SemiconductorsVLMK/R/Y71..Little Star ®1 Watt Power SMD LEDFEATURES•Super high brightness surface mount LED •High flux output •120° viewing angle•Compact package outline(L x W x H) of 6.0 x 6.0 x 1.5 mm •Ultra low height profile - 1.5 mm•Designed for high current drive; typically 400 mA •Low thermal resistance; R thJP = 20 K/W•Qualified according to JEDEC moisture sensitivity level 2a •Compatible with I R reflow solder processes according to CECC 00802 and J-STD-020C•LittleStar ® are class 1M LED products. Do not view directly with optical instrument•Component in accordance to RoHS 2002/95/ECand WEEE 2002/96/EC•Automotive qualified AEC-Q101 •ESD-withstand voltage: up to 2 kV according to JESD22-A114-B•Optical efficiency typical up to 52 lm/W20783DESCRIPTIONThe VLMK/R/Y71.. is one of the most robust and light efficient LEDs in the market. With its extremely high level of brightness and the ultra low high profile, which is only 1.5 mm are highly suitable for both conventional lighting and specialized application such as automotive signal lights, traffic lights, channel lights,tube lights and garden lights among others.PRODUCT GROUP AND PACKAGE DATA •Product group: LED•Package: SMD Little Star •Product series: power•Angle of half intensity: ± 60°APPLICATIONS•Automotive: exterior applications, e.g.: center high mounted stop light (CHMSL), rear combination lights (RCLs), signal lighting, etc.•Communication: indicator and backlight in mobile phone•Industry: white goods (e.g.: oven, microwave, etc.) •Lighting: garden light, architecture lighting, general lighting, etc.PARTS TABLEPARTCOLOR, LUMINOUS INTENSITY(at I F = 400 mA)LUMINOUS FLUXCORRELATION BETWEEN LUM. FLUX/LUM. INTENSITY(at I F = 400 mA)TECHNOLOGYVLMK71ABAD-GS08Amber, I V = (9000 to 18000) mcd 26100 to 52000 mlm AlInGaP VLMR71AAAC-GS08Red, I V = (7150 to 14000) mcd 20700 to 39000 mlm AlInGaP VLMY71AAAC-GS08Y ellow, I V = (7150 to 14000) mcd20700 to 39000 mlmAlInGaPVishay SemiconductorsVLMK/R/Y71..Note:Not designed for reverse operation 1)T amb = 25°C, unless otherwise specifiedNote:1)T amb = 25°C, unless otherwise specified 2)Forward voltages are tested at a current pulse duration of 1 ms and a tolerance of ± 0.05 VNote:1)T amb = 25°C, unless otherwise specified2) Forward voltages are tested at a current pulse duration of 1 ms and a tolerance of ± 0.05 VABSOLUTE MAXIMUM RATINGS 1) VLMK71../VLMR71../VLMY71..PARAMETER TEST CONDITIONSYMBOLVALUE UNIT Forward current I F 400mA Power dissipation P tot 1120mW Junction temperature T j + 120°C Surge current t < 10 µs, d = 0.1I FM 500mA Operating temperature range T amb - 40 to + 100°C Storage temperature range T stg - 40 to + 100°C Thermal resistance junction/pinR thJP20K/WOPTICAL AND ELECTRICAL CHARACTERISTICS 1) VLMK71.., AMBERPARAMETER TEST CONDITIONPART INCLUDED TYPES SYMBOLMIN.TYP.MAX.UNIT Luminous intensity I F = 400 mA VLMK71ABADVLMK71AB l V 900011250mcd VLMK71AC l V 1125014000mcd VLMK71ADl V 1400018000mcd Dominant wavelength I F = 400 mA λd 610620nm Spectral bandwidth at 50 % I rel max I F = 400 mA Δλ18nm Angle of half intensity I F = 400 mA ϕ60deg Forward voltage 2)I F = 400 mA V F 2.22.8V Optical efficiencyI F = 400 mAηopt4052Im/WOPTICAL AND ELECTRICAL CHARACTERISTICS 1) VLMR71.., REDPARAMETER TEST CONDITIONPART INCLUDED TYPES SYMBOLMIN.TYP.MAX.UNIT Luminous intensity I F = 400 mA VLMR71AAACVLMR71AA l V 71509000mcd VLMR71AB l V 900011250mcd VLMR71ACl V 1125014000mcd Dominant wavelength I F = 400 mA λd 620630nm Spectral bandwidth at 50 % I rel max I F = 400 mA Δλ18nm Angle of half intensity I F = 400 mA ϕ60degForward voltage 2)I F = 400 mA V F 2.22.8V Optical efficiencyI F = 400 mAηopt3039Im/WVishay SemiconductorsVLMK/R/Y71..Note:1)T amb = 25°C, unless otherwise specified2) Forward voltages are tested at a current pulse duration of 1 ms and a tolerance of ± 0.05 VNote:Luminous intensity is tested at a current pulse duration of 25 ms and an accuracy of ± 11 %.The above type numbers represent the order groups which include only a few brightness groups. Only one group will be shipped on each reel (there will be no mixing of two groups on each reel).In order to ensure availability, single brightness groups will not be orderable.In a similar manner for colors where wavelength groups are measured and binned, single wavelength groups will be shipped in any one reel.In order to ensure availability, single wavelength groups will not be orderable.Note:Wavelengths are tested at a current pulse duration of 25 ms and an accuracy of ± 1 nm.Note:Forward voltages are tested at a current pulse duration of 25 ms and a tolerance of ± 0.05 V.In order to ensure availability, a single forward voltage group can not be ordered.OPTICAL AND ELECTRICAL CHARACTERISTICS 1) VLMY71.., YELLOW PARAMETER TEST CONDITION PART INCLUDED TYPES SYMBOLMIN.TYP.MAX.UNIT Luminous intensity I F = 400 mA VLMY71AAACVLMY71AAl V 71509000mcd VLMY71AB l V 900011250mcd VLMY71ACl V 1125014000mcd Dominant wavelength I F = 400 mA λd 585597nm Spectral bandwidth at 50 % I rel max I F = 400 mA Δλ15nm Angle of half intensity I F = 400 mA ϕ± 60deg Forward voltage 2)I F = 400 mA V F 2.22.8V Optical efficiencyI F = 400 mAηopt3039Im/WLUMINOUS INTENSITY/FLUX CLASSIFICATION RED/AMBER/YELLOWGROUP LUMINOUS INTENSITY I V (MCD) LUMINOUS FLUX ΦV (MLM)CORRELATION TABLE STANDARDMIN.MAX.MIN.MAX.AA 715090002070026100AB 9000112502610033000AC 11250140003300039000AD 14000180003900052000AE 18000224005200071000AF22400285007100097000COLOR CLASSIFICATIONGROUPDOM. WAVELENGTH (NM)DOM. WAVELENGTH (NM)YELLOWAMBERMIN.MAX.MIN.MAX.A 585588610616B 588591616620C 591594D594597FORWARD VOLTAGE CLASSIFICATIONGROUPFORWARD VOLTAGE (V)MIN.MAX.02 2.2 2.5032.52.8Vishay SemiconductorsVLMK/R/Y71..TYPICAL CHARACTERISTICST amb = 25°C, unless otherwise specifiedFigure 1. Relative Luminous Flux vs. Forward Current Figure 2. Relative Luminous Intensity vs. Forward CurrentFigure 3. Forward Current vs. Solder Point TemperatureFigure 4. Forward Current vs. Forward VoltageFigure5. Relative Luminous Intensity vs. Angular DisplacementVLMK/R/Y71..Vishay Semiconductors in millimetersTAPING DIMENSIONSVLMK/R/Y71..Vishay SemiconductorsPACKAGE DIMENSIONS/SOLDERING PADS DIMENSIONS in millimetersSOLDERING PROFILE(acc. to J-STD-020C)Vishay SemiconductorsVLMK/R/Y71..BAR CODE PRODUCT LABELEXAMPLE:A)Type of componentB)Manufacturing plantC)SEL - selection code (bin):e.g.:DA=code for luminous intensity group5=code for color group4=code for forward voltageD)Batch:200707 = year 2007, week 07PH19 = plant codeE)Total quantityDRY PACKINGThe reel is packed in an anti-humidity bag to protect the devices from absorbing moisture during transportation and storage.FINAL PACKINGThe sealed reel is packed into a cardboard box. A secondary cardboard box is used for shipping purposes.RECOMMENDED METHOD OF STORAGEDry box storage is recommended as soon as the aluminum bag has been opened to prevent moisture absorption. The following conditions should be observed, if dry boxes are not available:• Storage temperature 10°C to 30°C• Storage humidity ≤ 60 % RH max.After more than 672 h under these conditions moisture content will be too high for reflow soldering.In case of moisture absorption, the devices will recover to the former condition by drying under the following condition:192 h at 40°C + 5°C/- 0°C and < 5 % RH (dry air/nitrogen) or96 h at 60°C + 5°C and < 5 % RH for all device containers or24 h at 100°C + 5°C not suitable for reel or tubes. An EIA JEDEC standard JESD22-A112 level 2a label is included on all dry bags.ESD PRECAUTIONProper storage and handling procedures should befollowed to prevent ESD damage to the devicesespecially when they are removed from the antistaticshielding bag. Electro-static sensitive devices warninglabels are on the packaging.VISHAY SEMICONDUCTORS STANDARDBAR CODE LABELSThe Vishay Semiconductors standard bar code labelsare printed at final packing areas. The labels are oneach packing unit and contain Vishay Semiconductorsspecific data.ACBDE20613VLMK/R/Y71..Vishay SemiconductorsOZONE DEPLETING SUBSTANCES POLICY STATEMENTIt is the policy of Vishay Semiconductor GmbH to1.Meet all present and future national and international statutory requirements.2.Regularly and continuously improve the performance of our products, processes, distribution and operatingsystems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.Vishay Semiconductor GmbH has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.1.Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively.2.Class I and I I ozone depleting substances in the Clean Air Act Amendments of 1990 by the EnvironmentalProtection Agency (EPA) in the USA.3.Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively. Vishay Semiconductor GmbH can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.The I EC/EN standards require that the desired classification Accessible Emission Limit shall not be exceeded in “Normal” and “Single Fault Conditions”. This product is in Compliance with the requirement in CEN/IEC/EN60825-1 to ensure that required classifications are not exceeded in single fault conditions.We reserve the right to make changes to improve technical designand may do so without further notice.Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use Vishay Semiconductors products for any unintended or unauthorized application, the buyer shall indemnify Vishay Semiconductors against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associated with suchunintended or unauthorized use.Vishay Semiconductor GmbH, P.O.B. 3535, D-74025 Heilbronn, GermanyDisclaimer Legal Disclaimer NoticeVishayAll product specifications and data are subject to change without notice.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, “Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.Product names and markings noted herein may be trademarks of their respective owners.元器件交易网。

机床手册-补充部分-DMC64V

我们希望您能够顺利正确地操作 DECKEL MAHO 机床。 此致

DECKEL MAHO Geretsried 股份有限公司

机床的最终用途

基础:

规定 DECKEL MAHO DMC 系列加工中心最终用途。

您购买的 DECKEL MAHO 加工中心采用最新技术制造并符合所有公认 的安全法规、标准和技术规格。

1-5

工作范围

键锁开关

位置 0 位置 1 位置 2 位置 3 参见西门子控制装置手册

轴移动长度

所示所有值均为公里

轴1 轴2 轴3 轴4 轴5 轴6 轴7 轴8 轴9 轴 10 轴 11 轴 12

半熟练操作者 熟练操作者 特别胜任工作的操作者 编程员,机床调整工

X轴 Y1 轴 Z轴 A1 轴 刀库 1 主轴 Y2 轴 A2 轴 刀库 2 未指定 未指定 未指定

用户数据

关闭开关

液压油压力设置 重刀具 门打开时使用润滑冷却剂 无人加工 用自动程序选择交换托盘

关闭开关(“省电”)通/断 在静止 20 分钟后机床驱动自动断开。 该功能具有等同紧急停止的效应。 在重新起动机床之前断开关闭开关。

激活液压工件夹紧 减速旋转运行转盘式刀库 工作区门打开时供应润滑冷却剂 (低压)通/断 无人看管运行通/断 自动程序选择托盘交换通/断

机床的操作可涉及不可预见的危险, 包括:

人员生命和四肢危险; 机床和公司或用户其他资产损坏的危险。

环境,水 源保护

本手册中所述的机床是一种生产、加工和可能使用水污染物质的设备。

这意味着无论何时操作、关闭或拆卸机床或其任何部件时,都必须遵守 用户所在国水资源保护或类似立法方面的法律和法规要求。详细资讯见 管辖可能使用水污染物质的适用国家或地方法规。

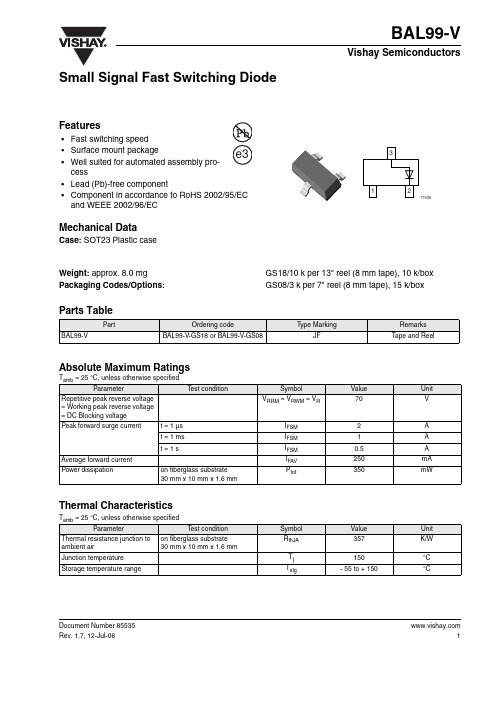

BAL99-V-GS08中文资料

BAL99-VDocument Number 85535Rev. 1.7, 12-Jul-06Vishay Semiconductors1Small Signal Fast Switching DiodeFeatures•Fast switching speed •Surface mount package•Well suited for automated assembly pro-cess•Lead (Pb)-free component•Component in accordance to RoHS 2002/95/EC and WEEE 2002/96/ECMechanical DataCase: SOT23 Plastic caseWeight: approx. 8.0 mgPackaging Codes/Options:GS18/10 k per 13" reel (8 mm tape), 10 k/box GS08/3 k per 7" reel (8 mm tape), 15 k/boxParts TableAbsolute Maximum RatingsT amb = 25°C, unless otherwise specifiedThermal CharacteristicsT amb = 25°C, unless otherwise specifiedPartOrdering codeType MarkingRemarks BAL99-VBAL99-V-GS18 or BAL99-V-GS08JFTape and ReelParameterT est conditionSymbol Value Unit Repetitive peak reverse voltage = Working peak reverse voltage = DC Blocking voltage V RRM = V RWM = V R70VPeak forward surge currentt = 1 µs I FSM 2A t = 1 ms I FSM 1A t = 1 sI FSM 0.5A Average forward current I FAV 250mA Power dissipationon fiberglass substrate 30 mm x 10 mm x 1.6 mmP tot350mWParameterT est conditionSymbol Value Unit Thermal resistance junction to ambient airon fiberglass substrate 30 mm x 10 mm x 1.6 mmR thJA 357K/W Junction temperature T j 150°C Storage temperature rangeT stg- 55 to + 150°C 2Document Number 85535Rev. 1.7, 12-Jul-06BAL99-VVishay Semiconductors Electrical CharacteristicsT amb = 25°C, unless otherwise specifiedPackage Dimensions in mm (Inches): SOT23ParameterTest conditionSymbol MinTyp.Max Unit Forward voltageI F = 1 mA V F 715mV I F = 10 mA V F 855mV I F = 50 mA V F 1000mV I F = 150 mAV F 1250mV Reverse currentV R = 70 VI R 2.5µA V R = 70 V , T j = 150°C I R 100µA V R = 25 V , T j = 150°CI R 30µA Diode capacitance V F = V R = 0, f = 1 MHz C D 1.5pF Reverse recovery timeI F = I R = 10 mA to I R = 1 mA, R L = 100 Ω, V R = 6 Vt rr6nsBAL99-VDocument Number 85535Rev. 1.7, 12-Jul-06Vishay Semiconductors3Ozone Depleting Substances Policy StatementIt is the policy of Vishay Semiconductor GmbH to1.Meet all present and future national and international statutory requirements.2.Regularly and continuously improve the performance of our products, processes, distribution and operating systems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.Vishay Semiconductor GmbH has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.1.Annex A, B and list of transitional substances of the Montreal Protocol and the L ondon Amendments respectively2.Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental Protection Agency (EPA) in the USA3.Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.Vishay Semiconductor GmbH can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.We reserve the right to make changes to improve technical designand may do so without further notice.Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use Vishay Semiconductors products for any unintended or unauthorized application, the buyer shall indemnify Vishay Semiconductors against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personaldamage, injury or death associated with such unintended or unauthorized use.Vishay Semiconductor GmbH, P.O.B. 3535, D-74025 Heilbronn, GermanyDocument Number: 91000Revision: 18-Jul-081DisclaimerLegal Disclaimer NoticeVishayAll product specifications and data are subject to change without notice.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, “Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.Product names and markings noted herein may be trademarks of their respective owners.元器件交易网。

美格64使用说明书

美格—64使用说明书尊敬的用户您好!感谢您选用美格64系列产品。

本控制器功能超级一流,性能卓越优异,界面赏心悦目,软件操作设定及选项全中文设计;液晶屏采用蓝底白字四行八位显示模式,比黄绿屏更为美观大方。

高低级功能选择让您的控制方式更加灵活自主,直观的操作方式无须说明书片刻即可轻松完成设定。

简述其功能特点如下:1.专家自整定+模糊控制方式,更符合供水控制特点。

2.高低级功能设置,特殊场合亦可满足复杂要求。

3.界面美观,操作直观。

全中文显示,无底层代码,无说明书也能自如设定应用。

4.实时时间、目标值、频率、各泵状态、型号均可同步显示;定时换泵倒计时、巡检倒计时、公司信息、电话、消防、变频故障等等一目了然。

5.超压保护、断线报警可选;稳压巡检、无压巡检可选,控制更为安全。

6.双恒压可选,可通过开关量设定稳压值。

7.多达八时段压力控制,且每时段内均可进行任意压力设定控制及实现定时开关机功能。

8.节能智能休眠模式,主泵、小泵皆可休眠,小泵变量亦可休眠。

压力提升休眠模式,并可控制小泵进休眠状态时间。

9.大小泵优先选项,定时换泵,正负反馈功能。

10.灵活的消防及巡检组合方式,自动显示消防型号。

11.消防泵巡检间隔及时长可随意设定,消防泵故障后自动转工频运引,符合公安部最新302标准。

12.自动抑制表头抖动及系统振荡,让系统更稳定,模拟输出增益更宽可调。

13.故障记忆功能,自动记录当前10条故障信息。

14.真正的在线编程功能,擦写随意,设定时无需掉电确认。

15.软件锁及数据初始化功能。

16.超压输出设专用接点,巡检泄压阀设专用接点,方便简化外部应用电路设计。

17.独一无二的软着陆功能。

即便在循环软起的系统当中,也可获得减速停车的平稳效果。

有效抑制水锤。

18 独一无二的传感器短路错线指示功能。

接线更为安全19 个性化设计可满足用户的特殊需求。

20.强大的密匙预约功能,免除您的后顾之忧。

面板及操作说明1.面板显示分为上排数码管及下排液晶屏显示两部分。

GS8640ZV36GT-167资料