3STM32F10x简介-精选文档

STM32F10xxx 寄存器--详细说明

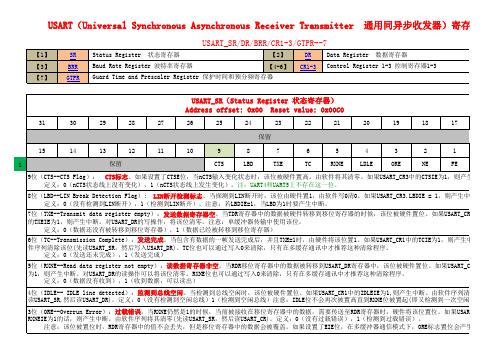

1位(RWU--Receiver wakeup):接收唤醒。该位用来决定是否把USART置于静默模式。该位由软件设置或清除。当唤醒序列到来时,硬件也会将其清零。 定义:0(接收器处于正常工作模式),1(接收器处于静默模式)。【注意】:1.在把USART置于静默模式(设置RWU位)之前,USART要已经先接收了一个数据字节 否则在静默模式下,不能被空闲总线检测唤醒。2.当配置成地址标记检测唤醒(WAKE位=1),在RXNE位被置位时,不能用软件修改RWU位。

DIV_Mantissa[11:0]

DIV_Fraction[3:0]

15-4位(DIV_Mantissa[11:0]--Mantissa of USARTDIV):USARTDIV的整数部分。这12位定义了USART分频器除法因子(USARTDIV)的整数部分。 3-0位(DIV_Fraction[3:0]--Fraction of USARTDIV):USARTDIV的小数部分。这4位定义了USART分频器除法因子(USARTDIV)的小数部分。

USART(Universal Synchronous Asynchronous Receiver Transmitter

USART_SR/DR/BRR/CR1-3/GTPR--7

【1】 【3】 【7】 SR BRR GTPR Status Register 状态寄存器 【2】 【4-6】 DR CR1-3

USART_DR(Data Register 数据寄存器) Addr offset: 0x04 Reset value: Undefined

31 30 29 28 27 26 25 24 保留 15 2 14 13 12 保留 11 10 9 8 7 6 5 4 DR[8:0] 3 2 1 23 22 21 20 19 18 17

第1章 STM32F10X系统介绍

功能简介(续)

• 多种外设接口

– ADC:2路12位(16通道); 通道); : 路 位 通道 – DMA:7通道 : 通道 – 定时器:共7个,包括6路PWM,2路16位看 个 包括 路 定时器: , 路 位看 门狗等 – 通信接口: 通信接口: • 2个I2C; 个 ; • 3个USART 个 • 2个SPI; 个 ; • CAN接口; 接口; 接口 • USB接口 接口 • JTAG

1.2.2 STM32F10X 主系统各单元的含义

• 1. ICode 总线 • 该总线将 Cortex-M3 内核的指令总线与 Flash 指 令接口相连接,指令的预取在此总线上完成。 • 2. DCode 总线 • 该总线将 Cortex-M3 内核的 DCode 总线与闪存 存储器的数据接口相连接(常量加载和调试访问)。

512kB to come in 2008

Power Supply

Reg 1.8V

POR/PDR/PVD

XTAL oscillators Up to 20kB SRAM

64kB to come in 2008 32KHz + 4~16MHz

JTAG/SW Debug Nested vect IT Ctrl 1x Systic Timer

Cortex-M3 处理器具有以下优势:

• • • • • 小的处理器内核、系统和存储器,可降低器件成本; 完整的电源管理,很低的功耗; 突出的处理器性能,可满足挑战性的需要; 快速的中断处理,满足高速、临界的控制需求; 可选的存储器保护单元( MPU ),提供平台级的安 全性; • 增强的系统调试功能,可加快开发进程; • 没有汇编代码要求,简化系统开发; • 宽广的适应范围:从超低成本的微控制器到高性能 的 SoC。

STM32低功耗模式简介

STM32低功耗模式简介STM32F10xxx 有三中低功耗模式:●睡眠模式(Cortex?-M3 内核停止,外设仍在运行)●停止模式(所有的时钟都以停止)●待机模式(1.8V 电源关闭)时钟频率72MHz 时,从闪存执行代码,STM32 功耗36mA,是32 位市场上功耗最低的产品,相当于0.5mA/MHz。

上电,默认使用内部HSI 时钟8M,经测试10mA 左右。

待机模式可实现系统的最低功耗。

可将电流消耗降至两微安。

在待机模式下,所有的I/O 引脚处于高阻态,除了以下的引脚:●复位引脚(始终有效)●当被设置为防侵入或校准输出时的TAMPER 引脚●被使能的唤醒引脚/*按钮GPIOB9 进入睡眠,WKUP pin(GPIOA0)唤醒,GPIOD3-LED 200ms闪烁*/int main(void){ /* System Clocks Configuration**********************************************/ RCC_Configuration();GPIO_Configuration();/* Enable PWR and BKP clock */ RCC_APB1PeriphClockCmd(RCC_APB1Periph_PWR | RCC_APB1Periph_BKP, ENABLE);/* Enable WKUP pin */ PWR_WakeUpPinCmd(ENABLE);/* Allow access to BKP Domain */ PWR_BackupAccessCmd(ENABLE);//RTC_Configuration();EXTI_Configuration();NVIC_Configuration();SysTick_Config(SystemFrequency / 1000 *200 ); //200ms。

4.1.STM32F10x系列芯片的命名、资源与引脚

STM32F10X系列芯片的命名、资源与引脚 芯片资源

外设 GPIO端口 12位ADC模块 (通道数) 12位DAC转换器 (通道数) CPU频率 工作电压

工作温度

封装形式

STM32F103RX 51

3(16)

STM32F103VX 80

外设 闪存(k字节) SRAM(k字节)

FSMC(静态储存器控制器)定通用时

高级控制

器

基本

SPI(I2S)

I2C 通 信 USART/UART

接

USB

口

CAN

SDIO

STM32F103RX

STM32F103VX

STM32F103ZX

256 384 512 256 384 512 256 384 512

3(16)

STM32F103ZX 112

3(21)

2(2)

72MHz 2.0~3.6V 环境温度:-40℃~+85℃/-40℃~+105℃ 结温度:-40℃~+125℃ LQFP64,WLCSP64 LQFP100,BGA100 LQFP144,BGA144

STM32F10X系列芯片的命名、资源与引脚

STM32F10X系列芯片的命名、资源与引脚

芯片引脚

以STM32F103VCT6为例:共100pin

GPIO共80pin PA0~15 PB0~15 PE0~15

PC0~15

PD0~15

5组电源、接地共10pin

AD变换的电源1组 VDDA(22) VSSA(19)

2pin

参考电压1组

VREF+(21) VREF-

STM32F10X系统介绍幻灯片课件

STM32F103VE STM32F101VE

STM32F103VD STM32F101VD STM32F103VC STM32F101VC

STM32F103ZE STM32F101ZE

STM32F103ZD STM32F101ZD STM32F103ZC STM32F101ZC

128 K

64 K 32 K 0K

– ARM 32位的CortexM3™CPU

– 72MHz,高达90DMips, 1.25DMips/MHz

– 单周期硬件乘法和除法—— 加快计算

• 存储器

– 从32K字节至128K字节闪存 程序存储器

– 从6K字节至20K字节SRAM – 多重自举功能

与之比较的16位DSP TMS320LF2407

1.1.1 ARM Cortex-M3 处理器简介

• Cortex-M3 处理器使用了ARM v7-M 体系结 构。它包含了一个高效的哈佛结构的三级 流水线,可提供 1.25 DMIPS/MHz 的性能。

• Cortex-M3 处理器采用了与系统部件紧偶合 的实现方法,来缩小芯片的面积,CortexM3 处理器实现了 Thumb-2指令集构架,具 有很高的代码密度,可降低存储器的需要, 并能达到非常接近 32 位 ARM指令集的性 能。

Cortex-M3 处理器具有以下优势:

• 小的处理器内核、系统和存储器,可降低器件成本; • 完整的电源管理,很低的功耗; • 突出的处理器性能,可满足挑战性的需要; • 快速的中断处理,满足高速、临界的控制需求; • 可选的存储器保护单元( MPU ),提供平台级的安

全性; • 增强的系统调试功能,可加快开发进程; • 没有汇编代码要求,简化系统开发; • 宽广的适应范围:从超低成本的微控制器到高性能

stm32f10x参考手册

STM32F10x参考手册第一版STM32F10x参考手册1文档中的约定 (1)1.1寄存器描述中使用的缩写列表 (1)2存储器和总线构架 (2)2.1系统构架 (2)2.2存储器组织 (3)2.3存储器映像 (4)2.3.1外设存储器映像 (5)2.3.2嵌入式SRAM (6)2.3.3位段 (6)2.3.4嵌入式闪存 (6)2.4启动配置 (8)3电源控制(PWR) (9)3.1电源 (9)3.1.1独立的A/D转换器供电和参考电压 (9)3.1.2电池备份 (9)3.1.3电压调节器 (10)3.2电源管理器 (10)3.2.1上电复位(POR)和掉电复位(PDR) (10)3.2.2可编程电压监测器(PVD) (10)3.3低功耗模式 (11)3.3.1降低系统时钟 (12)3.3.2外部时钟的控制 (12)3.3.3睡眠模式 (12)3.3.4停止模式 (13)3.3.5待机模式 (14)3.3.6低功耗模式下的自动唤醒(AWU) (15)3.4电源控制寄存器 (16)3.4.1电源控制寄存器(PWR_CR) (16)3.4.2电源控制/状态寄存器 (17)3.5PWR寄存器映像 (18)4复位和时钟控制 (19)4.1复位 (19)4.1.1系统复位 (19)4.1.2电源复位 (19)4.2时钟 (20)4.2.1HSE时钟 (22)4.2.2HSI时钟 (22)4.2.3PLL (23)4.2.4LSE时钟 (23)4.2.5LSI时钟 (23)4.2.6系统时钟(SYSCLK)选择 (24)4.2.7时钟安全系统(CSS) (24)4.2.8RTC时钟 (24)4.2.9看门狗时钟 (24)4.2.10时钟输出 (25)4.3RCC寄存器描述 (26)4.3.1时钟控制寄存器(RCC_CR) (26)4.3.2时钟配置寄存器(RCC_CFGR) (27)4.3.3时钟中断寄存器 (RCC_CIR) (29)4.3.4APB2外设复位寄存器 (RCC_APB2RSTR) (32)4.3.5APB1外设复位寄存器 (RCC_APB1RSTR) (33)4.3.6AHB外设时钟使能寄存器 (RCC_AHBENR) (35)4.3.7APB2外设时钟使能寄存器(RCC_APB2ENR) (36)4.3.8APB1外设时钟使能寄存器(RCC_APB1ENR) (37)4.3.9备份域控制寄存器 (RCC_BDCR) (39)4.3.10控制/状态寄存器 (RCC_CSR) (40)4.4RCC寄存器映像 (43)5通用和复用功能I/O(GPIO和AFIO) (44)5.1GPIO功能描述 (44)5.1.1通用I/O(GPIO) (45)5.1.2单独的位设置或位清除 (45)5.1.3外部中断/唤醒线 (46)5.1.4复用功能(AF) (46)5.1.5软件重新映射I/O复用功能 (46)5.1.6GPIO锁定机制 (46)5.1.7输入配置 (46)5.1.8输出配置 (47)5.1.9复用功能配置 (48)5.2GPIO寄存器描述 (50)5.2.1端口配置低寄存器(GPIOx_CRL) (x=A..E) (50)5.2.2端口配置高寄存器(GPIOx_CRH) (x=A..E) (51)5.2.3端口输入数据寄存器(GPIOx_IDR) (x=A..E) (52)5.2.4端口输出数据寄存器(GPIOx_ODR) (x=A..E) (52)5.2.5端口位设置/复位寄存器(GPIOx_BSRR) (x=A..E) (53)5.2.6端口位复位寄存器(GPIOx_BRR) (x=A..E) (53)5.2.7端口配置锁定寄存器(GPIOx_LCKR) (x=A..E) (54)5.3复用功能I/O和调试配置(AFIO) (55)5.3.1把OSC_IN/OSC_OUT引脚作为GPIO端口PD0/PD1 (55)5.3.2BXCAN复用功能重映射 (55)5.3.3JTAG/SWD复用功能重映射 (55)5.3.4定时器复用功能重映射 (56)5.3.5USART复用功能重映射 (57)5.3.6I2C 1 复用功能重映射 (58)5.3.7SPI 1复用功能重映射 (58)5.4AFIO寄存器描述 (59)5.4.1复用重映射和调试I/O配置寄存器(AFIO_MAPR) (60)5.4.2外部中断配置寄存器1(AFIO_EXTICR1) (62)5.4.3外部中断配置寄存器2(AFIO_EXTICR2) (62)5.4.4外部中断配置寄存器3(AFIO_EXTICR3) (63)5.4.5外部中断配置寄存器4(AFIO_EXTICR4) (63)5.5GPIO 和AFIO寄存器地址映象 (64)5.5.1GPIO寄存器地址映象 (64)5.5.2AFIO寄存器地址映象 (65)6中断和事件 (66)6.1嵌套向量中断控制器(NVIC) (66)6.1.1系统嘀嗒(SysTick)校准值寄存器 (66)6.1.2中断和异常向量 (66)6.2外部中断/事件控制器(EXTI) (68)6.2.1主要特性 (68)6.2.2框图 (69)6.2.3唤醒事件管理 (69)6.2.4功能说明 (69)6.2.5外部中断/事件线路映像 (71)6.3EXTI 寄存器描述 (72)6.3.1外部中断/事件寄存器映像 (75)7DMA 控制器(DMA) (76)7.1简介 (76)7.2主要特性 (76)7.3功能描述 (77)7.3.1DMA处理 (77)7.3.2仲裁器 (77)7.3.3DMA 通道 (78)7.3.4错误管理 (79)7.3.5DMA请求映像 (79)7.4DMA寄存器 (82)7.4.1DMA中断状态寄存器(DMA_ISR) (82)7.4.2DMA中断标志清除寄存器(DMA_IFCR) (82)7.4.3DMA通道x配置寄存器(DMA_CCRx)(x = 1...7).. (83)7.4.4DMA通道x传输数量寄存器(DMA_CNDTRx)(x = 1...7) (85)7.4.5DMA通道x外设地址寄存器(DMA_CPARx)(x = 1...7).. (85)7.4.6DMA通道x存储器地址寄存器(DMA_CPARx)(x = 1...7).. (85)7.5DMA寄存器映像 (86)8实时时钟(RTC) (88)8.1简介 (88)8.2主要特性 (88)8.3功能描述 (88)8.3.1概述 (88)8.3.2复位过程 (90)8.3.3读RTC寄存器 (90)8.3.4配置RTC寄存器 (90)8.3.5RTC标志的设置 (90)8.4RTC寄存器描述 (91)8.4.1RTC控制寄存器高位(RTC_CRH) (91)8.4.2RTC控制寄存器低位(RTC_CRL) (92)8.4.3RTC预分频装载寄存器(RTC_PRLH/RTC_PRLL) (93)8.4.4RTC预分频分频因子寄存器(RTC_DIVH / RTC_DIVL) (94)8.4.5RTC计数器寄存器 (RTC_CNTH / RTC_CNTL) (95)8.4.6RTC闹钟寄存器(RTC_ALRH/RTC_ALRL) (95)8.5RTC寄存器映像 (97)9备份寄存器(BKP) (98)9.1简介 (98)9.2特性 (98)9.3侵入检测 (98)9.4RTC校准 (98)9.5BKP寄存器描述 (99)9.5.1备份数据寄存器x(BKP_DRx) (x = 1 ... 10) (99)9.5.2RTC时钟校准寄存器(BKP_RTCCR) (99)9.5.3备份控制寄存器(BKP_CR) (99)9.5.4备份控制/状态寄存器(BKP_CSR) (100)9.6BKP寄存器映像 (101)10独立看门狗(IWDG) (103)10.1简介 (103)10.1.1硬件看门狗 (103)10.1.2寄存器访问保护 (103)10.1.3调试模式 (104)10.2IWDG寄存器描述 (104)10.2.1键寄存器(IWDG_KR) (104)10.2.2预分频寄存器(IWDG_PR) (105)10.2.3重装载寄存器(IWDG_RLR) (106)10.2.4状态寄存器(IWDG_SR) (106)10.3IWDG寄存器映像 (107)11窗口看门狗(WWDG) (108)11.1简介 (108)11.2主要特性 (108)11.3功能描述 (108)11.4如何编写看门狗超时程序 (109)11.5调试模式 (110)11.6寄存器描述 (111)11.6.1控制寄存器(WWDG_CR) (111)11.6.2配置寄存器(WWDG_CFR) (111)11.6.3状态寄存器(WWDG_SR) (112)11.7WWDG寄存器映像 (113)12高级控制定时器(TIM1) (114)12.1简介 (114)12.2主要特性 (114)12.3框图 (115)12.4功能描述 (116)12.4.1时基单元 (116)12.4.2计数器模式 (117)12.4.3重复向下计数器 (125)12.4.4时钟选择 (126)12.4.5捕获/比较通道 (129)12.4.6输入捕获模式 (131)12.4.7PWM输入模式 (132)12.4.8强置输出模式 (132)12.4.9输出比较模式 (133)12.4.10PWM 模式 (134)12.4.11互补输出和死区插入 (136)12.4.12使用刹车功能 (138)12.4.13在外部事件时清除OCxREF信号 (139)12.4.14六步PWM的产生 (140)12.4.15单脉冲模式 (141)12.4.16编码器接口模式 (143)12.4.17定时器输入异或功能 (144)12.4.18与霍尔元件的接口 (145)12.4.19定时器和外部触发的同步 (146)12.4.20定时器同步 (149)12.4.21调试模式 (149)12.5TIM1寄存器描述 (150)12.5.1控制寄存器1(TIM1_CR1) (150)12.5.2控制寄存器2(TIM1_CR2) (151)12.5.3从模式控制寄存器(TIM1_SMCR) (153)12.5.4DMA/中断使能寄存器(TIM1_DIER) (154)12.5.5状态寄存器(TIM1_SR) (156)12.5.6事件产生寄存器(TIM1_EGR) (157)12.5.7捕获/比较模式寄存器1(TIM1_CCMR1) (158)12.5.8捕获/比较模式寄存器2(TIM1_CCMR2) (161)12.5.10计数器(TIM1_CNT) (165)12.5.11预分频器(TIM1_PSC) (165)12.5.12自动重装载寄存器(TIM1_ARR) (165)12.5.13周期计数寄存器(TIM1_RCR) (166)12.5.14捕获/比较寄存器1(TIM1_CCR1) (166)12.5.15捕获/比较寄存器2(TIM1_CCR2) (167)12.5.16捕获/比较寄存器3(TIM1_CCR3) (167)12.5.17捕获/比较寄存器(TIM1_CCR4) (168)12.5.18刹车和死区寄存器(TIM1_BDTR) (168)12.5.19DMA控制寄存器(TIM1_DCR) (170)12.5.20连续模式的DMA地址(TIM1_DMAR) (170)12.6TIM1寄存器图 (171)13通用定时器(TIMx) (173)13.1概述 (173)13.2主要特性 (173)13.3框图 (174)13.4功能描述 (175)13.4.1时基单元 (175)13.4.2计数器模式 (176)13.4.3时钟选择 (183)13.4.4捕获/比较通道 (185)13.4.5输入捕获模式 (187)13.4.6PWM输入模式 (187)13.4.7强置输出模式 (188)13.4.8输出比较模式 (188)13.4.9PWM 模式 (189)13.4.10单脉冲模式 (191)13.4.11在外部事件时清除OCxREF信号 (193)13.4.12编码器接口模式 (193)13.4.13定时器输入异或功能 (195)13.4.14定时器和外部触发的同步 (195)13.4.15定时器同步 (198)13.4.16调试模式 (202)13.5TIMx寄存器描述 (203)13.5.2控制寄存器2(TIMx_CR2) (205)13.5.3从模式控制寄存器(TIMx_SMCR) (206)13.5.4DMA/中断使能寄存器(TIMx_DIER) (207)13.5.5状态寄存器(TIMx_SR) (209)13.5.6事件产生寄存器(TIMx_EGR) (211)13.5.7捕获/比较模式寄存器1(TIMx_CCMR1) (212)13.5.8捕获/比较模式寄存器2(TIMx_CCMR2) (215)13.5.9捕获/比较使能寄存器(TIMx_CCER) (216)13.5.10计数器(TIMx_CNT) (218)13.5.11预分频器(TIMx_PSC) (218)13.5.12自动重装载寄存器(TIMx_ARR) (218)13.5.13捕获/比较寄存器1(TIMx_CCR1) (219)13.5.14捕获/比较寄存器2(TIMx_CCR2) (220)13.5.15捕获/比较寄存器3(TIMx_CCR3) (220)13.5.16捕获/比较寄存器(TIMx_CCR4) (221)13.5.17DMA控制寄存器(TIMx_DCR) (221)13.5.18连续模式的DMA地址(TIMx_DMAR) (222)13.6TIMx寄存器图 (223)14控制器局域网(bxCAN) (225)14.1简介 (225)14.2主要特点 (225)14.3总体描述 (225)14.3.1CAN 2.0B内核 (226)14.3.2控制、状态和配置寄存器 (226)14.3.3发送邮箱 (226)14.3.4接收过滤器 (226)14.3.5接收FIFO (227)14.4工作模式 (228)14.4.1初始化模式 (228)14.4.2正常模式 (228)14.4.3睡眠模式(低功耗) (228)14.4.4测试模式 (229)14.4.5静默模式 (229)14.4.6环回模式 (229)14.4.7环回静默模式 (230)14.5功能描述 (230)14.5.1发送处理 (230)14.5.2时间触发通信模式 (232)14.5.3接收管理 (232)14.5.4标识符过滤 (234)14.5.5报文存储 (238)14.5.6出错管理 (239)14.5.7位时间特性 (239)14.6中断 (241)14.7寄存器访问保护 (243)14.8CAN 寄存器描述 (243)14.8.1控制和状态寄存器 (243)14.8.2邮箱寄存器 (255)14.8.3CAN过滤器寄存器 (260)14.9bxCAN寄存器列表 (264)15I2C接口 (267)15.1介绍 (267)15.2主要特点 (267)15.3概述 (268)15.4功能描述 (269)15.4.1I2C从模式 (269)15.4.2I2C主模式 (271)15.4.3错误条件 (274)15.4.4SDA/SCL线控制 (275)15.4.5SMBus (275)15.4.6DMA请求 (277)15.4.7包错误校验(PEC) (278)15.5中断请求 (279)15.6I2C寄存器描述 (281)15.6.1控制寄存器1(I2C_CR1) (281)15.6.2控制寄存器2(I2C_CR2) (283)15.6.3自身地址寄存器1 (I2C_OAR1) (284)15.6.4自身地址寄存器2(I2C_OAR2) (285)15.6.5数据寄存器(I2C_DR) (285)15.6.6状态寄存器1(I2C_SR1) (285)15.6.7状态寄存器2 (I2C_SR2) (288)15.6.8时钟控制寄存器(I2C_CCR) (289)15.6.9TRISE寄存器(I2C_TRISE) (290)15.7I2C寄存器地址映象 (291)16串行外设接口(SPI) (292)16.1简介 (292)16.2主要特征 (292)16.3功能描述 (292)16.3.1概述 (292)16.3.2SPI从模式 (295)16.3.3SPI主模式 (296)16.3.4单向通信 (297)16.3.5状态标志 (297)16.3.6CRC计算 (298)16.3.7利用DMA的SPI通信 (299)16.3.8错误标志 (299)16.3.9中断 (300)16.4SPI寄存器描述 (300)16.4.1SPI控制寄存器1(SPI_CR1) (300)16.4.2SPI控制寄存器2(SPI_CR2) (302)16.4.3SPI 状态寄存器(SPI_SR) (303)16.4.4SPI 数据寄存器(SPI_DR) (304)16.4.5SPI CRC多项式寄存器(SPI_CRCPR) (304)16.4.6SPI Rx CRC寄存器(SPI_RXCRCR) (305)16.4.7SPI Tx CRC寄存器(SPI_TXCRCR) (305)16.5SPI 寄存器地址映象 (306)17USART收发器(USART) (307)17.1介绍 (307)17.2概述 (308)17.2.1框图 (309)17.2.2USART 特征描述 (310)17.2.3发送器 (310)17.2.4接收器 (312)17.2.5分数波特率的产生 (315)17.2.617.2.6 多处理器通信 (316)17.2.7校验控制 (317)17.2.8LIN(局域互联网)模式 (318)17.2.9USART 同步模式 (320)17.2.10单线半双工通信 (322)17.2.11智能卡 (322)17.2.12IrDA SIR ENDEC 功能块 (324)17.2.13利用DMA连续通信 (325)17.2.14硬件流控制 (326)17.3中断请求 (327)17.4USART寄存器描述 (329)17.4.1状态寄存器(USART_SR) (329)17.4.2数据寄存器(USART_DR) (330)17.4.3波特比率寄存器(USART_BRR) (331)17.4.4控制寄存器1 (USART_CR1) (331)17.4.5控制寄存器2(USART_CR2) (333)17.4.6控制寄存器3(USART_CR3) (335)17.4.7保护时间和预分频寄存器(USART_GTPR) (336)17.5USART寄存器地址映象 (338)18USB全速设备接口(USB) (339)18.1导言 (339)18.2主要特征 (339)18.3方框图 (339)18.4功能描述 (340)18.4.1USB功能模块描述 (341)18.5编程中需要考虑的问题 (342)18.5.1通用USB设备编程 (342)18.5.2系统复位和上电复位 (342)18.5.3双缓冲端点 (346)18.5.4同步传输 (347)18.5.5挂起/恢复事件 (348)18.6USB寄存器描述 (350)18.6.1通用寄存器 (350)18.6.2端点寄存器 (355)18.6.3缓冲区描述表 (358)18.7USB寄存器映像 (361)19模拟/数字转换(ADC) (363)19.1介绍 (363)19.2主要特征 (363)19.3引脚描述 (365)19.4功能描述 (365)19.4.1ADC开关控制 (365)19.4.2ADC时钟 (365)19.4.3通道选择 (365)19.4.4单次转换模式 (366)19.4.5连续转换模式 (366)19.4.6时序图 (367)19.4.7模拟看门狗 (368)19.4.8扫描模式 (368)19.4.9注入通道管理 (369)19.4.10间断模式 (369)19.5校准 (370)19.6数据对齐 (371)19.7可编程的通道采样时间 (371)19.8外部触发转换 (371)19.9DMA请求 (372)19.10双ADC模式 (372)19.10.1同时注入模式 (374)19.10.2同时规则模式 (374)19.10.3快速交替模式 (375)19.10.4慢速交替模式 (375)19.10.5交替触发模式 (376)19.10.6独立模式 (377)19.10.7混合的规则/注入同步模式 (377)19.10.8混合的同步规则+交替触发模式 (377)19.10.9混合同步注入+交替模式 (378)19.11温度传感器 (378)19.12中断 (379)19.13ADC寄存器描述 (381)19.13.1ADC状态寄存器(ADC_SR) (381)19.13.2ADC控制寄存器1(ADC_CR1) (382)19.13.3ADC控制寄存器2(ADC_CR2) (384)19.13.4ADC采样时间寄存器1(ADC_SMPR1) (387)19.13.5ADC采样时间寄存器2(ADC_SMPR2) (387)19.13.6ADC注入通道数据偏移寄存器x (ADC_JOFRx)(x=1..4) (388)19.13.7ADC看门狗高阀值寄存器(ADC_HTR) (388)19.13.8ADC看门狗低阀值寄存器(ADC_LRT) (388)19.13.9ADC规则序列寄存器1(ADC_SQR1) (390)19.13.10ADC规则序列寄存器2(ADC_SQR2) (390)19.13.11ADC规则序列寄存器3(ADC_SQR3) (391)19.13.12ADC注入序列寄存器(ADC_JSQR) (391)19.13.13ADC 注入数据寄存器x (ADC_JDRx) (x= 1..4) (392)19.13.14ADC规则数据寄存器(ADC_DR) (392)19.14ADC寄存器地址映像 (394)20调试支持(DBG) (396)20.1概况 (396)20.2ARM参考文献 (397)20.3SWJ调试端口(serial wire and JTAG) (397)20.3.1JTAG-DP和SW-DP切换的机制 (397)20.4引脚分布和调试端口脚 (398)20.4.1SWJ调试端口脚 (398)20.4.2灵活的SWJ-DP脚分配 (398)20.4.3JTAG脚上的内部上拉和下拉 (399)20.4.4利用串行接口并释放不用的调试脚作为普通I/O口 (400)20.5STM32F10x JTAG TAP 连接 (400)20.6ID 代码和锁定机制 (401)20.6.1MCU DEVICE ID编码 (401)20.6.2TMC TAP (401)20.6.3Cortex-M3 TAP (401)20.6.4Cortex-M3 JEDEC-106 ID代码 (401)20.7JTAG调试端口 (402)20.8SW调试端口 (403)20.8.1SW协议介绍 (403)20.8.2SW协议序列 (403)20.8.3SW-DP状态机(Reset, idle states, ID code) (404)20.8.4DP和AP读/写访问 (404)20.8.5SW-DP寄存器 (405)20.8.6SW-AP寄存器 (405)20.9对于JTAG-DP或SWDP都有效的AHB-AP (AHB 访问端口) (405)20.10内核调试 (406)20.11调试器主机在系统复位下的连接能力 (407)20.12FPB (Flash patch breakpoint) (407)20.13DWT(data watchpoint trigger) (407)20.14ITM (instrumentation trace macrocell) (408)20.14.1概述 (408)20.14.2时间戳包,同步和溢出包 (408)20.15MCU调试模块(MCUDBG) (409)20.15.1低功耗模式的调试支持 (409)20.15.2支持定时器和看门狗和bxCAN的调试 (409)20.15.3调试MCU配置寄存器 (410)20.16TPIU (trace port interface unit) (411)20.16.1导言 (411)20.16.2跟踪引脚分配 (412)20.16.3TPUI格式器 (414)20.16.4TPUI帧异步包 (414)20.16.5同步帧包的发送 (415)20.16.6同步模式 (415)20.16.7异步模式 (415)20.16.8TRACECLKIN在STM32F10x内部的连接 (415)20.16.9TPIU寄存器 (416)20.16.10配置的例子 (416)20.17DBG寄存器地址映象 (417)STM32F10x参考手册第一版文档中的约定1 文档中的约定1.1 寄存器描述中使用的缩写列表在对寄存器的描述中使用了下列缩写:read / write (rw) 软件能读写此位。

STM32F10x参考手册参考手册参考手册参考手册

关于如何进入停止模式,详见表 3-4。 在停止模式下,通过设置电源控制寄存器(PWR_CR)的 LPDS 位使内部调节器进入低功耗 模式,能够降低更多的功耗。

如果正在进行 Flash 编程,直到对内存访问完成,系统才进入停止模式。 如果正在进行对 APB 的访问,直到对 APB 访问完成,系统才进入停止模式。 可以通过对独立的控制位进行编程,可选择以下功能:

表3-4 停止模式

进入

退出 唤醒延时

在以下条件下执行WFI或WFE指令: – 设置Cortex-M3系统控制寄存器中的SLEEPDEEP位 – 清除电源控制寄存器(PWR_CR)中的PDDS位 – 通过设置PWR_CR中LPDS位选择电压调节器的模式 注:为了进入停止模式,所有的外部中断的请求位(挂起寄存器(EXTI_PR))和RTC的闹 钟标志都必须被清除,否则停止模式的进入流程将会被跳过,程序继续运行。

STM32F10x 参考手册

第一版

电源控制(PWR)

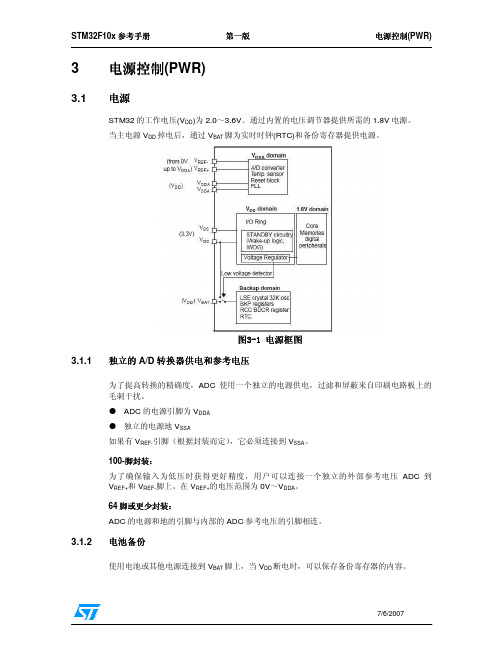

3 电源控制(PWR)

3.1 电源

STM32 的工作电压(VDD)为 2.0~3.6V。通过内置的电压调节器提供所需的 1.8V 电源。 当主电源 VDD 掉电后,通过 VBAT 脚为实时时钟(RTC)和备份寄存器提供电源。

3.1.1

图3-1 电源框图 独立的 A/D 转换器供电和参考电压

如果应用中没有使用外部电池,VBAT 必须连接到 VDD 引脚上。

注意:在 VDD 上升阶段(tRSTTEMPO),VBAT 和 VDD 之间的电源开关仍会保持连接在 VBAT。当 VDD 快速上升且达 到稳定状态,当 VBAT 低于 VDD−0.6V 时,电流通过 VDD 和 VBAT 之间的二极管流入到 VBAT。关于 tRSTTEMPO 可参考数据手册中的相关部分。

STM32F10x 大容量Flash 产品介绍

16位分频器

自动加载寄存器

TIMxCLK 时钟输入

16位递增计数器 更新事件 中断及DMA

基本定时器

2008年9月 6

新增外设 - FSMC

灵活静态存储控制器(FSMC)可用于连接外部存储器,共4个Bank. 当系统时钟频率为72MHz时,FSMC外部访问时钟频率为36MHz. 可编程的时序,支持多种不同时序要求的外设.

新增外设 – SDIO

SDIO共有10个引脚用于控制不同类型的存储卡

最多仅用6个引脚(SDIO_CMD, SDIO_CK, SDIO_D[3:0]) 用于SD卡的控制 ( 全尺寸SD卡, miniSD, microSD) 最多仅用6个引脚(SDIO_CMD, SDIO_CK, SDIO_D[3:0]) 用于SDIO卡的控制 (全尺寸SD, miniSD, microSD) 最多仅用10个引脚(SDIO_CMD, SDIO_CK, SDIO_D[7:0]) 用于MMC卡的控 制 (全尺寸MMC, RS-MMC, MMC+ 和 MMCMobile)

PC 卡信号

STM32 全国巡回研讨会

STM32大容量产品介绍

2008年9月 7

新增外设 - FSMC

BANK1:片选NE[1:4] BANK1:片选NE[1:4] BANK4: BANK4: 异步SRAM和ROM, BANK2&3:片选NCE[3:2] 片选NCE4_1,NCE4_2 异步SRAM和ROM, BANK2&3:片选NCE[3:2] 片选NCE4_1,NCE4_2

STM32F10x 大容量Flash 产品介绍

STM32 全国巡回研讨会

September 2008

大容量产品相对于中等容量产品的区别

STM32F10x芯片GPIOAFIO端口配置总结

STM32F10x芯片GPIO/AFIO端口配置总结1、介绍STM32F10x芯片的GPIO/AFIO配置主要包括以下几方面知识:在时钟控制模块中配置好相应总线时钟,并在总线上使能对应的GPIO口(AFIO口,需要的话)时钟后:根据需求配置相应GPIO端口为对应的输入/输出模式,按需求更改/读取端口的数据;端口功能重映射;若用外部中断,则将中断线与对应引脚链接起来。

STM32F10x芯片的每个GPIO端口都有7个相关的寄存器:2个32位配置寄存器(GPIOx_CRL,GPIOx_CRH),两个32位数据寄存器(GPIOx_IDR,GPIOx_ODR),一个32位置位/复位寄存器(GPIOx_BSRR),一个16位复位寄存器(GPIOx_BRR)和一个32位锁定寄存器(GPIOx_LCKR)。

每个I/O端口都可以设置成如下模式:✍输入浮空:GPIO_Mode_IN_FLOATING✍输入上拉:GPIO_Mode_IPU✍输入下拉:GPIO_Mode_IPD✍模拟输入:GPIO_Mode_AIN✍开漏输出:GPIO_Mode_Out_OD✍推免式输出:GPIO_Mode_Out_PP✍推免式复用功能:GPIO_Mode_AF_PP✍开漏复用功能:GPIO_Mode_AF_OD2、GPIO寄存器描述⚫端口配置低寄存器(GPIOx_CRL)(x=A…E)⚫端口配置高寄存器(GPIOx_CRH)(x=A…E)⚫端口输入数据寄存器(GPIOx_IDR)(x=A…E)⚫端口输出数据寄存器(GPIOx_ODR)(x=A…E)⚫端口位设置/清除寄存器(GPIOx_BSRR)(x=A…E)⚫端口位清除寄存器(GPIOx_BRR)(x=A…E)⚫端口配置锁定寄存器(GPIOx_LCKR)(x=A…E)2、AFIO寄存器描述⚫事件控制寄存器(AFIO_EVCR):控制内部时间输出到相应引脚⚫复用重映射和调试I/O配置寄存器(AFIO_MAPR)⚫外部中断配置寄存器(AFIO_EXTICRx)(x=1…4):设置端口为中断线(将端口与中端线连接)注意:对寄存器AFIO_EVCR、AFIO_MAPR、AFIO_EXTICRX进行读写操作前,应当首先打开AFIO的时钟。

第1章 STM32F10X系统介绍

• • • • •

多达2个 同步串行接口(18兆位 多达 个SPI同步串行接口 兆位 秒) 同步串行接口 兆位/秒 CAN 接口 接口(2.0B 主动 主动) USB 2.0 全速接口 调试模式 串行线调试(SWD)和JTAG接口 串行线调试 和 接口

1.1.4 STM32F10X 的应用前景

销售终端机 安防设备

• 72MHz CortexTM-M3 CPU

512 K

384 K

– 6KB to 64KB SRAM – Two lines: Performance and Access – FULL compatibility across family

256 K

128 K

STM32F103CB STM32F101CB STM32F103T8 STM32F103C8 STM32F101C8 STM32F103C6 STM32F101C6 48 pins LQFP

银行卡读卡器 超市收银机 扫描仪 报警系统 控制面板

USB 设备

生物认证和安全设备 读卡器

医药卫生

监护仪 检测设备

其它 工业自动化

程序控制器 工业网络 电池管理 ……

消费电子

PC附属设备 数码相机、GPS导航仪 卫星电话

强大的工具支持

Compilers and IDE Device Programming

– 16位处理器 位处理器 – 最高40MHz 最高

• 存储器

– 从32K字节至 字节至128K字节闪存 字节闪存 字节至 程序存储器 – 从6K字节至 字节至20K字节 字节SRAM 字节至 字节 – 多重自举功能

• 存储器

– 32K字节 字节 – SRAM:2K : – 只能从FLASH启动 只能从 启动

STM32F10xxx闪存编程参考手册

STM32F10xxx闪存编程手册

页1/22

依据2008年9月英文第4版翻译。本译文仅供参考,如有翻译错误,请以英文原稿为准

目录

1 概述 ...................................................................................................................................................4 1.1 特性 ........................................................................................................................................4 1.2 闪存模块组织 ...............................................................................................4

z Cortex-M3内核集成了两个调试端口: − JTAG调试接口(JTAG-DP)提供基于JTAG(Joint Test Action Group 联合测试行动 小组)协议的5线标准接口。 − SWD调试接口(SWD-DP)提供基于SWD(Serial Wire Debug 串行线调试)协议的2 线标准接口。

z 中容量产品是指闪存存储器容量在64K至128K字节之间的STM32F101xx、STM32F102xx 和STM32F103xx微控制器。

z 大 容 量 产 品 是 指 闪 存 存 储 器 容 量 在 256K 至 512K 字 节 之 间 的 STM32F101xx 和 STM32F103xx微控制器。

STM32F10x参考手册参考手册参考手册参考手册

STM32F10x参考手册

第一版

通用和复用功能I/O(GPIO和AFIO)

5.3

5.3.1 5.3.2

5.3.3

复用功能I/O和调试配置(AFIO)

为了优化64脚或100脚封装的外设数目,可以把一些复用功能重新映射到其他引脚上。设置 复用重映射和调试I/O配置寄存器(AFIO_MAPR)(参见5.4.1节)实现引脚的重新映射。这时, 复用功能不再映射到它们的原始分配上。

调试接口信号被映射到GPIO端口上,如表5-4所示。 表5-4 调试接口信号

复用功能 JTMS/SWDIO JTCK/SWCLK

JTDI JTDO/TRACESWO

JNTRST TRACECK TRACED0 TRACED1 TRACED2 TRACED3

GPIO端口 PA13 PA14 PA15 PB3 PB4 PE2 PE3 PE4 PE5 PE6

其它

禁用

1. I/O口只可在不使用异步跟踪时使用。

定时器复用功能重映射

定时器4的通道1到通道4可以从端口B重映射到端口D。其他定时器的重映射可能性列在表 5-6到表5-9里。

表5-6 定时器4复用功能重映像

复用功能

TIM4_REMAP = 0

TIM4_REMAP = 1

TIM4_CH1

PB6

PD12

第1章STM32F10X系统介绍

第1章STM32F10X系统介绍STM32F10X 是一款由意法半导体(STMicroelectronics)推出的32位ARM Cortex-M3 微控制器系列。

该系列具有高性能和低功耗的特点,广泛应用于工业控制、汽车电子、家用电器、医疗设备等领域。

STM32F10X 系列采用了先进的微控制器技术,结合了ARM Cortex-M3 内核的强大处理能力和低功耗特性。

它具有高达72MHz 的处理器频率,并且内置了丰富的外设和功能模块,如多个通用定时器、I/O 端口、通用串行总线接口(USART)、SPI 接口、I2C 接口等。

此外,它还支持多种存储介质,如闪存、SRAM 以及嵌入式模拟存储器。

在系统结构上,STM32F10X系列采用了多层总线架构。

它由处理器总线、AHB总线和APB总线组成,这些总线分别用于连接处理器核心、内存和外设。

这种层次化的总线结构使得系统具有高灵活性和可扩展性,能够满足不同应用场景的需求。

值得一提的是,STM32F10X 系列采用了意法半导体独有的ART (Adaptive Real-Time)加速器技术。

该技术能够提高嵌入式应用的实时性能和性能效率,通过优化指令和数据缓存访问,显著提高数据处理速度和系统响应速度。

综上所述,STM32F10X系列是一款高性能、低功耗的32位微控制器,具有强大的处理能力和丰富的外设。

它在工业控制、汽车电子、家用电器等领域得到广泛应用,并且配备了丰富的调试和开发工具,极大地简化了软件开发过程。

随着意法半导体不断推出新的版本和增加新的功能模块,STM32F10X系列将继续为嵌入式系统的设计者和开发者提供更多新的选择和解决方案。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.3 时钟结构

3.3 时钟结构

晶振 可关闭或旁路 时钟监视系统 一旦HSE失效 则自动切换至 SYSCLK=HSI

晶振 可关闭或旁路

内置振荡器 可关闭 输出 内部时钟

3.3 时钟结构

3.3 时钟结构

系统复位后,所有外设全部关闭,

但 SRAM 和 FLASH接口(FLITF)除外

使用外设之前需打开该外设时钟

DMA访问

DMA总线

将DMA的AHB主控接口与总线矩阵相连,协调CPU的

DCode和DMA到SRAM、闪存、外设的访问

总线矩阵

协调内核系统总线和DMA主控总线间的访问仲裁,仲

裁采用轮换算法 包含DCode、系统总线、DMA1和DMA2总线、被动单元

AHB到APB桥

两个AHB/APB桥在AHB和两个APB总线间提供同步连接 APB1速度限于36MHz,APB2全速最高72MHz

3.1 STM32系列微控制 器 3.2 STM32F10x内部结 构 3.3 时钟结构 3.4 存储结构 3.5 启动模式 3.6 片上外设 3.7 GPIO结构 3.8 引脚 3.9 开发工具 3.10 STM32系列的优点

3.2 STM32F10x内部结构

3.2 STM32F10x内部结构

3.4 存储结构

存储组织:

Cortex-M3的存储系统采用统一编址方式,小端方式 4GB 的线性地址空间内,寻址空间被分成 8 个主块 block0-block7 每块512MB 片内Flash:从 0x00000000开始

片内SRAM:从 0x20000000开始

包括: 代码空间 数据空间 位段、位段别名 寄存器 片上外设 外部存储器 外部外设

设置 RCC——AHBENR 寄存器

参见PDF资料

3 STM32F10x简介

3.1 STM32系列微控制 器 3.2 STM32F10x内部结 构 3.3 时钟结构 3.4 存储结构 3.5 启动模式 3.6 片上外设 3.7 GPIO结构 3.8 引脚 3.9 开发工具 3.10 STM32系列的优点

温度范围 6=商业级 -40~85 ℃ 7=工业级 -40~105 ℃

封装 H=BGA T=LQFP U=VFQFPN Y=WLCSP64

R =64

V=100

Z =144

闪存容量 4 = 16K 6 = 32K 8 = 64K B=128K C=256K D=384K E=512K

3 STM32F10x简介

基本型与增强型配置的差异

ARM Cortex-M3模块结构

3.2 STM32F10x内部结构

FLASH接口

总 线 矩 阵

3.2 STM32F10x内部结构

四个主动单元

M3内核的ICode总线(I-bus)、DCode总线(D-bus)、

系统总线(S-bus)、DMA(DMA1、DMA2、以太网DMA)

ST意法半导体公司产品 ARM

Cortex-M3内核 32位微控制器 高性能、低成本、低功耗、嵌入式应用

STM32F100:超值型 STM32F101:基本型(标准型) 入门产品;工作在36MHz;16位MCU的价格,32位的性能 STM32F102:USB基本型 STM32F103:增强型 同类产品性能最高;时钟72MHz;16K-512K闪存 带有更多片内SRAM 和 更丰富的外设 STM32F105或107:互联型 STM32L:超低功耗型

STM32F103xx中小容量型各系列外设资源

外设 闪存/K RAM/K F103Tx 32 10 2 64 20 3 STM32F103Cx 32 10 2 64 20 3 1 1 1 2 2 2 3 1 1 2 2 2 3 2 2 3 1 1 2 2 2 3 2 2 3 128 32 10 2 F103Rx 64 20 3 128 F103Vx 64 20 3 128

3.2 STM32F10x内部结构

3.2 STM32F10x内部结构

3.2 STM32F10x内部结构

3 STM32F10x简介

3.1 STM32系列微控制 器 3.2 STM32F10x内部结 构 3.3 时钟结构 3.4 存储结构 3.5 启动模式 3.6 片上外设 3.7 GPIO结构 3.8 引脚 3.9 开发工具 3.10 STM32系列的优点

3.4 存储结构

地址范围固定分配给 处理器系统控制寄存 器、位段区域、位段 别名

3.4 存储结构

定时 器

通用 高级 SPI I2 C

通 信

USART

USB

CAN 通用I/O 12位同步ADC CPU频率 工作电压 工作温度 封装

1

1 26

1

1

1

1

1

1 32

1

1

1

1 51

1

1

1

1 80 2 x 16

2 x 10 72MHz 2.0V ~ 3.6V -40℃~+85℃ / -40℃~+105℃ VFQFPN36 LQFP48 LQFP64

3 STM32F10x简介

3.1 STM32系列微控制 器 3.2 STM32F10x内部结 构 3.3 时钟结构 3.4 存储结构 3.5 启动模式 3.6 片上外设 3.7 GPIO结构 3.8 引脚 3.9 开发工具 3.10 STM32系列的优点

3.1 STM32系列微控制器

3.1 STM32系列微控制器

四个被动单元

内部SRAM、内部闪存、FSMC、AHB到APB桥

ICode总线

将M3内核的指令总线与FLASH指令接口相连,用于指

令预取

DCode总线

将M3内核的数据总线与FLASH数据接口相连,常量加

载和调试

3.2 STM32F10x内部结构

相连,协调内核与

LQFP/BGA100

3.1 STM32系列微控制器

STM32 F 103 C 8 T 6 A

产品系列 基于ARM的32位微控制器 产品类型 F = 通用类型 内部代码 A或空

子系列 101 = 基本型 103 = 增强型 引脚数 T = 36 C = 48

102 = USB基本型 105或107=互联型