33395T中文资料

33399中文资料

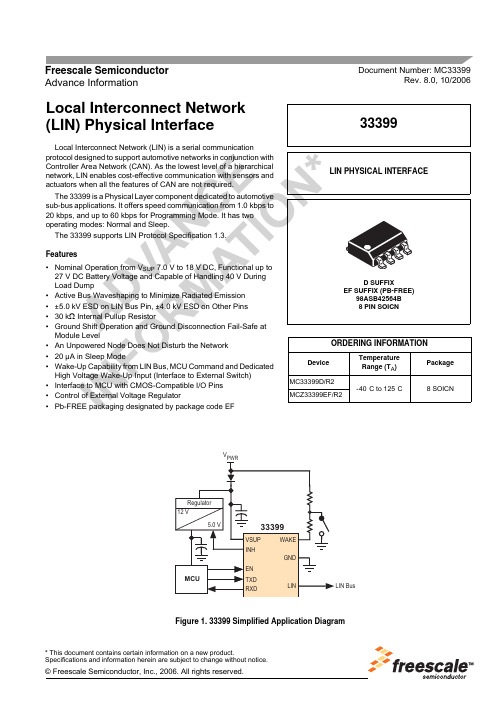

Document Number: MC33399Rev. 8.0, 10/2006Freescale Semiconductor Advance Information* This document contains certain information on a new product.Specifications and information herein are subject to change without notice.© Freescale Semiconductor, Inc., 2006. All rights reserved.Local Interconnect Network (LIN) Physical Interface•••± 5•30 k Ω••••••• Figure 1. 33399 Simplified Application Diagram33399Analog Integrated Circuit Device Data33399INTERNAL BLOCK DIAGRAMINTERNAL BLOCK DIAGRAMFigure 2. 33399 Simplified Internal Block DiagramV REF ReceiverINF ENRXDTXD GNDLIN30 k ΩVSUPDriverWAKE Wake-Up V REG ControlBiasProtectionLogicAnalog Integrated Circuit Device Data 33399PIN CONNECTIONSPIN CONNECTIONSFigure 3. 33399 8-SOICN Pin ConnectionsTable 1. 8-SOICN Pin DefinitionsA functional description of each pin can be found in the Functional Pin Description section beginning on page 10.Pin Pin Name Formal Name Definition1RXDData Output MCU interface that reports the state of the LIN bus voltage. 2EN Enable Control Controls the operation mode of the interface.3WAKEWake Input High voltage input used to wake up the device from the Sleep mode.4TXDData Input MCU interface that controls the state of the LIN output.5GNDGround Device ground pin.6LIN LIN Bus Bidirectional pin that represents the single-wire bus transmitter and receiver.7VSUPPower Supply Device power supply pin.8INHInhibit OutputControls an external switchable voltage regulator having an inhibit input.12345678RXD EN WAKE TXDINH V SUP LIN GNDAnalog Integrated Circuit Device Data33399ELECTRICAL CHARACTERISTICS MAXIMUM RATINGSELECTRICAL CHARACTERISTICSMAXIMUM RATINGSTable 2. Maximum RatingsAll voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.RatingSymbolValueUnitELECTRICAL RATINGS Power Supply Voltage Continuous Supply Voltage Transient Voltage (Load Dump)V SUP2740VWAKE DC and Transient Voltage (Through a 33 k Ω Serial Resistor)V WAKE - 18 to 40V Logic Voltage (RXD, TXD, EN Pins)V LOG - 0.3 to 5.5V LIN Pin DC VoltageTransient (Coupled Through 1.0 nF Capacitor)V BUS- 18 to 40- 150 to 100V INH Voltage / C urrent DC VoltageV INH - 0.3 to V SUP + 0.3V ESD Voltage, Human Body Model (1)All PinsLIN Bus Pin with Respect to Ground V E SD1± 4000± 5000VESD Voltage, Machine Model All PinsV E SD2± 200VTHERMAL RATINGS Operating Temperature Ambient JunctionT A T J - 40 to 125- 40 to 150°CStorage TemperatureT STG - 55 to 165°C Thermal Resistance , Junction to AmbientR θJA 150°C/W Peak Package Reflow Temperature During Reflow (2), (3)T PPRT Note 3.°C Thermal ShutdownT SHUT 150 to 200°C Thermal Shutdown HysteresisT HYST8.0 to 20°C Notes1.ESD1 testing is performed in accordance with the Human Body Model (C ZAP = 100 pF, R ZAP = 1500 Ω), ESD2 testing is performed inaccordance with the Machine Model (C ZAP = 220 pF, R ZAP = 0 Ω).2.Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.3.Freescale’s Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL),Go to , search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.Analog Integrated Circuit Device Data 33399ELECTRICAL CHARACTERISTICSSTATIC ELECTRICAL CHARACTERISTICSSTATIC ELECTRICAL CHARACTERISTICSTable 3. Static Electrical CharacteristicsCharacteristics noted under conditions 7.0 V ≤ V SUP ≤ 18 V, -40°C ≤ T A ≤ 125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T A = 25°C under nominal conditions unless otherwise noted.CharacteristicSymbolMinTypMaxUnitVSUP PIN (DEVICE POWER SUPPLY)Supply Voltage Range V SUP7.013.518V Supply Current in Sleep Mode V LIN > V SUP - 0.5 V, V SUP < 14 V 14 V < V SUP < 18 V I S1I S2——20—50150µASupply Current in Normal Mode Recessive StateDominant State, Total Bus Load > 500 ΩI S(REC)I S(DOM)———— 2.03.0mASupply Undervoltage Threshold V SUP_UV5.56.46.8VRXD OUTPUT PIN (LOGIC)Low-Level Output Voltage I IN ≤ 1.5 mAV OL0.0—0.9VHigh-Level Output Voltage I OUT ≤ 250 µΑV OH3.75—5.25V TXD INPUT PIN (LOGIC)Low-Level Input Voltage V IL —— 1.5V High-Level Input VoltageV IH 3.5——V Input Voltage Threshold Hysteresis V INHYST 100550800mV Pullup Current Source1.0 V < V TXD < 4.0 V, V EN = 5.0 V I PU- 50—- 25µAEN INPUT PIN (LOGIC)Low-Level Input Voltage V IL —— 1.5V High-Level Input VoltageV IH 3.5——V Input Voltage Threshold Hysteresis V INHYST100480800mV EN Low-Level Input Current V IN = 1.0 VI IL5.02030µAHigh-Level Input Current V IN = 4.0 V I IH—2040µAPulldown Current 1.0 V < EN < 4.0 VI PD—20—µAAnalog Integrated Circuit Device Data33399ELECTRICAL CHARACTERISTICSSTATIC ELECTRICAL CHARACTERISTICSLIN PIN (VOLTAGE EXPRESSED VERSUS VSUP VOLTAGE)Low-Level Bus Voltage (Dominant State) TXD LOW, V LIN = 40 mAV DOM0.0—1.4VHigh-Level Voltage (Recessive State) TXD HIGH, I OUT = 1.0 µA V REC0.85 V SUP——V Internal Pullup Resistor to VSUP (4)- 40°C ≤ T A ≤ 70°C 70°C < T A ≤ 125°C R PU203530494760k ΩCurrent Limitation TXD LOW, V LIN = V SUP I L IM50150200mALeakage Current to GNDRecessive State, V SUP - 0.3 V ≤ V LIN ≤ V SUP (4)V SUP Disconnected, -18 V ≤ V LIN ≤ 18 V (Excluding Internal Pullup Source)V SUP Disconnected, V LIN = -18 V (Including Internal Pullup Source)V SUP Disconnected, V LIN = +18 V (Including Internal Pullup Source)I L EAK0.0- 40————- 600151040——µALIN Receiver, Low-Level Input Voltage TXD HIGH, RXD LOWV L INL0 V SUP—0.4 V SUPVLIN Receiver, High-Level Input Voltage TXD HIGH, RXD HIGH V L INH0.6 V SUP—V SUPVLIN Receiver Threshold Center (V LINH - V LINL ) / 2V L INTH—V SUP /2—VLIN Receiver Input Voltage Hysteresis V LINH - V LINLV L INHYS0.05 V SUP—0.15 V SUPVLIN Wake-Up Threshold Voltage V L INWU 3.54.56.0VINH OUTPUT PINHigh-Level Voltage (Normal Mode)V WUH V SUP - 0.8—V SUPV Leakage Current (Sleep Mode)0 < V INH < V SUP I L EAK—5.0µAWAKE INPUT PINTypical Wake-Up Threshold (EN = 0 V, 7.0 V ≤ V SUP ≤ 18 V) (5)HIGH-to-LOW Transition LOW-to-HIGH Transition V WUTH0.3 V SUP 0.4 V SUP 0.43 V SUP 0.55 V SUP 0.55 V SUP 0.65 V SUP VWake-Up Threshold Hysteresis V WUHYS 0.1 V SUP0.16 V SUP0.2 V SUPV WAKE Input Current V WAKE ≤ 14 V V WAKE > 14 VI W U——1.0—5.0100µA Notes4. A diode structure is inserted with the pullup resistor to avoid parasitic current path from LIN to V SUP .5.When V SUP is greater than 18 V, the wake-up voltage thresholds remain identical to the wake-up thresholds at 18 V. Table 3. Static Electrical Characteristics (continued)Characteristics noted under conditions 7.0 V ≤ V SUP ≤ 18 V, -40°C ≤ T A ≤ 125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T A = 25°C under nominal conditions unless otherwise noted.CharacteristicSymbolMinTypMaxUnitAnalog Integrated Circuit Device Data 33399ELECTRICAL CHARACTERISTICSDYNAMIC ELECTRICAL CHARACTERISTICSDYNAMIC ELECTRICAL CHARACTERISTICSTable 4. Dynamic Electrical CharacteristicsCharacteristics noted under conditions 7.0 V ≤ V SUP ≤ 18 V, -40°C ≤ T A ≤ 125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T A = 25°C under nominal conditions unless otherwise noted.CharacteristicSymbolMinTypMaxUnitDIGITAL INTERFACE TIMING LIN Slew Rate (6) , (7)Falling Edge Rising Edget FALL t R ISE 0.750.75 2.02.0 3.03.0V/µsLIN Rise/Fall Symmetry (t RISE - t FALL )t S YM- 2.0—2.0µs Driver Propagation Delay (8) , (9) TXD LOW-to-LIN LOW TXD HIGH-to-LIN HIGH t TXDLINL t TXDLINH0.00.0——4.04.0µs Receiver Propagation Delay (9) ,(10) LIN LOW to RXD LOW LIN HIGH to RXD HIGHt RXDLINL t R XDLINH2.02.0 4.04.0 6.06.0µsReceiver Propagation Delay Symmetry t R ECSYM - 2.0— 2.0µs Transmitter Propagation Delay Symmetry t T RSYM - 2.0—2.0µs Propagation Delay (11)LIN Bus Wake-Up to INH HIGHt P ROP WL4570130µsNotess6.Measured between 20 and 80 percent of bus signal for 10 V < V SUP < 18 V. Between 30 and 70 percent of signal for7.0 V < V SUP < 10 V. 7.See Figure 5, page 8.8.t T XDLINL is measured from TXD (HIGH-to-LOW) and LIN (V REC - 0.2 V). t T XDLINH is measured from TXD (LOW-to-HIGH) and LIN (V DOM + 0.2 V).9.See Figure 4, page 8.10.Measured between LIN receiver thresholds and RXD pin.11.See Figure 6, page 8.Analog Integrated Circuit Device Data33399ELECTRICAL CHARACTERISTICS TIMING DIAGRAMSTIMING DIAGRAMSFigure 4. Normal Mode Bus Timing CharacteristicsFigure 5. LIN Rise and Fall Time Figure 6. LIN Bus Wake-UpTXDRXDLINV REC Dominant Statet TXDLINLt TXDLINHRecessive StateRecessive State 0.4 V SUP0.6 V SUPt RXDLINH t RXDLINLV DOM + 0.2VV REC - 0.2VV DOM t FALLt RISE0.2 V SUP0.8 V SUP0.8 V SUP0.2 V SUPINHLINV SUPDominant StateRecessive State 0.4 V SUPt PROP WLAnalog Integrated Circuit Device Data 33399FUNCTIONAL DIAGRAMSTIMING DIAGRAMSFUNCTIONAL DIAGRAMSFigure 7. LIN Wake-Up with INH Option Figure 8. LIN Wake-Up from Wake-Up SwitchFigure 9. LIN Wake-Up with MCU in Stop ModeLIN BusINH Bus Wake-Up Filtering Time (t PROG WL)Voltage Off StateOn StateNode in Sleep StateNode in Regulator Wake-Up Time DelayLow or FloatingHighMCU Startup Time DelayENEN HighOperation RegulatorWAKEINH Voltage Off StateOn StateNode in Sleep StateNode in Regulator Wake-Up Time DelayHighMCU Startup Time DelayENEN HighOperation State ChangeRegulatorLow or FloatingWAKE Filtering TimeLIN BusIRQWake-Up Filtering Time (t PROG WL)Voltage RegOn StateMCU in Stop ModeNode In OperationHighLow MCU Stop Mode Recovery/Startup Time DelayEN StateEN HighHighWake-Up from Stop ModeINHLow or Floating High(previous Wake-Up)I/O(2)High Impedance / I/O in Input State LowAnalog Integrated Circuit Device Data33399FUNCTIONAL DESCRIPTION TIMING DIAGRAMSFUNCTIONAL DESCRIPTIONINTRODUCTIONThe 33399 is a Physical Layer component dedicated to automotive LIN sub-bus applications.The 33399 features include speed communication from 1.0 kbps to 20 kbps, up to 60 kbps for Programming Mode, and active bus waveshaping to minimize radiated emission.The device offers three different wake-up capabilities: wake-up from LIN bus, wake-up from the MCU command, and dedicated high voltage wake-up input.The INH output may be used to control an external voltage regulator.FUNCTIONAL PIN DESCRIPTIONPOWER SUPPLY PIN (VSUP)The V SUP power supply pin is connected to a batterythrough a serial diode for reverse battery protection. The DC operating voltage is from 7.0 V to 27 V. This pin sustains standard automotive voltage conditions such as 27 V DC during jump-start conditions and 40 V during load dump. To avoid a false bus message, an undervoltage reset circuitry disables the transmission path (from TXD to LIN) when V SUP falls below 7.0 V. Supply current in the Sleep mode is typically 20 µA.GROUND PIN (GND)In case of a ground disconnection at the module level, the 33399 does not have significant current consumption on the LIN bus pin when in the recessive state. (Less than 100 µA is sourced from LIN bus pin, which creates 100 mV drop voltage from the 1.0 k Ω LIN bus pullup resistor.) For the dominant state, the pullup resistor should always be active. The 33399 handles a ground shift up to 3.0 V when V SUP > 9.0 V. Below 9.0 V V SUP , a ground shift can reduce V SUP value below the minimum V SUP operation of 7.0 V.LIN BUS PIN (LIN)The LIN bus pin represents the single-wire bus transmitter and receiver.Transmitter CharacteristicsThe LIN driver is a low-side MOSFET with internal current limitation and thermal shutdown. An internal pullup resistor with a serial diode structure is integrated so no external pullup components are required for the application in a slave node. An additional pullup resistor of 1.0 k Ω must be added when the device is used in the master node.Voltage can go from - 18 V to 40 V without current other than the pullup resistance. The LIN pin exhibits no reverse current from the LIN bus line to V SUP , even in the event of GND shift or V PWR disconnection. LIN thresholds are compatible with the LIN protocol specification.The fall time from recessive to dominant and the rise time from dominant to recessive are controlled to typically 2.0 V/µs. The symmetry between rise and fall time is also guaranteed.When going from dominant to recessive, the busimpedance parasitic capacitor must be charged up to V SUP.This charge-up is achieved by the total system pullup current resistors. In order to guarantee that the rise time is within specification, maximum bus capacitance should not exceed 10 nF with bus total pullup resistance less than 1.0 k Ω.Receiver CharacteristicsThe receiver thresholds are ratiometric with the device supply pin. Typical threshold is 50%, with a hysteresis between 5% and 10% of V SUP .DATA INPUT PIN (TXD)The TXD input pin is the MCU interface that controls the state of the LIN output. When TXD is LOW, LIN output is LOW; when TXD is HIGH, the LIN output transistor is turned OFF.This pin has an internal 5.0 V internal pullup currentsource to set the bus in a recessive state in case the MCU is not able to control it; for instance, during system power-up/power-down. During the Sleep mode, the pullup current source is turned OFF.DATA OUTPUT PIN (RXD)The RXD output pin is the MCU interface that reports the state of the LIN bus voltage. LIN HIGH (recessive) is reported by a high level on RXD; LIN LOW (dominant) is reported by a low voltage on RXD. RXD output structure is a CMOS-type push-pull output stage.ENABLE INPUT PIN (EN)The EN pin controls the operation mode of the interface. If EN = logic [1], the interface is in normal mode, with thetransmission path from TXD to LIN and from LIN to RXD both active. If EN = logic [0], the device is in Sleep mode or low power mode, and no transmission is possible.In Sleep mode, the LIN bus pin is held at V SUP through the bus pullup resistors and pullup current sources. The device can transmit only after being awakened. Refer to the INHIBIT OUTPUT PIN (INH) description on page 11.During Sleep mode, the device is still supplied from the battery voltage (through V SUP pin). Supply current is 20 µA typical. Setting the EN pin to LOW will turn the INH to high impedance. The EN pin has an internal 20 µA pulldown current source to ensure the device is in Sleep mode if EN floats.Analog Integrated Circuit Device Data 33399FUNCTIONAL DESCRIPTIONTIMING DIAGRAMSINHIBIT OUTPUT PIN (INH)The INH pin controls an external switchable voltageregulator having an inhibit input. This pin is a high-side switch structure to V SUP . When the device is in the Normal mode, the inhibit high-side switch is turned ON and the external voltage regulator is activated. When the device is in Sleep mode, the inhibit switch is turned OFF and disables the voltage regulator (if this feature is used).A wake-up event on the LIN bus line will switch the INH pin to V SUP level. Wake-up output current capability is limited to 280 µA. INH can also drive an external MOSFET connected to an MCU IRQ or XIRQ input to generate an interrupt. See the typical application illustrated in Figure 13, page 15.WAKE INPUT PIN (WAKE)The WAKE pin is a high-voltage input used to wake up the device from Sleep mode. WAKE is usually connected to an external switch in the application. The typical WAKE thresholds are V SUP / 2.The WAKE pin has a special design structure and allows wake-up from both HIGH-to-LOW or LOW-to-HIGHtransitions. When entering the Sleep mode, the LIN monitors the state of the WAKE pin and stores it as a reference state. The opposite state of this reference state will be the wake-up event used by the device to re-enter Normal mode.An internal filter is implemented (50 µs typical filtering time delay). The WAKE pin input structure exhibits a highimpedance with extremely low input current when voltage at this pin is below 14 V. When voltage at the WAKE pinexceeds 14 V, input current starts to sink into the device. A series resistor should be inserted in order to limit the input current, mainly during transient pulses. Recommended resistor value is 33 k Ω.Important The WAKE pin should not be left open. If the wake-up function is not used, WAKE should be connected to GND to avoid false wake-up.Analog Integrated Circuit Device Data33399FUNCTIONAL DEVICE OPERATION OPERATIONAL MODESFUNCTIONAL DEVICE OPERATIONOPERATIONAL MODESAs described below and depicted in Figure 10 and Table 5 on page 13, the 33399 has two operational modes, normal and sleep, and one transitional mode, Awake.NORMAL MODEThis is the normal transmitting and receiving mode. All features are available.SLEEP MODEIn this mode the transmission path is disabled and the device is in low power mode. Supply current from V SUP is 20 µA typical. Wake-up can occur from LIN bus activity, as well as from node internal wake-up through the EN pin and the WAKE input pin.DEVICE POWER-UP (AWAKE TRANSITIONAL MODE)At system power-up (V SUP rises from zero), the 33399 automatically switches into the “Awake ” mode (refer toFigure 10 below and Table 5 on page 13. It switches the INH pin in HIGH state to V SUP level. The microcontroller of the application then confirms the Normal mode by setting the EN pin HIGH.DEVICE WAKE-UP EVENTSThe device can be awakened from Sleep mode by three wake-up events:•LIN bus activity•Internal node wake-up (EN pin)•Wake-up from WAKE pinFigures 7, 8, and 9 on page 9 show device application circuit and detail of wake-up operations.Wake-Up from LIN Bus (Awake Transitional Mode)A wake-up from the LIN pin switching from recessive to dominant state (switch from V SUP to GND) can occur. This is achieved by a node sending a wake-up frame on the bus. This condition internally wakes up the interface, which switches the INH pin to a HIGH level to enable the voltage regulator. The device switches into the Awake mode. The microcontroller and the complete application power up. The microcontroller must switch the EN pin to a HIGH level to allow the device to leave the Awake mode and turn it into Normal mode in order to allow communication on the bus.Wake-Up from Internal Node Activity (Normal Mode)The application can internally wake up. In this case the microcontroller of the application sets the EN pin in the HIGH state. The device switches into Normal mode.Wake-Up from WAKE Pin (Awake Transitional Mode)The application can wake up with the activation of an external switch. Refer to Table 1, 8-SOICN Pin Definitions on page 3.Figure 10. Operational and Transitional Modes State DiagramPower-Up/SleepAwakeNormal EN LOWLIN Bus or WAKE PinEN HIGHWake-UpEN HIGH (Local Wake-Up Event)1.0 to 20kbpsV PWR > 7.0VNote Refer to Table 5 for explanation.V PWR < 7.0VV PWR < 7.0VV PWR < 7.0VDownAnalog Integrated Circuit Device Data 33399FUNCTIONAL DEVICE OPERATIONPROTECTION AND DIAGNOSIS FEATURESPROTECTION AND DIAGNOSIS FEATURESELECTROSTATIC DISCHARGE (ESD)The 33399 has two Human Body Model ESD values. All pins can handle ± 4.0 kV. The LIN bus pin, with respect to ground, can handle ± 5.0 kV.ELECTROMAGNETIC COMPATIBILITYRADIATED EMISSION ON LIN BUS OUTPUT LINERadiated emission level on the LIN bus output line is internally limited and reduced by active slew rate control of the output bus driver. Figure 11 shows the results in the frequency range 100 kHz to 2.0 MHz.ELECTROMAGNETIC IMMUNITY (EMI)On the LIN bus pin, the 33399 offers high EMI level from external disturbance occurring at the LIN bus pin in order to guarantee communication during external disturbance.On the WAKE input pin, an internal filter is implemented to reduce false wake-up during external disturbance.NOISE FILTERINGNoise filtering is used to protect the electronic module against illegal wake-up spikes on the bus. Integrated receiver filters suppress any high-frequency (HF) noise induced into the bus wires. The cut-off frequency of these filters is a compromise between propagation delay and HF suppression.Figure 11. Radiated Emission in Normal ModeTable 5. Explanation of Operational and Transitional Modes State DiagramOperational/ Transitional LININH EN TXD RXDSleep Mode Recessive state, driver off. 20 µA pullup current source.LOW LOW X High impedance.Awake Recessive state, driver off. HIGH LOW XLOW.Normal ModeDriver active. 30 k Ω pullup active.HIGHHIGHLOW to drive LIN bus in dominant.HIGH to drive LIN bus in recessive.Report LIN bus level: • LOW LIN bus dominant • HIGH LIN bus recessiveX = Don’t care.Analog Integrated Circuit Device Data33399TYPICAL APPLICATIONSTYPICAL APPLICATIONSThe 33399 can be configured in several applications. Figures 12 and 13 show slave and master node applications. An additional pullup resistor of 1.0 k Ω in series with a diode must be added when the device is used in the master node.Figure 12. Slave Node Typical Application with WAKE Input Switch and INH(Switchable 5.0 V Regulator)Actuator SCIMCUDriverM12V5.0VINH5.0 VL I N B u sV REGI/OV DD External SwitchRXDTXDENLINVSUPV REF LogicGNDDriverReceiverBias INHProtectionWake-Up WAKE30k Ω33399V PWRRegulator Regulator ControlAnalog Integrated Circuit Device Data 33399TYPICAL APPLICATIONSFigure 13. Master Node Typical Device Application with MCU Wake-Up from Stop Mode(Non-Switchable 5.0 V Regulator, MCU Stop Mode)Actuator SCIMCU DriverM5.0 VL I N B u sMaster Node PullupIRQ5.0VI/O V DD I/O(2)RXDTXDENLINVSUPV REF LogicGNDDriverReceiverBiasINHProtectionWAKE30k Ω1.0k Ω33399V PWRExternal Switch12V5.0VRegulator Wake-Up Regulator ControlREFERENCE DOCUMENTSREFERENCE DOCUMENTSTable 6. Reference DocumentsTitle LIterature Order Number Local Interconnect Network (LIN) Physical Interface: Difference Between MC33399 and MC33661EB21533399Analog Integrated Circuit Device DataAnalog Integrated Circuit Device Data 33399PACKAGINGPACKAGE DIMENSIONSPACKAGINGPACKAGE DIMENSIONSImportant For the most current revision of the package, visit and do a keyword search on the 98Adrawing number below.8-PIN SOIC NARROW BODYPLASTIC PACKAGE 98ASB42564B ISSUE UAnalog Integrated Circuit Device Data33399REVISION HISTORYREVISION HISTORYREVISIONDATE DESCRIPTION OF CHANGES7.07/2006•Implemented Revision History page •Added Pb-Free suffix code EF•Added EPP ordering part number MCZ33399EF/R2•Adjusted to the Freescale prevailing form and style8.010/2006•Removed Peak Package Reflow Temperature During Reflow (solder reflow) parameter from MAXIMUM RATINGS on page 4. Added note with instructions to obtain this information from .MC33399Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. “Typical” parameters that may beprovided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals”, must be validated for each customer application by customer’s technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended orunauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part. Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.© Freescale Semiconductor, Inc., 2006. All rights reserved.RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb-freecounterparts. For further information, see or contact your Freescale sales representative.For information on Freescale’s Environmental Products program, go to /epp .How to Reach Us:Home Page:Web Support:/support USA/Europe or Locations Not Listed:Freescale Semiconductor, Inc.Technical Information Center, EL5162100 East Elliot Road Tempe, Arizona 85284+1-800-521-6274 or +/supportEurope, Middle East, and Africa:Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 781829 Muenchen, Germany +44 1296 380 456 (English)+46 8 52200080 (English)+49 89 92103 559 (German)+33 1 69 35 48 48 (French)/supportJapan:Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064Japan0120 191014 or +81 3 5437 9125support.japan@Asia/Pacific:Freescale Semiconductor Hong Kong Ltd.Technical Information Center 2 Dai King StreetTai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080@For Literature Requests Only:Freescale Semiconductor Literature Distribution Center P .O. Box 5405Denver, Colorado 802171-800-441-2447 or 303-675-2140Fax: 303-675-2150LDCForFreescaleSemiconductor@。

ER9.5-2.5-5-3C92-S中文资料

PRODUCT STATUS DEFINITIONS

STATUS Prototype Design-in Preferred Support

INDICATION

DEFINITION

These are products that have been made as development samples for the purposes of technical evaluation only. The data for these types is provisional and is subject to change. These products are recommended for new designs.

TYPE NUMBER

ER9.5/2.5/5-3C92-S ER9.5/2.5/5-3C93-S ER9.5/2.5/5-3C94-A63-S ER9.5/2.5/5-3C94-A100-S ER9.5/2.5/5-3C94-A160-S ER9.5/2.5/5-3C94-S ER9.5/2.5/5-3C96-S ER9.5/2.5/5-3F3-A63-S ER9.5/2.5/5-3F3-A100-S ER9.5/2.5/5-3F3-A160-S ER9.5/2.5/5-3F3-S ER9.5/2.5/5-3F35-S ER9.5/2.5/5-3F4-A40-S ER9.5/2.5/5-3F4-A63-S ER9.5/2.5/5-3F4-A100-S ER9.5/2.5/5-3F4-S ER9.5/2.5/5-3F45-S

B (mT) at

CORE LOSS (W) at

GRADE

3C92 3C93 3C94 3C96 3F3 3F35 3F4 3F45

MC33399中文资料

Description

VSUP pin (Device power supply) Nominal DC Voltage Range Supply Current in Sleep Mode

Supply Current in Sleep Mode and Vsup>14V Supply Current in Normal Mode Supply Current in Normal Mode

• Speed Communication from 1 to 20Kb/s • Nominal Operation from VSUP 8 to 18V DC • Fully Functional up to 27V DC battery voltage. • 40V maximum Voltage during Load Dump • Handle from +40V to -18V DC voltage at LIN pin • Gnd disconnection fail safe at module level • An Unpowered Node does not disturb the network • GND Shift Operation at system level • Two Operation Modes: Normal and Sleep Mode • Very Low Standby Current during Sleep Mode 20uA • Wake-up Capability from LIN bus, MCU command and dedicated high voltage wake up input (interface to external switch) • Interface to MCU with CMOS compatible I/O pins • Control of External Voltage Regulator • LIN bus Threshold Voltage fully Compatible with LIN protocol specification • Bus slew rate control according to LIN protocol specification recommendations (2V/us typ.) • Internal pull up resistor • Handle Automotive Transients per ISO9137 Specification • ESD 4KV on LIN bus Pin • High EMC Immunity

车辆运行安全监控系统建设要求

车辆运行安全监控系统建设要求徐占山,张项(中国铁路济南局集团有限公司车辆部,济南250001)[摘要] 车辆运行安全监控系统(5T 系统)是保障铁路运输安全的重要铁路行车安全监测设备,其建设要求涉及房建、电力、通信、信息、车辆、工务等多个专业。

本文对分散在若干规章、标准、文件中的车辆运行安全监控系统建设要求,从探测站,检测、监测和复示站,维修工区,机房设施,检修通道,电磁防护,传输通道,供电,UPS ,消防设施等9个方面进行了梳理并结合现场需求进行了优化,在近年的新改建铁路工程实践中取得了较好的效果,降低了建设难度,减少了工程返工,提高了建设质量。

[关键词] 工程建设;车辆运行安全监控系统;5T 系统1 前言 车辆运行安全监控系统(下称5T 系统)[1],是保障铁路运输安全的重要铁路行车安全监测设备[2],包括车辆轴温智能探测系统(THDS )、铁道车辆运行品质轨旁动态监测系统(TPDS )、铁道车辆滚动轴承故障轨旁声学诊断系统(TADS )、货车故障轨旁图像检测系统(TFDS )、铁道客车故障轨旁图像检测系统(TVDS )、动车组运行故障图像检测系统(TEDS )、客车运行安全监控系统(TCDS )等子系统,由各级联网服务器和监测、检测(对TEDS 和TVDS 也称监控中心)、复示终端、探测站设备及机房、供电、通道、网络设备等配套设施组成[1],使用声学、光学、力学、电磁和图像等高性能传感器检测运行车辆(动车组)的载重、轮轨冲击、部件状态和轴承温度、内部缺陷等安全信息,采用信息化、智能化、网络化技术,全天候自动采集、传输、存贮、识别、报警运行中的动车组和客货车辆故障[3],点线成网、跟踪运行、局间互控,实现铁路车辆(动车组)运用质量在线监测,及时消除铁路安全隐患,为铁路车辆装备修程修制改革和铁路行车安全保障提供重要信息支撑[4]。

新建铁路须设计5T 系统并应与铁路主体工程同时投产[3]。

探测站是5T 系统信息采集源点和施工维修上道作业重点,分散布局在铁路沿线,如图1至图4所示,其中THDS 探测站间距30km 左右,TFDS 、TPDS 、TADS 探测站间距分别在300km 、400km 、500km左右[4],TCDS 设置在客车技术整备所,TVDS 和TEDS 设置在国铁集团、集团公司规划地点;各级联网服务器和监测、检测、复示终端是处理5T 信息的大脑,分别提供国铁集团、铁路局集团公司、车辆(动车)段和列检等各级应用;通道网络为5T 系统信息传输提供通路;机房、电力为5T 系统设备运行提供环境和动力保障。

Air King 5-Speed Table Fan User Manual

DOUBLE BLADEWHOLE ROOM STAND FANHSF1640 SeriesA001819R128SEP17Honeywell is a trademark of Honeywell International Inc., used under license by Helen of Troy Limited. Honeywell International Inc. makes no representation or warranties with respect to this product.© 2018 All rights reserved. Kaz USA, Inc., a Helen of Troy Company Marlborough, MA 01752Imported and Distributed by: Kaz Canada Inc., a Helen of Troy Company 6700 Century Avenue, Suite 210, Mississauga, Ontario L5N 6A4Contact us at 1-800-477-0457 or /fansHoneywell est une marque de commerce de Honeywell International, Inc. qu’utilise Helen of Troy Limited sous licence. Honeywell International Inc. ne fait aucune assertion et n’offre aucune garantie en ce qui concerne ce produit.© 2018 Tous droits réservés. Kaz USA, Inc., a Helen of Troy Company Marlborough, MA 01752Importé et distribué par : Kaz Canada Inc., a Helen of Troy Company 6700 Century Avenue, Suite 210, Mississauga, Ontario L5N 6A4Pour nous joindre : Composez le 1 800 477-0457 ou visitez notre site Web à /fans For Responsible recycling, please visit: Honeywell es una marca registrada de Honeywell International Inc., utilizada bajo licencia por Helen of Troy Limited. Honeywell International Inc. no hace ninguna representación o garantía con respecto a este producto.© 2018 Todos los derechos reservados. Kaz USA, Inc., una Empresa de Helen of Troy Marlborough, MA 01752Importado y Distribuido por: Kaz Canada Inc., una Empresa de Helen of Troy 6700 Century Avenue, Suite 210, Mississauga, Ontario L5N 6A4Contáctenos en el 1-800-477-0457 o /fans Para reciclar responsablemente, por favor visite:。

2985中文资料

8-CHANNEL SOURCE DRIVER Recommended for applications requiring separate logic and load grounds, load supply voltages to 30 V, and load currents to 250 mA, the UDN2985A source driver is used as an interface between standard low-power digital logic and LEDs, relays, and solenoids. The outputs feature saturated transistors for low collector-emitter saturation voltages.The UDN2985A driver is for use with 5 V logic systems: TTL, Schottky TTL, DTL, and CMOS. This device has a minimum output breakdown rating of 30 V with a minimum output sustaining voltage of 15 V. The output is switched on by an active-high input level.Under normal operating conditions, this device can source up to 120 mA for each of the eight outputs at an ambient temperature of 75°C and a supply voltage of 15 V. It incorporates input current-limiting resistors and output transient-suppression diodes.The UDN2985A source driver is supplied in an 18-pin dual in-line package. All inputs are on one side of the package, output pins on the other, to simplify printed wiring board layout.Always order by complete part number:UDN2985A.Dwg. No. DS-1013FEATURESI TTL, DTL, or CMOS Compatible Inputs I 250 mA Output Source Current Capability I Output Transient-Suppression DiodesI 30 V Minimum Output Breakdown Voltage I Low Output-Saturation VoltagePARTIAL SCHEMATIC DIAGRAM 1 of 8 DRIVERS Data Sheet29310.2A†298529858-CHANNELSOURCE DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000 LimitsCharacteristics Symbol Test Conditions Min.Typ.Max. Units Output Leakage Current I CEX V IN = 0.4 V, V OUT = 0 V —<-1.0-100µA Output Sustaining Voltage V CE(sus)l OUT = -120 mA, L = 3 mH 15——V Output Saturation VoltageV CE(SAT)V IN = 2.4, l OUT = -60 mA —0.8 1.1V V IN = 2.4, l OUT = -120 mA—0.9 1.2V Input Current VoltageI IN(ON)V IN = 2.4 V —90225µA V IN = 5.0 V—280650µA I IN(OFF)V IN = 0.4 V—1015µA Supply Current I S V S = 30 V, V IN = 2.4 V —1015mA (outputs open)Clamp Diode I R V R = 30 V, T A = 70°C —<1.050µA Leakage Current Clamp Diode V F I F = 120 mA— 1.1 2.0V Foward Voltage Turn-On Delay t ON —0.5 1.0µs Turn-Off Delayt OFF—5.010µsELECTRICAL CHARACTERISTICS at T A = 25°C, V S = 30 V (unless otherwise noted).COMMON-CATHODE LED DRIVERNOTE: Negative current is defined as coming out of (sourcing) the specified device pin.Dwg. No. DS-1014Copyright © 1984, 2000 Allegro MicroSystems, Inc.29858-CHANNEL SOURCE DRIVERNOTES:1.Exact body and lead configuration at vendor’s option within limits shown.2.Lead spacing tolerance is non-cumulative.3.Lead thickness is measured at seating plane or below.4.Supplied in standard sticks/tubes of 21 devices.Dimensions in Inches(controlling dimensions)Dimensions in Millimeters(for reference only)Dwg. MA-001-18A in181910Dwg. MA-001-18A mm191029858-CHANNELSOURCE DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000POWER SOURCE DRIVERSIN ORDER OF 1) OUTPUT CURRENT, 2) OUTPUT VOLTAGE, 3) NUMBER OF DRIVERSOutput Ratings *FeaturesSerial Latched Diode Saturated Internal mA V #Input Drivers Clamp Outputs ProtectionPart Number †-2560 8–X –––58156010X X active pull-down ––5810-F and 6809/106012XX active pull-down ––5811 and 68116020X X active pull-down ––5812-F and 68126032X X active pull-down ––5818-F and 681885 8–––––6118-120-25 8––X X –258530 8––X X –298550 8X X X X –5895-35035 8––X –X 298750 8––X ––2981 and 298250 8X X X ––5891-50 8––X ––258080 8––X ––2983 and 298480 8X X X ––5890-80 8––X ––2588-50061–––MO SFET X 2525 and 253562–––MOSFET X 2526 and 2536-4000604––X ––2944*Current is maximum specified test condition, voltage is maximum rating. See specification for sustaining voltage limits orover-current protection voltage limits.†Complete part number includes additional characters to indicate operating temperature range and package style.The products described here are manufactured under one or more U.S. patents or U.S. patents pending.Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, ormanufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsi-bility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.。

33389资料

Document Number: MC33389Rev. 5.0, 3/2007Freescale Semiconductor Advance Information* This document contains certain information on a new product.Specifications and information herein are subject to change without notice.© Freescale Semiconductor, Inc., 2007. All rights reserved.System Basis Chip with Low Speed Fault Tolerant CANThe 33389 is a monolithic integrated circuit combining manyfunctions frequently used by automotive Engine Control Units (ECUs). It incorporates a low speed fault tolerant CAN transceiver.Features•Dual Low Drop Voltage Regulators, with Respectively 100 mA and 200 mA Current Capabilities, Current Limitation, and Over Temperature Detection with Pre-warning • 5.0 V Output Voltage for V1 Regulator•Three Operational Modes (Normal, Stand-by, and Sleep Modes) Separated from the CAN Interface Operating Modes•Low Speed 125 kBaud Fault Tolerant CAN Interface, Compatible with 33388 Stand Alone Physical Interface •V1 Regulator Monitoring and Reset Function•Three External High Voltage Wake-Up Inputs, Associated with V3 V BAT Switch•100 mA Output Current Capability for V3 V BAT Switch Allowing Drive of External Switches or Relays•Low Stand-by and Sleep Current Consumption•V BAT Monitoring and V BAT Failure Detection Capabilities •DC Operating Voltage up to 27 V •40 V Maximum Transient Voltage•Programmable Software Window Watchdog and Reset•Wake-Up Capabilities (CAN Interface, Local Programmable Cycle Wake•INterface with the MCU through the SPI•Pb-Free Packaging Designated by Suffix Codes VW and EGFigure 1. 33389 Simplified Application DiagramSYSTEM BASIS CHIP33389ORDERING INFORMATIONDevice Temperature Range (T A )PackageMC33389CDH/R2-40 to 125°CHSOP-20MC33389CVW/R2MC33389CDW/R2SO-28MC33389DDW/R2Analog Integrated Circuit Device Data33389DEVICE VARIATIONSDEVICE VARIATIONSTable 1. Device VariationsFreescale Part No.V1 UndervoltageMC33389CDH MC33389CVW MC33389CDW In V1 undervoltage condition, device remains in permanent reset state until V1 returns to normal conditions. V1 is protected by overcurrent and overtemperature functions.MC33389DDWThe sole difference between the C version and the D version is V1 Reset Threshold. Reference V1 Reset Threshold on V1 on page 9.INTERNAL BLOCK DIAGRAMINTERNAL BLOCK DIAGRAMFigure 2. 33389 Simplified Internal Block Diagram33389 Analog Integrated Circuit Device DataAnalog Integrated Circuit Device Data33389PIN CONNECTIONSPIN CONNECTIONSFigure 3. 33389 Pin ConnectionsTable 1. 33389 Pin Definitions: HSOSP 20-LeadA functional description of each pin can be found in the Functional Pin Description section beginning on page 17.Pin NumberPin NameFormal Name Definition1TX Transmitter DataTransmitter input of the LS CAN interface2V1Voltage Regulator One This 5.0 V pin is a 3% low drop voltage regulator dedicated to the microcontroller supply.3RX Receiver DataReceiver output of the LS CAN interface 4RST Reset This is an Input/Output pin.5INT Interrupt Output This output is asserted LOW when an enabled interrupt condition occurs.6MISO Master In/Slave Out This pin is the tri-state output from the shift register. 7MOSI Master Out/Slave In This pin is for the input of serial instruction data. 8SCLK System Clock This pin clocks the internal shift registers.9CS Chip Select This pin communicates with the system MCU and enables SPI communication.10 - 12L0 - L2Level 0 - 2 inputs(L0: L2)Input interfaces to external circuitry. Levels at these pins can be read by SPI and input can be used as programmable wake-up input in Sleep or Stop mode.13RTH RTH Pin for the connection of the bus termination to CANH 14CANLCAN Low CAN low input/output15GND Ground This pin is the ground of the integrated circuit.16CANH CAN HighCAN high input/output17V2Voltage Regulator Two This 5.0 V pin is a low drop voltage regulator dedicated to the peripherals supply.18RTL RTL Pin for the connection of the bus termination to CANL 19VBAT Voltage Battery This pin is voltage supply from the battery.20V3Voltage RegulatorThreeThis pin is a 10 Ω switch to V BAT , used to supply external contacts or relays.Analog Integrated Circuit Device Data 33389PIN CONNECTIONSTable 2. 33389 Pin Definitions: SOICW 28-LeadA functional description of each pin can be found in the Functional Pin Description section beginning on page 17.Pin NumberPin Name Formal Name Definition1TXTransmitter Data Transmitter input of the LS CAN interface2V1Voltage Regulator OneThis 5.0 V pin is a 3% low drop voltage regulator dedicated to the microcontroller supply.3RXReceiver Data Receiver output of the LS CAN interface 4RST Reset This is an Input/Output pin.5INT Interrupt This output is asserted LOW when an enabled interrupt condition occurs.6 -9 20 - 23GND GroundThese device ground pins are internally connected to the package lead frame to provide a 33389-to-PCB thermal path.10MISO Master In/Slave OutThis pin is the tri-state output from the shift register. 11MOSIMaster Out/Slave In This pin is for the input of serial instruction data. 12SCLKSystem Clock This pin clocks the internal shift registers.13CS Chip Select This pin communicates with the system MCU and enables SPI communication.14, 15, 16L0: L2Wake-up Input (L0: L2)Input interfaces to external circuitry. Levels at these pins can be read by SPI and input can be used as programmable wake-up input in Sleep or Stop mode.17NCNo Connect This pin does not connect.18RTH Thermal Resistance High Pin for the connection of the bus termination to CANH 19CANLCAN Low CAN low input/output 24CANHCAN High CAN high input/output25V2Voltage Regulator TwoThis 5.0 V pin is a low drop voltage regulator dedicated to the peripherals supply.26RTL Thermal Resistance LowPin for the connection of the bus termination to CANL 27VBAT Voltage Battery This pin is voltage supply from the battery.28V3Voltage Regulator ThreeThis pin is a 10 Ω switch to V BAT , used to supply external contacts or relays.Analog Integrated Circuit Device Data33389ELECTRICAL CHARACTERISTICS MAXIMUM RATINGSELECTRICAL CHARACTERISTICSMAXIMUM RATINGSTable 3. Maximum RatingsAll voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.RatingsSymbol Value UnitELECTRICAL RATINGS DC Voltage at VBAT Pin V BAT -0.3 to 27V Transient Voltage at VBAT Pint < 500 ms (load dump)V BAT 40V DC Voltage at Pins CANH and CANL V BAT -20 to 27V Transient Voltage at Pins CANH and CANL 0.0 < V2 < 5.5, V BAT > 0.0, t < 500 msV BAT-40 to 40VCoupled Transient Voltage at Pins CANH and CANLWith 100 Ω Termination Resistors, Coupled Through 1.0 nF (1)V BAT-100 to 100 VDC Voltage at Pins V1 and V2V BAT -0.3 to 6.0V DC Current at Output Pins RX, MISO, RST, INT V BAT -20 to 20mA DC Voltage at Input Pins TX, MOSI, CS, RST V BAT -0.3 to 6.0V DC Voltage at Pins L0, L1, L20.0 < V BAT < 40 V V BAT-0.3 to 40VCurrent at Pins L0, L1, L2V BAT -15mA Transient Current at Pin V3V BAT -30 to 20mA DC Voltage at pins RTH and RTLV BAT -0.3 to 40V ESD Voltage on any Pin (HBM 100 pF, 1.5 K)V BAT -2.0 to 2.0kV ESD Voltage on L0, L1, L2, CANH, CANL, VBAT V BAT -2.0 to 2.0kV ESD Voltage on any Pin (MM 200 pF, 0 Ω)V BAT-150 to 150VTHERMAL RATINGSOperating Junction Temperature T J -40 to 150°C Ambient Temperature T A -40 to 125°C Storage TemperatureT S-55 to 165°CNotes1.Pulses 1, 2, 3a, and 3b according to ISO7637.Analog Integrated Circuit Device Data 33389ELECTRICAL CHARACTERISTICSMAXIMUM RATINGSTHERMAL RESISTANCERTH, RTL Termination ResistanceR RTHRTL 500 to 16 kΩJunction to Heatsink Thermal Resistance for HSOP-2033% Power on V1, 66% on V2 (including CAN) (2) R AJC3.1°C/WJunction to Pin Thermal Resistance for SO-28WD (3) R AS/P 17°C/W Thermal Shutdown TemperatureT SD 165°C Peak Package Reflow Temperature During Reflow (4), (5)T PPRTNote 5°CNotes2.Refer to thermal management in device description section.3.Refer to thermal management in device section. Ground pins 6, 7, 8, 9, 20, 21, 22, and 23 of SO28WB package.4.Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits maycause malfunction or permanent damage to the device.5.Freescale’s Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package ReflowTemperature and Moisture Sensitivity Levels (MSL),Go to , search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.Table 3. Maximum Ratings (continued)All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.RatingsSymbolValueUnitAnalog Integrated Circuit Device Data33389ELECTRICAL CHARACTERISTICSSTATIC ELECTRICAL CHARACTERISTICSSTATIC ELECTRICAL CHARACTERISTICSTable 4. Static Electrical CharacteristicsCharacteristics noted under conditions V BAT , - 40°C ≤ T A ≤ 125°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T A = 25°C under nominal conditions unless otherwise noted.CharacteristicSymbol Min Typ Max UnitPOWER INPUT (VBAT)Nominal VBAT Operating Range V BAT 5.5—18V Functional VBAT Operating Range V BAT 5.5—27V V BAT Threshold for BAT FAIL Flag BAT FAIL2.0— 4.0V Delay for Signalling BAT FAIL TFAIL—150400µs Overvoltage V BAT Threshold BAT HIGH 182022V Delay for Setting BAT HIGH Flag T HIGH 4.01850µs Supply Current in Sleep ModeForced Wake-Up and Cyclic Sense Disabled V BAT = 12 V, T J = 25°C to 150°C I SLEEP1—75125µASupply Current in Sleep ModeForced Wake-Up and Cyclic Sense Disabled V BAT = 12 V, T J = -40°C to 25°C I SLEEP2——210µASupply Current in Sleep ModeForced Wake-Up and Cyclic Sense Enabled V BAT = 12 V, T J = 25°C to 150°C I SLEEP3—105155µASupply Current in Sleep ModeForced Wake-Up and Cyclic Sense Enabled V BAT = 12 V, T J = -40°C to 25°C I SLEEP4——250µASupply Current in Sleep ModeForced Wake-Up and Cyclic Sense Disabled V BAT = 12 V, T J = 25°C to 150°C I SLEEP5——300µASupply Current in Stand-by Mode I STB2—0.5 1.0mA Supply Current in Normal Mode Normal Mode with I(V1) = 1 I(V2) = 0Bus in Recessive State I NREC—3.57.0mAPOWER OUTPUT V1 Output Voltage 0 mA < I OUT < 100 mA 5.5 V < V BAT < 27 V V1NOM4.855.05.15VV1 Output Voltage I OUT =< 100 mA 27 V < V BAT < 40 V V14.85.05.2VV1 Drop Voltage I OUT =< 100 mA (6)V1DROP —0.350.5VNotes6.Measured when V1 has dropped 100mV below its nominal valueAnalog Integrated Circuit Device Data 33389ELECTRICAL CHARACTERISTICSSTATIC ELECTRICAL CHARACTERISTICSPOWER OUTPUT (CONTINUED) V1 Output Current Limitation V1NOM - 100 mVI1MAX130170200mAV1 Overtemperature Shut OFF Threshold Junction TemperatureTV1H 160—190°CV1 Pre-Warning Temperature Threshold Junction TemperatureTV1L 130—160°CV1 Temperature Threshold Difference TV1H-TV1L20—40°C V1 Reset Threshold on V15.5 V < V BAT < 27 V (C Version)(D Version)VR1 4.1V2 - 0.4 4.3V1 - 0.284.8V1 - 0.1VV1 Reset Active V1 RangeV1R 1.0VR1—V V1 Reverse Current from V1 to V BAT and GND V1 = 4.9 V, 0 < V BAT < 4.9 V IREV——1.0mAV2 Output Voltage0 mA < I OUT < 200 mA 5.5 V < V BAT < 40 V V2NOM 4.75 5.0 5.25 VV2 Drop Voltage I OUT = 200 mA (7)V2DROP —0.2 0.5VV2 Drop Voltage I OUT = 20 mA (7)V2DROP —0.050.15VV2 Output Current Limitation V2NOM -100 mVI1MAX220280350mAV2 Threshold on V2 to Report V2 OFF V2 Nominal V R24.14.554.75VV R2 Delay TimeV R220—70µs V2 Overtemperature Pre-Warning Threshold V2 Junction TemperatureT V2L130—160°CV2 Overtemperature Switch-OFF Threshold V2 Junction Temperature T V2H155—185°CV2 Line Regulation 9.0 V < V BAT < 16.5V2LR1-15—+15mVV2 Load Regulation 4.0 mA < I LOAD < 200 mA V2LR2-75—+75mVV2 Line Ripple Rejection 100 Hz, 1.0 V PP on V BAT (8)V2LRR3055—dBNotes7.Measured when V1 has dropped 100mV below its nominal value 8.Guaranteed by design; however, it is not production testedTable 4. Static Electrical Characteristics (continued)Characteristics noted under conditions V BAT , - 40°C ≤ T A ≤ 125°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T A = 25°C under nominal conditions unless otherwise noted.CharacteristicSymbol Min Typ Max UnitAnalog Integrated Circuit Device Data33389ELECTRICAL CHARACTERISTICSSTATIC ELECTRICAL CHARACTERISTICSPOWER OUTPUT (CONTINUED) V2 Percentage Difference V2-V1V BAT > 9.0, I V1 = 20 mA, I V2 = 40 mA V2V2-V1-3.0—3.0%V3 High Level Voltage DropI V3 = -50 mA, 9.0 V < V BAT < 40 V V3DROP—0.41.0VV3 High Level Voltage DropI V3 = -50 mA, 6.0 V < V BAT < 9.0 V V3DROP——1.5VV3 Leakage Output Limitation 5.5 V < V BAT < 27 V I3LIM100150250mAV3 Leakage Current V3 = 0 (V3 OFF)I3LEAK——15µAV3 Overtemperature Detection Junction TemperatureT V3155—185°CV3 Voltage with -30 mA (negative current for Relay Switch OFF) No Functional Error Allowed for t < 100 msV V30.3—0.5VCAN Transceiver V2 for Forced Bus Stand-by Mode (Fail Safe) VRC2 3.0 3.9 4.7V CANH/L Differential Receiver, Threshold VoltageV CANTH -3.2—-2.5V CANH/L Differential Receiver, Dominant to Recessive Threshold (Bus Failures 1, 2, and 5)V CANDRTH-3.2—-2.5VCANH Recessive Output Voltage TX = High, R(RTH) < 4.0 k V CANH——0.2VCANL Recessive Output Voltage TX = High, R(RTH) < 4.0 k V CANLV2-0.2——VCANH Output Voltage, DominantTX = 0 V, BusNormal Mode, I CANH = - 40 mA V CANHV2-1.4——VCANL Output Voltage, DominantTX = 0 V, Bus Normal Mode, I CANL = - 40 mA V CANL——1.4VCANH Output Current Limit (V CANH = 0.0 V, TX = 0)I CANH5075100mACANL Output Current Limit (V CANL = 14 V, TX = 0)I CANL5095130mADetection Threshold for Short Circuit to Battery Voltage Bus Normal ModeV CANH -V CANL7.37.98.9VDetection Threshold for Short Circuit to Battery Voltage Bus Stand-by ModeV CANHV BAT /2+3—V BAT /2+5VCANH Output Current, Failure 3Bus Stand-by Mode V CANH = 12 V I CANHF3—5.010µACANL Output Current, Failure 4Bus Stand-by Mode, V CANL = 0.0 V, V BAT = 12 VI CANLF4—0.02.0µATable 4. Static Electrical Characteristics (continued)Characteristics noted under conditions V BAT , - 40°C ≤ T A ≤ 125°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T A = 25°C under nominal conditions unless otherwise noted.CharacteristicSymbolMinTypMaxUnitELECTRICAL CHARACTERISTICSSTATIC ELECTRICAL CHARACTERISTICSPOWER OUTPUT (CONTINUED)CANL Wake-Up Voltage ThresholdBus Stand-by ModeV WAKEL 2.5 3.3 3.9VCANH Wake-Up Voltage ThresholdBus Stand-by ModeV WAKEH 1.2 2.0 2.7VWake-Up Threshold Difference V WAKEL -V WAKEH0.2——V CANH Single Ended Receiver ThresholdFailures 4, 6, and 7V CANH 1.5 1.85 2.15VCANL Single Ended Receiver ThresholdFailures 3 and 8V CANL 2.8 3.05 3.4VCANL Pull-Up CurrentBus Normal ModeI CANLPU457590µACANH Pull Down CurrentBus Normal ModeI CANLPD457590µA Receiver Differential Input Impedance CANH/CANL R DIFF100—180kΩDifferential Receiver Common Mode Voltage Range V COM-8.0—8.0V RTL to V2 Switch on ResistanceI OUT < -10 mA, Bus Normal Operating ModeR RTL102570ΩRTL to Battery Switch Series ResistanceBus Stand-by ModeR RTL8.012.520kΩRTH to Ground Switch on ResistanceI OUT < 10 mA, All ModesR RTH—2570ΩCONTROL INTERFACEHigh Level Input Voltage VIH0.7 V1—V1 + 0.3 V VCS Threshold for SPI Wake-UpSBC in Sleep Mode, V1 < 1.5 VV CSTH— 2.2—VCS Filter Time for SPI Wake-UpSBC in Sleep Mode, V1 < 1.0 Vt CSFT—— 3.0µsLow Level Input Voltage VIL-0.3—0.3 V1V High Level Input Current on CSV I = 4.0 VI CSH-100—-20µALow Level Input Current on CSV I = 1.0 VI CSL-100—-20µATX High Level Input CurrentV I = 4.0 VI TXH-200-80-25µATX Low Level Input CurrentV I = 1.0 VI TXL-800-320-100µASI, SCLK Input Current0 < V IN < V1I SISLK-10—+10µATable 4. Static Electrical Characteristics (continued)Characteristics noted under conditions V BAT, -40°C ≤ T A ≤ 125°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T A = 25°C under nominal conditions unless otherwise noted.Characteristic Symbol Min Typ Max UnitELECTRICAL CHARACTERISTICSSTATIC ELECTRICAL CHARACTERISTICSCONTROL INTERFACE (CONTINUED)RX, INT, MISO High Level Output Voltage I 0 = -250 µAV OHV1 - 0.9—V1VRX, INT, MISO Low Level Output Voltage I 0 = -1.5 mAV OL0.0—0.9VRX, INT, MISO Tri-Stated SO Output Current 0 V < V SO < V1I Z-2.0—+2.0µARST High Level Input Voltage V IH 0.7 V1—V1 + 0.3 V —RST Low Level Input Voltage V IL -0.3—-0.3 V1V RST High Level Output Current 10.0 < V OUT < 0.5 V1I RSTH1-50-30-10µARST High Level Output Current 20.5 < V OUT < V1I RSTH2—-300—µARST Low Level Output Voltage (I 0 = 1.5 mA)1.0 V < V BAT < 27 VV RST0.0—0.9VLX/Wake-Up Positive Switching Threshold 6.0 V <V BAT < 16 VV WUP3.03.74.5VLX/Wake-Up Negative Switching Threshold 6.0 V <V BAT < 16 V V WUN2.53.03.8VLX/Wake-Up Hysteresis 6.0 V <V BAT < 16 VV HYS—700—mALX/Wake-Up Leakage Current 0 < V WU < V BAT I LXWU -5.0—+5.0µA LX Input Current at 40 VV IN—350600µATable 4. Static Electrical Characteristics (continued)Characteristics noted under conditions V BAT , - 40°C ≤ T A ≤ 125°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T A = 25°C under nominal conditions unless otherwise noted.CharacteristicSymbolMinTypMaxUnitELECTRICAL CHARACTERISTICSDYNAMIC ELECTRICAL CHARACTERISTICSDYNAMIC ELECTRICAL CHARACTERISTICSTable 5. Dynamic Electrical CharacteristicsCharacteristics noted under conditions 7.0 V ≤ V SUP≤ 18 V, - 40°C ≤ T A ≤ 125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T A = 25°C under nominal conditions unless otherwise noted.Characteristic Symbol Min Typ Max Unit MICROCONTROLLER INTERFACEAC CANL/CANH Slew Rates, Rising or Falling Edges, TX from Recessive toDominant StateC LOAD - 10 nF, 133 Ω Termination Resistorst CANRD 3.5 5.010V/µsAC CANL/CANH Slew Rates, Rising or Falling Edges, TX from Dominant toRecessive StateC LOAD - 10 nF, 133 Ω Termination Resistorst CANDR 2.0 3.510V/µsAC Propagation Delay TX to RX LowC LOAD - 10 nF, 133 Ω Termination Resistorst DH— 1.2 2.0µsAC Propagation Delay TX to RX HighC LOAD - 10 nF, 133 Ω Termination Resistorst DL— 2.0 3.0µsWake-Up Filter Time tWUFT8.02038µs RST Duration after V1 High t RES— 1.0—ms SCLK Clock Period t PSCLK500——ns SCLK Clock High Time t WSCLKH175——ns SCLK Clock Low Time t WSCLKL175——ns Falling Edge of CS to Rising Edge of SCLK t LEAD25050—ns Falling Edge of SCLK to Rising Edge of CS t LEAD25050—nsSI to Falling Edge of SCLK t SISU12525—ns Falling Edge of SCLK to SI t SI(HOLD)12525—nsSO Rise Time (C L = 200 pF)t RSO—2575nsSO Fall Time (C L = 200 pF)t FSO—2575ns SI, CS, SCLK Incoming Signal Rise Time t RSI——200ns SI, CS, SCLK Incoming Signal Fall Time t FSI——200—Time from Falling Edge of CS to SOLow Impedance High Impedance t SO(EN)t SO(DIS)——200200nsTime from Rising Edge of SCLK to SO Data Valid0.2 V1 or V2 < SO > 0.8 V1 or V2, C L = 200 pFt VALID—50125—Running Mode Oscillator Tolerance (Normal Request, Normal and Stand-byModes (9))RMOT-12—+12%Software Watchdog Timing 1 (9)tSW1 4.4 5.0 5.6msSoftware Watchdog Timing 2 (9)tSW28.81011.2msSoftware Watchdog Timing 3 (9)tSW317.62022.4msSoftware Watchdog Timing 4 (9)tSW4283236ms Notes9.Software watchdog timing accuracy is based on the running mode oscillator toleranceELECTRICAL CHARACTERISTICSDYNAMIC ELECTRICAL CHARACTERISTICSMICROCONTROLLER INTERFACE (CONTINUED)Software Watchdog Timing 5 (10)t SW544.85158ms Software Watchdog Timing 6 (10)t SW6657483ms Software Watchdog Timing 7 (10)t SW788100112ms Software Watchdog Timing 8 (10).t SW8167190213ms Sleep Mode Oscillator Tolerance (10)SMOT -30—+30%Cyclic Sense/FWU Timing 1 Sleep Mode (10)t CY122.43246.6ms Cyclic Sense/FWU Timing 2 Sleep Mode (10)t CY244.86483.2ms Cyclic Sense/FWU Timing 3 Sleep Mode (10)t CY389.6128166.4ms Cyclic Sense/FWU Timing 4 Sleep Mode (10)t CY4179256333ms Cyclic Sense/FWU Timing 5 Sleep Mode (10)t CY5358512665ms Cyclic Sense/FWU Timing 6 Sleep Mode (10).t CY671710241331ms Cyclic Sense/FWU Timing 7 Sleep Mode (10) t CY7143420482662ms Cyclic Sense/FWU Timing 8 Sleep Mode (10)t CY85734819210650ms Ground Shift Threshold 1 (11)CAN Transceiver Active in Two Wire Operation GS1-1.0-0.7-0.3VGround Shift Threshold 2 (11)CAN Transceiver Active in Two Wire Operation GS2-1.5-1.2-0.8VGround Shift Threshold 3 (11)CAN Transceiver Active in Two Wire Operation GS3-2.0-1.7-1.3VGround Shift Threshold 4 (11)CAN Transceiver Active in Two Wire Operation GS4-2.6-2.2-1.7VBUS TRANSMITTERAC Minimum Dominant Time for Wake-Up on CANL or CANH Bus Stand-by Mode, V BAT = 12 V t WAKE4.0—40µsAC Failure 3 Detection Time Bus Normal Mode t AC3D10—60µsAC Failure 3 Recovery Time Bus Normal Mode t AC3R10—60µsAC Failure 6 Detection Time Bus Normal Mode t AC6D50—400µsAC Failure 6 Recovery Time Bus Normal Modet AC6R150—1000µsAC Failure 4, 7, and 8 Detection Time Bus Normal Modet AC478D0.75—4.0msNotes10.Cyclic sense and forced wake-up timing accuracy are based on the Sleep mode oscillator tolerance.11.No overlap between two adjacent thresholds.Table 5. Dynamic Electrical Characteristics (continued)Characteristics noted under conditions 7.0 V ≤ V SUP ≤ 18 V, - 40°C ≤ T A ≤ 125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T A = 25°C under nominal conditions unless otherwise noted.CharacteristicSymbolMinTypMaxUnitELECTRICAL CHARACTERISTICSDYNAMIC ELECTRICAL CHARACTERISTICSBUS TRANSMITTER (CONTINUED)AC Failure 4, 7, and 8 Recovery Time Bus Normal Modet AC478R10—60µsAC Failure 3, 4, and 7 Detection Time Bus Stand-by Mode, V BAT = 12 V t AC347D0.8—8.0msAC Failure 3, 4 and 7 Recovery Time Bus Stand-by Mode, V BAT = 12 Vt AC347R—2.5—msAC Edge Count Difference Between CANH/CANL for Failures 1, 2, 5 Detection Bus Normal ModeCAN 125D—3.0——AC Edge Count Difference Between CANH/CANL for Failures 1, 2, 5 Recovery Bus Normal ModeCAN 125R—3.0——TX Permanent Dominant Timer Disable Time Bus Normal and Failure Modes t TXD0.75—4.0msPOWER INPUT TIMING V1 Reset Delay Time t D 2.0—20µs V1 Line Regulation9.0 V < V BAT < 16.5, I LOAD = 10 mA t D -152.0+15mVV1 Line Regulation5.5 V < V BAT < 27 V I LOAD = 10 mA t D -5010+50mVV1 Load Regulation1.0 mA < I LOAD < 100 mA t D -50—+50mVV1 Line Ripple Rejection100 Hz, 1.0 V PP on V BAT = 12 V, I LOAD = 100 mA (12)t D 3055—dBV1 Line Transient ResponseV BAT from 12 V to 40 V in 1.0 µs, (10 µF, ESR = 3 Ω)t D —27—mVV1 Load Transient ResponseI LOAD from 10 µA to 100 mA in 1.0 µs (CLOAD = 10 µF, ESR = 3 Ω) (13)t D —400—mVV1 Load Transient ResponseI LOAD from 10 µA to 100 mA in 1.0 µs (CLOAD = 10 µF, ESR= 0.1 Ω)t D—16—mVNotes12.Guaranteed by design. Not production tested.13.This condition does not produce a resetTable 5. Dynamic Electrical Characteristics (continued)Characteristics noted under conditions 7.0 V ≤ V SUP ≤ 18 V, - 40°C ≤ T A ≤ 125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T A = 25°C under nominal conditions unless otherwise noted.CharacteristicSymbolMinTypMaxUnitELECTRICAL CHARACTERISTICS TIMING DIAGRAMSTIMING DIAGRAMSFigure 4. Input Timing Switch CharacteristicsSISCLKCSDon’t Care Don’t CareDon’t CareValidValidt LEAD t WSCLKH t WSCLKLt R t F t LAGt SISUt SI(HOLD)FUNCTIONAL DESCRIPTIONINTRODUCTION FUNCTIONAL DESCRIPTIONINTRODUCTIONThe System Basis Chip (SBC) is an integrated circuit dedicated to car body applications. It includes three main blocks:1. A dual voltage regulator2.Reset, watchdog, wake-up inputs, cyclic wake-up3.CAN low speed fault tolerant physical interfaceSuppliesTwo low drop regulators and one switch to V BAT are provided to supply the ECU microcontroller or peripherals, with independent control and monitoring through SPI.FUNCTIONAL PIN DESCRIPTIONTRANSMIT AND RECEIVE DATA (TX AND RX) The RX and TX pins (receive data and transmit data pins, respectively) are connected to a microcontroller’s CAN protocol handler. TX is an input and controls the CANH and CANL line state (dominant when TX is LOW, recessive when TX is HIGH). RX is an output and reports the bus state.VOLTAGE REGULATOR ONE AND TWO(V1 AND V2)The V1 pin is a 3% low drop voltage regulator dedicated to the microcontroller supply (nominal 5V supply).The V2 pin is a low drop voltage regulator dedicated to the peripherals supply (nominal 5V supply).RESET (RST)The RST (reset) pin is an input/output pin. The typical reset duration from SBC to microcontroller is 1ms. If longer times are required, an external capacitor can be used. SBC provides two RST output pull-up currents. A typical 30µA pull up when Vreset is below 2.5V and a 300uA pull up when reset voltage is higher than 2.5V. RST is also an input for the SBC. It means the MC33389 is forced to Normal Request mode after RST is released by the microcontroller INTERRUPT (INT)The Interrupt pin INT is an output that is set LOW when an interrupt occurs. INT is enabled using the Interrupt Register (INTR). When an interrupt occurs, INT stays LOW until the interrupt source is cleared.INT output also reports a wake-up event.GROUND (GND)This pin is the ground of the integrated circuit.MASTER IN/ SLAVE OUT (MISO)MISO is the Master In Slave Out pin of the serial peripheral interface. Data is sent from the SBC to the microcontroller through the MISO pin.MASTER OUT/ SLAVE IN (MOSI)MOSI is the Master Out Slave In pin of the serial peripheral interface. Control data from a microcontroller is received through this pin.SYSTEM CLOCK (SCLK)This pin clocks the internal shift registers for SPI communication.CHIP SELECT (CS)CS is the Chip Select pin of the serial peripheral interface (SPI). When this pin is LOW, the SPI port of the device is selected.LEVEL 0-2 INPUTS (L0: L2)The L0: L2 pins can be connected to contact switches or the output of other ICs for external inputs. The input states can be read by the SPI. These inputs can be used as wake-up events for the SBC.NO CONNECT (NC)No pin connection.TERMINATION RESISTANCE (HIGH AND LOW?) (RTH AND RTL)External CAN bus high and low termination resistance pins are connected to these pins.CAN HIGH AND CAN LOW OUTPUTS(CANH AND CANL)The CAN High and CAN Low pins are the interfaces to the CAN bus lines. They are controlled by TX input level, and the state of CANH and CANL is reported through RX output. VOLTAGE BATTERY (VBAT)This pin is the voltage supply from the battery.VOLTAGE REGULATOR THREE (V3)This pin is a 10 Ω switch to VBAT, which is used to supply external contacts or relays.。

39352-00中文资料

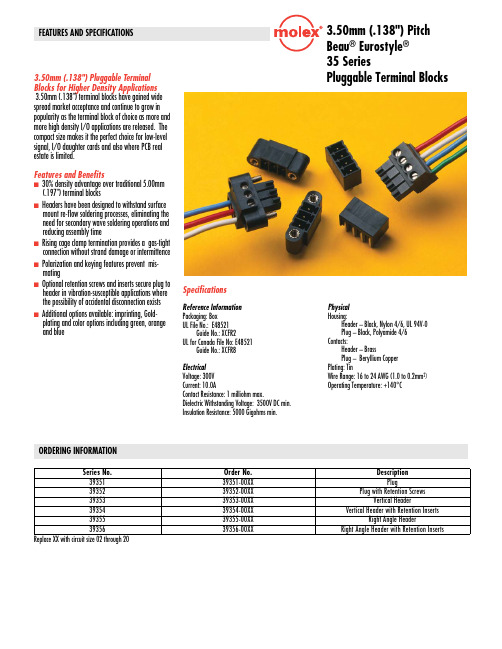

FEATURES AND SPECIFICATIONS3.50mm (.138") Pitch Beau ® Eurostyle ® 35 SeriesPluggable Terminal Blocks3.50mm (.138") Pluggable Terminal Blocks for Higher Density Applications3.50mm (.138") terminal blocks have gained wide spread market acceptance and continue to grow in popularity as the terminal block of choice as more and more high density I/O applications are released. The compact size makes it the perfect choice for low-level signal, I/O daughter cards and also where PCB real estate is limited.Features and Benefits■ 30% density advantage over traditional 5.00mm (.197") terminal blocks■Headers have been designed to withstand surface mount re-flow soldering processes, eliminating the need for secondary wave soldering operations and reducing assembly time■ Rising cage clamp termination provides a gas-tight connection without strand damage or intermittence ■ Polarization and keying features prevent mis-mating■Optional retention screws and inserts secure plug to header in vibration-susceptible applications where the possibility of accidental disconnection exists ■Additional options available: imprinting, Gold-plating and color options including green, orange and blueReplace XX with circuit size 02 through 20Series No.Order No.Description 3935139351-00XX Plug3935239352-00XX Plug with Retention Screws3935339353-00XX Vertical Header3935439354-00XX Vertical Header with Retention Inserts3935539355-00XX Right Angle Header3935639356-00XXRight Angle Header with Retention InsertsORDERING INFORMATIONSpecificationsReference Information Packaging: Box UL File No.: E48521Guide No.: XCFR2UL for Canada File No: E48521Guide No.: XCFR8Electrical Voltage: 300V Current: 10.0AContact Resistance: 1 milliohm max.Dielectric Withstanding Voltage: 3500V DC min.Insulation Resistance: 5000 Gigohms min.Physical Housing:Header – Black, Nylon 4/6, UL 94V-0 Plug – Black, Polyamide 4/6 Contacts:Header – BrassPlug – Beryllium Copper Plating: TinWire Range: 16 to 24 AWG (1.0 to 0.2mm2 )Operating Temperature: +140°C元器件交易网3.50mm (.138") PitchBeau® Eurostyle®35 SeriesPluggable Terminal Blocks APPLICATIONS■Process Controls ■Motors and Drives ■Motion Control■Factory Automation ■Instrumentation ■Security, Alarm and Surveillance ■Signal Conditioning■Scales and Weighing Equipment ■Switching EquipmentAmericas Headquarters Lisle, Illinois 60532 U.S.A. 1-800-78MOLEX amerinfo@ Far East North HeadquartersYamato, Kanagawa, Japan81-462-65-2324feninfo@Far East South HeadquartersJurong, Singapore65-6-268-6868fesinfo@European HeadquartersMunich, Germany49-89-413092-0eurinfo@Corporate Headquarters2222 Wellington Ct.Lisle, IL 60532 U.S.A.630-969-4550Fax:630-969-1352 Visit our Web site at /product/tblocks.htmlOrder No. USA-198 Rev. 1Printed in USA/7.5K/JI/JI/2004.03©2004, Molex 元器件交易网。

AO4459中文资料

AO4459中⽂资料SymbolTyp Max 33406275R θJL 1824Maximum Junction-to-Lead CSteady-State°C/WThermal Characteristics ParameterUnits Maximum Junction-to-AmbientAt ≤ 10s R θJA °C/W Maximum Junction-to-Ambient ASteady-State °C/W AO4459AO4459SymbolMin TypMaxUnits BV DSS -30V -1T J =55°C-5I GSS ±100nA V GS(th)-1.5-1.85-2.5V I D(ON)-30A 3846T J =125°C53685872m ?g FS 11S V SD -0.78-1V I S-3.5A C iss 668830pF C oss 126pF C rss 92pF R g69?Q g (10V)12.716nC Q g (4.5V) 6.4nC Q gs 2nC Q gd 4nC t D(on)7.7ns t r 6.8ns t D(off)20ns t f 10ns t rr 2230ns Q rr15nCTHIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT NOTICE.DYNAMIC PARAMETERS Maximum Body-Diode Continuous CurrentGate resistanceV GS =0V, V DS =0V, f=1MHzV GS =0V, V DS =-15V, f=1MHz Input Capacitance Output Capacitance Turn-On Rise Time Turn-Off DelayTime V GS =-10V, V DS =-15V, R L =2.5?, R GEN =3?Turn-Off Fall TimeTurn-On DelayTime SWITCHING PARAMETERSTotal Gate Charge (4.5V)Gate Source Charge Gate Drain Charge Total Gate Charge (10V)V GS =-10V, V DS =-15V, I D =-6.5Am ?V GS =-4.5V, I D =-5AI S =-1A,V GS =0V V DS =-5V, I D =-6.5AR DS(ON)Static Drain-Source On-ResistanceForward TransconductanceDiode Forward VoltageI DSS µA Gate Threshold Voltage V DS =V GS I D =-250µA V DS =-24V, V GS =0VV DS =0V, V GS =±20V Zero Gate Voltage Drain Current Gate-Body leakage current Electrical Characteristics (T J =25°C unless otherwise noted)STATIC PARAMETERS ParameterConditions Body Diode Reverse Recovery Time Body Diode Reverse Recovery ChargeI F =-6.5A, dI/dt=100A/µsDrain-Source Breakdown Voltage On state drain currentI D =-250µA, V GS =0V V GS =-10V, V DS =-5V V GS =-10V, I D =-6.5AReverse Transfer Capacitance I F =-6.5A, dI/dt=100A/µs A: The value of R θJA is measured with the device mounted on 1in 2FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The value in any a given application depends on the user's specific board design. The current rating is based on the t ≤ 10s thermal resistance rating.B: Repetitive rating, pulse width limited by junction temperature.C. The R θJA is the sum of the thermal impedence from junction to lead R θJL and lead to ambient.D. The static characteristics in Figures 1 to 6 are obtained using < 300µs pulses, duty cycle 0.5% max.E. These tests are performed with the device mounted on 1 in 2FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The SOA curve provides a single pulse rating. Rev0 Sept 2006AO4459AO4459。

M393T5166AZA-CC中文资料